(12) 发明专利

(10) 授权公告号 CN 107430883 B

(45) 授权公告日 2021.03.12

(21) 申请号 201680014624.6

(72) 发明人 Y·陆 X·李

(22) 申请日 2016.02.01

(74) 专利代理机构 上海专利商标事务所有限公司 31100

(65) 同一申请的已公布的文献号

代理人 周敏 陈炜

申请公布号 CN 107430883 A

(51) Int.CI.

G11C 11/16 (2006.01)

G11C 11/56 (2006.01)

(43) 申请公布日 2017.12.01

(56) 对比文件

(30) 优先权数据

US 2013051134 A1, 2013.02.28

14/645,213 2015.03.11 US

CN 101711408 A, 2010.05.19

(85) PCT国际申请进入国家阶段日

CN 103810118 A, 2014.05.21

2017.09.08

CN 102388358 A, 2012.03.21

(86) PCT国际申请的申请数据

CN 102282621 A, 2011.12.14

PCT/US2016/015932 2016.02.01

CN 102334166 A, 2012.01.25

(87) PCT国际申请的公布数据

CN 103858169 A, 2014.06.11

W02016/144436 EN 2016.09.15

审查员 余雯雯

(73) 专利权人 高通股份有限公司

权利要求书4页 说明书17页 附图8页

地址 美国加利福尼亚州

(54) 发明名称

使用串联磁性隧道结的多位自旋转移矩磁阻随机存取存储器STT-MRAM

(57) 摘要

一种设备包括具有第一读取余裕的第一磁性隧道结(MTJ)元件以及具有第二读取余裕的第二MTJ元件。第一读取余裕大于第二读取余裕的两倍。该设备还包括耦合在第一MTJ元件与第二MTJ元件之间的存取晶体管。存取晶体管的栅极耦合至字线。第一MTJ元件、第二MTJ元件和存取晶体管可形成多位自旋转移矩磁阻随机存取存储器(STT-MRAM)存储器单元。

1. 一种设备，包括：

具有第一读取余裕的第一磁性隧道结(MTJ)元件；

具有第二读取余裕的第二MTJ元件，所述第一读取余裕大于所述第二读取余裕的两倍；以及

耦合在所述第一MTJ元件与所述第二MTJ元件之间的存取晶体管，其中所述存取晶体管的栅极耦合至字线，

其中所述第一MTJ元件、所述第二MTJ元件和所述存取晶体管形成多位自旋转移矩磁阻随机存取存储器(STT-MRAM)存储器单元；以及

被配置成将所述STT-MRAM存储器单元的感测出的值与第二值进行比较的电路系统，所述第二值基于所述感测出的值与第一值的比较，

其中所述第一值是与所述第二MTJ元件相关联的第一参考电平，并且所述第二值是与所述第二MTJ元件相关联的第二参考电平，以及

其中所述第一参考电平和所述第二参考电平是从平均参考电平值推导的，所述平均参考电平值从初始化设备确定或者由其它MTJ结构确定。

2. 如权利要求1所述的设备，其特征在于，进一步包括，耦合至所述第一MTJ元件的位线以及耦合至所述第二MTJ元件的源线，其中所述电路系统被进一步配置成基于所述感测出的值与所述第二值的关系来确定所述第二MTJ元件的电阻状态。

3. 如权利要求1所述的设备，其特征在于，所述存取晶体管被配置成响应于字线信号而将所述第一MTJ元件耦合至所述第二MTJ元件。

4. 如权利要求1所述的设备，其特征在于，所述存取晶体管是n型金属氧化物半导体(NMOS)晶体管。

5. 如权利要求1所述的设备，其特征在于，所述存取晶体管是p型金属氧化物半导体(PMOS)晶体管。

6. 如权利要求1所述的设备，其特征在于，所述第一MTJ元件具有第一数据保持时间，并且所述第二MTJ元件具有比所述第一数据保持时间长的第二数据保持时间。

7. 如权利要求1所述的设备，其特征在于，所述第一MTJ元件具有第一大小，并且所述第二MTJ元件具有大于所述第一大小的两倍的第二大小。

8. 如权利要求1所述的设备，其特征在于，所述第二MTJ元件与由所述第一值指示的第一参考电平和由所述第二值指示的第二参考电平相关联，并且其中所述第一MTJ元件与一个参考电平相关联。

9. 如权利要求1所述的设备，其特征在于，进一步包括其中集成有所述第一MTJ元件、所述第二MTJ元件和所述存取晶体管的装置，所述装置选自移动电话、平板设备、机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、通信设备、个人数字助理(PDA)、固定位置数据单元、以及计算机。

10. 一种用于操作包括存取晶体管、第一磁性隧道结(MTJ)元件和第二MTJ元件的设备的方法，所述方法包括：

激活所述存取晶体管，其中所述第一MTJ元件和所述第二MTJ元件响应于所述存取晶体管，其中所述第一MTJ元件具有第一大小，并且其中所述第二MTJ元件具有大于第一大小的两倍的第二大小；以及

通过以下操作确定所述第二MTJ元件的电阻状态：

执行将感测出的值与第一参考值的第一比较；以及

执行将感测出的值与第二参考值的第二比较，其中所述第二参考值基于所述第一比较的结果，

其中所述第一参考值是与所述第二MTJ元件相关联的第一参考电平，并且所述第二参考值是与所述第二MTJ元件相关联的第二参考电平，以及

其中所述第一参考电平和所述第二参考电平是从平均参考电平值推导的，所述平均参考电平值从初始化设备确定或者由其它MTJ结构确定。

11. 如权利要求10所述的方法，其特征在于，进一步包括，在耦合至所述第一MTJ元件的位线处施加特定电流，其中所述存取晶体管经由被施加到所述存取晶体管的栅极的字线信号被激活，并且其中施加所述特定电流发生在确定所述电阻状态之前。

12. 如权利要求10所述的方法，其特征在于，所述第一MTJ元件、所述第二MTJ元件和所述存取晶体管形成多位自旋转移矩磁阻随机存取存储器(STT-MRAM)存储器单元。

13. 如权利要求12所述的方法，其特征在于，所述第一MTJ元件的电阻状态和所述第二MTJ元件的电阻状态基于所述第一MTJ元件的平行状态或反平行状态与所述第二MTJ元件的平行状态或反平行状态的一个或多个组合。

14. 一种装备，包括：

用于存储第一磁状态的第一装置，其中所述用于存储的第一装置具有第一大小；

用于存储第二磁状态的第二装置，其中所述用于存储的第二装置具有大于所述第一大小的两倍的第二大小；

用于将所述用于存储的第一装置和所述用于存储的第二装置耦合的装置，其中所述用于耦合的装置耦合至字线，并且其中所述用于存储的第一装置、所述用于存储的第二装置、和所述用于耦合的装置形成多位自旋转移矩磁阻随机存取存储器(STT-MRAM)存储器单元；以及

用于将所述STT-MRAM存储器单元的感测出的值与第二值进行比较的装置，所述第二值基于所述感测出的值与第一值的比较，

其中所述第一值是与所述第二装置相关联的第一参考电平，并且所述第二值是与所述第二装置相关联的第二参考电平，以及

其中所述第一参考电平和所述第二参考电平是从平均参考电平值推导的，所述平均参考电平值从初始化设备确定或者由其它MTJ结构确定。

15. 如权利要求14所述的装备，其特征在于，进一步包括，耦合至所述用于存储的第一装置的位线以及耦合至所述用于存储的第二装置的源线，所述用于耦合的装置被配置成响应于字线信号而将所述用于存储的第一装置耦合至所述用于存储的第二装置，所述第一值指示与所述用于存储的第二装置相关联的第一参考电平，所述第二值指示与所述用于存储的第二装置相关联的第二参考电平，并且所述用于比较的装置被进一步配置成基于所述感测出的值与所述第二值的关系来确定所述用于存储的第二装置的电阻状态。

16. 一种装置，包括：

第一磁性隧道结(MTJ)子阵列，其由存储器阵列的多个第一MTJ元件形成；以及

第二MTJ子阵列，其由所述存储器阵列的多个第二MTJ元件形成，

其中所述第一MTJ子阵列被配置成基于用于第一存储器使用的第一参数集操作，并且所述第二MTJ子阵列被配置成基于用于不同于所述第一存储器使用的第二存储器使用的第二参数集操作；以及

被配置成将与所述多个第二MTJ元件中的一MTJ元件相关联的感测出的值与第二值进行比较的电路系统，所述第二值基于所述感测出的值与第一值的比较，其中所述多个第一MTJ元件中的每一个MTJ元件具有第一读取余裕，其中所述多个第二MTJ元件中的每一个MTJ元件具有第二读取余裕，并且其中所述第一读取余裕大于所述第二读取余裕的两倍，

其中所述第一值是与所述多个第二MTJ元件中的所述MTJ元件相关联的第一参考电平，并且所述第二值是与所述多个第二MTJ元件中的所述MTJ元件相关联的第二参考电平，以及

其中所述第一参考电平和所述第二参考电平是从平均参考电平值推导的，所述平均参考电平值从初始化设备确定或者由其它MTJ结构确定。

17. 如权利要求16所述的装置，其特征在于，所述电路系统被进一步配置成基于所述感测出的值与所述第二值的关系来确定所述第二MTJ元件的电阻状态，所述多个第一MTJ元件中的每一个MTJ元件具有第一大小，并且所述多个第二MTJ元件中的每一个MTJ元件具有大于所述第一大小的两倍的第二大小。

18. 如权利要求16所述的装置，其特征在于，进一步包括，存储器控制器，其被配置成寻址所述第一MTJ子阵列的所述多个第一MTJ元件中的每一者以及所述第二MTJ子阵列的所述多个第二MTJ元件中的每一者。

19. 如权利要求16所述的装置，其特征在于，进一步包括，存储器控制器，其被配置成基于在所述存储器控制器处从中央处理单元(CPU)接收到的优先级指示符在所述第一MTJ子阵列处或在所述第二MTJ子阵列处存储数据，所述优先级指示符指示与要被存储的数据相关联的优先级水平。

20. 如权利要求16所述的装置，其特征在于，所述第二MTJ子阵列被配置成存储作为被存储在所述第一MTJ子阵列处的对应数据的复制值的数据值。

21. 如权利要求16所述的装置，其特征在于，所述第一MTJ子阵列被配置成操作为数据高速缓存。

22. 如权利要求16所述的装置，其特征在于，所述第二MTJ子阵列被配置成操作为用于所述第一MTJ子阵列的临时存储阵列。

23. 如权利要求16所述的装置，其特征在于，所述第二MTJ子阵列被配置成存储被用作电子设备的休眠模式操作的一部分的数据。

24. 如权利要求16所述的装置，其特征在于，所述第二MTJ子阵列被配置成存储被用作电子设备的初始化操作的一部分的数据。

25. 如权利要求16所述的装置，其特征在于，所述第一参数集基于所述多个第一MTJ元件中的每一者的物理特性，并且其中所述第二参数集基于所述多个第二MTJ元件中的每一者的物理特性。

26. 如权利要求25所述的装置，其特征在于，所述第一MTJ元件的物理特性包括第一大小，并且其中所述第二MTJ元件的物理特性包括大于所述第一大小的两倍的第二大小。

27. 如权利要求16所述的装置，其特征在于，所述第一MTJ子阵列和所述第二MTJ子阵列被集成在至少一个管芯中。

28. 如权利要求16所述的装置,其特征在于,进一步包括其中集成有所述第一MTJ子阵列和所述第二MTJ子阵列的设备,所述设备选自移动电话、平板设备、机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、通信设备、个人数字助理(PDA)、固定位置数据单元、以及计算机。

29. 一种存储指令的非瞬态计算机可读介质,所述指令在由装置的处理器执行时使得所述处理器执行包括以下的操作:

激活存取晶体管,其中所述装置处的第一MTJ元件和第二MTJ元件响应于所述存取晶体管,其中所述第一MTJ元件具有第一大小,并且其中所述第二MTJ元件具有大于第一大小的两倍的第二大小;以及

通过以下操作确定所述第二MTJ元件的电阻状态:

执行将感测出的值与第一参考值的第一比较;以及

执行将感测出的值与第二参考值的第二比较,其中所述第二参考值基于所述第一比较的结果,

其中所述第一参考值是与所述第二MTJ元件相关联的第一参考电平,并且所述第二参考值是与所述第二MTJ元件相关联的第二参考电平,以及

其中所述第一参考电平和所述第二参考电平是从平均参考电平值推导的,所述平均参考电平值从初始化设备确定或者由其它MTJ结构确定。

30. 如权利要求29所述的非瞬态计算机可读介质,其特征在于,所述操作进一步包括基于指示与要被存储的数据相关联的优先级水平的优先级指示符在所述第一MTJ子阵列处或在所述第二MTJ子阵列处存储数据。

## 使用串联磁性隧道结的多位自旋转移矩磁阻随机存取存储器 STT-MRAM

[0001] I. 优先权要求

[0002] 本申请要求共同拥有的于2015年3月11日提交的美国非临时专利申请No.14/645,213的优先权,该非临时专利申请的内容通过援引全部明确纳入于此。

[0003] II. 领域

[0004] 本公开一般涉及具有子阵列的多位自旋转移矩磁阻随机存取存储器(STT-MRAM)。

[0005] III. 相关技术描述

[0006] 技术进步已产生越来越小且越来越强大的计算设备。例如,各种各样的便携式个人计算设备(包括无线电话,诸如移动和智能电话、平板以及膝上型计算机)较小、轻量且易于由用户携带。这些设备可在无线网络上传达语音和数据分组。另外,许多此类设备纳入附加功能性,诸如数码相机、数码摄像机、数字记录器以及音频文件播放器。同样,此类设备可以处理可执行指令,包括可被用于访问因特网的软件应用,诸如web浏览器应用。如此,这些设备可包括显著的计算能力。

[0007] 电子设备(诸如,移动电话)可包括各自具有不同使用的单独类型的存储器阵列。例如,移动电话可具有操作为用于快速短期数据存储的高速缓存存储器(例如,静态随机存取存储器(SRAM))的单独存储器阵列、和操作为用于长期数据存储的主存储器(例如,动态随机存取存储器(DRAM))的另一单独存储器阵列、和/或操作为片外非瞬态存储器(NVM)的其他单独存储器阵列。维持具有不同类型的存储器使用的单独存储器阵列可要求添加的芯片面积和功率使用。

[0008] IV. 概述

[0009] 一种多位自旋转移矩磁阻随机存取存储器(STT-MRAM)可被配置成用于电子设备(例如,移动电话)上的多个存储器应用(例如,高速缓存、主存储器或NVM)。例如,多位STT-MRAM单元的磁性隧道结(MTJ)元件可被配置成具有不同的读取余裕以及被调整成适应特定存储器使用的其他区分性操作参数。例如,多位STT-MRAM单元的存储器阵列可包括MTJ元件的子阵列,每个子阵列被配置成用于特定存储器使用。

[0010] 在特定方面,一种设备包括具有第一读取余裕的第一MTJ元件。该设备还包括具有第二读取余裕的第二MTJ元件。第一读取余裕大于第二读取余裕的两倍。该设备还包括耦合在第一MTJ元件与第二MTJ元件之间的存取晶体管。存取晶体管具有耦合至字线的栅极。第一MTJ元件、第二MTJ元件和存取晶体管形成多位STT-MRAM存储器单元。

[0011] 在另一特定方面,一种操作包括存取晶体管、第一MTJ元件和第二MTJ元件的设备的方法包括激活存取晶体管。第一MTJ元件与第二MTJ元件响应于存取晶体管。第一MTJ元件具有第一大小,并且第二MTJ元件具有大于第一大小的两倍的第二大小。该方法还包括通过执行感测出的值与第一参考值的第一比较和执行感测出的值与第二参考值的第二比较来确定第二MTJ元件的电阻状态。第二参考值基于第一比较的结果。

[0012] 在另一特定方面,一种装备包括用于存储第一磁状态的第一装置。用于存储的第一装置具有第一大小。该装备还包括用于存储第二磁状态的第二装置。用于存储的第二装

置具有大于第一大小的两倍的第二大小。该装备还包括用于将用于存储的第一装置和用于存储的第二装置耦合的装置。该用于耦合的装置耦合至字线。用于存储的第一装置、用于存储的第二装置、和所述用于耦合的装置形成多位STT-MRAM存储器单元。

[0013] 在另一特定方面，一种装置包括由存储器阵列的多个第一MTJ元件形成的第一MTJ子阵列。该装置还包括由所述存储器阵列的多个第二MTJ元件形成的第二MTJ子阵列。第一MTJ子阵列被配置成基于用于第一存储器使用的第一参数集操作，并且第二MTJ子阵列被配置成基于用于不同于第一存储器使用的第二存储器使用的第二参数集操作。

[0014] 由至少一个所公开的方面提供的一个特定优点在于与将单独的存储器阵列用于单独的存储器使用相比，减小了芯片大小和功耗。多位STT-MRAM存储器单元可包括具有被调整以适应特定存储器使用的区分性操作参数的子阵列。存储器单元阵列可包括该阵列内的子阵列，这些子阵列各自具有特定存储器使用。具有特定存储器使用下的存储器子阵列的单个存储器阵列的使用可比多个单独的存储器设备的使用消耗较小芯片面积并利用较少功率来用于数据存取和存储操作。

[0015] 本公开的其他方面、优点和特征将在阅读了整个申请后变得明了，整个申请包括以下章节：附图简述、详细描述、以及权利要求书。

[0016] V. 附图简述

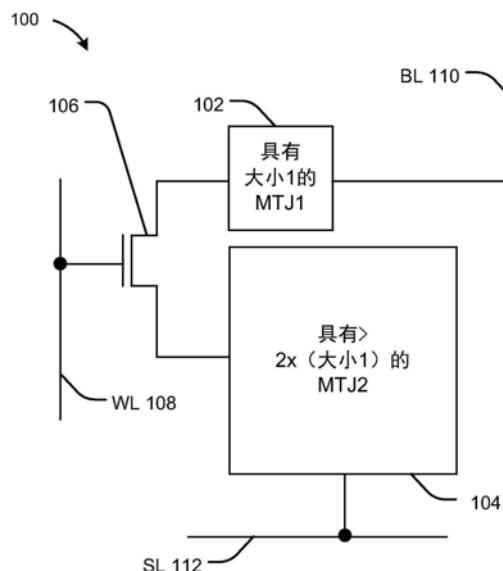

[0017] 图1是解说设备的特定方面的框图；

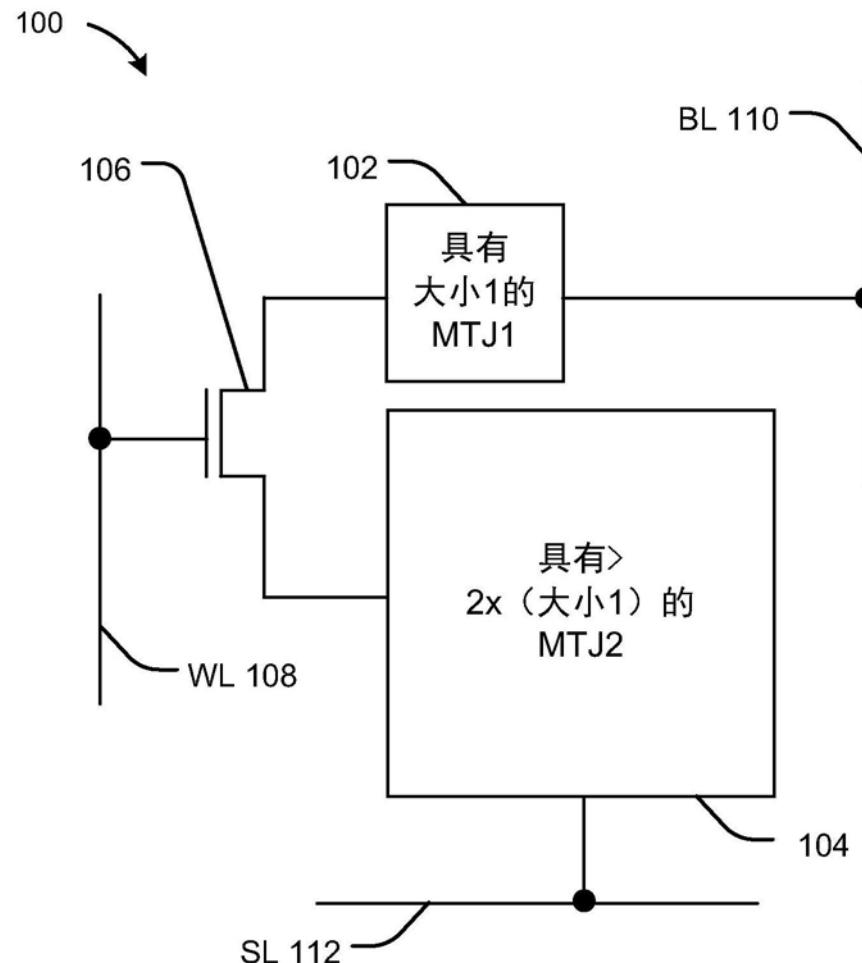

[0018] 图2是描绘存储器阵列的一部分的框图；

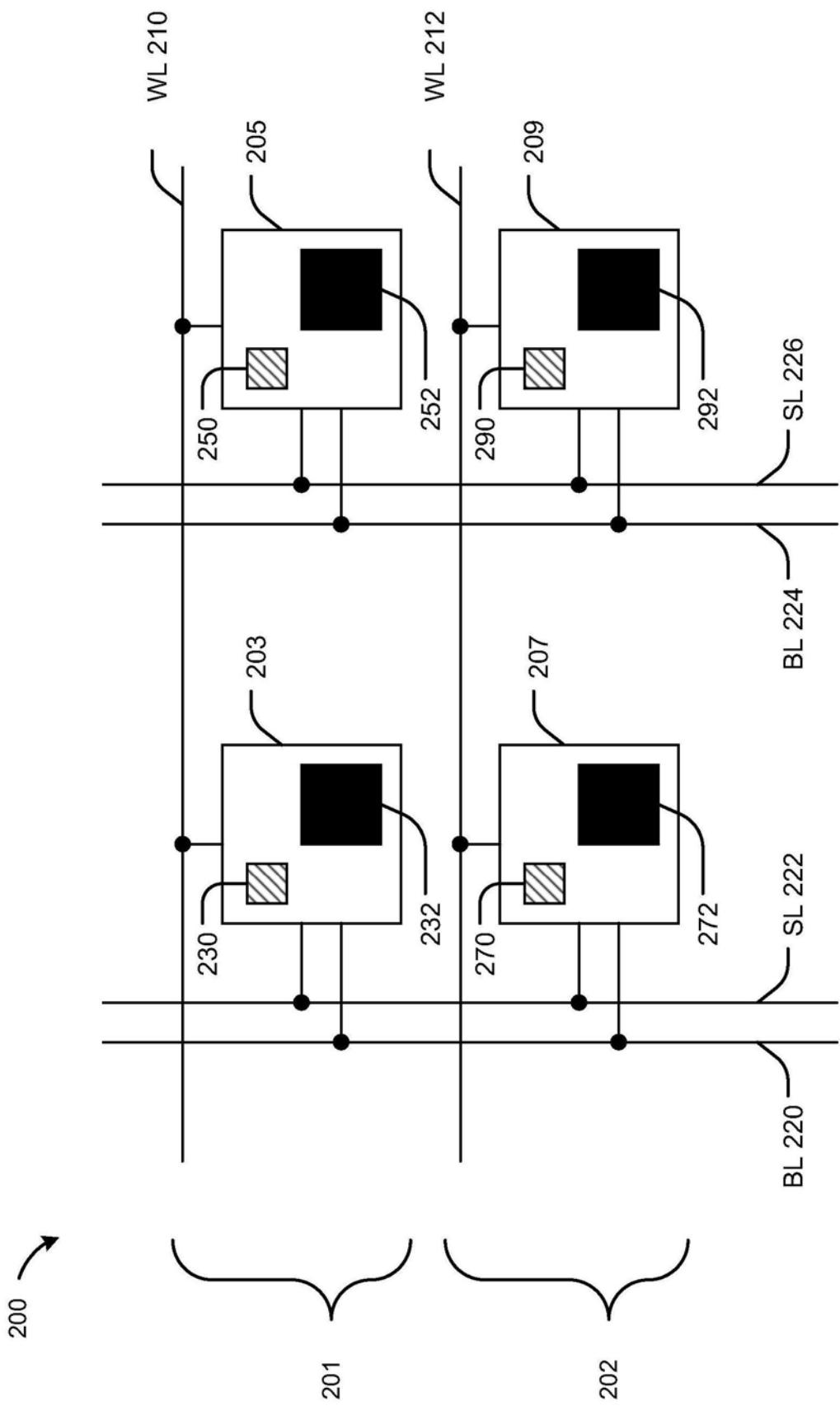

[0019] 图3A是解说具有存储器子阵列的系统的框图；

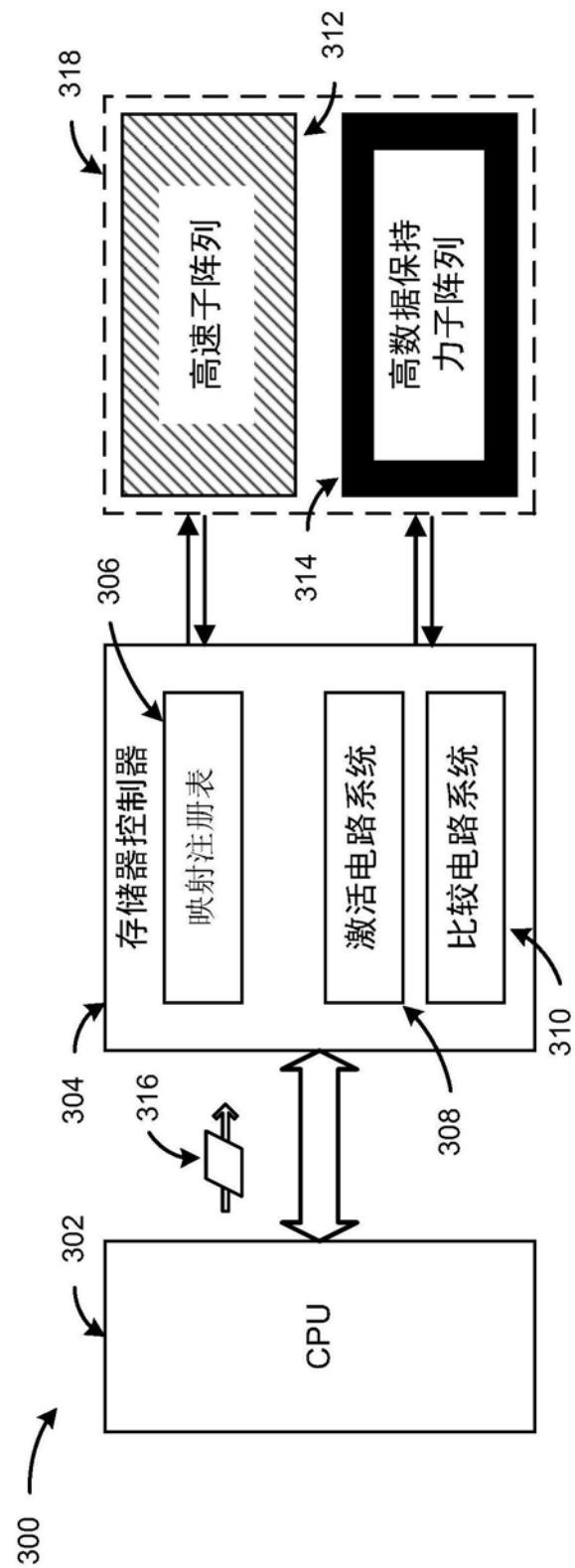

[0020] 图3B是解说具有子阵列的存储器阵列的框图；以及

[0021] 图4是解说操作设备的方法的特定方面的流程图；

[0022] 图5A是解说逻辑状态到设备的平行和反平行状态的特定映射的图表；

[0023] 图5B是解说读取设备(诸如，参照图5A描述的设备)的方法的示图；

[0024] 图5C是解说逻辑状态到设备的平行和反平行状态的另一映射的图表；

[0025] 图5D是解说读取设备(诸如，参照图5C描述的设备)的方法的示图；以及

[0026] 图6是解说无线通信设备的特定方面的框图。

[0027] VI. 详细描述

[0028] 参照图1，示出了设备100的特定解说性方面。设备100可以是多位自旋转移矩磁阻随机存取存储器(STT-MRAM)存储器单元。设备100可被集成在管芯(例如，半导体管芯)内。

[0029] 设备100包括第一磁性隧道结(MTJ)元件102、第二MTJ元件104、字线(WL)108、位线(BL)110、源线(SL)112、以及存取晶体管106。第一MTJ元件102耦合至位线110，并且第二MTJ元件102耦合至源线112。

[0030] 第一MTJ元件102可具有第一读取余裕( $\Delta R$ )，其大于第二MTJ元件104的第二读取余裕的两倍。例如，第一和第二MTJ元件102、104的大小可与特定读取余裕相关联。基于MTJ元件102、104的大小之差，MTJ元件102、104可具有彼此不同的操作参数或特性(例如，读取余裕、读/写速度、数据保持力)。例如，第二MTJ元件104可具有大于第一MTJ元件102的大小的两倍的大小。MTJ元件102、104的大小之差可导致第一MTJ元件102具有大于第二MTJ元件104的第二读取余裕的两倍的第一读取余裕。

[0031] 如本文所使用的，MTJ元件相对于另一MTJ元件的“大小”可指代使得MTJ元件具有

比另一MTJ元件的读取余裕大的读取余裕的MTJ元件的一个或多个尺寸。例如，第二MTJ元件104可具有大于第一MTJ元件102的长度的两倍的长度、大于第一MTJ元件102的高度的两倍的高度、大于第一MTJ元件102的宽度的两倍的宽度，或其组合。在以上示例中的每一者中，第二MTJ元件104的大小比第一MTJ元件102的大小大，并且第二MTJ元件104的读取余裕大于第一MTJ元件102的读取余裕的两倍。

[0032] 存取晶体管106可以是在第一MTJ元件102与第二MTJ元件104之间串联耦合的n型金属氧化物半导体(NMOS)晶体管。替换地，存取晶体管106可以是p型金属氧化物半导体(PMOS)晶体管。存取晶体管106可包括耦合到字线108的栅极。存取晶体管106可被来自字线108的被施加到存取晶体管106的栅极的字线信号激活。响应于来自字线108的字线信号，存取晶体管106可被配置成选择性地将第一MTJ元件102耦合至第二MTJ元件104以用于读或写操作。在与第一MTJ元件102相关联的特定读电流(或特定写电流)穿过位线110或源线112时，读(或写)操作可在第一MTJ元件102处执行。在与第二MTJ元件104相关联的特定读电流(或特定写电流)穿过位线110或源线112时，读(或写)操作可在第二MTJ元件104处执行。

[0033] 第一MTJ元件102、第二MTJ元件104和存取晶体管106可形成多位STT-MRAM存储器单元，其中数据可被存储在第一和第二MTJ元件102、104的电阻状态(例如，逻辑状态)的形式中。例如，存取晶体管106可被配置成耦合第一MTJ元件102和第二MTJ元件104以提供2位STT-MRAM存储器单元，其具有对应于四个逻辑状态(例如，逻辑状态“00”、“01”、“10”和“11”)的四个可能的电阻状态。

[0034] 在存取晶体管106经由施加在字线108的字线信号激活时，可发生从一个电阻状态到另一电阻状态的改变。例如，通过在位线110处或源线112处施加对应于第一MTJ元件102的特定写电流(例如，具有阈值幅值的写电流)以感生第一MTJ元件102的磁极性的改变时，可发生第一MTJ元件102的电阻状态的改变。通过在位线110处或源线112处施加对应于第二MTJ元件104的第二特定写电流(例如，具有阈值幅值的写电流)以感生第二MTJ元件104的磁极性的改变时，可发生第二MTJ元件104的电阻状态的改变。

[0035] 第一MTJ元件102和第二MTJ元件104可各自被配置成具有不同的操作参数。例如，用于改变MTJ元件的磁极性的阈值电流可以正面地取决于MTJ元件的大小(例如，一个或多个尺寸)。由于第二MTJ元件104具有大于第一MTJ元件102的大小的两倍的大小，因此用于改变第二MTJ元件104的磁极性的阈值电流可大于用于改变第一MTJ元件102的磁极性的阈值电流。

[0036] 基于大小之差，第一和第二MTJ元件102、104可具有彼此不同的其他操作参数或特性。例如，第二MTJ元件104可具有比第一MTJ元件102的数据保持参数(例如，能量势垒(E<sub>b</sub>))大的数据保持参数。在该示例中，第二MTJ元件104的较大数据保持参数提供了比第一MTJ元件102的数据保持时间长的第二MTJ元件104的数据保持时间。

[0037] 第一和第二MTJ元件102、104的不同操作参数或特性可使得第一和第二MTJ元件102、104能够被定制化以用于不同存储器使用。例如，具有比第一MTJ元件102大的数据保持力的第二MTJ元件104可保持数据达比第一MTJ元件102长的时间历时并且被配置成操作为长期数据存储元件。作为另一示例，具有比第二MTJ元件104大的读取余裕( $\Delta R$ )的第一MTJ元件102可提供较短的读/写历时，并且被配置成操作为快速存取存储元件。

[0038] 除了大小之外，第一和第二MTJ元件102、104可分开或组合地采用其他配置以达成

如上所述的不同的操作参数或特性。例如，第一MTJ元件102可包括与第二MTJ元件104不同的材料。作为另一示例，第一和第二MTJ元件102、104可具有不同的物理排列(例如，可以为平面或多维的排列)。

[0039] 第一MTJ元件102和第二MTJ元件104可各自包括“固定层”和“自由层”。自由层相对于固定层的特定磁取向导致MTJ元件的平行或反平行状态。第一和第二MTJ元件102、104的平行和反平行状态的特定组合可对应于特定电阻状态(例如，代表四个逻辑状态“00”、“01”、“10”和“11”的电阻状态)。

[0040] 在操作期间，可通过以下操作向第一MTJ元件102或第二MTJ元件104存储数据：在存取晶体管106经由在字线108处施加的字线信号激活时在位线110或源线112处施加特定写电流以感生第一和第二MTJ元件102、104的磁极性的改变。例如，在向第一MTJ元件102存储数据时，特定写电流(例如，超过与第一MTJ元件102相关联的阈值电流的电流)可流过位线110、第一和第二MTJ元件102、104以及源线112以改变第一MTJ元件102的磁极性。基于第一MTJ元件102的大小，用于向第一MTJ元件102写入的特定写电流可能小于改变第二MTJ元件104的磁极性所需的第二特定写电流(例如，超过与第二MTJ元件104相关联的阈值电流的电流)。在向第一MTJ元件102写入时，用于向第一MTJ元件102写数据的较小写电流不改变第二MTJ元件104的电阻状态(例如，逻辑状态)。

[0041] 由于第一和第二MTJ元件102、104具有不同大小或不同特性，所以向第二MTJ元件104写入可能需要比被用于向第一MTJ元件102写入的电流大的写电流。用来向第二MTJ元件104写入的较大写电流可改变第一MTJ元件102的电阻状态(例如，扰乱逻辑状态)。为了计及对第一MTJ元件102的可能“扰乱”，向第二MTJ元件104存储数据(例如，对第二MTJ元件104的写操作)可包括在向第二MTJ元件104写入之前发起“读及写回”过程。例如，在向第二MTJ元件104写入之前，可执行第一MTJ元件102的读操作以读取第一MTJ元件102的值(例如，读取值可被存储在存储器控制器处或者存储器控制器可访问的另一存储区域处)。在向第二MTJ元件104写入之后，第一MTJ元件102的可能已经被扰乱的电阻状态(例如，逻辑状态)可通过将先前读取的值写回第一MTJ元件102(例如，由存储器控制器控制的“写回”操作)来恢复。

[0042] 可通过施加通过位线110或源线112的特定读电流并感测与第一MTJ元件102相关联的电流值来从第一MTJ元件102读取数据。通过将感测出的电流值同与第一MTJ元件102相关联的特定参考电平进行比较，可确定第一MTJ元件102的特定电阻状态(例如，逻辑状态)。例如，在读取第一MTJ元件102时，与第一MTJ元件102相关联的特定读电流可通过位线110、第一和第二MTJ元件102、104以及源线112。第一MTJ元件102的电流值可被感测(例如，通过感测放大器或者在第一MTJ元件102外围的其他感测电路系统)。感测出的值可同与第一MTJ元件102相关联的特定参考值进行比较以确定第一MTJ元件102的特定电阻状态(例如，逻辑状态)。在该情形中，第一MTJ元件102被读取，而第二MTJ元件104未被读取。

[0043] 与第一MTJ元件102相关联的电阻状态(例如，逻辑状态)的改变可对应于逻辑状态改变。在解说性而非限定性示例中，第一MTJ元件102的电阻状态的改变可对应于从“01”到“11”或从“00”到“10”、或者反之的逻辑状态改变(即，第一MTJ元件102的电阻状态可指示位序列的最高有效位(MSB))。在另一解说性而非限定性示例中，第一MTJ元件102的电阻状态的改变可对应于从“00”到“11”或从“10”到“11”、或者反之的逻辑状态改变(即，第一MTJ元件102的电阻状态可指示位序列的最低有效位(LSB))。确定第一MTJ元件102的电阻状态可

采用一个或多个比较设备(例如,一个或多个比较器或感测放大器)以将与第一MTJ元件102相关联的感测出的值同与第一MTJ元件102相关联的参考电平进行比较。

[0044] 在特定方面,可通过施加通过位线110或源线112的特定读电流并感测与第二MTJ元件104相关联的电流值来从第二MTJ元件104读取数据。用来读取第二MTJ元件104的特定读电流可以大于用来读取第一MTJ元件102的读电流。读取第二MTJ元件104可利用双比较方法来确定第二MTJ元件104的电阻状态(例如,逻辑状态)。通过将感测出的第二MTJ元件104的电流值与同第二MTJ元件104相关联的特定参考电平进行比较,可确定第二MTJ元件104的特定电阻状态(例如,逻辑状态)。

[0045] 例如,与第二MTJ元件104相关联的特定读电流可通过位线110、第一和第二MTJ元件102、104和源线112。第二MTJ元件104的电流值可被感测,并且感测出的电流值可被用作同与第二MTJ元件104相关联的第一参考值的第一比较的一部分。第一比较的结果可指示第二MTJ元件104的可能电阻状态。基于第一比较的结果,感测出的电流值可被用作同与第二MTJ元件104相关联的第二参考值的第二比较的一部分以从第一比较指示的可能电阻状态确定第二MTJ元件104的电阻状态(例如,逻辑状态)。与第二MTJ元件104相关联的电阻状态(例如,逻辑状态)的改变可对应于逻辑状态改变。在解说性而非限定性示例中,第二MTJ元件104的电阻状态的改变可对应于从“00”到“01”的逻辑状态改变或从“10”到“11”的改变。

[0046] 确定第二MTJ元件104的电阻状态可采用双比较操作,其可使用与第二MTJ元件104相关联的至少两个不同的参考电平值。第二参考电平值可以大于第一参考电平值。在确定第二MTJ元件104的电阻状态时,双比较操作可采用使用与第二MTJ元件104相关联的两个参考电平值和与第一MTJ元件102相关联的一个参考电平值的组合的其他“选项”,如参照图5A、5B、5C和5D描述的。

[0047] 与第一和第二MTJ元件102、104相关联的参考电平值可被存储在设备100的外围(例如,存储在设备100的外围的存储器控制器处)。在另一方面,参考电平值可从平均参考电平值推导,该平均参考电平值从“初始化”设备(例如,特定测试设备100)确定。替换地,该参考电平可由其他存储器单元或其他MTJ结构(未示出)确定。

[0048] 第一和第二MTJ元件102、104的读和写操作可由可在第一和第二MTJ元件102、104的外围的电路系统(未示出)执行。例如,该外围电路系统可包括但不限于任何数目的存储器控制器、解码器、感测放大器、寄存器或可被用于存储器元件的读和写操作的其他设备。例如,第一和第二MTJ元件102、104的感测操作可由感测放大器或者能够感测MTJ元件的电流值的其他设备执行。第一和第二MTJ元件102、104的比较操作可由能够将感测出的值同与MTJ元件102、104相关联的参考值进行比较的一个或多个设备(例如,在第一和第二MTJ元件102、104的外围的比较器)执行。在非限定性示例中,与第一和第二MTJ元件102、104相关联的比较操作可由被配置成执行感测操作和比较操作两者的一个或多个感测放大器执行。

[0049] 通过将第二MTJ元件104配置成具有大于第一MTJ元件102的大小的两倍的大小,第一和第二MTJ元件可具有有助于不同存储器使用的不同操作参数。由多个双存储器使用设备(例如,设备100)形成的双存储器使用存储器阵列可被提供,如参照图2描述的。

[0050] 参照图2,示出了存储器阵列的一部分的细节并将其一般地指定为200。存储器阵列可包括一个或多个存储器设备(例如,存储器设备203、205、207和209)。存储器设备203、205、207和209可各自对应于图1的设备100。例如,存储器设备203、205、207和209可各自对

应于多位STT-MRAM存储器单元。

[0051] 存储器阵列的第一行201可包括存储器设备205。存储器设备205可与存储器阵列的第一行201的其他存储器设备(例如,存储器设备203)共享字线(WL)210。存储器设备205还可与存储器阵列的一存储器设备列的其他存储器设备(例如,存储器设备209)共享位线(BL)224和源线(SL)226。存储器阵列的第二行202可包括存储器设备209。存储器设备209可与存储器阵列的第二行202的其他存储器设备(例如,存储器设备207)共享字线212。存储器设备207还可与存储器阵列的一存储器设备列的其他存储器设备(例如,存储器设备203)共享位线220和源线222。字线210、212、位线220、224和源线222、226中的任一者的结构和操作可以如参照图1的字线108、位线110和源线112描述的,具有相应的字线到字线、位线到位线、和源线到源线对应性。

[0052] 存储器设备203、205、207和209中的每一者可包括相应的第一MTJ元件和第二MTJ元件,其可被包括在存储器阵列的第一和第二MTJ子阵列中。例如,存储器设备203、205、207和209的多个第一MTJ元件230、250、270和290(例如,条纹框)可各自具有大致第一大小并且可形成存储器阵列的第一MTJ子阵列的一部分。第一MTJ元件230、250、270和290可各自对应于图1的第一MTJ元件102。存储器设备203、205、207和209的多个第二MTJ元件232、252、272和292(例如,实心黑框)可各自具有大致大于第一大小的两倍的第二大小并且可形成存储器阵列的第二MTJ子阵列的一部分。第二MTJ元件232、252、272和292可各自对应于图1的第二MTJ元件104。多个第一MTJ元件和第一MTJ子阵列可具有与第一大小相关联的操作参数。多个第二MTJ元件和第二MTJ子阵列可具有与第二大小相关联的操作参数。

[0053] 基于第一和第二MTJ子阵列的操作参数,第一和第二MTJ子阵列可被配置成用于特定存储器使用。例如,与第一MTJ子阵列相关联的特定读取余裕( $\Delta R$ )参数可提供较短的读/写历时,其使得第一MTJ子阵列能够操作为快速/频繁存取阵列。作为另一示例,与第二MTJ子阵列相关联的数据保持参数可提供较长的数据保持历时,其使得第二MTJ子阵列能够操作为长期存储阵列。操作为长期存储阵列,第二MTJ子阵列可被用于长期数据存储(例如,用于封包使用的冗余/修整数据)或长期代码存储(例如,引导代码存储)。作为长期存储阵列,第二MTJ子阵列可比第一MTJ子阵列利用较少检错和纠错(ECC)或具有较少数据冗余需求。

[0054] 第一MTJ子阵列和第二MTJ子阵列可容适其他存储器使用。例如,在被配置为快速存取阵列时,第一MTJ子阵列可被用作数据高速缓存(例如,级别1高速缓存)。在被配置为长期存储阵列时,第二MTJ子阵列可被用作用于第一MTJ子阵列的临时存储阵列。第二MTJ子阵列还可被用来存储被用作电子设备的休眠模式操作的一部分的数据、或者被用作电子设备的初始化操作的一部分的数据(例如,用于初始化高速缓存阵列状态或处理器状态的数据)。

[0055] 在操作期间,可在所选存储器设备行的一个或多个存储器设备处执行写操作。写操作可包括向所选行的一个或多个存储器设备的第一或第二MTJ元件写入。例如,可在字线210处提供指示与存储器阵列的第一行201的存储器设备(例如,存储器设备203和205)相对应的写请求的信号(例如,电压)。字线210处提供的信号可以激活第一行201的存储器设备(例如,存储器设备203和205)中的每一者的存取晶体管(未示出)的栅极。作为向存储器设备205写入的示例,可通过提供用于向存储器设备205的第一MTJ元件250写入的特定写电流在第一MTJ元件250处存储数据值。该特定写电流可通过位线224、第一和第二MTJ元件250、

252以及源线226。用于向第一MTJ元件250写入的特定写电流可以小于用来向第二MTJ元件252写入的写电流。

[0056] 作为向存储器设备203写入的示例,可通过提供用于向存储器设备203的第二MTJ元件232写入的写电流以穿过位线220、第一和第二MTJ元件230、232以及源线222来在第二MTJ元件232处存储数据值。用于向第二MTJ元件232写入的写电流可能足够大到向第一和第二MTJ元件230、232两者写入,并且可“扰乱”在第一MTJ元件230处存储的值。因此,在向第二MTJ元件232写入之前,可在第一MTJ元件230处执行读操作。在向第二MTJ元件232写入之后,第一MTJ元件230的先前被读取的电阻状态(例如,逻辑状态)可被恢复(例如,通过向第一MTJ元件230重写该值以补偿由向第二MTJ元件232写入导致的扰乱效应)。

[0057] 可在所选存储器设备行的一个或多个存储器设备处执行读操作。读操作可包括从所选行的一个或多个存储器设备的第一或第二MTJ元件读取。例如,可在字线212处提供可指示与存储器阵列的第二行202的存储器设备(例如,存储器设备207和209)相对应的读请求的信号(例如,电压)。字线212处提供的信号可以激活第二行202的存储器设备(例如,存储器设备207和209)中的每一者的存取晶体管(未示出)的栅极。

[0058] 作为从存储器设备209读取的示例,存储在存储器设备209的第一MTJ元件290处的数据值可通过提供与第一MTJ元件290相关联的读电流以通过位线224、第一和第二MTJ元件290、292以及源线226来读取。第一MTJ元件290的电流值可被感测,并且该电流值可被用作同与第一MTJ元件290相关联的参考值的比较的一部分。基于该比较,可确定第一MTJ元件290的电阻状态(例如,逻辑状态)。与第一MTJ元件290相关联的读电流可以小于用来读取第二MTJ元件292的读电流。

[0059] 作为从存储器设备207读取的示例,存储在存储器设备207的第二MTJ元件272处的数据值可通过提供与第二MTJ元件272相关联的通过位线220、第一和第二MTJ元件270、272以及源线222的读电流来读取。与第二MTJ元件272相关联的读电流可以大于用来读取第一MTJ元件270的读电流。第二MTJ元件272的电流值可被感测,并且该电流值可同与第二MTJ元件272相关联的第一参考值进行比较(第一比较)。基于第一比较的结果,感测出的电流值可同与第二MTJ元件272相关联的第二参考值进行比较(第二比较)以确定第二MTJ元件272的电阻状态(例如,逻辑状态)。

[0060] 第一和第二MTJ子阵列的读和写操作可由可在存储器阵列的外围的电路系统(未示出)执行。例如,外围电路系统可包括但不限于任何数目的存储器控制器、解码器、感测放大器、寄存器或可被用于存储器元件的读/写操作的其他设备。例如,第一和第二MTJ子阵列的一个或多个存储器设备(例如,存储器设备203、205、207和209)的感测操作可由感测放大器或者能够感测第一和第二MTJ子阵列的多个第一和第二MTJ元件的电流值的其他设备执行。一个或多个存储器设备的比较操作可由比较器或者能够将感测出的值同与第一和第二MTJ子阵列的多个第一和第二MTJ元件相关联的参考值进行比较的其他设备执行。

[0061] 第一和第二MTJ元件可被配置成具有有助于特定存储器使用的不同操作参数。通过选择第一和第二MTJ元件以形成第一和第二MTJ子阵列,单个存储器阵列可包括多个MTJ子阵列,每个子阵列具有有助于特定存储器使用(例如,快速存取阵列或长期存储阵列)的不同操作参数,由此导致单个存储器阵列内的双(或多)存储器使用。作为示例,单个存储器阵列可容适高速数据存储和长期高数据保持力存储的存储器使用,如关于图3A和3B描述

的。

[0062] 参照图3A,示出了解说具有存储器子阵列的系统的框图并将其一般地指定为300。系统300包括单个存储器阵列318。存储器阵列318包括多个第一MTJ元件(例如,图2的第一MTJ元件230、250、270和290),其被配置成形成第一MTJ子阵列(例如,高速(HS)子阵列)312。存储器阵列318还包括多个第二MTJ元件(例如,图2的第二MTJ元件232、252、272和292),其形成第二MTJ子阵列(例如,高数据保持力(HDR)子阵列)314。第一和第二MTJ子阵列可被集成在管芯(例如,半导体管芯)内。

[0063] 第一MTJ子阵列可被配置成具有用于第一存储器使用(例如,作为快速/频繁存取阵列或作为数据高速缓存)的第一操作参数集,并且第二MTJ子阵列可被配置成具有用于不同于第一存储器使用的第二存储器使用(例如,作为长期存取阵列)的第二操作参数集。第一操作参数集可以不同于第二操作参数集。第一操作参数集可以基于多个第一MTJ元件中的每一个第一MTJ元件的物理特性。第二操作参数集可以基于多个第二MTJ元件中的每一个第二MTJ元件的物理特性。例如,第一MTJ元件的物理特性可包括第一大小,并且第二MTJ元件的物理特性可包括大于第一大小的两倍的第二大小。

[0064] 第一MTJ元件和第二MTJ元件的其他物理特性可用作第一和第二MTJ子阵列的不同操作参数的基础。例如,第一MTJ元件可具有第一材料类型的材料,并且第二MTJ元件可具有不同于第一材料类型的第二材料类型的材料。作为另一示例,第一和第二MTJ子阵列的第一和第二MTJ元件可被配置成具有不同的物理排列(例如,可以为平面或多维的排列)。

[0065] HS子阵列312和HDR子阵列314可各自具有有助于特定存储器使用的操作参数。例如,与多个第二MTJ元件相关联的操作参数(例如,高数据保持力)可与HDR子阵列314相关联。与多个第一MTJ元件相关联的操作参数(例如,用于较短读/写历时的较大读取余裕)可与HS子阵列312相关联。作为示例,HDR子阵列314可具有比HS子阵列312的数据保持时间长的数据保持时间。作为另一示例,HS子阵列312可具有比HDR子阵列314的读/写时间历时短的读/写时间历时(例如,快速读/写时间历时)。HS和HDR子阵列312、314可被集成在设备内,诸如作为解说性示例,移动电话、平板设备、机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、通信设备、个人数字助理(PDA)、固定位置数据单元、或计算机。

[0066] 系统300进一步包括存储器控制器304和中央处理单元(CPU)302。存储器控制器304可被配置成寻址第一MTJ子阵列(例如,HS子阵列312)的多个第一MTJ元件中的每一者以及第二MTJ子阵列(例如,HDR子阵列314)的多个第二MTJ元件中的每一者。存储器控制器304可被配置成基于与存储器控制器304所接收到的数据相关联的优先级指示符向特定MTJ子阵列(例如,HS子阵列312或HDR子阵列314)存储数据。

[0067] HS子阵列312和HDR子阵列314可以是单个存储器阵列318(例如,图2的存储器阵列200)的一部分。HS子阵列312和HDR子阵列314各自与存储器控制器304耦合并处于通信。存储器控制器305可与CPU 302耦合并处于通信。存储器控制器304可接收来自CPU 302的数据读/写请求以及与这些请求相关联的指令。存储器控制器304还可从CPU 302接收指示与将对单个存储器阵列318的HS子阵列312或HDR子阵列314读/写的数据相关联的优先级等级的优先级指示符316。

[0068] 存储器控制器304可包括映射注册表306,其被用作对来自CPU 302的数据读/写请求的处理的一部分。映射注册表306可包括被存储器控制器304用来基于数据的优先级水平

对特定MTJ子阵列读/写数据并将存储在特定MTJ子阵列处的数据映射到来自CPU 302的数据请求的数据参数(例如,数据标识符、CPU逻辑寻址、存储器物理寻址、数据优先级水平、子阵列分配)。

[0069] 对特定MTJ子阵列的数据存储可由存储器控制器304基于来自CPU 302的其他指示符来确定。例如,对特定MTJ子阵列的数据分配可以基于可指示数据的存取频度(例如,被经常存取的数据)的数据存取指示符。在另一示例中,对特定MTJ子阵列的数据分配可以基于可指示数据的特定使用(例如,用于处理器高速缓存操作的数据或者用于引导代码操作的数据)的数据使用指示符。

[0070] 存储器控制器304可包括用于激活HS和HDR子阵列312、314作为由存储器控制器304处理的读/写操作的一部分的激活电路系统308。激活电路系统308可提供用于激活与形成HS和HDR子阵列312、314的多个第一和第二MTJ元件相关联的存取晶体管(未示出)的激活的信号。在特定示例中,激活电路系统308可以是在HS和HDR子阵列312、314的外围的电路系统的一部分。例如,该外围电路系统可包括但不限于其他存储器控制器、解码器、感测放大器、寄存器或可被用于存储器阵列的存储器元件的读/写操作的其他设备。

[0071] 存储器控制器304可包括用于执行感测出的值与特定参考值的比较作为由存储器控制器304处理的读/写操作的一部分的比较电路系统310。例如,作为HS子阵列312的特定第一MTJ元件的读操作的一部分,比较电路系统310可以将该特定第一MTJ元件的感测出的值同与第一MTJ元件相关联的特定参考值进行比较以便确定特定第一MTJ元件的电阻状态(例如,逻辑状态)。

[0072] 比较电路系统310还可执行双比较方法来确定HDR子阵列314的特定第二MTJ元件的电阻状态(例如,逻辑状态)。例如,作为HDR子阵列314的特定第二MTJ元件的读操作的一部分,比较电路系统310可以执行将该特定第二MTJ元件的感测出的值同与第二MTJ元件相关联的特定参考值的第一比较以便确定该特定第二MTJ元件的电阻状态(例如,逻辑状态)。基于第一比较的结果,比较电路系统310可执行将感测出的值同与第二MTJ元件相关联的第二参考值的第二比较以确定第二MTJ元件的电阻状态(例如,逻辑状态)。在特定方面,比较电路系统310可以是在HS和HDR子阵列312、314的外围的电路系统的一部分。例如,该外围电路系统可包括但不限于其他存储器控制器、解码器、感测放大器、寄存器或可被用于存储器阵列的存储器元件的读/写操作的其他设备。

[0073] 在操作期间,存储器控制器304可从CPU 302接收数据读和写请求以及指示关于与请求相关联的数据的优先级水平的相关联优先级指示符。存储器控制器304可基于数据的优先级水平向HS或HDR子阵列312、314读和写数据。例如,CPU 302可提供优先级指示符316作为写请求的一部分,该写请求指示特定数据将被存储到被配置成用于快速数据存取或用于临时数据存储的存储器阵列(例如,存储器阵列318的HS子阵列312)。存储器控制器304可利用映射注册表306作为对接收自CPU 302的写请求和优先级指示符的处理的一部分。基于优先级指示符316,存储器控制器304可确定特定数据将被存储到HS子阵列312而不被存储到HDR子阵列314。存储器控制器304可利用激活电路系统308来激活HS子阵列312并且可执行特定数据到HS子阵列312的写操作。

[0074] 作为另一示例,存储器控制器304可从CPU 302接收取回特定数据的读请求。存储器控制器304可利用映射注册表306作为对接收自CPU 302的读请求的处理的一部分。在确

定HS子阵列312将被读取之际,存储器控制器304可利用激活电路系统308来激活HS子阵列312并且可利用比较电路系统310来执行与特定数据将被存储的HS子阵列312的第一MTJ元件相关联的感测出的值的比较。在某些方面,映射注册表306、激活电路系统308和比较电路系统310可以与存储器控制器304是分开的。基于比较的结果,比较电路系统310可确定特定数据被存储的HS子阵列312的第一MTJ元件的电阻状态(例如,逻辑状态),并且可完成读操作以履行读请求。

[0075] 在将特定数据从HDR子阵列314读取的情形中,存储器控制器304可利用比较电路系统310来执行双比较方法以确定特定数据被存储的HDR子阵列314的第二MTJ元件的电阻状态(例如,逻辑状态)。在某些方面,存储器控制器304可利用分开的激活电路系统308和比较电路系统310来用于从HDR子阵列314读取,并且可利用分开的激活电路系统308和比较电路系统310来用于从HS子阵列312读取。在某些方面,激活电路系统308和比较电路系统310可以与存储器控制器304是分开的。

[0076] 例如,比较电路系统310可执行将与HDR子阵列314的第二MTJ元件相关联的感测出的值同与HDR子阵列314的第二MTJ元件相关联的参考值的第一比较。基于第一比较的结果,比较电路系统310可执行将感测出的值同与HDR子阵列314的第二MTJ元件相关联的参考值的第二比较。基于第二比较,比较电路系统310可确定HDR子阵列314的第二MTJ元件的电阻状态(例如,逻辑状态),并且可完成读操作以履行读请求。

[0077] 分别由多个第一和第二MTJ元件形成的HS子阵列312和HDR子阵列314可容适不同存储器使用。在非限定性示例中,HDR子阵列314可被用作用于HS子阵列312的备份存储阵列,如参照图3B进一步描述的。

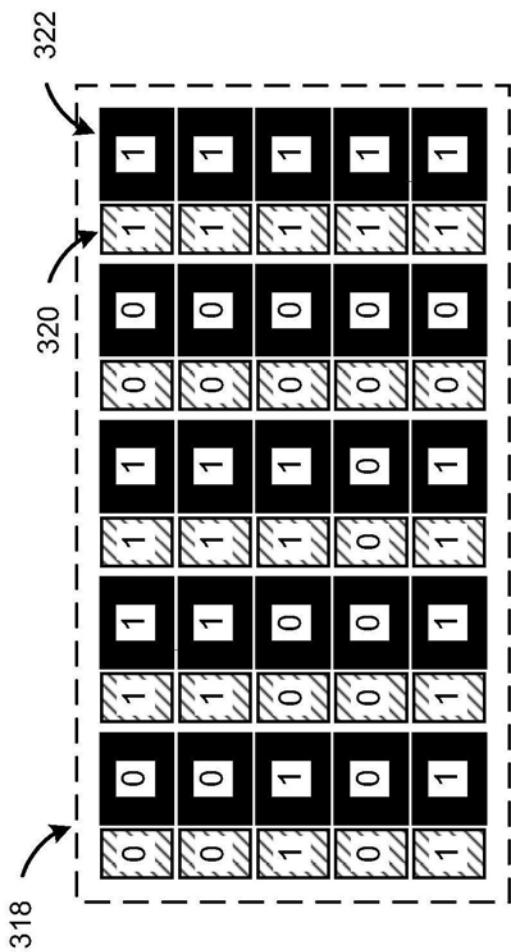

[0078] 图3B解说了图3A的存储器阵列318的示例。代表性第一MTJ元件320可具有第一大小并可以是具有大致第一大小的多个第一MTJ元件的一部分(例如,条纹框)。代表性第二MTJ元件322可具有大于第一大小的两倍的第二大小并可以是多个第二MTJ元件的一部分(例如,实心黑框)。多个第一MTJ元件和多个第二MTJ元件形成相应的第一和第二MTJ子阵列,其可各自被配置成基于相应的第一和第二操作集操作以用于特定存储器使用。在非限定性示例中,第二MTJ子阵列(例如,图3A的高数据保持力子阵列314)可被配置成存储作为存储在第一MTJ子阵列(例如,图3A的高速子阵列312)中的对应数据的复制值的数据值。因此,第二MTJ子阵列可被配置成作为第一MTJ子阵列的备份存储操作。

[0079] 例如,第一MTJ元件320可存储对应于逻辑值“1”的数据值。第二MTJ元件322可存储对应于逻辑值“1”的数据值,其是存储在特定第一MTJ元件320处的数据值的复制数据值。以类似方式,多个第一MTJ元件中的每一个第一MTJ元件中的逻辑数据值被复制在多个第二MTJ元件中的对应第二MTJ元件中的每一者中。

[0080] 存储器阵列318的第一和第二MTJ子阵列可利用图1的设备100或者图2的存储器阵列200的设备所利用的读和写操作。与存储器阵列318的第二MTJ子阵列相关联的读操作可利用双比较方法来确定形成第二MTJ子阵列的第二MTJ元件的电阻状态(例如,逻辑状态),如参照图4进一步描述的。

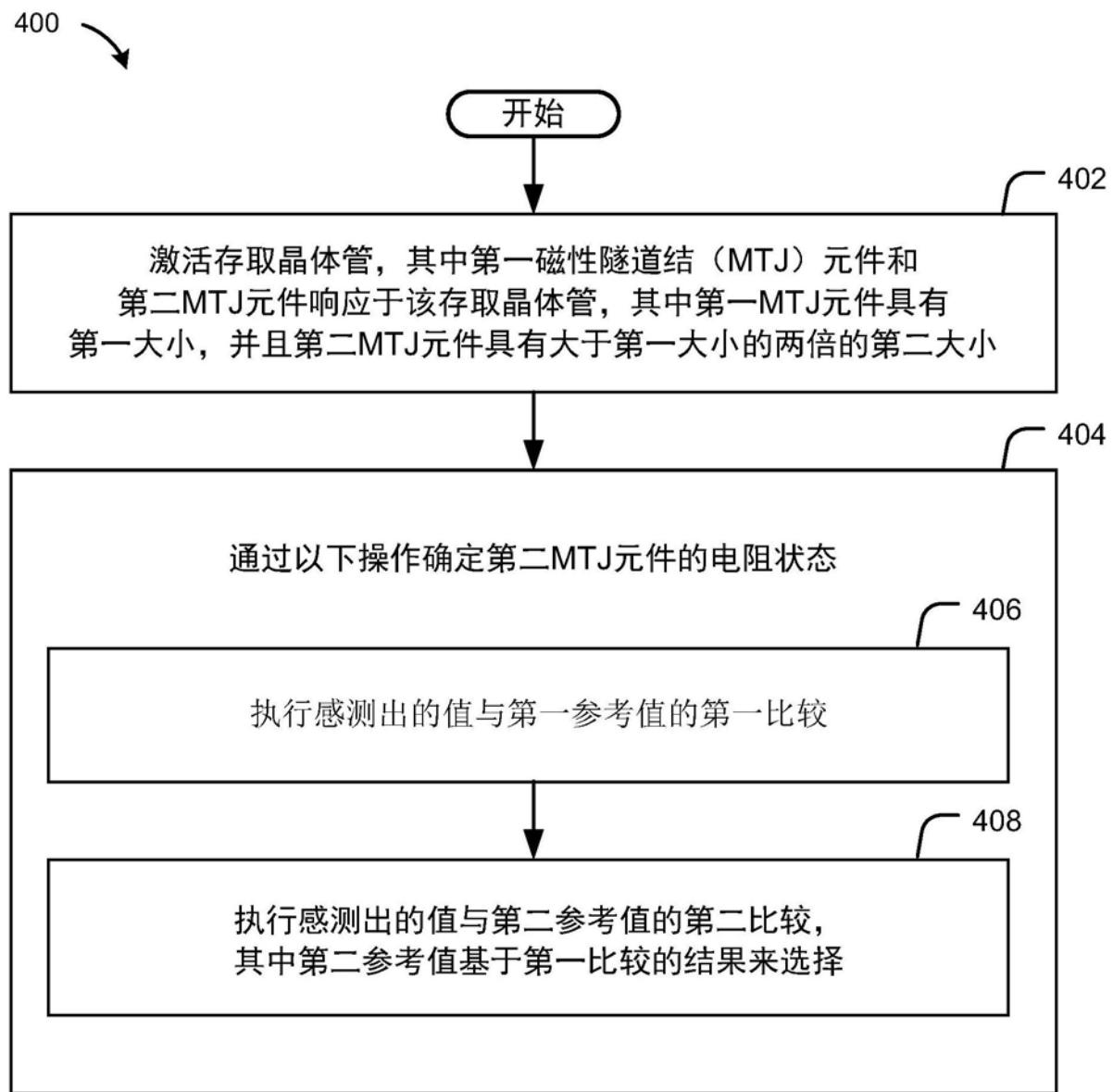

[0081] 参照图4,示出了解说操作设备的方法的特定方面的流程图并将其一般地指定为400。方法400可在包括存取晶体管、第一磁性隧道结(MTJ)元件和第二MTJ元件的设备处执行。方法400可以例如在图1的设备100、形成图2的存储器阵列200的一部分的存储器设备

(例如,存储器设备203、205、207或209)、图3A的系统300或其组合处执行。

[0082] 方法400可包括在402,激活存取晶体管,其中第一磁性隧道结(MTJ)元件和第二MTJ元件响应于该存取晶体管。在一个示例中,第一MTJ元件具有第一大小,并且第二MTJ元件具有大于第一大小的两倍的第二大小。例如,存取晶体管可对应于存取晶体管106、第一MTJ元件可对应于第一MTJ元件102,并且第二MTJ元件可对应于第二MTJ元件104。第一MTJ元件、第二MTJ元件和存取晶体管可形成多位STT-MRAM存储器单元。

[0083] 激活存取晶体管可包括经由字线(例如,图1的字线108或图2的字线210和212)向存取晶体管106的栅极提供可指示对应于第二MTJ元件的读请求的信号(例如,电压)。基于来自字线的信号,存取晶体管可选择性地将第一MTJ元件耦合至第二MTJ元件。作为读请求的一部分,可在耦合至第一MTJ元件的位线处或者在耦合至第二MTJ元件的源线处施加与第二MTJ元件相关联的特定电流,并且可感测与第二MTJ元件相关联的电流值。

[0084] 方法400还包括在404,确定第二MTJ元件的电阻状态。例如,两位STT-MRAM存储器单元的第一和第二MTJ元件的电阻状态(例如,逻辑状态)可以基于第一MTJ元件的平行或反平行状态与第二MTJ元件的平行或反平行状态的一个或多个组合。例如,MTJ元件的平行状态可对应于MTJ元件具有与“固定层”磁取向平行的“自由层”磁取向。MTJ元件的反平行状态可对应于MTJ元件具有与“固定层”磁取向不平行的“自由层”磁取向。第一和第二MTJ元件的电阻状态(例如,逻辑状态)可包括对应于四个逻辑状态(例如,逻辑状态“00”、“01”、“10”和“11”)的平行状态和反平行状态组合。

[0085] 作为在404确定第二MTJ元件的电阻状态的一部分,方法400还包括在406,执行感测出的值与第一参考值的第一比较。例如,第一比较可利用与第二MTJ元件相关联的感测出的值并且可将感测出的值与第一参考值进行比较。第一参考值可以是与第二MTJ元件相关联的第一参考电平。

[0086] 作为在404确定第二MTJ元件的电阻状态的一部分,方法400还包括在408,执行感测出的值与第二参考值的第二比较,第二参考值基于第一比较的结果来选择。例如,如果第一比较的结果(例如,为“1”的比较结果)指示感测出的值大于第一参考电平(例如,与第二MTJ元件相关联的第一参考电平),则第二参考电平(例如,与第二MTJ元件相关联的第二参考电平)可被用作在第二比较期间感测出的值与其作比较的参考电平。

[0087] 第二比较的结果指示感测出的值大于与第二MTJ元件相关联的第二参考电平可指示第二MTJ元件与特定逻辑状态相关联(例如,逻辑状态“11”对应于第一MTJ元件的反平行状态和第二MTJ元件的反平行状态)。第二MTJ元件的其他可能的电阻状态(例如,逻辑状态)可以基于来自第一和第二比较的不同结果来确定,如参照图5A、5B、5C和5D进一步描述的。

[0088] 尽管以上已经结合图1描述了图4的方法400,但方法400还可由图2的存储器阵列来执行。例如,方法400可由包括第一和第二MTJ元件的另一设备执行、发起或控制。可包括第一和第二MTJ元件的设备的示例包括现场可编程门阵列(FPGA)器件、专用集成电路(ASIC)、处理单元(诸如中央处理单元(CPU))、数字信号处理器(DSP)、控制器、另一硬件设备、固件设备、或其任何组合。作为示例,图4的方法400可由执行指令的存储器控制器或处理器来执行,如关于图3A或6所描述的。这些指令可提供用于读取第二MTJ元件的选项。这些指令还可指示将在确定第二MTJ元件的参考状态中使用的参考电平,如参照图5A、5B、5C和5D进一步描述的。

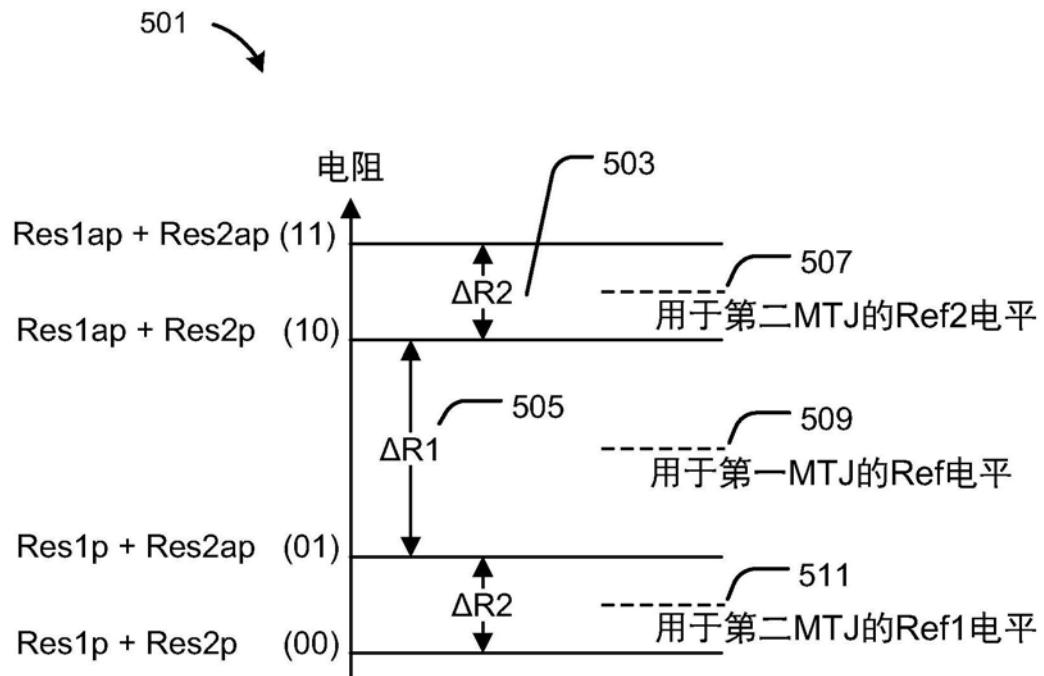

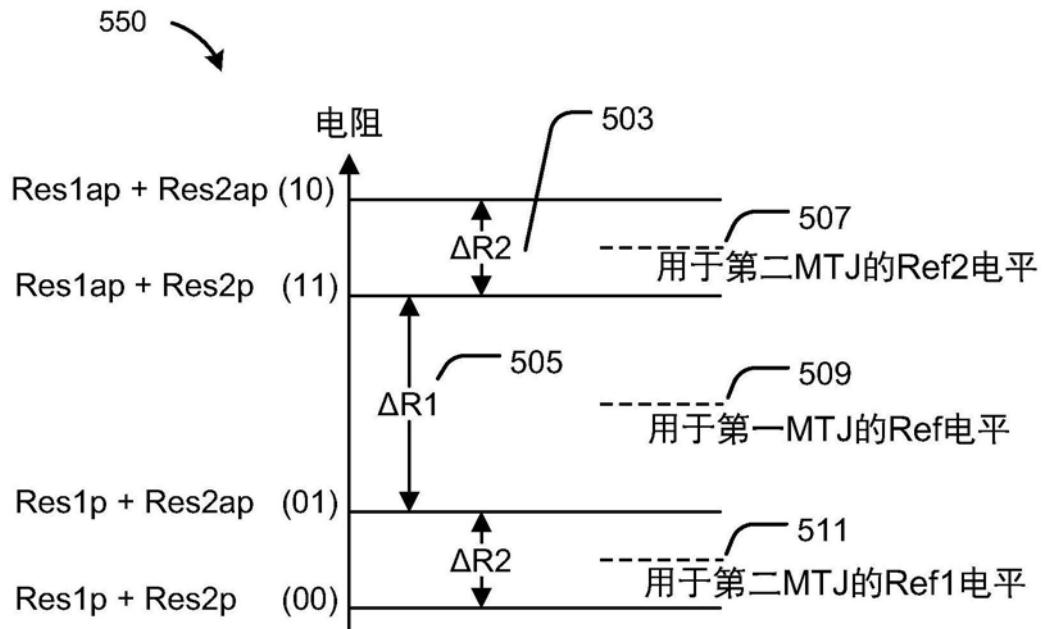

[0089] 参照图5A,逻辑状态到设备的平行和反平行状态的特定映射的细节被示出并通过图表501一般地指定。图表501示出第一和第二MTJ元件(例如,图1的第一和第二MTJ元件102、104或者图2的第一和第二MTJ元件230、232、250、252、270、272、290、292)的电阻状态。例如,包括第一MTJ元件和第二MTJ元件的两位STT-MRAM存储器单元可被编程为指示四个逻辑状态(例如,逻辑状态“00”、“01”、“10”和“11”)之一的串联电阻。

[0090] 图表501示出了逻辑状态到第一和第二MTJ元件的平行和反平行状态(例如,Res1p、Res2p、Res1ap和Res2ap)的特定映射。在图5A的示例中,对应于逻辑状态“00”的电阻状态可指示第一MTJ元件的平行状态(例如,Res1p)和第二MTJ元件的平行状态(例如,Res2p)。对应于逻辑状态“01”的电阻状态可指示第一MTJ元件的平行状态(例如,Res1p)和第二MTJ元件的反平行状态(例如,Res2ap)。对应于逻辑状态“10”的电阻状态可指示第一MTJ元件的反平行状态(例如,Res1ap)和第二MTJ元件的平行状态(例如,Res2p)。对应于逻辑状态“11”的电阻状态可指示第一MTJ元件的反平行状态(例如,Res1ap)和第二MTJ元件的反平行状态(例如,Res2ap)。

[0091] 确定第一和第二MTJ元件的电阻状态可包括将感测出的值同与第一和第二MTJ元件相关联的一个或多个参考电平值的比较。例如,第一MTJ元件可以与参考(Ref)电平509相关联,并且第二MTJ元件可以与第一参考(Ref1)电平511和第二参考(Ref2)电平507相关联。与第一MTJ元件(例如,图1的第一MTJ元件102)相关联的单个参考电平509可以大于与第二MTJ元件(例如,图1的第二MTJ元件104)相关联的第一参考电平511并且小于与第二MTJ元件相关联的第二参考电平507。

[0092] 第一和第二MTJ元件可具有不同的操作参数(例如,作为第二MTJ元件具有大于第一MTJ元件的大小的两倍的大小的结果)。例如,第一读取余裕( $\Delta R1$ )505可以与第一MTJ元件(例如,图1的第一MTJ元件102)相关联,并且第二读取余裕( $\Delta R2$ )503可以与第二MTJ元件(例如,图1的第二MTJ元件104)相关联。第二MTJ元件的 $\Delta R2$ 可以小于第一MTJ元件的 $\Delta R1$ 。

[0093] 第一和第二MTJ元件的读取余裕之差可使得一个MTJ元件被调整得比另一个MTJ元件更适应于特定存储器使用。例如,第一MTJ元件的较大 $\Delta R1$ 可为快速或频繁的读操作(例如,高速缓存存储器的快速和/或频繁的读操作)提供较大的差错余裕。第二MTJ元件的较小 $\Delta R2$ 可以更有助于较慢或不频繁的读操作(例如,长期存储存储器的较慢和较少读操作)。

[0094] 第一和第二MTJ元件的电阻状态可通过将第一和第二MTJ元件的感测出的值同与第一和第二MTJ元件相关联的参考值进行比较来确定。例如,在第一MTJ元件(例如,图1的第一MTJ元件102)的读操作期间,感测出的值可同与第一MTJ元件相关联的参考电平509进行比较。如果比较指示感测出的值大于参考电平509,则第一MTJ元件具有反平行状态(例如,Res1ap),其指示第一MTJ元件存储逻辑“1”位。如果比较指示感测出的值小于参考电平509,则第一MTJ元件具有平行状态(例如,Res1p),其指示第一MTJ元件存储逻辑“0”位。

[0095] 确定第二MTJ元件(例如,图1的第二MTJ元件104)的电阻状态(例如,逻辑状态)可利用双比较方法,其可使用与第一和第二MTJ元件相关联的参考电平(例如,参考电平值507、509和511)中的两者或更多者。

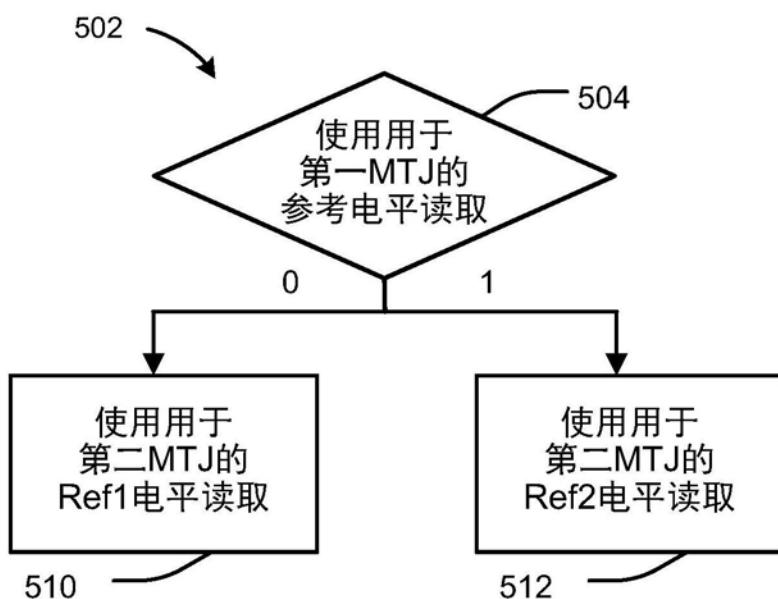

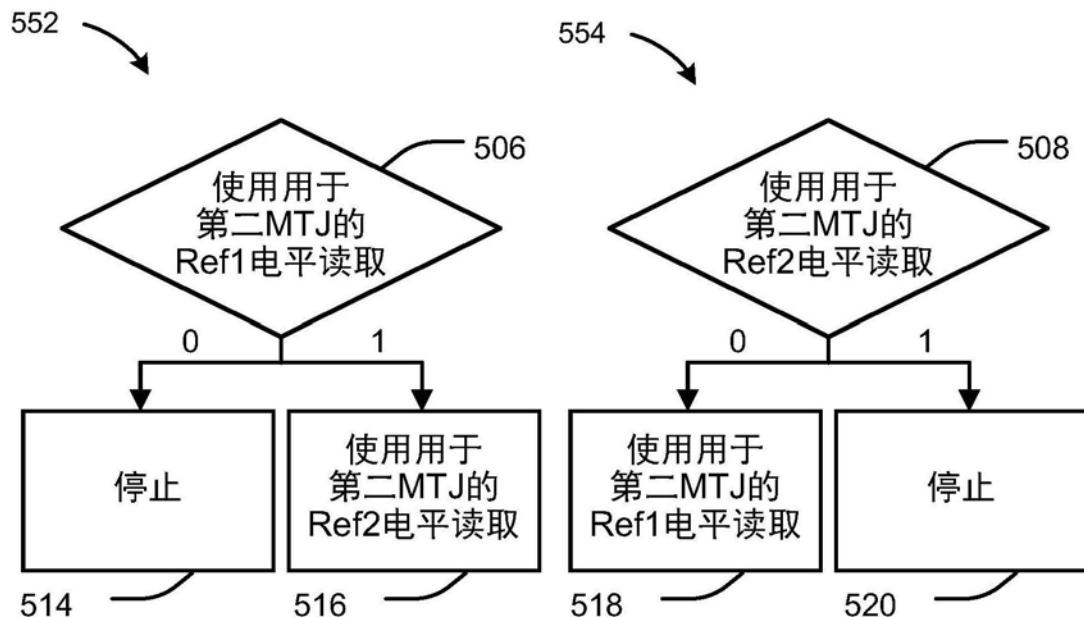

[0096] 参照图5B,示出了读取设备的方法并将其一般地指定为502。例如,方法502可被执行以确定与参照图5A描述的设备相关联的逻辑状态。从第二MTJ元件(例如,图1的第二MTJ元件104或图2的232、252、272、292)读取数据可利用双比较方法来确定第二MTJ元件的逻辑

状态。双比较方法可包括利用与第二MTJ元件相关联的感测出的值来执行感测出的值与第一参考值的第一比较,以及基于第一比较的结果,选择第二参考值来执行感测出的值与第二参考值的第二比较。

[0097] 双比较方法可包括用于从第二MTJ元件读取的第一选项。例如,在第一选项中,与第一MTJ元件相关联的参考电平(例如,图5A的参考电平509)可被用作作为在504执行的第一比较的一部分感测出的值与其作比较的参考电平。

[0098] 如果第一比较的结果(例如,为“1”的结果)指示感测出的值大于参考电平(例如,图5A的参考电平509),则与第二MTJ元件相关联的第二参考电平(例如,图5A的Ref2电平507)可被用作在512执行的第二比较期间感测出的值与其作比较的参考电平。如果第二比较指示感测出的值大于与第二MTJ元件相关联的第二参考电平(例如,图5A的Ref2电平507),则可作出第二MTJ元件存储逻辑“1”位的确定。如果第二比较指示感测出的值小于与第二MTJ元件相关联的第二参考电平(例如,图5A的Ref2电平507),则可作出第二MTJ元件存储逻辑“0”位的确定。

[0099] 如果第一比较的结果(例如,为“0”的结果)指示感测出的值小于参考电平(例如,图5A的参考电平509),则与第二MTJ元件相关联的第一参考电平(例如,图5A的Ref1电平511)可被用作在510执行的第二比较期间感测出的值与其作比较的参考电平。指示感测出的值大于与第二MTJ元件相关联的第一参考电平(例如,图5A的Ref1电平511)的第二比较的结果可指示第二MTJ元件存储逻辑“1”位。指示感测出的值小于与第二MTJ元件相关联的第一参考电平(例如,图5A的Ref1电平511)的第二比较的结果可指示第二MTJ元件存储逻辑“0”位。

[0100] 将领会,图5A解说了逻辑状态(例如,“00”、“01”、“10”和“11”)到第一和第二MTJ元件的平行和反平行状态(例如,Res1p、Res2p、Res1ap和Res2ap)的特定映射。图5A中示出的特定映射表示了对于第一和第二MTJ元件两者,平行状态对应于逻辑“0”状态并且反平行状态对应于逻辑“1”状态的情形。可实现逻辑状态到第一和第二MTJ元件的平行和反平行状态的其他映射。例如,在另一特定映射中,由第二MTJ元件的电阻状态指示的逻辑状态可取决于第一MTJ元件的电阻状态,如参照图5C和图5D进一步描述的。

[0101] 参照图5C,逻辑状态到设备的平行和反平行状态的另一映射的细节被示出并被图表550一般地指定。图表550示出第一和第二MTJ元件(例如,图1的第一和第二MTJ元件102、104或者图2的第一和第二MTJ元件230、232、250、252、270、272、290、292)的电阻状态。例如,包括第一MTJ元件和第二MTJ元件的两位STT-MRAM存储器单元可被编程为串联电阻,其指示四个逻辑状态(例如,逻辑状态“00”、“01”、“10”和“11”)之一。在图5C中,逻辑状态“10”对应于比逻辑状态“11”大的串联电阻(作为替代,逻辑状态“10”对应于比逻辑状态“11”低的串联电阻,如在图5A的示例中)。

[0102] 例如,对应于逻辑状态“00”的电阻状态可指示第一MTJ元件的平行状态(例如,Res1p)和第二MTJ元件的平行状态(例如,Res2p)。对应于逻辑状态“01”的电阻状态可指示第一MTJ元件的平行状态(例如,Res1p)和第二MTJ元件的反平行状态(例如,Res2ap)。对应于逻辑状态“11”的电阻状态可指示第一MTJ元件的反平行状态(例如,Res1ap)和第二MTJ元件的平行状态(例如,Res2p)。对应于逻辑状态“10”的电阻状态可指示第一MTJ元件的反平行状态(例如,Res1ap)和第二MTJ元件的反平行状态(例如,Res2ap)。因此,在图5C中,逻辑

状态“10”和“11”对应于与图5A的示例相比不同的串联电阻以及不同的平行和反平行状态。

[0103] 参照图5D,读取设备的第二MTJ元件的方法被示出并且被分别一般地指定为552和554。例如,方法552和554可被执行以确定与参照图5C描述的设备相关联的逻辑状态。双比较方法可包括用于从第二MTJ元件读取的第二选项。例如,在第二选项期间,在506执行第一比较。作为第一比较506的一部分,感测出的值可同与第二MTJ元件相关联的第一参考电平(例如,图5C的参考电平511)进行比较。

[0104] 如果第一比较的结果(例如,为“1”的结果)指示感测出的值大于参考电平(例如,图5C的参考电平511),则与第二MTJ元件相关联的第二参考电平(例如,图5C的Ref2电平507)可被用作在516执行的第二比较期间感测出的值与其作比较的参考电平。指示感测出的值大于与第二MTJ元件相关联的第二参考电平(例如,图5A的Ref1电平507)的第二比较的结果可指示第二MTJ元件存储逻辑“0”位。指示感测出的值小于与第二MTJ元件相关联的第二参考电平(例如,图5A的Ref1电平507)的第二比较的结果可指示第二MTJ元件存储逻辑“1”位。

[0105] 如果第一比较的结果(例如,为“0”的结果)指示感测出的值小于参考电平(例如,图5C的参考电平511),则不执行第二比较,方法在514结束,并且该结果可指示第二MTJ元件存储逻辑“0”位。

[0106] 双比较方法可包括用于从第二MTJ元件读取的第三选项。例如,使用第三选项,在508执行第一比较。作为第一比较508的一部分,感测出的值可同与第二MTJ元件相关联的第二参考电平(例如,图5C的参考电平507)进行比较。

[0107] 如果第一比较的结果(例如,为“0”的结果)指示感测出的值小于参考电平(例如,图5C的参考电平507),则与第二MTJ元件相关联的第一参考电平(例如,图5C的Ref1电平511)可被用作在518执行的第二比较期间感测出的值与其作比较的参考电平。指示感测出的值大于与第二MTJ元件相关联的第一参考电平(例如,图5C的Ref1电平511)的第二比较的结果可指示第二MTJ元件存储逻辑“1”位。指示感测出的值小于与第二MTJ元件相关联的第一参考电平(例如,图5C的Ref1电平511)的第二比较的结果可指示第二MTJ元件存储逻辑“0”位。

[0108] 如果第一比较的结果(例如,为“1”的结果)指示感测出的值大于参考电平(例如,图5C的参考电平507),则不执行第二比较,方法在520结束,并且该结果可指示第二MTJ元件存储逻辑“0”位。

[0109] 图5A和5B的示例解说了用于使用两个读操作以及逻辑状态到平行和反平行的特定映射来读取第二MTJ元件的第一选项。图5C和5D的示例解说了用于使用一个或两个读操作以及逻辑状态到平行和反平行的另一映射来读取第二MTJ元件的第二和第三选项。

[0110] 将领会,与图5C和5D的示例相比,图5A和5B可表示某些实现中涉及较少处理步骤的逻辑映射的情形,但可使用对第二MTJ元件的两个读操作。为了解说,在图5A和5B的情形中,对于第一和第二MTJ元件两者,平行状态对应于逻辑“0”状态并且反平行状态对应于逻辑“1”状态。在图5C和5D的情形中,对于第二MTJ元件,平行状态可对应于逻辑“0”状态或逻辑“1”状态(取决于第一MTJ元件分别具有平行状态还是反平行状态)。进一步,在图5C和5D中,第二MTJ元件的反平行可指示逻辑“1”状态或逻辑“0”状态(分别取决于第一MTJ元件具有平行状态还是反平行状态)。在图5C和5D的情形中,可在向第二MTJ元件的写操作期间利

用更多处理操作,以与图5A和5B的情形中的逻辑映射相比计及第二MTJ元件的替代映射。例如,使用图5C的映射向第二MTJ元件写入逻辑“0”状态或逻辑“1”状态可包括执行感测操作以确定第一MTJ元件的状态(并且基于第一MTJ元件的状态确定第二MTJ元件应当被编程为平行状态还是反平行状态)。参照图5C描述的设备可包括被配置成响应于发起对第二MTJ元件的写操作而感测第一MTJ元件的状态。参照图5C描述的设备可进一步包括被配置成向写电路系统提供指示第一MTJ元件的状态的信号以使得写电路系统能够确定要将第二MTJ元件编程为平行状态还是反平行状态的电路系统。

[0111] 在一些情形中,根据图5C和图5D的设备可使用比与图5A和5B相关联的逻辑映射(例如,平均为1.5次读操作)少的读操作(平均上)。由此,图5A和5B解说了其中写操作速度(针对第二MTJ元件)将被增大(例如,由于被编程到第二MTJ元件的平行或反平行状态可以不取决于与第一MTJ元件相关联的状态)的可以有利的情形。图5C和5D的示例解说了其中读操作速度(针对第二MTJ元件)将被增大(例如,由于第二MTJ元件的状态在一些情形中可使用单次读操作来确定,如在图5D中解说的)的可以有利的情形。应领会,设备可使用图5A和5B的示例,作为图5C和5D的示例的替换或补充。例如,在一些实现中,设备可动态地在根据图5A和5B的示例的操作(例如,以增大写操作速度)与根据图5C和5D的操作(例如,以增大读操作速度)之间交替。

[0112] 参照图5A、5B、5C和5D描述的操作可通过现场可编程门阵列(FPGA)器件、专用集成电路(ASIC)、处理单元(诸如中央处理器单元(CPU))、数字信号处理器(DSP)、控制器、另一硬件设备、固件设备、或其任何组合来实现。作为示例,参照图5A、5B、5C和5D描述的操作可由执行指令的处理器来执行,如参照图3A和6所描述的。

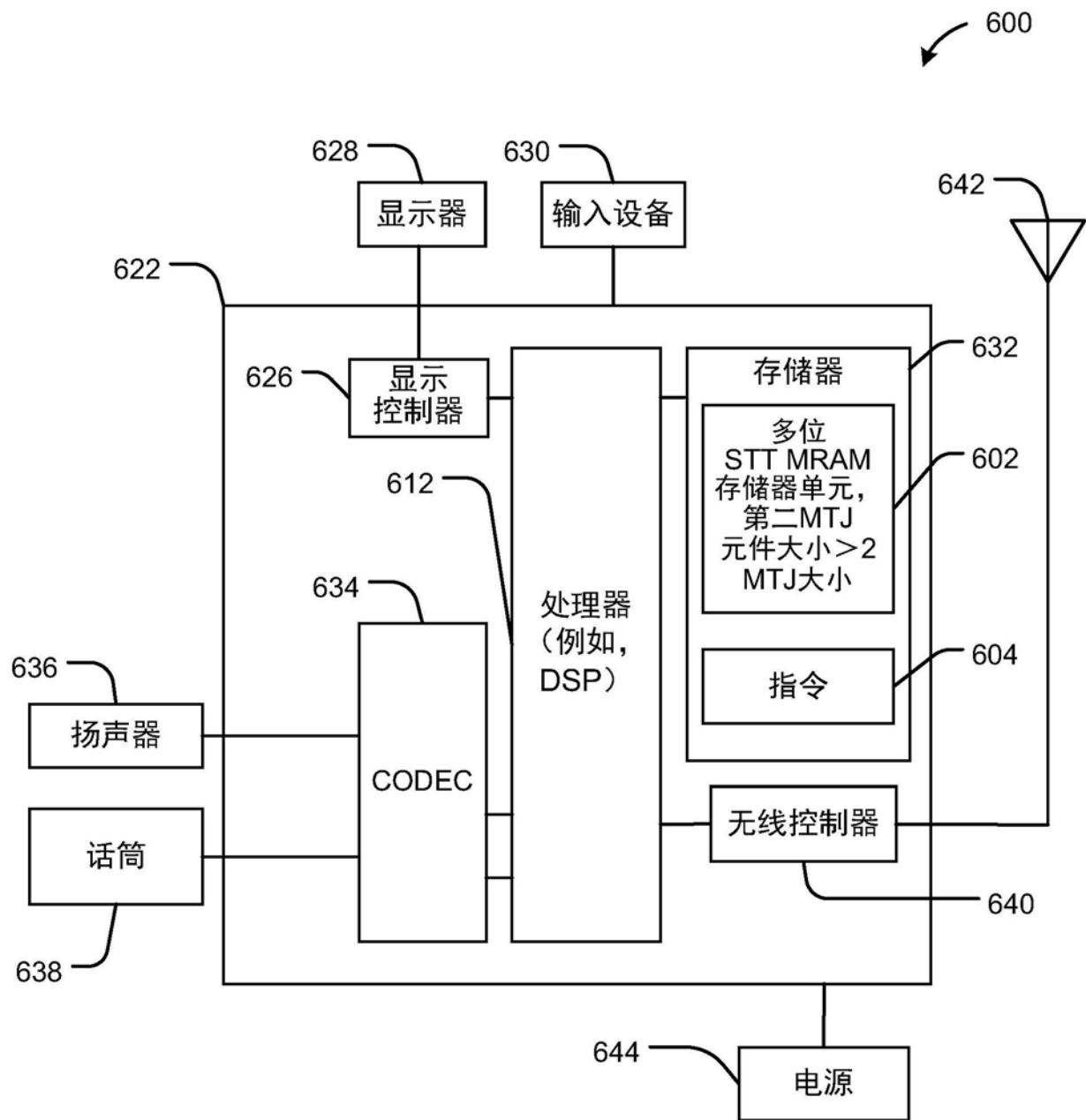

[0113] 参照图6,描绘了无线通信设备的特定方面的框图并将其一般地指定为600。设备600包括耦合至存储器632的处理器612(例如,数字信号处理器(DSP))。处理器612可包括能够处理指令的任何处理器或电子设备。存储器632包括一个或多个多位STT-MRAM存储器单元602,具有第二MTJ元件和第一MTJ元件作为存储器阵列(例如,图3的存储器阵列318)的存储器子阵列的一部分。在解说性示例中,多位STT-MRAM存储器单元602可对应于图1的设备100。在另一解说性示例中,存储器632可包括多位STT-MRAM存储器单元(诸如图2的多位STT-MRAM存储器单元203、205、207和209)的阵列。在另一解说性示例中,存储器632可包括图3A和3B的存储器阵列318。存储器632可根据图3或图4B的方法操作,并且可根据先前描述的存储器使用来操作。

[0114] 存储器632可以是设备的非瞬态计算机可读介质,其包括存取晶体管(例如,图1的存取晶体管106)、第一MTJ元件(例如,图1的第一MTJ元件102)、以及第二MTJ元件(例如,图1的第二MTJ元件104)。存储器632存储可由处理器612执行以使得处理器612激活存取晶体管的计算机可执行指令604。存取晶体管耦合在第一MTJ元件与第二MTJ元件之间。处理器612可进一步确定第一MTJ元件和第二MTJ元件的电阻状态。

[0115] 计算机可执行指令604可进一步包括可由处理器612执行以使得处理器612通过以下操作来确定第二MTJ元件的电阻状态:执行感测出的值与第一参考值(例如,图5A或图5C的参考电平507、509、511中的任一者)的第一比较以及执行感测出的值与第二参考值(例如,图5A或图5C的参考电平507、509、511中的任一者)的第二比较,第二参考值基于第一比较的结果来选择。例如,第二参考值可以基于指示感测出的值大于还是小于作为第一比较

的一部分使用的参考值的第一比较来选择。存储器632可被集成在设备中,诸如作为解说性示例,移动电话、平板设备、机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、通信设备、个人数字助理(PDA)、固定位置数据单元、或计算机。

[0116] 图6还示出了耦合至数字信号处理器612和显示器628的显示控制器626。编码器/解码器(CODEC)634也可耦合至数字信号处理器612。扬声器636和话筒638可耦合到CODEC634。

[0117] 图6还指示无线控制器640可耦合至数字信号处理器612和天线642。在一特定方面,处理器612、显示控制器626、存储器632、CODEC 634、和无线控制器640被包括在系统级封装或片上系统设备622中。在一特定方面,输入设备630和电源644被耦合到片上系统设备622。此外,在一特定方面,如图6中所解说的,显示器628、输入设备630、扬声器636、话筒638、天线642、和电源644在片上系统设备622的外部。然而,显示器628、输入设备630、扬声器636、话筒638、天线642和电源644中的每一者可耦合到片上系统设备622的组件(诸如耦合到接口或控制器)。

[0118] 该系统可包括用于存储第一磁状态的第一装置,诸如图1的第一MTJ元件102、配置成存储第一电阻状态的一个或多个其他设备或电路、或其任何组合。用于存储第一磁状态的第一装置可具有第一大小。该系统还可包括用于存储第二磁状态的第二装置,诸如图1的第二MTJ元件104、配置成存储第二电阻状态的一个或多个其他设备或电路、或其任何组合。用于存储第二磁状态的第二装置可具有大于第一大小的两倍的第二大小。该系统还可包括用于将用于存储的第一装置与用于存储的第二装置耦合的装置,诸如,图1的存取晶体管106、被配置成将用于存储的第一装置与用于存储的第二装置耦合的一个或多个其他设备或电路,或其任何组合。用于耦合的装置可被耦合至字线。用于耦合的装置、用于存储第一磁状态的第一装置以及用于存储第二磁状态的第二装置可形成多位STT-MRAM存储器单元,诸如图1的设备100。

[0119] 该系统还可包括耦合至用于存储的第一装置的位线以及耦合至用于存储的第二装置的源线。用于耦合的装置可被配置成响应于字线信号而将用于存储的第一装置耦合至用于存储的第二装置。该系统还可包括存储器阵列,其包括用于存储的第一装置、用于存储的第二装置以及用于耦合的装置(例如,图2的包括存储器设备203、205、207或209的存储器阵列200)。该系统可利用在存储器阵列的外围的其他设备或电路系统,其被配置成激活用于耦合的装置、用于存储的第一装置、用于存储的第二装置,并且确定用于存储的第一和第二装置的电阻状态。

[0120] 一种装置可包括由存储器阵列的多个第一MTJ元件形成的第一MTJ子阵列(例如,图3A的高速子阵列312),诸如包括图3B的第一MTJ元件320的多个第一MTJ元件(例如,图3B的多个条纹框)。该装置还可包括由存储器阵列的多个第二MTJ元件形成的第二MTJ子阵列(例如,图3A的高数据保持力子阵列314),诸如包括图3B的第二MTJ元件322的多个第二MTJ元件(例如,图3B的多个实心黑框)。第一MTJ子阵列可被配置成基于用于第一存储器使用的第一参数集操作,并且第二MTJ子阵列可被配置成基于用于不同于第一存储器使用的第一存储器使用的第二参数集操作。

[0121] 该装置还可包括存储器控制器,诸如图3A的存储器控制器304。存储器控制器可被配置成寻址第一MTJ子阵列(例如,图3A的高速子阵列312)的多个第一MTJ元件(例如,图3B

的多个条纹框)中的每一者以及第二MTJ子阵列(例如,图3A的高数据保持力子阵列314)的多个第二MTJ元件(例如,图3B的多个实心黑框)中的每一者。该装置可利用在存储器控制器、第一MTJ子阵列和第二MTJ子阵列的外围的可被配置成激活第一和第二MTJ子阵列的其他设备或电路系统。

[0122] 技术人员将进一步领会,结合本文所公开的方面来描述的各种解说性逻辑框、配置、模块、电路、和算法步骤可实现为电子硬件、由处理器执行的计算机软件、或这两者的组合。各种解说性组件、框、配置、模块、电路、和步骤已经在上文以其功能性的形式作了一般化描述。此类功能性是被实现为硬件还是处理器可执行指令取决于具体应用和加诸于整体系统的设计约束。技术人员可针对每种特定应用以不同方式来实现所描述的功能性,但此类实现决策不应被解读为致使脱离本公开的范围。

[0123] 结合本文中公开的方面描述的方法或算法的步骤可直接在硬件中、在由处理器执行的软件模块中、或在这两者的组合中执行。软件模块可驻留在磁阻随机存取存储器(MRAM)、随机存取存储器(RAM)、闪存、只读存储器(ROM)、可编程只读存储器(PROM)、可擦式可编程只读存储器(EPROM)、电可擦式可编程只读存储器(EEPROM)、寄存器、硬盘、可移动盘、压缩盘只读存储器(CD-ROM)、或本领域中所知的任何其他形式的非瞬态存储介质中。示例性存储介质耦合到处理器以使该处理器能从/向该存储介质读写信息。在替换方案中,存储介质可以被整合到处理器。处理器和存储介质可驻留在专用集成电路(ASIC)中。ASIC可驻留在计算设备或用户终端中。在替换方案中,处理器和存储介质可作为分立组件驻留在计算设备或用户终端中。

[0124] 提供前面对所公开的各方面的描述是为了使得本领域技术人员能够制作或使用所公开的各方面。对这些方面的各种修改对于本领域技术人员而言将是显而易见的,并且本文中定义的原理可被应用于其他方面而不会脱离本公开的范围。因此,本公开并非旨在被限定于本文中示出的各方面,而是应被授予与如由所附权利要求定义的原理和新颖性特征一致的最广的可能范围。

图1

图2

图3A

图3B

图4

图5A

图5B

图5C

图5D

图6