(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5249757号

(P5249757)

(45) 発行日 平成25年7月31日(2013.7.31)

(24) 登録日 平成25年4月19日(2013.4.19)

(51) Int.Cl.

F 1

**H01L 21/336 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 29/792 (2006.01)**

**H01L 21/8247 (2006.01)**

**H01L 27/115 (2006.01)**

H01L 29/78 371

H01L 27/10 434

請求項の数 5 (全 32 頁)

(21) 出願番号 特願2008-524015 (P2008-524015)

(86) (22) 出願日 平成18年7月24日 (2006.7.24)

(65) 公表番号 特表2009-503859 (P2009-503859A)

(43) 公表日 平成21年1月29日 (2009.1.29)

(86) 國際出願番号 PCT/US2006/028578

(87) 國際公開番号 WO2007/014117

(87) 國際公開日 平成19年2月1日 (2007.2.1)

審査請求日 平成21年7月23日 (2009.7.23)

(31) 優先権主張番号 11/188,588

(32) 優先日 平成17年7月25日 (2005.7.25)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衛

(72) 発明者 チンダロア、ゴーリシャンカー エル.

アメリカ合衆国 78749 テキサス州

オースティン ソーテル レーン 91

01

最終頁に続く

(54) 【発明の名称】不揮発性メモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

電子デバイスであって、

第1の壁と、該第1の壁と対向する第2の壁とを有する、基板内のトレンチと、

第1の方向に実質的に沿って配向された第1のメモリセルのセットと、

前記第1の方向に実質的に沿って配向された第2のメモリセルのセットと、

前記第1のメモリセルのセットに電気的に接続された選択ゲート線である第1のゲート

線であって、前記第1のゲート線の少なくとも一部が前記トレンチの外側に存在する、第

1のゲート線と、

前記第2のメモリセルのセットに電気的に接続された制御ゲート線である第2のゲート

線であって、前記第1のゲート線に比べて第2のゲート線は、前記第1の方向に沿って存

在する、より多くのメモリセルのセットに電気的に接続されているとともに、前記第1及

び第2のメモリセルのセットを含むメモリアレイ内で前記第1のゲート線が第2のゲート

線に実質的に平行であり、前記第2のゲート線の少なくとも一部が前記トレンチ内部に存

在する、第2のゲート線と、

複数の不連続記憶素子であって、前記第1のメモリセルのセット内の各メモリセルに

おいて、前記複数の不連続記憶素子のうちの第1のセットが、前記トレンチ内部に存在する

前記第2のゲート線の少なくとも一部と前記トレンチの前記第1の壁との間に該第1の壁

に沿って存在しており、前記第2のメモリセルのセット内の各メモリセルにおいて、前記

複数の不連続記憶素子のうちの第2のセットが、前記トレンチ内部に存在する前記第2の

10

20

ゲート線の少なくとも一部と前記トレンチの前記第2の壁との間に該第2の壁に沿って存在している、複数の不連続記憶素子と、

を備える電子デバイス。

**【請求項2】**

前記第1および第2のメモリセルのセット内の各メモリセルは、選択ゲート電極および制御ゲート電極を含む不揮発性メモリセルからなり。

前記第1のゲート線は、前記第1のメモリセルのセットの前記選択ゲート電極に電気的に接続されており、

前記第2のゲート線は、前記第2のメモリセルのセットの前記制御ゲート電極に電気的に接続されている、請求項1に記載の電子デバイス。

10

**【請求項3】**

電子デバイスであって、

第1の壁と、該第1の壁と対向する第2の壁とを有する、基板内のトレンチと、

第1の方向に実質的に沿って配向された第1のメモリセルのセットと、

前記第1の方向に実質的に沿って配向された第2のメモリセルのセットと、ここで、前記第1および第2のメモリセルのセット内の各メモリセルは、制御ゲート電極を含み、

前記第1のメモリセルのセットに電気的に接続された第1のビット線であって、他の2つのビット線の間に存在する第1のビット線と、

前記第2のメモリセルのセットに電気的に接続された第2のビット線であって、前記第1のビット線に比べて第2のビット線は、前記第1の方向に沿った、より多くのメモリセルのセットに電気的に接続されるとともに、前記第1及び第2のメモリセルのセットを含むメモリアレイ内で前記第1のビット線が第2のビット線に実質的に平行である、第2のビット線と、

20

複数の不連続記憶素子であって、前記第1のメモリセルのセット内の各メモリセルにおいて、前記複数の不連続記憶素子のうちの第1のセットが、前記制御ゲート電極と前記トレンチの前記第1の壁との間に該第1の壁に沿って存在しており、前記第2のメモリセルのセット内の各メモリセルにおいて、前記複数の不連続記憶素子のうちの第2のセットが、前記制御ゲート電極と前記トレンチの前記第2の壁との間に該第2の壁に沿って存在している、複数の不連続記憶素子と、

を備える電子デバイス。

30

**【請求項4】**

前記第1および第2のメモリセルのセット内の各メモリセルは、選択ゲート電極および前記制御ゲート電極を含む不揮発性メモリセルからなる、請求項3に記載の電子デバイス。

**【請求項5】**

前記第1および第2のメモリセルのセットのチャネル領域と前記制御ゲート電極との間に前記不連続記憶素子が存在し、

前記第1および第2のメモリセルのセットのチャネル領域と前記選択ゲート電極との間には前記不連続記憶素子が実質的に存在しない、請求項4に記載の電子デバイス。

**【発明の詳細な説明】**

40

**【技術分野】**

**【0001】**

本発明は電子デバイスに関し、さらに具体的にはゲート線、ビット線、またはこれらの組合せを含む電子デバイスに関する。

**【背景技術】**

**【0002】**

不揮発性フローティング・ゲート・メモリ（「FG NVM」）は従来からあり、一般的に多数の用途で使用されている。FG NVMのための最も一般的な3種類のプログラミング機構は、ファウラーノルドハイム・トンネリング、従来のホット・キャリア注入、およびソース・サイド注入を含む。ファウラーノルドハイム・トンネリングは有効である

50

が、非常に遅い。効率は、フロー・ティンギ・ゲートまたは他の1つ以上の記憶素子に入るキャリア数を、フロー・ティンギ・ゲートまたは他の1つ以上の記憶素子を有するメモリセルに入るキャリア数で割ることによって測定することができる。後者のキャリア数は、プログラミング電流とプログラミング時間との積を用いることにより概算することができる。

#### 【0003】

ホット・キャリア注入は、従来のホット・キャリア注入およびソース・サイド注入を含むことができる。両注入法ともホット・キャリアを生成し、そのうちのいくつかをフロー・ティンギ・ゲートまたは他の1つ以上の記憶素子に注入することを伴う。従来のホット・キャリア注入ではフロー・ティンギ・ゲートを用いる際、電界がメモリセルのチャネル領域に沿って生成される。このチャネル領域内では、電界はドレイン領域近傍で最も高くなる。この電界がチャネル領域内を流れるキャリアを加速させて、チャネル領域内では、キャリアはドレイン領域近傍で最も速く移動する。キャリアの少数部分はチャネル領域内のシリコンあるいは他の1つ以上の原子と衝突し、活発なキャリアをフロー・ティンギ・ゲートまたは他の1つ以上の電荷蓄積素子に再度方向付ける。コントロール・ゲート電極によって生成される電界が、そのホット・キャリアの少数部分のいくつかをフロー・ティンギ・ゲートに注入しやすくする。従来のホット・キャリア注入は非効率的であり、高いプログラミング電流を有する。

#### 【0004】

ソース・サイド注入は、効率およびプログラミング電流に関して、ファウラーノルドハイム・トンネリングと従来のホット・キャリア注入との間の一般的な妥協策である。ソース・サイド注入を用いれば、ホット・キャリアは依然として生成されるが、そのホット・キャリアの殆どはドレイン領域から離間されたチャネル領域の一部内で生成される。ソース・サイド注入によってプログラムされるように設計されたメモリセルは問題がないとは言えない。典型的には、このメモリセルは1つまたは複数の追加のリソグラフィ・シーケンスを必要とし、その結果、メモリセルは大型になる。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

高密度フロー・ティンギ・ゲート・メモリを商業的量で製造することが一層困難になっている。ゲート誘電体層の厚さが小さくなると、ゲート誘電体層の厚さにわたって延在するピンホールまたは他の欠陥が生じる可能性が大きくなる。こういった欠陥は基板とフロー・ティンギ・ゲートとの間に電気的短絡または漏れ経路を生じさせことがある。電気的短絡または漏れ経路は、フロー・ティンギ・ゲートの電圧に影響を及ぼすおそれがあり、このため、メモリセルがデータを保持できない可能性がある。二酸化ケイ素の代わりに1つまたは複数の材料をゲート誘電体層に使用してもよいが、そういった材料は、メモリセルに用いられる他の材料との材料互換性、新しい機器の必要性、製造コストが増大すること等の他の問題を生じさせることがある。

#### 【課題を解決するための手段】

#### 【0006】

電子デバイスは、第1の方向に実質的に沿って配向された第1のメモリセルのセットと、第1の方向に実質的に沿って配向された第2のメモリセルのセットとを含む。この電子デバイスはさらに、第1のメモリセルのセットに電気的に接続された第1のゲート線と、第2のメモリセルのセットに電気的に接続された第2のゲート線とを含む。第1のゲート線に比べて第2のゲート線は、第1の方向に沿って位置する、より多くのメモリセルのセットに電気的に接続されている。

#### 【0007】

電子デバイスは、第1の方向に実質的に沿って配向された第1のメモリセルのセットと、第1の方向に対して実質的に直交する第2の方向に実質的に沿って配向された第2のメモリセルのセットとを含む。この電子デバイスはさらに、第1のメモリセルのセットに電

10

20

30

40

50

気的に接続された第1のゲート線も含む。第1のメモリセルのセットは、第2のメモリセルのセットの一部ではない第1のメモリセルと、第2のメモリセルのセットの一部である第2のメモリセルとを含む。この電子デバイスはさらに、第2のメモリセルのセットに電気的に接続された第2のゲート線を含む。第2のゲート線は、第1の方向に実質的に沿って配向されたメモリセルに電気的に接続された第1のゲート線に比べて、第2の方向に実質的に沿って配向された、より多くのメモリセルに電気的に接続されている。

#### 【0008】

電子デバイスは、第1の方向に実質的に沿って配向された第1のメモリセルのセットと、第1の方向に実質的に沿って配向された第2のメモリセルのセットとを含む。この電子デバイスはさらに、第1のメモリセルのセットに電気的に接続された第1のビット線と、第2のメモリセルのセットに電気的に接続された第2のビット線とを含む。第1のビット線に比べて第2のビット線は、第1の方向に沿った、より多くのメモリセルのセットに電気的に接続されている。

10

#### 【発明を実施するための最良の形態】

#### 【0009】

本発明を一例として添付図面に例示するが、限定するものではない。当業者であれば、図中の要素は簡潔さおよび明確さを目的として示されたものであって、必ずしも寸法通りに描かれているわけではないことを理解し得る。例えば図面中の要素の一部の寸法は、本発明の実施形態の理解を深めることができるように他の要素に対して誇張されている場合がある。

20

#### 【0010】

ある1つの電子デバイスはトレンチ内に存する不連続な記憶素子を含むことができる。この電子デバイスは、相互に離間された第1のトレンチおよび第2のトレンチを含む基板を含むことができる。第1および第2のトレンチの各々は壁と底部とを含み、基板の主表面から延在する。電子デバイスは不連続な記憶素子も含むことができ、不連続な記憶素子の第1の部分は少なくとも第1のトレンチ内に位置し、不連続な記憶素子の第2の部分は少なくとも第2のトレンチ内に位置する。電子デバイスは不連続な記憶素子の第1の部分の上に位置する第1のゲート電極をさらに含むことができる。第1のゲート電極の上面は基板の主表面より下方に位置する。また、電子デバイスは不連続な記憶素子の第2の部分の上に位置する第2のゲート電極をさらに含むことができ、この第2のゲート電極の上面は基板の主表面より下方に位置する。電子デバイスは第1のゲート電極、第2のゲート電極、またはこれらの組合せの上に位置する第3のゲート電極も含むことができる。また本明細書に記載された実施形態は電子デバイスを形成する工程も含む。

30

#### 【0011】

電子デバイスはメモリ・アレイを含み、このメモリ・アレイでは、ビット線、ゲート線、またはこれらの組合せが上記トレンチ設計および埋め込みビット線を利用することができる。1つの実施形態では、制御ゲート線と比較して、選択ゲート線は、異なる数の行または列のメモリセルに電気的に接続されてもよい。具体的な実施形態では、選択ゲート線は1つの行または1つの列のメモリセルに電気的に接続され、制御ゲート線は2つの行または2つの列のメモリセルに電気的に接続される。別の実施形態では、同様の関係はビット線についても存在し得る。さらに別の実施形態では、選択ゲート線および制御ゲート線は、互いに実質的に直角であってよい。制御ゲート線と比較して、選択ゲート線は、異なる数の行または列のメモリセルに電気的に接続されてもよい。具体的な1つの実施形態では、選択ゲート線は1つの行または1つの列のメモリセルに電気的に接続され、制御ゲート線は2つの行または2つの列のメモリセルに電気的に接続される。

40

#### 【0012】

以下に記載の実施形態の詳細を述べる前に、いくつかの用語を定義し明確にする。用語「不連続な記憶素子 (discontinuous storage element)」とは、電荷を蓄積することのできる離間された物体を意味する。1つの実施形態では、実質的にすべての不連続な記憶素子が最初から形成されていてもよいし、相互に離間されたままであってもよい。別の実

50

施形態では、実質的に連続するように形成された材料層が、後で不連続な記憶素子に分離されてもよい。さらに別の実施形態では、実質的にすべての不連続な記憶素子が、最初から相互に分離した状態で形成されてもよく、また、形成中に後で形成されてもよく、また、不連続な記憶素子の全部ではないが一部が合体していてもよい。

#### 【0013】

用語「主表面」とは、メモリ・アレイ内のメモリセルが次に形成される基板表面を意味する。主表面は電子部品を形成する前の基板の元表面であってもよいし、メモリ・アレイ内のトレンチまたは他の永久構造体が形成される表面であってもよい。例えば、メモリ・アレイの少なくとも一部が、ベース材料の上に位置するエピタキシャル層内に形成され、周縁領域（メモリ・アレイの外側）内の電子部品がベース材料から形成されてもよい。この例では、主表面とはエピタキシャル層の上面を指し、ベース材料の元表面を指すものではない。10

#### 【0014】

用語「積層体」とは複数の層、または複数のうちの少なくとも1つの層および少なくとも1つの構造体（例えば、ナノ結晶）を意味し、複数の層または複数の1つ以上の層および1つ以上の構造体は電子的機能を提供する。例えば、不揮発性メモリ積層体は不揮発性メモリセルの少なくとも一部を形成するのに用いられる層を含むことができる。積層体はより大きな積層体の一部であってもよい。例えば、不揮発性メモリ積層体は、電荷を不揮発性メモリセル内に蓄積するのに用いられる電荷蓄積層を含むことができる。

#### 【0015】

別途定めのない限り、本明細書で使用されるすべての技術的用語および科学的用語は、本発明が属する当業者によって一般に理解され得る同じ意味を有する。本明細書で言及するすべての刊行物、特許出願、特許および他の引用物は全体的に本明細書に援用される。問題がある場合、諸定義を含む本明細書が支配するものとする。また、材料、方法および実施例は説明のためのものに過ぎず、限定することを意図するものではない。20

#### 【0016】

本発明の他の特徴および利点は以下の詳細な説明および添付の特許請求の範囲から明白となる。本明細書に記載されていない、具体的な材料、加工行為、および回路に関する多くの詳細については従来のものであって、半導体技術およびマイクロエレクトロニクス技術の資料等に見い出すことができる。30

#### 【0017】

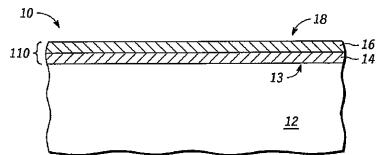

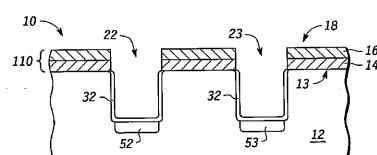

図1は集積回路などの電子デバイス10の一部分の断面図を含む。集積回路はスタンドアロン・メモリ、マイクロコントローラ、またはメモリを含む他の集積回路である。1つの実施形態では、電子デバイス10は不揮発性メモリ（「NVM」）アレイ18を含み、その一部分を図1に示す。基板12は、単結晶半導体ウェハ、セミコンダクター・オン・インシュレータ・ウェハ、フラット・パネル・ディスプレー（例えば、ガラス板を覆うシリコン層）、または電子デバイスの形成に従来用いられる他の基板を含むことができる。図示していないが、浅いトレンチ分離が、NVMアレイ18の外側の周縁領域内の基板12の一部分の上に形成されてもよい。場合によっては、主表面13の複数部分の上に逐次形成されるゲート電極間の漏れ電流を潜在的に低減すべく、NVMアレイ18内の主表面13に沿った基板12のドープ濃度を、従来のドーピング操作を用いて増大させることができる。保護層110は基板12上に形成される。保護層110は、基板12の上のパッド層14、およびパッド層14の上の酸化抵抗層16を含む。保護層110は図示のものよりも層が多くてもよいし、少なくてよい。パッド層14と接続するように図示された基板12の最上層が主表面13である。NVMアレイ18の製造が実質的に終了するまで、保護層110は周縁領域の上に残ったままであり得る。1つの実施形態では、パッド層14は酸化物を含み、酸化抵抗層16は窒化物を含む。40

#### 【0018】

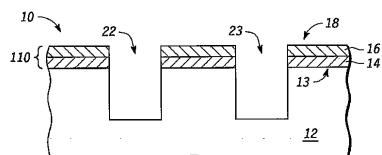

トレンチが形成されるべきNVMアレイ18内の場所において開口部を含むパターン化されたレジスト層（図示せず）が、従来の方法によって基板12の上に形成される。次い50

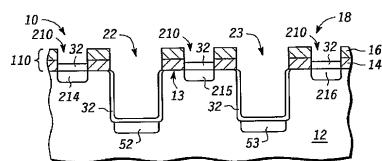

で、保護層 110 の露出部分が従来の方法によって除去され、主表面 13 が露出される。1つの実施形態では、図 2 に示すように、パターン化されたレジスト層を除去する前にトレンチ 22, 23 を形成する。別の実施形態では、パターン化されたレジスト層を除去し、次いで従来の方法によってトレンチ 22, 23 を形成することができる。トレンチ 22, 23 は互いに分離され、主表面 13 から延在し、壁および底部を含む。トレンチ 22, 23 の深さは、少なくとも一部において、トレンチ 22, 23 に隣接して形成されている 1つまたは複数のメモリセルのチャネル長を決定する。1つの実施形態では、トレンチ 22, 23 の深さは約 50 ~ 約 500 nm の範囲である。具体的な 1つの実施形態では、时限的異方性エッチング (timed anisotropic etch) を用いてトレンチ 22, 23 を形成して、実質的に垂直な壁を形成する。1つの実施形態では、トレンチ 22, 23 は実質的に均一な深さを有する。10

#### 【 0019 】

図 3 に示すように、トレンチ 22, 23 の露出表面に沿って絶縁層 32 が形成される。絶縁層 32 は実質的に等角であってもよいし、そうでなくてもよい。1つの実施形態では、絶縁層 32 は、酸化物、窒化物、酸窒化物、またはこれらの組合せを含んでよい。1つの実施形態では、絶縁層 32 は埋め込みスクリーンとして用いられる。具体的な実施形態では、絶縁層 32 は、トレンチ 22, 23 内の基板 12 の露出部分を熱酸化させることによって形成される。熱酸化法は、欠陥、例えばエッチングによって引き起こされる欠陥を除去する際に有用であり、トレンチ 22, 23 またはこれらの組合せの角を丸くするのに役立ち得る。他の実施形態（図示せず）では、絶縁層 32 は堆積される。堆積された絶縁層 32 は、加工物の露出表面の実質的に全部を覆う。20

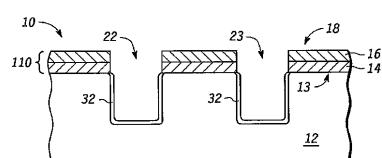

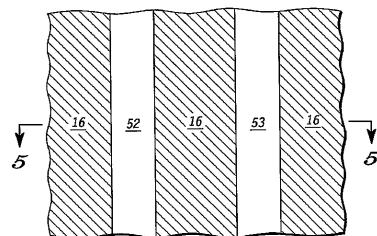

#### 【 0020 】

図 4 の上面図および図 5 の断面図にそれぞれ示すように、トレンチ 22, 23 の底部にある基板 12 の一部にドーパントを導入して、ドープ領域 52, 53 を形成する。ドープ領域 52 は基板 12 内のトレンチ 22 より下方に位置し、ドープ領域 53 は基板 12 内のトレンチ 23 より下方に位置する。ドープ領域 52, 53 はソース / ドレイン（「S / D」）領域であり、埋め込みビット線として機能し得る。ドーパントは p 型ドーパント（例えばホウ素）または n 型ドーパント（例えばリンまたは砒素）である。1つの実施形態では、ドーパントはイオン注入法を用いて導入される。ドーパントは任意の熱サイクルを行って活性化することができる。別の実施形態では、続く加工がドーパントを活性化し得る 1つまたは複数の熱サイクルを有してもよい。トレンチ 22, 23 の底部においては、ドープ領域 52, 53 のドープ濃度は少なくとも  $1 \times 10^{19}$  原子 /  $\text{cm}^3$  である。30

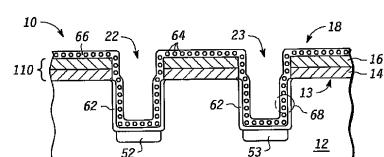

#### 【 0021 】

図 6 に示すように、次いで電荷蓄積層体 68 が形成される。電荷蓄積層体 68 は、誘電体層 62、不連続な記憶素子 64 および誘電体層 66 を含む。1つの実施形態では、トレンチ 22, 23 の壁および底部を含むトレンチ 22, 23 の露出表面上に誘電体層 62 を形成する前に、絶縁層 32 が除去される。別の実施形態では、絶縁層 32 は誘電体層 62 の代わりに用いられるか、またはそれと共に用いられる。誘電体層 62 は周囲を酸化または窒化させることを用いて熱的に成長させてもよいし、従来の化学的蒸着法、物理的蒸着法、原子層蒸着法、またはこれらの組合せを用いて堆積させてもよい。誘電体層 62 を熱的に成長させる場合、この誘電体層は、NVM アレイ 18 のトレンチの外側には形成されない。誘電体層 62 を堆積させる場合（図示せず）、加工物の露出表面の実質的に全ての上に、この誘電体層を堆積させることができる。誘電体層 62 は二酸化シリコン、窒化シリコン、酸窒化シリコン、高誘電率（「高 k」）（例えば、誘電率が 8 より大きい）の材料、またはこれらの組合せの 1つまたは複数の膜を含むことができる。高 k 材料としては、 $\text{Hf}_a\text{O}_b\text{N}_c$ 、 $\text{Hf}_a\text{Si}_b\text{O}_c$ 、 $\text{Hf}_a\text{Si}_b\text{O}_c\text{N}_d$ 、 $\text{Hf}_a\text{Zr}_b\text{O}_c\text{N}_d$ 、 $\text{Hf}_a\text{Zr}_b\text{Si}_c\text{O}_d\text{N}_e$ 、 $\text{Hf}_a\text{Zr}_b\text{O}_c$ 、 $\text{Zr}_a\text{Si}_b\text{O}_c$ 、 $\text{Zr}_a\text{Si}_b\text{O}_c\text{N}_d$ 、 $\text{ZrO}_2$ 、他の Hf 含有誘電体材料ないしは Zr 含有誘電体材料、前述のいずれかをドープ（ランタン・ドープ、ニオビウム・ドープ等）したもの、またはこれらの組合せが挙げられる。誘電体層 62 は、約 1 ~ 約 10 nm の範囲の厚さを有する。誘電体層4050

6 2 の厚さおよび材料選択が、その誘電体層の電気的特性を実質的に決定する。1つの実施形態では、厚さおよび材料は、誘電体層 6 2 が 1 0 n m 未満の同等の厚さの二酸化シリコンを有するように選択される。

#### 【 0 0 2 2 】

次いで、不連続な記憶素子 6 4 が N V M アレイ 1 8 上に形成される。1つの実施形態では、不連続な記憶素子 6 4 の一部は少なくともトレンチ 2 2 内に存在し、不連続な記憶素子 6 4 の別の部分は少なくともトレンチ 2 3 内に存在する。個々の不連続な記憶素子 6 4 は実質的に物理的に相互に離間されている。不連続な記憶素子 6 4 は電荷を蓄積することのできる材料、例えば、シリコン、窒化物、金属含有材料、電荷を蓄積することのできる他の適した材料、またはこれらの組合せを含むことができる。例えば、不連続な記憶素子 6 4 はシリコン・ナノクリスタルまたは金属ナノクラスタを含むことができる。具体的な1つの実施形態では、アモルファス・シリコンの実質的に連続した層が基板 1 2 の露出表面上に形成される。この実質的に連続した層は熱に曝すこともできるし、層を「ボールアップ (ball up)」させるかまたはシリコンナノ結晶を形成することのできる他の処理条件に曝すこともできる。不連続な記憶素子 6 4 はドープされていないものであってもよいし、堆積中にドープされてもよいし、堆積後にドープされてもよい。1つの実施形態では、不連続な記憶素子 6 4 は、熱酸化工程中に著しく有害な影響を受けない特性を持つ1つまたは複数の材料から形成される。このような材料は、白金、パラジウム、イリジウム、オスミウム、ルテニウム、レニウム、インジウム - スズ、インジウム - 亜鉛、アルミニウム - スズ、またはこれらの組合せを含むことができる。白金およびパラジウム以外のこのような材料の各々は、導電性金属酸化物を形成し得る。1つの実施形態では、不連続な記憶素子 6 4 の各々は、どの寸法も約 1 0 n m 以下である。別の実施形態では、不連続な記憶素子 6 4 が大きな場合があるが、不連続な記憶素子 6 4 はそれほど大きく形成されずに連続した構造を形成する（すなわち、不連続な記憶素子 6 4 の全部は一緒に融合されない。）。

#### 【 0 0 2 3 】

次いで、誘電体層 6 6 が不連続な記憶素子 6 4 上に形成される。誘電体層 6 6 は1つまたは複数の誘電体膜を含むことができ、そのうちのいずれかは熱的に成長させてもよいし、堆積させてもよい。誘電体層 6 6 は任意の1つまたは複数の材料を含んでもよいし、誘電体層 6 2 に関して前述した実施形態のいずれかを用いて形成されてもよい。誘電体層 6 6 は、誘電体層 6 2 と異なる組成または同じ組成を有し、また、誘電体層 6 2 と同じ形成法または異なる形成法を用いて形成される。

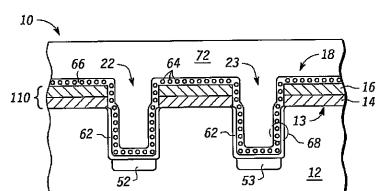

#### 【 0 0 2 4 】

次いで、図 7 に示すように、導電層 7 2 が加工物の上に形成される。導電層 7 2 は1つまたは複数の半導体含有膜または金属含有膜を含むことができる。1つの実施形態では、導電層 7 2 は化学的蒸着工程によって堆積されたポリシリコンまたはアモルファス・シリコンを含む。別の実施形態では、導電層 7 2 は1つまたは複数の他の材料を含んでもよいし、他の工程によって堆積されてもよい。具体的な1つの実施形態では、導電層 7 2 は堆積時にドープされ、別の具体的な実施形態では、その層が堆積された後でドープされる。導電層 7 2 の厚さは、N V M アレイ 1 8 内のトレンチを少なくとも実質的に充填するのに十分である。1つの実施形態では、導電層 7 2 の厚さは約 5 0 ~ 約 5 0 0 n m の範囲であり、完成したデバイスにおいては、導電層 7 2 の残りの部分は、導電層 7 2 がポリシリコンまたはアモルファス・シリコンを含んでいるときに、少なくとも  $1 \times 10^{19}$  原子 /  $c m^3$  のドーパント濃度を有する。

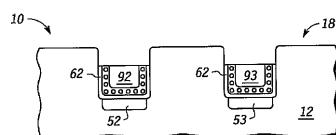

#### 【 0 0 2 5 】

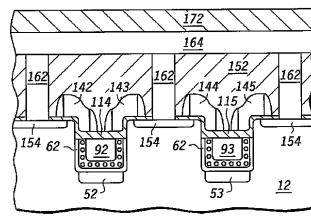

図 8 および図 9 に示すように、主表面 1 3 上に位置するとともにトレンチ 2 2 , 2 3 の外側に位置する導電層 7 2 の部分が除去される。図 8 および他の上面図では、N V M アレイ 1 8 内の特徴間の位置関係を分かりやすくするために、いくつかの誘電体層または絶縁層を示していない。導電層 7 2 は、その残りの材料が主表面 1 3 より下方において凹状に、かつトレンチ 2 2 , 2 3 内に含まれてゲート電極 9 2 , 9 3 を形成するように除去され

10

20

30

40

50

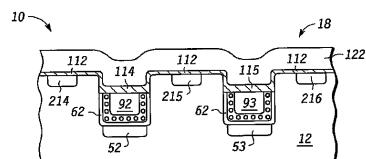

る。これらゲート電極の各々は主表面 13 より下方に位置する上面を有する。ゲート電極 92 はトレーナー 22 内の不連続な記憶素子 64 の一部分の上に位置し、ゲート電極 93 はトレーナー 23 内の不連続な記憶素子 64 の別の部分の上に位置する。1つの実施形態では、ゲート電極 92, 93 の各々は断面図から分かるように、実質的に矩形を有する。具体的な1つの実施形態では、導電層 72 は最初に堆積されるドープされていないポリシリコンである。次いで、完成されたデバイスにおいてゲート電極 92, 93 が少なくとも  $1 \times 10^{19}$  原子 /  $\text{cm}^3$  の濃度を有するように、ゲート電極 92, 93 を従来の方法によってドープする。別の実施形態では、シリコンと反応してシリサイドが形成され、かつ、Ti、Ta、Co、W、Mo、Zr、Pt、他の適した材料、またはこれらの組合せを含む材料をゲート電極 92, 93 上に形成し、反応させることによって金属シリサイドが形成される。10

#### 【0026】

具体的な1つの実施形態では、導電層 72 の一部分の除去は、従来の方法を用いた研磨により酸化抵抗層 16 を露出させ、続いて時限的エッティングを行うことによって達成される。別の実施形態（図示せず）では、この除去は研磨を行わないエッティング工程によって達成される。別の実施形態では、主表面 13 とゲート電極 92, 93 の最上部との間の段差である凹部は、トレーナー 22, 23 の深さの 20% ~ 80% の間である。

#### 【0027】

図 10 に示すように、従来の方法によって NVM アレイ 18 内の保護層 110 の残りの部分が除去される。1つの実施形態では、パッド層 14 は、不連続な記憶素子 64 をアンダーカットし、それらを灌ぎ流すウェット・エッティングによって除去された酸化物層である。別の実施形態（図示せず）では、誘電体層 66 の露出された部分を除去して不連続な記憶素子 64 を露出させ、次いでそれらを追加の処理によって導電性から電気的な絶縁性へと変化させる。具体的な1つの実施形態では、不連続な記憶素子 64 は、酸化されて二酸化シリコンが形成されるシリコン結晶である。1つの実施形態では、工程のこの時点においては、不連続な記憶素子 64 は主表面 13 上に実質的には存在しないか、またはゲート電極 22, 23 の最上部の上に位置するトレーナー 22, 23 の壁に沿って実質的には存在しない。20

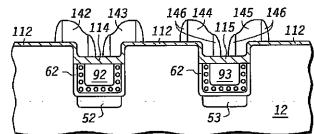

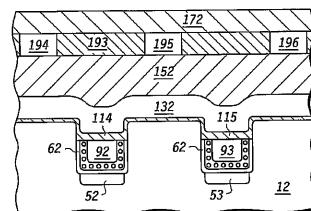

#### 【0028】

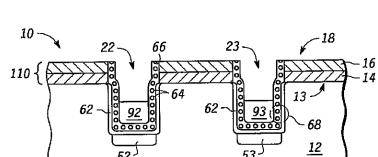

次いで、図 11 に示すように、ゲート誘電体部分 112 と中間ゲート誘電体部分 114, 115 を含む絶縁層が NVM アレイ 18 上に形成される。この絶縁層は1つまたは複数の誘電体膜を含むことができ、この誘電体膜は熱的に成長させててもよいし、堆積させててもよい。この絶縁層は1つまたは複数の材料を含むことができるか、または誘電体層 62 に関して前述した実施形態のいずれかを用いて形成することができる。この絶縁層は誘電体層 62 と同じ組成または異なる組成を有し、また、誘電体層 62 と同じ形成法または異なる形成法を用いて形成される。中間ゲート誘電体部分 114, 115 の厚さはメモリセルのチャネル領域内の電界に影響を及ぼし得る。この電界は、メモリセルの各々に対するソース・サイド注入を可能とすべく、チャネル領域内の電界が最も高く変化するように設計される。1つの実施形態では、中間ゲート誘電体部分 114, 115 の厚さは約 10 ~ 約 30 nm の範囲である。30

#### 【0029】

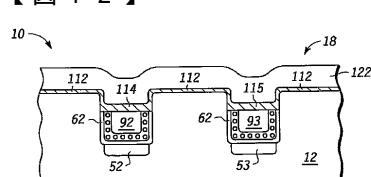

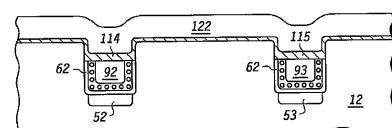

図 12 に示すように、導電層 122 が NVM アレイ 18 上に形成される。導電層 122 は1つまたは複数の半導体含有膜または金属含有膜を含むことができる。1つの実施形態では、導電層 122 はポリシリコンでドープされている。別の実施形態では、導電層 122 は金属含有材料から形成される。1つの実施形態では、導電層 122 の厚さは約 20 ~ 約 300 nm の範囲である。別の実施形態では、導電層 122 がポリシリコンまたはアモルファス・シリコンを含むとき、導電層 122 は少なくとも約  $1 \times 10^{19}$  原子 /  $\text{cm}^3$  のドーパント濃度を有する。40

#### 【0030】

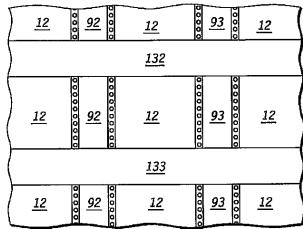

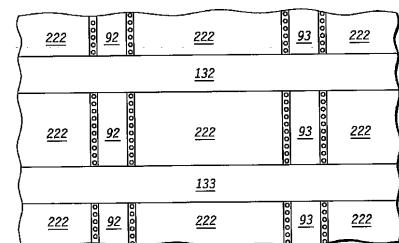

従来の方法を用いて導電層 122 をパターン化することにより、図 13 に示すように、50

ゲート電極を含む導電線 132, 133 を形成する。導電線 132, 133 は、少なくとも一部分が、トレンチ 22、トレンチ 23、NVM アレイ 18 内の 1つまたは複数の他のトレンチ(図示せず)、またはこれらの組合せのトレンチ内に位置する。1つの実施形態では、導電線 132, 133 の長さは、NVM アレイ 18 内のトレンチ 22, 23 の長さに対して実質的に直交する。場合によっては、シリコンと反応してシリサイドを形成することのできる材料(例えば、Ti、Ta、Co、W、Mo、Zr、Pt、他の適した材料、またはこれらの組合せ)を導電線 132, 133 上に形成し、反応させて金属シリサイドを形成する。別の実施形態では、導電線 132, 133 を NVM アレイ 18 のためのワード線として用いることができ、それらの一部分は複数のビット・セルのゲート電極として機能し得る。場合によっては、側壁スペーサが導電線 132, 133 に隣接して形成されてもよい。

#### 【0031】

1つの実施形態では、NVM アレイ 18 が実質的に完成する。1つの実施形態では、周縁の電気的接続(図示せず)を NVM アレイ 18 の導電性部分に接近させる。基板 12 の周縁領域上に位置する保護層 110 を除去することができる。別の保護層(図示せず)を NVM アレイ 18 上に形成することができ、この保護層は周縁領域内のコンポーネント製造中に NVM アレイ 18 を保護し得る。加工を継続して実質的に完成された電子デバイスを形成することができる。1つまたは複数の従来の方法を用いて、1つまたは複数の絶縁層、1つまたは複数の導電層、および1つまたは複数の封止層を形成する。

#### 【0032】

別の実施形態では、異なる NVM アレイ 18 のレイアウトおよび相互接続スキームが用いられてもよい。この実施形態では、NVM アレイ 18(図 12)全体の上に導電層 122 を形成する工程は、前述の実施形態を用いて形成することができる。

#### 【0033】

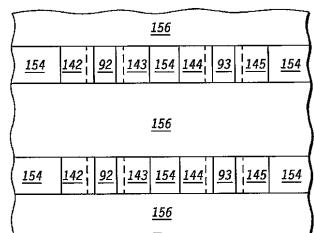

導電層 122 をパターン化およびエッチングすることにより、図 14 に示すように導電線 142 ~ 145 が形成される。導電線 142 ~ 145 は NVM アレイ 18 においてワード線として機能し得る。導電線 142 ~ 145 の長さはトレンチ 22, 23 の長さと実質的に平行である。実施形態では、導電線 142 ~ 145 の一部分はトレンチ 22, 23 の凹部内に位置することができる。導電線 142 ~ 145 の組成および形成方法は、導電線 132, 133 の形成に関して前述したいずれの方法であってもよい。場合によっては、側壁スペーサ 146 が導電線 142 ~ 145 に隣接して形成されてもよい。

#### 【0034】

図 15 に示すように、パターン化されたレジスト層 156 を加工物の上に形成して導電線 142 ~ 145 の一部分およびゲート誘電体部分 112 の一部分(図 15 には図示さず)を露出させる。1つの実施形態では、パターン化されたレジスト層 156 の開口部は、次にビット線がその上に形成される場所に実質的に相当する。図 15 に示すように、ドーパントが基板 12 の部分に導入されてドープ領域 154 が形成される。ドーパントは p 型ドーパント(例えば、ホウ素)または n 型ドーパント(例えば、リンまたは砒素)であってもよい。1つの実施形態では、イオン注入法を用いてドーパントを導入することができる。次いで、パターン化されたレジスト層 156 を従来の方法によって除去する。1つの実施形態では、注入されたドーパントを1つまたは複数の次の熱サイクルによって活性化させる。この熱サイクルは異なる主な目的、例えば異なる注入ドーパントの酸化、堆積、アニーリング、ドライブまたは活性化を提供し得る。1つの実施形態では、ドープ領域 154 の各々は少なくとも約 1 E 19 原子 / cm<sup>3</sup> のドーパント濃度を有する。具体的な実施形態では、完成したデバイスにおいてはドープ領域 154 は S / D 領域として働く。

#### 【0035】

1つの実施形態では、この時点で NVM アレイ 18 は、電気的接続が実質的に完成する。基板 12 の周縁領域上に位置する保護層 110 の残りの部分(図 15 には示さず)を除去し、また、周縁領域内のコンポーネント製造中に NVM アレイ 18 を保護し得る別の保護層(図示せず)を NVM アレイ 18 上に形成することができる。周縁領域内のコン

10

20

30

40

50

ポーネント製造は、1つまたは複数の従来の方法を用いて行うことができる。周縁領域内でのコンポーネント製造が実質的に完了すると、NVMアレイ18上に位置する保護層は除去することができる。

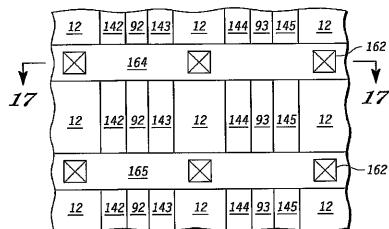

#### 【0036】

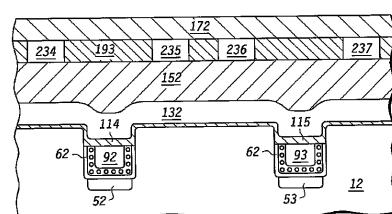

加工を継続して、図16および図17に示すように、実質的に完成された電子デバイスを形成する。図17を参照すると、中間誘電体層152が従来の方法によって加工物上に形成される。中間誘電体層152をパターン化することによって、ドープ領域154、および図16、図17には示されていないNVMアレイ18の他の部分にまで延びるコンタクト開口部が形成される。中間誘電体層152は、酸化物、窒化物、酸窒化物、またはこれらの組合せなどの絶縁材料を含むことができる。具体的な実施形態では、異方性エッチングを用いてコンタクト開口部を形成することができる。10

#### 【0037】

次いで、導電プラグ162ならびに導電線164、165が形成される。図16に示すように、導電線164、165の長さは導電線142～145の長さに対して実質的に直交する。1つの実施形態では、導電線164、165はNVMアレイ18のビット線であり、導電プラグ162はビット線コンタクトである。図16を参照すると、基板12の諸部分は導電線164、165間に位置しているのが示されている。図16には示していないが、ドープ領域154は基板12の諸部分の間の導電線164、165より下方に位置している。

#### 【0038】

1つの実施形態では、導電線164、165に先立って導電プラグ162が形成される。具体的な1つの実施形態では、導電層(図示せず)は中間誘電体層152上に形成され、その中にあるコンタクト開口部を実質的に充填する。このコンタクト開口部の外側に位置する導電層の諸部分が除去されて導電プラグ162が形成される。1つの実施形態では、従来の化学的-機械的研磨操作を行うことができ、別の実施形態では、従来のエッティング工程を行うことができる。20

#### 【0039】

次いで、別の絶縁層(図示せず)を堆積させ、パターン化することによって、その後に導電線164、165が形成されるトレンチを形成する。NVMアレイ18内の場所、NVMアレイ18の外側の場所、またはこれらの組合せの場所に他のトレンチを形成することができる。1つの実施形態では、別の導電層が中間誘電体層152上に形成され、絶縁層のトレンチを実質的に充填する。絶縁層内のトレンチの外側に位置する導電層の諸部分が除去されて導電線164、165が形成される。1つの実施形態では、従来の化学的-機械的研磨操作を行うことができ、別の実施形態では、従来のエッティング工程を行うことができる。図16および図17には示されていないが、絶縁層は導電線164、165間の実質的に同じ段差に位置している。別の実施形態(図示せず)では、従来のデュアル・インレイド法を用いて導電プラグ162ならびに導電線164、165は同時に形成される。30

#### 【0040】

導電プラグ162ならびに導電線164、165は、同じ導電性材料または異なる導電性材料を含むことができる。導電プラグ162ならびに線164、165の各々は、ドープされたシリコン、タンゲステン、チタン、タンタル、窒化チタン、窒化タンタル、アルミニウム、銅、別の適した導電性材料、またはこれらの組合せを含むことができる。具体的な1つの実施形態では、導電プラグ162はタンゲステンを含み、導電線164、165は銅を含む。任意の障壁層、接着層、またはこれらの組合せが、対応する導電層(例えば、導電プラグ162に対してはタンゲステン、導電線164、165に対しては銅)に先立って形成されてもよい。任意のキャップ層(例えば、金属含有窒化物)を用いて、導電線164、165内に銅を封入してもよい。

#### 【0041】

別の実施形態(図示せず)では、追加の絶縁層および導電層を形成し、パターン化する40

10

20

30

40

50

ことによって、1つまたは複数の相互接続レベルが形成される。最後の相互接続レベルが形成された後、NVMアレイ18および周縁領域を含むパッシベーション層172が基板12上に形成される。パッシベーション層172は、酸化物、窒化物、酸窒化物、またはこれらの組合せなどの1つまたは複数の絶縁膜を含むことができる。

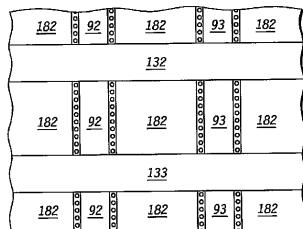

#### 【0042】

別の実施形態では、さらに別のNVMアレイ18のレイアウトおよび相互接続スキームが用いられてもよい。この実施形態では、導電線132, 133を形成する工程(図13)は、図1～図13に関して前述した実施形態を用いて行うことができる。1つの実施形態では、基板12の周縁領域の上に位置する保護層110の残りの部分(図示せず)を除去し、周縁領域内のコンポーネント製造中にNVMアレイ18を保護し得る別の保護層(図示せず)をNVMアレイ18上に形成することができる。周縁領域内のコンポーネント製造は、1つまたは複数の従来の方法を用いて行うことができる。周縁領域内のコンポーネント製造が実質的に終了すると、NVMアレイ18上に位置する保護層を除去することができる。

10

#### 【0043】

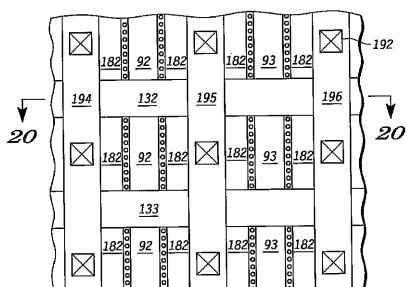

1つの実施形態では、周縁領域およびNVMアレイ18の加工の残りは実質的に同時に行うことができる。導電線132, 133や、NVMアレイ18および周縁領域のゲート電極を含む他の導電線を形成後、図18に示すように、ドーパントを基板12に導入して、ドープ領域182を導電線132, 133間の場所およびトレンチ22, 23の外側でトレンチ22, 23に隣接する場所に形成する。ドープ領域182は、1つまたは複数の材料を含むこともできるし、またはドープ領域154に関して前述した実施形態のいずれかを用いて形成することもできる。ドープ領域182はドープ領域154と同じ組成または異なる組成を有し、また、ドープ領域154と同じ形成法または異なる形成法を用いて形成される。場合によっては、ドープ領域182を形成する際に用いられる個々の作業の前、後、または間ににおいて、スペーサ(図示せず)が導電線132, 133に隣接して形成されてもよい。具体的な1つの実施形態では、任意の側壁スペーサを、他の実施形態に関して前述したように形成することができる。1つの実施形態では、ドープ領域182は完成されたデバイスにおいてS/D領域として機能し得る。具体的な実施形態では、ドープ領域182の各々は少なくとも約1E19原子/cm<sup>3</sup>のドーパント濃度を有する。場合によっては、従来の方法を用いて、導電線132, 133の一部分ならびにドープ領域182から金属シリサイドを形成することができる。

20

#### 【0044】

次いで、図19および図20に示すように、中間誘電体層152の形成およびパターン化に関して前述した実施形態のいずれかを用いて中間誘電体層152を形成し、パターン化してコンタクト開口部を形成する。コンタクト開口部の場所は、コンタクト開口部がドープ領域182まで延びているという点で、前述の実施形態とは異なる。

30

#### 【0045】

図19および図20を参照すると、中間誘電体層152を前述のように形成することができる。次いで、導電プラグ162について前述した実施形態を用いて導電プラグ192を形成する。導電プラグ192の場所は導電プラグ162について図示したものとは異なる。

40

#### 【0046】

図19および図20を参照すると、次いで絶縁層193が、中間誘電体層152および導電プラグ192上に堆積され、パターン化されて、その後に導電線194～196がそこに形成されるトレンチが形成される。NVMアレイ18内の場所、NVMアレイ18の外側の場所、またはこれらの組合せの場所に他のトレンチを形成することができる。次いで、導電線164, 165について前述した実施形態を用いて、導電線194～196が形成される。導電線194～196はNVMアレイ18内でビット線として機能し得る。導電プラグ192ならびに導電線194～196の場所は、それぞれ導電プラグ162および導電線164, 165について示した場所とは異なる。導電線194～196の配向

50

は導電線 164, 165 の配向とは異なる。図 19 に示すように、導電線 194 ~ 196 の長さは導電線 132, 133 の長さに対して実質的に直交する。

#### 【0047】

別の実施形態（図示せず）では、追加の絶縁層および導電層を形成し、パターン化することによって、追加の相互接続レベルを形成することができる。最後の相互接続レベルが形成された後、NVM アレイ 18 および周縁領域を含むパッシベーション層 172 が基板 12 上に形成される。パッシベーション層 172 は、酸化物、窒化物、酸窒化物、またはこれらの組合せなどの 1 つまたは複数の絶縁膜を含むことができる。

#### 【0048】

別の実施形態では、さらに別の NVM アレイ 18 のレイアウトおよび相互接続スキームが用いられてもよい。このレイアウトおよび相互接続スキームは図 1 ~ 図 13 および図 18 ~ 図 20 に示したものに類似するが、導電線 194 ~ 196 ではなく、仮想的な接地アレイ・アーキテクチャが用いられる。このレイアウトおよび編成は、図 21 ~ 図 25 に関する以下の説明を読めばさらに明白となる。

10

#### 【0049】

工程中の比較的早い段階で、それぞれ図 4 および図 5 に類似する図 21 および図 22 に示すように、開口部 210 が保護層 110 内に形成され、ドープ領域 214, 215, 216 がトレチ 22, 23 の外側の基板 12 の主表面 13 に沿って形成される。1 つまたは複数の従来の方法を用いて、開口部 210 ならびにドープ領域 214, 215, 216 を形成することができる。トレチ 22, 23 を形成する前または後から、開口部 210 を形成することができる。例えば、保護層 110 内の全開口部は実質的に同時に形成されてもよい。開口部 210 より下方にトレチが形成されるのを実質的に防ぐために、開口部 210 の上にマスク（図示せず）を形成することができる。トレチ 22, 23 を形成してから、マスクを除去することができる。別の実施形態では、トレチ 22, 23 が形成されてから、開口部 210 上に異なるマスク（図示せず）を形成してもよく、開口部 210 を形成した後でこのマスクを除去することができる。図 3 に関して記載した実施形態に類似する様式で、開口部 210 の底部に沿って絶縁層 32 を形成することができる。

20

#### 【0050】

ドープ領域 52, 53 に関して前述した実施形態の 1 つまたは複数を用いて、ドープ領域 214, 215, 216 を形成することができる。ドープ領域 214, 215, 216 のドーパントの種類、濃度、ならびにプロファイルおよび形成は、ドープ領域 52, 53 と同じであってもよいし、異なっていてもよい。1 つの実施形態では、ドープ領域 214, 215, 216 はドープ領域 52, 53 と同時に形成することができる。ドープ領域 52, 53, 214, 215, 216 は互いに実質的に平行であり、埋め込みビット線として機能し得る。ドープ領域 52, 53 は、ドープ領域 214, 215, 216 に比して基板 12 内のさらに深い高さに位置する。

30

#### 【0051】

さらに別の実施形態（図示せず）では、開口部 210 が形成される。これに代わりに、トレチ 22, 23 を形成後、絶縁層 32 を形成する前に NVM アレイ 18 内の保護層 110 の残りの部分を除去する。ドープ領域 214, 215, 216 は、ドープ領域 52, 53 を形成するときに除去することができる。ドープ領域 214, 215, 216 はトレチ 22, 23 の壁まで延在することができる。

40

#### 【0052】

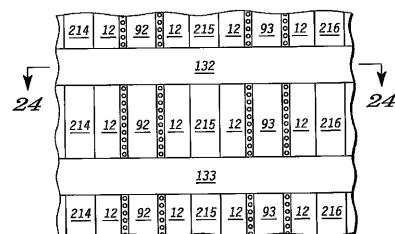

上記実施形態のいずれか 1 つまたはそれらの組合せを用いてドープ領域 52, 53, 214, 215, 216 を形成後、図 6 ~ 図 13 に関して記載した実施形態の 1 つまたは複数を用いて加工を継続する。図 23 および図 24 は NVM アレイ 18 の一部分の図を含み、NVM アレイの形成は実質的に完了する。図 19 および図 20 の導電線 194 ~ 196 に比して、ドープ領域 214 ~ 216 を導電線 194 ~ 196 の代わりに用いることができる。

#### 【0053】

50

1つの実施形態では、周縁の電気的接続（図示せず）をNVMアレイ18の導電性部分に接近させる。基板12の周縁領域上に位置する保護層110を除去することができ、周縁領域内のコンポーネント製造中にNVMアレイ18を保護し得る別の保護層（図示せず）をNVMアレイ18上に形成することができる。加工を継続して実質的に完成された電子デバイスを形成することができる。1つまたは複数の従来の方法を用いて、1つまたは複数の絶縁層、1つまたは複数の導電層、および1つまたは複数の封止層を形成する。

#### 【0054】

別の実施形態では、さらに別のNVMアレイ18のレイアウトおよび相互接続スキームが用いられてもよい。このレイアウトおよび相互接続スキームは、図1～図13および図18～図20に示した実施形態と類似するが、複数のビット線がトレンチ22, 23間に位置し、電気的接続がビット線とビット線より下方のドープ領域の一部のみとの間に形成される。図25～図29に関する以下の説明を読めば、このレイアウトおよび編成はさらに明白となる。

10

#### 【0055】

この実施形態では、図1～図13に関して前述した実施形態を用いて、導電線132, 133の形成工程（図13）が行われる。1つの実施形態では、図25に示すように、トレンチ22, 23間の空間を増大させて、設計規則に一致するビット線およびコンタクトが形成される。別の実施形態では、基板12の周縁領域上に位置する保護層110の残りの部分（図示せず）が除去され、周縁領域内のコンポーネント製造中にNVMアレイ18を保護し得る別の保護層（図示せず）がNVMアレイ18上に形成される。周縁領域内のコンポーネント製造は、1つまたは複数の従来の方法を用いて行うことができる。周縁領域内のコンポーネント製造が実質的に完了した後、NVMアレイ18の上に位置する保護層は取り除くことができる。

20

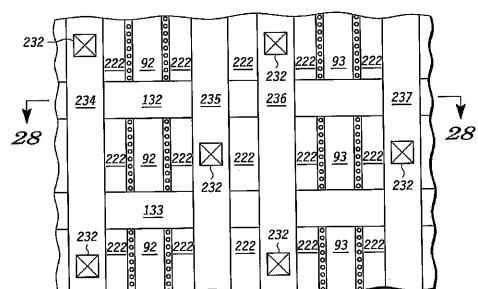

#### 【0056】

図26に示すように、導電線132, 133ならびにドープ領域222の形成は、図18に示す導電線132, 133ならびにドープ領域182に関して前述した実施形態のいずれか1つを用いて行うことができる。次いで、図27および図28に示すように、中間誘電体層152の形成およびパターン化に関して前述した実施形態のいずれかを用いて、中間誘電体層152を形成しパターン化することによって、コンタクト開口部を形成することができる。コンタクト開口部の場所は、コンタクト開口部がドープ領域222まで延びているという点で変更されている。

30

#### 【0057】

図27および図28を参照すると、次いで、導電プラグ192および導電線194～196について前述した実施形態を用いて、導電プラグ232および導電線234～237が形成される。導電線234～237はNVMアレイ18内でビット線として機能し得る。導電プラグ232および導電線234～237の場所はそれぞれ、導電プラグ192および導電線194～196について図示した場所とは異なっている。導電線234～237の配向は、導電線194～196の配向と実質的に同じである。図27に示すように、導電線234, 234の長さは導電線132, 133の長さに対して実質的に直交する。導電線194～196とは異なり、導電線234～237の各々は、導電プラグ232を介して下側ドープ領域222の一部のみへの電気的接続を有する。具体的な1つの実施形態では、下側ドープ領域222との電気的接続は導電線235, 236間で交互になっている。図27を参照すると、導電線235はドープ領域222の真ん中の行に電気的に接続されており、導電線236はドープ領域222の一番上の行および下の行に電気的に接続されている。

40

#### 【0058】

別の実施形態（図示せず）では、追加の絶縁層および導電層を形成してパターン化することによって、追加の相互接続レベルを形成することができる。最後の相互接続レベルが形成された後、NVMアレイ18および周縁領域を含んだパッシベーション層172が基板12上に形成される。パッシベーション層172は1つまたは複数の絶縁膜、例えば、

50

酸化物、窒化物、酸窒化物、またはこれらの組合せを含むことができる。

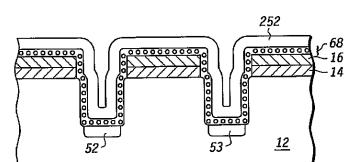

#### 【0059】

別の代替的実施形態では、トレンチ 22, 23 内のゲート電極は側壁スペーサに類似する形状を有することができる。この工程は図 6 に示した加工物とともに開始される。導電層 252 は図 29 に示すように堆積させることができる。1つの実施形態では、導電層 252 は比較的薄く、実質的に等角の層である。導電層 72 に関して前述した1つまたは複数の実施形態を用いて導電層 252 を形成することができる。導電層 252 の厚さは NVM アレイ 18 内のトレンチ構造 22, 23 を充填するには不十分である。1つの実施形態では、導電層 252 の厚さは約 10 nm ~ 約 100 nm の範囲である。

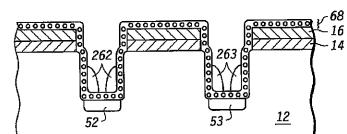

#### 【0060】

次いで、導電層 252 を異方性エッチングすることにより、図 30 に示すゲート電極 262, 263 が形成される。形成されると、ゲート電極 262, 263 はトレンチ 22, 23 内で実質的に側壁スペーサ形状を有する。上面図を示していないが、ゲート電極 262, 263 は、ゲート電極 262, 263 がトレンチ 22, 23 の周囲に沿っているという点で環状になっている。このため、トレンチ 22, 23 内のゲート電極 262, 263 の各々に対する曲線状表面に向いている離間された左右の部分が、相互に接続される。次いで、他の実施形態について前述したように、NVM アレイ 18 の加工を完了することができる。1つの実施形態では、導電線 132, 133 を形成するとき、追加の等方性エッチング部分を用いて、次に形成される導電線 132, 133 間に意図しない電気的接続または漏れ経路が形成される可能性を低減することができる。

10

#### 【0061】

本明細書を読めば、当業者であれば基板 12 のドーピング部分に関する多数の変形例を用いることが可能であることを理解し得る。NVM アレイ 18 内のメモリセルのためのソース / ドレイン領域の少なくとも一部であるドープ領域は、基板 12 とは反対の導電型を有する。図に示した基板 12 の一部分は、1つまたは複数のウェル領域内に位置してもよいし、位置しなくてもよい。このような1つ以上のウェル領域は、周縁領域 (NVM アレイ 18 の外側) 内の1つまたは複数の他のウェル領域とは異なるものであってもよい。破壊電圧、抵抗率、閾値電圧、ホット・キャリア生成、1つまたは複数の他の電気的特性、またはこれらの組合せに影響を及ぼし得る他のドーピングを行うことができる。当業者であれば、それらの要求または要望を満たすドーピング特性を有する電子デバイスを形成することができる。

20

#### 【0062】

NVM アレイ 18 は前述のレイアウトのいずれかを用いたメモリセルを含むことができる。NVM アレイ 18 内のメモリセルを如何にして電気的に構成、プログラミングすることができるかをさらによく説明するために、物理的実施形態に対する回路図および相互参照を記載する。

30

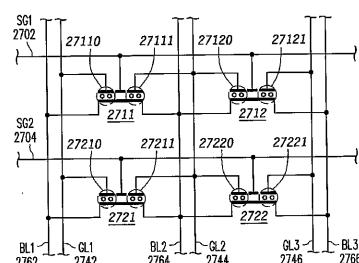

#### 【0063】

図 31 は図 32 に示す実施形態に関して説明したある実施形態についての回路図を含む。メモリセル 2711, 2712, 2721, 2722 は、図 31 に示すように NVM アレイ 18 内で配向されている。図面中、「BL」はビット線を指し、「GL」はゲート線を指し、「CG」は制御ゲート線を指し、「SG」は選択ゲート線を指す。バイアス条件に応じて、GL は CG または SG とすることもできる。

40

#### 【0064】

図 31 を参照すると、BL 1 2762 はメモリセル 2711 の S / D 領域およびメモリセル 2721 の S / D 領域に電気的に接続されている。BL 2 2764 はメモリセル 2711, 2721 の他の S / D 領域、ならびにメモリセル 2712 の S / D 領域およびメモリセル 2722 の S / D 領域に電気的に接続されている。BL 3 2766 はメモリセル 2712, 2722 の他の S / D 領域に電気的に接続されている。GL 1 2742 はメモリセル 2711 のゲート電極およびメモリセル 2721 のゲート電極に電気的に接続されている。GL 2 2744 はメモリセル 2711, 2721 の他のゲート電極、メ

50

モリセル 2712 のゲート電極、ならびにメモリセル 2722 のゲート電極に電気的に接続されている。GL3 2746 はメモリセル 2712, 2722 の他のゲート電極に電気的に接続されている。SG1 2702 は、メモリセル 2711 の選択ゲート電極およびメモリセル 2712 の選択ゲート電極に電気的に接続されている。SG2 2704 はメモリセル 2721 の選択ゲート電極およびメモリセル 2722 の選択ゲート電極に電気的に接続されている。メモリセル 2711 は電荷蓄積領域 27110, 27111 を含む。メモリセル 2712 は電荷蓄積領域 27120, 27121 を含む。メモリセル 2713 は電荷蓄積領域 27130, 27131 を含む。メモリセル 2714 は電荷蓄積領域 27140, 27141 を含む。

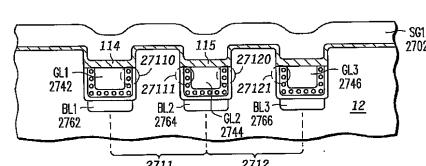

## 【0065】

10

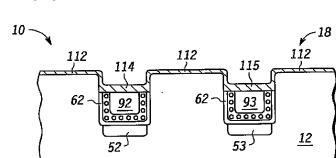

図 32 はメモリセル 2711, 2712 を含む行に相当する NVM アレイ 18 の一部分の物理的実施形態を示す。図 32 は図 12 と実質的に同じであるが、図 32 では回路図に用いられている参照番号が用いられている。

## 【0066】

20

メモリセル 2711, 2712 のための電荷蓄積領域を図 31 および図 32 に示す。メモリセル 2711 は電荷蓄積領域 27110, 27111 を含み、メモリセル 2712 は電荷蓄積領域 27120, 27121 を含む。メモリセル 2721, 2722 は類似する電荷蓄積領域を含むが、この電荷蓄積領域は図 31 には示していない。以下に記載のような電子デバイスの動作に関する対応を読めば、当業者であれば、電荷蓄積領域の重要性を理解し得る。

## 【0067】

図 33 は図 31 に示したメモリセルの動作電圧の一部を有する表を含む。「Pgm」はプログラムを意味する。電荷蓄積領域 27110, 27111 に言及することは、メモリセル 2711 を指し、さらに具体的には、メモリセル 2711 の左側のゲート電極および右側のゲート電極それぞれの下の不連続な記憶素子をプログラミングすることまたは読み出すことを指す。多くの電圧が図 33 の表および本明細書内の他の表に示されているが、他の電圧が用いられてもよい。電圧の絶対値は物理的パラメータの変化とともに変動するので、電圧の絶対値ではなく、電圧間の相対的な値および比はより関連性がある。

## 【0068】

30

図 31 に示す全メモリセルは、基板 12 とメモリセルのゲート電極との間に約 12 ~ 16 ボルトの範囲の電位差を生み出すことによって消去することができる。1 つの実施形態では、消去は、基板 12 (すなわちその中のウェル領域) を約 +7 ボルトにし、ゲート線を -7 ボルトにしてビット線を電気的にフロートにすることによって行うことができる。SG1 および SG2 は -7 ボルトにされてもよいし、電気的にフローとさせてもよい。別の実施形態では、消去は、基板 12 (すなわちその中のウェル領域) を約 -7 ボルトにし、ゲート線を +7 ボルトにしてビット線を電気的にフロートにすることによって行うことができる。なお、基板 12 およびゲート線に用いられる電圧は 0 ボルトに対して対称になっている必要はない。例えば、+5 ボルトおよび -9 ボルトの組合せを用いることができる。本明細書を読めば、当業者であれば、それらの要求または要望を満たす消去用の電圧セットを決定することができる。

40

## 【0069】

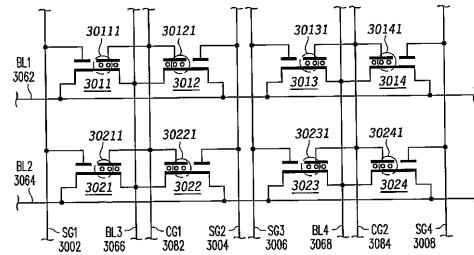

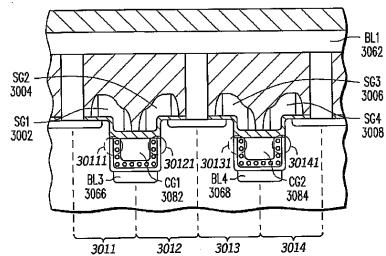

図 34 は図 35 に示す実施形態に関して記載した実施形態の回路図を含む。メモリセル 3011, 3012, 3013, 3014, 3021, 3022, 3023, 3024 は、図 34 に示すように NVM アレイ 18 内に配向されている。

## 【0070】

50

図 34 を参照すると、BL1 3062 は、メモリセル 3011, 3012, 3013, 3014 の S/D 領域に電気的に接続されている。BL2 3064 は、メモリセル 3021, 3022, 3023, 3024 の S/D 領域に電気的に接続されている。BL3 3066 は、メモリセル 3011, 3012, 3021, 3022 の他の S/D 領域に電気的に接続されている。BL4 3068 は、メモリセル 3013, 3014, 302

3, 3024 の他の S / D 領域に電気的に接続されている。CG1 3082 は、メモリセル 3011, 3012, 3021, 3022 の制御ゲート電極に電気的に接続されている。CG2 3084 は、メモリセル 3013, 3014, 3023, 3024 の制御ゲート電極に電気的に接続されている。SG1 3002 は、メモリセル 3011, 3021 の選択ゲート電極に電気的に接続されている。SG2 はメモリセル 3012, 3022 の選択ゲート電極に電気的に接続されている。SG3 はメモリセル 3013, 3023 の選択ゲート電極に電気的に接続されており、SG4 3008 はメモリセル 3014, 3024 の選択ゲート電極に電気的に接続されている。ピット・セル 3011 は電荷蓄積領域 30111 を含む。ピット・セル 3012 は電荷蓄積領域 30121 を含む。ピット・セル 3013 は電荷蓄積領域 30131 を含む。ピット・セル 3014 は電荷蓄積領域 30141 を含む。ピット・セル 3021 は電荷蓄積領域 30211 を含む。ピット・セル 3022 は電荷蓄積領域 30221 を含む。ピット・セル 3023 は電荷蓄積領域 30231 を含む。ピット・セル 3024 は電荷蓄積領域 30241 を含む。

10

#### 【0071】

図 34 に示すように、SG1 3002, SG2 3004, SG3 3006、および SG4 3008 の各々は、メモリセルの 1 列のみに電気的に接続されている。CG1 3082 および CG2 3084 の各々は、メモリセルの 2 列以上に電気的に接続されおり、さらに具体的には、メモリセルの 2 列に電気的に接続されている。

#### 【0072】

図 35 はメモリセル 3011, 3012, 3013, 3014 を含む行に相当する NV M アレイ 18 の一部分の物理的実施形態を示す。図 35 は図 17 と実質的に同じであるが、回路図に用いられている参照番号が図 35 では用いられている。図 36 は図 34 に示すメモリセルの動作電圧の一部を有する表を含む。例示的な 1 つの実施形態では、メモリセル 3012 の荷蓄積領域 30121 はプログラムされている。

20

#### 【0073】

図 34 に示す全メモリセルは、基板 12 とメモリセルのゲート電極との間に約 12 ~ 16 ボルトの範囲の電位差を生み出すことによって消去することができる。1 つの実施形態では、消去は基板 12 (すなわちその中のウェル領域) を約 +7 ボルトにし、ゲート線を -7 ボルトにしてピット線を電気的にフロートにすることによって行うことができる。SG1 および SG2 は -7 ボルトにされてもよいし、電気的にフローとさせてもよい。別の実施形態では、消去は基板 12 (すなわちその中のウェル領域) を約 -7 ボルトにし、ゲート線 +7 ボルトにしてピット線を電気的にフロートにすることによって行うことができる。なお、基板 12 およびゲート線に用いられる電圧は 0 ボルトに対して対称的になっている必要はない。例えば、+5 ボルトおよび -9 ボルトの組合せを用いることができる。本明細書を読めば、当業者であれば、それらの要求または要望を満たす消去用の電圧セットを決定することができる。

30

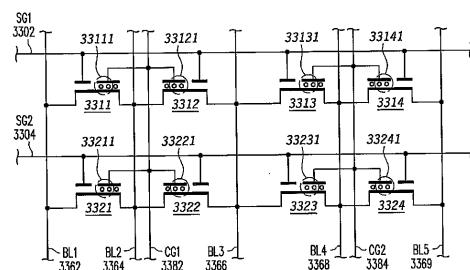

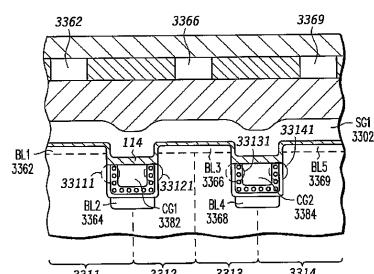

#### 【0074】

図 37 は図 38 に示す実施形態に関して記載した実施形態の回路図を含む。メモリセル 3311, 3312, 3313, 3314, 3321, 3322, 3323, 3324 は、図 37 に示すように NV M アレイ 18 内で配向されている。

40

#### 【0075】

図 37 を参照すると、BL1 3362 は、メモリセル 3311 の S / D 領域およびメモリセル 3321 の S / D 領域に電気的に接続されている。BL2 3364 は、メモリセル 3311, 3321 の他の S / D 領域ならびにメモリセル 3312, 3322 の S / D 領域に電気的に接続されている。BL3 3366 は、メモリセル 3312, 3322 の他の S / D 領域ならびにメモリセル 3313, 3323 の S / D 領域に電気的に接続されている。BL4 3368 は、メモリセル 3313, 3323 の他の S / D 領域ならびにメモリセル 3314, 3324 の S / D 領域に電気的に接続されている。BL5 3369 はメモリセル 3314, 3324 の他の S / D 領域に電気的に接続されている。CG1 3382 はメモリセル 3311, 3312, 3321, 3322 の制御ゲート電極

50

に電気的に接続されている。CG2 3384はメモリセル3313, 3314, 3323, 3324の制御ゲート電極に電気的に接続されている。SG1 3302は、メモリセル3311, 3312, 3313, 3314の選択ゲート電極に電気的に接続されている。SG2 3304はメモリセル3321, 3322, 3323, 3324の選択ゲート電極に電気的に接続されている。ピット・セル3311は電荷蓄積領域33111を含む。ピット・セル3312は電荷蓄積領域33121を含む。ピット・セル3313は電荷蓄積領域33131を含む。ピット・セル3314は電荷蓄積領域33141を含む。ピット・セル3321は電荷蓄積領域33211を含む。ピット・セル3322は電荷蓄積領域33221を含む。ピット・セル3323は電荷蓄積領域33231を含む。ピット・セル3324は電荷蓄積領域33241を含む。

10

#### 【0076】

図37に示すように、SG1 3302およびSG2 3304の各々はメモリセルの1つの行のみに電気的に接続されている。CG1 3382およびCG2 3384の各々は、メモリセルの2つ以上の列に電気的に接続されており、さらに具体的には、メモリセルの2つの列に電気的に接続されている。

#### 【0077】

図38はメモリセル3311, 3312, 3313, 3314を含む行に相当するNVMアレイ18の一部分の物理的実施形態を示す。図38は図20と実質的に同じであるが、回路図に用いられている参照番号が図38において用いられている。図39は図37に示すメモリセルの動作電圧の一部を有する表を含む。

20

#### 【0078】

図37に示す全メモリセルは、基板12(すなわちその中のウェル領域)とメモリセルのゲート電極との間に約12~16ボルトの範囲の電位差を生み出すことによって消去することができる。1つの実施形態では、消去は基板12(すなわちその中のウェル領域)を約+7ボルトにし、ゲート線を-7ボルトにして、ピット線を電気的にフロートさせることによって行うことができる。SG1およびSG2を-7ボルトにしてもよいし、電気的にフロートさせてもよい。別の実施形態では、消去は基板12(すなわちその中のウェル領域)を約-7ボルトにし、ゲート線を+7ボルトにして、ピット線を電気的にフロートさせることによって行うことができる。なお、基板12およびゲート線に用いられる電圧は、0ボルトに対して対称的になっている必要はない。例えば、+5ボルトおよび-9ボルトの組合せを用いることができる。本明細書を読めば、当業者であれば、それらの要求または要望を満たす消去のために使用されるべき電圧セットを決定することができる。

30

#### 【0079】

図21~図24に関して記載した実施形態は、図37に示したような回路図として表すことができ、図39に列挙した電圧を用いて動作させることができる。

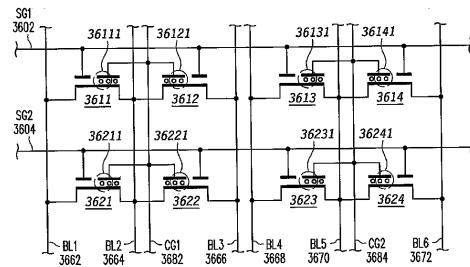

図40は図41に示した実施形態に関して記載した実施形態の回路図を含む。メモリセル3611, 3612, 3613, 3614, 3621, 3622, 3623, 3624は、図40に示すようにNVMアレイ18内に配向されている。

#### 【0080】

図40を参照すると、BL1 3662はメモリセル3611のS/D領域およびメモリセル3621のS/D領域に電気的に接続されている。BL2 3664はメモリセル3611, 3621の他のS/D領域ならびにメモリセル3612, 3622のS/D領域に電気的に接続されている。BL3 3666は、メモリセル3612, 3622の他のS/D領域に電気的に接続されている。BL4 3668はメモリセル3613, 3623のS/D領域に電気的に接続されている。BL5 3670は、メモリセル3613, 3623の他のS/D領域ならびにメモリセル3614, 3624のS/D領域に電気的に接続されている。BL6 3672は、メモリセル3614, 3624の他のS/D領域に電気的に接続されている。CG1 3682は、メモリセル3611, 3612, 3621, 3622の制御ゲート電極に電気的に接続されている。CG2 3684は、メモリセル3613, 3614, 3623, 3624の制御ゲート電極に電気的に接続さ

40

50

れている。SG1\_3602は、メモリセル3611, 3612, 3613, 3614の選択ゲート電極に電気的に接続されている。SG2\_3604は、メモリセル3621, 3622, 3623, 3624の選択ゲート電極に電気的に接続されている。ビット・セル3611は電荷蓄積領域36111を含む。ビット・セル3612は電荷蓄積領域36121を含む。ビット・セル3613は電荷蓄積領域36131を含む。ビット・セル3614は電荷蓄積領域36141を含む。ビット・セル3621は電荷蓄積領域36211を含む。ビット・セル3622は電荷蓄積領域36221を含む。ビット・セル3623は電荷蓄積領域36231を含む。ビット・セル3624は電荷蓄積領域36241を含む。

## 【0081】

10

図40に示すように、BL1\_3662、BL3\_3666、BL4\_3668、およびBL6\_3672の各々は、メモリセルの1つの列のみに電気的に接続されている。BL2\_3664およびBL5\_3670の各々はメモリセルの2つ以上の列に電気的に接続されており、さらに具体的には、メモリセルの2つの列に電気的に接続されている。

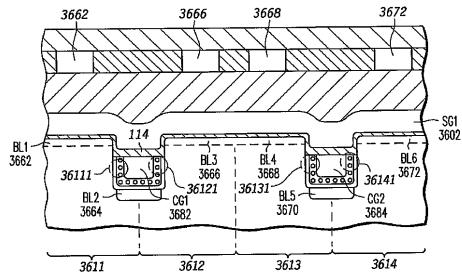

## 【0082】

図41はメモリセル3611, 3612, 3613, 3614を含む行に相当するNVMアレイ18の一部分の物理的実施形態を示す。図41は図28と実質的に同じであるが、回路図に用いられている参照番号が図41において用いられている。図42は図40に示すメモリセルの動作電圧の一部を有する表を含む。

## 【0083】

20

図40に示す全メモリセルは、基板12とメモリセルのゲート電極との間に約12~16ボルトの範囲の電位差を生み出すことによって消去することができる。1つの実施形態では、消去は基板12(すなわちその中のウェル領域)を約+7ボルトにし、ゲート線を-7ボルトにして、ビット線を電気的にフロートさせることによって行うことができる。SG1およびSG2を-7ボルトにしてもよいし、電気的にフロートさせてもよい。別の実施形態では、消去は基板12(すなわちその中のウェル領域)を約-7ボルトにし、ゲート線を+7ボルトにして、ビット線を電気的にフロートさせることによって行うことができる。なお、基板12およびゲート線に用いられる電圧は、0ボルトに対して対称的なになっている必要はない。例えば、+5ボルトおよび-9ボルトの組合せを用いることができる。本明細書を読めば、当業者であれば、それらの要求または要望を満たす消去のために使用されるべき電圧セットを決定することができる。

30

## 【0084】

NVMアレイ18、そのメモリセル、ビット線、およびゲート線に関して多くの詳細を記載してきた。本明細書を読めば、当業者であれば、行および列の配向を逆にすることが可能であることを理解し得る。メモリセルとそれらに関連するビット線、ゲート線、または1つまたは複数の行に沿ったそれらの組合せとの間の電気的接続を1つまたは複数の列に変えることができる。同様に、メモリセルとそれらに関連するビット線、ゲート線、または1つまたは複数の列に沿ったそれらの組合せとの間の電気的接続を1つまたは複数の行に変えることもできる。

## 【0085】

40

本明細書に記載の実施形態はNVMアレイまたはそれらの一部を形成する際に有用である。基板のトレンチ内に不連続な記憶素子を用いれば、より小型のメモリセルを形成することおよびメモリ密度を増大させることが可能となる。不連続な記憶素子によって、従来のフローティング・ゲート構造とは対照的に、より多くのビットをメモリセル内に蓄積することも可能となる。NVMアレイの製造は既存の材料および機器を用いて実施することができる。したがって、工程統合により、新しい機器のための新しい工程を開発する必要がなく、材料の不適合の問題に対処する必要もない。選択ゲート線の少なくとも一部がトレンチ内に凹状に形成されるように、このメモリセルを形成することができる。

## 【0086】

ソース・サイド注入を用いて、メモリセルをプログラムすることができる。中間ゲート

50

誘電体部分 114, 115 の厚さならびにプログラミング電圧を選択することによって、ビット線に電気的に接続された S / D 領域近傍に比して比較的大きな電界を、中間ゲート誘電体部分 114, 115 近傍で発生させることができるとなる。ソース・サイド注入によってプログラミング時間を従来のホット電子注入と同様にすることができ、ソース・サイド注入は従来のホット電子注入に比して高い電位効率を有する。

#### 【0087】

多数の異なる態様および実施形態が可能である。それらの態様および実施形態のいくつかを以下に記載する。本明細書を読めば、当業者であれば、それらの態様および実施形態は単なる例示であって、本発明の範囲を制限するものではないことを理解し得る。

#### 【0088】

第 1 の態様では、電子デバイスは壁および底部を含み、基板の主表面から延在する第 1 のトレンチを含んだ基板を備えることができる。この電子デバイスは不連続な記憶素子も含むことができ、不連続な記憶素子の第 1 の部分はその少なくとも一部が第 1 のトレンチ内に位置する。この電子デバイスは第 1 のゲート電極をさらに含むことができ、不連続な記憶素子の第 1 の部分の少なくとも一部は第 1 のゲート電極と第 1 のトレンチの壁との間に位置する。この電子デバイスは、第 1 のゲート電極と基板の主表面との上に位置する第 2 のゲート電極をさらに含むことができる。

#### 【0089】

第 1 の態様の 1 つの実施形態では、第 1 のゲート電極は基板の主表面より下方に位置する上面を有する。具体的な実施形態では、第 2 のゲート電極の少なくとも一部は第 1 のトレンチ内まで延びている。別の具体的な実施形態では、電子デバイスは第 3 のゲート電極をさらに含む。基板は第 1 のトレンチから離間された第 2 のトレンチをさらに含み、第 2 のトレンチは壁および底部を含み、かつ基板の主表面から延在し、不連続な記憶素子の第 2 の部分はその少なくとも一部が第 2 のトレンチ内に位置する。第 3 のゲート電極は基板の主表面より下方に位置する上面を有し、不連続な記憶素子の第 2 の部分の少なくとも一部分は第 3 のゲート電極と第 2 のトレンチの壁との間に位置する。

#### 【0090】

第 1 の態様のさらに具体的な実施形態では、電子デバイスは、第 1 のトレンチより下方の基板内に位置する第 1 のドープ領域と、第 2 のトレンチより下方の基板内に位置する第 2 のドープ領域とをさらに含む。さらに具体的な実施形態では、この電子デバイスは、第 1 のトレンチと第 2 のトレンチとの間の基板の主表面に沿って位置する第 3 のドープ領域をさらに含む。さらに具体的な実施形態では、第 3 のドープ領域は第 1 および第 2 のトレンチの壁まで延在する。さらに別の具体的な実施形態では、第 3 のドープ領域は第 1 および第 2 のトレンチの壁から離間されている。

#### 【0091】

第 1 の態様のさらに具体的な別の実施形態では、電子デバイスは、不連続な記憶素子の第 1 の部分内に第 1 の不連続な記憶素子を含む第 1 の電荷蓄積領域をさらに備え、第 1 の不連続な記憶素子は、第 1 のドープ領域よりも第 1 のゲート電極の上面近傍に位置する。この電子デバイスはさらに、不連続な記憶素子の第 2 の部分内に第 2 の不連続な記憶素子を含む第 2 の電荷蓄積領域も備え、第 2 の不連続な記憶素子は、第 2 のドープ領域よりも第 3 のゲート電極の上面近傍に位置する。第 2 の電荷蓄積領域は第 1 の電荷蓄積領域から離間されている。

#### 【0092】

第 1 の態様のさらに具体的な実施形態では、第 2 のゲート電極は、第 1 のゲート電極と、第 3 のゲート電極と、第 1 および第 2 のトレンチ間における基板の一部分とを覆うように位置する。さらに別の具体的な実施形態では、この電子デバイスは第 4 のゲート電極をさらに含む。第 2 のゲート電極は、第 1 のゲート電極と、第 1 および第 2 のトレンチ間ににおける基板の第 1 の部分とを覆うように位置し、第 4 のゲート電極は、第 3 のゲート電極と、第 1 および第 2 のトレンチ間ににおける基板の第 2 の部分とを覆うように位置する。

#### 【0093】

10

20

30

40

50

第1の態様の別の実施形態では、電子デバイスは、第1のトレンチの壁および底部に沿って位置する第1の誘電体層と、不連続な記憶素子の第1の部分と第1のゲート電極との間に位置する第2の誘電体層とをさらに含む。さらなる実施形態では、不連続な記憶素子はシリコンナノ結晶または金属ナノクラスタを含む。さらに別の実施形態では、電子デバイスはアレイをさらに含み、このアレイにおいては基板が第1のトレンチを含んだ複数のトレンチを含み、かつ、このアレイ内では不連続な記憶素子が基板のトレンチ内に位置する。具体的な実施形態では、電子デバイスはさらに、第1のトレンチ内に上面を含む第1のゲート電極上に位置する第1の誘電体層を含み、不連続な記憶素子の第1の部分は基板の主表面から離間されており、不連続な記憶素子はアレイ内のトレンチ間における基板の主表面上には実質的には存在しない。

10

#### 【0094】

第1の態様のさらに別の実施形態では、第1のゲート電極は断面図から、実質的な矩形を有する。さらに別の実施形態では、第1のゲート電極は断面図から、互いに対向する曲線状の外面を有した部分を含む。

#### 【0095】

第2の態様では、電子デバイスは、相互に離間された第1のトレンチおよび第2のトレンチを含んだ基板を備えることができ、第1および第2のトレンチの各々は壁および底部を含み、基板の主表面から延在する。この電子デバイスは不連続な記憶素子を含むことができ、不連続な記憶素子の第1の部分は第1のトレンチ内に位置し、不連続な記憶素子の第2の部分は少なくとも第2のトレンチ内に位置する。この電子デバイスは、第1のトレンチ内に位置し、かつ基板の主表面より下方に上面を有する第1のゲート電極を含むことができ、不連続な記憶素子の第1の部分の少なくとも一部は、第1のゲート電極と第1のトレンチの壁との間に位置する。この電子デバイスは、第2のトレンチ内に位置し、かつ基板の主表面より下方に位置する上面を有する第2のゲート電極をさらに含むことができ、不連続な記憶素子の第2の部分の少なくとも一部は第2のゲート電極と第2のトレンチの壁との間に位置し、第3のゲート電極は第1のゲート電極または第2のゲート電極の少なくとも1つを覆うように位置する。

20

#### 【0096】

第2の態様の1つの実施形態では、電子デバイスは、第1のトレンチの底部に沿って基板内に位置する第1のドープ領域と、第2のトレンチの底部に沿って基板内に位置する第2のドープ領域と、第1のトレンチと第2のトレンチとの間における基板の主表面に沿って位置する第3のドープ領域とをさらに含む。

30

#### 【0097】

第3の態様では、電子デバイスは、相互に離間された第1のトレンチおよび第2のトレンチを含む基板を備えることができ、第1および第2のトレンチの各々は、壁および底部を含み、かつ基板の主表面から延在する。この電子デバイスは、第1のトレンチの底部に沿って基板内に位置する第1のドープ領域と、第2のトレンチの底部に沿って基板内に位置する第2のドープ領域と、第1および第2のトレンチの壁および底部に沿って位置する第1の誘電体層とを含むことができる。この電子デバイスは不連続な記憶素子をさらに含むことができ、不連続な記憶素子の第1の部分は第1のトレンチ内に位置し、不連続な記憶素子の第2の部分は第2のトレンチ内に位置し、不連続な記憶素子の第1および第2の部分は基板の主表面から離間されており、不連続な記憶素子は、第1のトレンチと第2のトレンチとの間における基板の主表面上には実質的に存在しない。この電子デバイスは、第1および第2のトレンチ内の不連続な記憶素子に隣接する第2の誘電体層をさらに含むことができる。この電子デバイスは、第1のトレンチ内に位置するとともに基板の主表面より下方に位置する上面を有する第1のゲート電極をまたさらに含むことができ、不連続な記憶素子の第1の部分の少なくとも一部は、第1のゲート電極と第1のトレンチの壁との間に位置する。この電子デバイスは、第1のトレンチ内に位置するとともに基板の主表面より下方に位置する上面を有する第2のゲート電極を含むことができ、不連続な記憶素子の第1の部分の少なくとも一部は第1のゲート電極と第1のトレンチの壁との間に位置

40

50

する。この電子デバイスは、第1のトレンチ内の第1のゲート電極上に位置する第1の部分と第2のトレンチ内の第2のゲート電極上に位置する第2の部分とを含んだ第3の誘電体層をさらに含むことができる。この電子デバイスはさらに、第3の誘電体層上に位置する第3のゲート電極と、第1のゲート電極または第2のゲート電極の少なくとも1つとを含むことができ、第3のゲート電極はその少なくとも一部が第1のトレンチおよび第2のトレンチ内に位置する。

#### 【0098】

第4の態様では、電子デバイスを形成する工程は、壁および底部を含んで基板の主表面から延在する第1のトレンチを基板内に形成する工程と、基板の主表面上で第1のトレンチ内に不連続な記憶素子を形成する工程とを含むことができる。この工程は不連続な記憶素子を形成後に第1のトレンチ内に第1のゲート電極を形成する工程も含むことができ、不連続な記憶素子の第1の不連続な記憶素子は、第1のゲート電極と第1のトレンチの壁との間に位置する。この工程は基板の主表面上に位置する不連続な記憶素子を除去する工程をさらに含み、不連続な記憶素子の第1の部分は第1のトレンチ内に残る。この工程は不連続な記憶素子を形成後に第2のゲート電極を形成する工程をさらに含むことができ、第2のゲート電極は第1のゲート電極と基板の主表面との上に位置する。

10

#### 【0099】

第4の態様の1つの実施形態では、第1のゲート電極を形成する工程は、第1のゲート電極の上面が基板の主表面より下方に位置するように第1のゲート電極を形成する工程を含む。第2のゲート電極を形成する工程は、第2のゲート電極の一部分が第1のトレンチ内へと延びるように第2のゲート電極を形成する工程を含む。別の実施形態では、この工程は、第2のトレンチ内に第3のゲート電極を形成する工程をさらに含む。第1のトレンチを形成する工程は、第1のトレンチから離間された第2のトレンチを形成する工程をさらに含み、第2のトレンチは壁および底部を含み、基板の主表面から延在する。不連続な記憶素子を形成する工程は、不連続な記憶素子を第2のトレンチ内に形成する工程をさらに含む。第3のゲート電極を形成する工程は、不連続な記憶素子の第2の不連続な記憶素子が第3のゲート電極と第2のトレンチの壁との間に位置するように第3のゲート電極を形成する工程を含む。不連続な記憶素子を除去する工程は、基板の主表面上に位置する不連続な記憶素子を除去する工程を含み、不連続な記憶素子の第2の部分は第2のトレンチ内に残っている。

20

#### 【0100】

具体的な実施形態では、この工程は、第1および第2のトレンチの底部に沿って第1のドープ領域および第2のドープ領域をそれぞれ形成する工程をさらに含む。さらに具体的な実施形態では、この工程は、第1のトレンチと第2のトレンチとの間で基板の主表面に沿って位置する第3のドープ領域を形成する工程をさらに含む。さらに具体的な実施形態では、第3のドープ領域を形成する工程は、第2のゲート電極を形成する前に実行される。さらに具体的な別の実施形態では、第3のドープ領域を形成する工程は、第2のゲート電極を形成後に実行される。

30

#### 【0101】

別の具体的な実施形態では、不連続な記憶素子を除去する工程は、第1の不連続な記憶素子が第1の電荷蓄積領域の一部になり、第1のドープ領域近傍よりも第1のゲート電極の上面近傍に位置するように、かつ、第2の不連続な記憶素子が第2の電荷蓄積領域の一部になり、第2のドープ領域近傍よりも第3のゲート電極の上面近傍に位置するように、不連続な記憶素子を除去する工程を含む。第2の電荷蓄積領域は第1の電荷蓄積領域から離間されている。

40

#### 【0102】

さらに別の具体的な実施形態では、第2のゲート電極を形成する工程は、第2のゲート電極が第1および第3のゲート電極上に位置するように、かつ、上面図からは、第1および第2のトレンチの長さが第2のゲート電極の長さに対して実質的に直交するように、第2のゲート電極を形成する工程を含む。さらに別の具体的な実施形態では、この工程は第

50

4のゲート電極を形成する工程をさらに含む。第2のゲート電極を形成する工程は、第2のゲート電極が第1のゲート電極上に位置するように第2のゲート電極を形成する工程を含み、第4のゲート電極を形成する工程は、第4のゲート電極が第3のゲート電極上に位置するように第4のゲート電極を形成する工程を含む。上面図からは、第1のトレンチの長さは第2のゲート電極に長さに対して実質的に平行であり、第2のトレンチの長さは第4のゲート電極の長さに対して実質的に平行である。

#### 【0103】

第4の態様のさらなる実施形態では、工程は、第1のトレンチの壁および底部に沿って位置する第1の誘電体層を形成する工程と、不連続な記憶素子を形成後に第2の誘電体層を形成する工程と、第1のゲート電極を形成後に第3の誘電体層を形成する工程とをさらに含む。さらに具体的な実施形態では、第3の誘電体層を形成する工程および基板の主表面上に位置する不連続な記憶素子を除去する工程は、第1のゲート電極の露出部分と、第1のゲート電極と基板の主表面との間の高くなつた部分に位置する不連続な記憶素子の露出部分とを酸化させる工程を含む。10

#### 【0104】

第4の態様の別の実施形態では、第1のゲート電極を形成する工程は、不連続な記憶素子を形成後に導電層を形成する工程と、導電層を研磨して基板の主表面上に位置する導電層の部分を除去する工程と、第1のトレンチ内に導電層を凹状に形成して、第1のゲート電極の上面が主表面より下方に位置するように第1のゲート電極を形成する工程とを含む。さらに別の実施形態では、第1のゲート電極を形成する工程は、不連続な記憶素子を形成後に導電層を形成する工程と、導電層を異方性エッチングして第1のゲート電極を形成する工程とを含む。このゲート電極は、断面図からは側壁スペーサ形状を有する。またさらなる実施形態では、不連続な記憶素子を形成する工程は、シリコンナノ結晶を形成する工程または金属ナノクラスタを形成する工程を含む。20

#### 【0105】

第5の態様では、電子デバイスを形成する工程は、第1のトレンチおよび第2のトレンチを基板内に形成する工程を含むことができ、第1および第2のトレンチは相互に離間されており、第1および第2のトレンチの各々は壁および底部を含み、基板の主表面から延在する。この工程は基板の主表面上で、第1および第2のトレンチ内に不連続な記憶素子を形成する工程も含むことができる。この工程は、不連続な記憶素子の形成後に第1の導電層を形成する工程と、基板の主表面上に位置する第1の導電層の一部分を除去して、第1のトレンチ内に第1のゲート電極を形成し、第2のトレンチ内に第2のゲート電極を形成する工程とを含むこともできる。不連続な記憶素子の第1の部分は、第1のゲート電極と第1のトレンチの壁との間に位置し、不連続な記憶素子の第2の部分は、第2のゲート電極と第2のトレンチの壁との間に位置する。この工程は、基板の主表面上に位置する不連続な記憶素子を除去する工程と、基板の主表面上に位置する不連続な記憶素子を除去した後に第2の導電層を形成する工程と、第2の導電層をパターン化して、基板の主表面上に位置する第3のゲート電極と、第1のゲート電極または第2のゲート電極の少なくとも1つとを形成する工程とをさらにまた含むことができる。30

#### 【0106】

第5の態様の1つの実施形態では、工程は第1および第2のトレンチの底部に沿って第1のドープ領域と第2のドープ領域とをそれぞれ形成する工程をさらに含む。さらなる実施形態では、工程は第1のトレンチと第2のトレンチとの間の基板の主表面に沿って位置する第3のドープ領域を形成する工程をさらに含む。別の実施形態では、第1の導電層の一部分を除去する工程は、第1および第2のトレンチ内に第1の導電層を凹状に形成して、第1および第2のゲート電極の上面が主表面より下方に位置するように、第1および第2のゲート電極を形成する工程を含む。40

#### 【0107】

第6の態様では、電子デバイスを形成する工程は、第1のトレンチおよび第2のトレンチを基板内に形成する工程を含むことができ、第1および第2のトレンチは相互に離間さ50

れており、第1および第2のトレンチの各々は壁および底部を含み、基板の主表面から延在する。この工程は第1のドープ領域および第2のドープ領域を形成する工程も含むことができ、第1のドープ領域は第1のトレンチの底部に沿った基板内に位置し、第2のドープ領域は第2のトレンチの底部に沿った基板内に位置する。この工程は、第1および第2のトレンチの壁および底部に沿って位置する第1の誘電体層を形成する工程と、第1の誘電体層を形成後に不連続な記憶素子を形成する工程と、不連続な記憶素子を形成後に第2の誘電体層を形成する工程とをさらに含むことができる。この工程は、第2の誘電体層を形成後に第1の導電層を形成する工程と、第1の導電層をパターン化して、第1のトレンチ内に第1のゲート電極を形成し、第2のトレンチ内に第2のゲート電極を形成する工程とをさらに含むことができる。第1のゲート電極は基板の主表面より下方に位置する上面を有し、不連続な記憶素子の第1の部分は第1のゲート電極と第1のトレンチの壁との間に位置し、第2のゲート電極は基板の主表面より下方に位置する上面を有し、不連続な記憶素子の第2の部分は第2のゲート電極と第2のトレンチの壁との間に位置する。この工程は、不連続な記憶素子の第3の部分を除去して、不連続な記憶素子の第1の部分および不連続な記憶素子の第2の部分を含んだ不連続な記憶素子の残りの部分を残す工程をさらにまた含むことができる。不連続な記憶素子の第1の部分は第1のトレンチ内に位置し、不連続な記憶素子の第2の部分は第2のトレンチ内に位置し、不連続な記憶素子第1および第2の部分は基板の主表面から離間されており、不連続な記憶素子は第1トレンチと第2のトレンチとの間の基板の主表面の上には実質的に存在しない。この工程は第3の誘電体層を形成する工程も含むことができ、第3の誘電体層の第1の部分は第1のトレンチ内の第1のゲート電極上に位置し、第3の誘電体層の第2の部分は第2のトレンチ内の第2のゲート電極上に位置する。この工程は、第3の誘電体層形成後に第2の導電層を形成する工程と、第2の導電層をパターン化して第3の誘電体層上に位置する第3のゲート電極を形成する工程とを含むこともでき、第3のゲート電極は少なくとも一部が第1のトレンチおよび第2のトレンチ内に位置する。

10

20

#### 【0108】

第7の態様では、電子デバイスは第1の方向に実質的に沿って配向された第1のメモリセルのセットと、第1の方向に実質的に沿って配向された第2のメモリセルのセットとを含むことができる。この電子デバイスは第1のメモリセルのセットに電気的に接続された第1のゲート線と、第2のメモリセルのセットに電気的に接続された第2のゲート線とを含むこともでき、第1のゲート線に比して第2のゲート線は、第1の方向に沿って位置するより多くのメモリセルのセットに電気的に接続されている。

30

#### 【0109】

第7の態様の1つの実施形態では、第1のゲート線は選択ゲート線であり、第2のゲート線は制御ゲート線である。具体的な実施形態では、第1および第2のメモリセルのセット内のメモリセルの各々は、選択ゲート電極と制御ゲート電極とを含む不揮発性メモリセルからなる。第1のゲート線は第1のメモリセルのセットの選択ゲート電極に電気的に接続されており、第2のゲート線は第2のメモリセルのセットの制御ゲート電極に電気的に接続されている。さらに具体的な実施形態では、第1および第2のメモリセルのセットのチャネル領域と制御ゲート電極との間には不連続な記憶素子が存在し、第1および第2のメモリセルのセットのチャネル領域と選択ゲート電極との間には不連続な記憶素子が実質的に存在しない。

40

#### 【0110】

第7の態様の別の実施形態では、第1の方向は、ある行またはある列に関連する。別の実施形態では、第1のゲート線はメモリセルの1つの行または1つの列に電気的に接続されており、第2のゲート線はメモリセルの2つの行または2つの列に電気的に接続されている。さらなる実施形態では、電子デバイスは、第1の方向に実質的に沿って配向された第3のメモリセルのセットをさらに含み、第1、第2および第3のメモリセルのセットは、互いに異なる行または異なる列内に位置する。第3のメモリセルのセット内のメモリセルの各々は制御ゲート電極および選択ゲート電極を含み、第2のゲート線は第2および第50

3のメモリセルのセットの制御ゲート電極に電気的に接続されている。

**【0111】**

第7の態様の具体的な実施形態では、電子デバイスは、第1のビット線、第2のビット線および第3のビット線をさらに含み、第1のビット線は、第1のメモリセルのセットに電気的に接続され、第2のビット線は、第2および第3のメモリセルのセットに電気的に接続されている。第3のビット線は、第1のメモリセルのセットの一部であるが第2のメモリセルのセットの一部ではない第1のメモリセルと、第2のメモリセルのセットの一部であるが第1のメモリセルのセットの一部ではない第2のメモリセルとに電気的に接続されている。さらに具体的な実施形態では、第1および第2のビット線は、第1の方向に実質的に沿って配向されたメモリセルに電気的に接続され、第3のビット線は、第1の方向に対し実質的に直交する第2の方向に実質的に沿って配向されたメモリセルに電気的に接続されている。10

**【0112】**

第8の態様では、電子デバイスは、第1の方向に実質的に沿って配向された第1のメモリセルのセットと、第1の方向に対して実質的に直交する第2の方向に実質的に沿って配向された第2のメモリセルのセットとを含むことができる。この電子デバイスはさらに、第1のメモリセルのセットに電気的に接続された第1のゲート線も含むことができ、第1のメモリセルのセットは、第2のメモリセルのセットの一部ではない第1のメモリセルと、第2のメモリセルのセットの一部である第2のメモリセルとを含む。この電子デバイスはさらに、第2のメモリセルのセットに電気的に接続された第2のゲート線を含むことができ、第2のゲート線は、第1の方向に実質的に沿って配向されたメモリセルに電気的に接続されている第1のゲート線に比して、第2の方向に実質的に沿って配向された、より多くのメモリセルに電気的に接続されている。20

**【0113】**

第9の態様では、電子デバイスは、第1の方向に実質的に沿って配向された第1のメモリセルのセットと、第1の方向に実質的に沿って配向された第2のメモリセルのセットとを含むことができる。電子デバイスはさらに、第1のメモリセルのセットに電気的に接続された第1のビット線と、第2のメモリセルのセットに電気的に接続された第2のビット線であって、第1のビット線に比して、第1の方向に沿ってより多くのメモリセルのセットに電気的に接続された第2のビット線とを含むこともできる。30

**【0114】**

第9の態様の1つの実施形態では、第1および第2のメモリセルのセット内のメモリセル各々は、選択ゲート電極と制御ゲート電極とを含む不揮発性メモリセルからなる。具体的な実施形態では、第1および第2のメモリセルのセットのチャネル領域と制御ゲート電極との間には不連続な記憶素子が存在し、第1および第2のメモリセルのセットのチャネル領域と選択ゲート電極との間には不連続な記憶素子が実質的に存在しない。別の実施形態では、第1の方向はある行またはある列に関連している。40

**【0115】**

第9の態様のさらなる実施形態では、電子デバイスは、第3のメモリセルのセットをさらに含み、第1、第2および第3のメモリセルのセットは互いに異なる行または異なる列内に位置し、第3のメモリセルのセットは第1の方向に実質的に配向され、第2のビット線は第3のメモリセルのセットに電気的に接続されている。さらに別の実施形態では、第1のビット線はメモリセルの1つの行または1つの列に電気的に接続され、第2のビット線はメモリセルの2つの行または2つの列に電気的に接続されている。50

**【0116】**

第9の態様のさらに別の実施形態では、電子デバイスは、第1のゲート線、第2のゲート線、および第3のゲート線をさらに含む。第1のゲート線は第1のメモリセルのセットに電気的に接続されており、第2のゲート線は第2のメモリセルのセットに電気的に接続されている。第3のゲート線は、第1のメモリセルのセットの一部であるが第2のメモリセルのセットの一部ではない第1のメモリセルと、第2のメモリセルのセットの一部であ

るが第1のメモリセルのセットの一部ではない第2のメモリセルとに電気的に接続されている。さらに具体的な実施形態では、第1および第2のゲート線の各々は制御ゲート線であり、第3のゲート線は選択ゲート線である。

#### 【0117】

別のさらに具体的な実施形態では、第1および第2のゲート線は第1の方向に実質的に沿って配向されたメモリセルに電気的に接続され、第3のゲート線は第1の方向に対して実質的に直交する第2の方向に実質的に沿って配向されたメモリセルに電気的に接続されている。さらに具体的な実施形態では、第2および第3のメモリセルのセットのチャネル領域と制御ゲート電極との間には不連続な記憶素子が存在し、第1のメモリセルのセットのチャネル領域と選択ゲート電極との間には不連続な記憶素子が実質的に存在しない。

10

#### 【0118】

上記の概要または実施例に記載した全部の要素が必要というわけではなく、特定の要素の一部は必要でなくともよいし、それらの要素に加えて1つまたは複数のさらなる要素を加えてよいことが理解し得る。またさらに、列挙された動作の順序は、必ずしもそれらが行われる順序ではない。本明細書を読めば、当業者であれば、それらの具体的な要求または要望にどの動作を用いることができるかを決定することができる。

#### 【0119】

1つまたは複数の利益、1つまたは複数の他の利点、1つまたは複数の問題に対する1つまたは複数の解決策、またはこれらの組合せを1つまたは複数の具体的な実施形態に関して上述したが、1つ以上の利益、1つ以上の利点、1つ以上の問題に対する1つ以上の解決策、または利益、利点、解決策を生じさせ得るか、明らかにさせ得る1つ以上の要素は、特許請求の範囲の一部または全部の重要な、必要な、または本質的な特徴ないし要素であるとみなされるべきではない。

20

#### 【0120】

上記の説明は例示であると考えられるべきであり、限定的なものと考えられるべきではなく、添付の特許請求の範囲は本発明の範囲に入る変形例、強化例、および他の実施形態のすべてを包含するものとする。したがって、法的に許容される最大の範囲まで、添付の特許請求の範囲およびそれらの同等物の容認できる最も広い解釈によって形成されるべきであり、上記の詳細な説明によって制限または限定されないものとする。

#### 【図面の簡単な説明】

30

#### 【0121】

【図1】保護層形成後の加工物の一部を示す断面図。

【図2】トレンチ形成後の図1の加工物を示す断面図。

【図3】トレンチ内に絶縁層を形成した後の、図2の加工物を示す断面図。

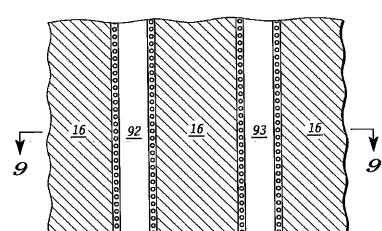

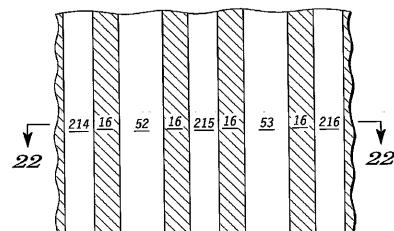

【図4】ドープ領域をトレンチの底部に形成後の図3の加工物を示す上面図。

【図5】ドープ領域をトレンチの底部に形成後の図3の加工物を示す断面図。

【図6】不連続な記憶素子を含んだ電荷蓄積層体を形成後の図5の加工物を示す断面図。

。

【図7】基板上に導電層を形成後の図6の加工物を示す断面図。

【図8】ゲート電極を形成後の図7の加工物を示す上面図。

40

【図9】ゲート電極を形成後の図7の加工物を示す断面図。

【図10】アレイ内の保護層の残りの部分を除去後の図9の加工物および電荷蓄積層体の露出部分を示す断面図。

【図11】絶縁層形成後の図10の加工物を示す断面図。

【図12】導電層形成後の図11の加工物を示す断面図。

【図13】導電線形成後の図12の加工物を示す上面図。

【図14】別の実施形態の導電線の形成後の図11の加工物を示す断面図。

【図15】パターン化されたレジスト層を形成後の図14の加工物を示す上面図。

【図16】電子デバイスの製造終了後の図15の加工物を示す上面図。

【図17】電子デバイスの製造終了後の図15の加工物を示す断面図。

50

- 【図18】基板内にドープ領域を形成後の図13の加工物を示す上面図。

- 【図19】電子デバイスの製造が実質的に終了した後の図18の加工物を示す上面図。

- 【図20】電子デバイスの製造が実質的に終了した後の図18の加工物を示す断面図。

- 【図21】基板内にドープ領域を形成後の図13の加工物を示す上面図。

- 【図22】基板内にドープ領域を形成後の図13の加工物を示す断面図。

- 【図23】電子デバイスの製造が実質的に終了した後の図21および22の加工物を示す上面図。

- 【図24】電子デバイスの製造が実質的に終了した後の図21および22の加工物を示す断面図。 10

- 【図25】トレンチが相互にさらに広く離間された、図12の加工物を示す断面図。

- 【図26】上側の導電線を形成後の図25の加工物を示す上面図。

- 【図27】電子デバイスの製造が実質的に終了した後の図26の加工物を示す上面図。

- 【図28】電子デバイスの製造が実質的に終了した後の図26の加工物を示す断面図。

- 【図29】導電層形成後の図6の加工物を示す断面図。

- 【図30】ゲート電極形成後の図29の加工物を示す断面図

- 【図31】NVMアレイ内の行に沿ったメモリセルを示す回路図。

- 【図32】NVMアレイ内の行に沿ったメモリセルの回路図の例示的な物理的実施形態を示す断面図。 20

- 【図33】NVMアレイ内の行に沿ったメモリセルの動作電圧を示す表。

- 【図34】NVMアレイ内の行に沿ったメモリセルを示す回路図。

- 【図35】NVMアレイ内の行に沿ったメモリセルの回路図の例示的な物理的実施形態を示す断面図。

- 【図36】NVMアレイ内の行に沿ったメモリセルの動作電圧を示す表。

- 【図37】NVMアレイ内の行に沿ったメモリセルを示す回路図。

- 【図38】NVMアレイ内の行に沿ったメモリセルの回路図の例示的な物理的実施形態を示す断面図。 30

- 【図39】NVMアレイ内の行に沿ったメモリセルの動作電圧を示す表。

- 【図40】NVMアレイ内の行に沿ったメモリセルを示す回路図。

- 【図41】NVMアレイ内の行に沿ったメモリセルの回路図の例示的な物理的実施形態を示す断面図。

- 【図42】NVMアレイ内の行に沿ったメモリセルの動作電圧を示す表。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図7】

FIG. 7

【図10】

FIG. 10

【図8】

FIG. 8

【図11】

FIG. 11

【図9】

FIG. 9

【図12】

FIG. 12

【図 13】

FIG. 13

【図 14】

FIG. 14

【図 15】

FIG. 15

【図 18】

FIG. 18

【図 19】

FIG. 19

【図 16】

FIG. 16

【図 17】

FIG. 17

【図 20】

FIG. 20

【図 21】

FIG. 21

【図 22】

FIG. 22

【図23】

FIG. 23

【図24】

FIG. 24

【図25】

FIG. 25

【図28】

FIG. 28

【図29】

*FIG. 29*

【四三〇】

FIG. 30

【 図 2 6 】

*FIG. 26*

〔 四 27 〕

FIG. 27

( 31 )

FIG. 31

〔図32〕

2/11

〔 四 3 3 〕

|            | SG1<br>2702 | SG2<br>2704 | GL1<br>2742 | GL2<br>2744 | GL3<br>2746 | BL1<br>2762 | BL2<br>2764 | BL3<br>2766 |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| PGM 27110  | 3           | 0           | 8           | 6           | 0           | 5           | 0           | 0           |

| 読み出し 27110 | 3           | 0           | 3.5         | 6           | 0           | 0           | 2           | 0           |

| PGM 27111  | 3           | 0           | 6           | 8           | 0           | 0           | 5           | 0           |

| 読み出し 27111 | 3           | 0           | 6           | 3.5         | 0           | 2           | 0           | 0           |

| PGM 27120  | 3           | 0           | 0           | 8           | 6           | 0           | 5           | 0           |

| 読み出し 27120 | 3           | 0           | 0           | 3.5         | 6           | 0           | 0           | 2           |

| PGM 27121  | 3           | 0           | 0           | 6           | 8           | 0           | 0           | 5           |

| 読み出し 27121 | 3           | 0           | 0           | 6           | 3.5         | 0           | 2           | 0           |

【図34】

FIG. 34

【図36】

|            | SG1<br>3002 | SG2<br>3004 | SG3<br>3066 | SG4<br>3008 | CG1<br>3082 | CG2<br>3084 | BL1<br>3062 | BL2<br>3064 | BL3<br>3066 | BL4<br>3068 |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| PGM 30111  | 3           | 0           | 0           | 0           | 8           | 0           | 0           | F           | 5           | 0           |

| 読み出し 30111 | 3           | 0           | 0           | 0           | 3.5         | 0           | 2           | F           | 0           | 0           |

| PGM 30121  | 0           | 3           | 0           | 0           | 8           | 0           | 0           | F           | 5           | 0           |

| 読み出し 30121 | 0           | 3           | 0           | 0           | 3.5         | 0           | 2           | F           | 0           | 0           |

| PGM 30131  | 0           | 0           | 3           | 0           | 0           | 8           | F           | 0           | 0           | 5           |

| 読み出し 30131 | 0           | 0           | 3           | 0           | 0           | 3.5         | F           | 2           | 0           | 0           |

| PGM 30141  | 0           | 0           | 0           | 3           | 0           | 8           | F           | 0           | 0           | 5           |

| 読み出し 30141 | 0           | 0           | 0           | 3           | 0           | 3.5         | F           | 2           | 0           | 0           |

【図35】

FIG. 35

【図37】

FIG. 37

【図39】

|            | SG1<br>3302 | SG2<br>3304 | CG1<br>3382 | CG2<br>3384 | BL1<br>3382 | BL2<br>3384 | BL3<br>3366 | BL4<br>3368 | BL5<br>3369 |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| PGM 33111  | 3           | 0           | 8           | 0           | 0           | 5           | F           | F           | F           |

| 読み出し 33111 | 3           | 0           | 3.5         | 0           | 2           | 0           | F           | F           | F           |

| PGM 33121  | 3           | 0           | 8           | 0           | F           | 5           | 0           | F           | F           |

| 読み出し 33121 | 3           | 0           | 3.5         | 0           | F           | 0           | 2           | F           | F           |

| PGM 33131  | 3           | 0           | 0           | 8           | F           | F           | 0           | 5           | F           |

| 読み出し 33131 | 3           | 0           | 0           | 3.5         | F           | F           | 2           | 0           | F           |

| PGM 33141  | 3           | 0           | 0           | 8           | F           | F           | F           | 5           | 0           |

| 読み出し 33141 | 3           | 0           | 0           | 3.5         | F           | F           | F           | 0           | 2           |

【図38】

FIG. 38

【図40】

FIG. 40

【図42】

【図41】

FIG. 41

|            | SG1<br>3602 | SG2<br>3604 | CG1<br>3682 | CG2<br>3684 | BL1<br>3662 | BL2<br>3664 | BL3<br>3666 | BL4<br>3668 | BL5<br>3670 | BL6<br>3672 |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| PGM 36111  | 3           | 0           | 8           | 0           | F           | 5           | 0           | F           | F           | F           |

| 読み出し 36111 | 3           | 0           | 3.5         | 0           | F           | 0           | 2           | F           | F           | F           |

| PGM 36121  | 3           | 0           | 8           | 0           | F           | 5           | F           | 0           | F           | F           |

| 読み出し 36121 | 3           | 0           | 3.5         | 0           | F           | 0           | F           | 2           | F           | F           |

| PGM 36131  | 3           | 0           | 0           | 8           | F           | F           | 0           | F           | 5           | F           |

| 読み出し 36131 | 3           | 0           | 0           | 3.5         | F           | F           | 2           | F           | 0           | F           |

| PGM 36141  | 3           | 0           | 0           | 8           | F           | F           | F           | 0           | 5           | F           |

| 読み出し 36141 | 3           | 0           | 0           | 3.5         | F           | F           | F           | 2           | 0           | F           |

---

フロントページの続き

(72)発明者 インガーソル、ポール エイ .

アメリカ合衆国 78739 テキサス州 オースティン オールド ハーバー レーン 630

4

(72)発明者 スウィフト、クレイグ テイ .

アメリカ合衆国 78749 テキサス州 オースティン ソーミル ドライブ 3613

審査官 堀江 義隆

(56)参考文献 特開2003-100914(JP,A)

特開2004-253702(JP,A)

特開平09-129759(JP,A)

特開2002-026149(JP,A)

特表2004-507091(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 21/8247

H01L 27/115

H01L 29/788

H01L 29/792