(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-229120

(P2011-229120A)

(43) 公開日 平成23年11月10日(2011.11.10)

(51) Int.Cl.

**H04N 5/378** (2011.01)

**H04N 5/363** (2011.01)

**H04N 5/374** (2011.01)

**H01L 27/146** (2006.01)

F 1

HO 4 N 5/335 780

HO 4 N 5/335 630

HO 4 N 5/335 740

HO 1 L 27/14 27/14

テーマコード(参考)

4 M 1 1 8

5 C O 2 4

A

審査請求 未請求 請求項の数 20 O L (全 49 頁)

(21) 出願番号 特願2011-15994 (P2011-15994)

(22) 出願日 平成23年1月28日 (2011.1.28)

(31) 優先権主張番号 特願2010-79017 (P2010-79017)

(32) 優先日 平成22年3月30日 (2010.3.30)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100120640

弁理士 森 幸一

(74) 代理人 100118290

弁理士 吉井 正明

(74) 代理人 100094363

弁理士 山本 孝久

(72) 発明者 権原 雅樹

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 大池 祐輔

東京都港区港南1丁目7番1号 ソニー株

式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像装置、固体撮像装置の信号処理方法、及び、電子機器

## (57) 【要約】

【課題】面内の大きな特性の揺らぎ(面内分布)の差異や、寄生容量の大きさに依存したオフセット成分を効果的に除去することを可能にする。

【解決手段】電荷検出部(FD部)に保持、もしくは、蓄積されている信号電荷を信号レベル $V_{sig}$ として読み出し、次いで、FD部42を所定電位にリセットして当該所定電位をリセットレベル $V_{rst}$ として読み出す。DS駆動において、単位画素から先に読み出される信号レベル $V_{sig}$ をAD変換回路23の変換可能な入力電圧範囲の基準電圧として用いる。そして、信号レベル $V_{sig}$ 及びリセットレベル $V_{rst}$ が入力電圧範囲内に入るように基準電圧を調整した状態でAD変換を行うようにする。

【選択図】図1 1

**【特許請求の範囲】****【請求項 1】**

光電変換部、及び、当該光電変換部で光電変換された電荷を検出する電荷検出部を有する単位画素が配置されてなる画素アレイ部と、

前記単位画素の信号を第1の信号及び第2の信号として2回に分けて読み出す駆動を行う駆動部と、

前記単位画素から先に読み出される前記第1の信号を、処理可能な入力電圧範囲の基準電圧として用い、前記第1の信号及び前記第2の信号が前記入力電圧範囲内に入るよう前記基準電圧を調整した状態で前記第1の信号及び前記第2の信号に対して信号処理を施す信号処理部と

を備えた固体撮像装置。

**【請求項 2】**

前記第1の信号は、前記電荷検出部に蓄積あるいは保持された信号電荷に基づく信号であり、

前記第2の信号は、前記電荷検出部をリセットしたときのリセット電位に基づく信号である

請求項1に記載の固体撮像装置。

**【請求項 3】**

前記駆動部は、

前記基準電圧を設定するために先ず前記第1の信号を読み出し、

しかる後、前記電荷検出部をリセットして前記第2の信号を読み出す

請求項2に記載の固体撮像装置。

**【請求項 4】**

前記信号処理部は、

前記第1の信号と前記第2の信号との差分をとる

請求項2に記載の固体撮像装置。

**【請求項 5】**

前記第1の信号は、前記電荷検出部をリセットしたときのリセット電位に基づく信号であり、

前記第2の信号は、前記電荷検出部に蓄積あるいは保持された信号電荷に基づく信号である

請求項1に記載の固体撮像装置。

**【請求項 6】**

前記駆動部は、

前記基準電圧を設定するために先ず前記第1の信号を読み出し、

しかる後、前記第1の信号、前記第2の信号の順に読み出す

請求項5に記載の固体撮像装置。

**【請求項 7】**

前記信号処理部は、

前記第1の信号と前記第2の信号との差分をとる

請求項6に記載の固体撮像装置。

**【請求項 8】**

前記駆動部は、

前記基準電圧を設定するために先ず前記電荷検出部に蓄積あるいは保持された信号電荷に基づく信号を読み出し、しかる後、前記電荷検出部をリセットしてそのリセット電位に基づく信号を読み出す第1の駆動と、

前記基準電圧を設定するために先ず前記電荷検出部をリセットしたときのリセット電位に基づく信号を読み出し、しかる後、当該リセット電位に基づく信号、前記電荷検出部に蓄積あるいは保持された信号電荷に基づく信号の順に読み出す第2の駆動とを選択的に実行可能である

10

20

30

40

50

請求項 1 に記載の固体撮像装置。

**【請求項 9】**

前記信号処理部は、

前記電荷検出部に蓄積あるいは保持された信号電荷に基づく信号と、前記電荷検出部のリセット電位に基づく信号との差分をとる

請求項 8 に記載の固体撮像装置。

**【請求項 10】**

前記信号処理部は、前記単位画素で得られるアナログ信号をデジタル信号に変換するアナログ - デジタル変換回路を有し、

前記基準電圧は、前記アナログ - デジタル変換回路の変換可能な入力電圧範囲の基準となる電圧である

請求項 8 に記載の固体撮像装置。

**【請求項 11】**

前記アナログ - デジタル変換回路は、

前記単位画素で得られるアナログ信号と傾斜状波形の参照信号とを比較する比較器と、前記第 1 の駆動の際に、前記比較器の 2 つの入力端に所定の初期電圧を与えることによって前記第 1 の信号及び前記第 2 の信号が前記入力電圧範囲内に入るように前記基準電圧の初期設定を行う設定回路とを有する

請求項 10 に記載の固体撮像装置。

**【請求項 12】**

前記アナログ - デジタル変換回路において、前記第 1 の駆動の際に、前記第 2 の駆動時の初期設定と同じ初期設定を行うことによって前記比較器の後段の回路部の動作点を前記第 1 の駆動時と前記第 2 の駆動時とで同じにし、かかる後、前記設定回路による初期設定を行う

請求項 11 に記載の固体撮像装置。

**【請求項 13】**

前記後段の回路部は、前記比較器の出力電圧に応じた電流値に基づく電圧値を記憶する

請求項 12 に記載の固体撮像装置。

**【請求項 14】**

前記傾斜状波形の参照信号を生成する参照信号生成部は、前記設定回路によって設定された前記基準電圧に対応して前記傾斜状波形の初期値を設定する

請求項 11 に記載の固体撮像装置。

**【請求項 15】**

前記設定回路は、前記比較器の 2 つの入力端に対して前記所定の初期電圧を選択的に与える 2 つのトランジスタによって構成される

請求項 11 に記載の固体撮像装置。

**【請求項 16】**

前記信号処理部は、前記単位画素からアナログ信号で出力される前記信号レベル及び前記リセットレベルを増幅するアンプ回路であり、

前記基準電圧は、前記アンプ回路の増幅可能な入力電圧範囲の基準となる電圧である

請求項 8 に記載の固体撮像装置。

**【請求項 17】**

前記信号処理部は、

一方の入力端に初期電圧が与えられる反転増幅器と、

前記反転増幅器の他方の入力端に接続される入力容量と、

前記反転増幅器の他方の入力端と出力端との間に接続される帰還容量と、

前記反転増幅器の出力電圧の初期値を所定の初期電圧にすることによって前記第 1 の信号及び前記第 2 の信号が前記入力電圧範囲内に入るように前記基準電圧を設定する設定回路とを有する

請求項 16 に記載の固体撮像装置。

10

20

30

40

50

**【請求項 1 8】**

前記設定回路は、前記反転増幅器の帰還ループを開放状態にするトランジスタと、当該帰還ループが開放状態にあるときに、前記帰還容量に対して前記所定の初期電圧を与えるトランジスタとによって構成される

請求項 1 7 に記載の固体撮像装置。

**【請求項 1 9】**

光電変換部、及び、当該光電変換部で光電変換された電荷を検出する電荷検出部を有する単位画素が配置されてなり、

前記単位画素の信号を第 1 の信号及び第 2 の信号として 2 回に分けて読み出す固体撮像装置の信号処理に当たって、

前記単位画素から先に読み出される前記第 1 の信号を、前記第 1 の信号及び前記第 2 の信号を処理する信号処理部の処理可能な入力電圧範囲の基準電圧として用い、

前記第 1 の信号及び前記第 2 の信号が前記入力電圧範囲内に入るよう前記基準電圧を調整した状態で前記第 1 の信号及び前記第 2 の信号に対して前記信号処理部によって信号処理を施す

固体撮像装置の信号処理方法。

**【請求項 2 0】**

光電変換部、及び、当該光電変換部で光電変換された電荷を検出する電荷検出部を有する単位画素が配置されてなる画素アレイ部と、

前記単位画素の信号を第 1 の信号及び第 2 の信号として 2 回に分けて読み出す駆動を行う駆動部と、

前記単位画素から先に読み出される前記第 1 の信号を、処理可能な入力電圧範囲の基準電圧として用い、前記第 1 の信号及び前記第 2 の信号が前記入力電圧範囲内に入るよう前記基準電圧を調整した状態で前記第 1 の信号及び前記第 2 の信号に対して信号処理を施す信号処理部と

を備えた固体撮像装置を有する電子機器。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本開示は、固体撮像装置、固体撮像装置の信号処理方法、及び、電子機器に関する。

30

**【背景技術】****【0 0 0 2】**

光電変換部、電荷検出部、及び、光電変換部で蓄積された電荷を電荷検出部へ転送する転送ゲート部を含む単位画素によって構成される固体撮像装置では、一般的に、リセット動作時のノイズを除去するために、相關二重サンプリングによるノイズ除去処理が行われる。以下では、電荷検出部を F D ( フローティング・ディフュージョン ) 部と記述する。ノイズ除去処理の方式としては、デジタル信号処理にて実行する方式と、アナログ信号処理にて実行する方式がある。

**【0 0 0 3】**

ノイズ除去処理を例えればデジタル信号処理にて実行する固体撮像装置として、単位画素の行列状の配列に対して列毎に A D C ( Analog-Digital Converter ; アナログ - デジタル変換回路 ) を配置してなる列並列 A D C 搭載の固体撮像装置が知られている（例えば、特許文献 1 参照）。

40

**【0 0 0 4】**

列並列 A D C 搭載の固体撮像装置では、最初に読み出されるリセットレベル  $V_{rst}$  を A D 変換回路の基準電圧  $V_{zr}$  として設定し、当該基準電圧  $V_{zr}$  を用いてリセットレベル  $V_{rs}$  及び信号レベル  $V_{sig}$  を A D 変換するようにしている。すなわち、基準電圧  $V_{zr}$  をリセットレベル  $V_{rst}$  と等しくすることで、リセットレベル  $V_{rst}$  がノイズによって変動しても、信号電荷による画素の出力振幅  $|V_{sig} - V_{rst}|$  を安定して A D 変換回路の入力電圧範囲に収めることができる。

50

## 【0005】

A D変換回路の基準電圧 $V_{zr}$ は、一般的に、A D変換回路の入力電圧範囲に対して十分小さい範囲でしか調整できない。従って、A D変換回路の基準電圧 $V_{zr}$ としては、リセットレベル $V_{rst}$ のように、ばらつきの幅が安定して限られている信号が好ましい。逆に、信号レベル $V_{sig}$ のように入射光量によって電圧が大きく振幅する信号は、A D変換回路の基準電圧 $V_{zr}$ としては適さない。

## 【0006】

上述した列並列A D C搭載の固体撮像装置のように、従来の固体撮像装置におけるノイズ除去処理では、最初にリセットレベル $V_{rst}$ を読み出し、当該リセットレベル $V_{rst}$ の直後に信号レベル $V_{sig}$ を読み出すことが前提となっている。一方で、リセットレベル $V_{rst}$ を信号レベル $V_{sig}$ の直前に読み出すことができない固体撮像装置では、ある単位画素の信号レベル $V_{sig}$ をA D変換する前に同一画素から基準電圧 $V_{zr}$ を取得することができない。10

## 【0007】

リセットレベル $V_{rst}$ を信号レベル $V_{sig}$ の直前に読み出すことができない固体撮像装置としては、次のようなものを例に挙げることができる。例えば、全画素一括の露光を実現すべく、光電変換部で発生した電荷を全画素同時にF D部へ転送し、当該F D部で信号電荷が保持された状態から、順次読み出し動作を実行するグローバル露光機能を持つC M O Sイメージセンサが挙げられる（例えば、特許文献2参照）。

## 【0008】

他にも、リセットレベル $V_{rst}$ を信号レベル $V_{sig}$ の直前に読み出すことができない固体撮像装置として、光電変換部から転送される光電荷を電荷検出部とは別に保持するメモリ部を有するC M O Sイメージセンサ（例えば、特許文献3参照）が挙げられる。更に、P N接合で発生した光電荷を直接増幅トランジスタによって読み出すC M O Sイメージセンサ（例えば、非特許文献1参照）や、有機光電変換膜を用いたイメージセンサ（例えば、特許文献4参照）などが挙げられる。20

## 【0009】

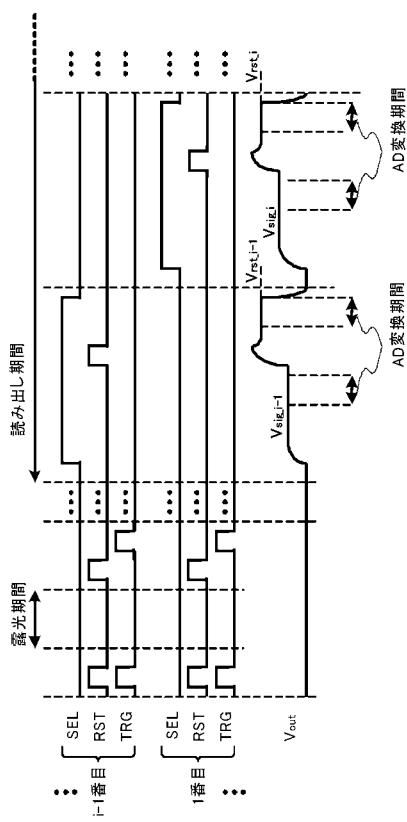

固体撮像装置においては、全画素一括での転送、あるいは露光開始時などにF D部が一旦リセットされており、信号を読み出すタイミングでは既にF D部に信号電荷が蓄積、あるいは保持されていることになる。このため、増幅トランジスタの閾値ばらつき等の固定パターンノイズを除去するには、図44に示すように、信号レベル $V_{sig}$ を読み出した後、F D部を所定電位に設定して、当該所定電位をリセットレベル $V_{rst}$ として読み出す必要がある。30

## 【0010】

しかし、全画素一括露光のために信号電荷がF D部へ保持された状態で信号読み出しが実行される固体撮像装置や、F D部へ直接信号電荷が蓄積されて信号読み出しが実行される固体撮像装置では、信号レベル $V_{sig}$ を読み出す直前にF D部を所定電位に設定することができない。この場合、信号レベルをA D変換する際の基準電圧を取得することができないため、外部印加や抵抗アレイ等で所定電圧を発生させ、当該所定電圧をA D変換回路に基準電圧として供給するようにしている（例えば、特許文献5参照）。40

## 【先行技術文献】

## 【特許文献】

## 【0011】

【特許文献1】特開2006-340044号公報

【特許文献2】特開2001-238132号公報

【特許文献3】特開2009-020176号公報

【特許文献4】特開2008-228265号公報

【特許文献5】特開2006-020176号公報

## 【非特許文献】

## 【0012】

10

20

30

40

50

【非特許文献 1】“128X128 CMOS PHOTODIODE-TYPE ACTIVE PIXEL SENSOR WITH ON-CHIP TIMING, CONTROL AND SIGNAL CHAIN ELECTRONICS” SPIE, vol. 2415, Charge-Coupled Devices and Solid State Optical Sensors V, paper no. 34 (1995)

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかし、リセットレベルには増幅トランジスタの閾値ばらつき等により、単位画素間でのばらつきだけでなく、単位画素の2次元配列における面内での空間的に大きな特性の揺らぎ（面内分布）による差異や、動作時の温度変化による経時変化が存在する。従って、リセットレベルに対して十分なマージンを確保する必要があるため、実際に取得すべき信号電荷の画素出力振幅に対して、これらの変動を加味した電圧範囲に、A/D変換回路の変換可能な入力電圧範囲を拡大する必要がある。

10

【0014】

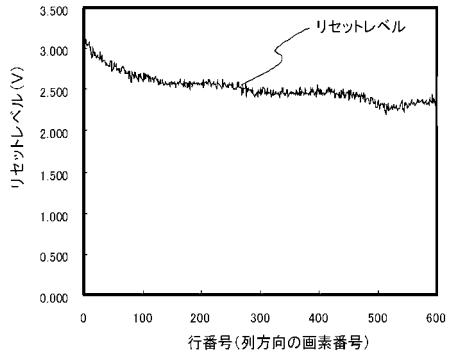

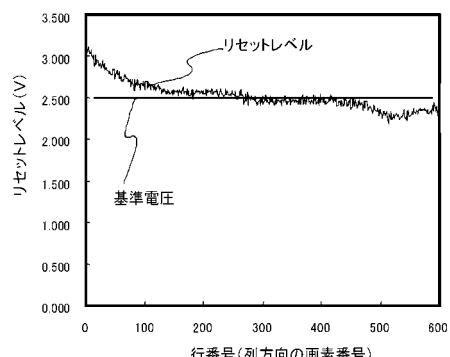

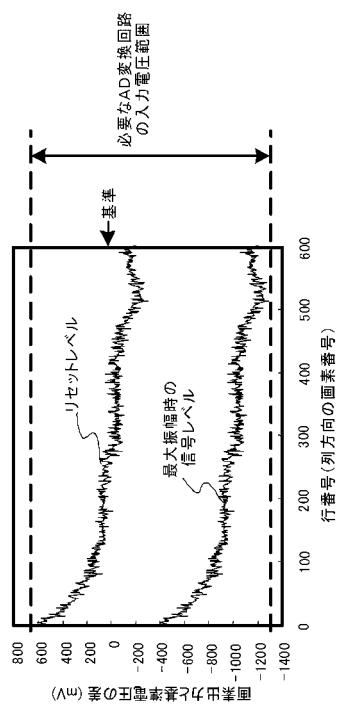

図45に、リセットレベルの縦方向（列方向、即ち、画素列の画素の配列方向）の面内分布の一例を示す。リセットレベルの隣接画素間における差異の他に、面内で大きな特性の揺らぎ（面内分布）が存在する。図46に示すように、一定電圧を基準電圧として印加する場合、画素によって大きな誤差を発生するため、A/D変換回路の入力電圧範囲を拡大する必要がある。

20

【0015】

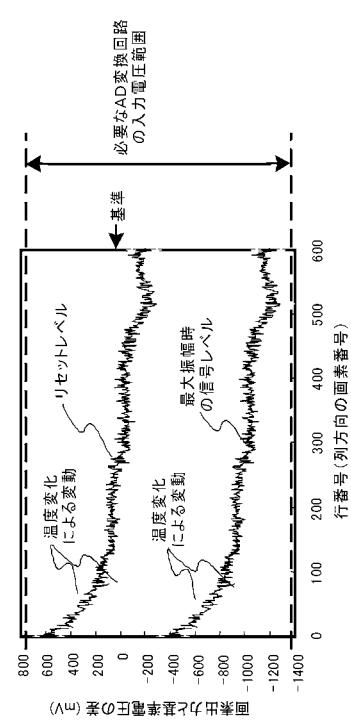

例えば、図47は、信号振幅が最大 - 1Vである場合の、基準電圧に対するリセットレベル及び最大振幅時の信号レベルを示している。この場合は、リセットレベルから信号レベルまでの信号振幅がPeak-to-Peakで1Vであるのに対して、2V程度のA/D変換可能な入力電圧範囲が必要となる。更に、温度変化によってリセットレベルが上下に変動した場合、基準電圧は一定値であるため、図48に示すように、更に入力電圧範囲を拡大する必要がある。

20

【0016】

先述した、外部印加や抵抗アレイ等で所定電圧を発生させ、当該所定電圧をA/D変換回路に基準電圧として供給する従来技術では、基準電圧とリセットレベルとの相関が低いため、A/D変換可能な入力電圧範囲が低下するという問題がある。更に、リセットレベルの画素ばらつきの面内分布や温度依存性などによっても、A/D変換可能な入力電圧範囲が低下するという問題がある。

30

【0017】

ここでは、ノイズ除去処理をデジタル信号処理にて実行する固体撮像装置において、A/D変換回路の基準電圧の設定について説明したが、上述した問題点はデジタル信号処理の場合に限られるものではない。すなわち、基準電圧を用いて単位画素からのアナログ信号に対して信号処理を行う固体撮像装置（その詳細については後述する）においても、デジタル信号処理の場合と同様のことが言える。

【0018】

そこで、本開示は、面内の大きな特性の揺らぎ（面内分布）の差異や、寄生容量の大きさに依存したオフセット成分を効果的に除去することが可能な固体撮像装置、当該固体撮像装置の信号処理方法、及び、当該固体撮像装置を有する電子機器を提供することを目的とする。

40

【課題を解決するための手段】

【0019】

上記目的を達成するために、本開示では、

光電変換部、及び、当該光電変換部で光電変換された電荷を検出する電荷検出部を有する単位画素が配列されてなり、

前記単位画素の信号を第1の信号及び第2の信号として2回に分けて読み出す固体撮像装置において、

前記単位画素から先に読み出される前記第1の信号を、前記第1の信号及び前記第2の

50

信号を処理する信号処理部の処理可能な入力電圧範囲の基準電圧として用い、

前記第1の信号及び前記第2の信号が前記入力電圧範囲内に入るよう前に前記基準電圧を調整した状態で前記第1の信号及び前記第2の信号に対して前記信号処理部によって信号処理を施す

構成を探っている。

#### 【0020】

単位画素から先に読み出される第1の信号を信号処理部の処理可能な入力電圧範囲の基準電圧として用いる。このとき、第1の信号が電荷検出部に蓄積、もしくは、保持された信号電荷に基づく信号、即ち、信号レベルである場合は、当該信号レベルを基準電圧として用いることになる。また、第1の信号が電荷検出部をリセットしたときのリセット電位に基づく信号、即ち、リセットレベルである場合は、当該リセットレベルを基準電圧として用いることになる。

10

#### 【0021】

先に読み出される第1の信号を基準電圧として設定した後、当該基準電圧を第1、第2の信号が、信号処理部の処理可能な入力電圧範囲内に入るよう調整する。この基準電圧の調整により、第1、第2の信号が入力電圧範囲内に入った状態でこれら第1、第2の信号に対して信号処理を実行することが可能になる。従って、先に読み出される第1の信号が信号レベルの場合、リセットレベルの場合のいずれの場合にも、処理対象の画素の信号を用いて基準電圧を設定した上で、第1、第2の信号に対して確実に信号処理を施すことができることとなる。

20

#### 【発明の効果】

#### 【0022】

本開示によれば、処理対象の画素の信号を用いて基準電圧を設定することで、別途生成した所定電圧を用いて基準電圧を設定する場合のような、面内の大きな特性の揺らぎ（面内分布）の差異や、寄生容量の大きさに依存したオフセット成分を効果的に除去できる。これにより、画素の出力振幅に対して、信号処理部の処理可能な入力電圧範囲に必要なマージンを低減することが可能となる。

#### 【図面の簡単な説明】

#### 【0023】

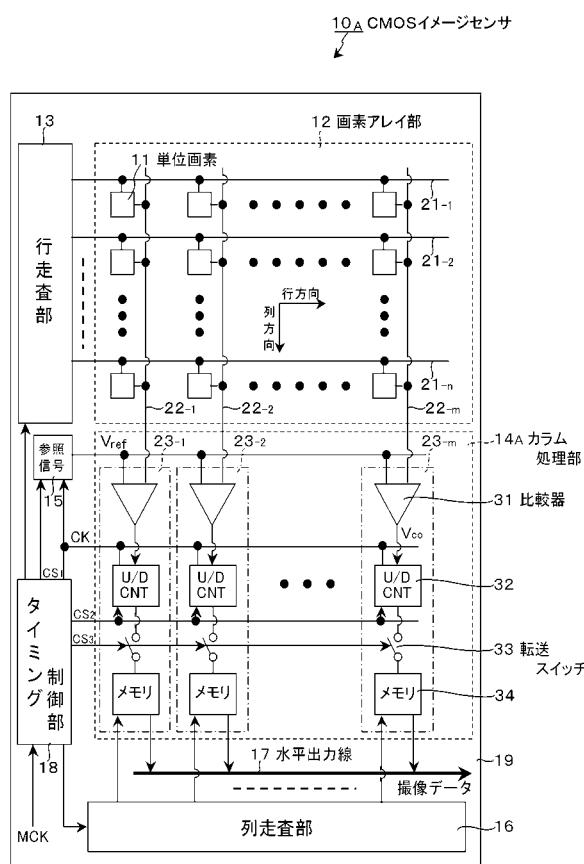

【図1】本開示の第1実施形態に係るCMOSイメージセンサの構成の概略を示すシステム構成図である。

30

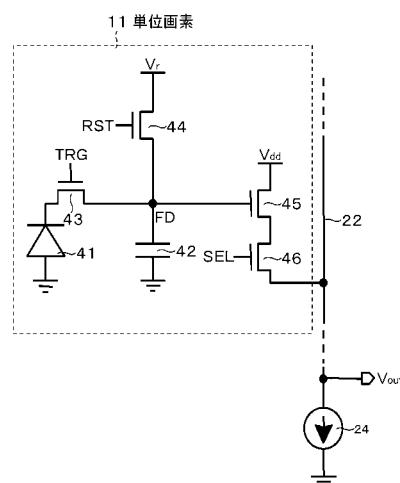

【図2】単位画素の構成の一例を示す回路図である。

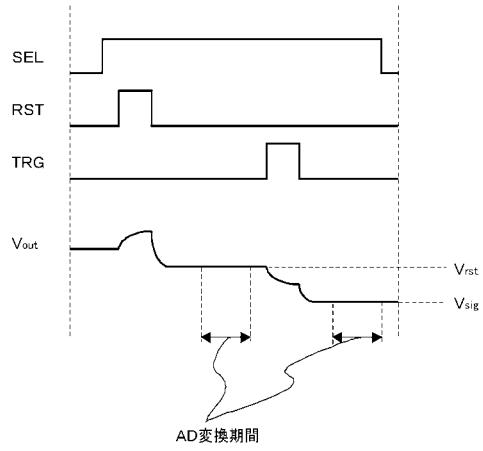

【図3】リセットレベル、信号レベルの順で読み出す場合の相關二重サンプリング動作の説明に供するタイミング波形図である。

【図4】先に読み出されるリセットレベルをAD変換回路の基準電圧として設定する場合の動作説明に供するタイミング波形図である。

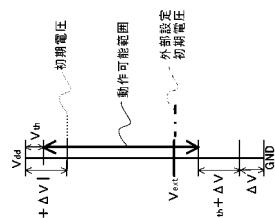

【図5】AD変換回路の入力段を構成する比較器の従来構成についての説明図であり、(A)は比較器の構成例を、(B)は比較器の動作範囲をそれぞれ示している。

【図6】CDS駆動時の比較器の内部ノードの電圧、及び、そのときの動作範囲を示す図である。

40

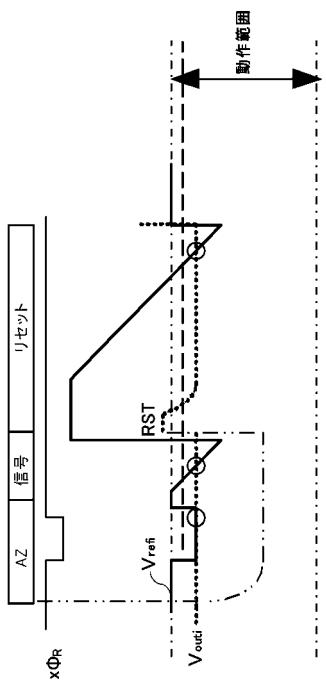

【図7】DDS駆動時の低照度時の比較器の内部ノードの電圧、及び、そのときの動作範囲を示す図である。

【図8】DDS駆動時の高照度時の比較器の内部ノードの電圧、及び、そのときの動作範囲を示す図である。

【図9】参照信号 $V_{ref}$ の傾斜を上下逆にした場合の比較器の動作範囲についての説明に供する図であり、(A)は低照度時、(B)は高照度時をそれぞれ示している。

【図10】PMOS入力の場合の比較器の構成についての説明図であり、(A)はPMOS入力の比較器の構成例を、(B)はPMOS入力の比較器の動作範囲をそれぞれ示している。

【図11】AD変換回路の基準電圧を調整する機能を備えた、実施例1に係る比較器につ

50

いての説明図であり、(A)は当該比較器の構成例を、(B)は当該比較器の動作範囲をそれぞれ示している。

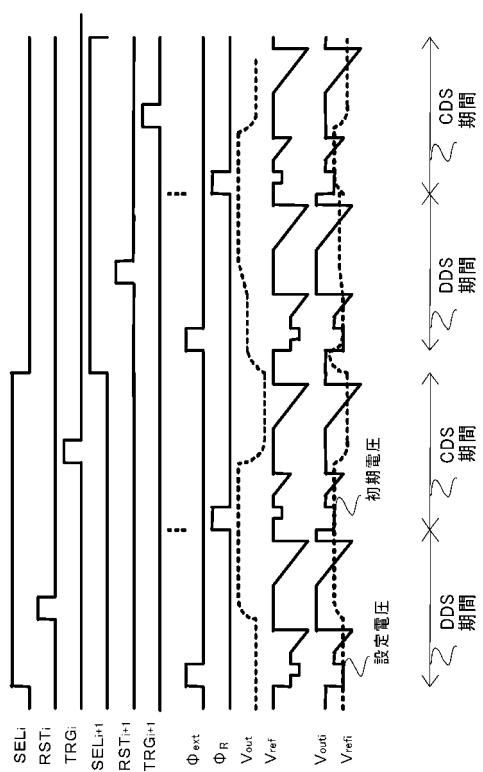

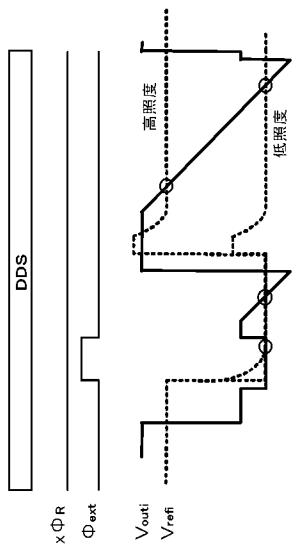

【図12】D D S駆動とC D S駆動を交互に行う場合の、D D S駆動の際の低照度時の場合の駆動波形を示す波形図である。

【図13】D D S駆動とC D S駆動を交互に行う場合の、D D S駆動の際の高照度時の場合の駆動波形を示す波形図である。

【図14】初期電圧設定回路をP M O Sトランジスタによって構成する場合の、実施例1に係る比較器についての説明図であり、(A)は当該比較器の構成例を、(B)は当該比較器の動作範囲をそれぞれ示している。

【図15】第1実施形態の実施例1に係る比較器の回路動作の説明に供するタイミング波形図である。 10

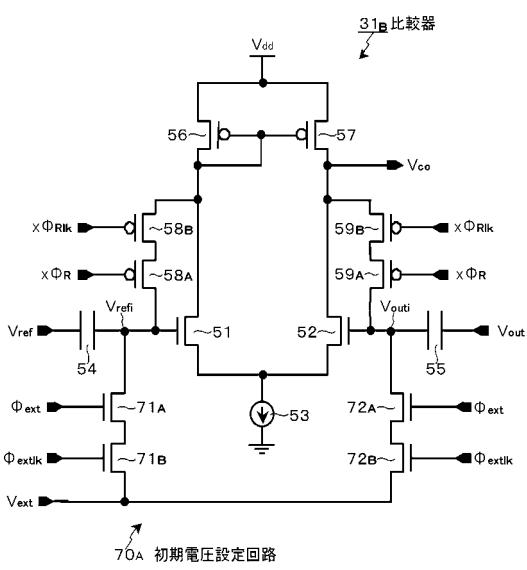

【図16】A D変換回路の内部の基準電圧 $V_{out_i}$ 、 $V_{ref_i}$ を調整する機能を備えた、実施例2に係る比較器の構成例を示す回路図である。

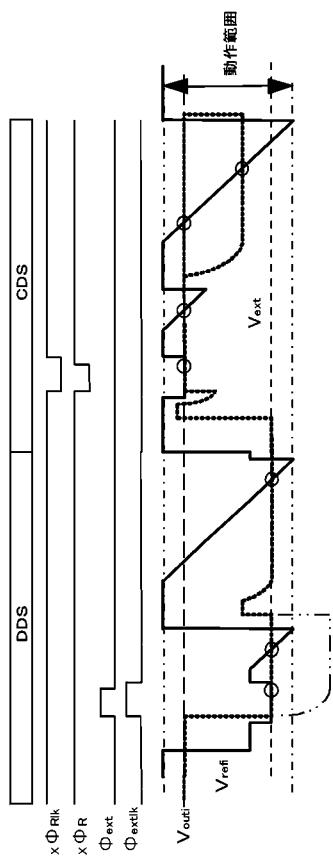

【図17】実施例2に係る比較器における制御信号 $x_R$ 、制御信号 $x_{Rik}$ 、制御信号 $ext$ 、制御信号 $ext_{lk}$ 、傾斜状波形の参照信号 $V_{ref}$ 、及び、信号電圧 $V_{out}$ の各波形を示すタイミング波形図である。

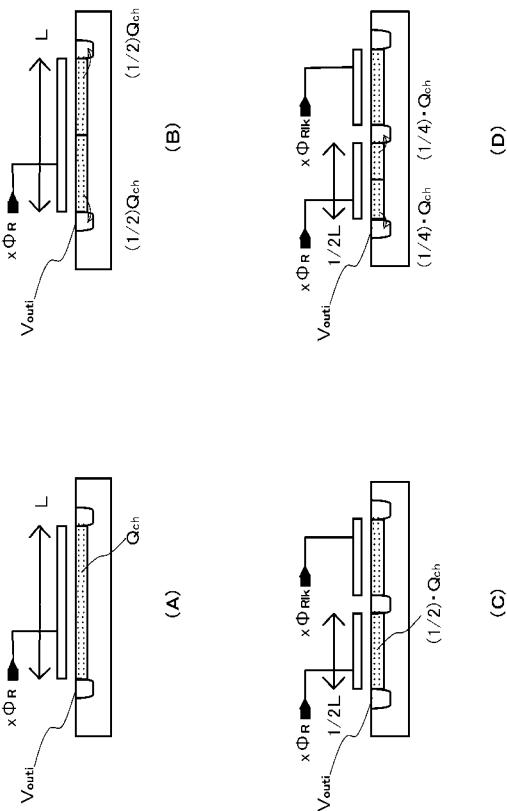

【図18】実施例2に係る比較器の作用、効果の説明に供するチャネル長及びインジェクション量についての説明図である。

【図19】比較回路部の後段に記憶回路部を有する、実施例3に係る比較器の構成例を示す回路図である。 20

【図20】実施例3に係る比較器の第1駆動例の動作説明に供するタイミング波形図である。

【図21】実施例3に係る比較器の第2駆動例の動作説明に供するタイミング波形図である。

【図22】参照信号 $V_{ref}$ のスロープについてC D S駆動とD D S駆動で同じ勾配にした場合の駆動の説明に供するタイミング波形図である。

【図23】参照信号 $V_{ref}$ のスロープについてD D S駆動側をC D S駆動側に比べて急勾配にした場合の駆動の説明に供するタイミング波形図である。 30

【図24】C D S駆動時のカウンタ部の動作説明に供するタイミング波形図である。

【図25】C D S駆動の低照度時のカウント動作についての説明図である。

【図26】C D S駆動の高照度時のカウント動作についての説明図である。

【図27】D D S駆動時のカウンタ部の動作説明に供するタイミング波形図である。

【図28】D D S駆動の低照度時のカウント動作についての説明図である。

【図29】D D S駆動の高照度時のカウント動作についての説明図である。

【図30】本開示の第2実施形態に係るC M O Sイメージセンサの構成の概略を示すシステム構成図である。 40

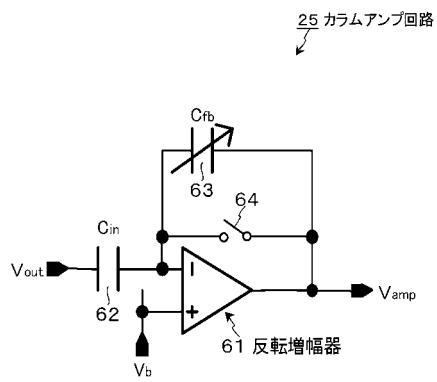

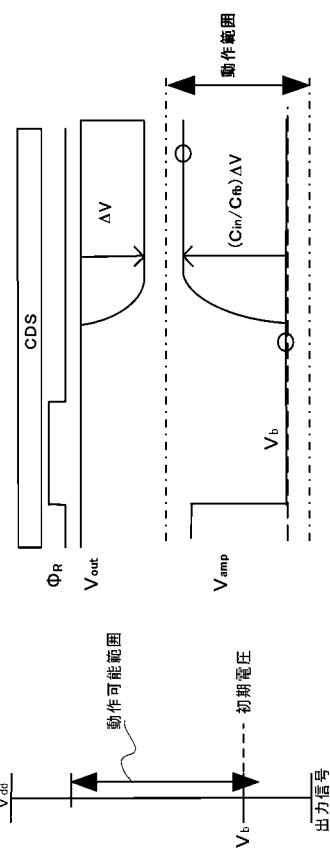

【図31】カラムアンプ回路の従来構成を示す回路図である。

【図32】従来構成に係るカラムアンプ回路の出力信号の動作範囲を示す図である。

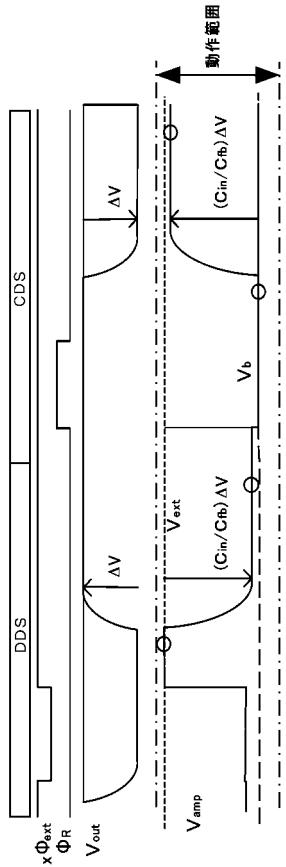

【図33】従来構成の係るカラムアンプ回路を用いてD D S駆動を行った場合の出力波形を示す波形図である。

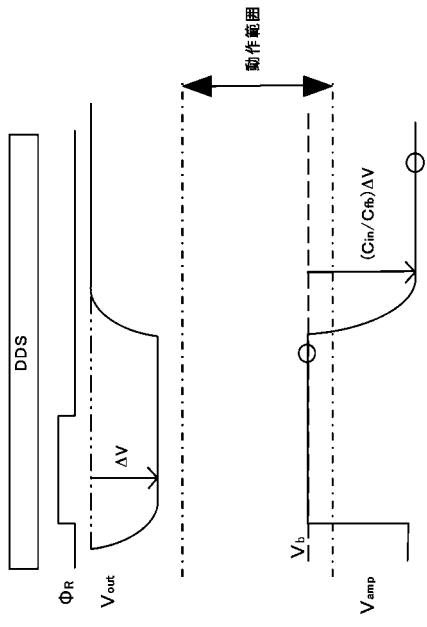

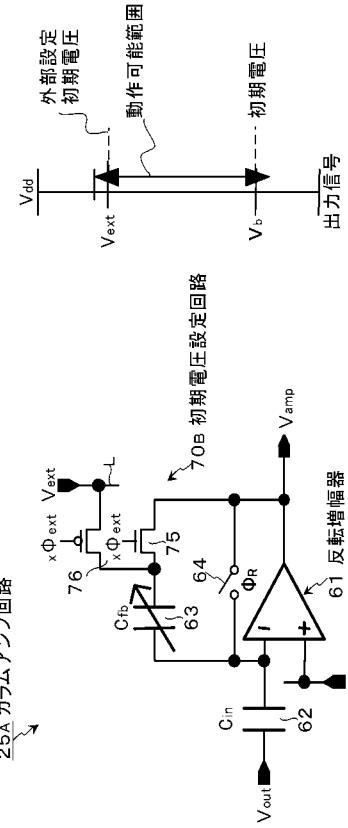

【図34】第2実施形態の実施例1に係るカラムアンプ回路についての説明図であり、(A)はカラムアンプ回路の構成例を、(B)はカラムアンプ回路の動作範囲をそれぞれ示している。

【図35】第2実施形態の実施例1に係るカラムアンプ回路の各部位の信号波形を示す波形図である。

【図36】第2実施形態の実施例2に係るカラムアンプ回路の構成の一例を示す回路図である。

【図37】第2実施形態の実施例2に係るカラムアンプ回路を有するC M O Sイメージセンサの動作説明に供するタイミング波形図である。

【図38】他の画素例1に係る単位画素の一例を示す構成図である。 50

【図39】他の画素例2に係る単位画素の一例を示す構成図である。

【図40】他の画素例2に係る単位画素を有し、グローバルシャッタ機能を持った固体撮像装置の動作の説明に供するタイミング波形図である。

【図41】他の画素例3に係る単位画素の一例を示す構成図である。

【図42】他の画素例3に係る単位画素を有し、グローバルシャッタ機能を持った固体撮像装置の動作の説明に供するタイミング波形図である。

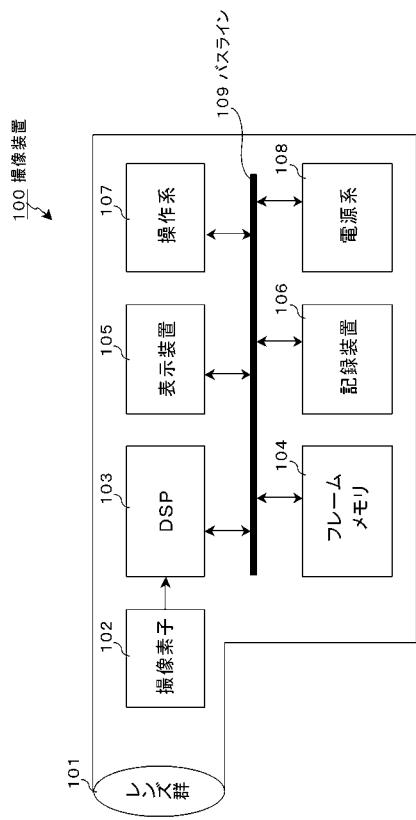

【図43】本開示に係る電子機器、例えば撮像装置の構成の一例を示すブロック図である。

【図44】固定パターンノイズを除去するには、信号レベルを読み出した後リセットレベルを読み出す必要があることについての説明に供する図である。

【図45】リセットレベルの縦方向の面内分布の一例を示す図である。

【図46】一定電圧を基準電圧として印加する場合、A/D変換回路の入力電圧範囲を拡大する必要があることについての説明に供する図である。

【図47】信号振幅が最大-1Vである場合の、基準電圧に対するリセットレベル及び最大振幅時の信号レベルを示す図である。

【図48】温度変化によってリセットレベルが上下に変動した場合、入力電圧範囲を拡大する必要があることについての説明に供する図である。

【発明を実施するための形態】

【0024】

以下、発明を実施するための形態（以下、「実施形態」と記述する）について図面を用いて詳細に説明する。尚、説明は以下の順序で行う。

1. 第1実施形態（カラムA/D変換回路の例）

1-1. システム構成

1-2. 画素構成

1-3. 相関二重サンプリングによるノイズ除去処理

1-4. 従来技術の説明

1-5. 第1実施形態の前提となる構成

1-6. 第1実施形態の特徴とする事項

2. 第2実施形態（カラムアンプ回路の例）

2-1. システム構成

2-2. 第2実施形態の特徴とする事項

3. 他の画素構成

4. 变形例

5. 電子機器（撮像装置の例）

【0025】

<1. 第1実施形態>

[1-1. システム構成]

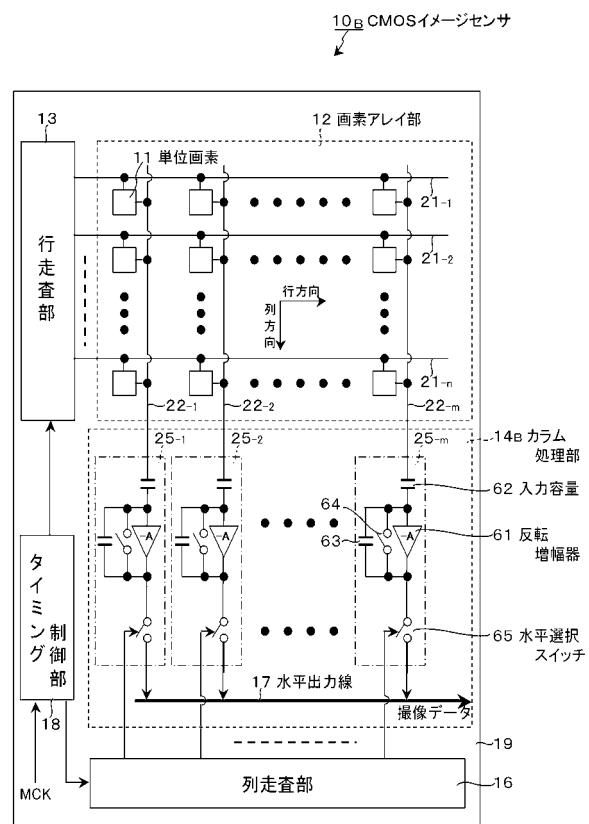

図1は、本開示の第1実施形態に係る固体撮像装置、例えばX-Yアドレス方式固体撮像装置の一種であるCMOSイメージセンサの構成の概略を示すシステム構成図である。ここで、CMOSイメージセンサとは、CMOSプロセスを応用して、または、部分的に使用して作成されたイメージセンサである。

【0026】

図1に示すように、本実施形態に係るCMOSイメージセンサ10<sub>A</sub>は、単位画素11が行列状に2次元配置されてなる画素アレイ部12と、当該画素アレイ部12の各画素11を駆動する周辺の駆動系及び信号処理系を有する。本例では、周辺の駆動系や信号処理系として、例えば、行走査部13、カラム処理部14<sub>A</sub>、参照信号生成部15、列走査部16、水平出力線17、及び、タイミング制御部18が設けられている。これらの駆動系及び信号処理系は、画素アレイ部12と同一の半導体基板（チップ）19上に集積されている。

【0027】

10

20

30

40

50

このシステム構成において、タイミング制御部18は、マスタークロックMCKに基づいて、行走査部13、カラム処理部14<sub>A</sub>、参照信号生成部15、及び、列走査部16などの動作の基準となるクロック信号や制御信号などを生成する。タイミング制御部18で生成されたクロック信号や制御信号などは、行走査部13、カラム処理部14<sub>A</sub>、参照信号生成部15、及び、列走査部16などに対してそれらの駆動信号として与えられる。

#### 【0028】

画素アレイ部12は、受光した光量に応じた光電荷を生成し、かつ、蓄積する光電変換部を有する単位画素（以下、単に「画素」と記述する場合もある）11が行方向及び列方向に、即ち、行列状に2次元配置された構成となっている。ここで、行方向とは画素行の画素の配列方向（即ち、水平方向／横方向）を言い、列方向とは画素列の画素の配列方向（即ち、垂直方向／縦方向）を言う。

10

#### 【0029】

この画素アレイ部12において、行列状の画素配置に対して、画素行毎に行制御線21（21<sub>..1</sub>～21<sub>..n</sub>）が行方向に沿って配線され、画素列ごとに列信号線22（22<sub>..1</sub>～22<sub>..m</sub>）が列方向に沿って配線されている。行制御線21は、単位画素11から読み出す際の制御を行うための制御信号を伝送する。図1では、行制御線21について1本の配線として示しているが、1本に限られるものではない。行制御線21<sub>..1</sub>～21<sub>..n</sub>の各一端は、行走査部13の各行に対応した各出力端に接続されている。

20

#### 【0030】

行走査部13は、シフトレジスタやアドレスデコーダなどによって構成され、画素アレイ部12の各画素11を全画素同時あるいは行単位等で駆動する。すなわち、行走査部13は、当該行走査部13を制御するタイミング制御部18と共に、画素アレイ部12の各画素11を駆動する駆動部を構成している。この行走査部13はその具体的な構成については図示を省略するが、一般的に、読み出し走査系と掃出し走査系の2つの走査系を有する構成となっている。

20

#### 【0031】

読み出し走査系は、単位画素11から信号を読み出すために、画素アレイ部12の単位画素11を行単位で順に選択走査する。単位画素11から読み出される信号はアナログ信号である。掃出し走査系は、読み出し走査系によって読み出し走査が行われる読み出し行に対して、その読み出し走査よりもシャッタスピードの時間分だけ先行して掃出し走査を行う。

30

#### 【0032】

この掃出し走査系による掃出し走査により、読み出し行の単位画素11の光電変換部から不要な電荷が掃き出されることによって当該光電変換部がリセットされる。そして、この掃出し走査系によって不要電荷を掃き出す（リセットする）ことにより、所謂、電子シャッタ動作が行われる。ここで、電子シャッタ動作とは、光電変換部の光電荷を捨てて、新たに露光を開始する（光電荷の蓄積を開始する）動作のことを言う。

#### 【0033】

読み出し走査系による読み出し動作によって読み出される信号は、その直前の読み出し動作または電子シャッタ動作以降に受光した光量に対応するものである。そして、直前の読み出し動作による読み出しタイミングまたは電子シャッタ動作による掃出しタイミングから、今回の読み出し動作による読み出しタイミングまでの期間が、単位画素11における光電荷の露光期間となる。

40

#### 【0034】

カラム処理部14<sub>A</sub>は、例えば、画素アレイ部12の画素列毎、即ち、列信号線22（22<sub>..1</sub>～22<sub>..m</sub>）毎に1対1の対応関係をもって設けられたAD（アナログ-デジタル）変換回路23（23<sub>..1</sub>～23<sub>..m</sub>）を有する。AD変換回路23（23<sub>..1</sub>～23<sub>..m</sub>）は、画素アレイ部12の各単位画素11から画素列毎に出力されるアナログ信号（画素信号）をデジタル信号に変換する。

#### 【0035】

参照信号生成部15は、時間が経過するにつれて電圧値が階段状に変化する、所謂、ラ

50

ンプ( RAMP )波形(傾斜状の波形)の参照信号  $V_{ref}$  を生成する。参照信号生成部 15 については、例えば、DAC(デジタル-アナログ変換)回路を用いて構成することができる。尚、参照信号生成部 15 としては、DAC回路を用いた構成のものに限られるものではない。

#### 【0036】

参照信号生成部 15 は、タイミング制御部 18 から与えられる制御信号 CS<sub>1</sub>による制御の下に、当該タイミング制御部 18 から与えられるクロック CK に基づいてランプ波の参照信号  $V_{ref}$  を生成する。そして、参照信号生成部 15 は、生成した参照信号  $V_{ref}$  をカラム処理部 15 の AD 变換回路 23<sub>1</sub> ~ 23<sub>m</sub> に対して供給する。

#### 【0037】

AD 变換回路 23<sub>1</sub> ~ 23<sub>m</sub> は全て同じ構成となっている。ここでは、m 列目の AD 变換回路 23<sub>m</sub> を例に挙げて説明するものとする。AD 变換回路 23<sub>m</sub> は、比較器 31、カウント部である例えばアップ/ダウンカウンタ(図中、「U/D CNT」と記している) 32、転送スイッチ 33、及び、メモリ装置 34 を有する構成となっている。

#### 【0038】

比較器 31 は、画素アレイ部 12 の n 列目の各単位画素 11 から出力される画素信号に応じた列信号線 22<sub>m</sub> の信号電圧  $V_{out}$  を比較入力とし、参照信号生成部 15 から供給されるランプ波の参照信号  $V_{ref}$  を基準入力とし、両者を比較する。そして、比較器 31 は、例えば、参照信号  $V_{ref}$  が信号電圧  $V_{out}$  よりも大なるときに出力  $V_c$  が第 1 の状態(例えば、高レベル)になり、参照信号  $V_{ref}$  が信号電圧  $V_x$  以下のときに出力  $V_c$  が第 2 の状態(例えば、低レベル)になる。

#### 【0039】

アップ/ダウンカウンタ 32 は非同期カウンタであり、タイミング制御部 18 から与えられる制御信号 CS<sub>2</sub> による制御の下に、当該タイミング制御部 18 からクロック CK が参照信号生成部 15 と同じタイミングで与えられる。そして、アップ/ダウンカウンタ 32 は、クロック CK に同期してダウン(DOWN)カウント、または、アップ(UP)カウントを行うことで、比較器 31 での比較動作の開始から比較動作の終了までの比較期間を計測する。

#### 【0040】

転送スイッチ 33 は、タイミング制御部 18 から与えられる制御信号 CS<sub>3</sub> による制御の下に、ある画素行の単位画素 11 についてのアップ/ダウンカウンタ 32 のカウント動作が完了した時点でオン(閉)状態となる。そして、転送スイッチ 33 は、アップ/ダウンカウンタ 32 のカウント結果をメモリ装置 34 に転送する。

#### 【0041】

このようにして、画素アレイ部 12 の各単位画素 11 から列信号線 22<sub>1</sub> ~ 22<sub>m</sub> を経由して画素列毎に供給されるアナログ信号について、AD 变換回路 23(23<sub>1</sub> ~ 23<sub>m</sub>)において先ず比較器 31 で比較動作が行われる。そして、アップ/ダウンカウンタ 32 において、比較器 31 での比較動作の開始から比較動作の終了までの期間に亘ってカウント動作を行うことで、アナログ信号がデジタル信号に変換されてメモリ装置 34 に格納される。

#### 【0042】

列走査部 16 は、シフトレジスタやアドレスデコーダなどによって構成され、カラム処理部 14<sub>A</sub> における AD 变換回路 23<sub>1</sub> ~ 23<sub>m</sub> の列アドレスや列走査の制御を行う。この列走査部 16 による制御の下に、AD 变換回路 23<sub>1</sub> ~ 23<sub>m</sub> の各々で AD 变換されたデジタル信号は順に水平出力線 17 に読み出され、当該水平出力線 17 を経由して撮像データとして出力される。

#### 【0043】

尚、本開示には直接関連しないため特に図示しないが、水平出力線 17 を経由して出力される撮像データに対して各種の信号処理を施す回路等を、上記構成要素以外に設けることも可能である。その際、これらの回路が画素アレイ部 12 と同一の半導体基板 19 上に

設けられているか否かは問わない。

#### 【0044】

上記構成の列並列ADC搭載のCMOSイメージセンサ10<sub>A</sub>は、画素アレイ部12中の全画素11に対して同一のタイミングで露光開始と露光終了とを実行するグローバル露光も可能としている。このグローバル露光は、行走査部13及びタイミング制御部18からなる駆動部による駆動の下に実行される。グローバル露光を実現するグローバルシャッタ機能は、高速に動く被写体の撮像や、撮像画像の同時性を必要とするセンシング用途に用いて好適なシャッタ動作である。

#### 【0045】

尚、本例では、カラム処理部14<sub>A</sub>について、AD変換回路23が列信号線22毎に1対1の対応関係をもって設けられた構成を例に挙げたが、1対1の対応関係の配置に限られるものではない。例えば、1つのAD変換回路23を複数の画素列で共有し、複数の画素列間で時分割にて使用する構成を探ることも可能である。

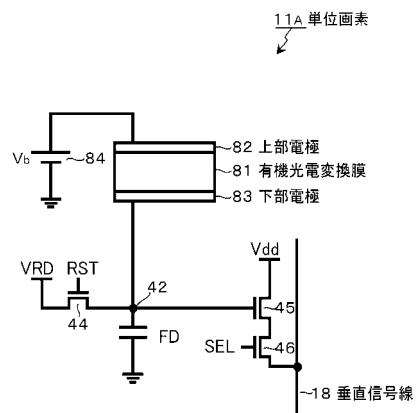

#### 【0046】

##### [1-2. 画素構成]

図2は、単位画素11の構成の一例を示す回路図である。図2に示すように、本構成例に係る単位画素11は、光電変換部として例えばフォトダイオード41を有している。単位画素11は、フォトダイオード41に加えて、例えば、電荷検出部42、転送トランジスタ(転送ゲート部)43、リセットトランジスタ44、増幅トランジスタ45、及び、選択トランジスタ46を有する構成となっている。

#### 【0047】

尚、ここでは、転送トランジスタ43、リセットトランジスタ44、増幅トランジスタ45、及び、選択トランジスタ46として、例えばNチャネル型のMOSトランジスタを用いている。但し、ここで例示した転送トランジスタ43、リセットトランジスタ44、増幅トランジスタ45、及び、選択トランジスタ46の導電型の組み合わせは一例に過ぎず、これらの組み合わせに限られるものではない。

#### 【0048】

この単位画素11に対して、先述した行制御線21(21<sub>1</sub>~21<sub>n</sub>)として、複数の制御線が同一画素行の各画素に対して共通に配線される。図2では、図面の簡略化のために、複数の制御線については図示を省略している。複数の制御線は、行走査部13の各画素行に対応した出力端に画素行単位で接続されている。行走査部13は、複数の制御線に対して転送信号TRG、リセット信号RST、及び、選択信号SELを適宜出力する。

#### 【0049】

フォトダイオード41は、アノード電極が負側電源(例えば、グランド)に接続されており、受光した光をその光量に応じた電荷量の光電荷(ここでは、光電子)に光電変換してその光電荷を蓄積する。フォトダイオード41のカソード電極は、転送トランジスタ43を介して増幅トランジスタ45のゲート電極と電気的に接続されている。

#### 【0050】

増幅トランジスタ45のゲート電極と電気的に繋がった領域は、電荷を電圧に変換する電荷検出部42である。以下、電荷検出部42をFD(フローティング・ディフュージョン/浮遊拡散領域/不純物拡散領域)部42と呼ぶ。

#### 【0051】

転送トランジスタ43は、フォトダイオード41のカソード電極とFD部42との間に接続されている。転送トランジスタ43のゲート電極には、高レベル(例えば、V<sub>dd</sub>レベル)がアクティブ(以下、「Highアクティブ」と記述する)となる転送信号TRGが行走査部13から与えられる。転送トランジスタ43は、転送信号RGに応答して導通状態となることで、フォトダイオード41で光電変換され、蓄積された光電荷をFD部42に転送する。

#### 【0052】

リセットトランジスタ44は、ドレイン電極がリセット電源V<sub>r</sub>に、ソース電極がFD

10

20

30

40

50

部42にそれぞれ接続されている。リセットトランジスタ44のゲート電極には、Highアクティブのリセット信号RSTが行走査部13から与えられる。リセットトランジスタ44は、リセット信号RSTに応答して導通状態となり、FD部42の電荷をリセット電源V<sub>r</sub>に捨てることによって当該FD部42をリセットする。

#### 【0053】

増幅トランジスタ45は、ゲート電極がFD部42に、ドレイン電極が画素電源V<sub>dd</sub>にそれぞれ接続されている。この増幅トランジスタ45は、フォトダイオード41での光電変換によって得られる信号を読み出す読出し回路であるソースフォロワの入力部となる。すなわち、増幅トランジスタ45は、ソース電極が選択トランジスタ46を介して列信号線22に接続されることで、当該列信号線22の一端に接続される電流源24とソースフォロワを構成する。10

#### 【0054】

選択トランジスタ46は、例えば、ドレイン電極が増幅トランジスタ45のソース電極に、ソース電極が列信号線22にそれぞれ接続されている。選択トランジスタ46のゲート電極には、Highアクティブの選択信号SELが行走査部13から与えられる。選択トランジスタ46は、選択信号SELに応答して導通状態となることで、単位画素11を選択状態として増幅トランジスタ45から出力される信号を列信号線22に伝達する。

#### 【0055】

尚、選択トランジスタ46については、画素電源V<sub>dd</sub>と増幅トランジスタ45のドレイン電極との間に接続した回路構成を探ることも可能である。20

#### 【0056】

##### [1-3. 相関二重サンプリングによるノイズ除去処理]

上記構成の単位画素11が行列状に2次元配置されて構成される固体撮像装置では、一般的に、リセット動作時のノイズを除去するために、相関二重サンプリングによるノイズ除去処理が行わる。図3に示すように、選択信号SELによって選択された状態にある単位画素11は、リセット信号RSTに応答してFD部42をリセット電位V<sub>r</sub>にリセットし、当該リセット電位V<sub>r</sub>をリセットレベルV<sub>rst</sub>として読み出す。続いて、転送信号TRGによって転送トランジスタ43を駆動し、フォトダイオード41に蓄積された電荷をFD部42へ転送し、当該電荷を信号レベルV<sub>sig</sub>として読み出す。

#### 【0057】

リセットレベルV<sub>rst</sub>及び信号レベルV<sub>sig</sub>には、熱雑音、寄生容量のカップリングによる雑音といった、リセット毎にランダムに発生するノイズ(Random Noise)が、FD部42をリセット電位V<sub>r</sub>にリセットした際に加わっている。これらのノイズとしては、FD部42をリセットする度に異なるノイズが加わる。30

#### 【0058】

リセットレベルV<sub>rst</sub>を先に読み出す読み出し方式においては、リセットしたときに発生するランダムノイズはFD部42で保持されているため、信号電荷を加えて読み出された信号レベルV<sub>sig</sub>には、リセットレベルV<sub>rst</sub>と同じノイズ量が保持されている。このため、信号レベルV<sub>sig</sub>からリセットレベルV<sub>rst</sub>を減算する相関二重サンプリング動作を行うことで、これらのノイズを除去した信号を得ることが可能となる。40

#### 【0059】

すなわち、相関二重サンプリング動作では、信号電荷をFD部42へ転送する前に、FD部42をリセットしてリセットレベルを読み出すことが、これらのリセットノイズを除去できる条件となる。また、信号の読み出しに用いられる増幅トランジスタ45の閾値ばらつき等、固定的に加わるノイズ(固定パターンノイズ;Fixed Pattern Noise)も除去することができる。

#### 【0060】

単位画素11から読み出されたリセットレベルV<sub>rst</sub>及び信号レベルV<sub>sig</sub>は、AD変換回路23においてデジタル信号に変換される。一般的に、AD変換回路23の変換可能な入力電圧の範囲には制限があるため、単位画素11から出力されるアナログ信号を、AD

10

20

30

40

50

変換回路 2 3 の入力電圧範囲に収まるよう設計する必要がある。

【 0 0 6 1 】

すなわち、リセットレベル  $V_{rst}$  から、取得すべき信号レベル  $V_{sig}$  までの電圧範囲が、A D 変換回路 2 3 の入力電圧範囲内に収まっている必要がある。例えば、リセットレベル  $V_{rst}$  が 3 V で、信号電荷による出力の振幅が - 1 V であったとすると、取得すべき最大の信号レベルが 2 V となる。この場合、A D 変換回路 2 3 の変換可能な入力電圧範囲は 2 V ~ 3 V であればよいことになる。

【 0 0 6 2 】

しかし、実際には、増幅トランジスタ 4 5 の閾値ばらつきや、列信号線 2 2 との間の寄生容量によるオフセット等で、リセットレベル  $V_{rst}$  は画素毎に異なっている。例えば、

10 2 次元配置された単位画素 1 1 のリセットレベル  $V_{rst}$  の平均値は 3 V であっても、単位画素 1 1 によって 3 . 1 V や 2 . 9 V のリセットレベル  $V_{rst}$  を出力する可能性がある。この場合、信号電荷による振幅の幅が一様に - 1 V であったとしても、A D 変換回路 2 3 は 1 . 9 V ~ 3 . 1 V の入力電圧を変換可能でなくてはいけない。A D 変換回路 2 3 の変換可能な入力電圧範囲を広げることは、即ち、A D 変換回路 2 3 の基本性能を高めることに他ならず、電源電圧、消費電力、面積などが増加する要因となる。

【 0 0 6 3 】

このことから、A D 変換回路 2 3 の変換可能な入力電圧範囲の幅は、信号電荷による出力の振幅に近づけることが好ましい。そのため、A D 変換回路 2 3 の入力電圧範囲の基準となる基準電圧を調整する方法が採られる。基準電圧によって A D 変換回路 2 3 の入力電圧範囲をシフトさせることで、画素の出力信号、即ち、A D 変換回路 2 3 の入力信号のオフセット成分を除去し、リセットレベル  $V_{rst}$  のばらつきによる必要な入力電圧範囲の拡大を回避することが可能となる。

20

【 0 0 6 4 】

[ 1 - 4 . 従来技術の説明 ]

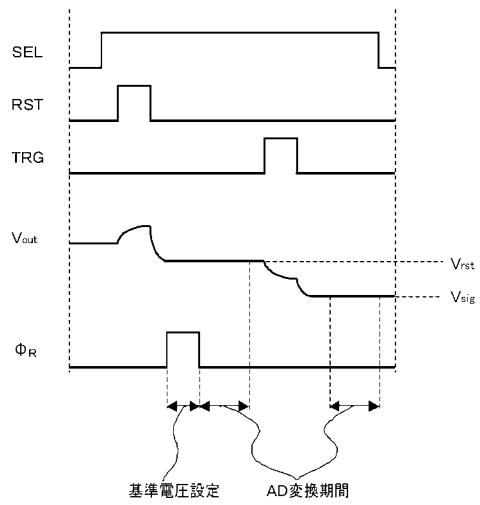

特許文献1に記載の従来技術では、図 4 に示すように、単位画素 1 1 から先に読み出されるリセットレベル  $V_{rst}$  を、制御信号  $V_R$  による制御の下に、A D 変換回路 2 3 の基準電圧  $V_{zr}$  として設定し、リセットレベル  $V_{rst}$  及び信号レベル  $V_{sig}$  を A D 変換するようしている。このように、基準電圧  $V_{zr}$  をリセットレベル  $V_{rst}$  と等しくすることで、リセットレベル  $V_{rst}$  がノイズによって変動しても、信号電荷による単位画素 1 1 の出力振幅  $|V_{sig} - V_{rst}|$  を安定して A D 変換回路 2 3 の入力電圧範囲に収めることが可能となる。

30

【 0 0 6 5 】

前にも述べたように、A D 変換回路 2 3 の基準電圧  $V_{zr}$  は、一般的に、A D 変換回路 2 3 の入力電圧範囲に対して十分小さい範囲でしか調整できない。従って、A D 変換回路 2 3 の基準電圧  $V_{zr}$  としては、リセットレベル  $V_{rst}$  のように、ばらつきの幅が安定して限られている信号が好ましい。逆に、信号レベル  $V_{sig}$  のように入射光量によって電圧が大きく振幅する信号は、A D 変換回路 2 3 の基準電圧  $V_{zr}$  としては適さない。

【 0 0 6 6 】

このように、特許文献1に記載の従来技術では、ノイズ除去処理に際して、単位画素 1 1 から先にリセットレベル  $V_{rst}$  を読み出し、当該リセットレベル  $V_{rst}$  の直後に信号レベル  $V_{sig}$  を読み出すことが前提となっている。

40

【 0 0 6 7 】

[ 1 - 5 . 第 1 実施形態の前提となる構成 ]

これに対して、第 1 実施形態に係る C M O S イメージセンサ 1 0 A は、全画素一括露光のために、信号電荷を F D 部 4 2 に保持した状態で信号読み出しを実行する構成を探っている。すなわち、第 1 実施形態に係る C M O S イメージセンサ 1 0 A は、リセットレベル  $V_{rst}$  を信号レベル  $V_{sig}$  の直前に読み出すことができない構成となっている。従って、上述した考えの下では、単位画素 1 1 の信号レベル  $V_{sig}$  を A D 変換する前に同一画素から基準電圧  $V_{zr}$  を取得することができないことになる。

【 0 0 6 8 】

10

20

30

40

50

一方で、全画素一括露光を実現するC M O Sイメージセンサ10<sub>A</sub>においては、基本的には1行毎に、単位画素11から信号を読み出す動作が2回行われる。2回の読み出し動作を行う前提として、単位画素11が、光電変換された電荷量が所定の電荷量を超えたときに、当該所定の飽和電荷量を超えた信号電荷がF D部42に蓄積される画素構造となっているものとする。

#### 【0069】

尚、本明細書においては、光電変換された電荷量が所定の電荷量を超える光が入射されるときを「高照度」と呼び、光電変換された電荷量が所定の電荷量以下となる光が入射されるときを「低照度」と呼ぶこととする。

#### 【0070】

2回の読み出し動作のうち1回目の読み出し動作では、F D部42に保持、もしくは、蓄積されている信号電荷を信号レベルとして読み出し、次いで、F D部42を所定電位にリセットして当該所定電位をリセットレベルとして読み出す駆動（第1の駆動）が行われる。以下では、1回目の駆動を、「D D S (Double Data Sampling) 駆動」と呼ぶこととする。このD D S駆動では、単位画素11から先に読み出される信号レベルを、A D変換回路23の変換可能な入力電圧範囲の基準となる基準電圧として用いる。

#### 【0071】

2回目の読み出し動作では、F D部42を所定電位にリセットして当該所定電位をリセットレベルとして読み出した後、フォトダイオード41に蓄積されている信号電荷をF D部42に転送し、次いで、F D部42の信号電荷を信号レベルとして読み出す駆動（第2の駆動）が行われる。以下では、2回目の駆動を、「C D S (Correlated Double Sampling) 駆動」と呼ぶこととする。このC D S駆動では、単位画素11から先に読み出されるリセットレベルを、A D変換回路23の変換可能な入力電圧範囲の基準となる基準電圧として用いる。

#### 【0072】

ここで、D D S駆動とC D S駆動とを併用する理由について説明する。先述したことから明らかなように、F D部42を信号保持、もしくは、蓄積部として用いることで、F D部42を用いない場合に比較して信号のダイナミックレンジを拡大することができる。但し、D D S駆動では、信号レベルの読み出しとリセットレベルの読み出しとの間にリセット動作が介在するため、先に読み出される信号レベルに含まれるリセットレベルと、後で読み出されるリセットレベルとの間の相関が低い。

#### 【0073】

これに対して、C D S駆動では、リセット動作を行った後に、リセットレベルと信号レベルとを連続して読み出すため、先に読み出されるリセットレベルと、後で読み出される信号レベルに含まれるリセットレベルとの間の相関が高い。従って、D D S駆動に比べてC D S駆動の方が確実にノイズ除去を行うことができるため高画質化を図る上で有利である。このような理由から、グローバル露光を実現しつつ高画質化を図るには、D D S駆動単独の駆動法よりも、D D S駆動とC D S駆動とを併用する駆動法の方が好ましい。

#### 【0074】

ところで、D D S駆動では、単位画素11から先に読み出される信号レベルをA D変換回路23の基準電圧として用いるとしているが、前にも述べたように、入射光量によって電圧が大きく振幅する信号レベルは、本来ならば、A D変換回路23の基準電圧としては適さない。信号レベルをA D変換回路23の基準電圧として用いる場合、A D変換回路23の入力段を構成する比較器31の動作範囲の確保の問題を解消する必要がある。この問題について詳しく説明する。その前に、A D変換回路23の入力段を構成する比較器31の従来構成について説明する。

#### 【0075】

（A D変換回路の入力段を構成する比較器の従来構成について）

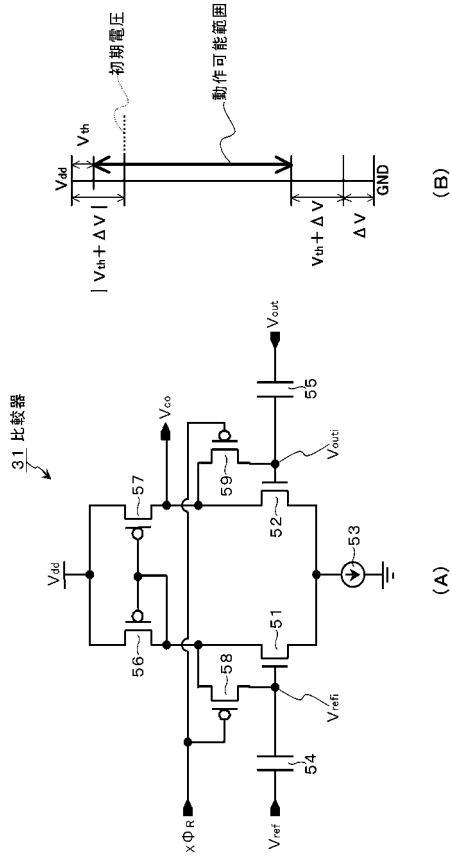

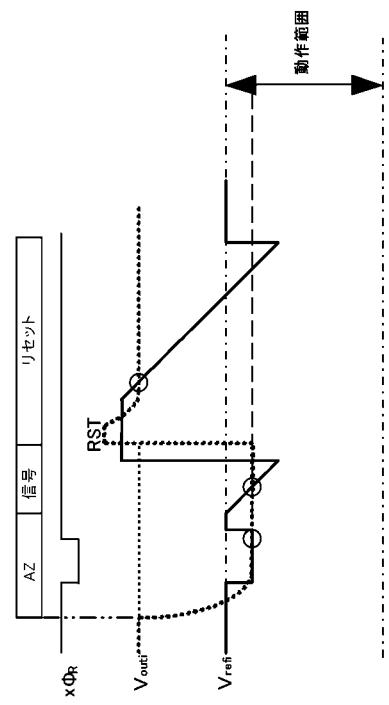

図5は、A D変換回路の入力段を構成する比較器の従来構成についての説明図であり、（A）は比較器の構成例を、（B）は比較器の動作範囲をそれぞれ示している。

10

20

30

40

50

## 【0076】

図5(A)に示すように、従来構成に係る比較器31は、ソース電極が共通に接続された差動対トランジスタ(コンパレータトランジスタ)51,52と、そのソース共通ノードとグランドとの間に接続された電流源53とを有している。差動対トランジスタ51,52として、Nチャネル型のMOSトランジスタ(以下、「NMOSトランジスタ」と記述する)が用いられている。

## 【0077】

NMOSトランジスタ51のゲート電極には、参照信号生成部15で生成される傾斜状波形(階段波)の参照信号 $V_{refi}$ が容量54を介して与えられる。NMOSトランジスタ52のゲート電極には、単位画素11から列信号線22\_mを通して供給される信号電圧 $V_{out}$ が容量55を介して与えられる。

10

## 【0078】

NMOSトランジスタ51のドレイン電極と電源 $V_{dd}$ との間にはダイオード接続構成、即ち、ゲート電極とドレイン電極とが共通に接続されたPチャネル型のMOSトランジスタ(以下、「PMOSトランジスタ」と記述する)56が接続されている。NMOSトランジスタ52のドレイン電極と電源 $V_{dd}$ との間には、PMOSトランジスタ57が接続されている。PMOSトランジスタ56,57は、ゲート電極が互いに共通に接続されている。

## 【0079】

NMOSトランジスタ51のゲート電極とドレイン電極との間にはPMOSトランジスタ58が接続されている。NMOSトランジスタ52のゲート電極とドレイン電極との間にも、PMOSトランジスタ59が接続されている。そして、これらPMOSトランジスタ58,59の各ゲート電極には、基準電圧を設定するための制御を行う制御信号 $x_R$ の反転信号 $x_{R'}$ が印加される。

20

## 【0080】

上記の従来構成に係る比較器31において、AD変換回路23の基準電圧は、制御信号 $x_R$ の反転信号 $x_{R'}$ がPMOSトランジスタ58,59の各ゲート電極に印加されることによって容量54,55に保持される。そして、比較器31において、参照信号 $V_{ref}$ と列信号線22\_mの信号電圧 $V_{out}$ とが比較される。具体的には、参照信号 $V_{ref}$ の変化に応じて、信号電圧 $V_{out}$ との比較結果(比較出力) $V_c$ が遷移するタイミングをデジタル信号として保持する。

30

## 【0081】

制御信号 $x_R$ の反転信号 $x_{R'}$ によって取得された基準電圧に対して、参照信号 $V_{ref}$ 及び信号電圧 $V_{out}$ がそれぞれ同じ振幅となったときに比較出力 $V_c$ が遷移する。図5(B)において、 $V_{th}$ はMOSトランジスタの閾値電圧であり、 $V$ は単位画素11のリセッタレベルと信号レベルとの電位差である。尚、本開示が適用されるAD変換回路23は、入力電圧範囲を調整する基準電圧の設定手段を有していれば、本構成に限るものではない。

。

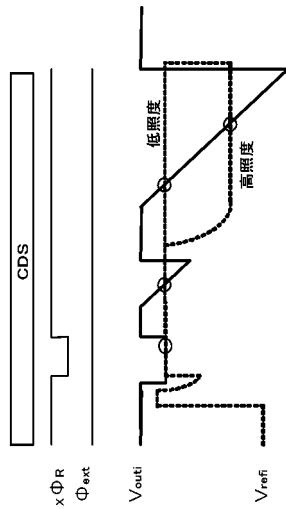

## 【0082】

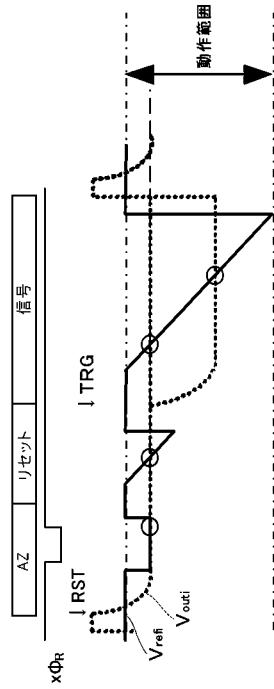

図6に、CDS駆動時の比較器31の内部ノードの電圧、及び、そのときの動作範囲を示す。また、図7及び図8に、DDS駆動時の低照度時、高照度時の比較器31の内部ノードの電圧、及び、そのときの動作範囲を示す。図6乃至図8に示すように、基準電圧を設定する期間(図中、AZの期間)の電圧は、図5の比較器31の入出力電圧をPMOSトランジスタ58,59にてショートした電圧となる。

40

## 【0083】

図6乃至図8において、印は、比較器31の2つの入力、即ち、画素信号に応じた列信号線22\_mの信号電圧 $V_{out}$ により変位するNMOSトランジスタ52のゲート電極側の電位 $V_{outi}$ と、参照信号生成部15から供給されるランプ波の参照信号 $V_{ref}$ により変位する、NMOSトランジスタ51のゲート電極側の電位 $V_{refi}$ とが一致するポイントを示している。以下の動作範囲を示す図でも同様とする。

50

## 【0084】

図6に示すCDS駆動の場合は、参照信号 $V_{ref}$ が比較器31の動作範囲内に収まる。これに対して、図7及び図8に示すDDS駆動の場合は、リセットレベルは信号レベルよりも高いために、比較のための参照信号 $V_{ref}$ については、信号レベルを読んだ場合よりも高い電圧とする必要がある。このとき、比較器31に入力される参照信号 $V_{ref}$ の電圧は比較器31の動作範囲を超えてしまうため、比較器31が動作しない。

## 【0085】

参照信号 $V_{ref}$ が比較器31の動作範囲を超えることについては、図9(A), (B)に示すように、参照信号 $V_{ref}$ の傾斜を上下逆にしても同じである。従って、比較器31の動作範囲の確保の問題については根本的に解決することはできない。図9において、(A)は低照度時、(B)は高照度時をそれぞれ示している。

10

## 【0086】

また、図10に示すように、比較器31に関して、NMOSトランジスタとPMOSトランジスタを入れ替えた回路構成を探る方法も考えられる。図10において、(A)はPMOS入力の比較器の構成例を、(B)はPMOS入力の比較器の動作範囲をそれぞれ示している。

20

## 【0087】

しかし、図10の回路構成は、CDS駆動の動作範囲を確保できず、CDS駆動を行うことができないことになる。比較器31として2種類、即ち、図5(A)に示す回路構成のもの、及び、図10(A)に示す回路構成のものの双方を用意して、DDS駆動とCDS駆動とで使い分ける方法も考えられる。この方法の場合には、CDS駆動用の回路と併せて回路規模が2倍になるため、コスト増を招くことと、2種類の異なる回路を用いるため特性のばらつきの問題が発生する。

20

## 【0088】

## [1-6. 第1実施形態の特徴とする事項]

そこで、第1実施形態では、単位画素11で得られるアナログ信号と傾斜状波形の参照信号 $V_{ref}$ とを比較する比較器31を有するAD変換回路23を備えたCMOSイメージセンサ10Aにおいて、次の構成を探ることを特徴とする。

## 【0089】

具体的には、先ず、単位画素11の信号を第1の信号及び第2の信号として2回に分けて読み出す際に、先に読み出される第1の信号を、第1, 第2の信号を処理する信号処理部の処理可能な入力電圧範囲の基準電圧として用いる。本実施形態の場合は、AD変換回路23が、第1, 第2の信号を処理する信号処理部に相当する。また、基準電圧は、AD変換回路23の変換可能な入力電圧範囲の基準となる電圧となる。本実施形態では、比較器31の動作範囲がAD変換回路23の入力電圧範囲ということになる。

30

## 【0090】

このとき、第1の信号がFD部42に蓄積、もしくは、保持された信号電荷に基づく信号、即ち、信号レベル $V_{sig}$ である場合には、当該信号レベル $V_{sig}$ を基準電圧として用いることになる。また、第1の信号がFD部42をリセットしたときのリセット電位 $V_r$ に基づく信号、即ち、リセットレベル $V_{rst}$ である場合には、当該リセットレベル $V_{rst}$ を基準電圧として用いることになる。そして、先に読み出される第1の信号をAD変換回路23の基準電圧として用いた上で、第1, 第2の信号がAD変換回路23の入力電圧範囲内に入るようAD変換回路23の内部の基準電圧、即ち、トランジスタ51, 52のゲート電圧 $V_{outi}, V_{refi}$ の初期値を調整した状態で第1, 第2の信号に対してAD変換処理を施すようとする。

40

## 【0091】

このように、第1, 第2の信号がAD変換回路23の入力電圧範囲内に入るように調整することで、AD変換回路23は、第1, 第2の信号が入力電圧範囲内に入った状態でこれら第1, 第2の信号に対してAD変換処理を実行することが可能になる。従って、先に読み出される第1の信号が信号レベル $V_{sig}$ の場合、リセットレベル $V_{rst}$ の場合のいずれ

50

の場合にも、処理対象の画素の信号を用いて基準電圧を設定した上で、第1，第2の信号に対して確実にA/D変換処理を施すことができるようになる。

#### 【0092】

これにより、特許文献5に記載の従来技術、即ち、別途外部で生成した所定電圧を用いて基準電圧を設定する場合のような、面内の大きな特性の揺らぎ（面内分布）の差異や、寄生容量の大きさに依存したオフセット成分を効果的に除去できる。その結果、画素の出力振幅に対して、A/D変換回路23の変換可能な入力電圧範囲に必要なマージンを低減することができる。そして、当該入力電圧範囲に必要なマージンを低減できることにより、A/D変換回路23の電源電圧の低電圧化や低消費電力化を図ることができる。

#### 【0093】

##### （実施例1）

以下に、具体的な実施例について説明する。前にも述べたように、CDS駆動では、先ず、FD部42に保持、もしくは、蓄積されている信号電荷を信号レベル $V_{sig}$ として読み出す駆動が行われる。次いで、FD部42をリセット電位 $V_r$ にリセットして当該リセット電位 $V_r$ をリセットレベル $V_{rst}$ として読み出す駆動が行われる。そして、単位画素11から先に読み出される信号レベル $V_{sig}$ を、A/D変換回路23の変換可能な入力電圧範囲の基準となる基準電圧として用いる。換言すれば、先に読み出される信号レベル $V_{sig}$ を用いてA/D変換回路23の内部の基準電圧 $V_{outi}$ ,  $V_{refi}$ を設定する。

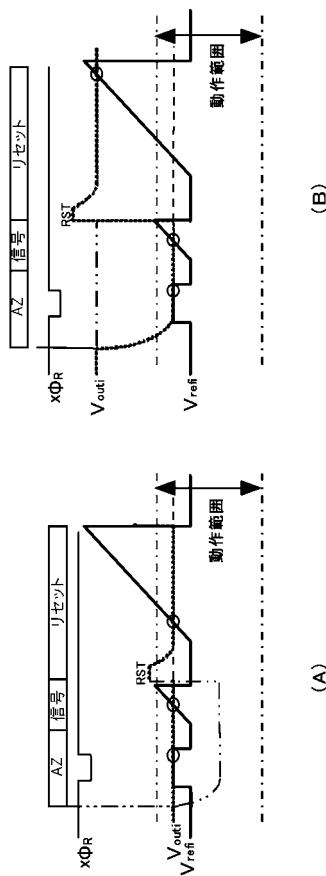

#### 【0094】

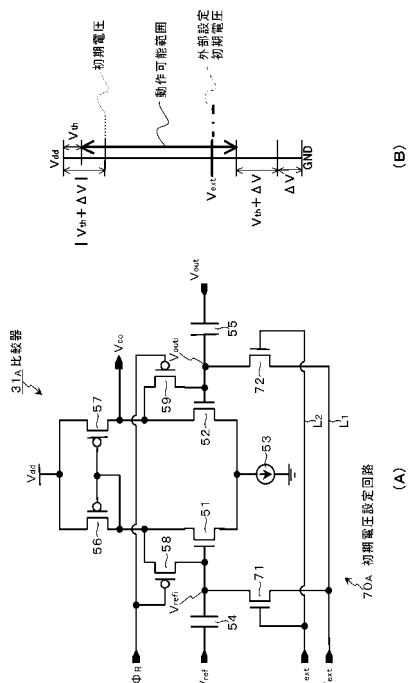

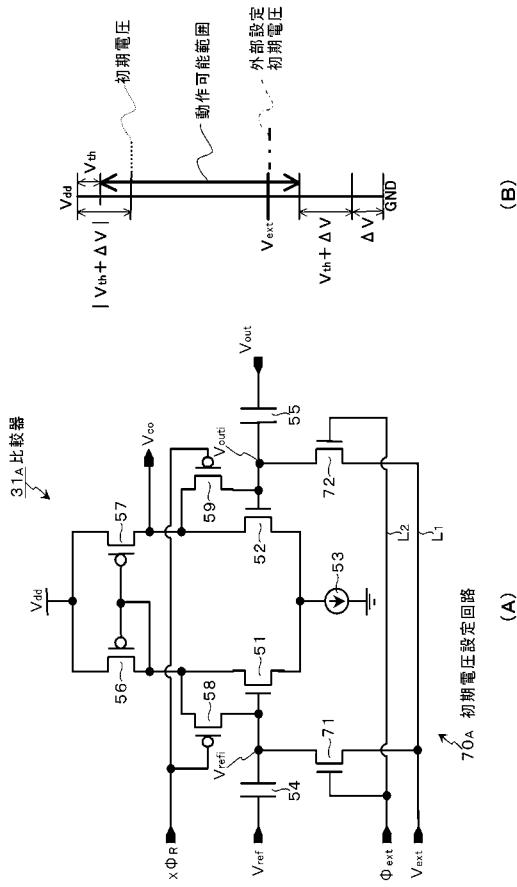

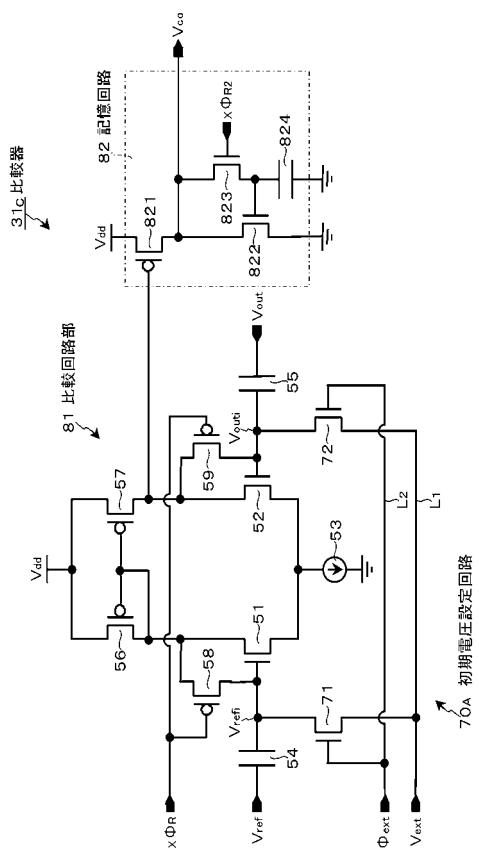

図11は、A/D変換回路23の内部の基準電圧 $V_{outi}$ ,  $V_{refi}$ を調整する機能を備えた、実施例1に係る比較器についての説明図であり、(A)は当該比較器の構成例を、(B)は当該比較器の動作範囲をそれぞれ示している。図11において、図5と同等部位には同一符号を付して示している。

#### 【0095】

図11(A)に示すように、実施例1に係る比較器31Aは、NMOSトランジスタ51, 52, 56, 57、PMOSトランジスタ58, 59、電流源53、及び、容量54, 55に加えて、A/D変換回路23の内部の基準電圧 $V_{outi}$ ,  $V_{refi}$ を設定(調整)するための初期電圧設定回路70Aを有する構成となっている。

#### 【0096】

初期電圧設定回路70Aは、外部で設定される外部設定初期電圧 $V_{ext}$ が与えられるライン $L_1$ とNMOSトランジスタ51, 52の各ゲート電極との間に接続されたNMOSトランジスタ71, 72によって構成されている。NMOSトランジスタ71, 72の各ゲート電極には、制御ライン $L_2$ を介して制御信号 $x_{ext}$ が与えられる。この制御信号 $x_{ext}$ は、例えば、図1に示すタイミング制御部18から与えられる。すなわち、タイミング制御部18は、初期電圧設定回路70Aを制御する制御部としての機能を持っている。

#### 【0097】

上記構成の比較器31Aにおいて、CDS駆動時は、A/D変換回路23の内部の基準電圧 $V_{outi}$ ,  $V_{refi}$ として、制御信号 $x_R$ の反転信号 $x_{\bar{R}}$ に応答してPMOSトランジスタ58, 59が導通状態になることによって設定される初期電圧がNMOSトランジスタ51, 52のゲート側に保持される。このCDS駆動時の初期電圧、即ち、A/D変換回路23の基準電圧は、MOSトランジスタの閾値電圧を $V_{th}$ 、単位画素11のリセットレベル $V_{rst}$ と信号レベル $V_{sig}$ との電位差を $V$ とすると、略 $(V_{dd} - |V_{th} + V|)$ となる。

#### 【0098】

DDS駆動時は、制御信号 $x_{ext}$ に応答してNMOSトランジスタ71, 72が導通状態になることで、外部設定初期電圧 $V_{ext}$ がNMOSトランジスタ51, 52のゲート電極に与えられる。この外部設定初期電圧 $V_{ext}$ により、比較器31Aの動作範囲が傾斜状波形の参照信号 $V_{ref}$ のスロープの範囲内に入り、当該スロープ内で比較器31Aが動作可能のように、A/D変換回路23の内部の基準電圧 $V_{outi}$ ,  $V_{refi}$ の調整が行われる。

#### 【0099】

10

20

30

40

50

このように、DDS 駆動時において、初期電圧設定回路  $70_A$  の作用により、信号レベル  $V_{sig}$  及びリセットレベル  $V_{rst}$  が AD 変換回路 23 の入力電圧範囲内に入るよう内部の基準電圧  $V_{outi}$ ,  $V_{refi}$  を調整することで、CDS 駆動と DDS 駆動との両立が可能になる。ここで、信号レベル  $V_{sig}$  及びリセットレベル  $V_{rst}$  が AD 変換回路 23 の入力電圧範囲内に入るということは、比較器  $31_A$  の動作範囲が AD 変換回路 23 の変換可能な入力電圧範囲内に入るということである。

#### 【0100】

また、基準電圧  $V_{outi}$ ,  $V_{refi}$  を設定するための初期電圧設定回路  $70_A$  としては、2つのN MOSトランジスタ 71, 72を追加するだけの非常に簡単な回路構成で実現できる。従って、比較器  $31_A$  個々としては、僅かなレイアウト面積の増加で済む。すなわち、CDS 駆動と DDS 駆動との両立を、比較器  $31_A$  のレイアウト面積を僅かに増加するだけで実現できる。

10

#### 【0101】

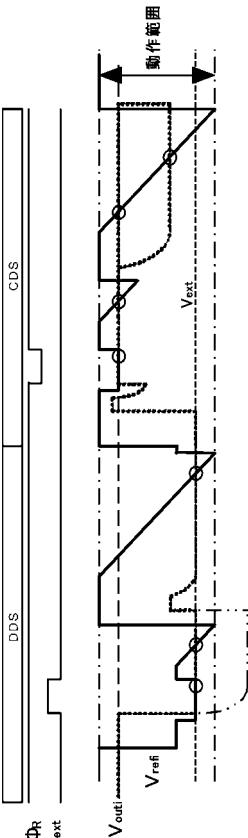

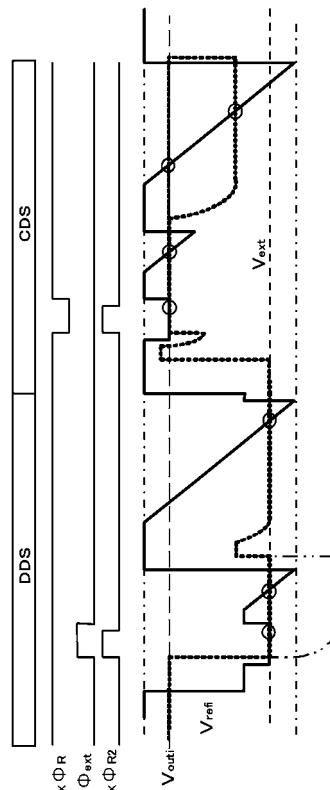

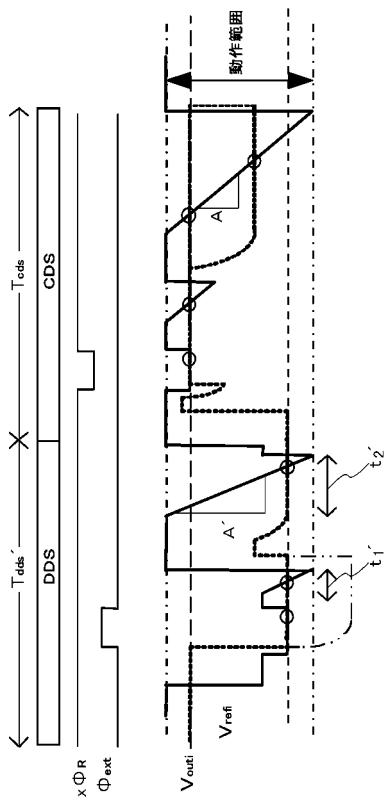

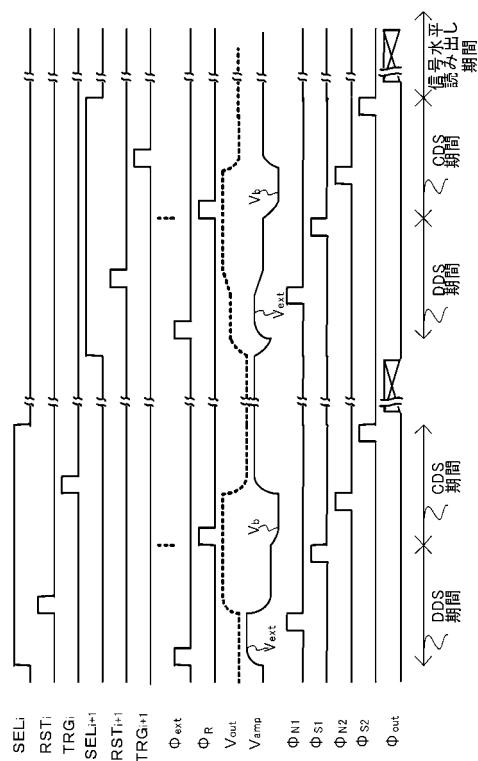

ここで、DDS 駆動と CDS 駆動とを 1 行の読み出し期間中に交互に行う場合の動作について説明する。図 12 及び図 13 に、DDS 駆動と CDS 駆動とを交互に行う場合の、DDS 駆動の際の低照度時、高照度時の場合の駆動波形をそれぞれ示す。図 12 及び図 13 には、制御信号  $x_R$ 、制御信号  $ext$ 、傾斜状波形の参照信号  $V_{ref}$ 、及び、単位画素 11 から列信号線 22 を介して与えられる信号電圧  $V_{out}$  の波形がそれぞれ示されている。

20

#### 【0102】

ここでは、参照信号  $V_{ref}$  について、電圧の時間変化方向が高い側から低い側の場合を例として挙げているが、図 9 に示すように、電圧の時間変化方向が逆、即ち、低い側から高い側であっても、比較器  $31_A$  の動作範囲内であれば、本実施形態の DDS 駆動を制限するものではない。また、図 10 に示すように、PMOS 入力で構成した比較器の場合は、初期電圧設定回路  $70_A$  については、図 14 に示すように、PMOS トランジスタ 73, 74 によって構成するようにすればよい。

30

#### 【0103】

続いて、図 11 に示す実施例 1 に係る比較器  $31_A$  の回路動作について、図 1、図 2、及び、図 5 を参照しつつ図 15 のタイミング波形図を用いて説明する。

#### 【0104】

先ず、選択信号  $SEL_i$  に応答して、選択トランジスタ 46 が導通状態になることにより、 $i$  番目 ( $i$  行目) の単位画素 11 の選択が行われる。そのとき、FD 部 42 には信号電荷が保持、もしくは、蓄積されている状態にあるものとする。この FD 部 42 の信号電荷に基づく信号レベル  $V_{sig}$  を比較器  $31_A$  の動作範囲内で検出するために、制御信号  $ext$  がアクティブ状態 (高電位の状態) になる。これにより、初期電圧設定回路  $70_A$  が動作状態となる。

30

#### 【0105】

初期電圧設定回路  $70_A$  が動作する、即ち、N MOS トランジスタ 71, 72 が導通状態になることで、外部設定初期電圧  $V_{ext}$  が N MOS トランジスタ 51, 52 に各ゲート電圧  $V_{outi}$ ,  $V_{refi}$  として印加される。これにより、比較器  $31_A$  の入力側の電位が、当該比較器  $31_A$  の動作範囲内で信号レベル  $V_{sig}$  を取得可能なように、PMOS トランジスタ 58, 59 によって設定される電位よりも低い電位に設定される。この初期電圧設定回路  $70_A$  による動作が、信号レベル  $V_{sig}$  及びリセットレベル  $V_{rst}$  が比較器  $31_A$  の動作範囲内、即ち、AD 変換回路 23 の入力電圧範囲内に入るように基準電圧  $V_{outi}$ ,  $V_{refi}$  を調整する動作である。

40

#### 【0106】

このとき、タイミング制御部 18 による制御の下に、参照信号生成部 15 で生成される傾斜状の参照信号  $V_{ref}$  の初期値も、比較器  $31_A$  の入力側電位に対応した低い電位に設定 (シフト) される。そして、制御信号  $ext$  が非アクティブ状態 (低電位の状態) になると、比較器  $31_A$  の入力側の電位、即ち、AD 変換回路 23 の変換可能な入力電圧範囲

50

の基準電圧を調整する動作が完了する。

#### 【0107】

この後、タイミング制御部18による制御の下に、参照信号生成部15において、参照信号 $V_{ref}$ を初期状態から、回路のばらつきマージンの取れる範囲で電位をわずかに持ち上げ、スロープ状(傾斜状)に電圧降下させる動作を開始する。そして、比較器31Aの入力電圧間、即ち、単位画素11から読み出された信号レベル $V_{sig}$ と参照信号 $V_{ref}$ との差分が0になったところで比較器31Aの比較出力 $V_{co}$ が反転する。

#### 【0108】

一方、アップ/ダウンカウンタ32は、参照信号 $V_{ref}$ のスロープ開始から例えばアップカウントを開始しており、比較器31Aの比較出力 $V_{co}$ の反転を受けて、アップカウントを終了する。すなわち、アップ/ダウンカウンタ32は、スロープ開始時点から比較出力 $V_{co}$ の反転時点までの時間をアップカウントする。このアップカウント動作により、AD変換回路23の基準電圧に対する信号レベル $V_{sig}$ の差を取得することができる。

10

#### 【0109】

次いで、i番目の単位画素11をリセットパルスRST<sub>i</sub>にてリセットし、FD部42を初期化する。このとき、リセット前の信号レベル $V_{sig}$ が低ければ、即ち、高輝度であれば、リセット後のFD部42の電位は大きく上昇する。併せて、参照信号 $V_{ref}$ も最大輝度時の信号量であってもスロープがかかるように上昇させる。このとき、アップ/ダウンカウンタ32は、参照信号 $V_{ref}$ のスロープ開始からダウンカウントを行う。そして、比較器31Aの比較出力 $V_{co}$ の反転を受けて、ダウンカウントを終了する。

20

#### 【0110】

このように、アップ/ダウンカウンタ32のカウント動作を1回目に例えばアップカウント動作とし、2回目に逆方向のダウンカウント動作とすることにより、当該アップ/ダウンカウンタ32内で自動的に(1回目の比較期間)-(2回目の比較期間)の減算処理が行われる。そして、参照信号 $V_{ref}$ と列信号線22<sub>-1</sub>～22<sub>-m</sub>の信号電圧 $V_{out}$ とが等しくなったときに比較器31の比較出力 $V_{co}$ が極性反転し、この極性反転を受けてアップ/ダウンカウンタ32のカウント動作が停止する。その結果、アップ/ダウンカウンタ32には、(1回目の比較期間)-(2回目の比較期間)の減算処理の結果に応じたカウント値が保持される。

30

#### 【0111】

(1回目の比較期間)-(2回目の比較期間)=(信号レベル $V_{sig\_i}$ +リセットレベル $V_{rst}$ )-(リセットレベル $V_{rst}$ )=(正味の信号レベル $V_{sig}$ )である。以上の2回の読み出し動作とアップ/ダウンカウンタ32での減算処理により、単位画素11毎のばらつきを含んだリセットレベル $V_{rst}$ が除去されるため、単位画素11毎の入射光量に応じた信号レベル $V_{sig}$ を取り出すことができる。なお、この信号レベル $V_{sig}$ は、限られた照度でより高いダイナミックレンジがとれるよう、外部電圧 $V_{ref}$ のスロープ状の傾きや、信号レベルとリセットレベル間の $V_{ref}$ 電圧のシフト量とで調整される。

#### 【0112】

続いて、CDS駆動に移行する。CDS駆動では、比較器31Aの入出力を制御信号<sub>R</sub>にて初期化する。この初期化動作により、単位画素11から先に読み出されるリセットレベル $V_{rst}$ を基にAD変換回路23の基準電圧を取得し、容量54,55に保持する。そして、参照信号生成部15において、参照信号 $V_{ref}$ を比較器31Aの動作範囲内で持ち上げてスロープを開始する。

40

#### 【0113】

このとき、参照信号 $V_{ref}$ のスロープ開始時点から比較器31Aの比較出力 $V_{co}$ の反転時点までの時間を、アップ/ダウンカウンタ32にてダウンカウントする。参照信号 $V_{ref}$ の電圧をスロープ開始位置まで戻し、単位画素11内の転送トランジスタ43を導通状態にすることで、フォトダイオード41に蓄積された信号電荷を読み出す。このとき、フォトダイオード41から読み出された信号電荷の電荷量に応じて列信号線22の電位が変化する。この列信号線22の電位は高照度になるほど降下する。

50

## 【0114】

参照信号生成部15において、比較器31<sub>A</sub>の動作範囲内で、かつ、単位画素11から読み出される信号をカバーするスロープの参照信号V<sub>ref</sub>の生成を開始する。そして、参照信号V<sub>ref</sub>のスロープ開始時点から比較器31<sub>A</sub>の比較出力V<sub>co</sub>の反転時点までの時間を、アップ／ダウンカウンタ32にてアップカウントする。このアップカウント動作により、FD部42のリセットレベルV<sub>rst</sub>と、フォトダイオード41からの信号電荷の転送後の信号レベルV<sub>sig</sub>との差が検出可能となる。

## 【0115】

ここで、アップ／ダウンカウンタ32のカウント結果の外部への読み出しについては、D DS駆動、C DS駆動で個別にカウントし、メモリ装置34に記憶し外部へ出力してもよいし、連続してカウントしてからメモリ装置34に記憶し外部へ出力してもよい。

10

## 【0116】

また、参照信号V<sub>ref</sub>のスロープの傾きを変化させることにより、比較器31<sub>A</sub>の比較出力V<sub>co</sub>が反転するまでの時間を変化させてゲインをかけることが可能である。このとき、D DS駆動とC DS駆動でスロープの傾きを変え、カウントするときのカウント値に、ゲイン倍の重みをつけてカウントする手法を探ることも可能である。

## 【0117】

また、通常必要とされているC DS駆動の開始時のリセット動作については、電荷検出部であるFD部42がリセットされた直後であるので、再度リセットは必要ないために省いている。但し、暗電流など、FD部42に対する外乱が大きい場合は、D DS駆動とC DS駆動の間でリセット動作をもう一度入れて再初期化することが好ましい。

20

## 【0118】

更に、参照信号生成部15で生成される参照信号V<sub>ref</sub>のスロープの方向についても、D DS駆動時とC DS駆動時とで傾き方向を逆にするなどの手法も考えられる。但し、C DS駆動の場合と動作起因の回路の特性ずれが発生しないように、D DS駆動時とC DS駆動時とでスロープの傾き方向と同じ方向にする方が好ましい。

## 【0119】

ところで、比較器31<sub>A</sub>において、初期設定を行うスイッチ素子であるMOSトランジスタ58, 59, 71, 72から入力部（差動対トランジスタ51, 52のゲート）にリーク電流に起因する電流が流れ込み、入力電位の上昇、もしくは、下降が発生する場合がある。このとき、比較器31<sub>A</sub>の両入力側でリーク量が同じであれば特性的には問題にならない。しかし、実デバイスにあっては、製造ばらつきなどによって比較器31<sub>A</sub>の両入力側のリーク量のバランスが崩れてしまうことがある。

30

## 【0120】

この問題については、MOSトランジスタ58, 59, 71, 72のチャネル長Lを長くすることで、これらトランジスタのリーク電流を抑えることができるため解決可能である。しかしながら、チャネル長Lを長くすると、MOSトランジスタ58, 59, 71, 72が非導通状態になるときに発生するクロックフィードスルーとチャージインジェクションが増加し、比較器31<sub>A</sub>の特性を劣化させてしまう懸念がある。

## 【0121】

ここで、クロックフィードスルーとは、クロック制御ノードとフローティングノードとの容量比による電圧降下の減少を言う。また、チャージインジェクションとは、MOSトランジスタ58, 59, 71, 72のチャネル直下の電荷のフローティングノードへの飛び込みを言う。クロックフィードスルー及びチャージインジェクションの量は、MOSトランジスタ58, 59, 71, 72の面積に比例する。従って、MOSトランジスタ58, 59, 71, 72のチャネル長Lを長くすると、必然的に、クロックフィードスルー及びチャージインジェクションが大きくなってしまう。

40

## 【0122】

このような理由から、MOSトランジスタ58, 59, 71, 72のリーク電流に起因する、入力電位の上昇、もしくは、下降の問題を解決するために、単純に、これらMOS

50

トランジスタのチャネル長 L を長くすることはできない。そこで、チャネル長 L を長くすることなく、上記の問題を解決するために為されたのが以下に説明する実施例 2 に係る比較器である。

#### 【0123】

##### (実施例 2 )

図 16 は、A/D 変換回路 23 の内部の基準電圧  $V_{outi}$ ,  $V_{refi}$  を調整する機能を備えた、実施例 2 に係る比較器の構成例を示す回路図であり、図中、図 11 と同等部位には同一符号を付して示している。

#### 【0124】

図 11 と図 16 との対比から明らかなように、実施例 2 に係る比較器 31B は、初期設定を行うスイッチ素子に関して、実施例 1 に係る比較器 31A と構成を異にしている。具体的には、実施例 1 に係る比較器 31A は、初期設定を行うスイッチ素子が単一の MOS トランジスタ 58, 59, 71, 72 によって構成されている。

#### 【0125】

これに対し、実施例 2 に係る比較器 31B は、MOS トランジスタ 58 に代えて直列に接続された 2 つの MOS トランジスタ 58A, 58B を用い、MOS トランジスタ 59 に代えて直列に接続された 2 つの MOS トランジスタ 59A, 59B を用いた構成を探っている。同様に、MOS トランジスタ 71 に代えて直列に接続された 2 つの MOS トランジスタ 71A, 71B を用い、MOS トランジスタ 72 に代えて直列に接続された 2 つの MOS トランジスタ 72A, 72B を用いている。

#### 【0126】

2 つの MOS トランジスタ 58A, 58B は、MOS トランジスタ 58 に比べてチャネル長 L が 1/2 のトランジスタであり、2 つの MOS トランジスタ 59A, 59B は、MOS トランジスタ 59 に比べてチャネル長 L が 1/2 倍のトランジスタである。同様に、2 つの MOS トランジスタ 71A, 71B は、MOS トランジスタ 71 に比べてチャネル長 L が 1/2 のトランジスタであり、2 つの MOS トランジスタ 72A, 72B は、MOS トランジスタ 72 に比べてチャネル長 L が 1/2 倍のトランジスタである。

#### 【0127】

尚、ここでは、直列に接続する MOS トランジスタの個数を 2 つとしているが、その個数は 2 つに限られるものではなく、3 つ以上の MOS トランジスタを直列に接続する構成であっても良い。

#### 【0128】

MOS トランジスタ 58A, 59A の各ゲート電極には制御信号  $x_R$  が印加され、MOS トランジスタ 58B, 59B の各ゲート電極には制御信号  $x_R$  よりも非アクティブ（本例では、高レベル）になるタイミングが遅い制御信号  $x_{RIk}$  が印加される。また、MOS トランジスタ 71A, 72A の各ゲート電極には制御信号  $x_{ext}$  が印加され、MOS トランジスタ 71B, 72B の各ゲート電極には制御信号  $x_{ext}$  よりも非アクティブ（本例では、低レベル）になるタイミングが遅い制御信号  $x_{extlk}$  が印加される。

#### 【0129】

図 17 に、実施例 2 に係る比較器 31B における制御信号  $x_R$ 、制御信号  $x_{RIk}$ 、制御信号  $x_{ext}$ 、制御信号  $x_{extlk}$ 、傾斜状波形の参照信号  $V_{ref}$ 、及び、信号電圧  $V_{out}$  の各タイミング波形を示す。

#### 【0130】

制御信号  $x_R$  が非アクティブ状態になり、次いで、制御信号  $x_{RIk}$  が非アクティブ状態になることで、比較器 31B の入力側の MOS トランジスタ 58A, 59A が先ず非導通状態になり、次いで、MOS トランジスタ 58B, 59B が非導通状態になる。同様にして、制御信号  $x_{ext}$  が非アクティブ状態になり、次いで、制御信号  $x_{extlk}$  が非アクティブ状態になることで、比較器 31B の入力側の MOS トランジスタ 71A, 72A が先ず非導通状態になり、次いで、MOS トランジスタ 71B, 72B が非導通状態になる。

#### 【0131】

10

20

30

40

50

ここで、初期設定を行うスイッチ素子として、直列に接続された複数、例えば2つのMOSトランジスタを用いることによる作用、効果、即ち、実施例2に係る比較器31<sub>B</sub>の作用、効果について説明する。

#### 【0132】

先ず、初期設定を行うスイッチ素子として単一のMOSトランジスタを用いる場合（実施例1の場合）について、図18（A），（B）を用いて説明する。チャネル長がLのMOSトランジスタにおいて、当該MOSトランジスタが導通状態（A）でチャネルに電荷Q<sub>ch</sub>が存在しているものとする。この状態から、非導通状態（B）にすると、チャネル内の電荷Q<sub>ch</sub>がチャネルの両側のソース／ドレイン領域にほぼ2分割されて分配される。これにより、一方のソース／ドレイン領域に対するインジェクション量が（1/2）・Q<sub>ch</sub>となる。10

#### 【0133】

これに対して、チャネル長が実施例1の場合の1/2倍のMOSトランジスタを2つ直列に接続することで、これら2つのMOSトランジスタが導通状態にあるとき（C）は、各チャネルには単一の場合の1/2の電荷、即ち、（1/2）・Q<sub>ch</sub>の電荷が存在することになる。

#### 【0134】

そして、これら2つのMOSトランジスタを順に非導通状態にする（D）ことで、先ず先に非導通状態になる一方のMOSトランジスタのチャネル内の電荷（1/2）・Q<sub>ch</sub>がチャネルの両側のソース／ドレイン領域にほぼ2分割されて分配される。これにより、一方のMOSトランジスタにおいて、一方のソース／ドレイン領域に対するインジェクション量が（1/4）・Q<sub>ch</sub>となる。後で導通状態になる他方のMOSトランジスタについても同様のことが言える。20

#### 【0135】

このように、例えば、チャネル長を1/2倍にすると、統計的に、インジェクション量がチャネル長Lのとき（（1/2）・Q<sub>ch</sub>）の1/2、即ち、（1/4）・Q<sub>ch</sub>となる。従って、チャネル長が実施例1の場合の1/2倍のMOSトランジスタを2つ直列に接続する構成を探ることで、比較器31<sub>B</sub>の2つの入力端に接続されるMOSトランジスタ58，59，71，72の各一方のソース／ドレイン領域へのインジェクション量を1/2にできる。その結果、インジェクション量に起因する、初期設定の値の変動を、実施例1の場合に比べて抑えることができる。30

#### 【0136】

尚、ここでは、チャネル長が実施例1の1/2倍のMOSトランジスタを2つ直列に接続するましたが、インジェクション量が実施例1と同程度で問題ない場合は、実施例1と同じチャネル長のMOSトランジスタを例えば2つ直列に接続する構成を探ることも可能である。この構成によれば、初期設定を行うスイッチ素子を構成するMOSトランジスタのトータルのチャネル長を2倍にできるため、トータルのトランジスタサイズは大きくなるものの、実施例1の場合に比べてリーク電流を抑制できる。

#### 【0137】

##### （実施例3）

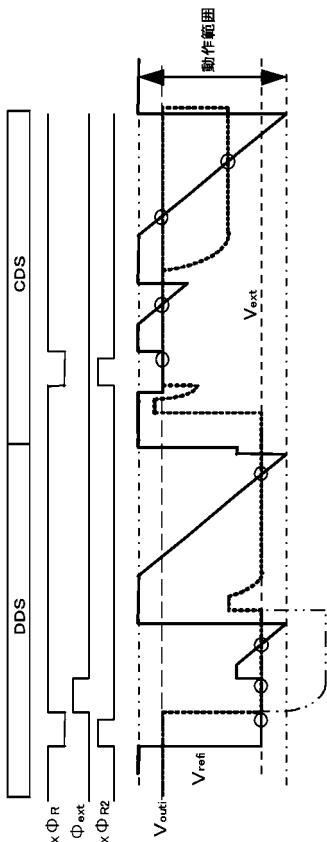

図19は、AD変換回路23の内部の基準電圧V<sub>outi</sub>，V<sub>refi</sub>を調整する機能を備えた、実施例3に係る比較器の構成例を示す回路図であり、図中、図11と同等部位には同一符号を付して示している。40

#### 【0138】

図19に示すように、実施例3に係る比較器31<sub>C</sub>は、前段の回路部と後段回路部との2段回路構成となっており、前段の回路部は、実施例1に係る比較器31<sub>A</sub>と同じ回路構成、即ち、比較回路部81となっている。尚、前段の回路部については、実施例1に係る比較器31<sub>A</sub>と同じ回路構成のものに限られるものではなく、実施例2に係る比較器31<sub>B</sub>と同じ回路構成とすることも可能である。

#### 【0139】

10

20

30

40

50

一方、後段の回路部は、前段の比較回路部 8 1 の出力電圧、即ち、PMOSトランジスタ 5 7 に流れる電流に応じた電圧によって決まる電流値に基づく（対応する）電圧値（バイアス電圧値）を記憶する記憶回路部 8 2 である。この記憶回路部 8 2 は、例えば、PMOSトランジスタ 8 2 1、NMOSトランジスタ 8 2 2, 8 2 3、及び、容量 8 2 4 によって構成されている。

#### 【0140】

PMOSトランジスタ 8 2 1 は、前段の比較回路部 8 1 の出力端、即ち、MOSトランジスタ 5 2, 5 7 のドレイン共通接続ノードにゲート電極が接続され、電源  $V_{dd}$  にソース電極が接続されている。NMOSトランジスタ 8 2 2 は、PMOSトランジスタ 8 2 1 のドレイン電極にドレイン電極が接続され、ソース電極が接地されている。

10

#### 【0141】

NMOSトランジスタ 8 2 3 は、PMOSトランジスタ 8 2 1 のドレイン電極にドレイン電極が接続され、NMOSトランジスタ 8 2 2 のゲート電極にソース電極が接続されている。容量 8 2 4 は、NMOSトランジスタ 8 2 2 のゲート電極に一端が接続され、他端が接地されている。そして、MOSトランジスタ 8 2 1, 8 2 2 のドレイン共通接続ノードが本比較器 3 1c の出力端となり、当該ドレイン共通接続ノードから比較出力  $V_{co}$  が導出される。

#### 【0142】

NMOSトランジスタ 8 2 3 のゲート電極には、制御信号  $x_{R2}$  が印加される。この制御信号  $x_{R2}$  は、例えば、図 1 に示すタイミング制御部 1 8 から与えられる。すなわち、タイミング制御部 1 8 は、実施例 3 に係る比較器 3 1c の後段の回路部、即ち、記憶回路部 8 2 を制御する制御部としての機能を持っている。

20

#### 【0143】

##### ・第 1 駆動例

次に、比較回路部 8 1 の後段に記憶回路部 8 2 を有する、実施例 3 に係る比較器 3 1c の第 1 駆動例について、図 2 0 のタイミング波形図を用いて説明する。図 2 0 には、制御信号  $x_R$ 、制御信号  $x_{extlk}$ 、制御信号  $x_{R2}$ 、傾斜状波形の参照信号  $V_{ref}$ 、及び、信号電圧  $V_{out}$  の各タイミング波形を示している。

#### 【0144】

先ず、CDS駆動時は、前段の比較回路部 8 1 において、制御信号  $x_R$  による制御の下に、PMOSトランジスタ 5 8, 5 9 が導通することによって設定される初期電圧が、内部の基準電圧  $V_{outi}$ ,  $V_{refi}$  として NMOSトランジスタ 5 1, 5 2 のゲート側に保持される。この初期設定状態において、制御信号  $x_{R2}$  による制御の下に、後段の記憶回路部 8 2 の NMOSトランジスタ 8 3 が導通状態となる。

30

#### 【0145】

後段の記憶回路部 8 2 において、NMOSトランジスタ 8 3 が導通状態となることで、前段の比較回路部 8 1 の初期設定値によって決まる出力電圧に応じた電流が MOSトランジスタ 8 2 1, 8 2 3 を通して容量 8 2 4 に流れる。そして、初期設定期間内において、制御信号  $x_{R2}$  による制御の下に、NMOSトランジスタ 8 3 が非導通状態になるタイミングで、比較回路部 8 1 の出力電圧の初期値によって決まる電流値に基づく電圧値が容量 8 2 4 に記憶（保持）される。

40

#### 【0146】

この容量 8 2 4 に記憶された電流値で後段の記憶回路部 8 2 の特性が決定される。後段の記憶回路部 8 2 の出力が反転するのは、比較回路部 8 1 の出力電流、即ち、PMOSトランジスタ 8 2 1 に流れる電流が容量 8 2 4 の保持電圧により発生する電流値を上回ったときとなる。

#### 【0147】

一方、DDS駆動時は、前段の比較回路部 8 1 において、制御信号  $x_{ext}$  による制御の下に、NMOSトランジスタ 7 1, 7 2 が導通状態になることで、外部設定初期電圧  $V_{ext}$  が NMOSトランジスタ 5 1, 5 2 のゲート電極に与えられる。また、制御信号  $x_{R2}$

50

による制御の下に、後段の記憶回路部 8 2 の N M O S トランジスタ 8 3 が導通状態となる。

#### 【 0 1 4 8 】

後段の記憶回路部 8 2において、N M O S トランジスタ 8 3 が導通状態となることで、外部設定初期電圧  $V_{ext}$  により入力が決定されたときの出力電圧に応じた電流がM O S トランジスタ 8 1 , 8 3 を通して容量 8 2 4 に流れる。そして、制御信号  $x_{R2}$  による制御の下に、N M O S トランジスタ 8 3 が非導通状態になるタイミングで、外部設定初期電圧  $V_{ext}$  によって決まる電流値に基づく電圧値が容量 8 2 4 に記憶（保持）される。

#### 【 0 1 4 9 】

上述したように、第 1 駆動例の場合は、C D S 駆動時、D D S 駆動時共に、初期設定のときの比較回路部 8 1 の出力電圧によって決まる電流値に基づく電圧値を記憶回路部 8 2 で記憶するようにしている。しかしながら、上述した動作説明から明らかのように、比較回路部 8 1 の C D S 駆動時における初期設定の出力電圧と、比較回路部 8 1 の D D S 駆動時における初期設定の出力電圧とに差が生じる。

10

#### 【 0 1 5 0 】

このように、C D S 駆動時とD D S 駆動時の初期設定の出力電圧に差が生じると、結果として、記憶回路部 8 2 が記憶する電圧値、即ち、記憶回路部 8 2 の出力が反転する電圧値がC D S 駆動時とD D S 駆動時で違ってくるため、比較器 3 1<sub>c</sub>として同じ動作点が得られなくなる。すなわち、C D S 駆動時とD D S 駆動時で比較器 3 1<sub>c</sub>の初期の動作点が変わってしまう。この点に鑑みて為されたのが、以下に説明する第 2 駆動例である。

20

#### 【 0 1 5 1 】

- ・第 2 駆動例

続いて、実施例 3 に係る比較器 3 1<sub>c</sub>の第 2 駆動例について、図 2 1 のタイミング波形図を用いて説明する。図 2 1 にも、図 2 0 と同様に、制御信号  $x_{R}$ 、制御信号  $x_{ext1k}$ 、制御信号  $x_{R2}$ 、傾斜状波形の参照信号  $V_{ref}$ 、及び、信号電圧  $V_{out}$  の各タイミング波形を示している。

20

#### 【 0 1 5 2 】

第 2 駆動例の場合、C D S 駆動時の動作については第 1 駆動例の場合と同じであり、D D S 駆動時の動作を特徴としている。すなわち、図 2 0 のタイミング波形図と図 2 1 のタイミング波形図との対比から明らかのように、D D S 駆動の際に、制御信号  $x_{ext}$  による制御に基づく外部設定初期電圧  $V_{ext}$  による初期設定を行う前に、C D S 駆動時と同じ初期設定の動作を行う構成を探っている。

30

#### 【 0 1 5 3 】

具体的には、外部設定初期電圧  $V_{ext}$  による初期設定に先立って、前段の比較回路部 8 1において、制御信号  $x_{R}$  による制御の下に、P M O S トランジスタ 5 8 , 5 9 が導通することによって設定される初期電圧を、内部の基準電圧  $V_{outi}$  ,  $V_{refi}$  として初期設定する。

#### 【 0 1 5 4 】

この初期設定状態において、制御信号  $x_{R2}$  による制御の下に、後段の記憶回路部 8 2 において、N M O S トランジスタ 8 2 3 が非導通状態になるタイミングで、比較回路部 8 1 の出力電圧の初期値によって決まる電流値に基づく電圧値を容量 8 2 4 に記憶（保持）する。このとき記憶する電圧値（電流値）は、C D S 駆動時の初期設定で記憶する電圧値（電流値）と同じである。これにより、C D S 駆動時とD D S 駆動時で比較器 3 1<sub>c</sub>の初期の動作点、即ち、両者の特性が揃うことになる。

40

#### 【 0 1 5 5 】

D D S 駆動の際には、C D S 駆動時と同じ初期設定を行った後、再度、外部設定初期電圧  $V_{ext}$  による初期設定を行うことで、信号レベル  $V_{sig}$  及びリセットレベル  $V_{rst}$  がA D 変換回路 2 3 の入力電圧範囲内に入るように内部の基準電圧  $V_{outi}$  ,  $V_{refi}$  を調整する。

#### 【 0 1 5 6 】

上述したように、D D S 駆動の際には、外部設定初期電圧  $V_{ext}$  による初期設定に先立

50

って、CDS駆動時と同じ初期設定を行い、しかる後再度本来の初期設定、即ち、外部設定初期電圧 $V_{ext}$ による初期設定を行うことで、第1駆動例の問題を解決することができる。すなわち、DDS駆動、CDS駆動の双方において、同じ初期設定を行うことにより両駆動時の出力の動作点の特性を揃えることができる。その結果、初期電圧設定回路70Aの作用による作用、効果に加えて、CDS駆動とDDS駆動とをより確実に両立できる、という作用、効果を得ることができる。

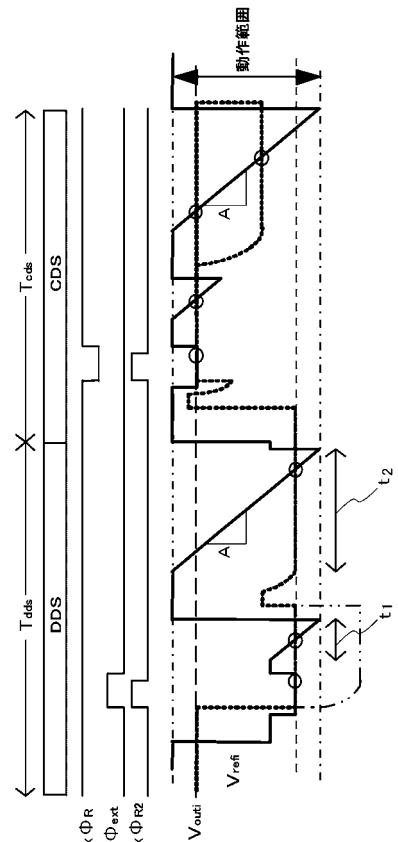

#### 【0157】

##### (駆動の高速化)

ところで、本実施形態に係るCMOSイメージセンサ10Aにおいては、単純に、CDS駆動とDDS駆動を交互に行うことで信号を取得する訳であるが、当然のことながら、信号の取得にはCDS駆動及びDDS駆動の時間分の時間を要することになる。具体的には、図22のタイミング波形図に示すように、DDS駆動の駆動時間を $T_{dds}$ 、CDS駆動の駆動時間を $T_{cds}$ とすると、CDS駆動及びDDS駆動で信号を取得する時間 $T_{total}$ は、 $T_{total} = T_{dds} + T_{cds}$ となる。この駆動例の場合は、AD変換の際に用いる傾斜状波形の参照信号 $V_{ref}$ のスロープ(傾斜)について、CDS駆動とDDS駆動で同じ勾配Aとなっている。

#### 【0158】

これに対して、傾斜状波形の参照信号 $V_{ref}$ に関して、CDS駆動及びDDS駆動のどちらか一方のスロープを他方のスロープに比べて急勾配にすることにより、AD変換に要する時間、ひいては、信号を取得するまでの時間を高速化できる。スロープを急勾配にした方の駆動によって得られるデータについては、後段の信号処理部において、高速化した分だけ、即ち、参照信号 $V_{ref}$ のスロープを急勾配にした分だけ係数(後述する)をかけることにより、入力換算で同じデータを取得するようにすれば良い。

#### 【0159】

一般的に、DDS駆動で取得する信号については、イメージセンサでは高輝度側の信号であることが多いために、DDS駆動側について、参照信号 $V_{ref}$ のスロープをCDS駆動側に比べて急勾配にするのが望ましい。

#### 【0160】

図23に、参照信号 $V_{ref}$ のスロープについてDDS駆動側をCDS駆動側(勾配A)に比べて急勾配A'にした場合のタイミング波形を示す。DDS駆動側を急勾配A'にすることで、AD変換に要する時間は、 $T_{dds}' + T_{cds}$ となる。ここで、 $T_{dds}' = T_{dds} - (t_1 - t_1') - (t_2 - t_2')$ の時間の短縮が見込まれる。そして、その短縮分だけ信号を取得するまでの時間を高速化できる。

#### 【0161】

高速化を図る図22の場合のDDS駆動時のスロープの傾き(勾配)をAとし、高速化を図った場合のDDS駆動時のスロープの傾きをA'としたとき、後段の信号処理部において用いる、先述した係数は、A'/Aとなる。すなわち、高速化した場合のDDS駆動で得られたデータに対してA'/Aなる係数をかけることで、高速化していない場合と同等の出力データを得ることが可能になる。尚、この係数をかける信号処理は、画素アレイ部12と同じチップ(半導体基板19)内、チップ外のどちらで行っても良く、特に制約は無い。

#### 【0162】

また、画素アレイ部12の全画素11に亘ってDDS駆動で取得する信号が無く、DDS動作自体が不要な信号レベルの場合、例えば、非常に暗い環境下での撮像の場合は、DDS駆動を止めてCDS駆動のみとすることによっても動作速度を向上させることができる。この場合、一例として、DDS駆動での出力データがゼロ出力と判定可能な出力結果がある一定時間連続していることを検出したら、その検出結果を受けてCDS駆動のみとする、といった制御が考えられる。

#### 【0163】

##### (カウンタの駆動法)

10

20

30

40

50

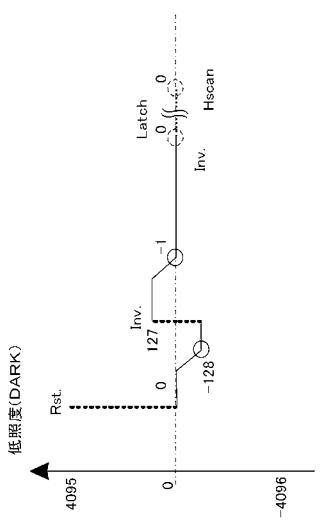

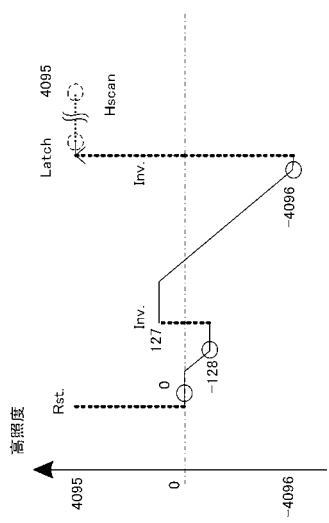

前にも述べたことから明らかなように、傾斜状波形の参照信号  $V_{ref}$  を用いる、所謂、スロープ型の A/D 変換回路 23 は、単調減少（または、単調増加）する傾斜状波形の参照信号  $V_{ref}$  と画素の信号電圧  $V_{out}$  とを比較する。そして、比較器 31 の出力が反転するまでの時間をクロック CK によってカウントし、比較器 31 の出力の反転タイミングでのカウント値を変換データとして記憶することで A/D 変換を実現している。

#### 【0164】

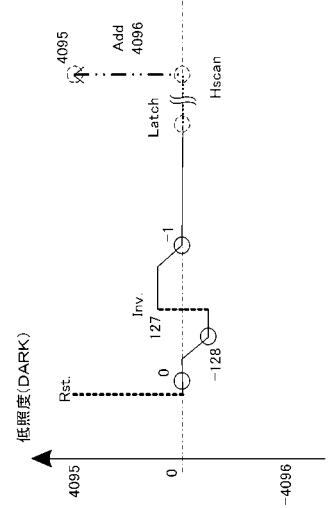

先述した実施形態の説明では、カラム A/D 変換回路のカウント部としてアップ / ダウンカウンタ 32 を用いるとしたが、例えば、カウント部が正負 12 ビットカウント可能な場合、CDS 駆動ではダウンカウントのカウンタを搭載するものとする。図 24 に、CDS 駆動時のカウンタ部の動作説明に供するタイミング波形を示す。CDS 駆動では、リセットレベル  $V_{RST}$  までの反転時刻  $t$  をダウンカウントし、カウント終了後 1 の補数を取ることで 0 を中心に正負を逆 -1 とした値にする。

10

#### 【0165】

次に、信号レベル  $V_{sig}$  についてもこの値を基準にダウンカウントを行う。もし、単位画素 11 の信号が低照度（DARK）で同じ電位レベルしか比較器 31 に入力されないと仮定すると、図 25 に示すように、カウント値 -1 でカウントが終了する。単位画素 11 の信号が高照度であった場合は、図 26 に示すように、-4096 までカウントする。最後に、このデータの 1 の補数を取得することで、低照度時は 0、高照度時は 4095 のデータを出力できることとなる。

20

#### 【0166】

しかしながら、同じ回路（カウンタ）を使用して DDS 駆動のデータを取得しようとすると、高照度側では、わずかのカウント後に比較器 31 の出力が反転するため、CDS 駆動時の低照度と同じレベルの信号が出力される。すなわち、DDS 駆動の高照度時は CDS 駆動の低照度に近いタイミングで反転し、DDS 駆動の低照度時は CDS 駆動の高照度時に近いタイミングで反転するために、同じ回路（カウンタ）を用いての入力信号とデータの整合性が取れることになる。

20

#### 【0167】

図 27 は、DDS 駆動時のカウンタ部の動作説明に供するタイミング波形図である。また、図 28 には、DDS 駆動の低照度時のカウント動作についての説明図を示し、図 29 には、DDS 駆動の高照度時のカウント動作についての説明図を示す。

30

#### 【0168】

カラム A/D 変換回路のカウント部において、同じ回路（カウンタ）を用いての入力信号とデータの整合性を取るために、DDS 駆動では、以下のような駆動を行うようとする。すなわち、DDS 駆動で取得した信号については、例えば列走査部 16 による走査で選択した後、外部に出力する前に 4096 のデータを加算して出力するようとする。

#### 【0169】

4096 のデータの加算処理については、画素アレイ部 12 と同じチップ（半導体基板 19）内で行っても良いし、チップ外部で演算処理の一環として行うようにしても良い。この加算処理回路については、DDS 駆動で取得した信号であるか否かを判別する回路部と、当該回路部の判別結果を受けて DDS 駆動時に加算処理を行う加算器とによって実現することが可能である。

40

#### 【0170】

このように、DDS 駆動では、DDS 駆動で取得した信号に対して、カウンタのビット数に対応したデータ、例えば 12 ビットの場合には 4096 のデータを加算することで、同じ回路（カウンタ）を用いての入力信号とデータの整合性を取ることができる。すなわち、CDS 駆動と DDS 駆動のデータの取得の際に、カラム A/D 変換回路のカウント部として同一の回路（カウンタ）を使用することが可能となる。

#### 【0171】

<2. 第 2 実施形態>

[2-1. システム構成]

50

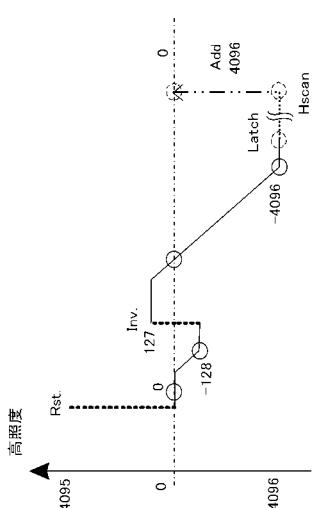

図30は、本開示の第2実施形態に係るCMOSイメージセンサの構成の概略を示すシステム構成図であり、図中、図1と同等部位には同一符号を付して示している。

#### 【0172】

図30に示すように、本実施形態に係るCMOSイメージセンサ10<sub>B</sub>は、画素アレイ部12に加えて、その周辺回路として、例えば、行走査部13、カラム処理部14<sub>B</sub>、参照信号生成部15、列走査部16、水平出力線17、及び、タイミング制御部18を有する。

#### 【0173】

CMOSイメージセンサ10<sub>B</sub>においては、カラム処理部14<sub>B</sub>が第1実施形態のカラム処理部14<sub>A</sub>と構成を異にしているだけであり、行走査部13、参照信号生成部15、列走査部16、水平出力線17、及び、タイミング制御部18については、基本的に、第1実施形態と同じである。10

#### 【0174】

カラム処理部14<sub>B</sub>は、例えば、画素アレイ部12の画素列毎、即ち、列信号線22(22<sub>.1</sub>~22<sub>.m</sub>)毎に1対1の対応関係をもって設けられたカラムアンプ回路25(25<sub>.1</sub>~25<sub>.m</sub>)を有する。カラムアンプ回路25(25<sub>.1</sub>~25<sub>.m</sub>)は、画素アレイ部12の各単位画素11から列毎に出力されるアナログ信号に対して増幅処理を行うとともに、信号レベルとリセットレベルとの差分をとる相関二重サンプリング処理を行う。

#### 【0175】

カラムアンプ回路25<sub>.1</sub>~25<sub>.m</sub>は全て同じ構成となっている。ここでは、m列目のカラムアンプ回路25<sub>.m</sub>を例に挙げて説明するものとする。カラムアンプ回路25<sub>.m</sub>は、反転増幅器61、入力容量62、帰還容量63、制御スイッチ64、及び、水平選択スイッチ65を有する構成となっている。そして、カラムアンプ回路25<sub>.m</sub>は、列信号線22<sub>.m</sub>を介して単位画素11から供給される信号電圧V<sub>out</sub>を増幅してアナログ信号V<sub>amp</sub>として出力する。20

#### 【0176】

尚、本例では、カラム処理部14<sub>B</sub>について、カラムアンプ回路25が列信号線22毎に1対1の対応関係をもって設けられた構成を例に挙げたが、1対1の対応関係の配置に限られるものではない。例えば、1つのカラムアンプ回路25を複数の画素列で共有し、複数の画素列間で時分割にて使用する構成とすることも可能である。30

#### 【0177】

##### (カラムアンプ回路の従来構成について)

信号処理部として、列並列に配置されたカラムアンプ回路25を用いる従来のCMOSイメージセンサは、CDS駆動を基本としている。すなわち、単位画素11から先にリセットレベルV<sub>rst</sub>を読み出し、次いで、信号レベルV<sub>sig</sub>が読み出すCDS駆動を基本としている。ここで、この従来例に係るCMOSイメージセンサに用いられるカラムアンプ回路の構成例について説明する

#### 【0178】

図31は、カラムアンプ回路25の従来構成を示す回路図である。図32に、従来構成に係るカラムアンプ回路25の出力信号の動作範囲を示す。40

#### 【0179】

図31に示すように、従来構成に係るカラムアンプ回路25は、反転増幅器61、入力容量62、帰還容量63、及び、制御スイッチ64を有する構成となっている。このカラムアンプ回路25においても、AD変換回路23の場合と同様に、制御信号<sub>R</sub>による制御の下に、制御スイッチ64によって反転増幅器61の入出力端間を短絡することで、カラムアンプ回路25の基準電圧を取得する。

#### 【0180】

CDS動作では、リセットレベルV<sub>rst</sub>、信号レベルV<sub>sig</sub>の順に読み出されるが、電位的には、高い電位~低い電位となる。カラムアンプ回路25において、初期値として、出力電圧は低く設定し、入力信号が低くなる場合、即ち、単位画素11からの信号レベルが

大きくなる場合、低い初期出力電圧が入力容量  $C_{in}$  と帰還容量  $C_{fb}$  の容量比で増幅される。具体的には、入力容量  $C_{in}$  の容量値を  $C_{in}$ 、帰還容量  $C_{fb}$  の容量値を  $C_{fb}$  とすると、容量比  $C_{in} / C_{fb}$  で増幅される。

#### 【0181】

制御信号  $V_R$  による制御の下に、制御スイッチ 64 によって反転増幅器 61 の入出力端間を短絡したときの初期電圧（基準電圧）を  $V_b$  とすると、カラムアンプ回路 25 の出力電圧  $V_{amp}$  は、

$$V_{amp} = V_b + (C_{in} / C_{fb}) \cdot V$$

となる。ここで、 $V$  はリセットレベル  $V_{rst}$  と信号レベル  $V_{sig}$  の電位差である。カラムアンプ回路 25 の出力動作範囲は、反転増幅器 61 の入出力端間を短絡したときの初期電圧  $V_b$  に対して閾値電圧程度低い電圧から、カラムアンプ回路 25 の回路構成で決まる上部の動作範囲までとなる。

10

#### 【0182】

この従来構成に係るカラムアンプ回路 25 を用いた CMOS イメージセンサで DDS 駆動を行った場合の、カラムアンプ回路 25 の出力波形を図 33 に示す。

#### 【0183】

DDS 駆動では、信号出力順が DDS 駆動の場合と逆である、即ち、信号レベル  $V_{sig}$  リセットレベル  $V_{rst}$  の順に出力される。従って、カラムアンプ回路 25 の出力信号は、低い初期電圧の電圧値から更に低くなるため、回路の動作範囲を外れてしまう。これを解決するために、第 2 実施形態では以下の構成を探っている。

20

#### 【0184】

##### [2-2. 第 2 実施形態の特徴とする事項]

すなわち、第 2 実施形態では、単位画素 11 からのアナログ信号に対して増幅処理を行うとともに、信号レベル  $V_{sig}$  とリセットレベル  $V_{rst}$  との差分をとる相関二重サンプリング処理を行うカラムアンプ回路 25 を用いた CMOS イメージセンサ 10B において、次の構成を探ることを特徴とする。

#### 【0185】

具体的には、先ず、単位画素 11 の信号を第 1 の信号及び第 2 の信号として 2 回に分けて読み出す際に、先に読み出される第 1 の信号を、第 1 , 第 2 の信号を処理する信号処理部の処理可能な入力電圧範囲の基準電圧として用いる。本実施形態の場合は、カラムアンプ回路 25 が、第 1 , 第 2 の信号を処理する信号処理部に相当する。また、基準電圧は、カラムアンプ回路 25 の増幅可能な入力電圧範囲の基準となる電圧となる。

30

#### 【0186】

このとき、第 1 の信号が FD 部 42 に蓄積、もしくは、保持された信号電荷に基づく信号、即ち、信号レベル  $V_{sig}$  である場合は、当該信号レベルを基準電圧として用いることになる。また、第 1 の信号が FD 部 42 をリセットしたときのリセット電位  $V_r$  に基づく信号、即ち、リセットレベル  $V_{rst}$  である場合は、当該リセットレベルを基準電圧として用いることになる。そして、先に読み出される第 1 の信号をカラムアンプ回路 25 の基準電圧として用いた上で、第 1 , 第 2 の信号がカラムアンプ回路 25 の入力電圧範囲内に入るように基準電圧を調整した状態で第 1 , 第 2 の信号に対して増幅処理を施すようとする。

40

#### 【0187】

このように、第 1 , 第 2 の信号がカラムアンプ回路 25 の入力電圧範囲内に入るように基準電圧を調整することで、カラムアンプ回路 25 は、第 1 , 第 2 の信号が入力電圧範囲内に入った状態でこれら第 1 , 第 2 の信号に対して増幅処理を施すことが可能になる。従って、先に読み出される第 1 の信号が信号レベル  $V_{sig}$  の場合、リセットレベル  $V_{rst}$  の場合のいずれの場合にも、処理対象の画素の信号を用いて基準電圧を設定した上で、第 1 , 第 2 の信号に対して確実に信号増幅処理を施すことができるようになる。

#### 【0188】

これにより、特許文献 5 に記載の従来技術、即ち、別途外部で生成した所定電圧を用い

50

て基準電圧を設定する場合のような、面内の大きな特性の揺らぎの差異や、寄生容量の大きさに依存したオフセット成分を効果的に除去できる。その結果、画素の出力振幅に対して、カラムアンプ回路25の増幅可能な入力電圧範囲に必要なマージンを低減することが可能となる。そして、当該入力電圧範囲に必要なマージンを低減できることにより、カラムアンプ回路25の電源電圧の低電圧化や低消費電力化を図ることができる。

#### 【0189】

##### (実施例1)

以下に、具体的な実施例について説明する。前にも述べたように、D D S 駆動では、先ず、F D 部42に保持、もしくは、蓄積されている信号電荷を信号レベル $V_{sig}$ として読み出す駆動が行われる。次いで、F D 部42をリセット電位 $V_r$ にリセットして当該リセット電位 $V_r$ をリセットレベル $V_{rst}$ として読み出す駆動が行われる。そして、単位画素11から先に読み出される信号レベル $V_{sig}$ を、カラムアンプ回路25の変換可能な入力電圧範囲の基準となる基準電圧として用いる。換言すれば、先に読み出される信号レベル $V_{sig}$ を用いてカラムアンプ回路25の基準電圧を設定する。

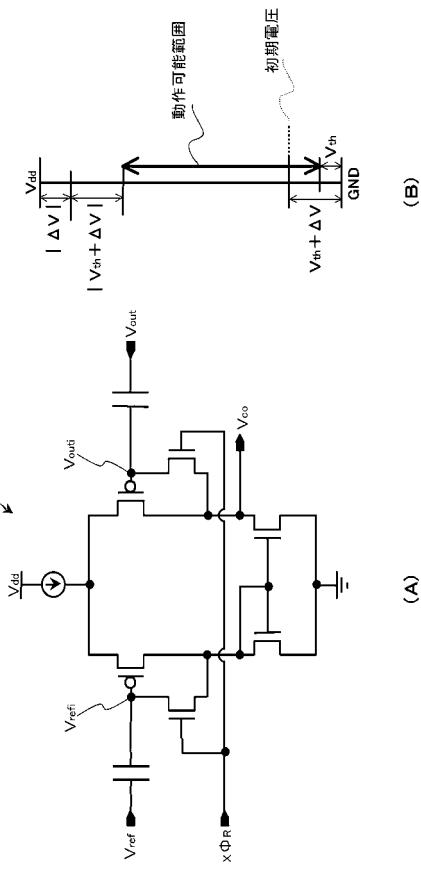

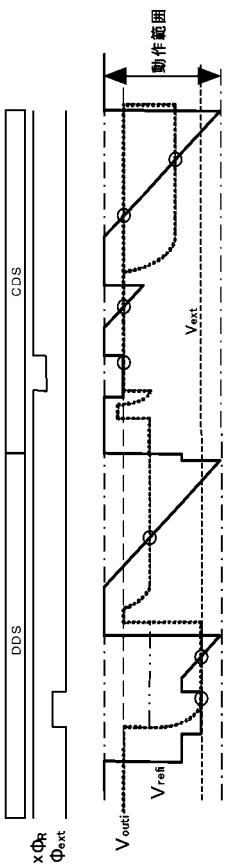

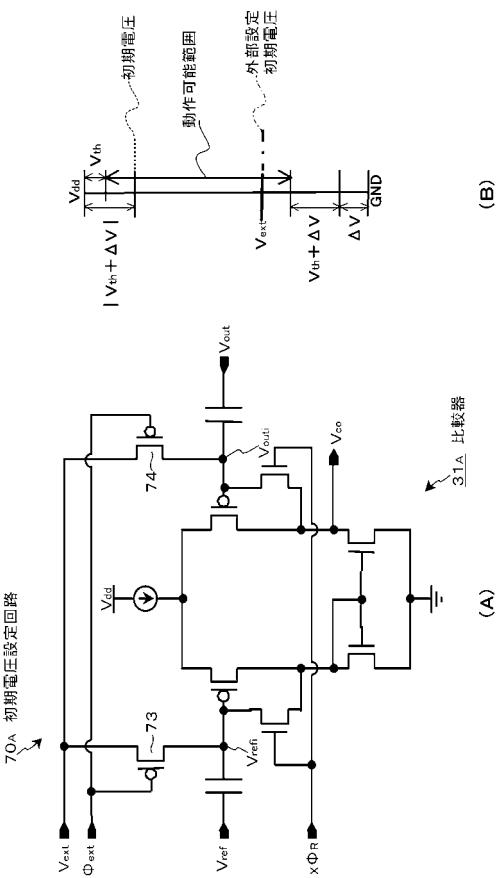

#### 【0190】

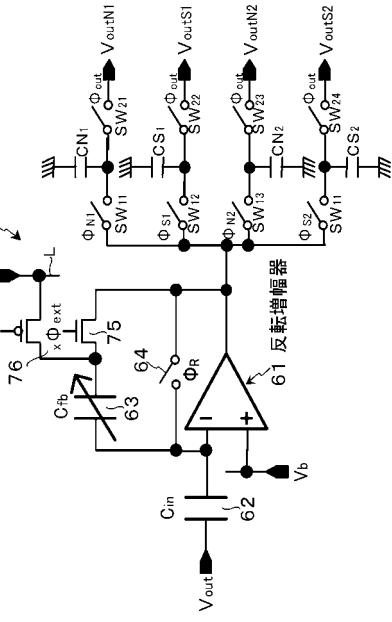

図34は、基準電圧を調整する機能を備えた、実施例1に係るカラムアンプ回路についての説明図であり、(A)はカラムアンプ回路の構成例を、(B)はカラムアンプ回路の動作範囲をそれぞれ示している。図34において、図31と同等部位には同一符号を付して示している。

#### 【0191】

図34(A)に示すように、実施例1に係るカラムアンプ回路25<sub>A</sub>は、反転増幅器61、入力容量62、帰還容量63、及び、制御スイッチ64に加えて、カラムアンプ回路25<sub>A</sub>の基準電圧を設定(調整)するための初期電圧設定回路70<sub>B</sub>を有する構成となっている。

#### 【0192】

初期電圧設定回路70<sub>B</sub>は、帰還容量63に対して直列に接続されたN M O Sトランジスタ75と、帰還容量63とN M O Sトランジスタ75との接続ノードと外部設定初期電圧 $V_{ext}$ が与えられるラインLとの間に接続されたP M O Sトランジスタ76によって構成されている。N M O Sトランジスタ75及びP M O Sトランジスタ76の各ゲート電極には、制御信号 $x_{ext}$ の反転信号 $x_{ext}$ が印加される。制御信号 $x_{ext}$ の反転信号 $x_{ext}$ は、例えば、図1に示すタイミング制御部18から与えられる。すなわち、タイミング制御部18は、初期電圧設定回路70<sub>B</sub>を制御する制御部としての機能を持っている。

#### 【0193】

図35は、実施例1に係るカラムアンプ回路25<sub>A</sub>の各部位の信号波形を示す波形図である。図35には、制御信号 $x_{ext}$ の反転信号 $x_{ext}$ 、制御信号 $x_R$ 、列信号線22の信号電圧 $V_{out}$ 、即ちカラムアンプ回路25<sub>A</sub>の入力電圧、及び、カラムアンプ回路25<sub>A</sub>の出力電圧 $V_{amp}$ の各波形を示している。

#### 【0194】

C D S 駆動の場合は、制御信号 $x_{ext}$ の反転信号 $x_{ext}$ が高電位の状態にあることで、N M O Sトランジスタ75が導通状態になり、帰還容量63をカラムアンプ回路25<sub>A</sub>の出力端に電気的に接続する。このときの回路構成は、図31に示したカラムアンプ回路25と同じ回路構成、即ち、通常のC D S駆動時の同じ回路形態となる。

#### 【0195】

D D S 駆動時は、カラムアンプ回路25<sub>A</sub>自体の入出力間を短絡することで、カラムアンプ回路25<sub>A</sub>の入力信号は初期電圧(基準電圧)を $V_b$ となる。これにより、出力振幅を確保でき、かつ、回路の動作する入力信号レベルとなる。

#### 【0196】

一方で、制御信号 $x_{ext}$ の反転信号 $x_{ext}$ が低電位の状態になることで、N M O Sトランジスタ75が非導通状態となり、カラムアンプ回路25<sub>A</sub>の出力端に対する帰還容量63の電気的接続を開放する。すなわち、反転増幅器61の帰還ループを開放状態にする。

10

20

30

40

50

このとき、PMOSトランジスタ76が導通状態になり、帰還容量63の開放端に対して外部設定初期電圧 $V_{ext}$ を印加する。これにより、反転増幅器61の出力電圧の初期値は、外部設定初期電圧 $V_{ext}$ となる。そして、DDS駆動の場合は、入力信号は、低い信号レベルから高いリセットレベルへと変化するので、この動作範囲になるように、カラムアンプ回路25Aの基準電圧の調整が行われる。

#### 【0197】

このように、DDS駆動時において、初期電圧設定回路70Bの作用により、信号レベル $V_{sig}$ 及びリセットレベル $V_{rst}$ がカラムアンプ回路25Aの動作範囲内に入るように基準電圧を調整することで、CDS駆動とDDS駆動の両立が可能になる。

#### 【0198】

また、基準電圧を調整するための初期電圧設定回路70Bとしては、2つのMOSトランジスタ75, 76を追加するだけの非常に簡単な回路構成で実現できる。従って、個々のカラムアンプ回路25Aとしては、僅かな面積の増加で済む。すなわち、CDS駆動とDDS駆動との両立を、カラムアンプ回路25Aの面積を僅かに増加するだけで実現できる。

#### 【0199】

(実施例2)

図36は、基準電圧を調整する機能を備えた、実施例2に係るカラムアンプ回路の構成例を示す回路図であり、図中、図34と同等部位には同一符号を付して示している。

#### 【0200】

実施例2に係るカラムアンプ回路25Bは、入力側の容量と出力側の容量の容量比で信号を増幅する構成となっている。具体的には、反転増幅器61の出力端に、スイッチ $SW_{11} \sim SW_{14}$ を介して4つの出力容量 $CN_1, CS_1, CN_2, CS_2$ が接続され、これら出力容量 $CN_1, CS_1, CN_2, CS_2$ の保持電荷がスイッチ $SW_{21} \sim SW_{24}$ によって選択的に出力される構成となっている。出力側の容量の回路部分以外の構成、及び、その動作については、実施例1に係るカラムアンプ回路25Aの場合と同じである。

#### 【0201】

また、反転増幅器61の帰還容量63の部位には、実施例1に係るカラムアンプ回路25Aの場合と同様に、カラムアンプ回路25Bの基準電圧を設定(調整)するための初期電圧設定回路70Bが設けられている。初期電圧設定回路70Bは、実施例1の同様の構成、即ち、帰還容量63に対して直列に接続されたNMOSトランジスタ75と、帰還容量63とNMOSトランジスタ75との接続ノードに外部設定初期電圧 $V_{ext}$ を選択的に与えるPMOSトランジスタ76とを有する構成となっている。

#### 【0202】

次に、上記構成の実施例2に係るカラムアンプ回路25Bの回路動作について、図37のタイミング波形図を用いて説明する。

#### 【0203】

第1実施形態の場合と同様、DDS駆動時にカラムアンプ回路25Bの出力が下側に飽和しないよう、初期電圧として外部設定初期電圧 $V_{ext}$ を設定する。その設定後、フィードバックがかかった状態のカラムアンプ回路25Bの出力信号を制御信号 $s_1$ にて出力容量 $CS_1$ にサンプルする。続いて、単位画素11のリセット信号 $RS_T$ をアクティブ状態にして、信号レベルを制御信号 $N_1$ にて出力容量 $CN_1$ にサンプルする。

#### 【0204】

カラムアンプ回路25Bに対して制御信号(リセット信号) $R$ を入力し、同時に、単位画素11のFD部42をリセットする。これにより、カラムアンプ回路25Bの入力側は初期電圧 $V_b$ に設定される。制御信号 $R$ の印加をやめた状態を初期値として出力容量 $CN_2$ に制御信号 $N_2$ にてサンプルし、転送信号 $TRG$ にてフォトダイオード41からFD部42へ信号を転送した後に制御信号 $s_2$ にて出力容量 $CS_2$ にサンプルする。出力容量 $CN_1, CS_1$ には、DDS駆動での信号レベル差、出力容量 $CN_2, CS_2$ にはCDS駆動での信号レベル差が蓄積されている。これらの信号を水平転送制御で出力へ読み出す。

10

20

30

40

50

**【0205】**

このように、入力側の容量と出力側の容量の容量比で信号を増幅する構成のカラムアンプ回路 $25_B$ においても、初期電圧設定回路 $70_B$ の作用により、適切な初期状態として、CDS駆動とDDS駆動とで、同一回路を用いて動作範囲内に出力が収まるように動作させることが可能となる。

**【0206】**

また、基準電圧を調整するための初期電圧設定回路 $70_B$ としては、2つのMOSトランジスタ $75, 76$ を追加するだけの非常に簡単な回路構成で実現できる。従って、個々のカラムアンプ回路 $25_B$ としては、僅かな面積の増加で済む。すなわち、CDS駆動とDDS駆動との両立を、カラムアンプ回路 $25_B$ の面積を僅かに増加するだけで実現できる。10

**【0207】**

また、DDS駆動とCDS駆動とでカラムアンプ回路 $25_B$ の入力側と帰還側の容量比を変えることで、信号のゲインをおのの個別に設定可能となる。加えて、カラムアンプ回路 $25_B$ の出力側に、第1実施形態に係るシングルスロープ型のAD変換回路を接続し、制御信号 $N_1, N_2, S_1, S_2$ で表された期間にAD変換を行うことで、信号を取得することも可能となる。

**【0208】**

<3. 他の画素構成>

第1、第2実施形態においては、リセットレベルを信号レベルの前に読み出すことができない固体撮像装置として、グローバル露光機能を持つCMOSイメージセンサ $10_A, 10_B$ を例に挙げた。このグローバル露光機能を持つCMOSイメージセンサ $10_A, 10_B$ は、全画素一括の露光を実現すべく、フォトダイオード $41$ で発生した電荷を全画素同時にFD部 $42$ へ転送し、当該FD部 $42$ で信号電荷が保持された状態から、順次読み出し動作を実行する。20

**【0209】**

但し、信号検出部にリセット前に読み出したい信号電荷が存在するため、リセットレベルを信号レベルの前に読み出すことができない固体撮像装置としては、グローバル露光機能を持つCMOSイメージセンサ $10_A, 10_B$ に限られるものではない。以下に他の画素例について説明する。30

**【0210】**

(他の画素例1)

図38は、有機光電変換膜を用いた、他の画素例1に係る単位画素の一例を示す構成図であり、図中、図2と同等部位には同一符号を付して示している。

**【0211】**

他の画素例1に係る単位画素 $11_A$ において、有機光電変換膜 $81$ は上部電極 $82$ と下部電極 $83$ で挟まれている。少なくとも下部電極 $83$ は画素毎に分割され、透明性の高い電極が使われることが多い。そして、上部電極 $82$ に対してバイアス電源 $84$ によりバイアス電圧 $V_b$ が印加されている。40

**【0212】**

有機光電変換膜 $81$ での光電変換によって発生した電荷はFD部 $42$ に蓄積される。FD部 $42$ の電荷は、増幅トランジスタ $45$ を含む読み出し回路を介して列信号線 $22$ から電圧として読み出される。FD部 $26$ は、リセットトランジスタ $44$ によりドレイン電位 $V_r$ に設定される。そして、リセットトランジスタ $44$ のドレイン電位 $V_r$ は、FD部 $42$ の空乏化されたリセットトランジスタ $44$ 側のポテンシャルよりも低い電圧 $V_{r1}$ から高い電圧 $V_{r2}$ へ遷移させることができとなっている。

**【0213】**

このように、有機光電変換膜 $81$ を用いた、他の画素例1に係る単位画素 $11_A$ の場合は、DDS駆動によって該当画素の信号を読み出す。他の有機光電変換膜のついていない、もしくは、有機光電変換膜の機能が無効となっている、4つのトランジスタ等で構成さ50

れた C D S 動作が可能な画素については、別の駆動によって信号を読み出す。例えば、有機光電変換膜 8 1 を用いていない他の画素が、例えば図 2 に示す画素構成の場合は、D D S 駆動と C D S 駆動の組み合わせ、もしくは、C D S 駆動のみの読み出しを行う。

#### 【 0 2 1 4 】

この他の画素例 1 に係る単位画素 1 1<sub>A</sub> を用いた固体撮像装置に対しても、先述した第 1 , 第 2 実施形態に係る信号処理部に関する技術を同様に適用することができる。すなわち、同一の信号処理部によって D D S 駆動と C D S 駆動を両立できる。

#### 【 0 2 1 5 】

##### (他の画素例 2 )

次に、単位画素内に F D 部 4 2 以外に電荷蓄積部を有する画素について、他の画素例 2 として説明する。ここでは、F D 部 4 2 以外に電荷蓄積部を有する画素構成として 2 つの例を図 3 9 ( A ) , ( B ) に示す。図 3 9 ( A ) , ( B ) において、図 2 と同等部位には同一符号を付して示している。10

#### 【 0 2 1 6 】

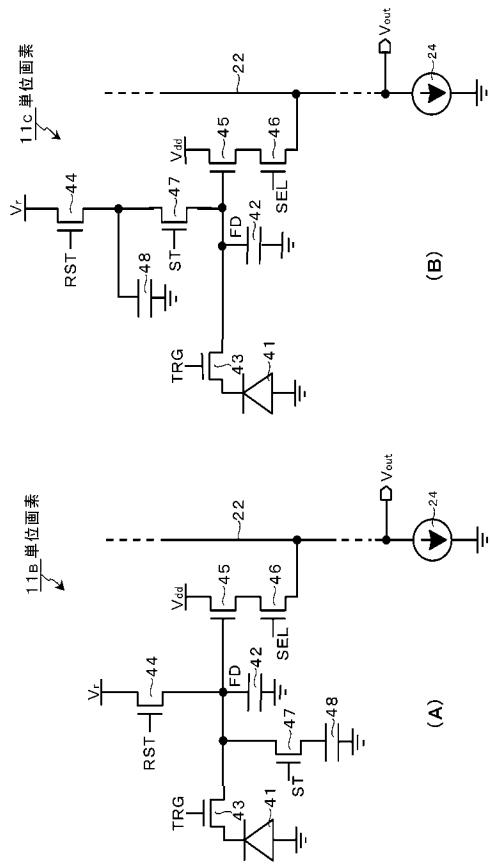

図 3 9 ( A ) に示す画素構成に係る単位画素 1 1<sub>B</sub> は、増幅トランジスタ 4 5 のゲート電極に対して、容量選択トランジスタ 4 7 を介して蓄積容量 4 8 が電荷蓄積部として接続された画素構成となっている。図 3 9 ( B ) に示す画素構成に係る単位画素 1 1<sub>C</sub> は、容量選択トランジスタ 4 7 が増幅トランジスタ 4 5 とリセットトランジスタ 4 4 との間に接続され、その接続ノードとグランドとの間に蓄積容量 4 8 が接続された画素構成となっている。20

#### 【 0 2 1 7 】

上記構成の他の画素例 2 に係る単位画素 1 1<sub>B</sub> , 1 1<sub>C</sub> を用いた固体撮像装置に対しても、先述した第 1 , 第 2 実施形態に係る信号処理部に関する技術を同様に適用することができる。すなわち、同一の信号処理部によって D D S 駆動と C D S 駆動を両立できる。

#### 【 0 2 1 8 】

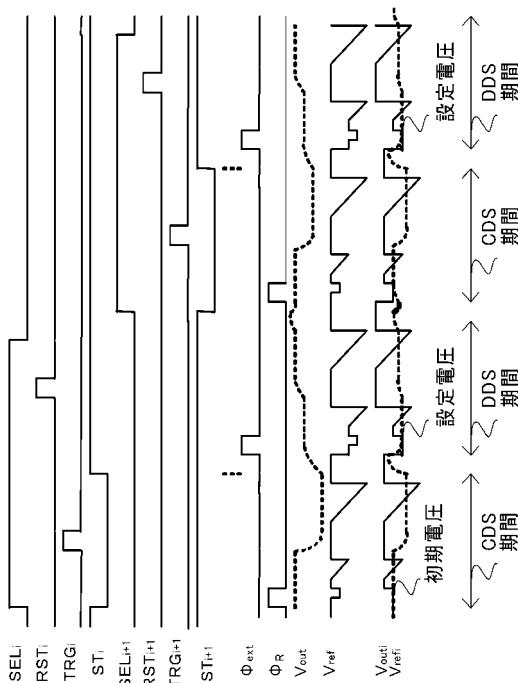

ここで、一例として、C D S 駆動 D D S 駆動の順で画素から信号を読み出す場合の動作について、図 4 0 のタイミング波形図を用いて説明する。

#### 【 0 2 1 9 】

選択信号 S E L によって選択トランジスタ 4 6 を導通状態にした後、リセット信号 R S T によってリセットトランジスタ 4 4 を導通状態にし、F D 部 4 2 をリセットする。このとき。容量選択トランジスタ 4 7 については非導通状態にしておく。そして、リセットしたときの F D 部 4 2 の電位をリセットレベルとして読み出し、次いで、転送信号 T R G をアクティブ状態にすることによってフォトダイオード 4 1 から F D 部 4 2 に信号電荷を読み出す。この一連の駆動が C D S 駆動である。30

#### 【 0 2 2 0 】

続いて、容量選択トランジスタ 4 7 を導通状態にし、F D 部 4 2 と蓄積容量 4 8 に蓄積されている信号電荷を読み出し、次いで、リセットトランジスタ 4 4 によって F D 部 4 2 と蓄積容量 4 8 をリセットし、そのリセットレベルを読み出す。この一連の駆動が D D S 駆動である。

#### 【 0 2 2 1 】

ここでは、一例として、C D S 駆動 D D S 駆動の順で読み出し動作を行う場合について説明したが、D D S 駆動 C D S 駆動の順で読み出し動作を行う場合に対しても、先述した第 1 , 第 2 実施形態に係る信号処理部に関する技術を同様に適用することができる。40

#### 【 0 2 2 2 】

##### (他の画素例 3 )

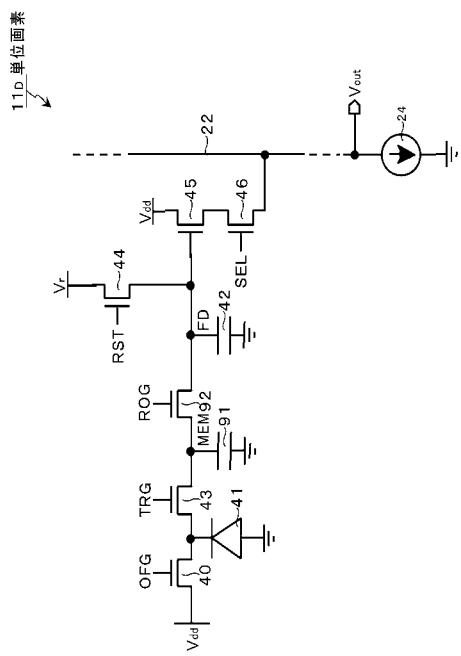

次に、単位画素内に信号蓄積用アナログメモリを有し、中間オーバーフロー構造になっている画素について、他の画素例 3 として説明する。

#### 【 0 2 2 3 】

図 4 1 は、信号蓄積用アナログメモリを有し、中間オーバーフロー構造になっている、他の画素例 3 に係る単位画素の一例を示す構成図であり、図中、図 2 と同等部位には同一50

符号を付して示している。

#### 【0224】

他の画素例3に係る単位画素 $11_D$ は、転送トランジスタ43の後段に信号蓄積用アナログメモリである画素内蓄積容量(MEM)91を有するとともに、当該蓄積容量91とFD部42との間に転送ゲート部92が配された構成となっている。単位画素 $11_D$ は更に、フォトダイオード41と電荷排出部(例えば、電源電圧 $V_{dd}$ )との間に接続された電荷排出ゲート部40を有している。電荷排出ゲート部40は、ゲート電極に印加される制御信号OFGがアクティブ状態になるとこれに応答して導通状態となり、フォトダイオード41から予め定められた所定量もしくはフォトダイオード41に蓄積された全ての光電荷を電荷排出部に選択的に排出する。

10

#### 【0225】

この他の画素例3に係る単位画素 $11_C$ では、転送トランジスタ43に印加する転送信号TRGの電圧を、高電位と低電位の中間電圧とする。これにより、画素に高照度信号が入射した場合は、転送トランジスタ43のゲートのボテンシャル以上となった電荷が、容量側にオーバーフローすることで、取り扱い電荷量を増加させることができる。

#### 【0226】

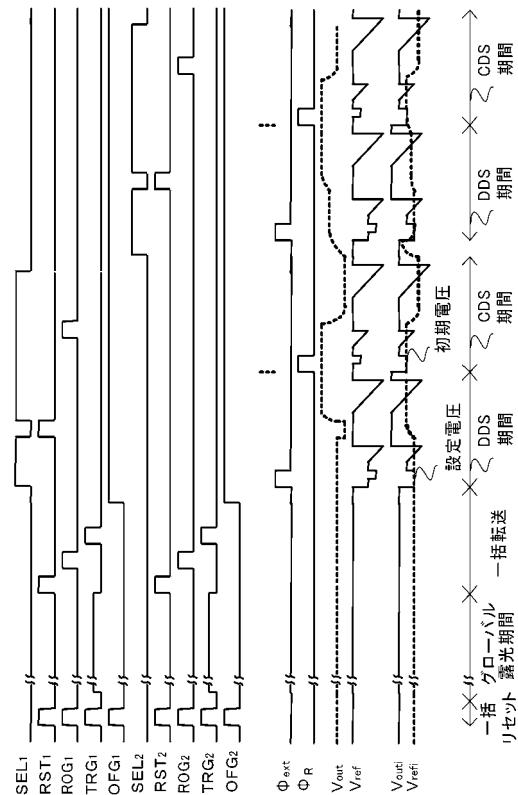

他の画素例3に係る単位画素 $11_D$ を有し、グローバルシャッタ機能を持った固体撮像装置の動作について、図42のタイミング波形図を用いて説明する。

#### 【0227】

先ず、蓄積時間の開始をグローバルリセットにて行い、全画素一斉に初期化する。蓄積時間が経過した後、オーバーフローで画素内蓄積容量91に蓄積した電荷を、転送ゲート部92の制御にて全画素一斉にFD部42へ転送する。その後、転送トランジスタ43を全画素一斉に導通状態にすることで、フォトダイオード41に蓄積した低照度側の信号を蓄積容量91に転送する。転送前後で、元々フォトダイオード41、蓄積容量91にあつた信号が、蓄積容量91、FD部42に全画素一斉に移動することになる。

20

#### 【0228】

図42に示すように、FD部42の信号をDDS駆動により読み出し、蓄積容量91の信号をCDS駆動により読み出す。なお、選択信号SELはグローバル露光時には非アクティブ状態になっていることを想定しているので、読み出し時のリセット信号RSTが入力されるときは、画素の状態に相関を持たせるために選択信号SELは非アクティブ状態とすることが好ましい。このときの制御信号<sub>ext</sub>と制御信号<sub>R</sub>も前述のCDS駆動、DDS駆動の際に適切なタイミングにて入力される。

30

#### 【0229】

##### <4. 変形例>

上記各実施形態においては、基本的に、DDS駆動 CDS駆動の駆動例であるが、CDS駆動の読み出し回数は1回に限定するものではない。図面の記載を簡素化するため、スイッチはシンボルで記載した場合もあるが、これらについてはNMOSもしくはPMOSのトランジスタで代用も可能であり、NMOSはHighでスイッチを活性、PMOSはLowで活性とすることで前述の動作は可能である。

40

#### 【0230】

また、1行の読み出し期間中にDDS駆動とCDS駆動を交互に1行毎実行するとしたが、この駆動法に限定するものではない。例えば、1フレーム毎にDDS駆動とCDS駆動を交互に実行する駆動法を探ることも可能である。この駆動法によれば、DDS駆動とCDS駆動の切り替えが1フレーム周期でよいため、1ライン(1行)周期で切り替えを行う場合に比べて、動作速度の高速化が図れる利点がある。一方、1フレーム周期での切り替えだと、後段の信号処理部においてフレームメモリが必要になるため、メモリ容量の観点からすると、1ライン周期での切り替えの方が有利ということも言える。

#### 【0231】

また、上記各実施形態では、単位画素が行列状に配置されてなるCMOSイメージセンサに適用した場合を例に挙げて説明したが、本開示はCMOSイメージセンサへの適用に

50

限られるものではない。すなわち、本開示は、単位画素が行列状に2次現配置されてなるX-Yアドレス方式の固体撮像装置全般に対して適用可能である。

#### 【0232】

また、本開示は、可視光の入射光量の分布を検知して画像として撮像する固体撮像装置への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像装置全般に対して適用可能である。

#### 【0233】

尚、固体撮像装置はワンチップとして形成された形態であってもよいし、撮像部と、信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

10

#### 【0234】

##### <5. 電子機器>

本開示は、固体撮像装置への適用に限られるものではなく、デジタルスチルカメラやビデオカメラ等の撮像装置や、携帯電話機などの撮像機能を有する携帯端末装置など、画像取込部（光電変換部）に固体撮像装置を用いる電子機器全般に対して適用可能である。画像取込部に固体撮像装置を用いる電子機器には、画像読取部に固体撮像装置を用いる複写機も含まれる。尚、電子機器に搭載される上記モジュール状の形態、即ちカメラモジュールを撮像装置とする場合もある。

#### 【0235】

##### (撮像装置)

20

図43は、本開示に係る電子機器、例えば撮像装置の構成の一例を示すブロック図である。

#### 【0236】

図43に示すように、本開示に係る撮像装置100は、レンズ群101等を含む光学系、撮像素子（撮像デバイス）102、DSP回路103、フレームメモリ104、表示装置105、記録装置106、操作系107及び電源系108等を有する。そして、DSP回路103、フレームメモリ104、表示装置105、記録装置106、操作系107及び電源系108がバスライン109を介して相互に接続されている。

#### 【0237】

レンズ群101は、被写体からの入射光（像光）を取り込んで撮像素子102の撮像面上に結像する。撮像素子102は、レンズ群101によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。

30

#### 【0238】

表示装置105は、液晶表示装置や有機EL(electro luminescence)表示装置等のパネル型表示装置からなり、撮像素子102で撮像された動画または静止画を表示する。記録装置106は、撮像素子102で撮像された動画または静止画を、ビデオテープやDVD(Digital Versatile Disk)等の記録媒体に記録する。

#### 【0239】

操作系107は、ユーザによる操作の下に、本撮像装置が持つ様々な機能について操作指令を発する。電源系108は、DSP回路103、フレームメモリ104、表示装置105、記録装置106及び操作系107の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

40

#### 【0240】

上記の構成の撮像装置は、ビデオカメラやデジタルスチルカメラ、さらには携帯電話機等のモバイル機器向けカメラモジュールなどの撮像装置として用いることができる。そして、当該撮像装置において、撮像素子102として、先述した各実施形態に係るCMOSイメージセンサ<sub>10A, 10B</sub>等の固体撮像装置を用いることで、次のような作用効果を得ることができる。

#### 【0241】

すなわち、先述した各実施形態に係るCMOSイメージセンサ<sub>10A, 10B</sub>は、グロー

50

バル露光によって歪みのない撮像を実現できる。従って、画像歪みが許容できない、高速に動く被写体の撮像や、撮像画像の同時性を必要とするセンシング用途に用いて好適な撮像装置として実現出来る。

### 【0242】

また、先述した各実施形態に係るCMOSイメージセンサ<sub>10A</sub>, <sub>10B</sub>は、面内の大きな特性の揺らぎ(面内分布)の差異や、寄生容量の大きさに依存したオフセット成分を効果的に除去することができる。これにより、画素の出力振幅に対して、信号処理部の処理可能な入力電圧範囲に必要なマージンを低減することが可能となるため、信号処理部の電源電圧の低電圧化や低消費電力化を図ることができる。従って、各種電子機器の低電圧化や低消費電力化に寄与できる。

10

### 【符号の説明】

#### 【0243】

<sub>10A</sub>, <sub>10B</sub>... CMOSイメージセンサ、<sub>11</sub>, <sub>11A</sub>, <sub>11B</sub>, <sub>11C</sub>, <sub>11D</sub>... 単位画素、<sub>12</sub>... 画素アレイ部、<sub>13</sub>... 行走査部、<sub>14A</sub>, <sub>14B</sub>... カラム処理部、<sub>15</sub>... 参照信号生成部、<sub>16</sub>... 列走査部、<sub>17</sub>... 水平出力線、<sub>18</sub>... タイミング制御部、<sub>21</sub>(<sub>21\_1</sub>~<sub>21\_n</sub>)... 行制御線、<sub>22</sub>(<sub>22\_1</sub>~<sub>22\_m</sub>)... 列信号線、<sub>23</sub>(<sub>23\_1</sub>~<sub>23\_m</sub>)... A/D変換回路、<sub>24</sub>... 電流源、<sub>25</sub>(<sub>25\_1</sub>~<sub>25\_m</sub>), <sub>25A</sub>, <sub>25B</sub>... カラムアンプ回路、<sub>31</sub>, <sub>31A</sub>, <sub>31B</sub>, <sub>31C</sub>... 比較器、<sub>32</sub>... アップ/ダウンカウンタ、<sub>33</sub>... 転送スイッチ、<sub>34</sub>... メモリ、<sub>41</sub>... フォトダイオード、<sub>42</sub>... 電荷検出部(FD部)、<sub>43</sub>... 転送トランジスタ(転送ゲート部)、<sub>44</sub>... リセットトランジスタ、<sub>45</sub>... 増幅トランジスタ、<sub>46</sub>... 選択トランジスタ、<sub>70A</sub>, <sub>70B</sub>... 初期電圧設定回路、<sub>81</sub>... 比較回路部、<sub>82</sub>... 記憶回路部

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【 図 1 1 】

【 図 1 2 】

【図13】

【 図 1 4 】

【図 15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

【図 21】

【図 22】

【図 2 3】

【図 2 4】

【図 2 5】

【図 2 6】

【図 2 7】

【図 2 8】

【図 2 9】

【図 3 0】

【図 3 1】

【図 3 2】

【図 3 3】

【図 3 4】

【図 3 5】

【図 3 6】

【図 3 7】

【図 3 8】

【図 3 9】

【図 4 0】

【図 4 1】

【図 4 2】

【図 4 3】

【図 4 4】

【図 4 5】

【図 4 6】

【図 4 7】

【図 4 8】

---

フロントページの続き

(72)発明者 加藤 昭彦

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 田浦 忠行

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 高塚 拳文

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 4M118 AA10 AB01 BA14 CA02 CB20 DB09 DD04 DD09 DD10 DD12

FA06 FA14 FA33 FA38

5C024 CX03 CX05 GX03 GX16 GX18 GY31 HX24 HX29 HX32 HX57