(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4669803号

(P4669803)

(45) 発行日 平成23年4月13日(2011.4.13)

(24) 登録日 平成23年1月21日(2011.1.21)

(51) Int.Cl.

F 1

G 06 F 1/04 (2006.01)

H 01 L 27/04 (2006.01)

H 01 L 21/822 (2006.01)G 06 F 1/04 301 C

H 01 L 27/04 U

請求項の数 7 (全 13 頁)

(21) 出願番号 特願2006-80796 (P2006-80796)

(22) 出願日 平成18年3月23日 (2006.3.23)

(65) 公開番号 特開2007-257290 (P2007-257290A)

(43) 公開日 平成19年10月4日 (2007.10.4)

審査請求日 平成21年2月27日 (2009.2.27)

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 110000176

一色国際特許業務法人

(72) 発明者 清崎 健一

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

審査官 田中 友章

最終頁に続く

(54) 【発明の名称】集積回路及びそれを用いた信号処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電源電圧を供給する外部電源が印加されて動作する集積回路において、前記外部電源から供給される前記第1の電源電圧のレベルを監視して前記外部電源から前記第1の電源電圧が供給されているか否かを判定する電源電圧監視部と、

第1の周波数の第1のクロック及び前記第1の周波数よりも低い第2の周波数を有する第2のクロックが供給され、前記電源電圧監視部において、前記第1の電源電圧が供給されている旨が判定された場合には前記第1のクロックを選択し、前記第1の電源電圧が供給されていない旨が判定された場合には前記第2のクロックを選択し出力するクロック選択部と、

前記クロック選択部が出力する前記第1のクロック又は前記第2のクロックのうちいずれか一方の供給を受けて動作し、前記集積回路の動作を制御するプロセッサと、を備え、

当該集積回路は、前記外部電源、又は、前記第1の電源電圧よりもレベルの低い第2の電源電圧を供給する内部電源、のうちいずれか一方が印加されて動作するものであって、

前記電源電圧監視部は、前記第1の電源電圧が供給されている旨が判定された場合には前記第1の電源電圧が印加され、前記第1の電源電圧が供給されていない旨が判定された場合には前記第2の電源電圧が印加されるべく制御を行うこと、

を特徴とする集積回路。

## 【請求項 2】

10

20

請求項 1 に記載の集積回路において、前記外部電源は、データ通信を行うとともに前記第 1 の電源電圧を供給することが可能なインターフェースより供給されること、を特徴とする集積回路。

【請求項 3】

請求項 1 に記載の集積回路において、当該集積回路は、更に、

前記第 2 のクロックに基づいて前記第 1 のクロックを生成する PLL 回路を備えること、を特徴とする集積回路。

【請求項 4】

請求項 1 に記載の集積回路において、前記電源電圧監視部は、

前記第 1 の電源電圧の供給開始の際には電源電圧の変化の後に前記クロック選択部における選択を切り替え、前記第 1 の電源電圧の供給終了の際には電源電圧の変化に先立って前記クロック選択部における選択を切り替えること、を特徴とする集積回路。 10

【請求項 5】

請求項 1 又は 3 に記載の集積回路において、当該集積回路は、更に、

デジタルデータをデコード処理するデジタル信号処理回路を備え、当該デジタル信号処理回路は、前記電源電圧監視部が選択制御する前記第 1 の電源電圧又は前記第 2 の電源電圧のうちいずれか一方に応じて動作すること、を特徴とする集積回路。

【請求項 6】

請求項 5 に記載する集積回路を備える信号処理装置において、当該信号処理装置は、更に、 20

前記外部電源及び前記内部電源に接続され、前記電源電圧監視部の判定結果に応じて前記第 1 の電源電圧又は前記第 2 の電源電圧のうちいずれか一方を出力する電源電圧選択部を備え、

前記集積回路は、前記電源電圧選択部が出力する前記第 1 の電源電圧又は前記第 2 の電源電圧のうちいずれか一方に応じて動作すること、を特徴とする集積回路。

【請求項 7】

請求項 6 に記載する信号処理装置において、当該信号処理装置は、更に、

前記デジタルデータを格納する不揮発性メモリを備え、

前記デジタル信号処理回路は、前記不揮発性メモリに格納された前記デジタルデータを読み出してデコード処理を行うこと、を特徴とする信号処理装置。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積回路及びそれを用いた信号処理装置に関する。

【背景技術】

【0002】

近年のエレクトロニクス技術の伸展に伴って、携帯オーディオ再生機器、携帯電話、携帯型ゲーム、PDA (Personal Digital Assistants) 等といった持ち運び便利な携帯性を売りとし且つ所望のアプリケーションに係る信号処理を実行する信号処理装置の普及がめざましい。かかる信号処理装置は、二次電池（ニッケル水素充電池、リチウムイオン充電池等）や一次電池（アルカリ乾電池、マンガン乾電池等）によって構成された内部電源を搭載することで携帯性を実現している（例えば、以下に示す特許文献 1 を参照）。 40

【特許文献 1】特開 2001-184146 号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

ところで、内部電源の電源電圧のみで所望のアプリケーションを長時間実行すると、当然の結果として内部電源の電力消費は増大する。従って、信号処理装置は、多種多様なアプリケーションを長時間実行させる意味で、さらなる低消費電力化の対策が必須となっており、既存の対策では不十分であった。 50

**【課題を解決するための手段】****【0004】**

前述した課題を解決するための主たる本発明は、第1の電源電圧を供給する外部電源が印加されて動作する集積回路において、前記外部電源から供給される前記第1の電源電圧のレベルを監視して前記外部電源から前記第1の電源電圧が供給されているか否かを判定する電源電圧監視部と、第1の周波数の第1のクロック及び前記第1の周波数よりも低い第2の周波数を有する第2のクロックが供給され、前記電源電圧監視部において、前記第1の電源電圧が供給されている旨が判定された場合には前記第1のクロックを選択し、前記第1の電源電圧が供給されていない旨が判定された場合には前記第2のクロックを選択し出力するクロック選択部と、前記クロック選択部が出力する前記第1のクロック又は前記第2のクロックのうちいずれか一方の供給を受けて動作し、前記集積回路の動作を制御するプロセッサと、を備える。

10

**【発明の効果】****【0005】**

本発明によれば、外部電源の供給状況に応じて供給する電源電圧を適切に制御することにより、集積回路における電力消費を低減することができる。

**【発明を実施するための最良の形態】****【0006】**

## &lt;信号処理装置の外部接続&gt;

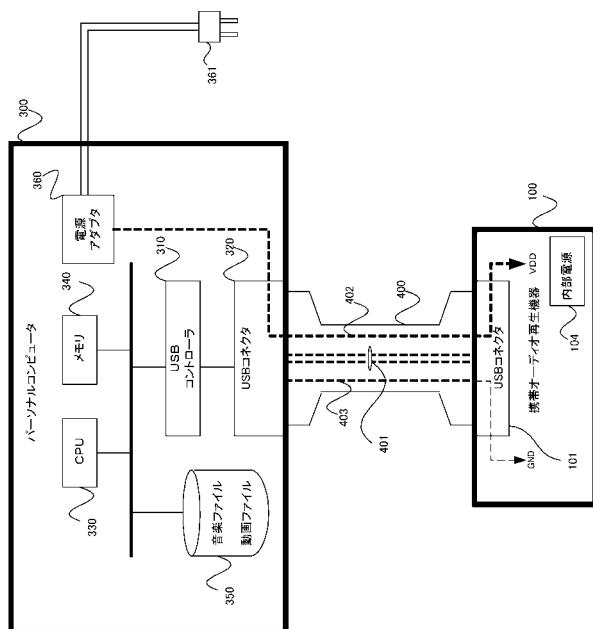

図1は、本発明に係る信号処理装置の外部接続を説明するための図である。以下では、本発明に係る信号処理装置の一例として、USB (Universal Serial Bus) インタフェース101を備えており、パーソナルコンピュータ300からUSBケーブル400のデータライン401を介して転送された圧縮オーディオデータのデジタル再生を行う携帯オーディオ再生機器100を取りあげて説明する。なお、本発明に係る信号処理装置としては、例えば、携帯電話、携帯ゲーム、PDA等であってもよい。

20

**【0007】**

ここで、USBとは、共通のUSBインターフェースで様々なタイプの信号処理装置をUSBホスト機器へと接続可能なシリアルインターフェース規格のことである。USBの現時点での最新バージョンは「USB2.0」であり、LS (Low Speed)、FS (Full Speed)及びHS (High Speed)の3種類の転送モードを備えており、用途に応じて3種類の転送モードが使い分けられる。また、USBは、ハブを利用することで最大127個のUSB機器をツリー状に接続可能であり、また、USBホスト機器の電源を投入した状態で新たなUSB機器を接続可能な所謂ホットプラグに対応している。

30

**【0008】**

まず、パーソナルコンピュータ300は、USBコントローラ310並びにUSBインターフェース320を備えてある場合とする。この場合、パーソナルコンピュータ300のUSBインターフェース320と、携帯オーディオ再生機器100のUSBインターフェース101との間を、USBケーブル400によって接続することで、パーソナルコンピュータ300と携帯オーディオ再生機器100間がUSB接続される。なお、USBケーブル400は、2本のデータライン401と、電源ライン402と、GNDライン403とによって構成されており、USBインターフェース320、101は、それぞれ、一対のデータ端子D+及びD-と、電源端子V<sub>BUS</sub>と、GND端子とが設けられる。

40

**【0009】**

パーソナルコンピュータ300は、電源プラグ361を介して供給されるAC電源電圧をDC電源電圧へと変換する電源アダプタ360を備えるとともに、全体の制御を司るCPU330、様々なプログラムを格納するROM等のメモリ340、音楽ファイルや動画ファイル等を格納するハードディスク350、が相互に通信可能に接続されている。ここで、ハードディスク350に格納される音楽ファイルは、例えば、MP3-Audio Layer 3 (MP3)形式等の圧縮オーディオデータであり、ハードディスク350に格納される動画ファイルは、例えば、MPEG-2形式、MPEG-4形式等の圧

50

縮ムービーデータである。

【0010】

ここで、パーソナルコンピュータ300から携帯オーディオ再生機器100に向けての音楽ファイルのデータ転送の概要を説明する。まず、パーソナルコンピュータ300は、メモリ340に格納されたプログラムを起動し、ポーリング要求等によって携帯オーディオ再生機器100を自身に接続されたUSB機器として認識する。そして、パーソナルコンピュータ300は、ハードディスク350から任意の音楽ファイルを読み出し、USBコントローラ310へと転送する。USBコントローラ310は、ハードディスク350から読み出された音楽ファイルをパケット形式へと変換して、USBインターフェース320乃至USBケーブル400を介して携帯オーディオ再生機器100へと差動の半二重伝送を行うためのUSB規格に準拠した通信プロトコル処理を行う。この結果、携帯オーディオ再生機器100は、パーソナルコンピュータ300から音楽ファイルを取り込むことができる。

【0011】

一方、携帯オーディオ再生機器100は、パーソナルコンピュータ300から音楽ファイルのデータ転送が完了した場合、一般的には、USBインターフェース101からUSBケーブル400を取り外した上で、当該音楽ファイルの再生処理を実行することになる。しかし、音楽ファイルのデータ転送が完了した場合に、USBインターフェース101にUSBケーブル400を接続したままの状態であっても、携帯オーディオ再生機器100は、音楽ファイルの再生処理を実行することが可能である。

【0012】

ところで、パーソナルコンピュータ300は、USBケーブル400が有する電源ライン402を利用して、携帯オーディオ再生機器100に向けて電源アダプタ360において生成したDC電源電圧（以下、電源電圧V<sub>BUS</sub>という。）を供給することができる。換言すると、携帯オーディオ再生機器100は、パーソナルコンピュータ300から音楽ファイルを取り込むのと併せて電源電圧V<sub>BUS</sub>の供給を受けることができる。

【0013】

従って、携帯オーディオ再生機器100は、内部電源104の電力消費を抑えるべく、パーソナルコンピュータ300から供給された電源電圧V<sub>BUS</sub>を動作電圧として、パーソナルコンピュータ300との間のUSB規格に準拠した通信プロトコル処理や音楽ファイルの再生処理を行える。

【0014】

<携帯オーディオ再生機器>

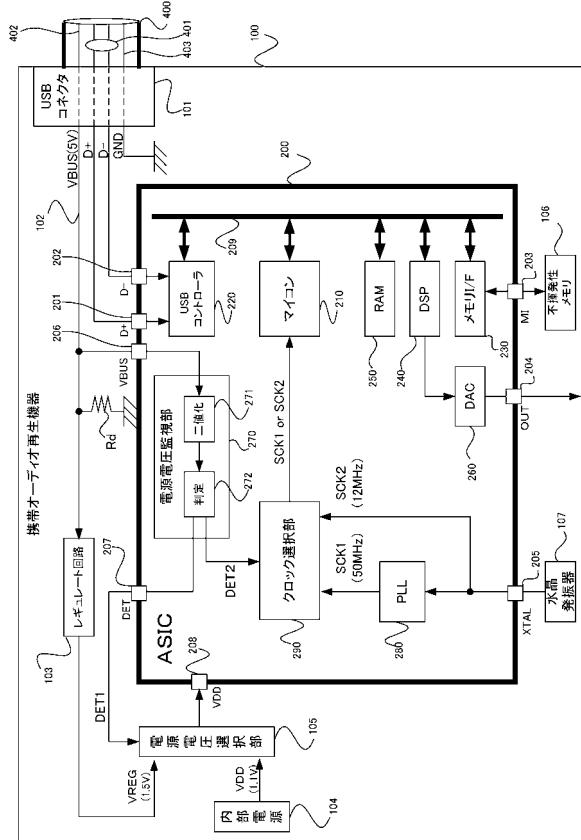

図2は、携帯オーディオ再生機器100の構成を示す図である。同図に示すように、携帯オーディオ再生機器100は、本発明に係る『集積回路』の一実施形態であるASIC(Application Specific Integrated Circuit)200と、その周辺回路によって構成される。なお、本実施形態では、『集積回路』をASIC200によって実現するが、その他にFPGA(Field Programmable Gate Array)やPLD(Programmable Logic Device)で実現してもよい。

【0015】

以下では、携帯オーディオ再生機器100の構成の説明に際して、ASIC200の周辺回路の構成と、ASIC200の構成と、に分けてそれぞれ説明する。

【0016】

= = = ASIC周辺回路の構成 = = =

USBインターフェース101は、電源ライン402を含んだUSBケーブル400を介してUSBホスト機器300と通信可能に接続させるためのインターフェースである。前述したとおり、USBケーブル400は、2本のデータライン401と、電源ライン402と、GNDライン403とによって構成されており、USBインターフェース101は、一对のデータ端子D+及びD-と、電源端子V<sub>BUS</sub>と、GND端子とが設けられる。

【0017】

10

20

30

40

50

レギュレート回路 103 は、USB インタフェース 101 から配線された電源ライン 102 の電源電圧 VBUS のレベルを、高速性が要求される通信プロトコル処理 (HS モードや FS モード等) を ASIC 200 が行う場合に必要となる電圧レベル (3.3V や 1.5V 等) へと調整したレギュレート電源電圧 VREG (本発明に係る『第 1 の電源電圧』) を生成する。なお、USB バスパワーとしてパーソナルコンピュータ 300 から供給される電源電圧は「+4.75V ~ +5.25V」の範囲と規定されており、本実施形態では、電源電圧 VBUS のレベルは「5V」とする。また、レギュレート電源電圧 VREG のレベルは「1.5V」とする。

## 【0018】

内部電源 104 は、一又は複数の二次電池 (ニッケル水素充電池 (公称電圧 1.2V) 、リチウムイオン充電池 (公称電圧 3.6V ~ 3.7V) 等) 若しくは一又は複数の一次電池 (アルカリ乾電池 (公称電圧 1.5V) 、マンガン乾電池 (公称電圧 1.5V) 等) によって構成される電源であり、レギュレート電源電圧 VREG のレベルよりも低いレベルの電源電圧 VDD (本発明に係る『第 2 の電源電圧』) を生成する。

## 【0019】

ここで、本実施形態では、内部電源 104 は、充電が可能であり且つ公称電圧が最も低い二次電池であるニッケル水素充電池 (公称電圧 1.2V) によって構成される場合とする。また、電源電圧 VDD は、ASIC 200 の低消費電力化のためにできる限り低いレベルにすることが好ましいが、ASIC 200 の正常動作が可能な範囲並びに ASIC 200 の半導体プロセスの兼ね合いによって、公称電圧 (1.2V) の 90% 程度の「1.1V」とする。

## 【0020】

電源電圧選択部 105 は、後述の電源電圧監視部 270 から DET 端子 207 を介して供給された選択信号 DET1 に基づいて、パーソナルコンピュータ 300 から携帯オーディオ再生機器 100 へ向けて電源電圧 VBUS が供給されている旨が判定された場合には、レギュレート電源電圧 VREG の方を選択する。また、電源電圧選択部 105 は、前述した選択信号 DET1 に基づいて、パーソナルコンピュータ 300 から携帯オーディオ再生機器 100 へ向けて電源電圧 VBUS が供給されていない旨が判定された場合には電源電圧 VDD の方を選択する。

## 【0021】

不揮発性メモリ 106 は、パーソナルコンピュータ 300 から USB ケーブル 400 を介して転送された音楽ファイルを格納する外部メモリである。不揮発性メモリ 106 は、例えば、フラッシュメモリを採用する。なお、本実施形態以外にも、より大容量のデータを格納する場合には、不揮発性メモリ 106 の代わりに、小型ハードディスク (不図示) を採用してもよい。

## 【0022】

水晶発振器 107 は、PLL 回路 280 において基準となる原クロック SCK2 を発振生成するための外付発振素子である。なお、本実施形態以外にも、携帯オーディオ再生機器 100 の外部から自励クロックの供給を受けるようにしてもよい。

## 【0023】

====ASIC の構成====

まず、ASIC 200 の端子としては、D+ 端子 201、D- 端子 202、MI 端子 203、OUT 端子 204、XTAL 端子 205、VBUS 端子 206、DET 端子 207、VDD 端子 208 が設けられる。

## 【0024】

D+ 端子 201、D- 端子 202 は、USB インタフェース 101 のデータ端子 D+、D- とそれぞれ接続させる入出力端子である。MI 端子 203 は、不揮発性メモリ 106 と接続させる入出力端子である。OUT 端子 204 は、音楽ファイルの再生結果を出力するための出力端子である。XTAL 端子 205 は、水晶発振器 107 と接続させる端子である。

10

20

30

40

50

## 【0025】

V B U S 端子 2 0 6 は、 U S B インタフェース 1 0 1 の電源端子より配線された電源ライン 1 0 2 と接続させる入力端子である。 D E T 端子 2 0 7 は、 電源電圧監視部 2 7 0 の判定結果である選択信号 D E T 1 を出力する出力端子である。 V D D 端子 2 0 8 は、 電源電圧選択部 1 0 5 において選択されたレギュレート電源電圧 V R E G 若しくは電源電圧 V D D の一方が印加される入力端子である。

## 【0026】

また、 A S I C 2 0 0 は、 マイクロコンピュータ 2 1 0 、 U S B コントローラ 2 2 0 、 メモリインターフェース回路 2 3 0 、 D S P (Digital Signal Processor) 2 4 0 、 R A M 2 5 0 、 D A 変換器 2 6 0 それぞれが内部バス 2 0 9 を介して相互に通信可能に接続され 10 ており、 更に、 電源電圧監視部 2 7 0 、 P L L 回路 2 8 0 、 クロック選択部 2 9 0 、 を有する。

## 【0027】

マイクロコンピュータ 2 1 0 は、 A S I C 2 0 0 全体の制御を司る『プロセッサ』である。 すなわち、 マイクロコンピュータ 2 1 0 は、 U S B コントローラ 2 2 0 における通信プロトコル処理や、 D S P 2 4 0 における音楽ファイルの再生処理等を統括制御する。 なお、 マイクロコンピュータ 2 1 0 は、 後述のクロック選択部 2 9 0 から供給される遅倍クロック S C K 1 又は原クロック S C K 2 によって動作する。

## 【0028】

U S B コントローラ 2 2 0 は、 信号処理装置側の通信プロトコル処理を行うものであり 20 、 U S B インタフェース 1 0 1 から D + 端子 2 0 1 並びに D - 端子 2 0 2 へと差動入力されてきたデータを A S I C 2 0 0 の内部バス 2 0 9 へと中継を行う U S B トランシーバや 、 パケットをデコードするデコーダ、 更にはデータバッファ用の F I F O 等を備える。 例えば、 U S B コントローラ 2 2 0 は、 マイクロコンピュータ 2 1 0 からの指令によって、 パーソナルコンピュータ 3 0 0 から転送された音楽ファイルを内部バス 2 0 9 を介してメモリインターフェース回路 2 3 0 へと転送する。

## 【0029】

メモリインターフェース回路 2 3 0 は、 A S I C 2 0 0 から M I 端子 2 0 3 に接続された不揮発性メモリ 1 0 6 に対するデータの読み出し・書き込みを制御するための回路である。 例え 30 ば、 メモリインターフェース回路 2 3 0 は、 U S B コントローラ 2 2 0 から転送された音楽ファイルを不揮発性メモリ 1 0 6 へと書き込む処理を行う。

## 【0030】

D S P 2 4 0 は、 音楽ファイルの再生に係るデジタル信号処理を行う回路である。 例え 40 ば、 音楽ファイルの再生の際には、 マイクロコンピュータ 2 1 0 からの指令によって、 不揮発性メモリ 1 0 6 に書き込まれた音楽ファイルがメモリインターフェース回路 2 3 0 によって読み出され、 作業用メモリとしての R A M 2 5 0 へと格納される。 D S P 2 4 0 は、 R A M 2 5 0 へと格納された音楽ファイルを読み出してそのデータ形式に準拠したデコード処理 ( 例え ば、 M P 3 デコード等 ) を行う。 そして、 デコード処理されたデジタル量が 、 D A 変換器 2 6 0 によってアナログ量へと変換された後に O U T 端子 2 0 4 を介して外部へと出力される。

## 【0031】

電源電圧監視部 2 7 0 は、 U S B インタフェース 1 0 1 に U S B ケーブル 4 0 0 が接続された場合にパーソナルコンピュータ 3 0 0 から電源ライン 4 0 2 を介して供給され得る電源電圧 V B U S のレベルを監視することで、 パーソナルコンピュータ 3 0 0 から電源電圧 V B U S が供給されているか否かを判定する。

## 【0032】

詳述すると、 電源ライン 4 0 2 と U S B インタフェース 1 0 1 を介して電気的に接続された電源ライン 1 0 2 上にブルダウン抵抗 R d を予め設けておく。 その上で、 U S B インタフェース 1 0 1 に U S B ケーブル 4 0 0 が接続されてパーソナルコンピュータ 3 0 0 から電源電圧 V B U S の供給を受けている場合には V B U S 端子 2 0 6 に印加される電圧レ 50

ベルは「5V」となる。一方、USBインターフェース101からUSBケーブル400が取り外された場合にはパーソナルコンピュータ300から電源電圧V<sub>BUS</sub>の供給を受けないので、V<sub>BUS</sub>端子206に印加される電圧レベルはプルダウン抵抗R<sub>d</sub>によって「0V」となる。

【0033】

そこで、電源電圧監視部270は、二値化処理部271並びに判定処理部272を具備しており、二値化処理部271は、V<sub>BUS</sub>端子206に印加される電圧レベルを予め定めておいた参照レベルV<sub>th</sub>（例えば、2.5V）と比較することで、Highレベル若しくはLowレベルを出力する。

【0034】

判定処理部272は、二値化処理部271より出力されたHighレベル又はLowレベルの期間を計測することで、Highレベルが一定期間T<sub>h</sub>継続した場合にはパーソナルコンピュータ300から電源電圧V<sub>BUS</sub>が供給されている旨を判定し、Lowレベルが一定期間T<sub>h</sub>継続した場合にはパーソナルコンピュータ300から電源電圧V<sub>BUS</sub>が供給されていない旨を判定する。このように、二値化処理部271より出力されるHighレベル又はLowレベルが一定期間T<sub>h</sub>継続するまでは判定を下さないようにすることによって、例えば、スパイク状の電源ノイズの影響を受けて、誤った判定結果が引き起こされることを防止することができる。

【0035】

なお、判定処理部272における判定結果は、電源電圧選択部105がレギュレート電源電圧V<sub>REG</sub>又は電源電圧V<sub>DD</sub>を選択するための選択信号DET1と、クロック選択部290が倍クロックSCK1又は原クロックSCK2を選択するための選択信号DET2として用いられる。ここで、電源電圧選択部105は、ASIC200の周辺回路であるため、選択信号DET1の方は、DET端子207を介して電源電圧選択部105へと出力される。

【0036】

PLL回路280は、水晶発振器107よりXTAL端子205を介して供給された原クロックSCK2（本発明に係る『第2のクロック』）と同期の合った倍クロックSCK1（本発明に係る『第1のクロック』）を生成する回路である。なお、倍クロックSCK1の周波数f<sub>1</sub>（本発明に係る『第1の周波数』）は、原クロックSCK2の周波数f<sub>2</sub>（本発明に係る『第2の周波数』）よりも、PLL回路280内の分周回路（不図示）の分周数の逆数倍とした周波数である。本実施形態では、倍クロックSCK1の周波数f<sub>1</sub>は「50MHz」とし、原クロックSCK2の周波数f<sub>2</sub>は「12MHz」とする。

【0037】

クロック選択部290は、PLL回路280より出力される倍クロックSCK1及びPLL回路280への入力される前の原クロックSCK2が供給される。そして、クロック選択部290は、電源電圧監視部270から供給された選択信号DET2に基づいて、パーソナルコンピュータ300から電源電圧V<sub>BUS</sub>が供給されている旨が判定された場合には倍クロックSCK1の方を選択してマイクロコンピュータ210へと供給する。また、クロック選択部290は、当該選択信号DET2に基づいて、パーソナルコンピュータ300から電源電圧V<sub>BUS</sub>が供給されていない旨が判定された場合には原クロックSCK2の方を選択してマイクロコンピュータ210へと供給する。

【0038】

すなわち、パーソナルコンピュータ300から携帯オーディオ再生機器100に向けて電源電圧V<sub>BUS</sub>が供給された場合、内部電源104の電力を消費しないように、電源電圧V<sub>DD</sub>よりも高いレベルのレギュレート電源電圧V<sub>REG</sub>が選択されるとともに、レギュレート電源電圧V<sub>REG</sub>が選択されていることを前提として、マイクロコンピュータ210の動作が停止してハングアップしないように、原クロックSCK2よりも高い周波数の倍クロックSCK1の方が選択される。

10

20

30

40

50

## 【0039】

ここで、ASIC200の消費電力は動作クロック周波数に比例するので、高い周波数の倍クロックSCK1を選択したことに伴って、ASIC200の消費電力は原クロックSCK2を選択した場合と比較して増加することになる。しかしながら、この場合、パソコンコンピュータ300から供給された電源電圧V<sub>BUS</sub>に応じたレギュレート電源電圧V<sub>REG</sub>の方を動作電圧として使用するので、内部電源104の電力消費を気にする必要がない。このように、携帯オーディオ再生機器100は、内部電源104の電力消費を気にすることなく、例えば、高周波数の倍クロックSCK1を使用可能となり、ひいては、パソコンコンピュータ300からUSBケーブル400を介した音楽ファイルのデータ転送を高速処理することが可能となる。

10

## 【0040】

また、パソコンコンピュータ300からの音楽ファイルのデータ転送が完了した後であっても、USBインターフェース101にUSBケーブル400を接続したままである場合、パソコンコンピュータ300から電源電圧V<sub>BUS</sub>の供給を受けている状態が継続しているので、引き続き、内部電源104の消費電力を抑えつつ、レギュレート電源電圧V<sub>REG</sub>並びに倍クロックSCK1を使用して、音楽ファイルの再生処理を実行できる。

## 【0041】

一方、USBインターフェース101にUSBケーブル400が接続されておらず、パソコンコンピュータ300から携帯オーディオ再生機器100に向けて電源電圧V<sub>BUS</sub>が供給されていない場合、倍クロックSCK1よりも低い周波数の原クロックSCK2が選択されるので、ASIC200の消費電力は倍クロックSCK1を選択した場合と比較して抑えられる。更に、この場合、レギュレート電源電圧V<sub>REG</sub>よりもレベルが低く、ASIC200を動作させるため最低限必要な電源電圧V<sub>DD</sub>の方が選択されるので、ASIC200の消費電力が更に抑えられる。また、ASIC200の消費電力を抑えられた結果として、音楽ファイルの再生時間を長くすることができる。

20

## 【0042】

<ASICの動作>

====USBケーブルを取り外した場合の動作=====

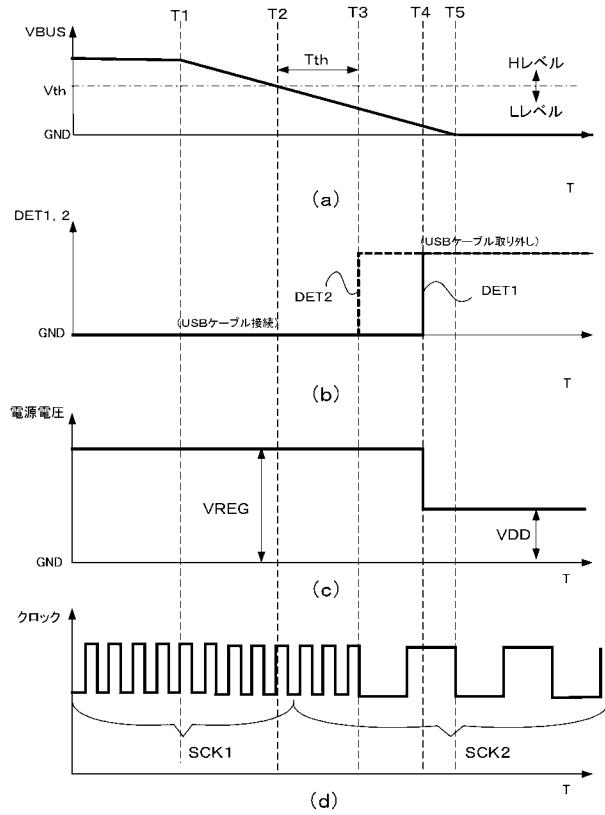

図3を用いて、音楽ファイルのデータ転送が完了したことや突発的な事故等に伴って、USBインターフェース101にUSBケーブル400が接続された状況から、USBケーブル400が取り外された状況へと切り替えた場合におけるASIC200の動作について説明する。なお、図3(a)は、V<sub>BUS</sub>端子206に印加される電圧レベルの波形を示し、図3(b)は、電源電圧監視部270より出力される選択信号DET1、2の波形を示し、図3(c)は、V<sub>DD</sub>端子208へと印加される電源電圧の波形を示し、図3(d)は、クロック選択部290からマイクロコンピュータ210へと供給されるクロックの波形を示した図である。

30

## 【0043】

まず、USBインターフェース101にUSBケーブル400が接続され、パソコンコンピュータ300から携帯オーディオ再生機器100に向けて音楽ファイルのデータ転送並びに電源電圧V<sub>BUS</sub>の供給がなされている場合とする。

40

## 【0044】

従って、V<sub>BUS</sub>端子206に印加される電圧レベルは「5V」であり(図3(a)参照)、電源電圧監視部270においてパソコンコンピュータ300から電源電圧V<sub>BUS</sub>が供給されている旨(DET1、DET2が共にLOWレベル)が判定される(図3(b)参照)。この結果、電源電圧選択部105ではLOWレベルの選択信号DET1に基づいてレギュレート電源電圧V<sub>REG</sub>が選択され(図3(c)参照)、また、クロック選択部290ではLOWレベルの選択信号DET2に基づいて倍クロックSCK1が選択される。

## 【0045】

50

時刻 T 1 では、USB インタフェース 101 から USB ケーブル 400 が取り外される。この場合、時刻 T 1 から時刻 T 5 に向けて、V B U S 端子 206 へと印加される電圧レベルは、電源ライン 102 に接続されたプルダウン抵抗 R d に基づいて「0 V」へと徐々に減衰していく（図 3 (a) 参照）。

#### 【0046】

つぎに、時刻 T 2 では、二値化処理部 271 の出力は、V B U S 端子 206 へと印加された電圧レベルが参照レベル V t h を下回る（図 3 (a) 参照）。しかし、スパイク状の電源ノイズによる誤判定を防ぐために、判定処理部 272 より出力される選択信号 D E T 1、D E T 2 は、L o w レベルのままである（図 3 (b) 参照）。

#### 【0047】

つぎに、時刻 T 2 から一定期間 T t h 経過した時刻 T 3 では、まず、選択信号 D E T 2 を選択信号 D E T 1 より先に L o w レベルから H i g h レベルへと切り替える（図 3 (b) 参照）。この理由は、二値化処理部 271 の出力は L o w レベルを継続しているので、判定処理部 272 は、電源ノイズに起因したレベル変化とは見なさないためである。この結果、クロック選択部 290 では H i g h レベルの選択信号 D E T 2 に基づいて原クロック S C K 2 が選択される（図 3 (d) 参照）。

#### 【0048】

つぎに、時刻 T 5 において V B U S 端子 206 の電圧レベルが「0 V」へと完全に減衰する前の時刻 T 4 では、判定処理部 272 は、選択信号 D E T 1 を L o w レベルから H i g h レベルへと切り替える。この結果、電源電圧選択部 105 では H i g h レベルの選択信号 D E T 1 に基づいて電源電圧 V D D が選択される（図 3 (c) 参照）。

#### 【0049】

このように、クロック選択部 290 は、電源電圧監視部 270 において、パーソナルコンピュータ 300 から電源電圧 V B U S が供給されている旨の判定から、パーソナルコンピュータ 300 から電源電圧 V B U S が供給されていない旨の判定へと切り替わる場合、電源電圧選択部 105 においてレギュレート電源電圧 V R E G の選択から電源電圧 V D D の選択へと切り替えられるよりも先に、遙倍クロック S C K 1 の選択から原クロック S C K 2 の選択へと切り替える。

#### 【0050】

すなわち、遙倍クロック S C K 1 の使用は、あくまで、レギュレート電源電圧 V R E G の供給が前提条件である。このため、USB ケーブル 400 の取り外しに伴って、高周波数の遙倍クロック S C K 1 から低周波数の原クロック S C K 2 へと切り替えた上で、高レベルのレギュレート電源電圧 V R E G から低レベルの電源電圧 V D D へと切り替える。

#### 【0051】

＝＝＝USB ケーブルを接続した場合の動作＝＝＝

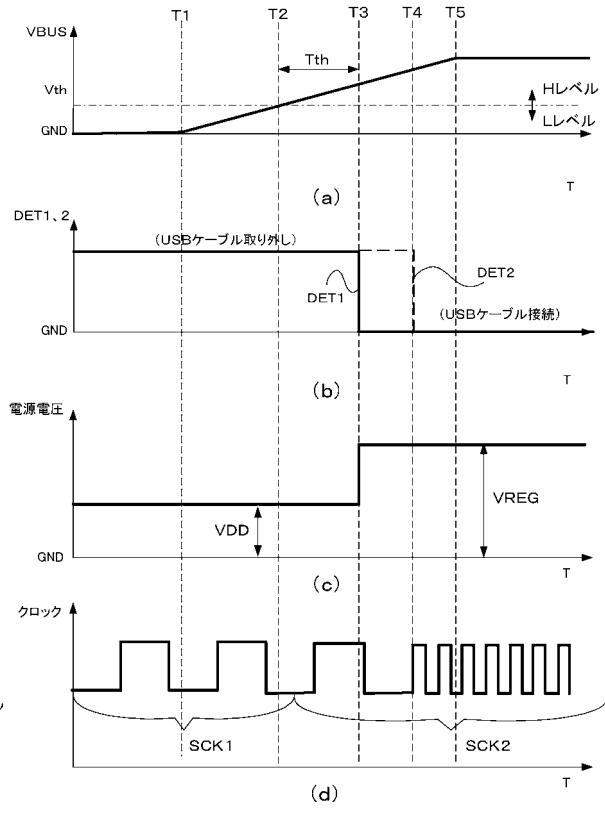

図 4 を用いて、音楽ファイルのデータ転送を行うべく、USB インタフェース 101 から USB ケーブル 400 が取り外された状況から、USB インタフェース 101 に USB ケーブル 400 を接続した状況へと切り替えた場合における A S I C 200 の動作について説明する。なお、図 4 (a) 乃至 (d) は、図 3 (a) 乃至 (d) それぞれと同様の波形を示した図である。

#### 【0052】

まず、USB インタフェース 101 から USB ケーブル 400 が取り外されており、携帯オーディオ再生機器 100 はパーソナルコンピュータ 300 から電源電圧 V B U S の供給を受けていない場合とする。

#### 【0053】

従って、V B U S 端子 206 に印加される電圧レベルは「0 V」であり（図 4 (a) 参照）、電源電圧監視部 270 においてパーソナルコンピュータ 300 から電源電圧 V B U S が供給されていない旨（D E T 1、D E T 2 が共に H i g h レベル）が判定される（図 4 (b) 参照）。この結果、電源電圧選択部 105 では H i g h レベルの選択信号 D E T 1 に基づいて電源電圧 V D D の方が選択され（図 4 (c) 参照）、また、クロック選択部

10

20

30

40

50

290ではHighレベルの選択信号DET2に基づいて原クロックSCK2の方が選択される。

【0054】

時刻T1では、USBインターフェース101にUSBケーブル400を接続する。この場合、時刻T1から時刻T5に向けて、VBUS端子206へと印加される電圧レベルは、「0V」から「5V」へと徐々に上昇していく(図4(a)参照)。

【0055】

つぎに、時刻T2では、二値化処理部271の出力は、VBUS端子206へと印加された電圧レベルが参照レベルVthを上回る(図4(a)参照)。しかし、スパイク状の電源ノイズによる誤判定を防ぐために、判定処理部272から出力される選択信号DET1、DET2は、Highレベルのままである(図4(b)参照)。

【0056】

つぎに、時刻T2から一定期間Tth経過した時刻T3では、まず、選択信号DET1を選択信号DET2より先にHighレベルからLowレベルへと切り替える(図4(b)参照)。この理由は、二値化処理部271の出力はHighレベルを継続しているので、判定処理部272は、電源ノイズに起因したレベル変化とは見なさないためである。なお、時刻T1から時刻T3までの期間中では、レギュレート回路103によってレギュレート電源電圧VREGが生成されている。この結果、電源電圧選択部105ではLowレベルの選択信号DET1に基づいてレギュレート電源電圧VREGが選択される(図4(c)参照)。

【0057】

つぎに、時刻T5においてVBUS端子206の電圧レベルが「5V」へと完全に上昇する前の時刻T4では、判定処理部272は、選択信号DET2をHighレベルからLowレベルへと切り替える。この結果、クロック選択部290ではLowレベルの選択信号DET2に基づいて遅倍クロックSCK1が選択される(図4(d)参照)。

【0058】

このように、クロック選択部290は、電源電圧監視部270において、パーソナルコンピュータ300から電源電圧V<sub>BUS</sub>が供給されていない旨の判定から、パーソナルコンピュータ300から電源電圧V<sub>BUS</sub>が供給されている旨の判定へと切り替わった場合、電源電圧選択部105において電源電圧VDDの選択からレギュレート電源電圧V<sub>REG</sub>の選択へと切り替えられるよりも後に、原クロックSCK2の選択から遅倍クロックSCK1の選択へと切り替える。

【0059】

すなわち、遅倍クロックSCK1の使用は、あくまで、レギュレート電源電圧V<sub>REG</sub>の供給が前提条件である。このため、USBケーブル400を接続したことに伴って、低レベルの電源電圧VDDから高レベルのレギュレート電源電圧V<sub>REG</sub>へと切り替えた上で、低周波数の原クロックSCK2から高周波数の遅倍クロックSCK1へと切り替える。

【0060】

以上、本発明の実施形態について説明したが、前述した実施形態は、本発明の理解を容易にするためのものであり、本発明を限定して解釈するためのものではない。本発明は、その趣旨を逸脱することなく、変更/改良され得るとともに、その等価物も含まれる。

【図面の簡単な説明】

【0061】

【図1】本発明に係る信号処理装置の外部接続を説明するための図である。

【図2】本発明に係る信号処理装置の構成を示す図である。

【図3】本発明に係る集積回路の動作を説明するための主要信号の波形図である。

【図4】本発明に係る集積回路の動作を説明するための主要信号の波形図である。

【符号の説明】

【0062】

10

20

30

40

50

100 携帯オーディオ再生機器

102、402 電源ライン

104 内部電源

106 不揮発性メモリ

200 A S I C

202 D - 端子

204 O U T 端子

206 V B U S 端子

208 V D D 端子

220、310 U S B コントローラ

240 D S P

260 D A 変換器

271 二値化処理部

280 P L L 回路

300 パーソナルコンピュータ

340 メモリ

360 電源アダプタ

400 U S B ケーブル

403 G N D ライン

101、320 U S B インタフェース

103 レギュレート回路

105 電源電圧選択部

107 水晶発振器

201 D + 端子

203 M I 端子

205 X T A L 端子

207 D E T 端子

210 マイクロコンピュータ

230 メモリインターフェース回路

250 R A M

270 電源電圧監視部

272 判定処理部

290 クロック選択部

330 C P U

350 ハードディスク

361 電源プラグ

401 データライン

10

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(56)参考文献 特開平04-097408(JP,A)

特開2003-256073(JP,A)

特開2004-070805(JP,A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| G 0 6 F | 1 / 0 4     |

| G 0 6 F | 1 / 3 2     |

| H 0 1 L | 2 1 / 8 2 2 |

| H 0 1 L | 2 7 / 0 4   |