## (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) . Int. Cl.<sup>7</sup>

H01L 21/335

(45) 공고일자 2005년08월18일

(11) 등록번호 10-0508840

(24) 등록일자 2005년08월09일

(21) 출원번호

(22) 출원일자

10-2003-0062948

2003년09월09일

(65) 공개번호

(43) 공개일자

10-2004-0024501

2004년03월20일

(30) 우선권주장

JP-P-2002-00268970

2002년09월13일

일본(JP)

(73) 특허권자

가부시끼가이샤 도시바

일본국 도쿄도 미나토구 시바우라 1초메 1방 1고

(72) 발명자

이즈하미쓰아끼

일본도쿄도미나토구시바우라1초메1방1고가부시끼가이샤도시바지적재

산부내

이이누마도시히코

일본도쿄도미나토구시바우라1초메1방1고가부시끼가이샤도시바지적재

산부내

스구로교이찌

일본도쿄도미나토구시바우라1초메1방1고가부시끼가이샤도시바지적재

산부내

(74) 대리인

장수길

구영창

심사관 : 정회환

#### (54) 살리사이드 프로세스를 이용하여 형성된 MOSFET 및 그 제조 방법

#### 요약

반도체 장치는, MOSFET을 구비하고 있다. 이 MOSFET는, 소스/드레인 영역, 게이트 절연막, 게이트 전극 및 제1, 제2, 제3 금속 실리사이드막을 구비한다. 소스/드레인 영역은, 반도체 기판의 주표면 영역 내에 형성된다. 게이트 절연막은, 소스/드레인 영역 사이의 채널 영역 상에 형성된다. 게이트 전극은, 상기 게이트 절연막 상에 형성되고, Ge/(Si+Ge) 조성비가  $x$ ( $0 < x < 0.2$ )인 poly-Si<sub>1-x</sub>Ge<sub>x</sub>층을 포함한다. 제1 금속 실리사이드막은, 상기 게이트 전극 상에 형성되고, NiSi<sub>1-y</sub>Ge<sub>y</sub>로 이루어진다. 제2, 제3 금속 실리사이드막은, 상기 소스/드레인 영역 상에 각각 형성되고, NiSi로 이루어진다.

#### 대표도

도 1

#### 색인어

MOSFET, 소스/드레인 영역, 게이트 전극, 게이트 절연막, 금속 실리사이드 막, 실리사이드

### 명세서

#### 도면의 간단한 설명

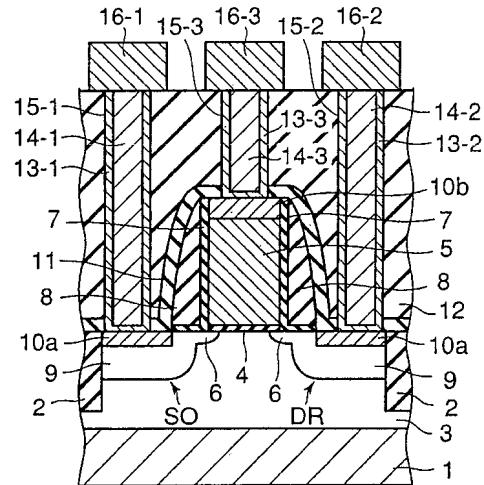

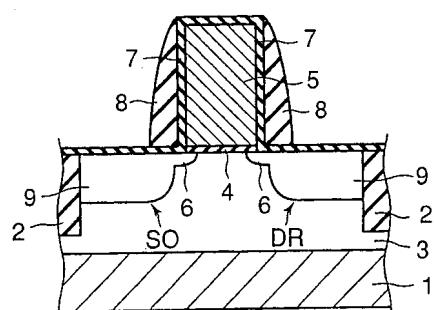

도 1은 본 발명의 실시 형태에 따른 반도체 장치에 대하여 설명하기 위한 것으로, MOSFET의 단면 구성도.

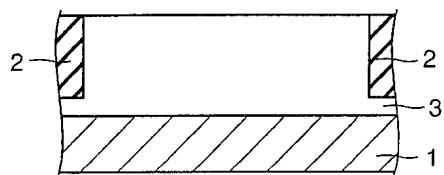

도 2는 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법에 대하여 설명하기 위한 것으로, 도 1의 MOSFET의 제조공정을 도시하고 있고, 제1 공정의 단면도.

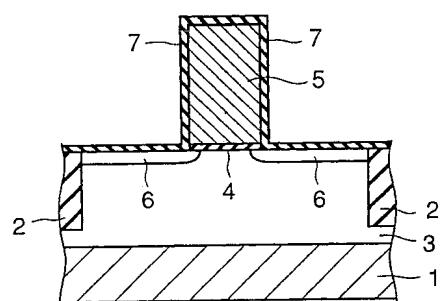

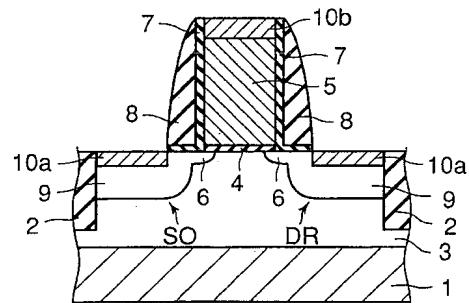

도 3은 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법에 대하여 설명하기 위한 것으로, 도 1의 MOSFET의 제조공정을 도시하고 있고, 도 2에 계속되는 제2 공정의 단면도.

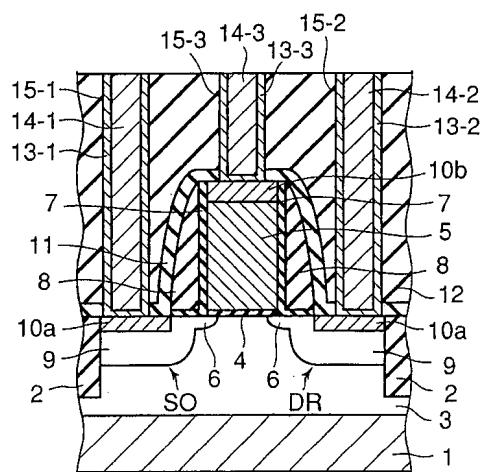

도 4는 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법에 대하여 설명하기 위한 것으로, 도 1의 MOSFET의 제조공정을 도시하고 있고, 도 3에 계속되는 제3 공정의 단면도.

도 5는 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법에 대하여 설명하기 위한 것으로, 도 1의 MOSFET의 제조공정을 도시하고 있고, 도 4에 계속되는 제4 공정의 단면도.

도 6은 본 발명의 실시 형태에 따른 반도체 장치의 제조 방법에 대하여 설명하기 위한 것으로, 도 1의 MOSFET의 제조공정을 도시하고 있고, 도 5에 계속되는 제5 공정의 단면도.

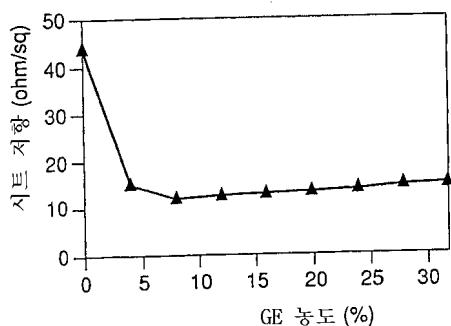

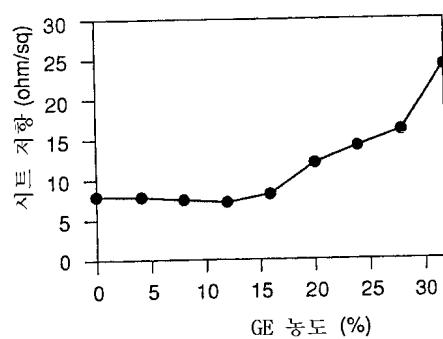

도 7은 p 채널형 MOSFET의 봉소가 도핑된 게이트 전극 상에 형성된 금속 실리사이드막의 Ge 농도와 시트 저항과의 관계를 도시하는 특성도.

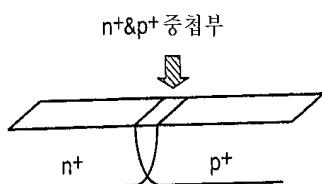

도 8a는 실제의 디바이스에 있어서의 p형 및 n형의 불순물의 중첩부의 개념에 대하여 설명하기 위한 모식도.

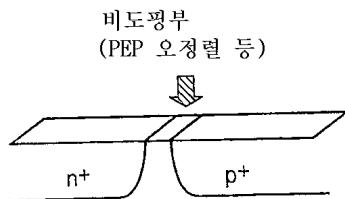

도 8b는 실제의 디바이스에 있어서의 PEP의 오정렬 등에 의한 비도핑부의 개념에 대하여 설명하기 위한 모식도.

도 9는 비도핑부를 갖는 게이트 전극 상의 금속 실리사이드막에 있어서의 Ge 농도와 시트 저항과의 관계를 도시하는 특성도이다.

#### <도면의 주요 부분에 대한 부호의 설명>

1 : 기판

2 : 소자 분리 구조

3 : 웰 영역

4 : 게이트 절연막

5 : 게이트 전극

6 : 저농도의 불순물 확산 영역

8 : 측벽 절연막

9 : 고농도의 불순물 확산 영역

10a, 10b : 금속 실리사이드막

13-1, 13-2, 13-3 : 배리어 메탈층

14-1, 14-2, 14-3 : 텅스텐(W) 플러그

15-1, 15-2, 15-3 : 컨택트홀

16-1 : 소스 배선

16-2 : 드레인 배선

16-3 : 게이트 배선

SO, DR : 소스/드레인 영역

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 반도체 장치 및 그 제조 방법에 관한 것이다. 특히 살리사이드 프로세스를 이용하여 형성된 트랜지스터(MOSFET)와 그 제조 방법에 관한 것으로, 게이트 전극 및 소스/드레인 영역과 이들의 인출 전극과의 컨택트부에 적용되는 것이다.

최근, MOSFET에서의 게이트 전극의 재료로서, 공핍화를 억제하기 위해서 poly-SiGe를 도입하는 검토가 진행되고 있다. 그러나, 현재, 컨택트 재료로서 주로 이용되고 있는  $\text{CoSi}_2$ 는, 제1 저온 RTA(400 °C 정도)에서는  $\text{Co}(\text{Si}_{1-y}\text{Ge}_y)$ 를 형성하지만, 제2 온도 RTA(700 °C 정도)에서는 Ge를 토출하여 Ge-rich한 아일런드의 SiGe 층과  $\text{CoSi}_2$ 를 형성한다. 그 결과, 시트 저항의 현저한 상승이 나타난다(예를 들면, Z.Wang, D.B.Aldrich, Y.L.Chen, D.E.Sayers and R.J.Nemanich, Thin Solid Films, Vol.270(1995)555-560. 참조). 이 때문에, 게이트 전극에 poly-SiGe를 이용하는 경우에는,  $\text{CoSi}_2$ 과의 계면에 poly-Si 캡층을 도입할 필요가 있는 것이 알려져 있다.

또한, 게이트 길이가 50 nm 세대 이후의 MOSFET에서는, 살리사이드 프로세스를 적용하기 위한 컨택트 재료로서  $\text{NiSi}$ 가 검토되고 있다. 이  $\text{NiSi}$ 의 결점으로서는, 지금까지 이용되어 온  $\text{TiSi}_2$ 나  $\text{CoSi}_2$ 에 비교하여 내열성이 낮은 것을 들 수 있다. 그러나, poly-SiGe 상에  $\text{NiSi}$ 를 컨택트재로서 이용하는 경우, 상술한  $\text{CoSi}_2$ 에서 나타났던 것 같은 poly-SiGe와의 심한 부정합은 생기지 않는다. 보다 내열성을 향상시키기 위해서 「인출 전극(28)의 하층 층에  $\text{Si}_x(\text{Ge}_y\text{C}_{1-y})_{1-x}$  화합물층(28a)을 이용한다」라는 제안이 되어 있다(예를 들면, 일본국 특허 공개 공보 H11-214680호 참조).

이 일본국 특허 공보에 기재된 발명의 요지는, 게이트 전극 또는 소스/드레인 확산층과의 계면 부정합을 작게 함으로써, 후열공정 후의 쇼트키 장벽 변화와, 그것에 수반하는 컨택트 저항의 변화를 억제한다고 하는 것이다.

#### 발명이 이루고자 하는 기술적 과제

그런데, 상기 내열성과는 별도로, 고온의 열공정 후에 Ni 실리사이드의 시트 저항이 증가한다고 하는 문제가 알려져 있다. 이 원인으로서는, 고비저항의  $\text{NiSi}_2$ 의 형성(상전이)이나 응집이 생각되고 있다.

그 대책으로서, Ni/Si 및 Ni/SiGe 계면에 Co 중간층을 도입하는 보고가 되어 있다(예를 들면, J-S.Maa, D.J.Tweet, Y.Ono, L.Stecker and S.T.Hsu, Mat.Res.Soc.Symp.Proc.Vol.1670, K6.9.1(2001). 참조). 그러나, 제조 프로세스가 증가하는, 등의 집적화하는 데에 있어서의 과제가 늘어나게 된다.

#### 발명의 구성 및 작용

본 발명의 한 양상에 따르면, MOSFET을 구비하는 반도체 장치로서, 상기 MOSFET은 반도체 기판의 주표면 영역 내에 형성되는 소스/드레인 영역, 상기 소스/드레인 영역 사이의 채널 영역 상에 형성되는 게이트 절연막, 상기 게이트 절연막 상에 형성되고, Ge/(Si+Ge) 조성비가  $x(0 < x < 0.2)$ 인 poly-Si<sub>1-x</sub>Ge<sub>x</sub> 층을 포함하는 게이트 전극, 상기 게이트 전극 상에 형성되고, NiSi<sub>1-y</sub>Ge<sub>y</sub>로 이루어지는 제1 금속 실리사이드막, 및 상기 소스/드레인 영역 상에 각각 형성되고, NiSi로 이루어지는 제2, 제3 금속 실리사이드막을 포함한다.

본 발명의 다른 양상에 따르면, 반도체 장치를 제조하는 방법에 있어서, 반도체 기판 상에 게이트 절연막을 형성하는 단계, 상기 게이트 절연막 상에 Ge/(Si+Ge) 조성비가  $x(0 < x < 0.2)$ 인 poly-Si<sub>1-x</sub>Ge<sub>x</sub> 층을 포함하는 게이트 전극을 형성하는 단계, 상기 반도체 기판의 주표면 영역 내에 불순물을 도입하여 소스/드레인 영역을 형성하는 단계, 상기 게이트 전극 상 및 상기 소스/드레인 영역 상에 Ni 막을 형성하는 단계, 및 열처리를 행하여, 상기 게이트 전극 상의 Ni 막을 NiSi<sub>1-y</sub>Ge<sub>y</sub> 막으로 치환하고, 또한 상기 소스/드레인 영역 상의 Ni 막을 NiSi 막으로 치환하는 단계를 포함한다.

#### <실시 형태>

도 1은, 본 발명의 실시 형태에 따른 반도체 장치에 대하여 설명하기 위한 것으로, MOSFET의 단면도이다.

기판(1)은, N형 실리콘 기판 또는 P형 실리콘 기판이고, 이 기판(1)의 주표면에는 예를 들면 매립 소자 분리법 등에 의해 소자 분리 구조(2)가 형성되어 있다. 또한, 이 소자 분리 구조(2)로 구획된 기판(1)의 능동 소자 영역 내에는, P형 또는 N형의 웰 영역(3)이 형성되어 있다. 이 웰 영역(3) 내에는, 채널 영역을 사이에 두고 소스/드레인 영역 SO, DR가 형성되어 있다. 이 소스/드레인 영역 SO, DR는, 소스/드레인 익스텐션을 갖는 구조이고, 고농도의 불순물 확산 영역(9, 9)과, 이들 영역(9, 9)에 있어서의 채널 영역의 근방에 형성된 저농도의 불순물 확산 영역(6, 6)으로 형성된다. 이 소스/드레인 영역 SO, DR에서의, 상기 고농도의 불순물 확산 영역(9, 9) 상에는, 실리사이드 프로세스에 의해 금속 실리사이드막(NiSi)(10a)이 형성되어 있다.

상기 소스/드레인 영역 SO, DR 사이의 채널 영역 상에는, 게이트 절연막(4)이 형성되어 있다. 이 게이트 절연막(4)의 재료는, 실리콘 산화막이어도 되지만, 실리콘 질화막을 포함하고 있는 편이 바람직하다. 상기 게이트 절연막(4) 상에는, 게이트 전극(5)이 형성되어 있다. 이 게이트 전극(5)은, poly-Si<sub>0.88</sub>Ge<sub>0.12</sub>층의 1층 구조, 또는 poly-Si 층상에 poly-Si<sub>0.88</sub>Ge<sub>0.12</sub>층이 적층된 2층 구조로 되어 있다. 이 poly-Si<sub>0.88</sub>Ge<sub>0.12</sub>층은, Ge/(Si+Ge) 조성비가  $x(0 < x < 0.2)$ , 보다 바람직하게는  $0.04 \leq x \leq 0.16$ 인 poly-Si<sub>1-x</sub>Ge<sub>x</sub>가 적합하고, 여기서는 그 일례로서 poly-Si<sub>0.88</sub>Ge<sub>0.12</sub>를 이용하고 있다.

상기 게이트 전극(5) 상에는, 실리사이드 프로세스에 의해 금속 실리사이드막(NiSi<sub>1-y</sub>Ge<sub>y</sub>( $y$ 는  $x$ 와 거의 같다), 예를 들면 NiSi<sub>0.88</sub>Ge<sub>0.12</sub>)(10b)가 형성되어 있다. 상기 게이트 전극(5)의 측벽부에는, 후산화막(7, 7)으로서의 실리콘 산화막과, 측벽 절연막(8, 8)이 형성되어 있다. 상기 측벽 절연막(8, 8)은, 상기하였던 것 같은 소스/드레인 영역 SO, DR를 형성하기 위해서 제조 프로세스 상에서 필요한 구조로서, 예를 들면 실리콘 질화막과 실리콘 산화막으로 형성된다. 또, 상기 게이트 전극(5)의 측벽부에는, 오프셋 스페이서가 형성되어 있어도 된다.

상기 MOSFET 상에는, 예를 들면 실리콘 질화막(11)과 실리콘 산화막(12)을 포함하는 층간 절연막이 형성되어 있다. 이 층간 절연막의 상기 소스/드레인 영역 SO, DR(금속 실리사이드(10a, 10b))에 대응하는 위치, 및 게이트 전극(5)(금속 실리사이드(10b))에 대응하는 위치에는, 컨택트홀(15-1, 15-2, 15-3)이 형성되어 있다. 이들 컨택트홀(15-1, 15-2, 15-3) 내에는, TiN 또는 TiN과 Ti가 적층된 배리어 메탈층(13-1, 13-2, 13-3)을 개재하여 텅스텐(W) 플러그(14-1, 14-2, 14-3)가 매립 형성되어 있다.

그리고, 상기 층간 절연막 상에, 상기 W 플러그(14-1, 14-2, 14-3)와 각각 전기적으로 접속된 상태에서, 소스 배선(16-1), 드레인 배선(16-2) 및 게이트 배선(16-3) 등의 인출 전극이 형성되어 있다.

본 실시 형태에서 기술한 바와 같이, MOSFET의 게이트 전극 재료로서,  $x(0 < x < 0.2)$ , 보다 바람직하게는  $0.04 \leq x \leq 0.16$ 인 poly-Si<sub>1-x</sub>Ge<sub>x</sub> 층을 이용함으로써, 게이트 전극(5) 상의 금속 실리사이드(10b)의 시트 저항의 상승을 억제할 수 있다. 이에 따라, 트랜지스터의 기생 저항을 저감할 수 있고, 스위칭 속도를 고속화할 수 있다.

그런데, 상술한 바와 같이 게이트 전극(5)으로서는, poly-Si<sub>1-x</sub>Ge<sub>x</sub>의 1층 구조나, poly-Si<sub>1-x</sub>Ge<sub>x</sub>/poly-Si 와 같은 2층 구조(poly-Si가 게이트 절연막과의 계면층)가 이용되지만, 이 때의 poly-Si<sub>1-x</sub>Ge<sub>x</sub> 층의 막 두께가 얇으면, Ni가 Si<sub>1-x</sub>Ge<sub>x</sub>를 관통하여 Si와 우선적으로 반응하게 된다. Ni인 경우, 반응에 의해서 소비되는 기초 Si<sub>1-x</sub>Ge<sub>x</sub>의 막 두께는, 반응 전의 Ni 막 두께와 같은 정도이다. 또한, NiSi<sub>1-y</sub>Ge<sub>y</sub>/Si<sub>1-x</sub>Ge<sub>x</sub> 계면의 모폴로지 불균일성에 따른 마진을 고려하면, 반응 전의 Ni 막 두께의 적어도 2배 정도의 막 두께가 바람직하다.

또, 본 발명자 등의 실험에 따르면, Si<sub>1-x</sub>Ge<sub>x</sub>의 막 두께가 얇을 때에는, 시트 저항의 상승이 나타나고, 단면 TEM 관찰을 행한 바 Ni 실리사이드가 Si<sub>1-x</sub>Ge<sub>x</sub>를 관통하여 Si와 반응하여 응집하고 있었다. 이것은, Ni-Ge의 결합보다 Ni-Si의 결합 쪽이 에너지 적으로 안정적이기 때문에, NiSi<sub>1-y</sub>Ge<sub>y</sub>보다도 NiSi로 진행하기 때문이라고 생각할 수 있다.

상기한 바와 같은 구성에 따르면, 컨택트 재료로서 NiSi를 이용하는 경우에, 고온의 후열공정에 의해 소스/드레인 영역이나 게이트 전극과의 계면 저항의 상승이나 시트 저항의 상승 등의 내열성의 문제를 회피하고 트랜지스터의 스위칭 속도를 고속화할 수 있다.

다음에, 상기 도 1에 도시한 MOSFET의 제조 방법에 대하여 설명한다. 도 2 내지 도 6은 각각, 상기 도 1에 도시한 MOSFET의 제조 방법을 공정 순으로 도시하는 단면도이다.

우선, 도 2에 도시한 바와 같이, P형 실리콘 기판 또는 N형 실리콘 기판(1)에, 예를 들면 매립 소자 분리법 등에 의해, 깊이 300 nm 정도의 소자 분리 구조(2)를 형성한다. 그 후, 열 산화를 행하여 능동 소자 영역 상에 10 nm 정도의 실리콘 산화막을 형성하고, 이 산화막 너머로 상기 기판(1) 내에 불순물을 이온 주입하여, 웰 영역(3) 및 채널 스토퍼를 형성한다. 이 때의, 전형적인 이온 주입 조건으로서는, 예를 들면 P 웰 영역을 형성하는 경우에는 봉소(B)를 가속 에너지 260 KeV, 도우즈량 2.0×10<sup>13</sup> cm<sup>-2</sup>의 조건, N 웰 영역에서는 인(P)을 가속 에너지 500 KeV, 도우즈량 2.5×10<sup>13</sup> cm<sup>-2</sup>의 조건이다.

그 후, 도 3에 도시한 바와 같이, 능동 소자 영역 상에 게이트 절연막(4)(Si<sub>3</sub>N<sub>4</sub>, SiO<sub>2</sub>+Si<sub>3</sub>N<sub>4</sub>, 또는 SiO<sub>x</sub>N<sub>y</sub>+Si<sub>3</sub>N<sub>4</sub>)을 1~5 nm의 두께로 형성한다. 계속해서, 이 게이트 절연막(4) 상에 예를 들면 poly-Si<sub>0.88</sub>Ge<sub>0.12</sub>(또는 poly-Si, poly-Si<sub>0.88</sub>Ge<sub>0.12</sub>의 순으로)를 성막하여 패터닝함으로써 게이트 전극(5)을 형성한다. 계속해서, 후산화 공정을 행하여 상기 기판(1)의 주표면 상, 상기 게이트 전극(5)의 상면과 측벽에 각각 후산화막(7)을 형성한다. 다음에, 필요에 따라 상기 게이트 전극(5)의 측벽에 오프셋 스페이서를 형성한 후(도시 생략), 상기 게이트 전극(5)을 마스크로 하여, 기판(1)의 주표면 영역 내에 이온 주입을 행하여, 소스/드레인 익스텐션(저농도의 불순물 확산 영역(6, 6))을 형성한다. 상기 익스텐션을 형성하기 위한 전형적인 이온 주입 조건은, N형으로는 비소(As)를 가속 에너지 10 KeV, 도우즈량 5×10<sup>14</sup> cm<sup>-2</sup>의 조건, P형으로는 BF<sub>2</sub>을 가속 에너지 7 KeV, 도우즈량 5×10<sup>14</sup> cm<sup>-2</sup>의 조건이다.

다음에, 도 4에 도시한 바와 같이, 800 °C 정도의 활성화 RTA(급속 열어닐링 처리)를 실시한 후, CVD법, 이방성 에칭법 등의 기술에 의해 실리콘 질화막과 실리콘 산화막을 포함하는 측벽 절연막(8, 8)을 형성한다. 그 후, 상기 게이트 전극(5) 및 측벽 절연막(8, 8)을 마스크로 하여, 기판(1)의 주표면 영역 내에 이온 주입을 행함으로써, 깊은 접합부(고농도의 불순물 확산 영역(9, 9))를 형성한다. 이 깊은 접합부를 형성하기 위한 전형적인 이온 주입 조건은, N형으로는 As를 가속 에너지 50 KeV, 도우즈량 7×10<sup>15</sup> cm<sup>-2</sup>의 조건, P형으로는 B를 가속 에너지 5 KeV, 도우즈량 4×10<sup>15</sup> cm<sup>-2</sup>의 조건이다. 그 후, 약 1000 °C 정도의 활성화 RTA를 행함으로써, 소스/드레인 영역 SO, DR로서 기능하는 불순물 확산층의 도우편트의 활성화를 행한다.

다음에, 상기 후산화막(7)이 소스/드레인 영역 SO, DR 상 및 게이트 전극(5) 상에 잔존하고 있으면 약물 처리에 의해 박리한다. 그 후, 스퍼터법(또는 CVD법)을 이용하여 전면에 Ni 막을 성막한다. 이 Ni 막의 막 두께는, 10~15 nm 정도로 한다. Ni 막의 막 두께를 두껍게 하면 할수록, 응집에 의한 시트 저항의 상승은 억제할 수 있지만, 반대로 접합 누설 레벨이 상승하기 때문에, 상기 10~15 nm 정도가 바람직하다. 다음에, 500 °C의 RTA에 의해 소스/드레인 영역 SO, DR 상 및 게이트 전극(5) 상의 Ni 막을, 각각 금속 실리사이드막(NiSi)(10a) 및 금속 실리사이드막(NiSi<sub>0.88</sub>Ge<sub>0.12</sub>)(10b)으로 치환한다. RTA 온도가 450 °C 이하와 같이 낮은 경우에는, 반응이 충분히 진행하지 않고 Ni<sub>2</sub>Si<sub>0.88</sub>Ge<sub>0.12</sub>가 NiSi<sub>0.88</sub>Ge<sub>0.12</sub> 표면

에 잔존하고 있었다. 이  $\text{Ni}_2\text{Si}_{0.88}\text{Ge}_{0.12}$ 가 잔존한 상태에서,  $\text{HCl}$ 과  $\text{H}_2\text{O}_2$ 나  $\text{O}_3$ 를 포함한 약물 처리를 행하면, 과잉  $\text{Ni}$ 와 악물이 반응하여 막 박리를 발생시켰다. 또한, 박리부를 분석하면 그 개소의  $\text{Ni}$ 는 소실되고,  $\text{SiO}_2$ 층이 관찰되었다. 이어서, 미반응의 금속( $\text{Ni}$  막)을 선택 에칭에 의해 제거하면, 도 5에 도시한 바와 같이 된다.

그 후, 도 6에 도시한 바와 같이, 전면에 실리콘 질화막(11) 및 실리콘 산화막(12)을 층간 절연막으로서 퇴적 형성한 후, CMP 처리에 의해 표면의 평탄화를 행한다. 계속해서, RIE에 의해, 소스/드레인 영역  $\text{SO}_x$ ,  $\text{DR}$  및 게이트 전극(5)의 인출 전극 형성을 위한 컨택트홀(15-1, 15-2, 15-3)을 개구한다. 그리고,  $\text{Ti}$ 를 CVD 성막한 후,  $\text{N}_2$  분위기(또는  $\text{NH}_3$  분위기, 또는 FG (3%의  $\text{H}_2$ 를 포함하는  $\text{N}_2$ ) 분위기) 속에서 550 °C 정도의 온도에 의해 60분간의 어닐링을 실시하여 질화함으로써, 적어도 일부를  $\text{TiN}$ 으로 한 배리어 메탈층(13-1, 13-2, 13-3)을 형성한다. 이 어닐링은, 금속 실리사이드(10a, 10b) 형성 후의 최고 온도 열공정으로 되어있다. 또한, CVD법에 의해 텅스텐(W) 플러그(14-1, 14-2, 14-3)를 매립 형성하고, CMP를 행함으로써 층간 절연막의 표면을 평탄화한다.

그 후, 알루미늄 등의 금속을 증착한 후, 패터닝하여 소스 배선(16-1), 드레인 배선(16-2) 및 게이트 배선(16-3) 등의 인출 전극을 형성하고, 도 1에 도시하였던 것 같은 MOSFET를 형성한다.

본 실시 형태에서 중요한 것은, 게이트 전극 재료인  $\text{poly-Si}_{1-x}\text{Ge}_x$ 의  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비이다. 도 7은, p 채널형 MOSFET의 봉소(B)가 도핑된 게이트 전극( $\text{poly-Si}_{1-x}\text{Ge}_x$ ) 상에 형성된 금속 실리사이드( $\text{NiSi}_{1-y}\text{Ge}_y$ )막의  $\text{Ge}$  농도( $\text{Ge}$  concentration)와 게이트 전극 상의 금속 실리사이드의 시트 저항(Sheet resistance)과의 관계를 도시하고 있다. 바꾸어 말하면,  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비에 대한 시트 저항의 의존성을 도시하고 있다. 도 7로부터 분명한 바와 같이, 조성비  $\text{Ge}/(\text{Si} + \text{Ge})$ 가 0~0.16(0~16%)의 범위에서는 시트 저항은 거의 변화하지 않지만, 0.2(20%) 이상에서는 시트 저항의 급격한 상승이 보인다.

이 경향은, n 채널형 MOSFET의 인(P) 또는 비소(As)를 도핑한 게이트 전극  $\text{poly-Si}_{1-x}\text{Ge}_x$  상의 금속 실리사이드( $\text{NiSi}_{1-y}\text{Ge}_y$ )막에 있어서도 마찬가지이다.

그런데, 실제의 디바이스에서는, 도 8a에 도시한 바와 같은 p형 및 n형의 불순물의 중첩부나, 도 8b에 도시한 바와 같은 PEP의 오정렬 등에 의한 비도핑부가 존재한다.

도 9는, 상기 도 8b에 상당하는 비도핑부를 갖는 게이트 전극( $\text{poly-Si}_{1-x}\text{Ge}_x$ ) 상의 금속 실리사이드( $\text{NiSi}_{1-y}\text{Ge}_y$ )막에 있어서의  $\text{Ge}$  농도( $\text{Ge}$  concentration)와 시트 저항(Sheet resistance)과의 관계를 도시하고 있다. 즉, 시트 저항의  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비에 대한 의존성을 도시하고 있다. 이 경우에는, 도 7에 도시한 경우와는 경향이 전혀 다르고, 게이트 전극( $\text{poly-Si}_{1-x}\text{Ge}_x$ )의  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비가 0에 대응하는 게이트 전극( $\text{poly-Si}$ )에서 시트 저항의 상승이 나타났다. 물리 해석으로서, 단면 SEM 관찰 및 EDX 분석을 한 바,  $\text{poly-Si}$  층을 포함하는 게이트 전극 상의  $\text{NiSi}_2$ 막으로는  $\text{NiSi}_2$ 막에의 상전이를 따라 응집이 생기고 있는 것이 관측되었다. 한편, 본 실시 형태에 이용한  $\text{poly-Si}_{0.88}\text{Ge}_{0.12}$ 층을 포함하는 게이트 전극 상의  $\text{NiSi}_{0.88}\text{Ge}_{0.12}$ 막으로서는 상전이는 관측되지 않았다.

여기서, 도 9에 도시한  $\text{poly-Si}$ 와  $\text{Si}_{1-x}\text{Ge}_x$ 의 결정 입경은, 거의 같은 것을 이용하였다. 내열성의 경향으로서는, 이 결정 입경이 커질수록 응집이 진행하기 쉽고, 시트 저항도 상승한다. 또한, 결정 입경이 작은 경우에는 응집은 진행하기 어렵지만,  $\text{NiSi}_2$ 에의 상전이가 일어나기 쉽게 되고, 이에 따라 시트 저항 상승이 나타났다.

상기 실시 형태에서 기술한 바와 같이,  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비가  $x(0 < x < 0.2)$ , 보다 바람직하게는  $0.04 \leq x \leq 0.16$ 인  $\text{poly-Si}_{1-x}\text{Ge}_x$ 층을 포함하는 게이트 전극 재료를 선택함으로써, 상기 불순물을 도핑한  $\text{poly-Si}_{1-x}\text{Ge}_x$ 층을 포함하는 게이트 전극과, 비도핑의  $\text{poly-Si}_{1-x}\text{Ge}_x$ 로 이루어지는 게이트 전극의 쌍방의 시트 저항의 상승을 억제할 수 있다.

따라서, 금속 실리사이드 형성 후에 열공정을 실시한 MOSFET에서, 게이트 전극 상의 금속 실리사이드의 시트 저항의 상승을 억제할 수 있다. 이 시트 저항의 상승의 억제에 의해서, 그것에 수반하는 트랜지스터의 기생 저항의 저감에 따른 스위칭 속도의 고속화가 가능해진다. 게다가, 여러 가지의 패턴부, 예를 들면 PEP의 오정렬에 의한 비도핑부에서의 시트 저항의 상승도 억제할 수 있기 때문에, 제조 수율과 신뢰성을 향상시킬 수 있다.

또, 상술한 실시 형태에서는, Ni와 SiGe의 조합을, 게이트 전극에 대하여 설명하였다. 그러나, 이것과는 별도로, 소스/드레인 영역의 Si 기판 위에 Si나 SiGe를 에피택셜 성장시켜, 접합 깊이를 벼는 시도가 검토되고 있다. 이 경우에 대해서도, 게이트 전극 상과 마찬가지로 Ge 농도를 상술한 바와 같은 저농도로 함으로써, Ni 실리사이드의 응집, 및  $\text{NiSi}_2$ 에의 상전이 억제가 가능하다.

### 발명의 효과

상술한 바와 같이, 본 발명의 한 양상에 따르면, 컨택트 재료로서  $\text{NiSi}$ 를 이용하는 경우에, 고온의 후열공정에 의한 게이트 전극의 시트 저항의 상승이라고 하는 내열성의 문제를 회피하여 트랜지스터의 스위칭 속도를 고속화할 수 있는 반도체 장치가 얻어진다.

또한, 제조 수율과 신뢰성을 향상시킬 수 있는 반도체 장치의 제조 방법이 얻어진다.

당 분야의 업자라면 부가적인 장점 및 변경들이 용이하게 생성될 수 있다. 따라서, 광의의 관점에서의 본 발명은 본 명세서에 예시되고 기술된 상세한 설명 및 대표 실시예들에 한정되는 것은 아니다. 따라서, 첨부된 청구범위들 및 그 등가물들에 의해 정의된 바와 같은 일반적인 발명적 개념의 정신 또는 범위로부터 벗어나지 않고 다양한 변경들이 생성될 수 있다.

### (57) 청구의 범위

#### 청구항 1.

MOSFET를 구비하는 반도체 장치에 있어서,

상기 MOSFET은,

반도체 기판의 주표면 영역 내에 형성되는 소스/드레인 영역,

상기 소스/드레인 영역 사이의 채널 영역 상에 형성되는 게이트 절연막,

상기 게이트 절연막 상에 형성되고,  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비가  $x(0 < x < 0.2)$ 인  $\text{poly}-\text{Si}_{1-x}\text{Ge}_x$  층을 포함하는 게이트 전극,

상기 게이트 전극 상에 형성되고,  $\text{NiSi}_{1-y}\text{Ge}_y$ 로 이루어지는 제1 금속 실리사이드막,

상기 소스/드레인 영역 상에 각각 형성되고,  $\text{NiSi}$ 로 이루어지는 제2, 제3 금속 실리사이드막

을 포함하는 것을 특징으로 하는 반도체 장치.

#### 청구항 2.

제1항에 있어서,

상기  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비는, 보다 바람직하게는  $0.04 \leq x \leq 0.16$ 의 범위 내인 것을 특징으로 하는 반도체 장치.

#### 청구항 3.

제1항에 있어서,

상기 MOSFET 상에 형성되는 층간 절연막과,

상기 충간 절연막의 상기 게이트 전극 상에 형성된 제1 컨택트홀 내에 형성되는 제1 금속 플러그와,

상기 제1 금속 플러그와 상기 제1 금속 실리사이드막과의 사이에 개재되는 제1 배리어 메탈층과,

상기 충간 절연막의 상기 소스/드레인 영역 상에 각각 형성된 제2, 제3 컨택트홀 내에 형성되는 제2, 제3 금속 플러그와,

상기 제2, 제3 금속 플러그와 상기 제2 금속 실리사이드막과의 사이에 개재되는 제2, 제3 배리어 메탈층

을 더 구비하는 것을 특징으로 하는 반도체 장치.

#### 청구항 4.

제3항에 있어서,

상기 제1 내지 제3 금속 플러그는 텅스텐이고, 상기 제1 내지 제3 배리어 메탈층은 TiN을 포함하는 것을 특징으로 하는

반도체 장치.

#### 청구항 5.

제1항에 있어서,

상기 게이트 전극에 있어서의  $\text{poly-Si}_{1-x}\text{Ge}_x$  층의 막 두께는, 상기 제1 금속 실리사이드막의 막 두께의 적어도 2배인 것을

특징으로 하는 반도체 장치.

#### 청구항 6.

제1항에 있어서,

상기 반도체 기판 내에 형성되는 웰 영역을 더 구비하며, 상기 소스/드레인 영역은 상기 웰 영역 내에 형성되고, 또한 상기 소스/드레인 영역은, 소스/드레인 익스텐션을 갖는 구조이고, 고농도의 제1, 제2 불순물 확산 영역과, 상기 제1, 제2 불순물 확산 영역에서의 채널 영역의 근방에 형성되는 저농도의 제3, 제4 불순물 확산 영역을 갖는 것을 특징으로 하는 반도체 장치.

#### 청구항 7.

반도체 장치의 제조 방법에 있어서,

반도체 기판 상에 게이트 절연막을 형성하는 단계,

상기 게이트 절연막 상에  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비가  $x(0 < x < 0.2)$ 인  $\text{poly-Si}_{1-x}\text{Ge}_x$  층을 포함하는 게이트 전극을 형성하는 단계,

상기 반도체 기판의 주표면 영역 내에 불순물을 도입하여 소스/드레인 영역을 형성하는 단계,

상기 게이트 전극 상 및 상기 소스/드레인 영역 상에 Ni 막을 형성하는 단계,

열 처리를 행하여, 상기 게이트 전극 상의 Ni 막을  $\text{NiSi}_{1-y}\text{Ge}_y$  막으로 치환하고, 또한 상기 소스/드레인 영역 상의 Ni 막을 NiSi 막으로 치환하는 단계를 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 8.

제7항에 있어서,

상기  $\text{Ge}/(\text{Si} + \text{Ge})$  조성비는, 보다 바람직하게는  $0.04 \leq x \leq 0.16$ 의 범위 내인 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 9.

제7항에 있어서,

상기  $\text{NiSi}_{1-y}\text{Ge}_y$  막 상, 및 상기 NiSi 막 상에 충간 절연막을 형성하는 단계,

상기 충간 절연막에 있어서의 상기 게이트 전극 상 및 상기 소스/드레인 영역 상에 대응하는 위치에 각각 제1 내지 제3 컨택트홀을 형성하는 단계,

상기 제1 내지 제3 컨택트홀 내에 제1 내지 제3 배리어 메탈층을 형성하는 단계,

상기 제1 내지 제3 컨택트홀 내의 상기 제1 내지 제3 배리어 메탈층 상에 제1 내지 제3 금속 플러그를 매립 형성하는 단계

를 더 구비하는 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 10.

제7항에 있어서,

상기 게이트 절연막을 형성하는 단계의 전에,

상기 반도체 기판의 주표면에 소자 분리 구조를 형성하는 단계,

상기 소자 분리 구조로 구획된 능동 소자 영역에 웨л 영역을 형성하는 단계

를 더 구비하는 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 11.

제7항에 있어서,

상기 소스/드레인 영역을 형성하는 단계는,

상기 게이트 전극을 마스크로 하여 상기 반도체 기판의 주표면 영역 내에 불순물을 이온 주입하여 저농도의 제1, 제2 불순물 확산 영역을 형성하는 단계,

상기 게이트 전극의 측벽부에 측벽 절연막을 형성하는 단계,

상기 게이트 전극 및 상기 측벽 절연막을 마스크로 하여 상기 반도체 기판의 주표면 영역 내에 불순물을 이온 주입하여 고농도의 제3, 제4 불순물 확산 영역을 형성하는 단계

를 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 12.

제9항에 있어서,

상기 층간 절연막을 형성하는 단계는,

상기 반도체 기판의 주표면 상 및 상기 게이트 전극의 상면 및 측벽부에 실리콘 질화막을 퇴적 형성하는 단계,

상기 실리콘 질화막 상에 실리콘 산화막을 퇴적 형성하는 단계

를 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 13.

제9항에 있어서,

상기 제1 내지 제3 배리어 메탈층을 형성하는 단계는,

상기 층간 절연막 상 및 상기 제1 내지 제3 컨택트홀 내에 Ti 막을 형성하는 단계,

상기 Ti 막을 질화함으로써 적어도 일부를 TiN 막으로 하는 단계

를 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 14.

제9항에 있어서,

제1 내지 제3 금속 플러그를 매립 형성하는 단계는,

상기 층간 절연막 상 및 상기 제1 내지 제3 컨택트홀 내에, CVD법에 의해 텅스텐을 형성하는 단계,

CMP을 행하여 평탄화하고, 상기 텅스텐을 상기 제1 내지 제3 컨택트홀 내에 잔존시킴으로써, 제1 내지 제3 금속 플러그를 형성하는 단계

를 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

도면

## 도면1

## 도면2

### 도면3

## 도면4

도면5

도면6

도면7

도면8a

도면8b

도면9