(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-135318

(P2004-135318A)

(43) 公開日 平成16年4月30日(2004.4.30)

(51) Int.Cl.<sup>7</sup>

H04L 7/04

F 1

H04L 7/04

テーマコード(参考)

B

5K047

審査請求 未請求 請求項の数 10 O L (全 23 頁)

(21) 出願番号 特願2003-323294 (P2003-323294)

(22) 出願日 平成15年9月16日 (2003.9.16)

(31) 優先権主張番号 268196

(32) 優先日 平成14年10月9日 (2002.10.9)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアルト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100105913

弁理士 加藤 公久

(72) 発明者 リチャード・ケイ・カールクイスト

アメリカ合衆国カリフォルニア州クバチーノ アルカザル・アベニュー21861

F ターム(参考) 5K047 AA05 AA11 FF02 GG03 MM28

(54) 【発明の名称】改善されたタイミングマージンを有する位相検出器

## (57) 【要約】

【課題】タイミングマージンが大きなハーフレート連続位相検出器を提供する。

【解決手段】上記課題は、入力データ信号とクロック信号を表わす出力とを供給する回路であって、奇数番と偶数番の前記入力データ信号を個別リタイミング処理し、偶数番リタイミング処理データ信号と奇数番リタイミング処理データ信号を供給する手段と、前記データ信号と前記クロック信号と反転した前記クロック信号と、リタイミングした前記偶数番データ及び奇数番データ信号をそれぞれ論理合成して論理合成信号を出力する第1論理合成手段と、前記論理合成信号を合成して前記出力を供給する第2合成手段とを有することを特徴とする回路により解決される。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

入力データ信号とクロック信号を表わす出力とを供給する回路であって、奇数番と偶数番の前記入力データ信号を個別リタイミング処理し、偶数番リタイミング処理データ信号と奇数番リタイミング処理データ信号を供給する手段と、前記データ信号と前記クロック信号と反転した前記クロック信号と、リタイミングした前記偶数番データ及び奇数番データ信号をそれぞれ論理合成して論理合成信号を出力する第1論理合成手段と、前記論理合成信号を合成して前記出力を供給する第2合成手段と、を有することを特徴とする回路。

10

**【請求項 2】**

前記第2合成手段は線形合成器であることを特徴とする請求項1に記載の回路。

**【請求項 3】**

前記第1論理合成手段は少なくとも4個の3入力論理積ゲートを備え、第1ゲートの第1入力と第3ゲートの第1入力は反転した前記リタイミング処理していないデータ信号であり、

前記第1ゲートの第2入力は前記偶数番リタイミング処理データ信号であり、第2ゲートの第2入力は反転した前記偶数番リタイミング処理データ信号であり、前記第1ゲートの第3入力は前記クロック信号であり、前記第2ゲートの第1入力と第4ゲートの第1入力は前記リタイミング処理していないデータ信号であり、

前記第3ゲートの第2入力は前記奇数番リタイミング処理データ信号であり、前記第4ゲートの第2入力は反転した前記奇数番リタイミング処理データ信号であり、前記第3ゲートの第3入力と前記第4ゲートの第3入力は反転した前記クロック信号であることを特徴とする請求項1または請求項2に記載の回路。

20

**【請求項 4】**

前記第1論理合成手段は、少なくとも二つの2入力論理積ゲートと少なくとも二つの2入力排他的論理和ゲートを備え、

第1排他的論理和ゲートの第1入力は前記偶数番のリタイミング処理データ信号であり、第1排他的論理和ゲートの第2入力と第2論理和ゲートの第1入力は前記リタイミング処理していないデータ信号であり、

前記第2排他的論理和ゲートの第2入力は前記奇数番のリタイミング処理データ信号であり、

第1論理積ゲートへの第1入力は前記第1排他的論理和ゲートの出力であり、前記第1論理積ゲートへの第2入力は前記クロック信号であり、第2論理積ゲートへの第1入力は前記第2排他的論理和ゲートの出力であり、前記第2論理積ゲートへの第2入力は反転した前記クロック信号である、ことを特徴とする請求項1または請求項2に記載の回路。

30

**【請求項 5】**

前記データ信号を前記リタイミング処理回路を介する信号遅延を補償する量だけ遅延させ、前記クロック信号を前記リタイミング処理回路と前記排他的論理和ゲートを介する信号遅延を補償する量だけ遅延させることを特徴とする請求項4に記載の回路。

40

**【請求項 6】**

前記第1論理合成手段と前記第2合成手段の間に介挿した少なくとも一つの低域濾波フィルタをさらに含むことを特徴とする請求項1から請求項5に記載の回路。

**【請求項 7】**

データ信号を受信する入力端と、クロック信号を受信する入力端と、前記データ入力端で受信したデータをリタイミング処理するリタイミング処理回路と、

50

複数の多入力ゲートで、各ゲートの入力が、前記リタイミング処理回路によりリタイミング処理したデータ信号と、リタイミング処理していないデータ信号と、前記クロック入力端から受信したクロック信号と反転した前記クロック信号とが異なる組み合わせで構成してあり、前記ゲートの線形合成出力が前記出力端での信号であって、前記データ入力端で受信した前記データパルスと前記クロック入力端で受信したクロックパルスの間の位相差に比例するパルスを供給することを特徴とする位相検出器。

#### 【請求項 8】

前記リタイミング処理していないデータ信号が前記ゲート入力端に達する前に該リタイミング処理していないデータ信号を遅延させる遅延回路をさらに備えることを特徴とする請求項 7 に記載の位相検出器。

10

#### 【請求項 9】

データ信号とクロック信号の間の位相差を表す出力を供給する回路であって、

前記データ信号と前記リタイミング処理したデータ信号とクロック信号の組み合わせを合成し、前記位相差を示す一連のパルスを供給する複数の論理素子で、同一の論理素子により連続パルスから前記組み合わせが生成されないようにした前記論理素子と、

前記一連のパルスを複数のデータ信号パルスに亘って平均化する合成器を備える、ことを特徴とする回路。

#### 【請求項 10】

前記合成器は線形合成器であることを特徴とする請求項 9 に記載の回路。

20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、位相検出器に係り、より詳しくはノンリターン・ツー・ゼロ (NRZ) データからのクロック再生用システム及び方法に関し、さらにより具体的にはタイミングマージンを改善したハーフレート連続位相検出器用のシステム及び方法に関する。

#### 【背景技術】

#### 【0002】

NRZ 形式を用いるデータ転送システムでは、データ再生に用いることのできるデータと共に転送される明確なクロック信号が存在しない。このクロックは、先ずデータ転送時間に基づいてデータから再生しなければならない。これには、NRZ データと内部クロックの間の位相誤差を計測して誤差信号を生成する位相検出器が必要である。誤差信号は、誤差を修正する制御ループを駆動する。適切に作動するシステムにあっては、制御ループは位相誤差を無視可能な値に保持することが可能である。再生クロックは、そこでデータ再生に用いられる。上記の操作を実行する回路は、クロック / データ再生 (CDR) 回路と呼ばれる。ほとんど全ての最新のデータ転送システムは CDR 回路を用いており、位相検出器はこの種の CDR 回路の必須部分をなす。

30

#### 【0003】

一般に「離散的 (bang-bang)」と「連続的 (continuous)」と呼ばれる、二分類した位相検出器が広く用いられている。離散的回路は、非特許文献 1 に記載された Alexander 氏原作の設計に由来するものである。離散的回路は、クロックが「進相」か「遅相」かのみを示し、位相誤差を示さない 2 値量子化出力を有する。このような不連続な「離散的」モードによる動作は、制御ループにおいて、再生クロックにスプリアスジッタを加え、ジッタ計測システム内での離散的位相検出器が使用する問題点となる。また、通信システムではこのスプリアスジッタがシステムの性能を落とすことになる。

40

#### 【0004】

連続的位相検出器は、非特許文献 2 に記載の Hogghe 氏原作の検出器に倣ってパターン化するかエミュレートされる。これらの検出器は位相誤差に比例する電圧を生成するのに用いることのできる出力を有しており、制御ループに対し「比例」モードをもたらす。

50

オペレーショナルシステムにおいてより望ましいことであり、ジッタ計測システムには不可欠である。しかしながら、業界標準のクロックレートで動作する多くのシステムが依然として離散的位相検出器を使用しているのは、所定の論理ハードウェア技術にとって連続的位相検出器よりも相当に高速に動作させることができるからである。なぜなら、連続的位相検出器においては、より精密なタイミングが必要となるからである。

#### 【0005】

上記位相検出器は、クロック周波数がデータのボーレートに一致することを意味する「フルレート」でクロック動作するものである。例えば、データが毎秒10ギガビットのレート( $10^{10}$  ポー)である場合、クロックは10GHzであり、回路は「フルレート」でクロック動作すると説明される。この文脈では、「ハーフレート」クロック動作は、例えれば5GHzクロックを伴う毎秒10ギガビットのデータを指すことになる。10

#### 【0006】

よりレートを増すために、非特許文献3や非特許文献4に開示されているような「ハーフレート」クロック動作連続位相検出器が開発されている。このクロックは、双対フリップフロップを起動する180度離れた二つの位相を有する。二つの位相は、クロック波形の立ち上がりエッジと立ち下がりエッジに対応する。これにより、潜在的には少なくともフリップフロップを2倍の回数だけ切り替えることができ、最大クロックレートを2倍にすることができる。

#### 【0007】

【非特許文献1】アレキサンダー・ジェイ・ディー・エイチ(Alexander, J D H)著、「不規則2値信号からのクロック再生(Clock Recovery from Random Binary Signals)」、電子寄稿(Electronic Letters)、第11巻、第32号、1975年10月30日、p. 541-542

【非特許文献2】ホッジ・シー・ピー(Hogge, C P)著、「自己修正クロック再生回路(A Self Correcting Clock Recovery Circuit)」、光波技術ジャーナル(Journal of Lightwave Technology)、LT第3巻、第6号、1985年12月、p. 1312-1314

【非特許文献3】ライス・エー・ディー(Reis, A D)等著、「低速動作する高データレート同期器(High Data Rate Synchronizers Operating at Low Speed)」、KEGS2001年、第8回電子・回路・システムIEEE国際会議、2001年、p. 1127-1130, V3

【非特許文献4】サボジ・ジェイ(Savoj, J)とラザビ・ビー(Razavi, B)著、「光通信システム用ハーフレートクロック及びデータ再生回路の設計(Design of Half-Rate Clock and Data Recovery Circuits for Optical Communications System)」、ソリッドステート回路IEEEジャーナル、第36巻、第5号、2001年5月、p. 761-768

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0008】

しかしながら、これらのハーフレート位相検出器は依然としてそれらの最大クロックレートを制限する臨界タイミングマージンに関する制約を有する。連続的位相検出器のアナログ特性が原因で、最大レートに近づくにつれてそれらの精度とダイナミックレンジが次第に劣化する。それ故、たとえ最大レート未満であったとしても、設計上のマージンを大きくとることにより、性能を改善することができる。マージンを大きくとると、効果的に最大データレートを向上させる。従って、増大するレートと性能に合わせ改善したタイミングマージンを備えるハーフレート連続位相検出器が望まれていた。

#### 【課題を解決するための手段】

#### 【0009】

10

20

30

40

50

本発明は、複数の多入力ゲートから構成した位相検出器に係り、これがリタイミング処理していない入力データをリタイミング処理したデータとクロック信号に組み合わせ、リタイミング処理していないデータとクロックの間の位相差に比例する出力パルスを得る。

#### 【0010】

実施形態にあっては、位相検出器は、データ信号を受信する入力端とクロック信号を受信する入力端と位相制御信号を供給する出力端と前記データ入力端からリタイミング処理していないデータ信号を受け入れ、そこから偶数番と奇数番のリタイミング処理した信号を供給するデータリタイミング処理回路と、前記リタイミング処理していないデータ信号と前記リタイミング処理したデータ信号と前記クロック信号の異なる組み合わせに接続した入力端を有する複数の多入力ゲートで、UIを単一ビットに割り当てた時間長として規定したときに、二つの連続的なUIにおいてアクティブとなることが一切あり得ない前記ゲートと、少なくとも二つの前記ゲートの出力を混合する合成器を備える。

#### 【発明を実施するための最良の形態】

#### 【0011】

本発明をより完全に理解するため、添付図面と併せ以下の説明をここで参照する。詳細な説明を開始する前に、データを正確に再生するためのクロック位相について図9A～図20Dを参照下に説明を行う。

#### 【0012】

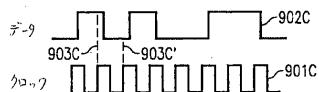

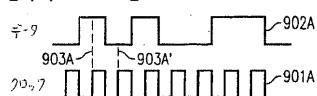

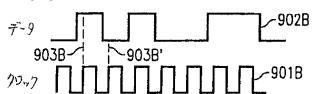

図9A、図9B、図9Cは、理想化した方形波形のクロック901A、901B、901Cと、各ビット境界において瞬間に状態を切り替えるよう理想化したデータ902A、902B、902Cを示すフルレート動作に関するタイミング線図である。単一ビットへの割り当て時間長を、単位期間(UI)と呼ぶ。データをサンプリングする最適なタイミングは、図9Aに903A、903A'で示すような各ビットのUIの中心である。この手法を用いることで、時間誤差に関する設計マージンは正の誤差も負の誤差と同じものとなる。図9Bは、進相サンプリング903B、903B'を示し、図9Cは遅相サンプリング903C、903C'を示す。

#### 【0013】

データは通常は、クロック(903A、903B、903C)の立ち上がりエッジにおいてデータをサンプリングするサンプラであるエッジトリガD型フリップフロップにより捕捉される。このため、クロックとデータの転送は、UI/2だけ離しておかねばならない。

#### 【0014】

実際のシステムでは、データが遷移しているときに幾らかの無駄時間が存在する。このためタイミングマージンはUI/2未満に減ることになるが、その原理に変わりはない。すなわち、データをサンプリングする最適タイミングはデータが有効な時間間隔の中心である。

#### 【0015】

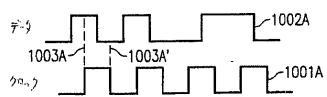

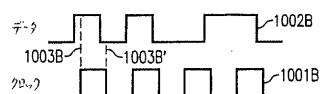

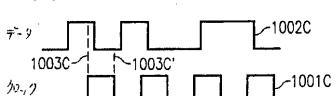

図10A、図10B、図10Cは、ハーフレートクロック動作を示す以外は、図9A、図9B、図9Cと同様である。この場合、データ1002A、1002B、1002Cは、正であろうが負であろうが各クロックの遷移1003A、1003A'、1003B、1003B'、1003C、1003C'でサンプリングされる。無論、クロック信号1001A、1001B、1001Cのクロック遷移は1UIだけ離れている。

#### 【0016】

ジッタとは、ビットからビットへクロック位相(データ信号に対するクロック信号の関係)のタイミングの変動をいう。クロック位相を統計学上の確率変数とみなした場合、そのときはジッタは変数の「不規則性」の測度(分散に類似)となる。クロック位相は平均的には正しいが、それは任意の特定のビットで変化することがある。ジッタを含むデータ信号を一様な間隔でもってサンプリングした場合、ビット中央部でサンプリングがなされず、時として進相したり時として遅相したりする。このタイミング誤差が、ノイズと他の欠陥に起因するビット誤差に対しシステムをより脆弱なものとする。

## 【0017】

ジッタを考える別 の方法は、信号に対するクロック位相を考へることである。このとき、ジッタは位相成分のノイズと考えることができる。ジッタは、正弦波のスプリアス位相変調の測度である「位相ノイズ」と密接に関連している。

## 【0018】

基本的には、二つのジッタ源が存在する。直接的なジッタのメカニズムは、クロック信号自体がその上にジッタを有し、データ生成デバイスがこのジッタを受け継ぐものである。このジッタメカニズムは、転送されるデータの特性とは無縁である。第2のジッタメカニズムは、「データパターンジッタ」と呼ばれる。これは、たとえ完全なクロックの存在下であっても発生するデバイス内群遅延欠陥が原因で、データのタイミングがデータ転送デバイス通過中に変わる。ジッタ特性が転送されるデータの特性に依存するということから、上述したような名前で呼ばれている。

## 【0019】

位相検出器は、ゲートや他の素子の無関係な収集体としてではなく、回路ブロックの階層的編成の組み合わせから構築されている。

## 【0020】

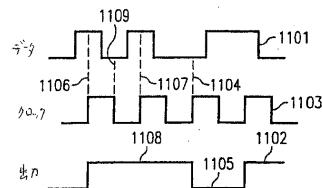

図11Aは、Dフリップフロップ1100（以下、単にフリップフロップと呼ぶ）を示し、図11Bはそのタイミング線図を示す。フリップフロップ1100の基本機能は、クロック1103の制御下で、D入力端でデータ1101を取り込み、Q出力端で出力をリード線1102へ返送することにある。クロックの立ち上がり1104（図11B）では、D入力がロウである場合、その出力はロウ1105となる（或いは既にロウである場合はロウのままとなる）。同様に、D入力がクロックの立ち上がり1106、1107においてハイである場合、その出力はハイ1108となる（或いは既にハイである場合は、ハイのままとなる）。クロックの立下り1109には、フリップフロップは何もしない。

## 【0021】

フリップフロップは、データのリタイミング処理器として考えることができる。フリップフロップへのD入力端におけるリタイミング処理されていないデータが、適当量のジッタをその上に有するものと仮定する。フリップフロップは、一般に非最適時刻にデータをサンプリングするが、各ビットごとに正確な値を維持する。このデータは出力端に出力されるが、そのタイミングは入力端への到着時刻ではなくクロックにより制御される。このように、正確なクロックを備えたフリップフロップがデータをリタイミング処理し、全てのジッタを取り除くことになる。

## 【0022】

クロックがジッタを有する場合、その出力はこのジッタを受け継ぐ。また、フリップフロップが周波数依存性振幅や群遅延を有する場合、その出力はパターンジッタを有する。それ故、実際には、フリップフロップはジッタを増加或いは減少させることになる。

## 【0023】

以後、フリップフロップへの入力データは「リタイミング処理していないデータ」と呼び、フリップフロップからの出力データは「リタイミング処理したデータ」と呼ぶことにする。

## 【0024】

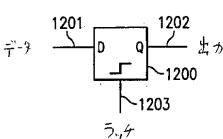

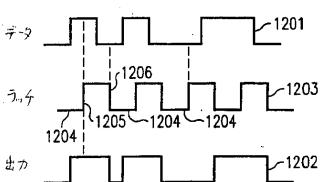

図12AはDラッチ1200（以下、単に「ラッチ」と呼ぶ）を示し、図12Bはそのタイミング線図を示す。ラッチは前述のSavoj等の論文において使用されており、フリップフロップの構成要素であるため重要である。フリップフロップと同じく、D入力からデータ1201を取り込み、このデータをQ出力端1202から出力する。しかしながら、ラッチはクロック入力の代わりにラッチ入力1203により制御され、その挙動はフリップフロップとは若干異なる。それは、ラッチ入力の状態に応じて二つのモードを有する。ラッチ入力がロウ1204であるときは、ラッチは追尾モードにある。追尾モードは直通転送モードであり、出力は入力に直に応答する。ラッチ入力がハイになると、ラッチはラッチモードとなる。ラッチモードでは、モード変更時の状態を維持する。ラッチ入力

10

20

30

40

50

はハイからロウへ遷移 1206 すると、ラッチは追尾モードへ変わる。遷移の瞬間に、(必要に応じて)出力状態は直ちに変化して電流入力状態と同じになり、その後に任意の入力変化に追随する。

#### 【0025】

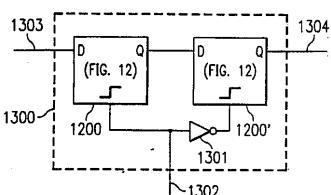

図13はフリップフロップ1300が二つのラッチ1200, 1200'を用いて如何に構成できるかを示すものである。このようなフリップフロップを、マスター・スレーブ型フリップフロップと呼ぶ。マスター・ラッチ1200はクロック入力1302により動作し、スレーブラッチ1200'は補完クロック入力(インバータ1301経由)で動作する。それ故、クロックがロウであるときは、マスター・ラッチが追尾しスレーブラッチがラッチする。クロックがハイであるときは、マスター・ラッチがラッチしスレーブラッチが追尾する。動作は、次の通りである。マスター・ラッチがリタイミング処理していないデータ1303をクロックの立ち上がりにラッチし、それをスレーブラッチへ出力する。スレーブラッチは追尾モードにあるため、データを出力端へ通過させる。クロックの立下りでは、スレーブラッチが出力端のデータをラッチしてそれを保持する。一方、マスター・ラッチはリタイミング処理していないデータの現在の状態の追尾を開始する。

#### 【0026】

各ビットがマスター・スレーブ型フリップフロップの二つの動作を必要とするため、各動作はクロック周期の1/2未満で実行しなければならない。フルレートクロックを用いる場合、クロック周期は1/2UIである。これにより、連続的なラッチがデータレートの2倍で動作できることが要求される。ハーフレートを用いた場合、クロック周期の1/2は1UIである。これにより、連続的なラッチがデータレートで動作できる。

#### 【0027】

1対2デマルチプレクサは、リタイミング処理していないデータ信号をリタイミング処理した出力データ信号に分割し、出力データレートは入力データレートの半分となる。その基本的な機能は、データのレートを低下させ、それがより低速のハードウェアによってより低速のレートで処理できるようにすることにある。

#### 【0028】

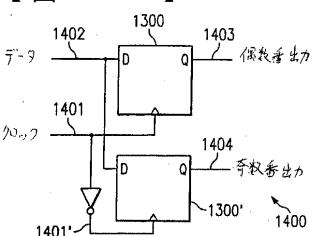

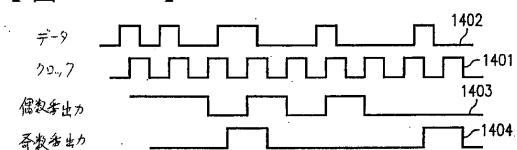

図14A, 14Bは、デマルチプレクサ1400(図14C)が二つのフリップフロップ1300, 1300'から構成できる仕方を示すものである。ハーフレートクロック1401は一方のフリップフロップ(「偶数番」と表記)用に用いられ、補完ハーフレートクロック1401'は他方のフリップフロップ(「奇数番」と表記)用に用いられる。フリップフロップ1300は、クロックの立ち上がりでリタイミング処理されていないデータ1402をサンプリングし、その一方でフリップフロップ1300'はクロックの立下りでリタイミング処理されていないデータをサンプリングする。サンプリングしたデータは、リタイミング処理していないデータの半分のレートである。リタイミング処理したデータは、「偶数番」出力端1403と、次に「奇数番」出力端1404へ交互に転送される。かくして、偶数番番号付きビットが偶数番出力端へ行き、奇数番番号付きビットが奇数番出力端へ行く。

#### 【0029】

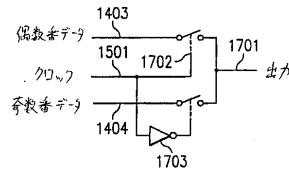

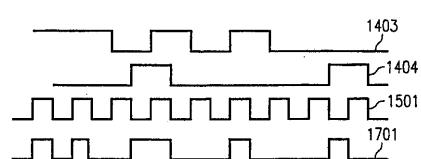

2対1マルチプレクサは、二つのハーフレートデータ入力を一つのフルレートデータ入力へ合成することで逆変換動作を行なう。図15A, 図15Bは、2対1マルチプレクサ1500(図15C)がハーフレートクロックにより駆動されるデータ選択スイッチであることを示すものである。ハーフレートクロック1501がハイであるときは、一方の入力1403は出力端1701へ切り替えられる。クロックがロウであるときは、他方の入力1404は出力端1701へ切り替えられる。相補的クロック信号が、インバータ1703により生成される。データスイッチは、組み合わせ論理回路を用いて簡単に構成される。これにより、マルチプレクサは、リタイミング処理したデータを生成する。

#### 【0030】

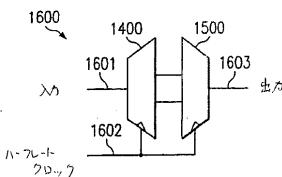

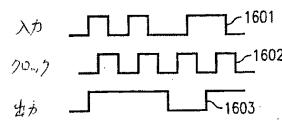

図16A, 図16Bは、1対2デマルチプレクサ1400を2対1マルチプレクサ1500と組み合わせ、図16Cに記号を示したハーフレートリタイミング処理器1600を

形成することができる事を示している。多重化機能は、多重解除機能を元に戻すものであり、リタイミング処理されたデータが出力されることになる。かくして、データ1601は、図16Bに示す如くデータ出力1603としてリタイミング処理される。フリップフロップがデータをリタイミング処理する点において、ほぼ同じ機能を実現する。主な差異は、それがハーフレートクロック1602で動作し、リタイミング処理器の内部動作がフリップフロップのレートの半分である点にある。このためより高速のデータレートに対応できる。ハーフレートリタイミング処理器は時として両エッジトリガ型フリップフロップと呼ばれるが、それはそれがクロックの立ち上がりと立下りの両方で動作するためである。

## 【0031】

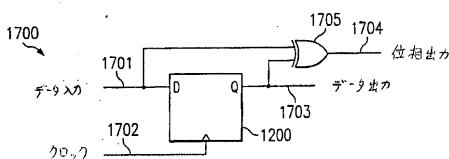

10

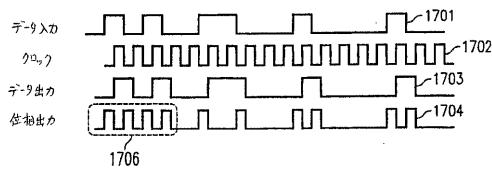

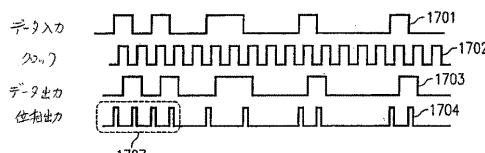

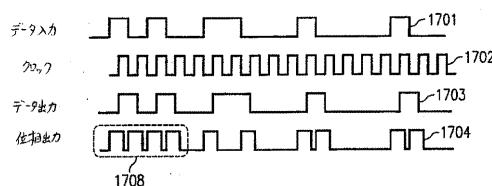

図17Aに示した回路1700は、リタイミング処理していないデータをクロック1702によりフルレートでクロック動作する従来のフリップフロップ1200(図12)を用いてリタイミング処理する回路である。排他的論理和ゲート1705は、リタイミング処理したデータ1703をリタイミング処理していないデータ1701と比較する。ゲートの出力1704は、クロック1702の位相に比例した持続期間を有するパルスから成る。位相情報を収集するデータ遷移が存在するときにのみ、パルスが生成される。通常状態でクロック位相は、図17Bの1706として指し示したパルスにより示す如く、パルスは1/2UIの長さにある。クロックが進相しているときは、図17Cに1707で指し示したパルスにより示した如くパルスは幅狭となる。クロックが遅相しているときは、図17Dに1708で指し示したパルスにより示した如く幅広となる。パルスは、低域濾波フィルタにより平滑化し、位相に比例する電圧を生成するようできる。

20

## 【0032】

30

回路1700は、少なくとも四つの重大な制約がある。(1)フリップフロップは、フルクロックレートで動作させねばならない。(2)位相出力の効果的なデータレートはリタイミング処理していないデータのデータレートの2倍である。このため、最大クロックレートはベースとなるハードウェアの最大切り替えレート能力の半分へ制限される。(3)位相が通常の変動域を越えて逸脱したときに、非常に幅狭のパルスを出力するときに位相出力性能が求められることになる。この制約のため、最大使用可能位相範囲を制限し或いは最大クロックレートを最大論理切り替えレートの半分未満に制限する必要がある。(4)この回路はリタイミング処理していないデータタイミングを直接クロックと比較はしない。リタイミング処理していないデータに代え、タイミングはフリップフロップの出力端においてリタイミング処理済みデータに対し比較される。リタイミング処理したデータは、クロックタイミングの代わりとなる。それ故、フリップフロップ内の固有のどんなジッタも伝搬遅延ドリフトも或いは他の不正確さも、出力精度を劣化させる。重要であるがしばしば看過される最大レート近傍で動作するフリップフロップ内の誤差源は、データ入力端でのセットアップ時間における伝搬遅延に依存する。

## 【0033】

40

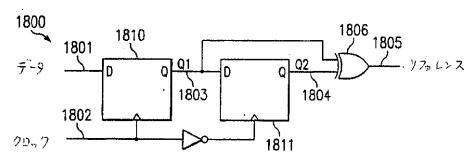

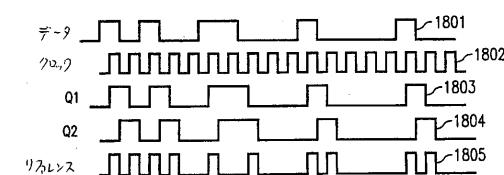

位相パルスがデータ遷移でのみ生成されるため、位相出力の平均値はデータ遷移の平均密度に依存する。かくして、零位相誤差を表わす基準電圧は、遷移密度に従ってシフトする。この問題に対抗するため、図18Aに示した回路1800には、データ遷移密度への同じ依存度を有するものの位相とは無関係の基準電圧のシフトを生成する追加のリファレンス出力1805が追加してある。リファレンス出力は、各データ遷移後に生成される1/2UIの固定持続時間をもつパルスからなる。基準出力は位相出力から減算され、位相誤差が零であるときは常に(標準的には)零である補正出力に帰結する。基準出力は、位相出力と同様、リタイミング処理していないデータのレートの2倍で動作しなければならないため、最大クロックレートが制限される。また、この二つのフリップフロップ1810, 1811はクロックの両相で動作するため、第1のフリップフロップ1810の伝搬遅延と第2のフリップフロップ1811のセットアップ時間とホールド時間は通常許容量の半分となる。図18Bは、1801内のデータと1802内のクロックとQ1(1803)とQ2(1804)とリファレンス出力1805に関する回路1800のタイミング

50

を示す。フリップフロップ 1810, 1811 からの出力が、排他的論理和 (XOR) ゲート 1806 へ供給される。

#### 【0034】

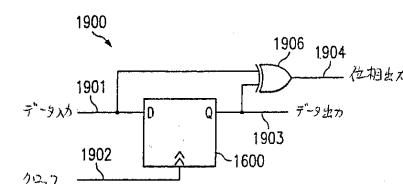

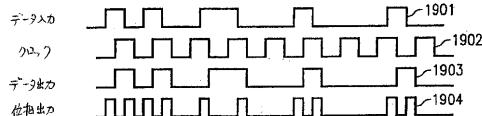

図 19A に示した位相検出器 1900 は、フルレートフリップフロップをハーフレートリタイミング処理器 1600 で置き換えたものである。位相に比例する持続期間を有するパルス 1903 を生成する排他的論理和ゲート 1906 の動作は、回路 1700 について説明したものと同じである。回路 1700 を上回る回路 1900 の主要利点は、リタイミング処理機能がハーフレートで実行され、そのことで前記制約 (1) に対処することにある。制約 (2) ~ (4) は残る。図 19B は、1901 内のデータとクロック 1902 とデータ出力 1903 と位相出力 1904 に関する回路 1900 のタイミングを示す。

10

#### 【0035】

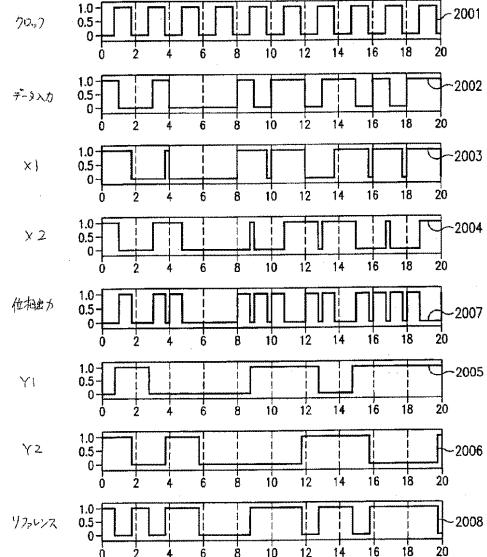

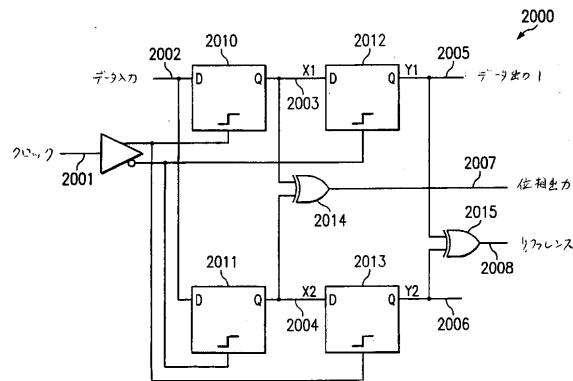

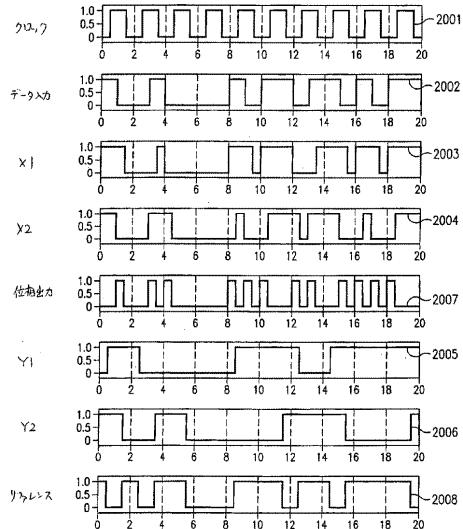

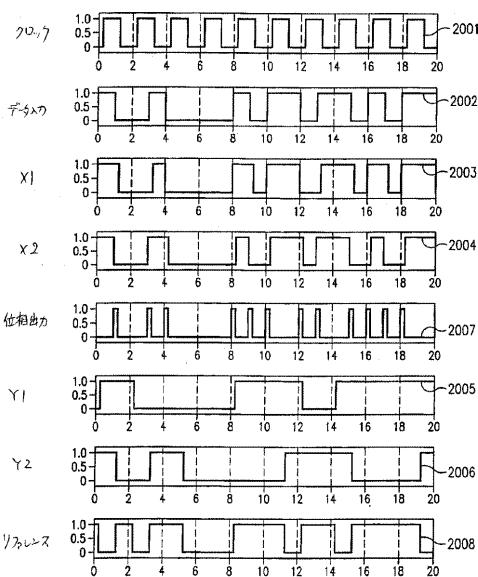

図 20A は、前記特定した Savoj 等の引用に記載された位相検出器を示し、図 20B はクロック 2001, 2002 内データと Y1(2003) と X2(2005) と位相出力 2007 と Y1(2004) と Y2(2006) とリファレンス出力 2008 についての最適クロック位相に関するタイミング線図を示す。この回路は、ハーフレートクロック 2001 で動作する。前述したアーキテクチャを用いて 1 対 2 デマルチプレクサへ編成した 4 個のラッチ 2010 ~ 2012 を用いる。マルチプレクサの出力端が再生データを供給し、これがまた排他的論理和ゲート 2015 を駆動してリファレンス出力パルス 2008 を生成する。これらのリファレンスパルスは、持続時間が 1/2UI である回路 1800 とは対照的に持続時間が 1UI であることには注意されたい。加えて、この二つの主ラッチ出力は位相出力パルス 2007 を生成する別の排他的論理和ゲート 2014 へ個別に出力される。

20

#### 【0036】

ラッチはハーフレートでもってクロック動作するが、図 20B はラッチ 2007 の出力が 1/2UI の持続期間のパルスを含むことを示している。同様にパルスは、排他的論理和ゲート 2015 にも供給される。クロック位相が進相しているときは、図 20C に示す如く、パルス持続期間は 1/2UI 未満に減少する。大きな負の位相誤差にとって、出力パルスの持続期間は図 20C のグラフ 2007 に示す如く実用に耐えないまでに小さくなり、出力パルスはもはや正確には生成されず、位相計測における誤差を招く。

30

#### 【0037】

クロック位相が遅相しているときは、図 20D に示す如く、パルスの持続期間は 1/2UI 以上に増加する。連続的な出力パルスが存在するときは、パルス間隔は図 20D のグラフ 2007 に示す如く 1/2UI 未満に減少する。このため、やはり幅狭のパルスを生ずることになり、やはり大きな位相誤差にとって、パルスの持続期間は実用に耐えないまでに小さくなり、出力パルスはもはや正確には生成されず、再び位相検出器の計測誤差を招く。加えて、タイミングが遅れる場合には、幅狭のパルスがノード X1, X2 に出現する（図 20D のグラフ 2003, 2004）。これらの幅狭のパルスは、排他的論理和ゲートを通じて伝搬しなければならない。極端に幅狭のパルスは、ゲートを伝搬した後でそれらの持続期間が変わる傾向がある。持続期間のこの変化は、別の不正確さの源泉となる。

40

#### 【0038】

リファレンス出力は、位相検出器とは幾分か異なる方法で機能する。偶数番の非多重化データは、第 2 の排他的論理和ゲートにより奇数番の非多重化データと比較される。このゲートは、各データ遷移後に 1UI パルスを生成する。これらのパルスを平均化したときに、それらは回路 1800 のリファレンスパルスの正確に 2 倍の電圧を生成する。かくして、実際にこの電圧は位相出力から減算する前に係数 2 で減衰させられる。倍加したパルス持続期間のお陰で、リファレンス出力はハーフレートクロック動作に利点を生かすことになる。

#### 【0039】

ここで二つの実施形態について本発明概念を説明する。すなわち、高性能の実施形態と

50

、性能の低い代替実施形態である。

#### 【0040】

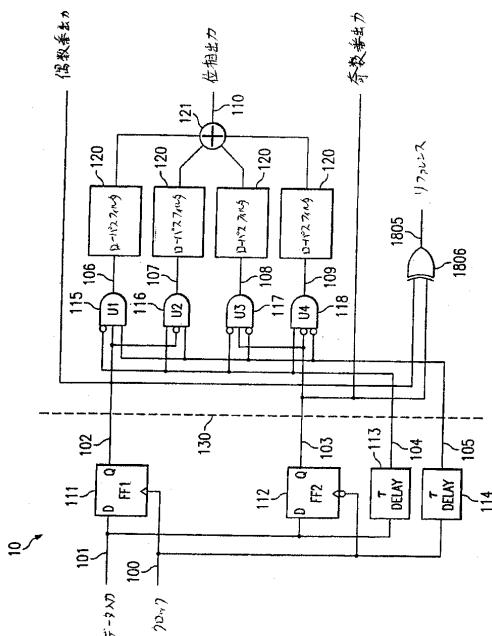

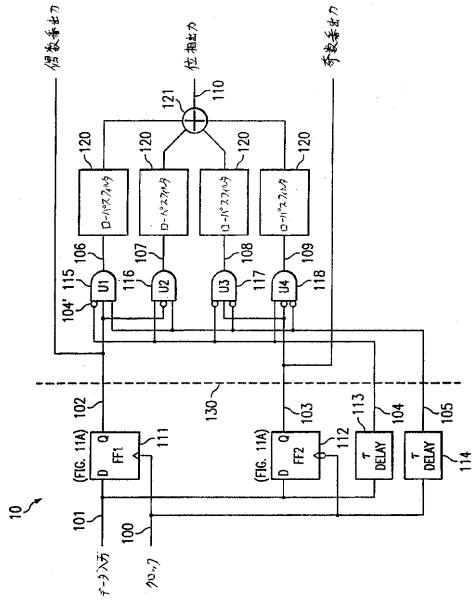

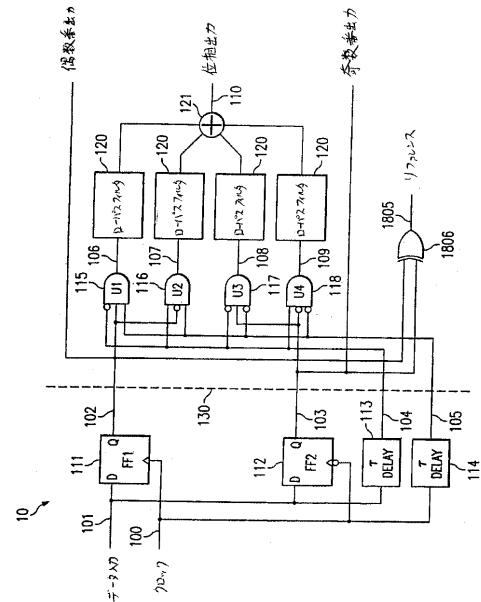

図1は、第1実施形態10の概略図を示す。位相検出器2000(図20A)と同様に、例えはクロック信号100の両クロックエッジにおいてクロック動作する二つのフリップフロップ111, 112(FF1, FF2)からなる従来のハーフレート1対2デマルチプレクサによりデータ再生が行なわれる。しかしながら、この場合、主ラッチ出力は個別に分解出力されない。その代わりに、リタイミング処理されたデータ102は、本実施形態の場合4つの3入力論理積ゲート115, 116, 117, 118(U1~U4)群により、リタイミング処理されていないデータの遅延信号104とクロック信号の遅延信号105と合成される。ゲート出力は、線形受動型合成器121により合成されて位相出力110を出力する。図面中の論理積ゲートの入力端における「丸印」は、反転入力を表わす。また、全てのゲートがハーフレート以下で動作することに注意されたい。10

#### 【0041】

図2は、図18Aに関して説明したリファレンス出力を生成する排他的論理和ゲート1806の追加を示す。このゲート(或いは他の回路網)は、図1の回路に追加されて完全な作動システムを作るが、それは両設計が1対2デマルチプレクサに基づくものであるからである。

#### 【0042】

回路10の動作を説明する前に、幾つかの定義が必要である。正クロックエッジ間で有効なデータビットを、「偶数番」ビットと定義する。負クロックエッジ間で有効であるデータビットを、「奇数番」ビットと定義する。偶数番ビットで始まり奇数番ビットで終わるデータ遷移は、「偶数番遷移」と定義する。奇数番ビットで始まり偶数番ビットで終わるデータ遷移は、「奇数番遷移」と定義する。ビット0で始まりビット1で終わるデータ遷移は、「正遷移」と定義する。ビット1で始まりビット0で終わるデータ遷移は、「負遷移」と定義する。20

#### 【0043】

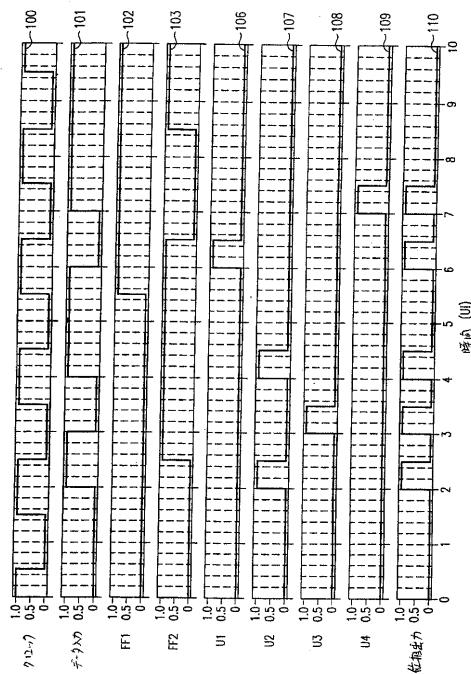

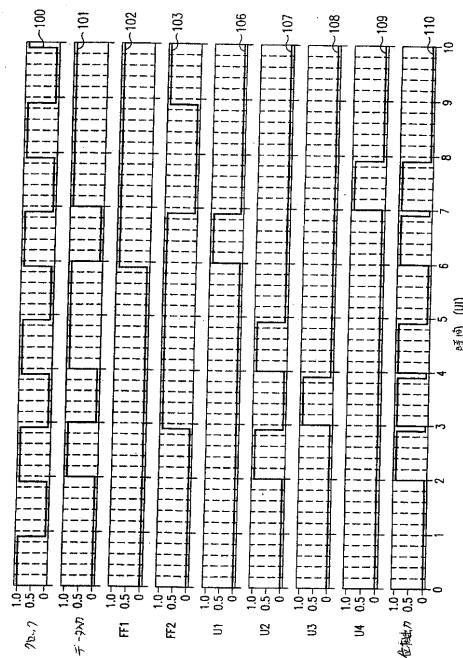

図3Aは、(オプションの低域濾波フィルタ120をもたない)回路10に関する(最適クロック位相)のタイミング線図を示す。同様に、図3B、図3Cはそれぞれ遅相と進相を示している。説明を簡単にするため、フリップフロップを介する遅延は零であると仮定する。非零遅延による影響は、後述するものとする。図1に示す如く、FF1(111)は偶数番データを処理し、FF2(112)は奇数番データを処理する。リタイミング処理したデータ(或いはその補完データ)は、論理積ゲート115~118(U1~U4)の様々な組み合せにおいて、リタイミング処理していないデータ(或いはその補完データ)とクロック(或いはその補完クロック)と合成される。30

#### 【0044】

図1の実施形態では、ゲートUは各偶数番負遷移においてパルスを生成する。ゲートU2は、各偶数番正遷移でパルスを生成する。ゲートU3は各奇数番負遷移でパルスを生成し、ゲートU4は各奇数番正遷移でパルスを生成する。ゲートU1~U4からのパルスの持続期間は、位相に比例する。このパルスは、随意選択的ではあるがフィルタ120により低域濾波され、続いて線形合成器121により合成され、各データ遷移における位相に比例するパルスからなる位相出力に帰結する。図3A、図3B、図3Cにおける位相信号110は、低域濾波フィルタ120をもたない場合のものである。低域濾波回路の効果は、この後に論ずるものとする。出力合成を、以下さらに詳細に説明する。この出力は、機能的には従来技術に関連して前記した出力と同一であり、かくして回路10はそのまま従来技術に置き換わるものとなる。40

#### 【0045】

動作理論は、0と1が交互する系列(すなわち、0101...)を用いて先ず動作を説明し、続いて他の系列で何が起こるかを説明する。0101...パターンについては、一方のフリップフロップ111或いは112が常に0をサンプリングし、他方のフリップフロップが1をサンプリングする。かくして、FF1が常に0であり、FF2が常に150

であるとタイミングを仮定しよう。この場合、ゲート U<sub>1</sub>, U<sub>4</sub> はディスエーブル状態とされ、ゲート U<sub>2</sub>, U<sub>3</sub> はクロック 100 (或いはその補完クロック) とリタイミング処理していないデータ 104 (或いはその補完データ) により駆動される 2 個の入力信号により出力状態が決まることになる。ゲート U<sub>2</sub> は、正データ遷移で始まって負クロック遷移で終わるパルスを出力する。同様に、ゲート U<sub>3</sub> は負データ遷移で始まって正クロック遷移で終わるパルスを出力する。U<sub>2</sub>, U<sub>3</sub> パルスは時間内で交互し、合成器 121 により合成される。パルスの持続期間は、データとクロックの間の時間間隔 (位相に比例する) に依存する。

#### 【0046】

他の系列としては、少なくとも 1 に先行する二つの 0 と、0 に先行する二つの 1 がある。2 以上の連続的な 0 が、位相検出器 10 により受信されたと仮定する。このとき、両方の FF1, FF2 はロウとなる。この場合、ゲート U<sub>1</sub>, U<sub>3</sub> はディスエーブル状態とされ、ゲート U<sub>2</sub>, U<sub>4</sub> は 2 個の入力信号で出力状態が決定することになる。これらのゲートはクロックと補完クロックにより交互に一つのゲートで一度にイネーブル状態とされ、そのことでゲート U<sub>2</sub>, U<sub>4</sub> をそれぞれ駆動する。クロックがロウであると仮定すると、これによりゲート U<sub>4</sub> がイネーブル状態とされる。0 から 1 へのデータ遷移が発生すると、ゲート U<sub>4</sub> はハイとなって出力パルスが開始する。クロックがハイとなると、ゲート U<sub>4</sub> はロウとなって出力パルスは終わる。FF1 はハイとなり、そのことでゲート U<sub>2</sub> はディスエーブル状態となり、追加の出力パルスが始まらないようとする。

10

#### 【0047】

実際に、パターンは 0101... 系列と他の系列が混ったものとなる。図 3A は、この回路がこれらの系列間で正確に遷移できることを示している。

20

#### 【0048】

どんなゲートも、以下の数学的属性が故に二つの連続する UI 間でアクティブになることは出来ない。(1) (中間に遷移を伴わない UI が存在することもあるが) 正と負の遷移は常に交互する。(2) 連続的な UI で発生する遷移は、共に偶数番とか共に奇数番とかにはなり得ない。それ故、どんな個別ゲートもハーフレート (或いはそれ未満) で動作し、常にパルス間に少なくとも 1 UI の時間余裕を有する。理想的には、ゲート U<sub>1</sub> ~ U<sub>4</sub> の出力は単純に (実際に使用する線形合成器に代わる) 4 入力論理和ゲートにより合成して図 3A ~ 3C の位相出力波形を生成できる筈であり、何故なら (理想的には) ゲートは一度にただ一つだけアクティブとされるからである。

30

#### 【0049】

位相が 1/2 UI の遅相に近付くと、ゲート U<sub>1</sub> ~ U<sub>4</sub> の出力端におけるパルスは持続時間が 1 UI に接近する。その場合、連続的なデータ遷移が存在すると、一つのパルスの終端と次の始端との間にごく僅かな時間しか存在しなくなる。図 3B に示した理想的なケースでは、出力パルス間の時間を表わす幅狭のパルスが位相出力に含まれる。実際には、論理ハードウェアの能力近傍で動作するシステムにとって、このような幅狭パルスは再生するに余りにも幅狭のため、いったんロウにならずにハイに止まる位相出力を招く。前記した如く、このことは従来技術の位相検出器にとって重大な問題である。しかしながら、本実施例では位相検出器の出力は利用前に多くのパルスに亘って平均化することで、この制約を克服するものである。この平均化の手段としては積分と考えられるが、精度に関して位相検出器に求められる唯一の要件は、パルスの面積が正確に位相を示すことである。この要件を満たせば、位相検出器はパルス波形を出力する必要はない。

40

#### 【0050】

より具体的には、位相出力電圧 110 (図 1) の曲線下側の面積は、個々のゲート出力 106, 107, 108, 109 の曲線下側の面積の合計に等しくなければならない。線形合成器 121 は、総和の積分が積分の総和に等しいという特性を有するため、要件に応えるものである。合成器 121 が受動的である場合、設計により線形となるようにする。適切に設計された能動的合成器もまた、線形になり得る。合成器の帯域幅はシステム用途に依存し、32 ビットの動作長 (run length) で毎秒 40 ギガビットの速度で

50

動作しているとき、通常は 0 ~ 640 MHz となる。

#### 【0051】

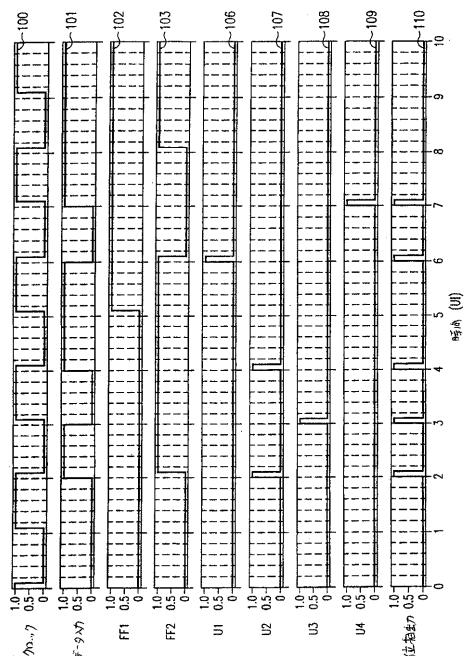

図4は、ゲート出力 106, 107, 108, 109が非零の立ち上がり時間と立ち下り時間有するときの生起内容を示すものである。これらのパルスは、位相出力端 110と一緒に通過する。しかしながら、この面積は前述した理由で正しいものとなる。このことは、線形合成器 121を4入力論理和ゲートで置換した場合には真実ではない、何故なら論理和ゲートは非線型デバイスであるからである。論理和ゲートの実装は、低減された位相範囲及び／又は低減された精度へ寄与する。

#### 【0052】

線形合成器 121の入力端間のアイソレーションが不十分であると、ゲート出力 106, 107, 108, 109間のクロストークの問題が生ずる。図1の任意の低域濾波フィルタ 120(図1)を用い、一つのゲートから出て来る高速過渡パルスが他のゲートの動作不良を起こさせないようにすることができる。これらのフィルタは、位相出力端の下流に用いる低域濾波フィルタの置換又は補充のいずれかができる。本実施例においてフィルタ周波数は、0 ~ 640 MHz である。

#### 【0053】

遅延器 113, 114は、二つの目的を有する。先ず、それをフリップフロップの伝搬遅延に等しくすることで、遅延を相殺する効果を有する。遅延検出器内の全てのデータ流が、図1に示す如く、帰還なしで基準線 130を横切って入力端から出力端へ向かうものであることに注意されたい。それ故、遅延器 114をクロックに挿入し、遅延器 113をリタイミング処理されていないデータ路に挿入した場合、この遅延はあたかも仮想上の負遅延がフリップフロップ出力で挿入されたのと同じ効果を有する。この負遅延は、効果的にフリップフロップの伝搬遅れ時間を相殺するのに用いることができる。第2に、フリップフロップ遅延を上回る 1 / 2 UI の付加遅延を加えることによって、タイミングマージンは増加する。

#### 【0054】

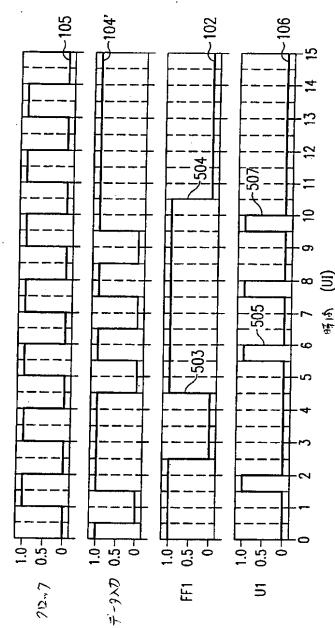

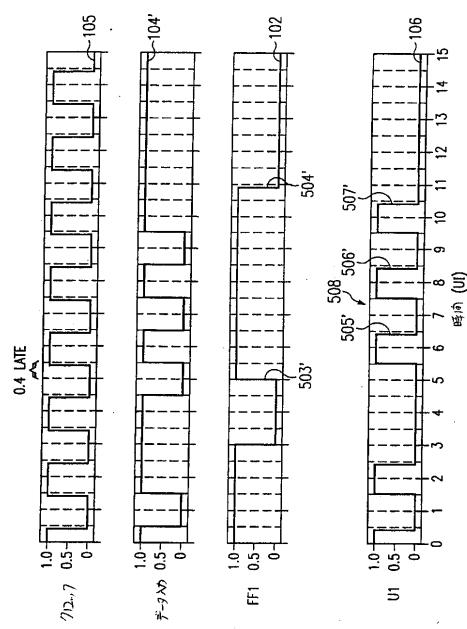

図5Aは、通常のクロック位相のときのゲート U1(115)の動作を示す。他の3つのゲート U2, U3, U4も同様な動作をする。このゲートの出力 106と3つの入力(102, 104, 105)が図示してある。U1(115)への入力は反転入力のため、遅延されたリタイミング処理していないデータ 104は、補完データ 104' (104と逆相のデータ)を図示した。遅延クロック 105もまた、図示してある。図5Aは、がフリップフロップ 101の伝搬遅延よりも正確に 1 / 2 UIだけ長いと仮定している。ANDゲートの出力 106(U1)は、3入力(102, 104', 105)が全てハイである場合、またその場合にのみハイとなる。

#### 【0055】

図5Aのような標準的な位相の場合には、出力パルス立ち上がりに対する最小のフリップフロップタイミングマージンは 1 UI である。例えば、パルス 505 は  $t = 5.5$  で始まって  $t = 6.0$  で終わる。FF1(102)の出力は、パルス 505 の期間中はハイである必要がある。FF1(102)は、1 UIだけ進相した  $t = 4.5$  (503) でハイとなっている。FF1(102)はそこでは、 $t = 5.5$  でのパルス終端の後、多数の UI に亘ってハイに止まる。同様に、出力パルスの立下り区間にに対する最小のフリップフロップタイミングマージンは、1 / 2 UI である。例えば、パルス 507 は  $t = 9.5$  で始まり、 $t = 10$  で終わる。FF1(102)の出力は、パルス 507 の期間中ハイである必要がある。FF1(102)が、1 / 2 UIだけ遅相した  $t = 10.5$  (504) までハイに止まっている。FF1(102)はまた、 $t = 9.5$  におけるパルス立ち上がり前は多数の UI に亘ってハイであった。

#### 【0056】

図5Bは、クロック位相が 0.4 UI 遅相であるときの波形の変化の様子を示す。出力パルス(505', 506', 507')は、ここでは 0.9 UI の長さである。出力パルス立ち上がりに対する最小のフリップフロップタイミングマージンは、0.6 UI に縮

減されてしまっている。例えば、パルス 5 0 5' は  $t = 5.5$  で始まり、 $t = 6.4$  で終わる。FF1(111)の出力 102 は、0.6 UI 進相した  $t = 4.9$  (503') でハイとなる。FF1(111)の出力 102 はそこで、 $t = 6.4$  でのパルス立下りに多数の UI に亘ってハイに止まる。同様に、出力パルスの後端に対する最小のフリップフロップタイミングマージンは 1 / 2 UI である。例えば、パルス 5 0 7' は  $t = 9$  で始まり、 $t = 10.4$  で終わる。FF1(111)の出力 102 は、パルス 5 0 7' の期間中ハイである必要がある。FF1(111)の出力 102 が、1 / 2 UI だけ遅相した  $t = 10.9$  (504') までハイに止まるっている。FF1(111)の出力 102 はまた、 $t = 9.5$  におけるパルス立ち上がり前に多数の UI に亘りハイであった。

## 【0057】

10

位相検出器の精度はフリップフロップ伝搬遅延時間とは無関係であるため、それはフリップフロップにより引き起こされるパターンジッタとも無関係である。ジッタ計測に応用するときは、このことは重要な考え方である。

## 【0058】

位相検出器を多クロックレートで使用しなければならないときは、UI から絶対秒への変換は使用する最大データレートに基づいてなされる。最大レート未満で を増大させる必要はない。この回路は、 値を最大レートに基づいて選択した場合に、少なくとも最大にて行なうのと同じく良好により低いレートで動作する。

## 【0059】

20

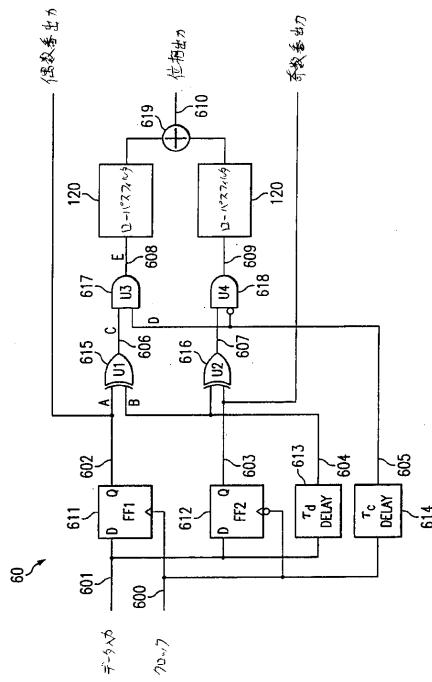

図 6 は代替実施形態 60 を示しており、差動電流モード論理回路 (CML) などの一部の汎用高速論理技術が 3 入力ゲートに影響を受けにくいという事実による。この技術では、3 入力機能は二つの 2 入力機能の縦列接続として実装する必要がある。直接的な実装が、各 3 入力ゲートを二つの 2 入力ゲートの縦列接続に変え、元々の 4 個の 3 入力ゲートに代わる全部で 8 個の 2 入力ゲートに帰結する。しかしながら、図 6 はたった 2 個の 2 入力論理積ゲート 617, 618 (U3, U4) と二つの排他的論理和ゲート 615, 616 (U1, U2) を用いるより効率化している。回路 60 は、論理的には回路 10 (図 1) と等価である。この場合、位相出力用にゲートが二つだけ存在する。回路 10 と同様、回路 60 の全ての論理はハーフレート以下で動作する。

## 【0060】

30

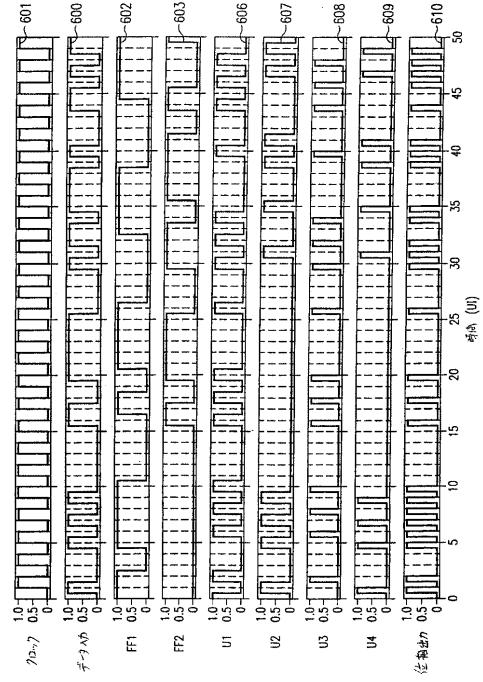

図 7 は、回路 60 についてのタイミング線図を示す。回路 10 と同様に、動作理論原理は先ず 0 と 1 が交互するパターン (すなわち 0101...) を説明し、続いて他のパターンで何が生ずるかを説明する。0101... パターンでは、一方のフリップフロップ 611 又は 612 は常に 0 をサンプリングし、他方のフリップフロップは常に 1 をサンプリングする。0101... パターンを、FF1(611) の出力 602 が常に 0 で、FF2(612) の出力 603 が常に 1 であるようなタイミングで位相検出器が受信したと仮定する。この場合、ゲート U1(615) は、実質的に非反転バッファとなり、ゲート U2(616) はインバータとなる。(614 により遅延される) 遅延クロック 605 とその補完、リタイミング処理していないデータ 606 と、その補完データ 607 により駆動されるゲート U3(617) 及び U4(618) の動作は、このときは回路 10 と同じである。ゲート U3(617) の出力 608 には、正データ遷移で始まって負クロック遷移で終わるパルスが含まれる。同様に、ゲート U4(618) の出力 609 には負データ遷移で始まり正クロック遷移で終わるパルスが含まれる。ゲート U3(617) と U4(618) は時間内で交互に動作し、合成器 619 により合成されて位相出力 610 を生ずる。このパルスの持続期間は、回路 10 の場合にそうであったように、データとクロックの間の時間期間に依存する。

40

## 【0061】

50

他のパターンとして、1 に先行する少なくとも二つの 0 と、0 に先行する少なくとも二つの 1 が存在する。2 以上の連続的な 0 が位相検出器 60 により受信されたと仮定する。そのときは、FF1(611) の出力 602 と FF2 の出力 603 はロウとなる。この場合、ゲート U1(615) と U2(616) は実質的には、非反転バッファ

となる。ゲート U3 (617) と U4 (618) は、クロック信号と補完クロックにより一つの UI ごとに交互にイネーブル状態とされよう。遅延クロック 605 がロウであって、これによりゲート U4 (618) がイネーブル状態にあると仮定する。遅延されたリタイミング処理していないデータ 604 内で 0 から 1 への遷移が発生するとき、ゲート U4 の出力 609 はハイとなり、出力パルスが始まる。遅延クロック 605 がハイになると、ゲート U4 の出力 609 はロウとなり、出力パルスは終わる。その上、FF1 (611) の出力 602 がハイとなり、そのことがゲート U1 (615) を介してゲート U3 (617) をディスエーブル状態とし、そのことが余分な出力パルスが始まらないようにする。

#### 【0062】

10

回路 10 に関するタイミングマージンの考察は、基本的には時間遅延を除き、回路 60 の図 7 に関するタイミングマージンにもまた当てはまる。同じ遅延  $d$  に代え、リタイミング処理していないデータ 600 とクロック 601 の双方にとって、ここで回路 613, 614 に関してそれぞれ個別選択された遅延  $d_d$ ,  $d_c$  が存在する。 $d_d$  は、回路 10 のと同じものである。しかしながら、 $d_c$  は に排他的論理和ゲートの伝搬遅延を加えたものに等しく、ゲート U1 (615), U2 (616) を介する遅延を埋め合わせる。

#### 【0063】

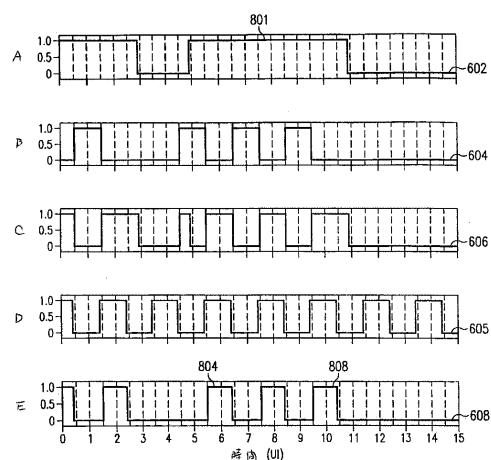

図 8 は、0.4 UI のクロック遅相の最悪の場合について、クロック  $d_d$  と  $d_c$  の正確な値を用いたぎりぎりのタイミング関係を示す。出力パルス幅は、依然としてフリップフロップ伝搬遅延内小変動 (UI/2まで) とは無縁であり、フリップフロップのジッタを免れている。

#### 【0064】

図 8 では、基準点 A, B, C, D 及び E は図 6 に示すものであり、 $d_c$  は 0.5 UI にフリップフロップの遅延を加算したものであり、 $d_d$  は 0.5 UI にフリップフロップの遅延と排他的論理和の遅延を加算したものである。回路 10 の線路沿いに迎れば、出力パルスの始端に対する最小のフリップフロップのタイミングマージンは 0.6 UI である。例えば、時点 E (608) における出力パルス 804 は、 $t = 5.5$  に始まって  $t = 6.4$  で終わる。時点 A における FF1 (611) の出力 602 は、標準値よりも 0.6 UI だけ進相した  $t = 4.9$  においてハイのパルス 801 を生成する。パルス 801 はそこで、 $t = 6.4$  におけるパルスの終端後、多数の UI に亘ってハイに留まる。同様に、出力パルスの後端に対する最小のフリップフロップタイミングマージンは 1/2 UI である。例えば、パルス 802 は  $t = 9.5$  で始まって  $t = 10.4$  で終わる。パルス 801 は、パルス 802 の期間中ハイであることが必要である。FF1 (611) の出力 (パルス 801) が、標準値よりも 1/2 UI 進相した  $t = 10.9$  までハイに留まる。パルス 801 はまた、 $t = 9.5$  でのパルス 802 の開始前は多数の UI に亘ってハイである。

30

#### 【0065】

回路 10 に関して説明した基準出力 1805 が、前記の如く回路 60 に簡単に追加できることには注意されたい。

#### 【0066】

40

出力ゲートの働きの分割が原因で、それらの全出力を一緒に寄せ集めるのではなく、それらを個別に利用するか或いは様々な対で利用することが可能である。例えば、正遷移の位相誤差を負遷移から分離することを利用可能とすることもある。一例を挙げれば、他方以上に一方の極性に影響を及ぼす非対称的な欠陥が存在する場合、このことは重要となる。同様に、偶数番遷移の位相誤差の奇数番遷移からの分離を利用可能とすることもある。データを多重化により生成した場合、偶数番データと奇数番データの間には系統的な位相差が存在することがある。

#### 【0067】

回路網の部分集合だけを構築し、遷移の部分集合からクロックを再生することで回路を単純化することもまた可能である。この場合、正の遷移だけ或いは偶数番遷移だけ等が全ての遷移を十分に代表するというのがその前提となる。

50

## 【0068】

本発明とその長所を詳細に説明してきたが、特許請求の範囲の趣旨ならびに範囲から逸脱することなく、様々な変形と置換と変更がここで可能である。さらに、本出願範囲は明細書に記載したプロセス、機械、製品、合成物、手段、方法、ステップの特定の実施形態に限定することは意図していないものである。例えば、データ入力とリタイミング処理したデータ信号とクロック信号の論理合成を見込んだ二つの実施形態(図1,図6)を図示してきたが、任意の数の論理積ゲートや論理和ゲートや排他的論理和ゲートといった論理素子やフリップフロップやリタイミング処理器やラッチといった他の素子ならびにそれらの組み合わせを用い、ハードウェアによらず幾つかの信号パルスに亘って平均化することができる連続パルスを生成することができる。この種の代替回路構成は、所望のパルス出力特性から始め、素子の適当な機能の組み合わせを達成するよう、回路設計者に実際の回路を特定の設計規範或いは全体的な回路制約に適合させる自由を可能にしよう。このことは、信号タイミング因子或いは信号伝搬遅延がぎりぎりとなつた場合に重要となることがある。

10

## 【0069】

最後に、本発明の代表的な実施態様を示す。

## (実施態様1)

入力データ信号とクロック信号を表わす出力とを供給する回路であつて、

奇数番と偶数番の前記入力データ信号を個別リタイミング処理し、偶数番リタイミング処理データ信号と奇数番リタイミング処理データ信号を供給する手段と、

20

前記データ信号と前記クロック信号と反転した前記クロック信号と、リタイミングした前記偶数番データ及び奇数番データ信号をそれぞれ論理合成して論理合成信号を出力する第1論理合成手段と、

前記論理合成信号を合成して前記出力を供給する第2合成手段と、

を有することを特徴とする回路。

## 【0070】

## (実施態様2)

前記第2合成手段は線形合成器であることを特徴とする実施態様1に記載の回路。

## 【0071】

## (実施態様3)

30

前記第1論理合成手段は少なくとも4個の3入力論理積ゲートを備え、

第1ゲートの第1入力と第3ゲートの第1入力は反転した前記リタイミング処理していないデータ信号であり、

前記第1ゲートの第2入力は前記偶数番リタイミング処理データ信号であり、

第2ゲートの第2入力は反転した前記偶数番リタイミング処理データ信号であり、

前記第1ゲートの第3入力は前記クロック信号であり、

前記第2ゲートの第1入力と第4ゲートの第1入力は前記リタイミング処理していないデータ信号であり、

前記第3ゲートの第2入力は前記奇数番リタイミング処理データ信号であり、

前記第4ゲートの第2入力は反転した前記奇数番リタイミング処理データ信号であり、

40

前記第3ゲートの第3入力と前記第4ゲートの第3入力は反転した前記クロック信号であることを特徴とする実施態様1または実施態様2に記載の回路。

## 【0072】

## (実施態様4)

前記第1論理合成手段は、少なくとも二つの2入力論理積ゲートと少なくとも二つの2入力排他的論理和ゲートを備え、

第1排他的論理和ゲートの第1入力は前記偶数番のリタイミング処理データ信号であり、

、

第1排他的論理和ゲートの第2入力と第2論理和ゲートの第1入力は前記リタイミング処理していないデータ信号であり、

50

前記第2排他的論理和ゲートの第2入力は前記奇数番のリタイミング処理データ信号であり、

第1論理積ゲートへの第1入力は前記第1排他的論理和ゲートの出力であり、

前記第1論理積ゲートへの第2入力は前記クロック信号であり、

第2論理積ゲートへの第1入力は前記第2排他的論理和ゲートの出力であり、

前記第2論理積ゲートへの第2入力は反転した前記クロック信号である、

ことを特徴とする実施態様1または実施態様2に記載の回路。

#### 【0073】

(実施態様5)

前記データ信号を前記リタイミング処理回路を介する信号遅延を補償する量だけ遅延させ、前記クロック信号を前記リタイミング処理回路と前記排他的論理和ゲートを介する信号遅延を補償する量だけ遅延させることを特徴とする実施態様4に記載の回路。 10

#### 【0074】

(実施態様6)

前記第1論理合成手段と前記第2合成手段の間に介挿した少なくとも一つの低域濾波フィルタをさらに含むことを特徴とする実施態様1から実施態様5に記載の回路。

#### 【0075】

(実施態様7)

データ信号を受信する入力端と、

クロック信号を受信する入力端と、

前記データ入力端で受信したデータをリタイミング処理するリタイミング処理回路と、複数の多入力ゲートで、各ゲートの入力が、前記リタイミング処理回路によりリタイミング処理したデータ信号と、リタイミング処理していないデータ信号と、前記クロック入力端から受信したクロック信号と反転した前記クロック信号とが異なる組み合わせで構成してあり、前記ゲートの線形合成出力が前記出力端での信号であって、前記データ入力端で受信した前記データパルスと前記クロック入力端で受信したクロックパルスの間の位相差に比例するパルスを供給することを特徴とする位相検出器。 20

#### 【0076】

(実施態様8)

前記リタイミング処理していないデータ信号が前記ゲート入力端に達する前に該リタイミング処理していないデータ信号を遅延させる遅延回路をさらに備えることを特徴とする実施態様7に記載の位相検出器。 30

#### 【0077】

(実施態様9)

データ信号とクロック信号の間の位相差を表す出力を供給する回路であって、

前記データ信号と前記リタイミング処理したデータ信号とクロック信号の組み合わせを合成し、前記位相差を示す一連のパルスを供給する複数の論理素子で、同一の論理素子により連続パルスから前記組み合わせが生成されないようにした前記論理素子と、

前記一連のパルスを複数のデータ信号パルスに亘って平均化する合成器を備える、ことを特徴とする回路。 40

#### 【0078】

(実施態様10)

前記合成器は線形合成器であることを特徴とする実施態様9に記載の回路。

#### 【図面の簡単な説明】

#### 【0079】

【図1】本発明例示例の一実施形態を示す図である。

【図2】追加のリファレンス出力端を備える図1の実施形態を示す図である。

【図3A】図1の回路に関するタイミング線図である。

【図3B】図1の回路に関するタイミング線図である。

【図3C】図1の回路に関するタイミング線図である。 50

【図4】図1の回路のタイミング線図である。

【図5A】 $= 0.5 UI + \text{フリップフロップ遅延}$ を有する図1の回路のタイミング線図である。

【図5B】 $0.4 UI$ 遅相クロックで  $= 0.5 UI + \text{フリップフロップ遅延}$ を有する図1の回路のタイミング線図である。

【図6】本発明の別の実施形態を示す図である。

【図7】図6の回路のタイミング線図である。

【図8】図6の回路のタイミング線図である。

【図9A】フルレートクロックに関する従来技術のタイミング線図である。

10

【図9B】フルレートクロックに関する従来技術のタイミング線図である。

【図9C】フルレートクロックに関する従来技術のタイミング線図である。

【図10A】ハーフレートクロックに関する従来技術のタイミング線図である。

【図10B】ハーフレートクロックに関する従来技術のタイミング線図である。

【図10C】ハーフレートクロックに関する従来技術のタイミング線図である。

【図11A】フリップフロップの説明図である。

【図11B】フリップフロップのタイミングを示す図である。

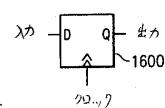

【図12A】ラッチの説明図である。

【図12B】ラッチのタイミングを示す図である。

【図13】マスター・スレーブ型フリップフロップを示す図である。

20

【図14A】マルチプレクサの回路図である。

【図14B】マルチプレクサのタイミングを示す図である。

【図14C】マルチプレクサの説明図である。

【図15A】デマルチプレクサの回路図である。

【図15B】デマルチプレクサのタイミングを示す図である。

【図15C】デマルチプレクサの説明図である。

【図16A】ハーフレートリタイミング処理器の回路図である。

30

【図16B】ハーフレートリタイミング処理器のタイミングを示す図である。

【図16C】ハーフレートリタイミング処理器の説明図である。

【図17A】位相検出器の構成図である。

【図17B】位相検出器のタイミングを示す図である。

【図17C】位相検出器のタイミングを示す図である。

【図17D】位相検出器のタイミングを示す図である。

【図18A】リファレンス出力の回路図である。

【図18B】リファレンス出力のタイミングを示す図である。

【図19A】ハーフレート位相検出器の回路図である。

【図19B】ハーフレート位相検出器のタイミングを示す図である。

【図20A】ハーフレート位相検出器の回路図である。

【図20B】ハーフレート位相検出器のタイミングを示す図である。

【図20C】ハーフレート位相検出器のタイミングを示す図である。

【図20D】ハーフレート位相検出器のタイミングを示す図である。

40

#### 【符号の説明】

##### 【0080】

10, 60 位相検出器(回路網)

100 クロック信号

101 データ信号

102 入力(偶数番リタイミング処理データ信号)

103 入力(奇数番リタイミング処理データ信号)

104 入力(リタイミング処理していないデータ信号)

105 入力(クロック信号)

106, 107, 108, 109 ゲート出力

50

1 1 0 位相出力(出力)

1 1 1 フリップフロップ(F F 1)

1 1 2 フリップフロップ(F F 2)

1 1 3 , 1 1 4 遅延器(遅延回路網)

1 1 5 論理積ゲート(第1ゲートU 1)

1 1 6 論理積ゲート(第2ゲートU 2)

1 1 7 論理積ゲート(第3ゲートU 3)

1 1 8 論理積ゲート(第4ゲートU 4)

1 2 0 低域濾波フィルタ

1 2 1 線形合成器

1 3 0 基準線

6 0 0 クロック信号

6 0 1 データ信号

6 0 2 , 6 0 3 , 6 0 4 , 6 0 5 , 6 0 6 , 6 0 7 , 6 0 8 , 6 0 9 出力

6 1 0 位相出力

6 1 1 フリップフロップ(F F 1)

6 1 2 フリップフロップ(F F 2)

6 1 3 , 6 1 4 回路(遅延回路網)

6 1 5 排他的論理和ゲート(第1排他的論理和ゲートU 1)

6 1 6 排他的論理和ゲート(第2排他的論理和ゲートU 2)

6 1 7 論理積ゲート(第1論理積ゲートU 3)

6 1 8 論理積ゲート(第2論理積ゲートU 4)

6 1 9 線形合成器

10

20

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図4】

【図 5 A】

【図 5 B】

【図 6】

【図 7】

【図8】

【図9C】

【図10A】

【図10B】

【図10C】

【図9A】

【図9B】

【図11B】

【図12A】

【図12B】

【図11A】

【図13】

【図14A】

【図14B】

【図 1 4 C】

【図 1 5 A】

【図 1 5 B】

【図 1 5 C】

【図 1 7 B】

【図 1 7 C】

【図 1 7 D】

【図 1 8 A】

【図 1 6 A】

【図 1 6 B】

【図 1 6 C】

これは両エッジトリガ型 クロック

でスルヒーリングです。

【図 1 7 A】

【図 1 8 B】

【図 1 9 A】

【図 1 9 B】

【図20A】

【図20B】

【図20C】

【図20D】