(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7692828号

(P7692828)

(45)発行日 令和7年6月16日(2025.6.16)

(24)登録日 令和7年6月6日(2025.6.6)

(51)国際特許分類

|         |                 |         |       |         |

|---------|-----------------|---------|-------|---------|

| H 1 0 B | 12/00 (2023.01) | H 1 0 B | 12/00 | 8 0 1   |

| H 1 0 B | 41/70 (2023.01) | H 1 0 B | 12/00 | 6 2 1   |

| H 1 0 D | 86/40 (2025.01) | H 1 0 B | 12/00 | 6 7 1 C |

| H 1 0 D | 86/60 (2025.01) | H 1 0 B | 12/00 | 6 7 1 Z |

|         |                 | H 1 0 B | 41/70 |         |

F I

請求項の数 5 (全67頁) 最終頁に続く

(21)出願番号 特願2021-532540(P2021-532540)

(86)(22)出願日 令和2年6月29日(2020.6.29)

(86)国際出願番号 PCT/IB2020/056106

(87)国際公開番号 WO2021/009586

(87)国際公開日 令和3年1月21日(2021.1.21)

審査請求日 令和5年6月8日(2023.6.8)

(31)優先権主張番号 特願2019-129927(P2019-129927)

(32)優先日 令和1年7月12日(2019.7.12)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 青木 健

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

黒川 義元

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

上妻 宗広

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

金村 卓郎

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

最終頁に続く

(54)【発明の名称】 半導体装置、電子部品、及び電子機器

## (57)【特許請求の範囲】

## 【請求項1】

複数の積和演算ユニットを有し、

前記複数の積和演算ユニットのそれぞれは、第1回路と、前記第1回路上に積層された第2回路と、を有し、

前記第2回路は、マトリクス状に配置された複数のメモリセルを有し、

前記第1回路は、前記複数のメモリセルの各列に対応する複数の回路と、積和演算を行う機能とを有し、

前記複数の回路のそれぞれは、対応する列の前記メモリセルに記憶されたデータを読み出す機能を有し、

前記データを読み出す複数の回路のそれぞれは、半導体基板にチャネル形成領域を有するpチャネル型の第1トランジスタ、pチャネル型の第2トランジスタ、nチャネル型の第3トランジスタ及びnチャネル型の第4トランジスタと、第1インバータ乃至第3インバータと、を有し、

前記複数のメモリセルのそれぞれは、チャネル形成領域に金属酸化物を含む第5トランジスタを有し、

前記第1トランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1トランジスタのソース又はドレインの他方は、前記第2トランジスタのソース又はドレインの一方と電気的に接続され、

前記第2トランジスタのソース又はドレインの他方は、前記第1インバータの出力端子

及び前記第2インバータの入力端子と電気的に接続され、

前記第3トランジスタのソース又はドレインの一方は、前記第1インバータの出力端子及び前記第2インバータの入力端子と電気的に接続され、

前記第3トランジスタのソース又はドレインの他方は、前記第4トランジスタのソース又はドレインの一方と電気的に接続され、

前記第4トランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、

前記第1インバータの入力端子は、第3の配線と電気的に接続され、

前記第2インバータの出力端子は、前記第3の配線と電気的に接続され、

前記第3インバータの入力端子は、第4の配線と電気的に接続され、

前記第3インバータの出力端子は、前記第1トランジスタのゲートと電気的に接続され、

前記第2トランジスタのゲート及び前記第3トランジスタのゲートは、第5の配線を介して前記複数のメモリセルの一と電気的に接続され、

前記第4トランジスタのゲートは、前記第4の配線と電気的に接続され、

前記複数の前記積和演算ユニットは、マトリクス状に配置されている、半導体装置。

【請求項2】

ワード線ドライバ回路と、

ピット線ドライバ回路と、

積和演算ブロックと、を有し、

前記積和演算ブロックは、複数の積和演算ユニットを有し、

前記複数の積和演算ユニットのそれぞれは、第1回路と、前記第1回路上に積層された第2回路と、を有し、

前記第2回路は、マトリクス状に配置された複数のメモリセルを有し、

前記第1回路は、前記複数のメモリセルの各列に対応する複数の回路と、積和演算を行う機能とを有し、

前記ワード線ドライバ回路と、前記ピット線ドライバ回路とは、前記複数のメモリセルにデータを書き込む機能を有し、

前記複数の回路のそれぞれは、対応する列の前記メモリセルに記憶された前記データを読み出す機能を有し、

前記データを読み出す複数の回路のそれぞれは、半導体基板にチャネル形成領域を有するpチャネル型の第1トランジスタ、pチャネル型の第2トランジスタ、nチャネル型の第3トランジスタ及びnチャネル型の第4トランジスタと、第1インバータ乃至第3インバータと、を有し、

前記複数のメモリセルのそれぞれは、チャネル形成領域に金属酸化物を含む第5トランジスタを有し、

前記第1トランジスタのソース又はドレインの一方は、第1の配線と電気的に接続され、

前記第1トランジスタのソース又はドレインの他方は、前記第2トランジスタのソース又はドレインの一方と電気的に接続され、

前記第2トランジスタのソース又はドレインの他方は、前記第1インバータの出力端子及び前記第2インバータの入力端子と電気的に接続され、

前記第3トランジスタのソース又はドレインの一方は、前記第1インバータの出力端子及び前記第2インバータの入力端子と電気的に接続され、

前記第3トランジスタのソース又はドレインの他方は、前記第4トランジスタのソース又はドレインの一方と電気的に接続され、

前記第4トランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、

前記第1インバータの入力端子は、第3の配線と電気的に接続され、

前記第2インバータの出力端子は、前記第3の配線と電気的に接続され、

前記第3インバータの入力端子は、第4の配線と電気的に接続され、

前記第3インバータの出力端子は、前記第1トランジスタのゲートと電気的に接続され、

前記第2トランジスタのゲート及び前記第3トランジスタのゲートは、第5の配線を介して前記複数のメモリセルの一と電気的に接続され、

10

20

30

40

50

前記第4トランジスタのゲートは、前記第4の配線と電気的に接続され、前記複数の前記積和演算ユニットは、マトリクス状に配置されている、半導体装置。

【請求項3】

請求項1又は請求項2において、

前記金属酸化物は、InまたはZnの少なくとも一方を含む、半導体装置。

【請求項4】

請求項1乃至請求項3のいずれか一項に記載の半導体装置を有する、電子部品。

【請求項5】

請求項1乃至請求項3のいずれか一項に記載の半導体装置を有する、電子機器。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明の一形態は、積和演算回路と記憶装置を有する半導体装置に関する。

【0002】

本明細書等において、半導体装置とは、半導体特性を利用した装置のことであり、例えば、半導体素子（トランジスタ、ダイオード、フォトダイオード等）を含む回路、同回路を有する装置等を指す。また、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般のことであり、例えば、集積回路、集積回路を備えたチップや、パッケージにチップを収納した電子部品、集積回路を備えた電子機器は、半導体装置の一例である。

20

【0003】

なお、本発明の一形態は、上記の技術分野に限定されない。本明細書等で開示する発明の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一形態は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

【背景技術】

【0004】

積和演算は、例えば、ニューラルネットワークを利用した計算において多く用いられる。ニューラルネットワークは、ニューロンとシナプスで構成される神経回路網を模した回路構成を有している。それぞれのニューロンには複数のデータが入力され、それぞれのデータは結合の強度を表す「重み係数」と掛け合わされ、その結果が足しあわされる。このようにして得られた積和演算の結果が閾値を超えたとき、ニューロンはハイレベルの信号を出力し、この現象は「発火」と呼ばれている。

30

【0005】

神経回路網をモデルにした情報処理システムであるニューラルネットワークを利用することで、従来のノイマン型コンピュータを利用した情報処理よりも高性能なコンピュータが実現できると期待されており、近年、ニューラルネットワークを構築する種々の研究が進められている。

【0006】

ニューラルネットワークは、例えば、画像認識に利用される。画像認識では、画像データにフィルタのパラメータを掛けて足し合わせ、またスライドさせて同じ動作を繰り返すことで画像データの特徴を検出する畳み込み演算が行われている。畳み込み演算は複数回行われ、最初の方の畳み込み演算では画像のエッジなどを検出し、後の方の畳み込み演算では画像の形やパターンなど複雑な特徴を検出する。

40

【0007】

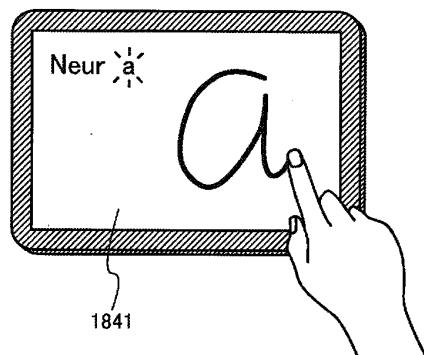

特許文献1には、CPU(Central Processing Unit)やGPU(Graphics Processing Unit)などのプロセッサを用いて、ニューラルネットワークによる機械学習を行い、手書き文字の認識を行う例が開示されている。

【0008】

また、近年、トランジスタのチャネル形成領域に、酸化物半導体または金属酸化物を有す

50

るトランジスタ（酸化物半導体トランジスタ、OS（O x i d e S e m i c o n d u c t o r）トランジスタ、ともいう）が注目されている。OSトランジスタは、トランジスタがオフ状態にあるときのドレイン電流（オフ電流、ともいう）が非常に小さい（例えば、非特許文献1、2、参照）ため、OSトランジスタをDRAMのメモリセルに用いることで、容量素子に蓄積した電荷を長時間保持することができる。

#### 【0009】

特許文献2には、駆動回路や制御回路などの周辺回路を形成した半導体基板上に、OSトランジスタを用いた複数のメモリセルを有する半導体装置、および、DRAM（D y n a m i c R a n d o m A c c e s s M e m o r y）のメモリセルにOSトランジスタを適用した例が、開示されている。例えば、単結晶シリコン基板に形成されたSiトランジスタを用いて周辺回路を構成し、その上方にOSトランジスタを用いたメモリセルを積層して設けることで、チップ面積を削減することができる。

10

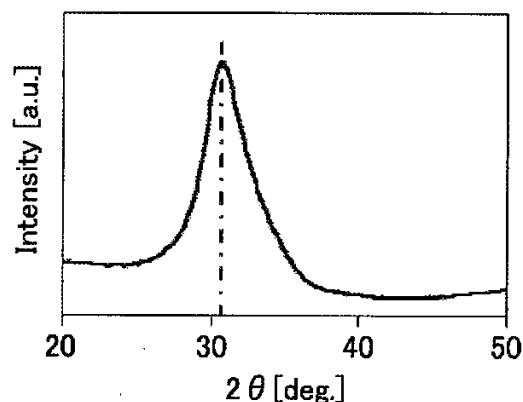

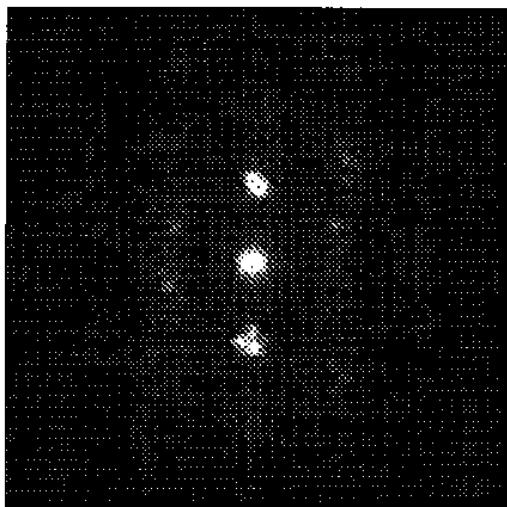

#### 【0010】

酸化物半導体では、単結晶でも非晶質でもない、CAAC（c-axis aligned crystalline）構造およびnc（nanocrystalline）構造が見出されている（非特許文献1および非特許文献3参照）。非特許文献1および非特許文献3では、CAAC構造を有する酸化物半導体を用いてトランジスタを作製する技術が開示されている。

#### 【先行技術文献】

##### 【特許文献】

20

##### 【0011】

【文献】特開2005-182785号公報

【文献】特開2012-256820号公報

##### 【非特許文献】

##### 【0012】

【文献】S. Yamazaki et al., "Properties of crystalline In-Ga-Zn-oxide semiconductor and its transistor characteristics," Jpn. J. Appl. Phys., vol. 53, 04ED18 (2014).

【文献】K. Kato et al., "Evaluation of Off-State Current Characteristics of Transistor Using Oxide Semiconductor Material, Indium-Gallium-Zinc Oxide," Jpn. J. Appl. Phys., vol. 51, 021201 (2012).

30

【文献】S. Yamazaki et al., "SID Symposium Digest of Technical Papers," 2012, volume 43, issue 1, p. 183-186

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0013】

40

画像認識における画像データとフィルタのパラメータは、それぞれ、ニューラルネットワークにおける、ニューロンに入力される複数のデータと重み係数に相当する。また、画像認識における畳み込み演算では、積和演算が行われている。

##### 【0014】

重み係数は、例えば、学習によって生成される。学習が終わった重み係数は、ニューロンに入力される複数のデータに対して、繰り返し用いられる。そのため、重み係数は、記憶装置への書き込みよりも、積和演算回路への読み出しにおいて、スピードおよび効率的な処理が求められている。

##### 【0015】

本発明の一形態は、積和演算回路と記憶装置を有する半導体装置であって、重み係数の読

50

み出しと積和演算とを、効率よく行うことができる半導体装置を提供することを課題の一つとする。または、本発明の一形態は、積和演算回路と記憶装置を有する半導体装置であって、チップ面積を削減した半導体装置を提供することを課題の一つとする。

【0016】

なお、本発明の一形態は、必ずしも上記の課題の全てを解決する必要はなく、少なくとも一つの課題を解決できるものであればよい。また、上記の課題の記載は、他の課題の存在を妨げるものではない。これら以外の課題は、明細書、特許請求の範囲、図面などの記載から自ずと明らかになるものであり、明細書、特許請求の範囲、図面などの記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0017】

本発明の一形態は、複数の積和演算ユニットを有する半導体装置である。積和演算ユニットは、第一回路とメモリセルとを有する。第一回路は、半導体基板に形成された第一トランジスタを有し、メモリセルは、チャネル形成領域に金属酸化物を含む第二トランジスタを有する。第二トランジスタは、第一トランジスタの上方に積層して形成され、第一回路は、メモリセルに記憶されたデータを読み出す機能と、積和演算を行う機能とを有する。

【0018】

また、本発明の一形態は、ワード線ドライバ回路と、ビット線ドライバ回路と、積和演算ブロックとを有する半導体装置である。積和演算ブロックは、複数の積和演算ユニットを有し、積和演算ユニットは、第一回路とメモリセルとを有する。第一回路は、半導体基板に形成された第一トランジスタを有し、メモリセルは、チャネル形成領域に金属酸化物を含む第二トランジスタを有する。第二トランジスタは、第一トランジスタの上方に積層して形成され、ワード線ドライバ回路とビット線ドライバ回路は、メモリセルにデータを書き込む機能を有し、第一回路は、メモリセルに記憶されたデータを読み出す機能と、積和演算を行う機能とを有する。

【0019】

また、本発明の一形態は、ワード線ドライバ回路と、ビット線ドライバ回路と、積和演算ブロックとを有する半導体装置である。積和演算ブロックは、複数の積和演算ユニットを有し、積和演算ユニットは、第一回路とメモリセルとを有する。ワード線ドライバ回路と、ビット線ドライバ回路と、第一回路は、それぞれ半導体基板に形成された第一トランジスタを有し、メモリセルは、チャネル形成領域に金属酸化物を含む第二トランジスタを有する。第二トランジスタは、第一トランジスタの上方に積層して形成され、ワード線ドライバ回路とビット線ドライバ回路は、メモリセルにデータを書き込む機能を有し、第一回路は、メモリセルに記憶されたデータを読み出す機能と、積和演算を行う機能とを有する。

【0020】

また、上記形態において、金属酸化物は  $\text{In}$  または  $\text{Zn}$  の少なくとも一方を含む。

【発明の効果】

【0021】

本発明の一形態により、積和演算回路と記憶装置を有する半導体装置であって、重み係数の読み出しと積和演算とを、効率よく行うことができる半導体装置を提供することができる。または、本発明の一形態により、積和演算回路と記憶装置を有する半導体装置であって、チップ面積を削減した半導体装置を提供することができる。

【0022】

なお、本発明の一形態は、必ずしも上記の課題の全てを解決する必要はなく、少なくとも一つの課題を解決できるものであればよい。また、上記の課題の記載は、他の課題の存在を妨げるものではない。これら以外の課題は、明細書、特許請求の範囲、図面などの記載から自ずと明らかになるものであり、明細書、特許請求の範囲、図面などの記載から、これら以外の課題を抽出することが可能である。

【図面の簡単な説明】

【0023】

10

20

30

40

50

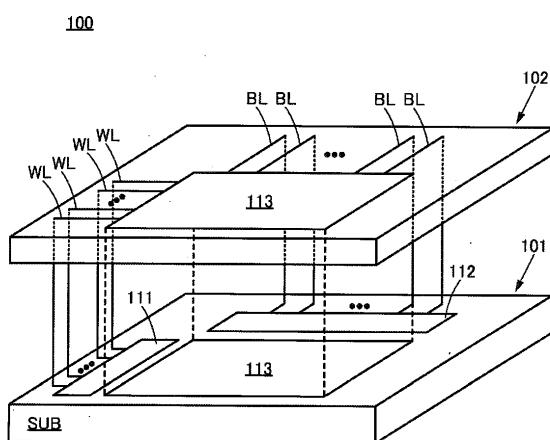

図1は、半導体装置の構成例を示す斜視概略図である。

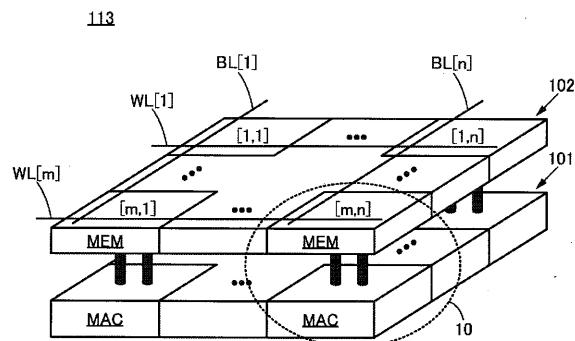

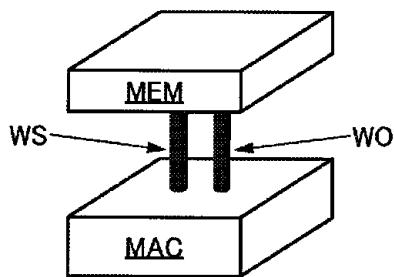

図2Aは、積和演算ブロックの構成例を示す斜視概略図である。図2Bは、積和演算ユニットの構成例を示す斜視概略図である。

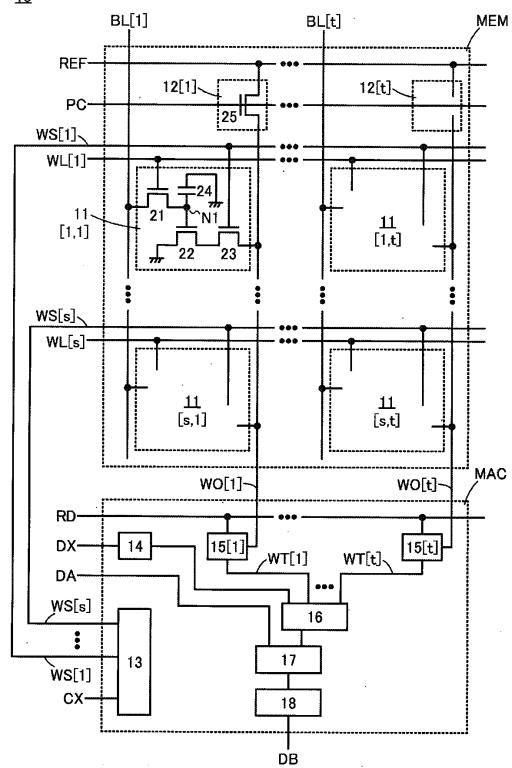

図3は、積和演算ユニットの構成例を示す回路図である。

図4Aは、回路15の構成例を示す回路図である。図4Bは、タイミングチャートである。

図5Aは、データ信号Xとデータ信号Wのイメージを示す図である。図5Bは、画像データPのイメージを示す図である。図5Cは、フィルタFのイメージを示す図である。

図6は、記憶装置の構成例を示す断面図である。

図7A乃至図7Cは、トランジスタの構造例を示す断面図である。

図8Aは、トランジスタの構造例を示す上面図である。図8B、図8Cは、トランジスタの構造例を示す断面図である。

10

図9Aは、トランジスタの構造例を示す上面図である。図9B、図9Cは、トランジスタの構造例を示す断面図である。

図10Aは、トランジスタの構造例を示す上面図である。図10B、図10Cは、トランジスタの構造例を示す断面図である。

図11Aは、トランジスタの構造例を示す上面図である。図11B、図11Cは、トランジスタの構造例を示す断面図である。

図12Aは、トランジスタの構造例を示す上面図である。図12B、図12Cは、トランジスタの構造例を示す断面図である。

図13Aは、トランジスタの構造例を示す上面図である。図13B、図13Cは、トランジスタの構造例を示す断面図である。

20

図14A、図14Bは、トランジスタの構造例を示す断面図である。

図15は、記憶装置の構成例を示す断面図である。

図16A、図16Bは、トランジスタの構造例を示す断面図である。

図17Aは、IGZOの結晶構造の分類を説明する図である。図17Bは、CAAC-IGZO膜のXRDSペクトルを説明する図である。図17Cは、CAAC-IGZO膜の極微電子線回折パターンを説明する図である。

図18Aは、半導体ウエハの上面図である。図18Bは、チップの上面図である。

図19Aは、電子部品の作製工程例を説明するフローチャートである。図19Bは、電子部品の斜視模式図である。

30

図20A、図20Bは、電子機器の構成を説明する図である。

図21A、図21Bは、電子機器の構成を説明する図である。

#### 【発明を実施するための形態】

##### 【0024】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる形態で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

##### 【0025】

また、以下に示される複数の実施の形態は、適宜組み合わせることが可能である。また、1つの実施の形態の中に複数の構成例が示される場合は、互いに構成例を適宜組み合わせることが可能である。

40

##### 【0026】

なお、本明細書に添付した図面では、構成要素を機能ごとに分類し、互いに独立したブロックとしてブロック図を示しているが、実際の構成要素は機能ごとに完全に切り分けることが難しく、一つの構成要素が複数の機能に係わることもあり得る。

##### 【0027】

また、図面等において、大きさ、層の厚さ、領域等は、明瞭化のため誇張されている場合がある。よって、必ずしもそのスケールに限定されない。図面は、理想的な例を模式的に示したものであり、図面に示す形状または値などに限定されない。

50

## 【0028】

また、図面等において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。

## 【0029】

また、本明細書等において、「膜」という用語と、「層」という用語とは、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

## 【0030】

また、本明細書等において、「上」や「下」などの配置を示す用語は、構成要素の位置関係が、「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

10

## 【0031】

また、本明細書等において、「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。

## 【0032】

また、本明細書等において、複数の要素に同じ符号を用いる場合、特にそれらを区別する必要があるときは、符号に、「\_1」、「\_2」、「[n]」、「[m, n]」等、識別用の符号を付して記載する場合がある。例えば、2番目の配線GLを、配線GL[2]と記載する。

20

## 【0033】

また、本明細書等において、「電気的に接続」とは、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、容量素子、その他の各種機能を有する素子などが含まれる。また、「電気的に接続」と表現される場合であっても、実際の回路において、物理的な接続部分がなく、配線が延在しているだけの場合もある。

30

## 【0034】

また、本明細書等において、「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆も同様である。

## 【0035】

また、本明細書等において、電気回路における「端子」とは、電流または電位の入力（または、出力）や、信号の受信（または、送信）が行なわれる部位を言う。よって、配線または電極の一部が端子として機能する場合がある。

## 【0036】

一般に、「容量素子」は、2つの電極が絶縁体（誘電体）を介して向かい合う構成を有する。また、本明細書等において、「容量素子」は、2つの電極が絶縁体を介して向かい合う構成を有したもの以外に、2本の配線が絶縁体を介して向かい合う構成を有したもの、または、2本の配線が絶縁体を介して配置されたもの、である場合が含まれる。また、本明細書等において、「容量素子」を、「コンデンサ」、「キャパシタ」、または、「容量」、と呼ぶ場合がある。

40

## 【0037】

また、本明細書等において、「電圧」とは、ある電位と基準の電位（例えば、グラウンド電位）との電位差のことを示す場合が多い。よって、電圧と電位差とは言い換えることができる。

## 【0038】

50

また、本明細書等において、トランジスタとは、ソースと、ドレインと、ゲートとを含む、少なくとも三つの端子を有する素子である。そして、ソース（ソース端子、ソース領域、または、ソース電極）とドレイン（ドレイン端子、ドレイン領域、または、ドレイン電極）の間にチャネル形成領域を有しており、チャネル形成領域を介して、ソースとドレインとの間に電流を流すことができるものである。なお、本明細書等において、チャネル形成領域とは、電流が主として流れる領域をいう。

#### 【 0 0 3 9 】

また、ソースやドレインの機能は、異なる極性のトランジスタを用いる場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等において、ソースやドレインの用語は、入れ替えて用いることができるものとする。

10

#### 【 0 0 4 0 】

また、本明細書等において、特に断りがない場合、オフ電流とは、トランジスタがオフ状態（非導通状態、遮断状態、ともいう）にあるときのドレイン電流をいう。オフ状態とは、特に断りがない場合、nチャネル型のトランジスタでは、ソースに対するゲートの電圧  $V_{g s}$  がしきい値電圧  $V_{t h}$  よりも低い状態、pチャネル型のトランジスタでは、ソースに対するゲートの電圧  $V_{g s}$  がしきい値電圧  $V_{t h}$  よりも高い状態をいう。つまり、nチャネル型のトランジスタのオフ電流とは、ソースに対するゲートの電圧  $V_{g s}$  がしきい値電圧  $V_{t h}$  よりも低いときのドレイン電流、という場合がある。

#### 【 0 0 4 1 】

上記オフ電流の説明において、ドレインをソースと読み替えてよい。つまり、オフ電流は、トランジスタがオフ状態にあるときのソース電流をいう場合がある。また、オフ電流と同じ意味で、リーク電流という場合がある。また、本明細書等において、オフ電流とは、トランジスタがオフ状態にあるときに、ソースとドレインとの間に流れる電流を指す場合がある。

20

#### 【 0 0 4 2 】

また、本明細書等において、オン電流とは、トランジスタがオン状態（導通状態、ともいう）にあるときに、ソースとドレインとの間に流れる電流を指す場合がある。

#### 【 0 0 4 3 】

また、本明細書等において、金属酸化物（metal oxide）とは、広い意味での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体（透明酸化物導電体、を含む）、酸化物半導体などに分類される。

30

#### 【 0 0 4 4 】

例えば、トランジスタのチャネル形成領域に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、金属酸化物が増幅作用、整流作用、およびスイッチング作用の少なくとも1つを有する場合、当該金属酸化物を、金属酸化物半導体（metal oxide semiconductor）と呼ぶことができる。すなわち、チャネル形成領域に金属酸化物を有するトランジスタを、「酸化物半導体トランジスタ」、「OSトランジスタ」と呼ぶことができる。同様に、「酸化物半導体を用いたトランジスタ」も、チャネル形成領域に金属酸化物を有するトランジスタである。

#### 【 0 0 4 5 】

また、本明細書等において、窒素を有する金属酸化物も金属酸化物（metal oxide）と呼称する場合がある。また、窒素を有する金属酸化物を、金属酸窒化物（metal oxy nitride）と呼称してもよい。金属酸化物の詳細については後述する。

40

#### 【 0 0 4 6 】

##### （実施の形態1）

本実施の形態では、本発明の一形態に係わる半導体装置の構成例および動作例について説明する。本発明の一形態に係わる半導体装置は、積和演算回路と記憶装置を有する。また、本発明の一形態に係わる半導体装置は、半導体基板に形成されたトランジスタを有する層の上方に、OSトランジスタを有する層が積層して設けられた構造を有する。OSトランジスタは、オフ電流が非常に小さいという性質を有する。

50

## 【0047】

## &lt;半導体装置の斜視概略図&gt;

図1は、本発明の一形態に係わる半導体装置100の構成例を示す斜視概略図である。図1に示す半導体装置100は、層101および層102を有し、層101の上方に層102が積層して設けられた構造を有する。層101および層102には、それぞれ半導体特性を利用することで機能しうる回路が設けられている。なお、本明細書等で説明する図面においては、主な信号の流れを矢印または線で示しており、電源線等は省略する場合がある。

## 【0048】

半導体装置100は、ワード線ドライバ回路111、ピット線ドライバ回路112、および積和演算ブロック113を有する。ワード線ドライバ回路111およびピット線ドライバ回路112は、層101に設けられており、積和演算ブロック113は、層101および層102にまたがって設けられている。

10

## 【0049】

ワード線ドライバ回路111およびピット線ドライバ回路112は、半導体基板SUBに形成されたトランジスタを用いて構成される。半導体基板SUBは、トランジスタのチャネル領域を形成することが可能であれば、特に限定されない。例えば、単結晶シリコン基板、単結晶ゲルマニウム基板、化合物半導体基板(SiC基板、GaN基板など)、SOI(Silicon on Insulator)基板などを用いることができる。

20

## 【0050】

SOI基板としては、例えば、鏡面研磨ウエハに酸素イオンを注入した後、高温加熱することにより、表面から一定の深さに酸化層を形成させるとともに、表面層に生じた欠陥を消滅させて形成されたSIMOX(Separation by Implanted Oxygen)基板や、水素イオン注入により形成された微小ボイドの熱処理による成長を利用して半導体基板を劈開するスマートカット法、ELTRAN法(登録商標:Epitaxial Layer Transfer)などを用いて形成されたSOI基板を用いることができる。また、単結晶基板を用いて形成されたトランジスタは、チャネル形成領域に単結晶半導体を有する。

## 【0051】

積和演算ブロック113は、半導体基板SUBに形成されたトランジスタ、およびOSトランジスタを用いて構成される。OSトランジスタは薄膜法などの手法を用いて形成できるため、半導体基板SUB上に積層して設けることができる。すなわち、層101では、半導体基板SUBに形成されたトランジスタを用いて回路が構成され、層102では、OSトランジスタを用いて回路が構成される。

30

## 【0052】

なお、本実施の形態では、半導体基板SUBに、単結晶シリコン基板を用いた例について説明する。単結晶シリコン基板に形成されたトランジスタを、Siトランジスタと呼ぶ。Siトランジスタを用いて構成された回路は、高速な動作が可能である。

## 【0053】

積和演算ブロック113を、SiトランジスタおよびOSトランジスタを用いて構成することで、Siトランジスタのみを用いて構成した場合よりも、半導体装置100のチップ面積を削減(半導体装置100を小型化)することができる。また、OSトランジスタは、Siトランジスタと同様の製造装置を用いて作製できるため、低コストでの作製が可能である。

40

## 【0054】

ここで、酸化物半導体のバンドギャップは2.5eV以上、好ましくは3.0eV以上であるため、OSトランジスタは熱励起によるリーク電流が小さく、オフ電流が非常に小さい性質を有する。なお、オフ電流とは、トランジスタがオフ状態にあるときに、ソースとドレインとの間に流れる電流をいう。

## 【0055】

50

OSトランジスタのチャネル形成領域に用いられる金属酸化物は、インジウム (In) および亜鉛 (Zn) の少なくとも一方を含む酸化物半導体であることが好ましい。このような酸化物半導体としては、In-M-Zn酸化物（元素Mは、例えばAl、Ga、Y及びSnから選ばれる一または複数）が代表的である。電子供与体（ドナー）となる水分、水素などの不純物を低減し、かつ酸素欠損も低減することで、酸化物半導体をi型（真性）、または実質的にi型にすることができる。このような酸化物半導体は、高純度化された酸化物半導体と呼ぶことができる。OSトランジスタの詳細については、実施の形態2および実施の形態3で説明する。

#### 【0056】

また、図1に示すように、層101に設けられたワード線ドライバ回路111と、積和演算ブロック113の層102に設けられた部分とは、配線WLによって電気的に接続される。同様に、層101に設けられたビット線ドライバ回路112と、積和演算ブロック113の層102に設けられた部分とは、配線BLによって電気的に接続される。

10

#### 【0057】

なお、本実施の形態では、ワード線ドライバ回路111およびビット線ドライバ回路112を、Siトランジスタを用いて構成する例について説明したが、OSトランジスタを用いて構成してもよい。

#### 【0058】

<積和演算ブロックの構成例>

図2Aは、積和演算ブロック113の構成例を示す斜視概略図である。積和演算ブロック113は、 $m \times n$ 個の積和演算ユニット10、配線WL、および配線BLを有する（m、nは1以上の整数）。

20

#### 【0059】

図2Aに示すように、一列にm個、一行にn個の積和演算ユニット10が行列状（マトリクス状、ともいう）に配置され、図2Aに示す[1, 1]、[m, 1]、[1, n]、[m, n]は、積和演算ユニット10のアドレスを示している。各積和演算ユニット10は、配線WLおよび配線BLと電気的に接続される。

#### 【0060】

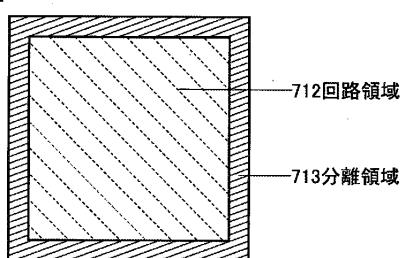

また、積和演算ユニット10は、層101および層102にまたがって設けられ、積和演算ユニット10の層102に設けられた部分を回路MEM、積和演算ユニット10の層101に設けられた部分を回路MACと呼称する。

30

#### 【0061】

図2Bは、積和演算ユニット10の構成例を示す斜視概略図である。積和演算ユニット10において、回路MEMと回路MACとは、配線WSおよび配線WOによって電気的に接続されている。

#### 【0062】

図3は、積和演算ユニット10の構成例を示す回路図である。積和演算ユニット10は、回路MEM、回路MAC、配線REF、配線PC、配線RD、配線DX、配線DA、配線DB、配線CX、s本の配線WS、およびt本の配線WOを有する（s、tは1以上の整数）。

40

#### 【0063】

回路MEMと回路MACとは、s本の配線WS、およびt本の配線WOを介して電気的に接続される。また、図3に示すように、回路MEMには、積和演算ブロック113が有する配線WLおよび配線BLのうち、s本の配線WLおよびt本の配線BLが配置されている。

#### 【0064】

<回路MEMの構成例>

回路MEMは、t個のプリチャージ回路12、 $s \times t$ 個のメモリセル11を有し、一列にs個、一行にt個のメモリセル11が行列状に配置される。図3に示す[1, 1]、[s, 1]、[1, t]、[s, t]は、メモリセル11のアドレスを示している。

50

## 【0065】

なお、本明細書等で説明する図面において、プリチャージ回路12、メモリセル11等の構成要素が複数個存在する場合、その一つに対して回路図等の詳細を図示し、それ以外に対しては詳細を省略する場合がある。例えば、図3において、メモリセル11[1, 1]については回路図を図示し、メモリセル11[s, 1]、メモリセル11[1, t]、およびメモリセル11[s, t]については回路図を省略している。

## 【0066】

メモリセル11は、配線WSおよび配線WOと電気的に接続され、kを1以上s以下の整数、1を1以上t以下の整数とした場合、メモリセル11[k, 1]は、配線WS[k]および配線WO[1]と電気的に接続される(k、1は図示せず)。また、メモリセル11[k, 1]は、配線WL[k]および配線BL[1]と電気的に接続される。

10

## 【0067】

同様に、プリチャージ回路12は、配線WOと電気的に接続され、プリチャージ回路12[1]は、配線WO[1]と電気的に接続される。また、プリチャージ回路12は、配線REFおよび配線PCと電気的に接続される。

## 【0068】

プリチャージ回路12は、トランジスタ25を有し、配線WOをプリチャージする機能を有する。トランジスタ25のソースまたはドレインの一方は、配線REFと電気的に接続され、トランジスタ25のソースまたはドレインの他方は、配線WOと電気的に接続され、トランジスタ25のゲートは配線PCと電気的に接続される。すなわち、配線PCにハイレベルの電位が印加された場合、トランジスタ25はオン状態となり、プリチャージ回路12は、配線WOを、配線REFに供給される電位でプリチャージする機能を有する。

20

## 【0069】

メモリセル11は、トランジスタ21乃至トランジスタ23、および容量24を有する。トランジスタ21のソースまたはドレインの一方は、配線BLと電気的に接続され、トランジスタ21のソースまたはドレインの他方は、トランジスタ22のゲート、および容量24の一方の電極と電気的に接続され、トランジスタ21のゲートは配線WLと電気的に接続される。トランジスタ22のソースまたはドレインの一方は、トランジスタ23のソースまたはドレインの一方と電気的に接続され、トランジスタ23のソースまたはドレインの他方は、配線WOと電気的に接続される。

30

## 【0070】

また、トランジスタ22のソースまたはドレインの他方は、基準の電位と電気的に接続され、容量24の他方の電極は、例えば、基準の電位と電気的に接続される。なお、トランジスタ21のソースまたはドレインの他方と、トランジスタ22のゲート、および容量24の一方の電極との接続部を、ノードN1と呼称する。

## 【0071】

メモリセル11は、電荷を蓄積し保持することでデータを記憶する機能を有する。メモリセル11は、例えば、2値(ハイレベルまたはローレベル)のデータを記憶する機能を有する。なお、本実施の形態において、ローレベルは、前述した基準の電位を用いて表される。また、ハイレベルを表す電位を、配線REFに供給することができる。

40

## 【0072】

メモリセル11において、データの書き込みは、配線BLおよび配線WLを用いて行われる。メモリセル11にデータを書き込む場合、配線BLはビット線として機能し、配線WLはワード線として機能し、トランジスタ21は、容量24の一方の電極と配線BLとを導通または非導通とするスイッチとして機能する。データの書き込みは、配線WLにハイレベルの電位を印加し、容量24の一方の電極と配線BLとを導通状態とし、配線BLの電位をノードN1に書き込むことによって行われる。

## 【0073】

メモリセル11において、データの読み出しが、配線WO、配線WS、およびプリチャージ回路12を用いて行われる。メモリセル11からデータを読み出す場合、トランジスタ

50

22は、ノードN1の電位によって導通または非導通の状態となり、トランジスタ23は、トランジスタ22のソースまたはドレインの一方と配線WOとを導通または非導通とするスイッチとして機能する。

【0074】

データの読み出しへ、プリチャージ回路12を用いて配線WOにハイレベルの電位（配線REFに供給される電位）を印加した後、配線WOをフローティング状態（電気的に浮遊な状態）とし、配線WSにハイレベルの電位を印加して、トランジスタ22のソースまたはドレインの一方と配線WOとを導通状態とすることによって行われる。すなわち、ノードN1の電位がハイレベルの場合、トランジスタ22は導通状態であり、配線WOはローレベル（基準の電位）となる。ノードN1の電位がローレベルの場合、トランジスタ22は非導通状態であり、配線WOはハイレベルのままである。

10

【0075】

ここで、トランジスタ21乃至トランジスタ23、およびトランジスタ25は、チャネル形成領域に金属酸化物を有するトランジスタ（OSトランジスタ）である。例えば、トランジスタ21のチャネル形成領域に、インジウム、元素M（元素Mは、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種）、亜鉛のいずれか一つを有する金属酸化物を用いることができる。特に、インジウム、ガリウム、亜鉛からなる金属酸化物であることが好ましい。

20

【0076】

OSトランジスタはオフ電流が非常に小さいため、トランジスタ21にOSトランジスタを用いることで、メモリセル11は、容量24に蓄積した電荷を長時間保持することができる。または、トランジスタ21にOSトランジスタを用いることで、メモリセル11が有する容量24の容量値を小さくしても、容量24に蓄積した電荷を保持することができる。また、OSトランジスタは高温環境下でもオフ電流が増加しにくく、メモリセル11を信頼性の高いメモリセルとすることができます。

30

【0077】

また、トランジスタ21乃至トランジスタ23、およびトランジスタ25は、バックゲートを有していてもよい。例えば、トランジスタ21がバックゲートを有する場合、トランジスタ21のバックゲートに所定の電位を印加することで、トランジスタ21のしきい値電圧を増減することができる。または、トランジスタ21のバックゲートを、トランジスタ21のゲートと電気的に接続することで、トランジスタ21のオン電流を大きくすることができます。

【0078】

また、容量24は、電極となる導電体の間に絶縁体を挟んだ構成である。電極を構成する導電体としては、金属の他、導電性を付与した半導体などを用いることができる。

【0079】

<回路MACの構成例>

回路MACは、デコーダ回路13、レジスタ回路14、t個の回路15、乗算回路16、加算回路17、レジスタ回路18、およびt本の配線WTを有する。なお、乗算回路16および加算回路17は、積和演算回路を構成する。

40

【0080】

回路MACは、例えば、Siトランジスタを用いたCMOS（Complementary Metal Oxide Semiconductor）回路で構成することができる。CMOS回路は、例えば、単結晶シリコン基板に形成されたnチャネル型トランジスタとpチャネル型トランジスタを用いて構成され、ハイレベルまたはローレベル（HighまたはLow、HまたはL、1または0、等と表される場合がある）で表されるデジタル信号を扱う回路（デジタル回路、論理回路、ともいう）として、広く用いられている。

【0081】

50

なお、配線 D X、配線 D A、配線 C X には、複数ビットの情報量を有する信号が入力されてもよい。例えば、配線 D X に入力される信号を、8 ビット、16 ビット、32 ビット、または 64 ビットの情報量を有する信号とすることができます。

【 0 0 8 2 】

デコーダ回路 13 は、配線 C X、および s 本の配線 W S と電気的に接続され、配線 C X に入力される信号をデコードし、s 本の配線 W S を駆動する機能を有する。より具体的には、デコーダ回路 13 は、配線 C X に入力される信号に従って、配線 W S [ 1 ] 乃至配線 W S [ s ] から 1 本を選択し、選択した配線 W S にハイレベルの電位を印加する。

【 0 0 8 3 】

レジスタ回路 14 は、配線 D X と電気的に接続され、配線 D X に入力される信号を一時的に保持する機能を有する。レジスタ回路 14 は、配線 D X に入力された信号を保持し、乗算回路 16 に出力する。

【 0 0 8 4 】

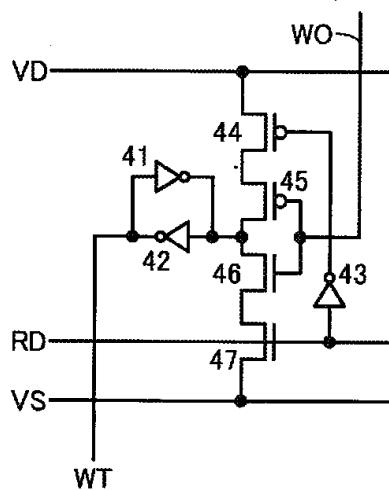

回路 15 の構成例について、図 4 A に回路図を示す。回路 15 は、インバータ 4 1 乃至インバータ 4 3、トランジスタ 4 4 乃至トランジスタ 4 7、配線 V D、および配線 V S を有する。

【 0 0 8 5 】

トランジスタ 4 4 のソースまたはドレインの一方は、配線 V D と電気的に接続され、トランジスタ 4 4 のソースまたはドレインの他方は、トランジスタ 4 5 のソースまたはドレインの一方と電気的に接続され、トランジスタ 4 5 のソースまたはドレインの他方は、トランジスタ 4 6 のソースまたはドレインの一方、インバータ 4 2 の入力端子、およびインバータ 4 1 の出力端子と電気的に接続され、トランジスタ 4 6 のソースまたはドレインの他方は、トランジスタ 4 7 のソースまたはドレインの一方と電気的に接続され、トランジスタ 4 7 のソースまたはドレインの他方は、配線 V S と電気的に接続される。

【 0 0 8 6 】

トランジスタ 4 4 のゲートは、インバータ 4 3 の出力端子と電気的に接続され、トランジスタ 4 5 のゲートは、トランジスタ 4 6 のゲート、および配線 W O と電気的に接続され、トランジスタ 4 7 のゲートは、インバータ 4 3 の入力端子、および配線 R D と電気的に接続される。また、インバータ 4 2 の出力端子は、インバータ 4 1 の入力端子、および配線 W T と電気的に接続される。

【 0 0 8 7 】

配線 V D には高電源電位 V D D が供給され、配線 V S には低電源電位 V S S が供給される。なお、低電源電位 V S S は、半導体装置 100 において、基準の電位として用いてよい。

【 0 0 8 8 】

回路 15 において、配線 R D にハイレベルの電位が印加された場合、インバータ 4 3 はローレベルの電位を出力するため、トランジスタ 4 4 およびトランジスタ 4 7 はオン状態となり、トランジスタ 4 5 およびトランジスタ 4 6 はインバータとして機能する。また、インバータ 4 1 およびインバータ 4 2 はインバータループを形成し、メモリとしての機能を有するため、回路 15 は、配線 R D にハイレベルの電位が印加された時の配線 W O の電位状態（ハイレベルまたはローレベル）を取得し、インバータ 4 1 およびインバータ 4 2 によって保持し、配線 W T に出力する機能を有する。

【 0 0 8 9 】

配線 W T に出力された信号は、乗算回路 16 にて、レジスタ回路 14 から出力された信号と掛け合わせ、加算回路 17 へ出力される。加算回路 17 は、乗算回路 16 から出力された信号と、配線 D A に入力された信号とを足し合わせ、レジスタ回路 18 へ出力する。レジスタ回路 18 は、加算回路 17 から出力された信号を一時的に保持し、配線 D B を介して積和演算ユニット 10 の外部へ出力する。

【 0 0 9 0 】

なお、デコーダ回路、レジスタ回路、乗算回路、加算回路については、それぞれ、C M O

10

20

30

40

50

S回路で構成されたデコーダ回路、レジスタ回路、乗算回路、加算回路が知られているため、説明を省略する。

【0091】

<積和演算ユニット>

ここで、配線DXに入力される信号を、データ信号Xとし、配線DAに入力される信号を、データ信号Aとし、配線DBに出力される信号を、データ信号Bとする。また、t本の配線WT(配線WT[1]乃至配線WT[t])に出力される信号を、データ信号Wとする。すると、積和演算ユニット10はデータ信号Bを出力する機能を有し、データ信号Bは、データ信号Xにデータ信号Wを掛け合わせ、データ信号Aを足した結果である、と言い換えることができる。

10

【0092】

また、回路MEMはs×t個のメモリセル11を有するため、回路MEMは、メモリセル11に、データ信号W[1]乃至データ信号W[s]を記憶する機能を有する。データ信号W[1]乃至データ信号W[s]は、配線WS[1]乃至配線WS[s]を駆動することで、時間を区切って読み出すことができる。

【0093】

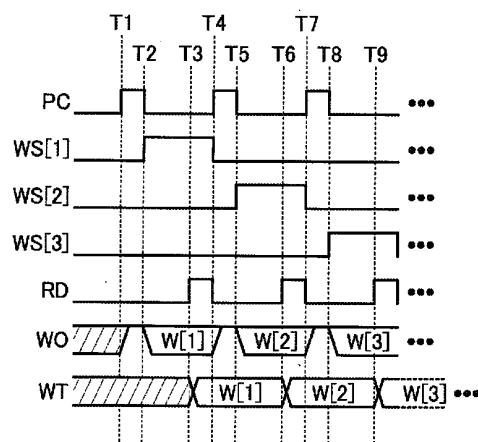

例えば、データ信号W[1]乃至データ信号W[s]のうち、データ信号W[1]乃至データ信号W[3]を配線WTに読み出す場合について、図4Bにタイミングチャートを示す。図4Bは、時刻T1乃至時刻T9における、配線PC、配線WS[1]乃至配線WS[3]、配線RD、配線WO、および配線WTの電位状態(ハイレベルまたはローレベル)を示すタイミングチャートである。

20

【0094】

図4Bに示すように、時刻T1において配線PCがハイレベルとなり、配線WOはハイレベルの電位でプリチャージされる。時刻T2において配線WS[1]がハイレベルになると、配線WOは、メモリセル11[1,1]乃至メモリセル11[1,t]が記憶していたデータに応じた電位状態となる(図4Bでは、W[1]と表記)。時刻T3において配線RDがハイレベルになると、配線WOの電位状態が配線WTに出力される。

【0095】

また、時刻T4において配線PCがハイレベルとなり、配線WOはハイレベルの電位でプリチャージされる。時刻T5において配線WS[2]がハイレベルになると、配線WOは、メモリセル11[2,1]乃至メモリセル11[2,t]が記憶していたデータに応じた電位状態となる(図4Bでは、W[2]と表記)。時刻T6において配線RDがハイレベルになると、配線WOの電位状態が配線WTに出力される。時刻T7乃至時刻T9においても同様のため、説明を省略する。

30

【0096】

データ信号Xとデータ信号Aについても、複数のデータ信号Xおよび複数のデータ信号Aを用意し、時間を区切って積和演算ユニット10に入力することで、複数の積和演算を行うことができる。

【0097】

例えば、s個のデータ信号X(データ信号X[1]乃至データ信号X[s])、およびs個のデータ信号A(データ信号A[1]乃至データ信号A[s])を用意し、データ信号X[1]乃至データ信号X[s]のそれぞれと、メモリセル11から読み出したデータ信号W[1]乃至データ信号W[s]を掛け合わせ、データ信号A[1]乃至データ信号A[s]を足すことで、s個のデータ信号B(データ信号B[1]乃至データ信号B[s])を得ることができる。すなわち、kを1以上s以下の整数とした場合、データ信号B[k] = データ信号X[k] × データ信号W[k] + データ信号A[k]である。

40

【0098】

さらに、データ信号B[k]をデータ信号A[k+1]に入力し、データ信号A[1]を0とすることで、データ信号B = データ信号X[1] × データ信号W[1] + データ信号X[2] × データ信号W[2] + (途中省略) + データ信号X[s-1] × データ信号W

50

[ s - 1 ] + データ信号 X [ s ] × データ信号 W [ s ] を得ることができる。

【 0 0 9 9 】

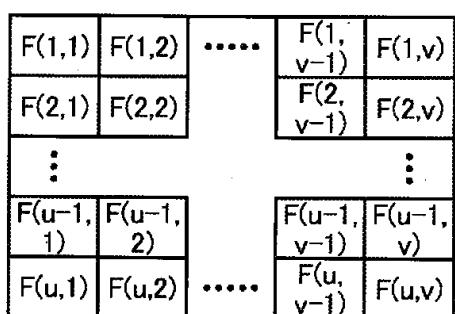

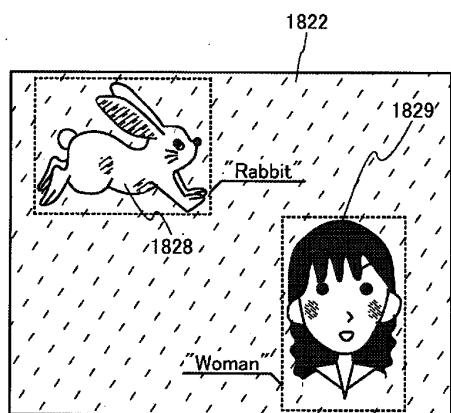

例えば、 $s = 9$  の場合、データ信号 X を 3 行 × 3 列のデータ信号、データ信号 W を 3 行 × 3 列のデータ信号とすることができます。 $s = 9$  の場合における、データ信号 X とデータ信号 W のイメージ図を、図 5 A に示す。この場合、データ信号 B = データ信号 X [ 1 ] × データ信号 W [ 1 ] + データ信号 X [ 2 ] × データ信号 W [ 2 ] + (途中省略) + データ信号 X [ 8 ] × データ信号 W [ 8 ] + データ信号 X [ 9 ] × データ信号 W [ 9 ] は、例えば、画像データに対する畳み込み演算に用いることができる。

【 0 1 0 0 】

< 畳み込み演算 >

10

次に、画像データに対する畳み込み演算の例を示す。 $p$  行  $q$  列の画像データを画像データ  $P ( 1, 1 )$  乃至  $P ( p, q )$  で表し ( $p, q$  は 2 以上の整数)、 $u$  行  $v$  列のフィルタをフィルタ  $F ( 1, 1 )$  乃至  $F ( u, v )$  で表す ( $u, v$  は 1 以上の整数であり、 $u < p, v < q$ )。画像データ  $P ( 1, 1 )$  乃至  $P ( p, q )$  は、それぞれ 1 画素分に相当する画像データであり、フィルタ  $F ( 1, 1 )$  乃至  $F ( u, v )$  は、それぞれフィルタを構成するパラメータである。図 5 B に、画像データ  $P$  のイメージ図を示し、図 5 C に、フィルタ  $F$  のイメージ図を示す。

【 0 1 0 1 】

例えば、 $p = q = 3, u = v = 2$  の時、下記に示す  $Y ( 1, 1 )$  乃至  $Y ( 2, 2 )$  を計算する。

20

$$Y ( 1, 1 ) = P ( 1, 1 ) \times F ( 1, 1 ) + P ( 1, 2 ) \times F ( 1, 2 ) + P ( 2, 1 ) \times F ( 2, 1 ) + P ( 2, 2 ) \times F ( 2, 2 ) \quad ( a 1 )$$

$$Y ( 1, 2 ) = P ( 1, 2 ) \times F ( 1, 1 ) + P ( 1, 3 ) \times F ( 1, 2 ) + P ( 2, 2 ) \times F ( 2, 1 ) + P ( 2, 3 ) \times F ( 2, 2 ) \quad ( a 2 )$$

$$Y ( 2, 1 ) = P ( 2, 1 ) \times F ( 1, 1 ) + P ( 2, 2 ) \times F ( 1, 2 ) + P ( 3, 1 ) \times F ( 2, 1 ) + P ( 3, 2 ) \times F ( 2, 2 ) \quad ( a 3 )$$

$$Y ( 2, 2 ) = P ( 2, 2 ) \times F ( 1, 1 ) + P ( 2, 3 ) \times F ( 1, 2 ) + P ( 3, 2 ) \times F ( 2, 1 ) + P ( 3, 3 ) \times F ( 2, 2 ) \quad ( a 4 )$$

【 0 1 0 2 】

式 a 1 乃至 a 4 を一般式で表すと、

30

$$Y ( x, y ) = a ( b P ( a + x - 1, b + y - 1 ) \times F ( a, b ) ) \quad ( a 5 )$$

である。なお、 $a$  は 1 乃至  $u$  の整数、 $b$  は 1 乃至  $v$  の整数であり、 $\times$  は 1 乃至  $p - u + 1$  の整数、 $y$  は 1 乃至  $q - v + 1$  の整数である。例えば、 $Y ( 1, 1 )$  を計算する場合、図 5 B に示す、領域 5 0 の画像データ  $P$  に対して積和演算を行う。

【 0 1 0 3 】

画像データに対する畳み込み演算は、前記積和演算を用いて  $Y ( 1, 1 )$  乃至  $Y ( u, v )$  を計算することで行われる。画像データに対する畳み込み演算を行うことで、例えば、画像のエッジなどを検出することができる。また、畳み込み演算を複数回行うことで、画像の形やパターンなど、画像データの特徴を検出することができ、このような畳み込み演算は、画像認識において利用されている。

40

【 0 1 0 4 】

積和演算ユニット 1 0 のメモリセル 1 1 にフィルタ  $F$  のパラメータを記憶し、データ信号 X に画像データ  $P$  を入力することで、積和演算ユニット 1 0 は前記畳み込み演算を行うことができる。畳み込み演算に用いられるフィルタ  $F$  のパラメータは、例えば学習によって生成され、学習が終わったフィルタ  $F$  のパラメータは繰り返し用いられる。積和演算ユニット 1 0 では、個々の積和演算ユニット 1 0 が有する配線  $W_S$  および配線  $W_O$  を用いて、フィルタ  $F$  のパラメータをデータ信号  $W$  として取り出すため、フィルタ  $F$  のパラメータを繰り返し用いる点において、積和演算ユニット 1 0 は効率的である。

【 0 1 0 5 】

なお、複数の積和演算ユニット 1 0 を使って畳み込み演算を行ってもよい。画像データ  $P$

50

およびフィルタ F は 2 次元のデータであるため、例えば、u 行 v 列のフィルタ F (1, 1) 乃至 F (u, v) に対して、フィルタ F (1, 1) 乃至 F (1, v) を積和演算ユニット 10 [1, 1] に、フィルタ F (2, 1) 乃至 F (2, v) を積和演算ユニット 10 [2, 1] に、(途中省略)、フィルタ F (u, 1) 乃至 F (u, v) を積和演算ユニット 10 [u, 1] に記憶することができる (m >= u とする)。この場合、画像データ P (1, 1) 乃至 P (1, v) に対する積和演算を積和演算ユニット 10 [1, 1] で、画像データ P (2, 1) 乃至 P (2, v) に対する積和演算を積和演算ユニット 10 [2, 1] で、(途中省略)、画像データ P (u, 1) 乃至 P (u, v) に対する積和演算を積和演算ユニット 10 [u, 1] で行うことができ、それらの結果を足し合わせることで、Y (1, 1) を計算することができる。

10

#### 【0106】

また、本実施の形態では、積和演算ユニット 10 を画像データに対する畳み込み演算に用いる例を示したが、積和演算は、ニューロンとシナプスで構成される神経回路網を模したニューラルネットワークで多用されており、積和演算ユニット 10 をニューラルネットワークに用いることもできる。積和演算ユニット 10 をニューラルネットワークに用いる場合、フィルタ F のパラメータは重み係数に相当し、積和演算ユニット 10 は、メモリセル 11 に重み係数を記憶することで、前記重み係数を効率よく用いることができる。

#### 【0107】

本発明の一形態に係わる半導体装置 100 は、半導体基板に形成されたトランジスタを有する層の上方に、OS トランジスタを有する層が積層して設けられ、OS トランジスタを用いてメモリセルが構成される。OS トランジスタはオフ電流が非常に小さいため、OS トランジスタを用いて構成されたメモリセルは、記憶したデータを長時間保持することができる。

20

#### 【0108】

また、半導体基板に形成されたトランジスタを用いて積和演算回路が構成され、積和演算回路は、上方に積層して設けられたメモリセルと、配線 WS および配線 WO を介して電気的に接続される。半導体装置 100 は、積和演算回路とメモリセルとを組み合わせた積和演算ユニット 10 を複数有し、積和演算ユニット 10 のそれぞれにおいて、メモリセルに記憶したフィルタ F のパラメータ (または、重み係数) を読み出すことで、畳み込み演算 (または、ニューラルネットワークを用いた計算) を効率よく行うことができる。半導体装置 100 は、フィルタ F のパラメータが繰り返し用いられる畳み込み演算 (または、重み係数が繰り返し用いられるニューラルネットワークの計算) に好適に用いることができる。

30

#### 【0109】

半導体装置 100 は、積和演算回路の上方にメモリセルが積層して設けられるため、半導体装置 100 は小型である。OS トランジスタは高温環境下でもオフ電流が増加しにくいため、積和演算回路の発熱に対しても信頼性の高いメモリセルとすることができます。また、OS トランジスタは、Si トランジスタと同様の製造装置を用いて作製できるため、半導体装置 100 は低コストでの作製が可能である。

40

#### 【0110】

なお、本実施の形態は、本明細書に記載する他の実施の形態と適宜組み合わせて実施することができる。

#### 【0111】

##### (実施の形態 2)

本実施の形態では、上記実施の形態で説明した半導体装置 100 を構成する、トランジスタの構成例について説明する。本実施の形態では、単結晶シリコン基板に形成された Si トランジスタを有する層の上方に、OS トランジスタを有する層が積層して設けられた構造を有する、半導体装置の構成例について説明する。

#### 【0112】

<半導体装置の構成例>

50

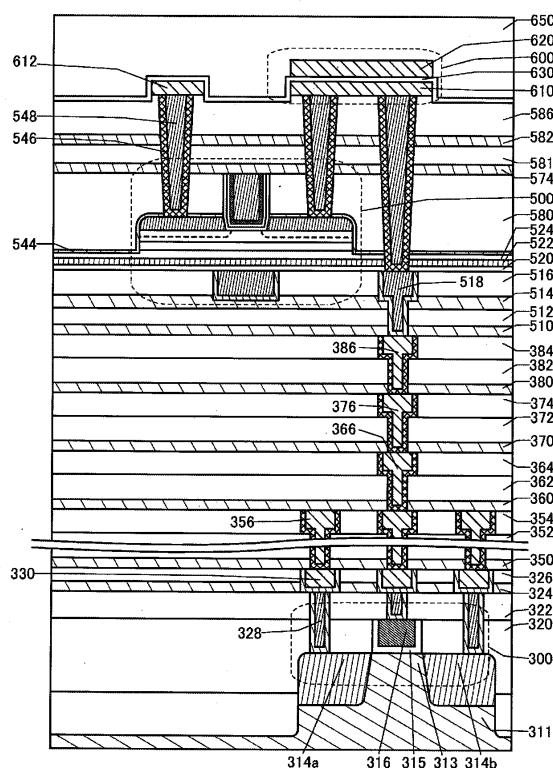

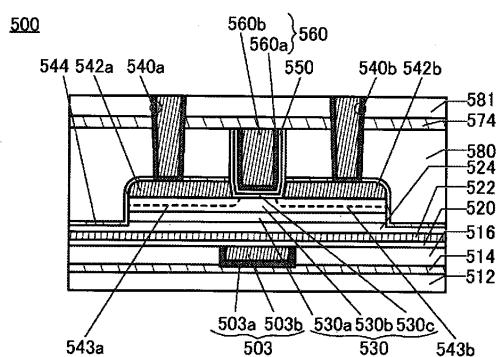

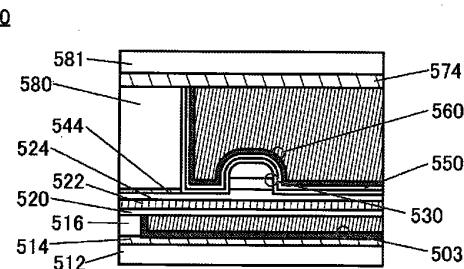

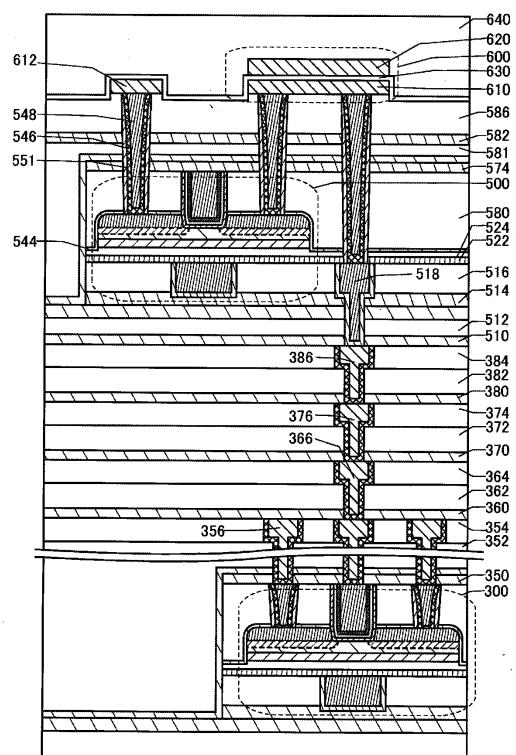

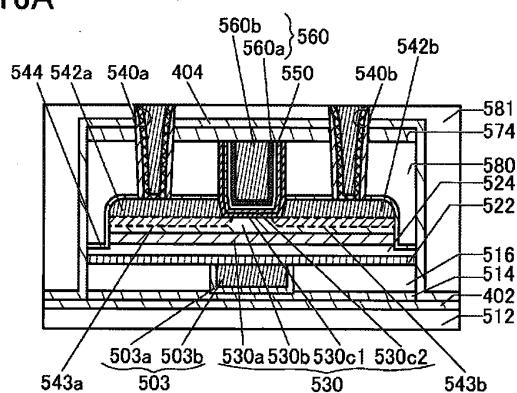

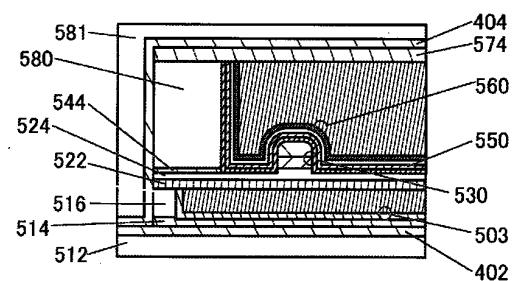

図6に示す半導体装置は、トランジスタ300と、トランジスタ500、および容量素子600を有する。図7Aはトランジスタ500のチャネル長方向の断面図であり、図7Bはトランジスタ500のチャネル幅方向の断面図であり、図7Cはトランジスタ300のチャネル幅方向の断面図である。

【0113】

例えば、トランジスタ500は上記実施の形態に示したトランジスタ21に相当し、トランジスタ500は第1のゲート（トップゲート、または単に、ゲート、ともいう）に加えて、第2のゲート（ボトムゲート、バックゲート、ともいう）を有する。また、トランジスタ300は、例えば、半導体装置100が有するトランジスタ47に相当し、容量素子600は容量24に相当する。

10

【0114】

トランジスタ500は、チャネル形成領域に金属酸化物を有するトランジスタ（OSトランジスタ）である。トランジスタ500は、オフ電流が非常に小さい、高温環境下でもオフ電流が増加しにくいという特徴を有するため、上記実施の形態では、これを半導体装置100に用いることにより、当該半導体装置を信頼性の高い半導体装置とすることができます。

【0115】

図6に示すように、本実施の形態で説明する半導体装置において、トランジスタ500はトランジスタ300の上方に設けられ、容量素子600は、トランジスタ300およびトランジスタ500の上方に設けられている。

20

【0116】

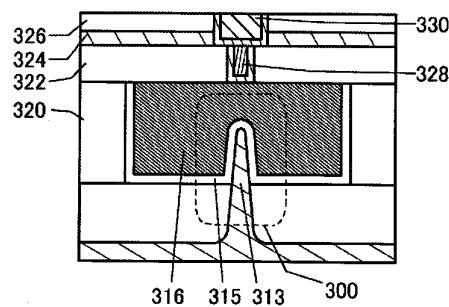

トランジスタ300は、基板311上に設けられ、導電体316、絶縁体315、基板311の一部からなる半導体領域313、およびソース領域またはドレイン領域として機能する低抵抗領域314a、および低抵抗領域314bを有する。

30

【0117】

トランジスタ300は、図7Cに示すように、半導体領域313の上面およびチャネル幅方向の側面が絶縁体315を介して導電体316に覆われている。このように、トランジスタ300をFin型とすることにより、実効上のチャネル幅が増大することによりトランジスタ300のオン特性を向上させることができる。また、ゲート電極の電界の寄与を高くすることができるため、トランジスタ300のオフ特性を向上させることができる。

【0118】

なお、トランジスタ300は、pチャネル型、あるいはnチャネル型のいずれでもよい。

【0119】

半導体領域313のチャネルが形成される領域、その近傍の領域、ソース領域、またはドレイン領域となる低抵抗領域314a、および低抵抗領域314bなどにおいて、シリコン系半導体などの半導体を含むことが好ましく、単結晶シリコンを含むことが好ましい。または、Ge（ゲルマニウム）、SiGe（シリコンゲルマニウム）、GaAs（ガリウムヒ素）、GaAlAs（ガリウムアルミニウムヒ素）などを有する材料で形成してもよい。結晶格子に応力を与え、格子間隔を変化させることで有効質量を制御したシリコンを用いた構成としてもよい。またはGaAsとGaAlAs等を用いることで、トランジスタ300をHEMT（High Electron Mobility Transistor）としてもよい。

40

【0120】

低抵抗領域314a、および低抵抗領域314bは、半導体領域313に適用される半導体材料に加え、ヒ素、リンなどのn型の導電性を付与する元素、またはホウ素などのp型の導電性を付与する元素を含む。

【0121】

ゲート電極として機能する導電体316は、ヒ素、リンなどのn型の導電性を付与する元素、もしくはホウ素などのp型の導電性を付与する元素を含むシリコンなどの半導体材料、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。

50

## 【0122】

なお、導電体の材料により、仕事関数が定まるため、導電体の材料を変更することで、トランジスタの  $V_{th}$  を調整することができる。具体的には、導電体に窒化チタンや窒化タンタルなどの材料を用いることが好ましい。さらに導電性と埋め込み性を両立するために導電体にタングステンやアルミニウムなどの金属材料を積層して用いることが好ましく、特にタングステンを用いることが耐熱性の点で好ましい。

## 【0123】

なお、図6に示すトランジスタ300は一例であり、その構造に限定されず、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

## 【0124】

トランジスタ300を覆って、絶縁体320、絶縁体322、絶縁体324、および絶縁体326が順に積層して設けられている。

## 【0125】

絶縁体320、絶縁体322、絶縁体324、および絶縁体326として、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウムなどを用いればよい。

## 【0126】

絶縁体322は、その下方に設けられるトランジスタ300などによって生じる段差を平坦化する平坦化膜としての機能を有していてもよい。例えば、絶縁体322の上面は、平坦性を高めるために化学機械研磨(CMP)法等を用いた平坦化処理により平坦化されていてもよい。

10

## 【0127】

また、絶縁体324には、基板311、またはトランジスタ300などから、トランジスタ500が設けられる領域に、水素や不純物が拡散しないようなバリア性を有する膜を用いることが好ましい。

## 【0128】

水素に対するバリア性を有する膜の一例として、例えば、CVD法で形成した窒化シリコンを用いることができる。ここで、トランジスタ500等の酸化物半導体を有する半導体素子に、水素が拡散することで、当該半導体素子の特性が低下する場合がある。したがって、トランジスタ500と、トランジスタ300との間に、水素の拡散を抑制する膜を用いることが好ましい。水素の拡散を抑制する膜とは、具体的には、水素の脱離量が少ない膜とする。

20

## 【0129】

水素の脱離量は、例えば、昇温脱離ガス分析(TDS分析)法などを用いて分析することができる。例えば、絶縁体324の水素の脱離量は、TDS分析において、膜の表面温度が50から500の範囲において、水素原子に換算した脱離量が、絶縁体324の面積当たりに換算して、 $1.0 \times 10^{15} \text{ atoms/cm}^2$ 以下、好ましくは $5 \times 10^{15} \text{ atoms/cm}^2$ 以下であればよい。

30

## 【0130】

なお、絶縁体326は、絶縁体324よりも比誘電率が低いことが好ましい。例えば、絶縁体326の比誘電率は4未満が好ましく、3未満がより好ましい。また例えば、絶縁体326の比誘電率は、絶縁体324の比誘電率の0.7倍以下が好ましく、0.6倍以下がより好ましい。比誘電率が低い材料を層間膜として、配線間に生じる寄生容量を低減することができる。

40

## 【0131】

また、絶縁体320、絶縁体322、絶縁体324、および絶縁体326には容量素子600、またはトランジスタ500と接続する導電体328、および導電体330等が埋め込まれている。なお、導電体328、および導電体330は、プラグまたは配線としての機能を有する。また、プラグまたは配線としての機能を有する導電体は、複数の構造をまとめて同一の符号を付与する場合がある。また、本明細書等において、配線と、配線と接

50

続するプラグとが一体物であってもよい。すなわち、導電体の一部が配線として機能する場合、および導電体の一部がプラグとして機能する場合もある。

【0132】

各プラグ、および配線（導電体328、および導電体330等）の材料としては、金属材料、合金材料、金属窒化物材料、または金属酸化物材料などの導電性材料を、単層または積層して用いることができる。耐熱性と導電性を両立するタンゲステンやモリブデンなどの高融点材料を用いることが好ましく、タンゲステンを用いることが好ましい。または、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。低抵抗導電性材料を用いることで配線抵抗を低くすることができる。

【0133】

絶縁体326、および導電体330上に、配線層を設けてもよい。例えば、図6において、絶縁体350、絶縁体352、および絶縁体354が順に積層して設けられている。また、絶縁体350、絶縁体352、および絶縁体354には、導電体356が形成されている。導電体356は、トランジスタ300と接続するプラグ、または配線としての機能を有する。なお導電体356は、導電体328、および導電体330と同様の材料を用いて設けることができる。

10

【0134】

なお、例えば、絶縁体350は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体356は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体350が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ300とトランジスタ500とは、バリア層により分離することができ、トランジスタ300からトランジスタ500への水素の拡散を抑制することができる。

20

【0135】

なお、水素に対するバリア性を有する導電体としては、例えば、窒化タンタル等を用いるとよい。また、窒化タンタルと導電性が高いタンゲステンを積層することで、配線としての導電性を保持したまま、トランジスタ300からの水素の拡散を抑制することができる。この場合、水素に対するバリア性を有する窒化タンタル層が、水素に対するバリア性を有する絶縁体350と接する構造であることが好ましい。

【0136】

絶縁体354、および導電体356上に、配線層を設けてもよい。例えば、図6において、絶縁体360、絶縁体362、および絶縁体364が順に積層して設けられている。また、絶縁体360、絶縁体362、および絶縁体364には、導電体366が形成されている。導電体366は、プラグまたは配線としての機能を有する。なお導電体366は、導電体328、および導電体330と同様の材料を用いて設けることができる。

30

【0137】

なお、例えば、絶縁体360は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体366は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体360が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ300とトランジスタ500とは、バリア層により分離することができ、トランジスタ300からトランジスタ500への水素の拡散を抑制することができる。

40

【0138】

絶縁体364、および導電体366上に、配線層を設けてもよい。例えば、図6において、絶縁体370、絶縁体372、および絶縁体374が順に積層して設けられている。また、絶縁体370、絶縁体372、および絶縁体374には、導電体376が形成されている。導電体376は、プラグまたは配線としての機能を有する。なお導電体376は、導電体328、および導電体330と同様の材料を用いて設けることができる。

【0139】

なお、例えば、絶縁体370は、絶縁体324と同様に、水素に対するバリア性を有する

50

絶縁体を用いることが好ましい。また、導電体376は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体370が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ300とトランジスタ500とは、バリア層により分離することができ、トランジスタ300からトランジスタ500への水素の拡散を抑制することができる。

【0140】

絶縁体374、および導電体376上に、配線層を設けてもよい。例えば、図6において、絶縁体380、絶縁体382、および絶縁体384が順に積層して設けられている。また、絶縁体380、絶縁体382、および絶縁体384には、導電体386が形成されている。導電体386は、プラグまたは配線としての機能を有する。なお導電体386は、導電体328、および導電体330と同様の材料を用いて設けることができる。

10

【0141】

なお、例えば、絶縁体380は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体386は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体380が有する開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ300とトランジスタ500とは、バリア層により分離することができ、トランジスタ300からトランジスタ500への水素の拡散を抑制することができる。

【0142】

上記において、導電体356を含む配線層、導電体366を含む配線層、導電体376を含む配線層、および導電体386を含む配線層、について説明したが、本実施の形態に係る半導体装置はこれに限られるものではない。導電体356を含む配線層と同様の配線層を3層以下にしてもよいし、導電体356を含む配線層と同様の配線層を5層以上にしてもよい。

20

【0143】

絶縁体384上には絶縁体510、絶縁体512、絶縁体514、および絶縁体516が、順に積層して設けられている。絶縁体510、絶縁体512、絶縁体514、および絶縁体516のいずれかは、酸素や水素に対してバリア性のある物質を用いることが好ましい。

30

【0144】

例えば、絶縁体510、および絶縁体514には、例えば、基板311、またはトランジスタ300を設ける領域などから、トランジスタ500を設ける領域に、水素や不純物が拡散しないようなバリア性を有する膜を用いることが好ましい。したがって、絶縁体324と同様の材料を用いることができる。

【0145】

水素に対するバリア性を有する膜の一例として、CVD法で形成した窒化シリコンを用いることができる。ここで、トランジスタ500等の酸化物半導体を有する半導体素子に、水素が拡散することで、当該半導体素子の特性が低下する場合がある。したがって、トランジスタ500と、トランジスタ300との間に、水素の拡散を抑制する膜を用いることが好ましい。水素の拡散を抑制する膜とは、具体的には、水素の脱離量が少ない膜とする。

40

【0146】

また、水素に対するバリア性を有する膜として、例えば、絶縁体510、および絶縁体514には、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどの金属酸化物を用いることが好ましい。

【0147】

特に、酸化アルミニウムは、酸素、およびトランジスタの電気特性の変動要因となる水素、水分などの不純物、の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウムは、トランジスタの作製工程中および作製後において、水素、水分などの不純物のトランジスタ500への混入を防止することができる。また、トランジスタ500を構成する酸化物からの酸素の放出を抑制することができる。そのため、トランジスタ

50

500に対する保護膜として用いることに適している。

【0148】

また、例えば、絶縁体512、および絶縁体516には、絶縁体320と同様の材料を用いることができる。また、比較的誘電率が低い材料を層間膜として、配線間に生じる寄生容量を低減することができる。例えば、絶縁体512、および絶縁体516として、酸化シリコン膜や酸化窒化シリコン膜などを用いることができる。

【0149】

また、絶縁体510、絶縁体512、絶縁体514、および絶縁体516には、導電体518、およびトランジスタ500を構成する導電体(導電体503)等が埋め込まれている。なお、導電体518は、容量素子600、またはトランジスタ300と接続するプラグ、または配線としての機能を有する。導電体518は、導電体328、および導電体330と同様の材料を用いて設けることができる。

10

【0150】

特に、絶縁体510、および絶縁体514と接する領域の導電体518は、酸素、水素、および水に対するバリア性を有する導電体であることが好ましい。当該構成により、トランジスタ300とトランジスタ500とは、酸素、水素、および水に対するバリア性を有する層で、分離することができ、トランジスタ300からトランジスタ500への水素の拡散を抑制することができる。

【0151】

絶縁体516の上方には、トランジスタ500が設けられている。

20

【0152】

図7A、図7Bに示すように、トランジスタ500は、絶縁体514および絶縁体516に埋め込まれるように配置された導電体503と、絶縁体516と導電体503の上に配置された絶縁体520と、絶縁体520の上に配置された絶縁体522と、絶縁体522の上に配置された絶縁体524と、絶縁体524の上に配置された酸化物530aと、酸化物530aの上に配置された酸化物530bと、酸化物530b上に、互いに離して配置された導電体542a、および導電体542bと、導電体542aおよび導電体542b上に配置され、導電体542aと導電体542bの間に重畠して開口が形成された絶縁体580と、開口の中に配置された導電体560と、酸化物530b、導電体542a、導電体542b、および絶縁体580と、導電体560と、の間に配置された絶縁体550と、酸化物530b、導電体542a、導電体542b、および絶縁体580と、絶縁体550と、の間に配置された酸化物530cと、を有する。

30

【0153】

また、図7A、図7Bに示すように、酸化物530a、酸化物530b、導電体542a、および導電体542bと、絶縁体580の間に絶縁体544が配置されることが好ましい。また、図7A、図7Bに示すように、導電体560は、絶縁体550の内側に設けられた導電体560aと、導電体560aの内側に埋め込まれるように設けられた導電体560bと、を有することが好ましい。また、図7A、図7Bに示すように、絶縁体580、導電体560、および絶縁体550の上に絶縁体574が配置されることが好ましい。

40

【0154】

なお、以下において、酸化物530a、酸化物530b、および酸化物530cをまとめて酸化物530という場合がある。また、導電体542aおよび導電体542bをまとめて導電体542という場合がある。

【0155】

なお、トランジスタ500では、チャネルが形成される領域と、その近傍において、酸化物530a、酸化物530b、および酸化物530cの3層を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、酸化物530bの単層、酸化物530bと酸化物530aの2層構造、酸化物530bと酸化物530cの2層構造、または4層以上の積層構造を設ける構成にしてもよい。また、トランジスタ500では、導電体560を2層の積層構造として示しているが、本発明はこれに限られるものではな

50

い。例えば、導電体 560 が、単層構造であってもよいし、3層以上の積層構造であってもよい。また、図6、図7A、図7Bに示すトランジスタ500は一例であり、その構造に限定されず、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

#### 【0156】

ここで、導電体560は、トランジスタのゲート電極として機能し、導電体542aおよび導電体542bは、それぞれソース電極またはドレイン電極として機能する。上記のように、導電体560は、絶縁体580の開口、および導電体542aと導電体542bに挟まれた領域に埋め込まれるように形成される。導電体560、導電体542aおよび導電体542bの配置は、絶縁体580の開口に対して、自己整合的に選択される。つまり、トランジスタ500において、ゲート電極を、ソース電極とドレイン電極の間に、自己整合的に配置させることができる。よって、導電体560を位置合わせのマージンを設けることなく形成することができるので、トランジスタ500の占有面積の縮小を図ることができる。これにより、半導体装置の微細化、高集積化を図ることができる。

#### 【0157】

さらに、導電体560が、導電体542aと導電体542bの間の領域に自己整合的に形成されるので、導電体560は、導電体542aまたは導電体542bと重畳する領域を有さない。これにより、導電体560と導電体542aおよび導電体542bとの間に形成される寄生容量を低減することができる。よって、トランジスタ500のスイッチング速度を向上させ、高い周波数特性を有せしめることができる。

#### 【0158】

導電体560は、第1のゲート電極として機能する場合がある。また、導電体503は、第2のゲート電極として機能する場合がある。その場合、導電体503に印加する電位を、導電体560に印加する電位と連動させず、独立して変化させることで、トランジスタ500のV<sub>th</sub>を制御することができる。特に、導電体503に負の電位を印加することにより、トランジスタ500のV<sub>th</sub>を0Vより大きくし、オフ電流を低減することができる。したがって、導電体503に負の電位を印加したほうが、印加しない場合よりも、導電体560に印加する電位が0Vのときのドレイン電流を小さくすることができる。

#### 【0159】

導電体503は、酸化物530、および導電体560と、重なるように配置する。これにより、導電体560、および導電体503に電位を印加した場合、導電体560から生じる電界と、導電体503から生じる電界と、がつながり、酸化物530に形成されるチャネル形成領域を覆うことができる。本明細書等において、第1のゲート電極、および第2のゲート電極の電界によって、チャネル形成領域を電気的に取り囲むトランジスタの構造を、surrounded channel (S-channel) 構造とよぶ。

#### 【0160】

また、本明細書等において、S-channel 構造は、ソース電極およびドレイン電極として機能する導電体542aおよび導電体542bに接する酸化物530の側面及び周辺が、チャネル形成領域と同じくI型であるといった特徴を有する。また、導電体542aおよび導電体542bに接する酸化物530の側面及び周辺は、絶縁体544と接しているため、チャネル形成領域と同様にI型となりうる。なお、本明細書等において、I型とは後述する、高純度真性と同様として扱うことができる。また、本明細書等で開示するS-channel 構造は、Fin型構造及びプレーナ型構造とは異なる。S-channel 構造を採用することで、短チャネル効果に対する耐性を高める、別言すると短チャネル効果が発生し難いトランジスタとすることができます。

#### 【0161】

また、導電体503は、導電体518と同様の構成であり、絶縁体514および絶縁体516の開口の内壁に接して導電体503aが形成され、さらに内側に導電体503bが形成されている。

#### 【0162】

絶縁体520、絶縁体522、絶縁体524、および絶縁体550は、ゲート絶縁膜とし

10

20

30

40

50

ての機能を有する。

【0163】

ここで、酸化物530と接する絶縁体524は、化学量論的組成を満たす酸素よりも多くの酸素を含む絶縁体を用いることが好ましい。つまり、絶縁体524には、過剰酸素領域が形成されていることが好ましい。このような過剰酸素を含む絶縁体を酸化物530に接して設けることにより、酸化物530中の酸素欠損を低減し、トランジスタ500の信頼性を向上させることができる。

【0164】

過剰酸素領域を有する絶縁体として、具体的には、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。加熱により酸素を脱離する酸化物とは、TDS (Thermal Desorption Spectroscopy) 分析にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18}$  atoms/cm<sup>3</sup> 以上、好ましくは  $1.0 \times 10^{19}$  atoms/cm<sup>3</sup> 以上、さらに好ましくは  $2.0 \times 10^{19}$  atoms/cm<sup>3</sup> 以上、または  $3.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以上である酸化物膜である。なお、上記TDS分析時における膜の表面温度としては 100 以上 700 以下、または 100 以上 400 以下の範囲が好ましい。

10

【0165】

また、絶縁体524が、過剰酸素領域を有する場合、絶縁体522は、酸素(例えば、酸素原子、酸素分子など)の拡散を抑制する機能を有する(上記酸素が透過しにくい)ことが好ましい。

20

【0166】

絶縁体522が、酸素や不純物の拡散を抑制する機能を有することで、酸化物530が有する酸素は、絶縁体520側へ拡散することがなく、好ましい。また、導電体503が、絶縁体524や、酸化物530が有する酸素と反応することを抑制することができる。

【0167】

絶縁体522は、例えば、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニウム、チタン酸ジルコン酸鉛(PZT)、チタン酸ストロンチウム(SrTiO<sub>3</sub>)または(Ba, Sr)TiO<sub>3</sub>(BST)などのいわゆるhig h-k材料を含む絶縁体を単層または積層で用いることが好ましい。トランジスタの微細化、および高集積化が進むと、ゲート絶縁膜の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁膜として機能する絶縁体にhig h-k材料を用いることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。

30

【0168】

特に、不純物、および酸素などの拡散を抑制する機能を有する(上記酸素が透過しにくい)絶縁性材料であるアルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体を用いるとよい。アルミニウムおよびハフニウムの一方または双方の酸化物を含む絶縁体として、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物(ハフニウムアルミネート)などを用いることが好ましい。このような材料を用いて絶縁体522を形成した場合、絶縁体522は、酸化物530からの酸素の放出や、トランジスタ500の周辺部から酸化物530への水素等の不純物の混入を抑制する層として機能する。

40

【0169】

または、これらの絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タンゲステン、酸化イットリウム、酸化ジルコニウムを添加してもよい。またはこれらの絶縁体を窒化処理してもよい。上記の絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

【0170】

また、絶縁体520は、熱的に安定していることが好ましい。例えば、酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、好適である。また、hig h-k材料の絶縁体を酸化シリコン、または酸化窒化シリコンと組み合わせることで、熱的に安定かつ

50

比誘電率の高い積層構造の絶縁体 520 を得ることができる。

【0171】

なお、絶縁体 520、絶縁体 522、および絶縁体 524 が、2 層以上の積層構造を有していてもよい。その場合、同じ材料からなる積層構造に限定されず、異なる材料からなる積層構造でもよい。

【0172】

トランジスタ 500 は、チャネル形成領域を含む酸化物 530 に、酸化物半導体として機能する金属酸化物を用いることが好ましい。例えば、酸化物 530 として、In-M-Z<sub>n</sub>酸化物（元素 M は、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種）等の金属酸化物を用いるとよい。また、酸化物 530 として、In-Ga 酸化物、In-Zn 酸化物を用いてもよい。

10

【0173】

なお、酸化物半導体として機能する金属酸化物の形成は、スパッタリング法で行なってもよいし、ALD (A t o m i c L a y e r D e p o s i t i o n) 法で行なってもよい。酸化物半導体として機能する金属酸化物については、他の実施の形態で説明する。

【0174】

また、トランジスタ 500 には、キャリア密度の低い金属酸化物を用いることが好ましい。金属酸化物のキャリア密度を低くする場合においては、金属酸化物中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性または実質的に高純度真性という。なお、金属酸化物中の不純物としては、例えば、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

20

【0175】

特に、金属酸化物に含まれる水素は、金属原子と結合する酸素と反応して水になるため、金属酸化物中に酸素欠損を形成する場合がある。金属酸化物中のチャネル形成領域に酸素欠損が含まれていると、トランジスタはノーマリーオン特性となる場合がある。さらに、酸素欠損に水素が入った欠陥はドナーとして機能し、キャリアである電子が生成されることがある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成する場合がある。従って、水素が多く含まれている金属酸化物を用いたトランジスタは、ノーマリーオン特性となりやすい。

30

【0176】

酸素欠損に水素が入った欠陥は、金属酸化物のドナーとして機能しうる。しかしながら、当該欠陥を定量的に評価することは困難である。そこで、金属酸化物においては、ドナー濃度ではなく、キャリア密度で評価される場合がある。よって、本明細書等では、金属酸化物のパラメータとして、ドナー濃度ではなく、電界が印加されない状態を想定したキャリア密度を用いる場合がある。つまり、本明細書等に記載の「キャリア密度」は、「ドナー濃度」と言い換えることができる場合がある。

30

【0177】

よって、金属酸化物を酸化物 530 に用いる場合、金属酸化物中の水素はできる限り低減されていることが好ましい。具体的には、金属酸化物において、二次イオン質量分析法 (S I M S : S e c o n d a r y I o n M a s s S p e c t r o m e t r y) により得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup> 未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup> 未満、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup> 未満とする。水素などの不純物が十分に低減された金属酸化物をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

40

【0178】

また、酸化物 530 に金属酸化物を用いる場合、チャネル形成領域の金属酸化物のキャリ

50

ア密度は、 $1 \times 10^{18} \text{ cm}^{-3}$  以下であることが好ましく、 $1 \times 10^{17} \text{ cm}^{-3}$  未満であることがより好ましく、 $1 \times 10^{16} \text{ cm}^{-3}$  未満であることがさらに好ましく、 $1 \times 10^{13} \text{ cm}^{-3}$  未満であることがさらに好ましく、 $1 \times 10^{12} \text{ cm}^{-3}$  未満であることがさらに好ましい。なお、チャネル形成領域の金属酸化物のキャリア密度の下限値については、特に限定は無いが、例えば、 $1 \times 10^{-9} \text{ cm}^{-3}$  とすることができます。

#### 【0179】

また、酸化物 530 に金属酸化物を用いる場合、導電体 542（導電体 542a、および導電体 542b）と酸化物 530 とが接することで、酸化物 530 中の酸素が導電体 542 へ拡散し、導電体 542 が酸化する場合がある。導電体 542 が酸化することで、導電体 542 の導電率が低下する蓋然性が高い。なお、酸化物 530 中の酸素が導電体 542 へ拡散することを、導電体 542 が酸化物 530 中の酸素を吸収する、と言い換えることができる。

10

#### 【0180】

また、酸化物 530 中の酸素が導電体 542（導電体 542a、および導電体 542b）へ拡散することで、導電体 542a と酸化物 530b との間、および、導電体 542b と酸化物 530b との間に異層が形成される場合がある。当該異層は、導電体 542 よりも酸素を多く含むため、当該異層は絶縁性を有すると推定される。このとき、導電体 542 と、当該異層と、酸化物 530b との 3 層構造は、金属 - 絶縁体 - 半導体からなる 3 層構造とみなすことができ、MIS（Metal - Insulator - Semiconductor）構造、または MIS 構造を主としたダイオード接合構造と呼ぶ場合がある。

20

#### 【0181】

なお、上記異層は、導電体 542 と酸化物 530b との間に形成されることに限られず、例えば、異層が、導電体 542 と酸化物 530c との間に形成される場合や、導電体 542 と酸化物 530b との間、および導電体 542 と酸化物 530c との間に形成される場合がある。

#### 【0182】

また、酸化物 530 においてチャネル形成領域として機能する金属酸化物は、バンドギャップが 2 eV 以上、好ましくは 2.5 eV 以上のものを用いることが好ましい。このように、バンドギャップの大きい金属酸化物を用いることで、トランジスタのオフ電流を低減することができる。

30

#### 【0183】

その他、酸化物 530 に用いることができる半導体材料は、上述の金属酸化物に限られない。酸化物 530 として、バンドギャップを有する半導体材料（ゼロギャップ半導体ではない半導体材料）を用いてもよい。例えば、シリコンなどの単体元素の半導体、ヒ化ガリウムなどの化合物半導体、半導体として機能する層状物質（原子層物質、2 次元材料などともいう）などを半導体材料に用いることが好ましい。特に、半導体として機能する層状物質を半導体材料に用いると好適である。

#### 【0184】

ここで、本明細書等において、層状物質とは、層状の結晶構造を有する材料群の総称である。層状の結晶構造は、共有結合やイオン結合によって形成される層が、ファンデルワールス力のような、共有結合やイオン結合よりも弱い結合を介して積層している構造である。層状物質は、単位層内における電気伝導性が高く、つまり、2 次元電気伝導性が高い。半導体として機能し、かつ、2 次元電気伝導性の高い材料をチャネル形成領域に用いることで、オフ電流の大きいトランジスタを提供することができる。

40

#### 【0185】

層状物質として、グラフェン、シリセン、カルコゲン化物などがある。カルコゲン化物は、カルコゲンを含む化合物である。また、カルコゲンは、第 16 族に属する元素の総称であり、酸素、硫黄、セレン、テルル、ポロニウム、リバモリウムが含まれる。また、カルコゲン化物として、遷移金属カルコゲナイト、13 族カルコゲナイトなどが挙げられる。

#### 【0186】

50

酸化物 530 として、例えば、半導体として機能する遷移金属カルコゲナイトを用いることが好ましい。酸化物 530 として適用可能な遷移金属カルコゲナイトとして、具体的には、硫化モリブデン（代表的には  $\text{MoS}_2$ ）、セレン化モリブデン（代表的には  $\text{MoSe}_2$ ）、モリブデンテルル（代表的には  $\text{MoTe}_2$ ）、硫化タンゲステン（代表的には  $\text{WS}_2$ ）、セレン化タンゲステン（代表的には  $\text{WSe}_2$ ）、タンゲステンテルル（代表的には  $\text{WTc}_2$ ）、硫化ハフニウム（代表的には  $\text{HfS}_2$ ）、セレン化ハフニウム（代表的には  $\text{HfSe}_2$ ）、硫化ジルコニウム（代表的には  $\text{ZrS}_2$ ）、セレン化ジルコニウム（代表的には  $\text{ZrSe}_2$ ）などが挙げられる。

#### 【0187】

酸化物 530 は、酸化物 530b 下に酸化物 530a を有することで、酸化物 530a よりも下方に形成された構造物から、酸化物 530b への不純物の拡散を抑制することができる。また、酸化物 530b 上に酸化物 530c を有することで、酸化物 530c よりも上方に形成された構造物から、酸化物 530b への不純物の拡散を抑制することができる。

10

#### 【0188】

なお、酸化物 530 は、各金属原子の原子数比が異なる複数の酸化物層の積層構造を有することが好ましい。具体的には、酸化物 530a に用いる金属酸化物において、構成元素中の元素 M の原子数比が、酸化物 530b に用いる金属酸化物における、構成元素中の元素 M の原子数比より、大きいことが好ましい。また、酸化物 530a に用いる金属酸化物において、In に対する元素 M の原子数比が、酸化物 530b に用いる金属酸化物における、In に対する元素 M の原子数比より大きいことが好ましい。また、酸化物 530b に用いる金属酸化物において、元素 M に対する In の原子数比が、酸化物 530a に用いる金属酸化物における、元素 M に対する In の原子数比より大きいことが好ましい。また、酸化物 530c は、酸化物 530a または酸化物 530b に用いることができる金属酸化物を、用いることができる。

20

#### 【0189】

また、酸化物 530a および酸化物 530c の伝導帯下端のエネルギーが、酸化物 530b の伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物 530a および酸化物 530c の電子親和力が、酸化物 530b の電子親和力より小さいことが好ましい。

30

#### 【0190】

ここで、酸化物 530a、酸化物 530b、および酸化物 530c の接合部において、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、酸化物 530a、酸化物 530b、および酸化物 530c の接合部における伝導帯下端のエネルギー準位は、連続的に変化または連続接合するともいうことができる。このようにするために、酸化物 530a と酸化物 530b との界面、および酸化物 530b と酸化物 530c との界面において形成される混合層の欠陥準位密度を低くするとよい。

#### 【0191】

具体的には、酸化物 530a と酸化物 530b、酸化物 530b と酸化物 530c が、酸素以外に共通の元素を有する（主成分とする）ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物 530b が In - Ga - Zn 酸化物の場合、酸化物 530a および酸化物 530c として、In - Ga - Zn 酸化物、Ga - Zn 酸化物、酸化ガリウムなどを用いるとよい。

40

#### 【0192】

このとき、キャリアの主たる経路は酸化物 530b となる。酸化物 530a、酸化物 530c を上述の構成とすることで、酸化物 530a と酸化物 530b との界面、および酸化物 530b と酸化物 530c との界面における欠陥準位密度を低くすることができる。そのため、界面散乱によるキャリア伝導への影響が小さくなり、トランジスタ 500 は高いオン電流を得られる。

#### 【0193】

酸化物 530b 上には、ソース電極、およびドレイン電極として機能する導電体 542（

50

導電体 542a、および導電体 542b) が設けられる。導電体 542 としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウム、ルテニウム、イリジウム、ストロンチウム、ランタンから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いることが好ましい。例えば、窒化タンタル、窒化チタン、タングステン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物などを用いることが好ましい。また、窒化タンタル、窒化チタン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物は、酸化しにくい導電性材料、または、酸素を吸収しても導電性を維持する材料であるため、好ましい。

#### 【0194】

また、図 7A に示すように、酸化物 530 の、導電体 542 との界面とその近傍には、低抵抗領域として、領域 543 (領域 543a、および領域 543b) が形成される場合がある。このとき、領域 543a はソース領域またはドレイン領域の一方として機能し、領域 543b はソース領域またはドレイン領域の他方として機能する。また、領域 543a と領域 543b に挟まれる領域にチャネル形成領域が形成される。

#### 【0195】

酸化物 530 と接するように上記導電体 542 を設けることで、領域 543 の酸素濃度が低減する場合がある。また、領域 543 に導電体 542 に含まれる金属と、酸化物 530 の成分とを含む金属化合物層が形成される場合がある。このような場合、領域 543 のキャリア密度が増加し、領域 543 は、低抵抗領域となる。

#### 【0196】

絶縁体 544 は、導電体 542 を覆うように設けられ、導電体 542 の酸化を抑制する。このとき、絶縁体 544 は、酸化物 530 の側面を覆い、絶縁体 524 と接するように設けられてもよい。

#### 【0197】

絶縁体 544 として、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タングステン、チタン、タンタル、ニッケル、ゲルマニウム、または、マグネシウムなどから選ばれた一種、または二種以上が含まれた金属酸化物を用いることができる。

#### 【0198】

特に、絶縁体 544 として、アルミニウム、またはハフニウムの一方または双方の酸化物を含む絶縁体である、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物 (ハフニウムアルミネート) などを用いることが好ましい。特に、ハフニウムアルミネートは、酸化ハフニウム膜よりも、耐熱性が高い。そのため、後の工程での熱処理において、結晶化しにくいため好ましい。なお、導電体 542 が耐酸化性を有する材料、または、酸素を吸収しても著しく導電性が低下しない場合、絶縁体 544 は、必須の構成ではない。求めるトランジスタ特性により、適宜設計すればよい。

#### 【0199】

絶縁体 550 は、ゲート絶縁膜として機能する。絶縁体 550 は、酸化物 530c の内側 (上面および側面) に接して配置することが好ましい。絶縁体 550 は、加熱により酸素が放出される絶縁体を用いて形成することが好ましい。例えば、TDS 分析にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18} \text{ atoms/cm}^3$  以上、好ましくは  $1.0 \times 10^{19} \text{ atoms/cm}^3$  以上、さらに好ましくは  $2.0 \times 10^{19} \text{ atoms/cm}^3$  以上、または  $3.0 \times 10^{20} \text{ atoms/cm}^3$  以上である酸化物膜である。なお、上記 TDS 分析時における膜の表面温度としては 100 以上 700 以下の範囲が好ましい。

#### 【0200】

10

20

30

40

50

具体的には、過剰酸素を有する酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコンを用いることができる。特に、酸化シリコン、および酸化窒化シリコンは熱に対し安定であるため好ましい。

【0201】

加熱により酸素が放出される絶縁体を、絶縁体550として、酸化物530cの上面に接して設けることにより、絶縁体550から、酸化物530cを通じて、酸化物530bのチャネル形成領域に効果的に酸素を供給することができる。また、絶縁体524と同様に、絶縁体550中の水または水素などの不純物濃度が低減されていることが好ましい。絶縁体550の膜厚は、1nm以上20nm以下とするのが好ましい。

10

【0202】

また、絶縁体550が有する過剰酸素を、効率的に酸化物530へ供給するために、絶縁体550と導電体560との間に金属酸化物を設けてもよい。当該金属酸化物は、絶縁体550から導電体560への酸素拡散を抑制することが好ましい。酸素の拡散を抑制する金属酸化物を設けることで、絶縁体550から導電体560への過剰酸素の拡散が抑制される。つまり、酸化物530へ供給する過剰酸素量の減少を抑制することができる。また、過剰酸素による導電体560の酸化を抑制することができる。当該金属酸化物としては、絶縁体544に用いることができる材料を用いればよい。

【0203】

第1のゲート電極として機能する導電体560は、図7A、図7Bでは2層構造として示しているが、単層構造でもよいし、3層以上の積層構造であってもよい。

20

【0204】

導電体560aは、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子( $N_2O$ 、 $NO$ 、 $NO_2$ など)、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素(例えば、酸素原子、酸素分子などの少なくとも一つ)の拡散を抑制する機能を有する導電性材料を用いることが好ましい。導電体560aが酸素の拡散を抑制する機能を持つことにより、絶縁体550に含まれる酸素により、導電体560bが酸化して導電率が低下することを抑制することができる。酸素の拡散を抑制する機能を有する導電性材料としては、例えば、タンタル、窒化タンタル、ルテニウム、または酸化ルテニウムなどを用いることが好ましい。

30

【0205】

また、導電体560bは、タンゲステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体560bは、配線としても機能するため、導電性が高い導電体を用いることが好ましい。例えば、タンゲステン、銅、またはアルミニウムを主成分とする導電性材料を用いることができる。また、導電体560bは積層構造としてもよく、例えば、チタン又は窒化チタンと上記導電性材料との積層構造としてもよい。

【0206】

絶縁体580は、絶縁体544を介して、導電体542上に設けられる。絶縁体580は、過剰酸素領域を有することが好ましい。例えば、絶縁体580として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコン、または樹脂などを有することが好ましい。特に、酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため好ましい。特に、酸化シリコン、空孔を有する酸化シリコンは、後の工程で、容易に過剰酸素領域を形成するため好ましい。

40

【0207】

また、加熱により酸素が放出される絶縁体580を、酸化物530cと接して設けることで、絶縁体580中の酸素を、酸化物530cを通じて、酸化物530へと効率良く供給することができる。なお、絶縁体580中の水または水素などの不純物濃度が低減されていることが好ましい。

50

## 【0208】

絶縁体580の開口は、導電体542aと導電体542bの間の領域に重畠して形成される。これにより、導電体560は、絶縁体580の開口、および導電体542aと導電体542bに挟まれた領域に、埋め込まれるように形成される。

## 【0209】

半導体装置を微細化するに当たり、ゲート長を短くすることが求められるが、導電体560の導電性が下がらないようにする必要がある。そのために導電体560の膜厚を大きくすると、導電体560はアスペクト比が高い形状となりうる。本実施の形態では、導電体560を絶縁体580の開口に埋め込むように設けるため、導電体560をアスペクト比の高い形状にしても、工程中に導電体560を倒壊させることなく、形成することができる。

10

## 【0210】

絶縁体574は、絶縁体580の上面、導電体560の上面、および絶縁体550の上面に接して設けられることが好ましい。絶縁体574をスパッタリング法で成膜することで、絶縁体550および絶縁体580へ過剰酸素領域を設けることができる。これにより、当該過剰酸素領域から、酸化物530中に酸素を供給することができる。

## 【0211】

例えば、絶縁体574として、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タンクスチン、チタン、タンタル、ニッケル、ゲルマニウム、またはマグネシウムなどから選ばれた一種、または二種以上が含まれた金属酸化物を用いることができる。

20

## 【0212】

特に、酸化アルミニウムはバリア性が高く、0.5nm以上3.0nm以下の薄膜であっても、水素、および窒素の拡散を抑制することができる。したがって、スパッタリング法で成膜した酸化アルミニウムは、酸素供給源であるとともに、水素などの不純物のバリア膜としての機能も有することができる。

## 【0213】

また、絶縁体574の上に、層間膜として機能する絶縁体581を設けることが好ましい。絶縁体581は、絶縁体524などと同様に、膜中の水または水素などの不純物濃度が低減されていることが好ましい。

30

## 【0214】

また、絶縁体581、絶縁体574、絶縁体580、および絶縁体544に形成された開口に、導電体540aおよび導電体540bを配置する。導電体540aおよび導電体540bは、導電体560を挟んで対向して設ける。導電体540aおよび導電体540bは、後述する導電体546および導電体548と同様の構成である。

## 【0215】

絶縁体581上には、絶縁体582が設けられている。絶縁体582は、酸素や水素に対してバリア性のある物質を用いることが好ましい。したがって、絶縁体582には、絶縁体514と同様の材料を用いることができる。例えば、絶縁体582には、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどの金属酸化物を用いることが好ましい。

40

## 【0216】

特に、酸化アルミニウムは、酸素、およびトランジスタの電気特性の変動要因となる水素、水分などの不純物、の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウムは、トランジスタの作製工程中および作製後において、水素、水分などの不純物のトランジスタ500への混入を防止することができる。また、トランジスタ500を構成する酸化物からの酸素の放出を抑制することができる。そのため、トランジスタ500に対する保護膜として用いることに適している。

## 【0217】

また、絶縁体582上には、絶縁体586が設けられている。絶縁体586は、絶縁体320と同様の材料を用いることができる。また、比較的誘電率が低い材料を層間膜とする

50

ことで、配線間に生じる寄生容量を低減することができる。例えば、絶縁体 586 として、酸化シリコン膜や酸化窒化シリコン膜などを用いることができる。

【0218】

また、絶縁体 520、絶縁体 522、絶縁体 524、絶縁体 544、絶縁体 580、絶縁体 574、絶縁体 581、絶縁体 582、および絶縁体 586 には、導電体 546、および導電体 548 等が埋め込まれている。

【0219】

導電体 546、および導電体 548 は、容量素子 600、トランジスタ 500、またはトランジスタ 300 と接続するプラグ、または配線としての機能を有する。導電体 546、および導電体 548 は、導電体 328、および導電体 330 と同様の材料を用いて設けることができる。

10

【0220】

続いて、トランジスタ 500 の上方には、容量素子 600 が設けられている。容量素子 600 は、導電体 610 と、導電体 620、絶縁体 630 とを有する。

【0221】

また、導電体 546、および導電体 548 上に、導電体 612 を設けてもよい。導電体 612 は、トランジスタ 500 と接続するプラグ、または配線としての機能を有する。導電体 610 は、容量素子 600 の電極としての機能を有する。なお、導電体 612、および導電体 610 は、同時に形成することができる。

20

【0222】

導電体 612、および導電体 610 には、モリブデン、チタン、タンタル、タンゲステン、アルミニウム、銅、クロム、ネオジム、スカンジウムから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜（窒化タンタル膜、窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）等を用いることができる。または、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。

【0223】

図 6 では、導電体 612、および導電体 610 は単層構造として示しているが、当該構成に限定されず、2 層以上の積層構造でもよい。例えば、バリア性を有する導電体と導電性が高い導電体との間に、バリア性を有する導電体、および導電性が高い導電体に対して密着性が高い導電体を形成してもよい。

30

【0224】

絶縁体 630 を介して、導電体 610 と重畳するように、導電体 620 を設ける。なお、導電体 620 は、金属材料、合金材料、または金属酸化物材料などの導電性材料を用いることができる。耐熱性と導電性を両立するタンゲステンやモリブデンなどの高融点材料を用いることが好ましく、特にタンゲステンを用いることが好ましい。また、導電体などの他の構造と同時に形成する場合は、低抵抗金属材料である Cu (銅) や Al (アルミニウム) 等を用いればよい。

40

【0225】

導電体 620、および絶縁体 630 上には、絶縁体 650 が設けられている。絶縁体 650 は、絶縁体 320 と同様の材料を用いて設けることができる。また、絶縁体 650 は、その下方の凹凸形状を被覆する平坦化膜として機能してもよい。

【0226】

本構造を用いることで、酸化物半導体を有するトランジスタを用いた半導体装置において、電気特性の変動を抑制するとともに、信頼性を向上させることができる。または、オン電流が大きい酸化物半導体を有するトランジスタを提供することができる。または、オフ電流が小さい酸化物半導体を有するトランジスタを提供することができる。または、消費電力が低減された半導体装置を提供することができる。または、酸化物半導体を有するト

50

ランジスタを用いた半導体装置において、微細化または高集積化を図ることができる。

【0227】

<トランジスタの構造例>

なお、本実施の形態に示す半導体装置のトランジスタ500は、上記の構造に限られるものではない。以下、トランジスタ500に用いることができる構造例について説明する。

【0228】

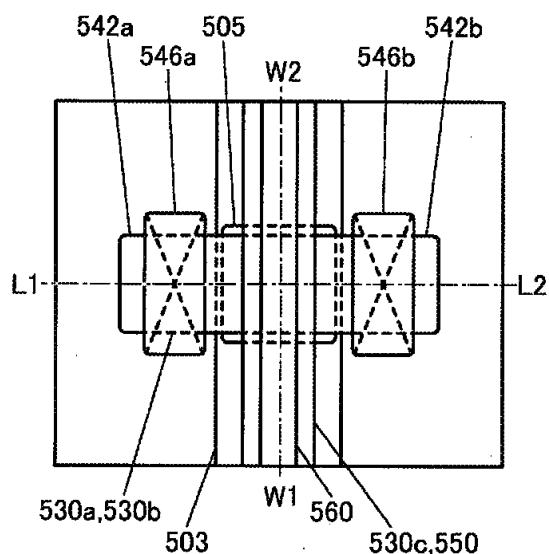

<トランジスタの構造例1>

図8A、図8Bおよび図8Cを用いてトランジスタ510Aの構造例を説明する。図8Aはトランジスタ510Aの上面図である。図8Bは、図8Aに一点鎖線L1-L2で示す部位の断面図である。図8Cは、図8Aに一点鎖線W1-W2で示す部位の断面図である。なお、図8Aの上面図では、図の明瞭化のために一部の要素を省いている。

10

【0229】

図8A、図8Bおよび図8Cでは、トランジスタ510Aと、層間膜として機能する絶縁体511、絶縁体512、絶縁体514、絶縁体516、絶縁体580、絶縁体582、および絶縁体584を示している。また、トランジスタ510Aと電気的に接続し、コンタクトプラグとして機能する導電体546（導電体546a、および導電体546b）と、配線として機能する導電体503と、を示している。

【0230】

トランジスタ510Aは、第1のゲート電極として機能する導電体560（導電体560a、および導電体560b）と、第2のゲート電極として機能する導電体505（導電体505a、および導電体505b）と、第1のゲート絶縁膜として機能する絶縁体550と、第2のゲート絶縁膜として機能する絶縁体521、絶縁体522、および絶縁体524と、チャネルが形成される領域を有する酸化物530（酸化物530a、酸化物530b、および酸化物530c）と、ソースまたはドレインの一方として機能する導電体542aと、ソースまたはドレインの他方として機能する導電体542bと、絶縁体574とを有する。

20

【0231】

また、図8に示すトランジスタ510Aでは、酸化物530c、絶縁体550、および導電体560が、絶縁体580に設けられた開口部内に、絶縁体574を介して配置される。また、酸化物530c、絶縁体550、および導電体560は、導電体542a、および導電体542bとの間に配置される。

30

【0232】

絶縁体511、および絶縁体512は、層間膜として機能する。

【0233】

層間膜としては、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタル、酸化ジルコニウム、チタン酸ジルコン酸鉛（PZT）、チタン酸ストロンチウム（SrTiO<sub>3</sub>）または（Ba, Sr）TiO<sub>3</sub>（BST）などの絶縁体を単層または積層で用いることができる。またはこれらの絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タンゲステン、酸化イットリウム、酸化ジルコニウムを添加してもよい。またはこれらの絶縁体を窒化処理してもよい。上記の絶縁体に酸化シリコン、酸化窒化シリコンまたは窒化シリコンを積層して用いてもよい。

40

【0234】

例えば、絶縁体511は、水または水素などの不純物が、基板側からトランジスタ510Aに混入するのを抑制するバリア膜として機能することが好ましい。したがって、絶縁体511は、水素原子、水素分子、水分子、銅原子などの不純物の拡散を抑制する機能を有する（上記不純物が透過しにくい）絶縁性材料を用いることが好ましい。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一つ）の拡散を抑制する機能を有する（上記酸素が透過しにくい）絶縁性材料を用いることが好ましい。また、例えば、絶縁体511として酸化アルミニウムや窒化シリコンなどを用いてもよい。当該構成により、水素、

50

水などの不純物が絶縁体 511 よりも基板側からトランジスタ 510A 側に拡散するのを抑制することができる。

【0235】

例えば、絶縁体 512 は、絶縁体 511 よりも誘電率が低いことが好ましい。誘電率が低い材料を層間膜としてすることで、配線間に生じる寄生容量を低減することができる。

【0236】

導電体 503 は、絶縁体 512 に埋め込まれるように形成される。ここで、導電体 503 の上面の高さと、絶縁体 512 の上面の高さは同程度にできる。なお導電体 503 は、単層とする構成について示しているが、本発明はこれに限られるものではない。例えば、導電体 503 を 2 層以上の多層膜構造としてもよい。なお、導電体 503 は、タンゲステン、銅、またはアルミニウムを主成分とする導電性が高い導電性材料を用いることが好ましい。

10

【0237】

トランジスタ 510A において、導電体 560 は、第 1 のゲート電極として機能する場合がある。また、導電体 505 は、第 2 のゲート電極として機能する場合がある。その場合、導電体 505 に印加する電位を、導電体 560 に印加する電位と連動させず、独立して変化させることで、トランジスタ 510A のしきい値電圧を制御することができる。特に、導電体 505 に負の電位を印加することにより、トランジスタ 510A のしきい値電圧を 0V より大きくし、オフ電流を低減することが可能となる。したがって、導電体 505 に負の電位を印加したほうが、印加しない場合よりも、導電体 560 に印加する電位が 0V のときのドレイン電流を小さくすることができる。

20

【0238】

また、例えば、導電体 505 と、導電体 560 とを重畠して設けることで、導電体 560 、および導電体 505 に電位を印加した場合、導電体 560 から生じる電界と、導電体 505 から生じる電界と、がつながり、酸化物 530 に形成されるチャネル形成領域を覆うことができる。

【0239】

つまり、第 1 のゲート電極としての機能を有する導電体 560 の電界と、第 2 のゲート電極としての機能を有する導電体 505 の電界によって、チャネル形成領域を電気的に取り囲むことができる。すなわち、先に記載のトランジスタ 500 と同様に、surrounded channel (S-channel) 構造である。

30

【0240】

絶縁体 514 、および絶縁体 516 は、絶縁体 511 または絶縁体 512 と同様に、層間膜として機能する。例えば、絶縁体 514 は、水または水素などの不純物が、基板側からトランジスタ 510A に混入するのを抑制するバリア膜として機能することができる。当該構成により、水素、水などの不純物が絶縁体 514 よりも基板側からトランジスタ 510A 側に拡散するのを抑制することができる。また、例えば、絶縁体 516 は、絶縁体 514 よりも誘電率が低いことが好ましい。誘電率が低い材料を層間膜としてすることで、配線間に生じる寄生容量を低減することができる。

【0241】

第 2 のゲートとして機能する導電体 505 は、絶縁体 514 および絶縁体 516 の開口の内壁に接して導電体 505a が形成され、さらに内側に導電体 505b が形成されている。ここで、導電体 505a および導電体 505b の上面の高さと、絶縁体 516 の上面の高さは同程度にできる。なお、トランジスタ 510A では、導電体 505a および導電体 505b を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、導電体 505 は、単層、または 3 層以上の積層構造として設ける構成にしてもよい。

40

【0242】

ここで、導電体 505a は、水素原子、水素分子、水分子、銅原子などの不純物の拡散を抑制する機能を有する（上記不純物が透過しにくい）導電性材料を用いることが好ましい

50

。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一つ）の拡散を抑制する機能を有する（上記酸素が透過しにくい）導電性材料を用いることが好ましい。なお、本明細書等において、不純物、または酸素の拡散を抑制する機能とは、上記不純物、または上記酸素のいずれか一つ、または、すべての拡散を抑制する機能とする。

【0243】

例えば、導電体505aが酸素の拡散を抑制する機能を持つことにより、導電体505bが酸化して導電率が低下することを抑制することができる。

【0244】

また、導電体505が配線の機能を兼ねる場合、導電体505bは、タングステン、銅、またはアルミニウムを主成分とする、導電性が高い導電性材料を用いることが好ましい。その場合、導電体503は、必ずしも設けなくともよい。なお、導電体505bを単層で図示したが、積層構造としてもよく、例えば、チタン又は窒化チタンと上記導電性材料との積層としてもよい。

10

【0245】

絶縁体521、絶縁体522、および絶縁体524は、第2のゲート絶縁膜としての機能を有する。

【0246】

また、絶縁体522は、バリア性を有することが好ましい。絶縁体522がバリア性を有することで、トランジスタ510Aの周辺部からトランジスタ510Aへの水素等の不純物の混入を抑制する層として機能する。

20

【0247】

絶縁体522は、例えば、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物（ハフニウムアルミネート）、酸化タンタル、酸化ジルコニウム、チタン酸ジルコン酸鉛（PZT）、チタン酸ストロンチウム（SrTiO<sub>3</sub>）または（Ba, Sr）TiO<sub>3</sub>（BST）などのいわゆるhigh-k材料を含む絶縁体を単層または積層で用いることが好ましい。トランジスタの微細化、および高集積化が進むと、ゲート絶縁膜の薄膜化により、リーク電流などの問題が生じる場合がある。ゲート絶縁膜として機能する絶縁体にhigh-k材料を用いることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。

30

【0248】

また、絶縁体521は、熱的に安定していることが好ましい。例えば、酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため、好適である。また、high-k材料の絶縁体を酸化シリコン、または酸化窒化シリコンと組み合わせることで、熱的に安定かつ比誘電率の高い積層構造の絶縁体521を得ることができる。

【0249】

なお、図8には、第2のゲート絶縁膜として、3層の積層構造を示したが、2層以下、または4層以上の積層構造としてもよい。その場合、同じ材料からなる積層構造に限定されず、異なる材料からなる積層構造でもよい。

【0250】

チャネル形成領域として機能する領域を有する酸化物530は、酸化物530aと、酸化物530a上の酸化物530bと、酸化物530b上の酸化物530cと、を有する。酸化物530b下に酸化物530aを有することで、酸化物530aよりも下方に形成された構造物から、酸化物530bへの不純物の拡散を抑制することができる。また、酸化物530b上に酸化物530cを有することで、酸化物530cよりも上方に形成された構造物から、酸化物530bへの不純物の拡散を抑制することができる。酸化物530として、上述した金属酸化物の一種である酸化物半導体を用いることができる。

40

【0251】

なお、酸化物530cは、絶縁体580に設けられた開口部内に、絶縁体574を介して設けられることが好ましい。絶縁体574がバリア性を有する場合、絶縁体580からの不純物が酸化物530へと拡散することを抑制することができる。

50

## 【0252】

導電体542は、一方がソース電極として機能し、他方がドレイン電極として機能する。

## 【0253】

導電体542aと、導電体542bとは、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタンゲステンなどの金属、またはこれを主成分とする合金を用いることができる。特に、窒化タンタルなどの金属窒化物膜は、水素または酸素に対するバリア性があり、また、耐酸化性が高いため、好ましい。

## 【0254】

また、図8では単層構造を示したが、2層以上の積層構造としてもよい。例えば、窒化タンタル膜とタンゲステン膜を積層するとよい。また、チタン膜とアルミニウム膜を積層してもよい。また、タンゲステン膜上にアルミニウム膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タンゲステン膜上に銅膜を積層する二層構造としてもよい。

10

## 【0255】

また、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

20

## 【0256】

また、導電体542上に、バリア層を設けてもよい。バリア層は、酸素、または水素に対してバリア性を有する物質を用いることが好ましい。当該構成により、絶縁体574を成膜する際に、導電体542が酸化することを抑制することができる。

## 【0257】

バリア層には、例えば、金属酸化物を用いることができる。特に、酸化アルミニウム、酸化ハフニウム、酸化ガリウムなどの、酸素や水素に対してバリア性のある絶縁膜を用いることが好ましい。また、CVD法で形成した窒化シリコンを用いてもよい。

30

## 【0258】

バリア層を有することで、導電体542の材料選択の幅を広げることができる。例えば、導電体542に、タンゲステンや、アルミニウムなどの耐酸化性が低い一方で導電性が高い材料を用いることができる。また、例えば、成膜、または加工がしやすい導電体を用いることができる。

## 【0259】

絶縁体550は、第1のゲート絶縁膜として機能する。絶縁体550は、絶縁体580に設けられた開口部内に、酸化物530c、および絶縁体574を介して設けられることが好ましい。

## 【0260】

トランジスタの微細化、および高集積化が進むと、ゲート絶縁膜の薄膜化により、リーコ電流などの問題が生じる場合がある。その場合、絶縁体550は、第2のゲート絶縁膜と同様に、積層構造としてもよい。ゲート絶縁膜として機能する絶縁体を、high-k材料と、熱的に安定している材料との積層構造とすることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。また、熱的に安定かつ比誘電率の高い積層構造とすることができる。

40

## 【0261】

第1のゲート電極として機能する導電体560は、導電体560a、および導電体560a上の導電体560bを有する。導電体560aは、導電体505aと同様に、水素原子、水素分子、水分子、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一つ

50

) の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

【 0 2 6 2 】

導電体 5 6 0 a が酸素の拡散を抑制する機能を持つことにより、導電体 5 6 0 b の材料選択性を向上することができる。つまり、導電体 5 6 0 a を有することで、導電体 5 6 0 b の酸化が抑制され、導電率が低下することを防止することができる。

【 0 2 6 3 】

酸素の拡散を抑制する機能を有する導電性材料としては、例えば、タンタル、窒化タンタル、ルテニウムまたは酸化ルテニウムなどを用いることが好ましい。また、導電体 5 6 0 a として、酸化物 5 3 0 として用いることができる酸化物半導体を用いることができる。その場合、導電体 5 6 0 b をスパッタリング法で成膜することで、導電体 5 6 0 a の電気抵抗値を低下させて導電体とすることができます。これを O C ( O x i d e C o n d u c t o r ) 電極と呼ぶことができる。

10

【 0 2 6 4 】

導電体 5 6 0 b は、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体 5 6 0 は、配線として機能するため、導電体 5 6 0 b に導電性が高い導電体を用いることが好ましい。例えば、タングステン、銅、またはアルミニウムを主成分とする導電性材料を用いることができる。また、導電体 5 6 0 b は積層構造としてもよく、例えば、チタン又は窒化チタンと上記導電性材料との積層としてもよい。

20

【 0 2 6 5 】

絶縁体 5 8 0 と、トランジスタ 5 1 0 A との間に絶縁体 5 7 4 を配置する。絶縁体 5 7 4 は、水または水素などの不純物、および酸素の拡散を抑制する機能を有する絶縁性材料を用いるとよい。例えば、酸化アルミニウムまたは酸化ハフニウムなどを用いることが好ましい。また、他にも、例えば、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコンまたは窒化シリコンなどを用いることができる。

30

【 0 2 6 6 】

絶縁体 5 7 4 を有することで、絶縁体 5 8 0 が有する水、および水素などの不純物が酸化物 5 3 0 c 、絶縁体 5 5 0 を介して、酸化物 5 3 0 b に拡散することを抑制することができる。また、絶縁体 5 8 0 が有する過剰酸素により、導電体 5 6 0 が酸化するのを抑制することができる。

30

【 0 2 6 7 】

絶縁体 5 8 0 、絶縁体 5 8 2 、および絶縁体 5 8 4 は、層間膜として機能する。

【 0 2 6 8 】

絶縁体 5 8 2 は、絶縁体 5 1 4 と同様に、水または水素などの不純物が、外部からトランジスタ 5 1 0 A に混入するのを抑制するバリア絶縁膜として機能することができる。

40

【 0 2 6 9 】

また、絶縁体 5 8 0 、および絶縁体 5 8 4 は、絶縁体 5 1 6 と同様に、絶縁体 5 8 2 よりも誘電率が低いことが好ましい。誘電率が低い材料を層間膜とすることで、配線間に生じる寄生容量を低減することができる。

【 0 2 7 0 】

また、トランジスタ 5 1 0 A は、絶縁体 5 8 0 、絶縁体 5 8 2 、および絶縁体 5 8 4 に埋め込まれた導電体 5 4 6 などのプラグや配線を介して、他の構造と電気的に接続してもよい。

40

【 0 2 7 1 】

また、導電体 5 4 6 の材料としては、導電体 5 0 5 と同様に、金属材料、合金材料、金属窒化物材料、または金属酸化物材料などの導電性材料を、単層または積層して用いることができる。例えば、耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましい。または、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。低抵抗導電性材料を用いることで配線抵抗を低くすることができる。

50

## 【0272】

例えば、導電体546として、水素、および酸素に対してバリア性を有する導電体である窒化タンタル等と、導電性が高いタンゲステンとの積層構造を用いることで、配線としての導電性を保持したまま、外部からの不純物の拡散を抑制することができる。

## 【0273】

上記構造を有することで、オン電流が大きい酸化物半導体を有するトランジスタを提供することができる。または、オフ電流が小さい酸化物半導体を有するトランジスタを提供することができる。または、酸化物半導体を有するトランジスタを用いた半導体装置において、電気特性の変動を抑制するとともに、信頼性を向上させることができる。

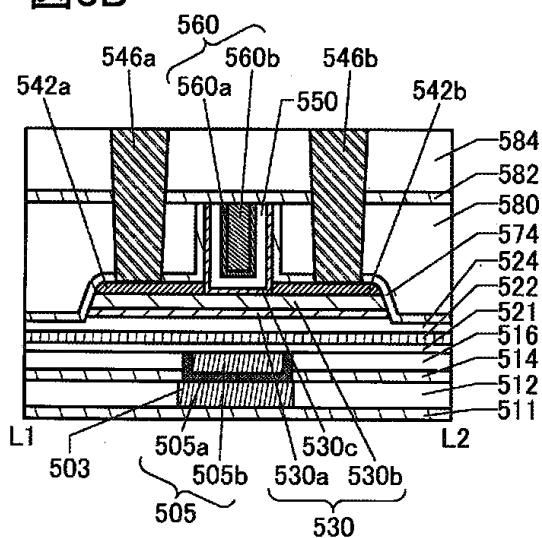

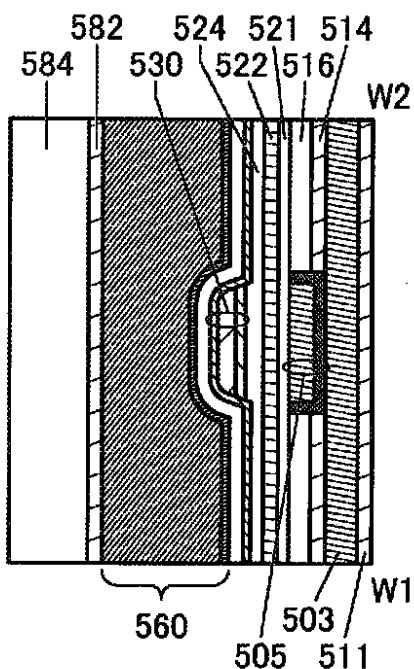

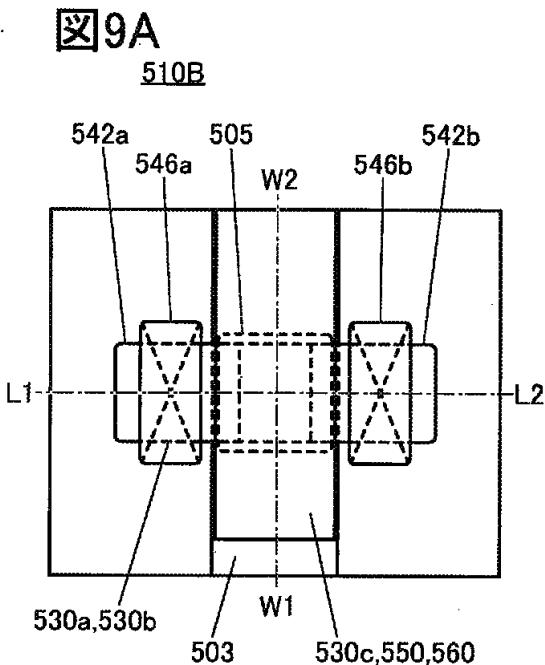

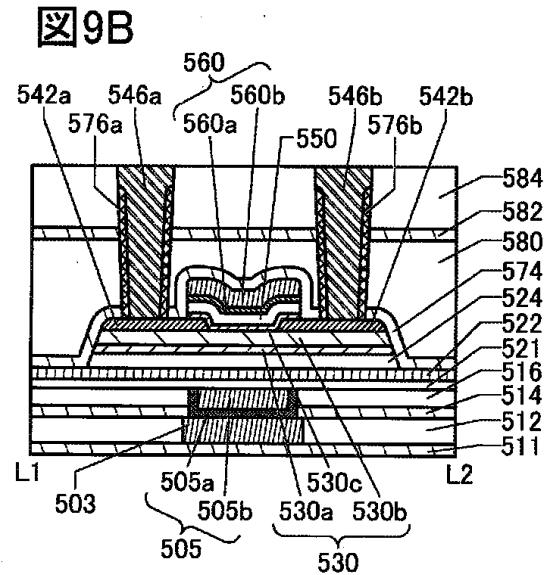

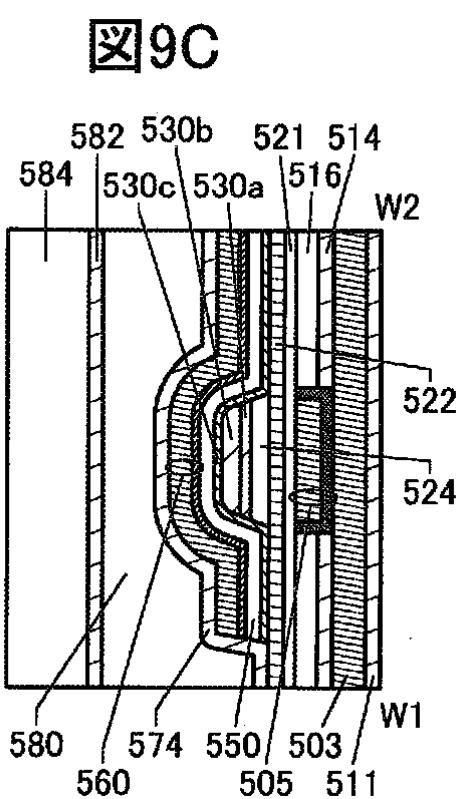

## 【0274】

<トランジスタの構造例2>

図9A、図9Bおよび図9Cを用いてトランジスタ510Bの構造例を説明する。図9Aはトランジスタ510Bの上面図である。図9Bは、図9Aに一点鎖線L1-L2で示す部位の断面図である。図9Cは、図9Aに一点鎖線W1-W2で示す部位の断面図である。なお、図9Aの上面図では、図の明瞭化のために一部の要素を省いている。

## 【0275】

トランジスタ510Bはトランジスタ510Aの変形例である。よって、説明の繰り返しを防ぐため、主にトランジスタ510Aと異なる点について説明する。

## 【0276】

トランジスタ510Bは、導電体542（導電体542a、および導電体542b）と、酸化物530c、絶縁体550、および導電体560と、が重畠する領域を有する。当該構造とすることで、オン電流が高いトランジスタを提供することができる。また、制御性が高いトランジスタを提供することができる。

## 【0277】

第1のゲート電極として機能する導電体560は、導電体560a、および導電体560a上の導電体560bを有する。導電体560aは、導電体505aと同様に、水素原子、水素分子、水分子、銅原子などの不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。または、酸素（例えば、酸素原子、酸素分子などの少なくとも一つ）の拡散を抑制する機能を有する導電性材料を用いることが好ましい。

## 【0278】

導電体560aが酸素の拡散を抑制する機能を持つことにより、導電体560bの材料選択性を向上することができる。つまり、導電体560aを有することで、導電体560bの酸化が抑制され、導電率が低下することを防止することができる。

## 【0279】

また、導電体560の上面および側面、絶縁体550の側面、および酸化物530cの側面を覆うように、絶縁体574を設けることが好ましい。なお、絶縁体574は、水または水素などの不純物、および酸素の拡散を抑制する機能を有する絶縁性材料を用いるとよい。例えば、酸化アルミニウムまたは酸化ハフニウムなどを用いることが好ましい。また、他にも、例えば、酸化マグネシウム、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジムまたは酸化タンタルなどの金属酸化物、窒化酸化シリコンまたは窒化シリコンなどを用いることができる。

## 【0280】

絶縁体574を設けることで、導電体560の酸化を抑制することができる。また、絶縁体574を有することで、絶縁体580が有する水、および水素などの不純物がトランジスタ510Bへ拡散することを抑制することができる。

## 【0281】

また、導電体546と、絶縁体580との間に、バリア性を有する絶縁体576（絶縁体576a、および絶縁体576b）を配置してもよい。絶縁体576を設けることで、絶縁体580の酸素が導電体546と反応し、導電体546が酸化することを抑制することができる。

10

20

30

40

50

## 【0282】

また、バリア性を有する絶縁体576を設けることで、プラグや配線に用いられる導電体の材料選択の幅を広げることができる。例えば、導電体546に、酸素を吸収する性質を持つ一方で、導電性が高い金属材料を用いることで、低消費電力の半導体装置を提供することができる。具体的には、タンゲステンや、アルミニウムなどの耐酸化性が低い一方で導電性が高い材料を用いることができる。また、例えば、成膜、または加工がしやすい導電体を用いることができる。

## 【0283】

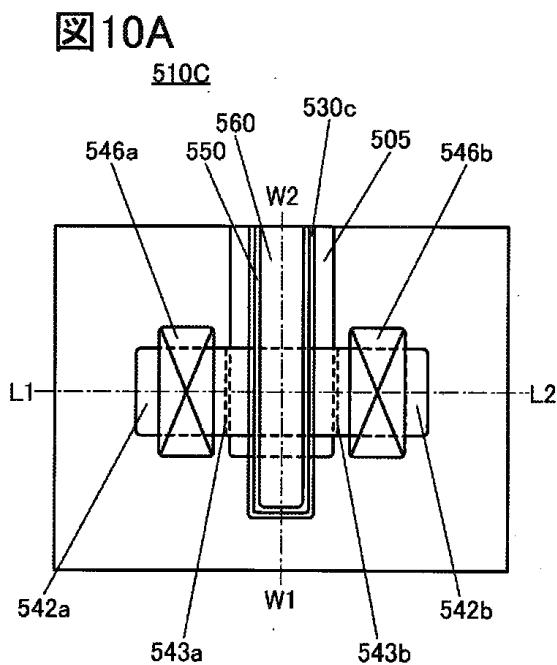

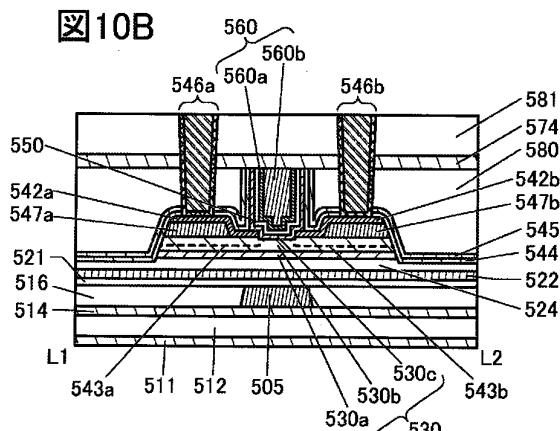

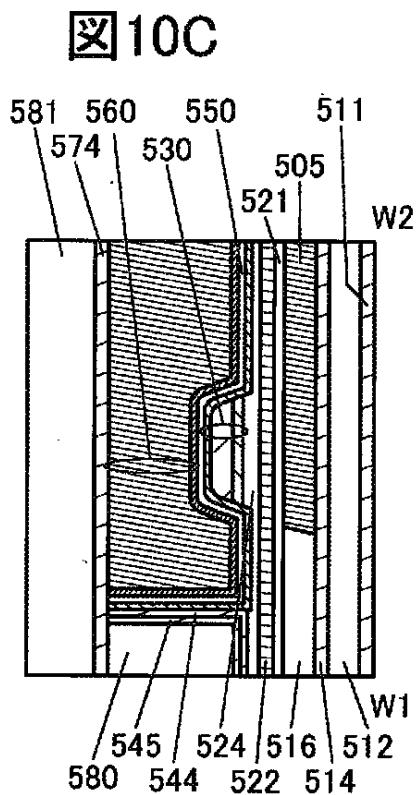

<トランジスタの構造例3>

図10A、図10Bおよび図10Cを用いてトランジスタ510Cの構造例を説明する。

図10Aはトランジスタ510Cの上面図である。図10Bは、図10Aに一点鎖線L1-L2で示す部位の断面図である。図10Cは、図10Aに一点鎖線W1-W2で示す部位の断面図である。なお、図10Aの上面図では、図の明瞭化のために一部の要素を省いている。

10

## 【0284】

トランジスタ510Cはトランジスタ510Aの変形例である。よって、説明の繰り返しを防ぐため、主にトランジスタ510Aと異なる点について説明する。

## 【0285】

図10に示すトランジスタ510Cは、導電体542aと酸化物530bの間に導電体547aが配置され、導電体542bと酸化物530bの間に導電体547bが配置されている。ここで、導電体542a(導電体542b)は、導電体547a(導電体547b)の上面および導電体560側の側面を越えて延在し、酸化物530bの上面に接する領域を有する。ここで、導電体547は、導電体542に用いることができる導電体を用いればよい。さらに、導電体547の膜厚は、少なくとも導電体542より厚いことが好ましい。

20

## 【0286】

図10に示すトランジスタ510Cは、上記のような構成を有することにより、トランジスタ510Aよりも、導電体542を導電体560に近づけることができる。または、導電体542aの端部および導電体542bの端部と、導電体560を重ねることができる。これにより、トランジスタ510Cの実質的なチャネル長を短くし、オン電流および周波数特性の向上を図ることができる。

30

## 【0287】

また、導電体547a(導電体547b)は、導電体542a(導電体542b)と重畠して設けられることが好ましい。このような構成にすることで、導電体546a(導電体546b)を埋め込む開口を形成するエッティングにおいて、導電体547a(導電体547b)がストップとして機能し、酸化物530bがオーバーエッティングされるのを防ぐことができる。

## 【0288】

また、図10に示すトランジスタ510Cは、絶縁体544の上に接して絶縁体545を配置する構成にしてもよい。絶縁体544としては、水または水素などの不純物や、過剰な酸素が、絶縁体580側からトランジスタ510Cに混入するのを抑制するバリア絶縁膜として機能することが好ましい。絶縁体545としては、絶縁体544に用いることができる絶縁体を用いることができる。また、絶縁体544としては、例えば、窒化アルミニウム、窒化アルミニウムチタン、窒化チタン、窒化シリコンまたは窒化酸化シリコンなどの、窒化物絶縁体を用いてもよい。

40

## 【0289】

また、図10に示すトランジスタ510Cは、図8に示すトランジスタ510Aと異なり、導電体505を単層構造で設けてもよい。この場合、パターン形成された導電体505の上に絶縁体516となる絶縁膜を成膜し、当該絶縁膜の上部を、導電体505の上面が露出するまでCMP法などを用いて除去すればよい。ここで、導電体505の上面の平坦

50

性を良好にすることが好ましい。例えば、導電体 505 上面の平均面粗さ (Ra) を 1 nm 以下、好ましくは 0.5 nm 以下、より好ましくは 0.3 nm 以下にすればよい。これにより、導電体 505 の上に形成される、絶縁層の平坦性を良好にし、酸化物 530b および酸化物 530c の結晶性の向上を図ることができる。

【0290】

<トランジスタの構造例 4 >

図 11A、図 11B および図 11C を用いてトランジスタ 510D の構造例を説明する。図 11A はトランジスタ 510D の上面図である。図 11B は、図 11A に一点鎖線 L1 - L2 で示す部位の断面図である。図 11C は、図 11A に一点鎖線 W1 - W2 で示す部位の断面図である。なお、図 11A の上面図では、図の明瞭化のために一部の要素を省いている。

10

【0291】

トランジスタ 510D は上記トランジスタの変形例である。よって、説明の繰り返しを防ぐため、主に上記トランジスタと異なる点について説明する。

【0292】

図 11A 乃至図 11C では、導電体 503 を設げずに、第 2 のゲートとしての機能を有する導電体 505 を配線としても機能させている。また、酸化物 530c 上に絶縁体 550 を有し、絶縁体 550 上に金属酸化物 552 を有する。また、金属酸化物 552 上に導電体 560 を有し、導電体 560 上に絶縁体 570 を有する。また、絶縁体 570 上に絶縁体 571 を有する。

20

【0293】

金属酸化物 552 は、酸素拡散を抑制する機能を有することが好ましい。絶縁体 550 と、導電体 560 との間に、酸素の拡散を抑制する金属酸化物 552 を設けることで、導電体 560 への酸素の拡散が抑制される。つまり、酸化物 530 へ供給する酸素量の減少を抑制することができる。また、酸素による導電体 560 の酸化を抑制することができる。

【0294】

なお、金属酸化物 552 は、第 1 のゲートの一部としての機能を有してもよい。例えば、酸化物 530 として用いることができる酸化物半導体を、金属酸化物 552 として用いることができる。その場合、導電体 560 をスパッタリング法で成膜することで、金属酸化物 552 の電気抵抗値を低下させて導電層とすることができます。これを O<sub>C</sub> (Oxide Conductor) 電極と呼ぶことができる。

30

【0295】

また、金属酸化物 552 は、ゲート絶縁膜の一部としての機能を有する場合がある。したがって、絶縁体 550 に酸化シリコンや酸化窒化シリコンなどを用いる場合、金属酸化物 552 は、比誘電率が高い hig h - k 材料である金属酸化物を用いることが好ましい。当該積層構造とすることで、熱に対して安定、かつ比誘電率の高い積層構造とすることができます。したがって、物理膜厚を保持したまま、トランジスタ動作時に印加するゲート電位の低減が可能となる。また、ゲート絶縁膜として機能する絶縁層の等価酸化膜厚 (EOT) の薄膜化が可能となる。

【0296】

トランジスタ 510D において、金属酸化物 552 を単層で示したが、2 層以上の積層構造としてもよい。例えば、ゲート電極の一部として機能する金属酸化物と、ゲート絶縁膜の一部として機能する金属酸化物とを積層して設けてもよい。

40

【0297】

金属酸化物 552 を有することで、ゲート電極として機能する場合は、導電体 560 からの電界の影響を弱めることなく、トランジスタ 510D のオン電流の向上を図ることができる。または、ゲート絶縁膜として機能する場合は、絶縁体 550 と、金属酸化物 552 との物理的な厚みにより、導電体 560 と、酸化物 530 との間の距離を保つことで、導電体 560 と酸化物 530 との間のリーク電流を抑制することができる。従って、絶縁体 550、および金属酸化物 552 との積層構造を設けることで、導電体 560 と酸化物 5

50

30との間の物理的な距離、および導電体560から酸化物530へかかる電界強度を、容易に適宜調整することができる。

【0298】

具体的には、金属酸化物552として、酸化物530に用いることができる酸化物半導体を低抵抗化することで、金属酸化物552として用いることができる。または、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タンゲステン、チタン、タンタル、ニッケル、ゲルマニウム、または、マグネシウムなどから選ばれた一種、または二種以上が含まれた金属酸化物を用いることができる。

【0299】

特に、アルミニウム、またはハフニウムの一方または双方の酸化物を含む絶縁層である、酸化アルミニウム、酸化ハフニウム、アルミニウムおよびハフニウムを含む酸化物（ハフニウムアルミネート）などを用いることが好ましい。特に、ハフニウムアルミネートは、酸化ハフニウム膜よりも、耐熱性が高い。そのため、後の工程での熱処理において、結晶化しにくいため好ましい。なお、金属酸化物552は、必須の構成ではない。求めるトランジスタ特性により、適宜設計すればよい。

10

【0300】

絶縁体570は、水または水素などの不純物、および酸素の透過を抑制する機能を有する絶縁性材料を用いるとよい。例えば、酸化アルミニウムまたは酸化ハフニウムなどを用いることが好ましい。これにより、絶縁体570よりも上方からの酸素で導電体560が酸化するのを抑制することができる。また、絶縁体570よりも上方からの水または水素などの不純物が、導電体560および絶縁体550を介して、酸化物530に混入することを抑制することができる。

20

【0301】

絶縁体571はハードマスクとして機能する。絶縁体571を設けることで、導電体560の加工の際、導電体560の側面が概略垂直、具体的には、導電体560の側面と基板表面のなす角を、75度以上100度以下、好ましくは80度以上95度以下とすることができます。

【0302】

なお、絶縁体571に、水または水素などの不純物、および酸素の透過を抑制する機能を有する絶縁性材料を用いることで、バリア層としての機能を兼ねさせててもよい。その場合、絶縁体570は設けなくともよい。

30

【0303】

絶縁体571をハードマスクとして用いて、絶縁体570、導電体560、金属酸化物552、絶縁体550、および酸化物530cの一部を選択的に除去することで、これらの側面を略一致させて、かつ、酸化物530b表面の一部を露出させることができる。

【0304】

また、トランジスタ510Dは、露出した酸化物530b表面の一部に領域531aおよび領域531bを有する。領域531aまたは領域531bの一方はソース領域として機能し、他方はドレイン領域として機能する。

【0305】

領域531aおよび領域531bの形成は、例えば、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、またはプラズマ処理などを用いて、露出した酸化物530b表面にリンまたはボロンなどの不純物元素を導入することで実現できる。なお、本実施の形態などにおいて「不純物元素」とは、主成分元素以外の元素のことをいう。

40

【0306】

また、酸化物530b表面の一部を露出させた後に金属膜を成膜し、その後加熱処理することにより、該金属膜に含まれる元素を酸化物530bに拡散させて領域531aおよび領域531bを形成することもできる。

【0307】

酸化物530bの不純物元素が導入された領域は、電気抵抗率が低下する。このため、領

50

域 5 3 1 a および領域 5 3 1 b を「不純物領域」または「低抵抗領域」という場合がある。

【 0 3 0 8 】

絶縁体 5 7 1 および / または導電体 5 6 0 をマスクとして用いることで、領域 5 3 1 a および領域 5 3 1 b を自己整合 (セルフアライメント) 的に形成することができる。よって、領域 5 3 1 a および / または領域 5 3 1 b と、導電体 5 6 0 が重ならず、寄生容量を低減することができる。また、チャネル形成領域とソースドレイン領域 (領域 5 3 1 a または領域 5 3 1 b ) の間にオフセット領域が形成されない。領域 5 3 1 a および領域 5 3 1 b を自己整合 (セルフアライメント) 的に形成することにより、オン電流の増加、しきい値電圧の低減、動作周波数の向上などを実現できる。

【 0 3 0 9 】

なお、オフ電流を更に低減するため、チャネル形成領域とソースドレイン領域の間にオフセット領域を設けてもよい。オフセット領域とは、電気抵抗率が高い領域であり、前述した不純物元素の導入が行なわれない領域である。オフセット領域の形成は、絶縁体 5 7 5 の形成後に前述した不純物元素の導入を行なうことで実現できる。この場合、絶縁体 5 7 5 も絶縁体 5 7 1 などと同様にマスクとして機能する。よって、酸化物 5 3 0 b の絶縁体 5 7 5 と重なる領域に不純物元素が導入されず、該領域の電気抵抗率を高いままとすることができる。

【 0 3 1 0 】

また、トランジスタ 5 1 0 D は、絶縁体 5 7 0 、導電体 5 6 0 、金属酸化物 5 5 2 、絶縁体 5 5 0 、および酸化物 5 3 0 c の側面に絶縁体 5 7 5 を有する。絶縁体 5 7 5 は、比誘電率の低い絶縁体であることが好ましい。例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素および窒素を添加した酸化シリコン、空孔を有する酸化シリコン、または樹脂などであることが好ましい。特に、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、空孔を有する酸化シリコンを絶縁体 5 7 5 に用いると、後の工程で絶縁体 5 7 5 中に過剰酸素領域を容易に形成できるため好ましい。また、酸化シリコンおよび酸化窒化シリコンは、熱的に安定であるため好ましい。また、絶縁体 5 7 5 は、酸素を拡散する機能を有することが好ましい。

【 0 3 1 1 】

また、トランジスタ 5 1 0 D は、絶縁体 5 7 5 、酸化物 5 3 0 上に絶縁体 5 7 4 を有する。絶縁体 5 7 4 は、スパッタリング法を用いて成膜することが好ましい。スパッタリング法を用いることにより、水または水素などの不純物の少ない絶縁体を成膜することができる。例えば、絶縁体 5 7 4 として、酸化アルミニウムを用いるとよい。

【 0 3 1 2 】

なお、スパッタリング法を用いた酸化膜は、被成膜構造体から水素を引き抜く場合がある。従って、絶縁体 5 7 4 が酸化物 5 3 0 および絶縁体 5 7 5 から水素および水を吸収することで、酸化物 5 3 0 および絶縁体 5 7 5 の水素濃度を低減することができる。

【 0 3 1 3 】

<トランジスタの構造例 5 >

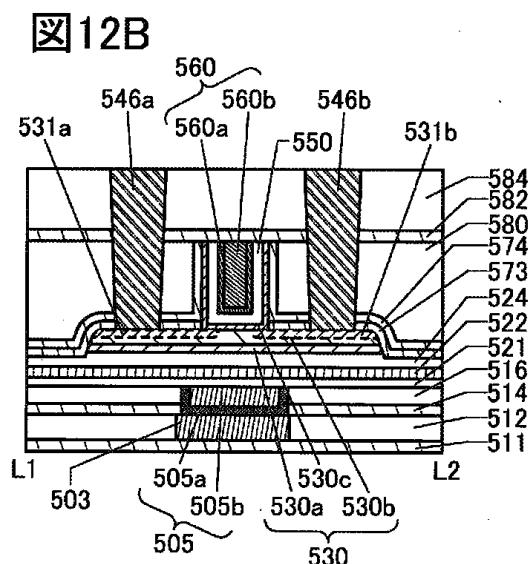

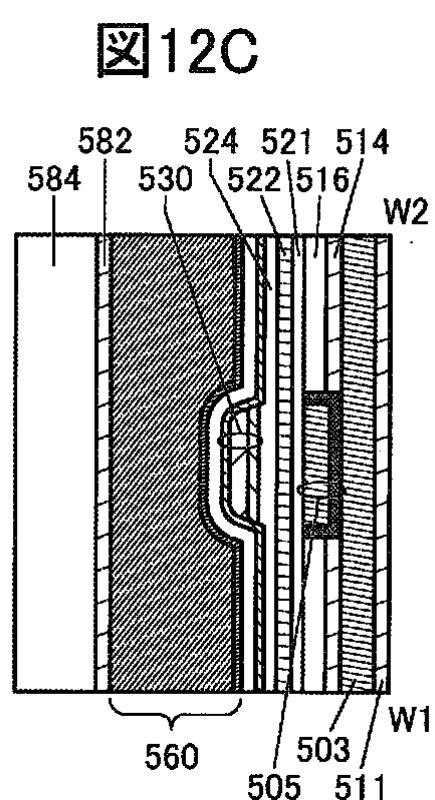

図 1 2 A 乃至図 1 2 C を用いてトランジスタ 5 1 0 E の構造例を説明する。図 1 2 A はトランジスタ 5 1 0 E の上面図である。図 1 2 B は、図 1 2 A に一点鎖線 L 1 - L 2 で示す部位の断面図である。図 1 2 C は、図 1 2 A に一点鎖線 W 1 - W 2 で示す部位の断面図である。なお、図 1 2 A の上面図では、図の明瞭化のために一部の要素を省いている。

【 0 3 1 4 】

トランジスタ 5 1 0 E は上記トランジスタの変形例である。よって、説明の繰り返しを防ぐため、主に上記トランジスタと異なる点について説明する。

【 0 3 1 5 】

図 1 2 A 乃至図 1 2 C では、導電体 5 4 2 を設けずに、露出した酸化物 5 3 0 b 表面の一部に領域 5 3 1 a および領域 5 3 1 b を有する。領域 5 3 1 a または領域 5 3 1 b の一方はソース領域として機能し、他方はドレイン領域として機能する。また、酸化物 5 3 0 b

10

20

30

40

50

と、絶縁体 574 の間に、絶縁体 573 を有する。

【0316】

図12に示す、領域531（領域531a、および領域531b）は、酸化物530bに下記の元素が添加された領域である。領域531は、例えば、ダミーゲートを用いることで形成することができる。

【0317】

具体的には、酸化物530b上にダミーゲートを設け、当該ダミーゲートをマスクとして用い、上記酸化物530bを低抵抗化する元素を添加するとよい。つまり、酸化物530が、ダミーゲートと重畠していない領域に、当該元素が添加され、領域531が形成される。なお、当該元素の添加方法としては、イオン化された原料ガスを質量分離して添加するイオン注入法、イオン化された原料ガスを質量分離せずに添加するイオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

10

【0318】

なお、酸化物530を低抵抗化する元素としては、代表的には、ホウ素、またはリンが挙げられる。また、水素、炭素、窒素、フッ素、硫黄、塩素、チタン、希ガス等を用いてもよい。希ガスの代表例としては、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノン等がある。当該元素の濃度は、二次イオン質量分析法（S I M S : Secondary Ion Mass Spectrometry）などを用いて測定すればよい。

20

【0319】

特に、ホウ素、及びリンは、低温ポリシリコン等の製造ラインの装置を使用することができるため、好ましい。既存の設備を転用することができ、設備投資を抑制することができる。

【0320】

続いて、酸化物530b、およびダミーゲート上に、絶縁体573となる絶縁膜、および絶縁体574となる絶縁膜を成膜してもよい。絶縁体573となる絶縁膜、および絶縁体574となる絶縁膜を積層して設けることで、領域531と、酸化物530cおよび絶縁体550とが重畠する領域を設けることができる。

30

【0321】

具体的には、絶縁体574となる絶縁膜上に絶縁体580となる絶縁膜を設けた後、絶縁体580となる絶縁膜にC M P（C hemical M echanical P olish i n g）処理を行うことで、絶縁体580となる絶縁膜の一部を除去し、ダミーゲートを露出する。続いて、ダミーゲートを除去する際に、ダミーゲートと接する絶縁体573の一部も除去するとよい。従って、絶縁体580に設けられた開口部の側面には、絶縁体574、および絶縁体573が露出し、当該開口部の底面には、酸化物530bに設けられた領域531の一部が露出する。次に、当該開口部に酸化物530cとなる酸化膜、絶縁体550となる絶縁膜、および導電体560となる導電膜を順に成膜した後、絶縁体580が露出するまでC M P処理などにより、酸化物530cとなる酸化膜、絶縁体550となる絶縁膜、および導電体560となる導電膜の一部を除去することで、図12に示すトランジスタを形成することができる。

30

【0322】

なお、絶縁体573、および絶縁体574は必須の構成ではない。求めるトランジスタ特性により、適宜設計すればよい。

40

【0323】

図12に示すトランジスタは、既存の装置を転用することができ、さらに、導電体542を設けないため、コストの低減を図ることができる。

【0324】

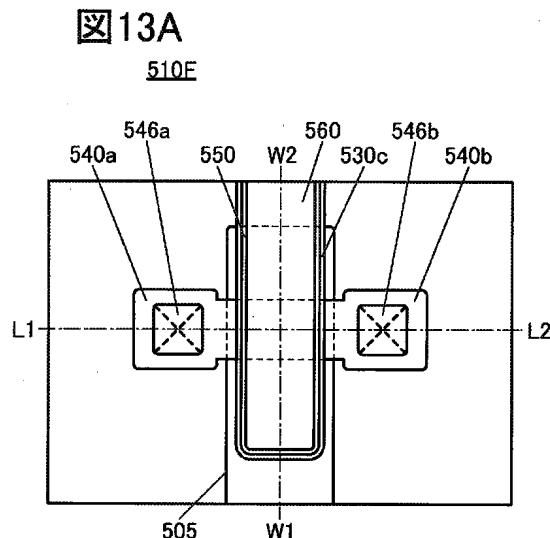

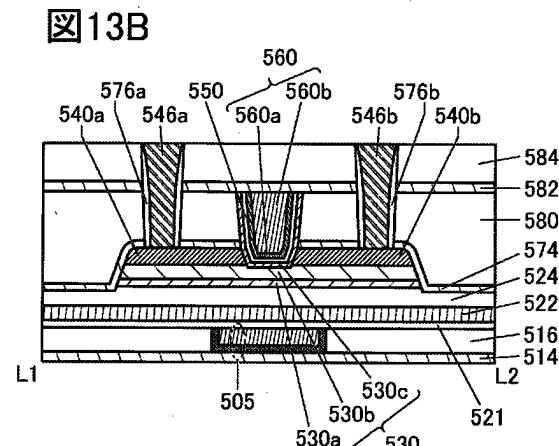

<トランジスタの構造例6>

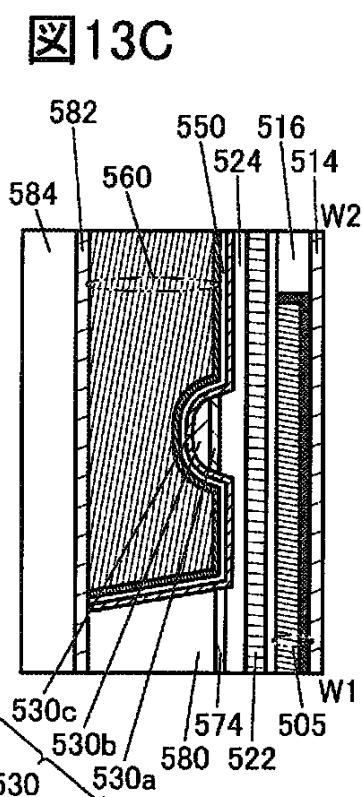

図13A乃至図13Cを用いてトランジスタ510Fの構造例を説明する。図13Aはトランジスタ510Fの上面図である。図13Bは、図13Aに一点鎖線L1-L2で示す部位の断面図である。図13Cは、図13Aに一点鎖線W1-W2で示す部位の断面図で

50

ある。なお、図13Aの上面図では、図の明瞭化のために一部の要素を省いている。

【0325】

トランジスタ510Fはトランジスタ510Aの変形例である。よって、説明の繰り返しを防ぐため、主に上記トランジスタと異なる点について説明する。

【0326】

トランジスタ510Aでは、絶縁体574の一部が絶縁体580に設けられた開口部内に設けられ、導電体560の側面を覆うように設けられている。一方で、トランジスタ510Fでは絶縁体580と絶縁体574の一部を除去して開口が形成されている。

【0327】

また、導電体546と、絶縁体580との間に、バリア性を有する絶縁体576（絶縁体576a、および絶縁体576b）を配置してもよい。絶縁体576を設けることで、絶縁体580の酸素が導電体546と反応し、導電体546が酸化することを抑制することができる。

【0328】

なお、酸化物530として酸化物半導体を用いる場合は、各金属原子の原子数比が異なる複数の酸化物層の積層構造を有することが好ましい。具体的には、酸化物530aに用いる金属酸化物において、構成元素中の元素Mの原子数比が、酸化物530bに用いる金属酸化物における、構成元素中の元素Mの原子数比より大きいことが好ましい。また、酸化物530aに用いる金属酸化物において、Inに対する元素Mの原子数比が、酸化物530bに用いる金属酸化物における、Inに対する元素Mの原子数比より大きいことが好ましい。また、酸化物530bに用いる金属酸化物において、元素Mに対するInの原子数比が、酸化物530aに用いる金属酸化物における、元素Mに対するInの原子数比より大きいことが好ましい。また、酸化物530cは、酸化物530aまたは酸化物530bに用いることができる金属酸化物を用いることができる。

【0329】

酸化物530a、酸化物530b、および酸化物530cは、結晶性を有することが好ましく、特に、CAC-O<sub>S</sub>を用いることが好ましい。CAC-O<sub>S</sub>等の結晶性を有する酸化物は、不純物や欠陥（酸素欠損等）が少なく、結晶性の高い、緻密な構造を有している。よって、ソース電極またはドレイン電極による、酸化物530bからの酸素の引き抜きを抑制することができる。これにより、熱処理を行っても、酸化物530bから酸素が引き抜かれることを低減できるので、トランジスタ510Fは、製造工程における高い温度（所謂サーマルバジェット）に対して安定である。

【0330】

なお、酸化物530aおよび酸化物530cの一方または双方を省略してもよい。酸化物530を酸化物530bの単層としてもよい。酸化物530を、酸化物530a、酸化物530b、および酸化物530cの積層とする場合は、酸化物530aおよび酸化物530cの伝導帯下端のエネルギーが、酸化物530bの伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物530aおよび酸化物530cの電子親和力が、酸化物530bの電子親和力より小さいことが好ましい。この場合、酸化物530cは、酸化物530aに用いることができる金属酸化物を用いることが好ましい。具体的には、酸化物530cに用いる金属酸化物において、構成元素中の元素Mの原子数比が、酸化物530bに用いる金属酸化物における、構成元素中の元素Mの原子数比より大きいことが好ましい。また、酸化物530cに用いる金属酸化物において、Inに対する元素Mの原子数比が、酸化物530bに用いる金属酸化物における、Inに対する元素Mの原子数比より大きいことが好ましい。また、酸化物530bに用いる金属酸化物において、元素Mに対するInの原子数比が、酸化物530cに用いる金属酸化物における、元素Mに対するInの原子数比より大きいことが好ましい。

【0331】

ここで、酸化物530a、酸化物530b、および酸化物530cの接合部において、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、酸化物530a、酸化物

10

20

30

40

50

530b、および酸化物530cの接合部における伝導帯下端のエネルギー準位は、連続的に変化または連続接合するともいうことができる。このようにするために、酸化物530aと酸化物530bとの界面、および酸化物530bと酸化物530cとの界面において形成される混合層の欠陥準位密度を低くするとよい。

#### 【0332】

具体的には、酸化物530aと酸化物530b、酸化物530bと酸化物530cが、酸素以外に共通の元素を有する（主成分とする）ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物530bがIn-Ga-Zn酸化物の場合、酸化物530aおよび酸化物530cとして、In-Ga-Zn酸化物、Ga-Zn酸化物、酸化ガリウム等を用いてもよい。また、酸化物530cを積層構造としてもよい。例えば、In-Ga-Zn酸化物と、当該In-Ga-Zn酸化物上のGa-Zn酸化物との積層構造、またはIn-Ga-Zn酸化物と、当該In-Ga-Zn酸化物上の酸化ガリウムとの積層構造を用いることができる。別言すると、In-Ga-Zn酸化物と、Inを含まない酸化物との積層構造を、酸化物530cとして用いてもよい。

10

#### 【0333】

具体的には、酸化物530aとして、In:Ga:Zn = 1:3:4 [原子数比]、または1:1:0.5 [原子数比]の金属酸化物を用いればよい。また、酸化物530bとして、In:Ga:Zn = 4:2:3 [原子数比]、または3:1:2 [原子数比]の金属酸化物を用いればよい。また、酸化物530cとして、In:Ga:Zn = 1:3:4 [原子数比]、In:Ga:Zn = 4:2:3 [原子数比]、Ga:Zn = 2:1 [原子数比]、またはGa:Zn = 2:5 [原子数比]の金属酸化物を用いればよい。また、酸化物530cを積層構造とする場合の具体例としては、In:Ga:Zn = 4:2:3 [原子数比]と、Ga:Zn = 2:1 [原子数比]との積層構造、In:Ga:Zn = 4:2:3 [原子数比]と、Ga:Zn = 2:5 [原子数比]との積層構造、In:Ga:Zn = 4:2:3 [原子数比]と、酸化ガリウムとの積層構造等が挙げられる。

20

#### 【0334】

このとき、キャリアの主たる経路は酸化物530bとなる。酸化物530a、酸化物530cを上述の構成とすることで、酸化物530aと酸化物530bとの界面、および酸化物530bと酸化物530cとの界面における欠陥準位密度を低くすることができる。そのため、界面散乱によるキャリア伝導への影響が小さくなり、トランジスタ510Fは高いオン電流、および高い周波数特性を得ることができる。なお、酸化物530cを積層構造とした場合、上述の酸化物530bと、酸化物530cとの界面における欠陥準位密度を低くする効果に加え、酸化物530cが有する構成元素が、絶縁体550側に拡散するのを抑制することが期待される。より具体的には、酸化物530cを積層構造とし、積層構造の上方にInを含まない酸化物を位置させるため、絶縁体550側に拡散しうるInを抑制することができる。絶縁体550は、ゲート絶縁体として機能するため、Inが拡散した場合、トランジスタの特性不良となる。したがって、酸化物530cを積層構造とすることで、信頼性の高い半導体装置を提供することが可能となる。

30

#### 【0335】

酸化物530は、酸化物半導体として機能する金属酸化物を用いることが好ましい。例えば、酸化物530のチャネル形成領域となる金属酸化物としては、バンドギャップが2eV以上、好ましくは2.5eV以上のものを用いることが好ましい。このように、バンドギャップの大きい金属酸化物を用いることで、トランジスタのオフ電流を低減することができる。このようなトランジスタを用いることで、低消費電力の半導体装置を提供できる。

40

#### 【0336】

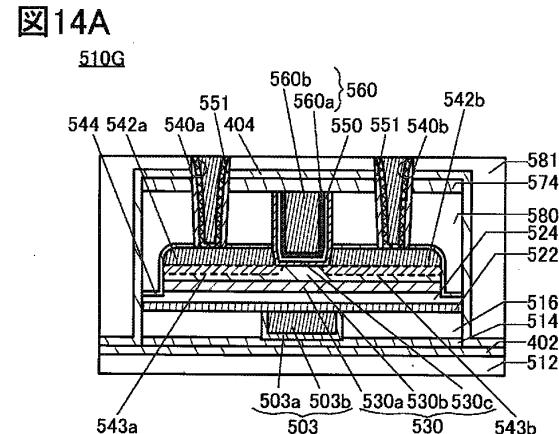

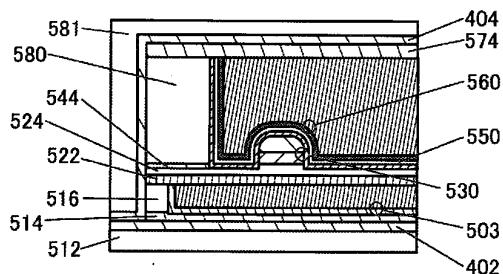

##### <トランジスタの構造例7>

図14A、図14Bを用いてトランジスタ510Gの構造例を説明する。トランジスタ510Gはトランジスタ500の変形例である。よって、説明の繰り返しを防ぐため、主に上記トランジスタと異なる点について説明する。なお、図14A、図14Bに示す構成は、トランジスタ300等、本発明の一形態の半導体装置が有する他のトランジスタにも適

50

用することができる。

【0337】

図14Aは、トランジスタ510Gのチャネル長方向の断面図であり、図14Bは、トランジスタ510Gのチャネル幅方向の断面図である。図14A、図14Bに示すトランジスタ510Gは、絶縁体402及び絶縁体404を有する点が、図7A、図7Bに示すトランジスタ500と異なる。また、導電体540aの側面に接して絶縁体551が設けられ、導電体540bの側面に接して絶縁体551が設けられる点が、図7A、図7Bに示すトランジスタ500と異なる。さらに、絶縁体520を有さない点が、図7A、図7Bに示すトランジスタ500と異なる。

【0338】

図14A、図14Bに示すトランジスタ510Gは、絶縁体512上に絶縁体402が設けられる。また、絶縁体574上、及び絶縁体402上に絶縁体404が設けられる。

【0339】

図14A、図14Bに示すトランジスタ510Gでは、絶縁体514、絶縁体516、絶縁体522、絶縁体524、絶縁体544、絶縁体580、及び絶縁体574がパターニングされており、絶縁体404がこれらを覆う構造になっている。つまり、絶縁体404は、絶縁体574の上面、絶縁体574の側面、絶縁体580の側面、絶縁体544の側面、絶縁体524の側面、絶縁体522の側面、絶縁体516の側面、絶縁体514の側面、絶縁体402の上面とそれぞれ接する。これにより、酸化物530等は、絶縁体404と絶縁体402によって外部から隔離される。

【0340】

絶縁体402及び絶縁体404は、水素（例えば、水素原子、水素分子などの少なくとも一つ）又は水分子の拡散を抑制する機能が高いことが好ましい。例えば、絶縁体402及び絶縁体404として、水素バリア性が高い材料である、窒化シリコン又は窒化酸化シリコンを用いることが好ましい。これにより、酸化物530に水素等が拡散することを抑制することができるので、トランジスタ510Gの特性が低下することを抑制することができる。よって、本発明の一形態の半導体装置の信頼性を高めることができる。

【0341】

絶縁体551は、絶縁体581、絶縁体404、絶縁体574、絶縁体580、及び絶縁体544に接して設けられる。絶縁体551は、水素又は水分子の拡散を抑制する機能を有することが好ましい。たとえば、絶縁体551として、水素バリア性が高い材料である、窒化シリコン、酸化アルミニウム、又は窒化酸化シリコン等の絶縁体を用いることが好ましい。特に、窒化シリコンは水素バリア性が高い材料であるので、絶縁体551として用いると好適である。絶縁体551として水素バリア性が高い材料を用いることにより、水又は水素等の不純物が、絶縁体580等から導電体540a及び導電体540bを通じて酸化物530に拡散することを抑制することができる。また、絶縁体580に含まれる酸素が導電体540a及び導電体540bに吸収されることを抑制することができる。以上により、本発明の一形態の半導体装置の信頼性を高めることができる。

【0342】