(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4117985号

(P4117985)

(45) 発行日 平成20年7月16日(2008.7.16)

(24) 登録日 平成20年5月2日(2008.5.2)

(51) Int.Cl.

F 1

G09F 9/30 (2006.01)

G09F 9/30 338

H01L 27/32 (2006.01)

G09F 9/30 365Z

H01L 51/50 (2006.01)

H05B 33/14 A

請求項の数 11 (全 12 頁)

(21) 出願番号

特願平11-277084

(22) 出願日

平成11年9月29日(1999.9.29)

(65) 公開番号

特開2001-100654(P2001-100654A)

(43) 公開日

平成13年4月13日(2001.4.13)

審査請求日

平成16年11月19日(2004.11.19)

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100131071

弁理士 ▲角▼谷 浩

(72) 発明者 西川 龍司

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

審査官 河原 英雄

最終頁に続く

(54) 【発明の名称】 E L表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

陽極と陰極との間に発光層を有する E L 素子と、

半導体膜からなる能動層のドレインが前記 E L 素子の駆動ラインに電気的に接続され、

前記能動層のソースが前記 E L 素子に電気的に接続された薄膜トランジスタと、

を備えた表示画素を基板上にマトリクス状に配列して成る E L 表示装置であり、

前記駆動ラインと交差する方向に延在され、且つ前記駆動ラインと電気的に接続され、

前記駆動ラインと前記基板との間に設けられたバイパスラインを有する事を特徴とする E

L 表示装置。

## 【請求項 2】

陽極と陰極との間に発光層を有する E L 素子と、

半導体膜から成る能動層のドレインがドレンラインに接続され、ゲートがゲートライ

ンにそれぞれ接続された第 1 の薄膜トランジスタと、

前記半導体膜からなる能動層のドレインが前記 E L 素子の駆動ラインに接続され、ゲー

トが前記第 1 の薄膜トランジスタのソースに電気的に接続され、ソースが前記 E L 素子に

接続された第 2 の薄膜トランジスタと、

を備えた表示画素を基板上にマトリクス状に配列して成る E L 表示装置であり、

前記駆動ラインと交差する方向に延在され、且つ前記駆動ラインと電気的に接続され、

前記駆動ラインと前記基板との間に設けられたバイパスラインを有する事を特徴とする E

L 表示装置。

10

20

**【請求項 3】**

前記バイパスラインは、前記ゲートが形成された層に形成される請求項 2 に記載の E L 表示装置。

**【請求項 4】**

前記バイパスラインは、前記半導体膜が形成された層に形成される請求項 2 に記載の E L 表示装置。

**【請求項 5】**

前記バイパスラインは、前記半導体膜と前記駆動ラインとの間に位置する絶縁層の層間に形成される請求項 2 に記載の E L 表示装置。

**【請求項 6】**

前記バイパスラインは、前記ゲートラインと同時に形成し、高融点金属で形成される請求項 3 に記載の E L 表示装置。

10

**【請求項 7】**

前記バイパスラインは、前記半導体膜、もしくは、高融点金属で形成される請求項 4 に記載の E L 表示装置。

**【請求項 8】**

前記バイパスラインは、高融点金属もしくはアルミを主成分とする材料もしくは半導体膜で形成される請求項 5 に記載の E L 表示装置。

**【請求項 9】**

前記バイパスラインは、少なくとも一部が前記陽極と重畠して成る請求項 1 または請求項 2 に記載の E L 表示装置。

20

**【請求項 10】**

前記バイパスラインは、前記表示画素毎に形成され、前記駆動ラインとの重畠部には前記表示画素毎にコンタクトが形成される請求項 1 または請求項 2 に記載の E L 表示装置。

**【請求項 11】**

前記薄膜トランジスタは、トップゲート型構造からなる請求項 1 または請求項 2 に記載の E L 表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

30

本発明は、エレクトロルミネッセンス素子及び薄膜トランジスタを備えたエレクトロルミネッセンス表示装置に関する。

**【0002】****【従来の技術】**

近年、エレクトロルミネッセンス (Electro Luminescence : 以下、「E L」と称する。) 素子を用いた E L 表示装置が、C R T や L C D に代わる表示装置として注目されており、例えば、その E L 素子を駆動させるスイッチング素子として薄膜トランジスタ (Thin Film Transistor : 以下、「T F T」と称する。) を備えた E L 表示装置の研究開発も進められている。

**【0003】**

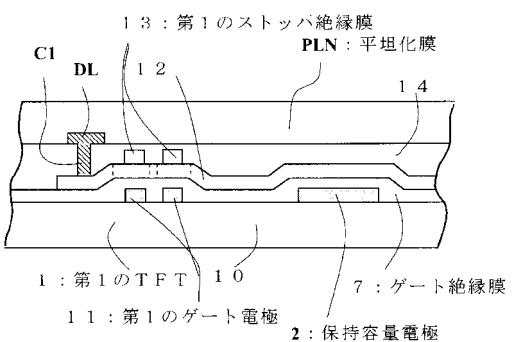

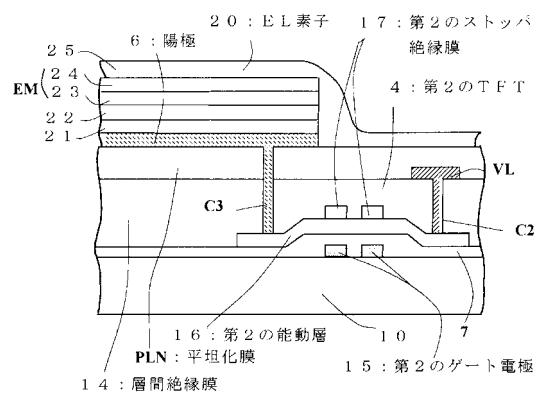

図 7 に有機 E L 表示装置の表示画素を示し、図 8 に有機 E L 表示装置の等価回路図を示す。また、図 9 に図 7 の A - A 線に沿った断面図を示し、図 10 に図 7 の B - B 線に沿った断面図を示す。

40

**【0004】**

図に示すように、ゲートライン G L とドレインライン D L とに囲まれた領域に表示画素が形成されている。両信号線の交点付近にはスイッチング素子である第 1 の T F T 1 が備えられており、その T F T 1 のソースは、保持容量電極 2 と容量を構成する容量電極 3 を兼ねるとともに、有機 E L 素子を駆動する第 2 の T F T 4 のゲート 5 に接続されている。第 2 の T F T 4 のソースは有機 E L 素子の陽極 6 に接続され、他方のドレインは有機 E L 素子を駆動する駆動ライン V L に接続されている。

50

## 【0005】

また、前記保持容量電極2はクロム等から成っており、上層のゲート絶縁膜7を介して第1のTFT1のソースと一体の容量電極3と重畠し、前記ゲート絶縁膜7を誘電体層として電荷を蓄積している。この保持容量8は、第2のTFT4のゲート5に印加される電圧を保持している。

## 【0006】

続いて、スイッチング用の第1のTFT1について図7と図9を参照しながら説明する。

## 【0007】

まず石英ガラス、無アルカリガラス等からなる透明な絶縁性基板10上に、クロム(Cr)、モリブデン(Mo)などの高融点金属からなる第1のゲート電極11が設けられている。この第1のゲート電極11は、図7のようにゲートラインGLと一体で例えば左右に複数本並行に延在されている。また図9の第1のゲート電極11の右隣には、第1のゲート電極11と同一工程で作られた保持容量電極2が形成されている。この保持容量電極2は、図7の様に容量を構成するため、第1のTFT1と第2のTFT4の間で、拡大された部分を有し、これらは左右に延在された保持容量ラインCLと一体で構成されている。

10

## 【0008】

続いて、ゲート絶縁膜7を介して多結晶シリコン(p-Siと称する。)膜からなる第1の能動層12が形成されている。この能動層12は、LDD(Lightly Doped Drain)構造が採用されている。即ち、ゲートの両側に低濃度領域が設けられ、更に外側には、高濃度のソース領域及びドレイン領域が設けられている。前記能動層12の上には、ストップ絶縁膜13が設けられている。このストップ絶縁膜13は、能動層12へのイオン注入阻止膜であり、ここではSi酸化膜から成る。

20

## 【0009】

そして、ゲート絶縁膜7、能動層12及びストップ絶縁膜13上には、例えば、順にSiO<sub>2</sub>膜、SiN膜及びSiO<sub>2</sub>膜が積層された層間絶縁膜14が設けられ、ドレインに設けたコンタクトホールC1を介してドレイン電極と成るドレインラインDLが電気的に接続されている。更に全面には、表面の凹凸を平坦にするため、例えば有機樹脂から成る平坦化膜PLNが形成されている。EL表示装置は、電流駆動なので、EL層が均一な膜厚でなければならない。膜厚が薄い部分で電流集中が発生するからである。従って少なくともこの形成領域は、かなりの平坦性が要求されるため、前記平坦化膜PLNが採用される。

30

## 【0010】

次に、有機EL素子を駆動する第2のTFT4について図10を参照して説明する。

## 【0011】

前述した絶縁性基板10上には、前記第1のゲート11と同一材料の第2のゲート電極15が設けられており、ゲート絶縁膜7を介して第2の能動層16が設けられている。前述と同様に能動層の上にはストップ絶縁膜17が設けられている。

## 【0012】

前記能動層16には、ゲート電極15上方に真性又は実質的に真性であるチャネルと、このチャネルの両側に、p型不純物のソース領域及びドレイン領域が設けられp型チャネルTFTを構成している。

40

## 【0013】

そして全面には、前述した層間絶縁膜14が形成されている。そしてコンタクトホールC2を介して駆動ラインVLが電気的に接続されている。更に全面には、前述した平坦化膜PLNが形成され、コンタクトホールC3によりソースが露出されている。そしてこのコンタクトホールを介してITO(Indium Thin Oxide)から成る透明電極(有機EL素子の陽極)6が形成されている。

## 【0014】

有機EL素子20は、前記陽極6、MTDATA(4,4-bis(3-methylphenylphenylamino)biphenyl)から成る第1ホール輸送層21、及びTPD(4,4,4-tris(3-methylphenylphenylamino)triphenylamine)からなる第2ホール輸送層22、キナクリドン(Quinacridone)

50

ne) 誘導体を含む B e b q 2 (10-ベンゾ [h] キノリノール - ベリリウム錯体) から成る発光層 2 3 及び B e b q 2 から成る電子輸送層 2 4 からなる発光素子層 E M、マグネシウム・インジウム合金から成る陰極 2 5 がこの順番で積層形成された構造であり、有機 E L 素子の実質全面に設けられている。

## 【0015】

有機 E L 素子の発光原理および動作は、陽極 6 から注入されたホールと、陰極 2 5 から注入された電子とが発光層 E M の内部で再結合し、発光層 E M を形成する有機分子を励起して励起子を発生させる。この励起子が放射失活する過程で発光層から光が放たれ、この光が透明な陽極から透明絶縁基板を介して外部へ放出されて発光する。

## 【0016】

10

このように、第 1 の TFT 1 のソース S から供給された電荷が保持容量 8 に蓄積され、第 2 の TFT 4 のゲート 1 5 に印加され、その電圧に応じて有機 E L 素子を電流駆動し、発光する。

## 【0017】

## 【発明が解決しようとする課題】

ところが、図 8 に示すように有機 E L 素子を駆動する駆動ライン V L は、表示画素領域外に設けた駆動電源入力端子 T に接続されており、そして縦に並んだ表示画素ごとに接続されて配置されている。そのため、駆動電源入力端子 T から遠ざかるにつれて駆動ライン V L の抵抗がその長さに応じて大きくなるので、駆動電源入力端子 T から遠い位置にある表示画素の有機 E L 素子には本来供給されるべき電流が供給されなくなり、表示が暗くなり、表示ムラが発生する欠点があった。

## 【0018】

そこで本発明は、上記の従来の欠点に鑑みて為されたものであり、駆動ライン V L の抵抗による電源電流の低下を抑制し、本来供給されるべき電流が E L 素子に供給して、明るい表示を得ることができる E L 表示装置を提供することを目的とする。

## 【0019】

## 【課題を解決するための手段】

本発明は、前述したように各表示画素に位置する駆動ラインの抵抗をより均一にするもので、

第 1、第 2 は、駆動ラインのそれぞれを、延在方向と交差する方向に設けると共に、駆動ラインと電気的に接続され、前記駆動ラインよりも下層の位置にバイパスラインを設けることで解決するものである。

## 【0020】

例えば、ゲートラインが形成された層に、クロムで成るバイパスラインを設け、駆動ラインとコンタクトすれば、駆動ラインは、格子状に形成されたことになり、駆動電源入力端子から遠ざかっても、抵抗値の下がる割合は、従来のものよりも抑制される。

## 【0021】

第 3 に、バイパスラインを、ゲートが形成された層、半導体膜が形成された層、または半導体膜と駆動ラインとの間に位置する絶縁層に形成する事で解決するものである。

## 【0022】

駆動ラインとバイパスラインは、本来同層にて形成できるが、その分バイパスラインの配置面積を必要とする。しかしバイパスラインを駆動ラインの下層に置くことで、例えば陽極と重疊させることができる。しかも陽極とバイパスラインとの間には、かなり厚く絶縁層が形成されるため、寄生容量の問題も抑制される。

## 【0023】

第 4 に、前述したようにバイパスラインの少なくとも一部を前記陽極と重疊させることで、バイパスラインの配置に依って拡大する表示領域の拡大化を抑制させることができる。また抑制させた分、他の構成要素を拡大させることもできる。

## 【0024】

第 5 に、バイパスラインを、前記表示画素毎に形成し、前記駆動ラインとの重疊部にコン

10

20

30

40

50

タクトを形成する事で解決するものである。

【0025】

前述までは、バイパスラインは、少なくとも1本で効果がある。しかし表示画素毎にバイパスラインが無いと、その有無により表示画素のムラがやはり発生する。ここでは、これを更に抑制する。

【0026】

第6に、本発明は、ボトムゲート型構造でも、トップゲート型構造でも実現できる。

【0027】

【発明の実施の形態】

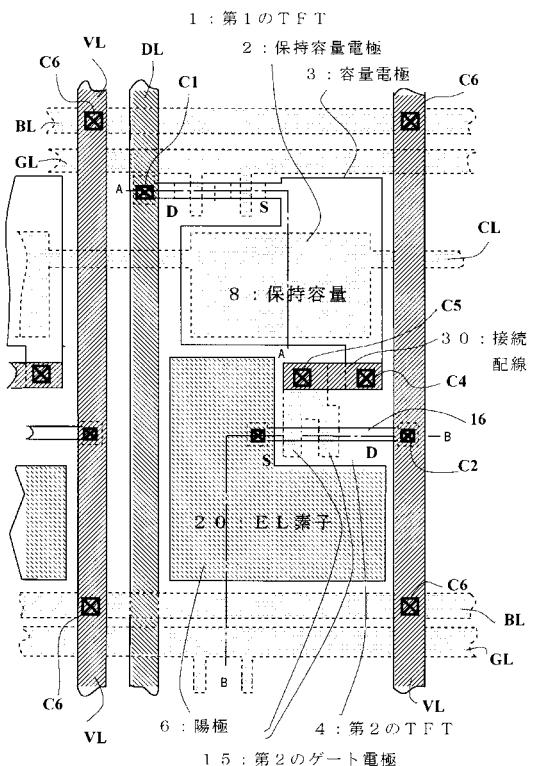

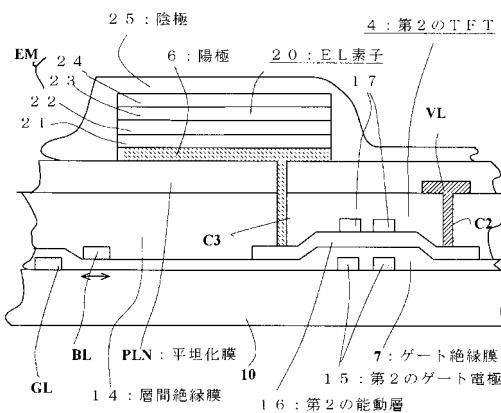

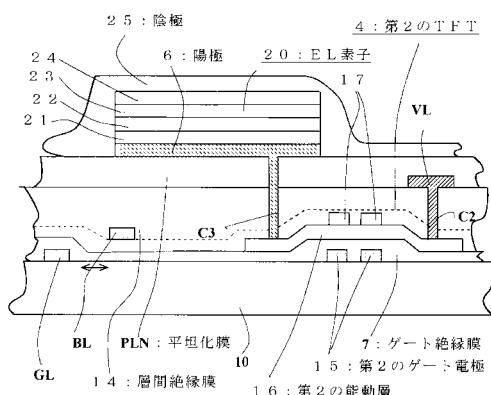

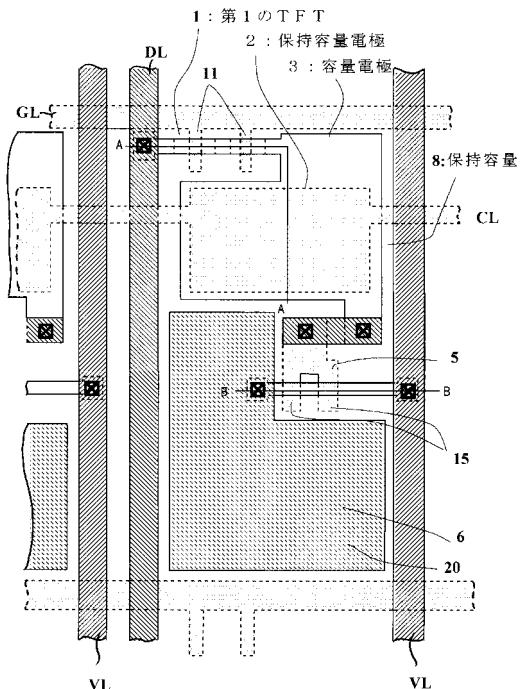

本発明のEL表示装置について説明する。図1は、EL表示装置の表示画素を平面図で示したもので、点線で囲まれ点でハッチングした領域は、ゲート材料で形成された領域、実線で囲まれハッチングされていない部分は、P-Si層、実線で囲まれ斜め点でハッチングした部分は、透明電極材料で成る部分である。更に実線で囲まれ斜め線でハッチングされた部分が、Alを主材料とする金属材料で形成された部分である。

10

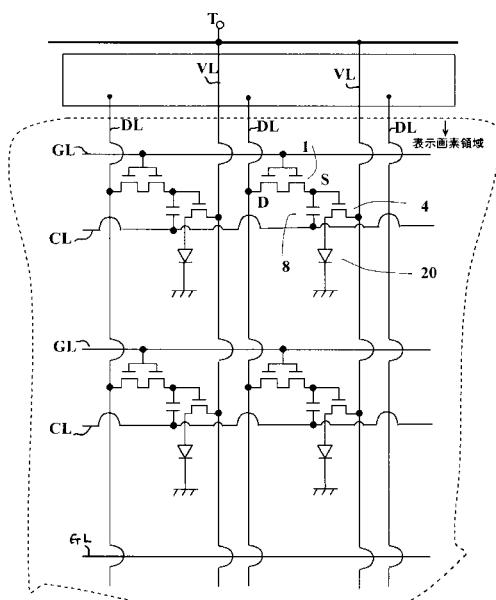

【0028】

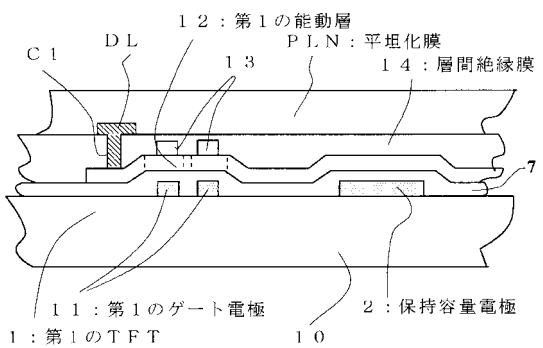

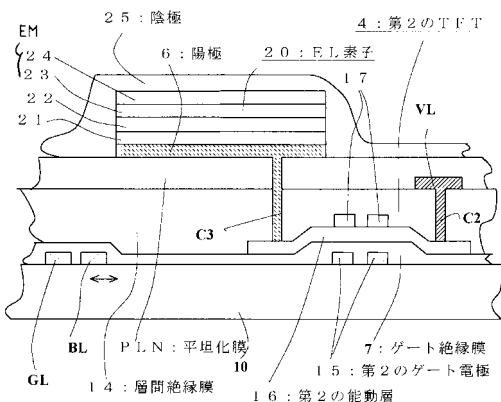

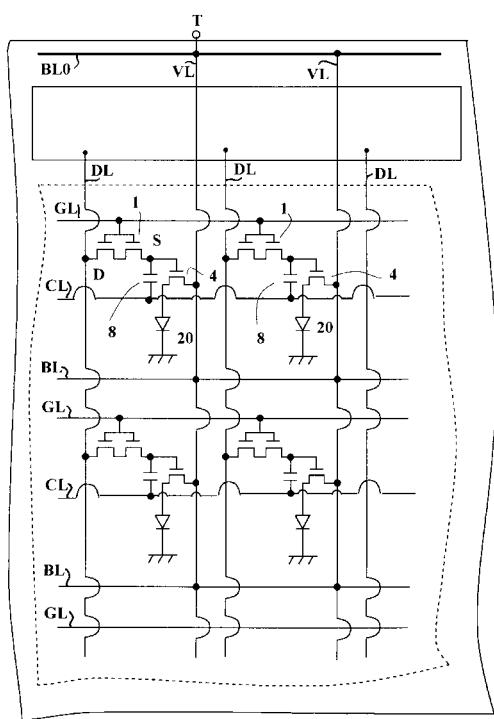

図2は、図1のA-A線断面図であり、図3は、B-B線断面図である。更に図4は、その等価回路図である。尚図4に於いて点線で囲まれた部分は、表示画素領域を示す。

【0029】

なお、本実施の形態においては、第1、第2のTFT1、4とともに、ボトムゲート型のTFTを採用しており、能動層としてp-Si膜を用いている。またゲート電極11、15は、ダブルゲート構造である。

20

【0030】

では、図1～図3を参照し、有機EL表示装置を具体的に説明していく。

【0031】

まず、少なくとも表面が絶縁性を有する透明基板10がある。本実施の形態では、EL素子を水分から保護するため、メタルキャップ(カン)がEL材料を封止するように上面に設置されている。尚、図においてメタルキャップは省略をした。このメタルキャップが設置されているため発光光は、前記透明基板10から取り出すため、基板10は、透明である必要があるが、発光光を上方から取り出す場合は、透明である必要はない。ここでは、ガラスや合成樹脂などから成る透明基板10を採用している。

30

【0032】

この透明基板10の上には、図1の一表示画素の上側辺に沿って、左右にゲートラインGLが設けられ、下側辺にはバイパスラインBLが左右に延在されている。また保持容量8の下層電極として作用する保持容量電極2が設けられると共に、この保持容量電極2をお互いにつなぐため、保持容量ラインCLが左右に延在されている。これら両ラインGL、CLは、同層でなるため、点でハッチングしてある。また材料としては、上層にP-Siを採用する理由からCrやTa等の高融点金属が採用される。ここでは、約1000～2000のCrがスパッタリングにて形成されている。またパターニングの際は、ステップカバレージが考慮され、側辺はテーパー形状に加工されている。

40

【0033】

続いて、全面にはゲート絶縁膜7と半導体層が積層されて形成されている。ここでは、前記ゲート絶縁膜7、能動層12、16および保持容量8の上層電極である容量電極3の材料であるa-Siも含めてプラズマCVDで形成されている。具体的には、下層より約500のSi窒化膜、約1300のSi酸化膜および約500のa-Siが連続プラズマCVDで形成される。

【0034】

このa-Siは、約400度の窒素雰囲気中で脱水素アニールが行われ、その後、エキシマレーザによりP-Si化される。また符号13、17は、Si酸化膜から成るストップ絶縁膜であり、能動層12、16のイオン注入時のマスクとなる。第1のTFT1は、このストップ絶縁膜13をマスクにしてP(リン)イオンが注入され、Nチャンネル型のソ

50

ース、ドレインが形成され、第2のTFT4は、B(ボロン)イオンが注入されてPチャンネル型のソース、ドレインが形成されている。

【0035】

また図1のように、ホトリソグラフィ技術によりパターニングされている。つまり第1のTFT1のP-Si層は、ゲートラインGLとドレインラインDLの左上交差部の下方で、ドレインラインDLと重畠し、ゲート電極11の上層を延在した後、保持容量電極2と重畠する容量電極3として延在されている。またこの容量電極3は、第2のTFT4のゲート電極15と電気的に接続するために用いられる接続配線30右端の下層に延在される。一方、第2のTFT4のP-Si層は、右側の駆動ラインVLの下層から第2のゲート電極15の上を延在し、透明電極から成る陽極6の下層に延在されている。

10

【0036】

そして全面には、層間絶縁膜14が形成されている。この層間絶縁膜14は、下から約1000のSi酸化膜、約3000のSi窒化膜、1000のSi酸化膜の三層構造が連続CVDで形成されている。この層間絶縁膜は、少なくとも一層有れば良い。膜厚もこれに限らない。

【0037】

次に、層間絶縁膜14の上層には、図1の斜め線でハッチングしたドレインラインDL、駆動ラインVLおよび接続配線30が形成される。当然コンタクトが形成され、ドレインラインDLと第1のTFT1の半導体層とのコンタクト孔C1、駆動ラインVLと第2のTFT4の半導体層とのコンタクト孔C2、接続配線30と容量電極3とのコンタクト孔C4は、それぞれの半導体層が露出されている。また接続配線30と第2のゲート電極15のコンタクト孔C5、本発明の特徴となる駆動ラインVLとバイパスラインBLのコンタクト孔C6は、前述のコンタクト孔とは異なり、ゲート絶縁膜が余分に積層されているため、更にエッチングされCrが露出されている。このライン材料は、下層に1000のMo、上層に7000のAlが積層された構造であり、Moは、バリア層である。尚コンタクト孔C3は、後述する。

20

【0038】

更に約2~3μmの平坦化膜PLNが全面に形成されている。この平坦化膜PLNの採用の理由の一つとして、従来例でも述べた有機EL用の膜にある。この膜は、第1のホール輸送層21、第2ホール輸送層22、発光層23及び電子輸送層24から成る。またホール輸送層は、一層から構成されても良い。従って、有機層が非常に薄い膜の積層体である。またEL素子は、電流駆動であるため、これらの膜厚が極めて均一に形成されないと、膜厚の薄い部分を介して電流が大量に流れ、その部分にひときわ輝く輝点が発生すると同時に、このポイントは、有機膜の劣化を発生し、最悪の場合破壊に至る。従って、この破壊を防止するには、陽極6を含む全面ができるだけ平坦である必要があり、ここではアクリル系の液状樹脂が塗布され、硬化後は平坦になる。もちろんこの平坦化膜PLNは、これに限らない事は言うまでもない。

30

【0039】

ここでは、陽極6と第2のTFT4のソースが接続されるため、平坦化膜PLNおよび層間絶縁膜14が開口され、第2の能動層16が露出されたコンタクト孔C3が形成されている。

40

【0040】

更に少なくとも陽極6上には、EL素子を構成する有機膜が形成されている。まず陽極6の上には、

M T D A T A (4,4-bis(3-methylphenylphenylamino)biphenyl)から成る第1ホール輸送層21、

及びT P D (4,4,4-tris(3-methylphenylphenylamino)triphenylamine)からなる第2ホール輸送層22、

キナクリドン(Quinacridone)誘導体を含むBebq2(10-ベンゾ[h]キノリノール-ベリリウム錯体)から成る発光層23及びBebq2から成る電子輸送層24からなる発

50

光素子層 E M、

マグネシウム・インジウム合金、Al と Ti の合金または LiF 等から成る陰極 25 がこの順番で積層形成された構造である。有機層の膜厚は、前述してあるのでそれを参照。また、陰極 25 は Al と Ti の合金を採用し、その膜厚は 1000 ~ 2000 である。

【0041】

ここで陽極 6 は、画素毎にパターニングされる必要があるが、陽極 6 の上の膜は、構造により区別される。

1：陽極 6 から陰極 25 まで画素毎にパターニングされる第 1 の構造

2：1 に於いて、陰極 25 は、パターニングされず、実質的に表示領域全域にベタで形成される第 2 の構造。

3：陽極 6 だけが図 1 の様に画素毎にパターニングされ、陽極の上層から陰極までは、表示領域全域に励精された前記ベタ構造の第 3 の構造。

【0042】

ただし、陰極 6 は、わざわざパターニングすることもない一般には全面ベタ構造を採用している。また図面では、陽極 6 と陰極 25 が短絡してゐる如く図示されているが、EL 素子の有機膜は、陽極 6 周辺も含み完全に覆われてゐる短絡は防止されている。これは従来例でも同じである。また陽極 6 のエッジをカバーするように、平坦化膜 PLN の上に更に別の平坦化膜が形成されても良い。

【0043】

更に、表示領域の EL 層、または全ての EL 層をカバーするメタルキャップが形成されている。EL 層は、水を吸湿すると劣化し、水の浸入に対して保護が必要となるからである。従って EL 層を劣化させず、耐湿性の高い膜、例えば樹脂膜でキャップの代用としても良いし、更にこの上にメタルキャップをしても良い。

【0044】

有機 EL 素子の発光原理および動作は、陽極 6 から注入されたホールと、陰極 25 から注入された電子とが発光層 EM の内部で再結合し、発光層 EM を形成する有機分子を励起して励起子を発生させる。この励起子が放射失活する過程で発光層から光が放たれ、この光が透明な陽極から透明絶縁基板を介して外部へ放出されて発光する。

【0045】

本発明の特徴は、バイパスライン BL にある。

【0046】

図 4 の等価回路からも明らかなように、駆動ライン VL は、点線で囲んだ表示領域内において、列方向に延在しており、列方向の各表示画素に接続されて駆動電流を供給している。この表示領域は、非常な長さになり、解決しようとする課題の欄にも述べたように抵抗分が発生するが、行方向に延在させたバイパスライン BL と接続させることで、隣接する表示画素には同電位の電圧が印加されることになる。また電流も格子状に形成された駆動ライン VL 及びバイパスライン BL により色々な方向から供給されることになり、各表示画素に設けられた有機 EL 素子に本来供給すべき電流を供給することができるので、前述した抵抗分による表示劣化、表示の明るさの低下を防止することができる。

【0047】

また図 3 のバイパスライン BL の様に、ゲートが形成された層に形成すれば、矢印で示す方向に移動が可能となる。つまり図 1 の陽極 6 とゲートライン GL との間に形成されたバイパスライン BL を見て説明すれば、バイパスライン BL は、陽極 6 と少なくとも一部を重畳させることができ、重畳させることにより、バイパスライン BL を配置することによる面積増大を抑制することができる。またゲートライン GL と陽極 6 の間には、ゲート絶縁膜 7 と層間絶縁膜 14 および平坦化膜 PLN が介在されるので、この間に発生する寄生容量は、殆ど無視することができる。

【0048】

またバイパスライン BL の位置は、駆動ライン VL よりも下層に位置すれば良く、図 5、図 6 に他の例を説明する。

10

20

30

40

50

## 【0049】

図5は、バイパスラインB Lがゲート絶縁膜7の上に形成されるものである。ここで工程を簡略化する場合は、P - S iで構成されるが、前述した高融点金属でも良い。

## 【0050】

図6は、バイパスラインB Lが層間絶縁膜の層間に形成されたもので、ここではP - S iが形成された後であるので、製造工程の温度上昇もそれほど厳しくないため、バイパスラインB Lは、A 1を主成分とする材料や高融点金属材料、P - S iを採用できる。層間絶縁膜は、下層からS i酸化膜、S i窒化膜、S i酸化膜が形成されるので、これらの間に前記バイパスラインB Lを配置することができる。もちろん陽極との重畠も可能である。しかし上層に配置するに従い、寄生容量の増大は免れない。尚層間絶縁膜14内に形成される点線は、層間の界面を示すものである。 10

## 【0051】

更にバイパスラインB Lの挿入本数について述べる。つまり図4において、バイパスラインB Lの本数は、少なくとも1本形成されれば、抵抗の減少は抑制できる。しかし各画素毎に配置すれば、抵抗の分布、電圧の分布が更に均一となり本来流れる電流、すなわち発光すべき輝度をより忠実に再現させることができる。

## 【0052】

以上、ボトムゲート型構造で説明してきたが、本発明は、トップゲート型構造でも採用できる。トップゲート型TFTの場合は、透明基板上には、例えばP - S iから成る能動層、ゲート絶縁膜、ゲート、層間絶縁膜、メタル配線が積層され（この上層はボトムゲート型構造と実質同じ構造）るため、透明基板上では、C rや高融点金属で、ゲート絶縁膜の上には前記A 1材料、高融点金属材料で、配線が形成できる。 20

## 【0053】

最後に、表示画素領域の外側に配置されるバイパスラインB L 0について述べる。図4で、一番外側の実線は、E L表示装置の外形であり、太い実線は駆動電源と接続されたバイパスラインB L 0で、更にその下に示す矩形は、駆動回路が形成された領域である。つまり表示領域から透明基板の外形までの形態を模式的に示している。ここで駆動回路はP - S iで作り込まれている。図からも判るようにドレインラインD Lは、駆動回路形成領域で回路と接続されて一端終結しており、駆動回路形成領域と外形の間は、ドレインラインD Lが形成されていない。従ってドレインラインD Lとの交差もなく図のようにバイパスラインB L 0が左右に太く延在できるスペースを有している。しかもバイパスラインB L 0は、ドレインラインD Lまたは駆動ラインV Lと同層で形成でき、A 1を主成分とする材料で配線が形成できる。従ってバイパスラインB L 0自身の抵抗を大きく低下させることができ、駆動ラインV Lの抵抗値をより低下させることができると同時に安定した電圧を供給できる。 30

## 【0054】

上述の実施の形態においては、半導体膜としてp - S i膜を用いたが、微結晶シリコン膜又は非晶質シリコン膜等の半導体膜を用いても良い。

## 【0055】

更に、上述の実施の形態においては、有機E L表示装置について説明したが、本発明はそれに限定されるものではなく、発光層が無機材料から成る無機E L表示装置にも適用が可能であり、同様の効果が得られる。 40

## 【0056】

## 【発明の効果】

以上の説明からも明らかのように、第1に、駆動ラインのそれぞれを、延在方向と交差する方向に設け、駆動ラインと電気的に接続され、前記駆動ラインよりも下層の位置にバイパスラインを設けることで、駆動ラインは、格子状に形成されたことになり、駆動電源入力端子から遠ざかっても、抵抗値の下がる割合は、従来のものよりも抑制させる事ができる。

## 【0057】

10

20

30

40

50

また駆動ラインとバイパスラインは、本来同層にて形成できるが、その分バイパスラインの配置面積を必要とする。しかしバイパスラインを駆動ラインの下層に置くことで、例えば陽極と重畠させることができる。しかも陽極とバイパスラインとの間には、かなり厚く絶縁層が形成されるため、寄生容量の問題も抑制される。

【0058】

更には、前述したようにバイパスラインの少なくとも一部を前記陽極と重畠させることで、バイパスラインの配置に依って拡大する表示領域の拡大化を抑制させることができる。また抑制させた分、他の構成要素を拡大させることもできる。

【0059】

また、バイパスラインを、前記表示画素毎に形成し、前記駆動ラインとの重畠部にコンタクトを形成する事で、各表示画素のムラをより抑制させることができる。

10

【0060】

従って、駆動ラインの長さによる抵抗の増大を低減し、本来供給されるべき電流を各表示画素のEL素子に供給することができ、暗い表示になることを防止することができるEL表示装置を得ることができると同時に、EL表示領域の拡大化も抑止することができる。

【図面の簡単な説明】

【図1】本発明のEL表示装置の表示画素の平面図である。

【図2】図1のA-A線の断面図である。

【図3】図1のB-B線の断面図である。

【図4】本発明のEL表示装置の等価回路図である。

20

【図5】図3のバイパスラインBLの配置位置を説明する図である。

【図6】図3のバイパスラインBLの配置位置を説明する図である。

【図7】従来のEL表示装置の表示画素の平面図である。

【図8】従来のEL表示装置の等価回路図である。

【図9】図7のA-A線の断面図である。

【図10】図7のB-B線の断面図である。

【符号の説明】

|    |           |    |

|----|-----------|----|

| 1  | 第1のTFT    |    |

| 2  | 保持容量電極    |    |

| 3  | 容量電極      | 30 |

| 4  | 第2のTFT    |    |

| 6  | 陽極        |    |

| 7  | ゲート絶縁膜    |    |

| 8  | 保持容量      |    |

| 14 | 層間絶縁膜     |    |

| 20 | EL素子      |    |

| GL | ゲートライン    |    |

| DL | ドラインライン   |    |

| CL | 保持容量ライン   |    |

| VL | 駆動ラインVL   | 40 |

| BL | バイパスラインBL |    |

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【 図 6 】

【図7】

【 図 8 】

【 図 9 】

【 囮 1 0 】

---

フロントページの続き

(56)参考文献 国際公開第98/036407 (WO, A1)

特開平10-172763 (JP, A)

特開平10-239699 (JP, A)

特開平11-064889 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09F 9/00 - 9/46

H01L 27/32

H01L 51/50

H05B 33/00 - 33/28