(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5175131号

(P5175131)

(45) 発行日 平成25年4月3日(2013.4.3)

(24) 登録日 平成25年1月11日(2013.1.11)

(51) Int.Cl.

G05F 3/30 (2006.01)

F 1

G 05 F 3/30

請求項の数 10 (全 17 頁)

(21) 出願番号 特願2008-114930 (P2008-114930)

(22) 出願日 平成20年4月25日 (2008.4.25)

(65) 公開番号 特開2009-265954 (P2009-265954A)

(43) 公開日 平成21年11月12日 (2009.11.12)

審査請求日 平成23年4月13日 (2011.4.13)

(73) 特許権者 000233169

株式会社日立超エル・エス・アイ・システムズ

東京都国分寺市東恋ヶ窪三丁目1番地1

(74) 代理人 100081938

弁理士 德若 光政

(72) 発明者 長野 知博

東京都小平市上水本町五丁目22番1号

株式会社日立超エル・エス・アイ・システムズ内

(72) 発明者 田中 均

東京都小平市上水本町五丁目22番1号

株式会社日立超エル・エス・アイ・システムズ内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

C M O S 製造プロセスで形成されたバイポーラトランジスタとM O S F E T を含む回路素子で構成された参考基準電圧発生回路を有する半導体集積回路装置であって、上記参考基準電圧発生回路は、

エミッタが基準電位に接続された第1バイポーラトランジスタと、

上記第1バイポーラトランジスタのエミッタ面積よりも大きなエミッタ面積を有し、エミッタが第1抵抗素子を介して上記基準電位に接続され、ベースが上記第1バイポーラトランジスタのベースに接続された第2バイポーラトランジスタと、

上記第1バイポーラトランジスタのコレクタ電圧とベース電圧を一対の入力とし、出力信号を上記第1及び第2バイポーラトランジスタのベースに帰還伝達する構成によって上記第1バイポーラトランジスタのベース電圧とコレクタ電圧が等しくなる状態を維持する第1差動增幅回路と、

コレクタとベースとが結合され、エミッタと上記基準電位との間に第2抵抗素子が設けられ、上記結合されたコレクタ・ベースと上記基準電位との間に第3抵抗素子が設けられた第3バイポーラトランジスタと、

上記第1バイポーラトランジスタのコレクタ電圧と第2バイポーラトランジスタのコレクタの電圧を一対の入力とする第2差動增幅回路と、

上記第2差動增幅回路の出力電圧がゲートに供給され、ソースが第4ないし第6抵抗素子を介してそれぞれ電源電位に接続され、上記第1ないし第3バイポーラトランジスタの

10

20

コレクタ電流をそれぞれ形成する第1ないし第3MOSFETと

を有し、

参照基準電圧が上記第3バイポーラトランジスタの結合されたコレクタ・ベースから出力され、

上記第1抵抗素子は、エミッタ面積の異なる上記第1バイポーラトランジスタと上記第2バイポーラトランジスタとの間に生じるエミッタ電流密度の違いに対応して発生するエミッタ・ベース間電圧の差分を補償する大きさの抵抗値に設定され、

上記第1抵抗素子と第2抵抗素子は、上記参照基準電圧に生じる温度依存性を相殺する抵抗比に設定され、

上記第4ないし第6抵抗素子は、上記第1ないし第3MOSFETを含む電流路間に生じるバラツキに起因する上記参照基準電圧の変動を抑制する大きさの抵抗値に設定されてなる

半導体集積回路装置。

【請求項2】

請求項1において、

ソースが上記電源電位に接続され、ゲートが上記第1差動增幅回路の出力に接続され、ドレインが上記第1及び第2バイポーラトランジスタのベースに共通接続され、上記第1差動增幅回路の上記出力信号で制御されるドレイン電流を上記共通結合されたベースに帰還伝達する構成に接続された第4MOSFETと、

上記第4MOSFETで検出された上記第1及び第2バイポーラトランジスタのベース電流に対応して、上記第3バイポーラトランジスタの上記コレクタ・ベース結合部に供給される電流の変動を抑制する電流ミラー回路と、を更に有する

半導体集積回路装置。

【請求項3】

C MOS製造プロセスで形成されたバイポーラトランジスタとMOSFETを含む回路素子で構成された参照基準電圧発生回路を有する半導体集積回路装置であって、

上記参照基準電圧発生回路は、

エミッタが基準電位に接続された第1バイポーラトランジスタと、

上記第1バイポーラトランジスタのエミッタ面積よりもエミッタ面積が大きく形成され、エミッタが第1抵抗素子を介して上記基準電位に接続され、ベースが上記第1バイポーラトランジスタのベースに接続された第2バイポーラトランジスタと、

上記第1バイポーラトランジスタのコレクタ電圧とベース電圧を一対の入力とし、出力信号を上記第1及び第2バイポーラトランジスタのベースに帰還伝達する構成によって上記第1バイポーラトランジスタのベース電圧とコレクタ電圧が等しくなる状態を維持する第1差動增幅回路と、

コレクタとベースとが結合され、エミッタと上記基準電位との間に第2抵抗素子が設けられ、上記結合されたコレクタ・ベースと上記基準電位との間に第3抵抗素子が設けられた第3バイポーラトランジスタと、

上記第1バイポーラトランジスタのコレクタ電圧と上記第2バイポーラトランジスタのコレクタ電圧を一対の入力とする第2差動增幅回路と、

上記第2差動增幅回路の出力電圧がゲートに共通に供給され、ソースがそれぞれ電源電位に接続され、上記第1ないし第3バイポーラトランジスタのコレクタに供給される電流が等しくなるような電流をそれぞれ形成する第1ないし第3MOSFETと

を有し、

参照基準電圧が上記第3バイポーラトランジスタの結合されたコレクタ・ベースから出力され、

上記第1抵抗素子は、エミッタ面積の異なる上記第1バイポーラトランジスタと上記第2バイポーラトランジスタとの間に生じるエミッタ電流密度の違いに対応して発生するエミッタ・ベース間電圧の差分を補償する大きさの抵抗値に設定され、

上記第1抵抗素子と第2抵抗素子は、上記参照基準電圧に生じる温度依存性を相殺する

10

20

30

40

50

抵抗比に設定されてなり、

ソースが上記電源電位に接続され、ドレンが上記第1及び第2バイポーラトランジスタのベースに接続され、上記第1差動增幅回路の出力電圧がゲートに供給された第4MOSFETと、

上記第4MOSFETで検出された上記第1及び第2バイポーラトランジスタのベース電流に対応して、上記第3バイポーラトランジスタの上記コレクタ・ベース結合部に供給される電流の変動を抑制する電流ミラー回路と、を更に有する

半導体集積回路装置。

【請求項4】

請求項3において、

上記第1乃至第3MOSFETのソースが第4乃至第6抵抗素子を介してそれぞれ電源電位に接続され、上記第4乃至第6抵抗素子は、上記製造プロセスに起因して上記第1乃至第3MOSFETの間に生じるしきい値電圧のバラツキを抑制する大きさの抵抗値に設定されてなる

半導体集積回路装置。

【請求項5】

請求項1乃至4のいずれかにおいて、

上記CMOS製造プロセスは、P型基板上にN型ウェル領域を形成する段階と、上記N型ウェル領域内にP型ウェル領域を形成する段階と、上記P型ウェル領域内にNチャネルMOSFETのソース、ドレンを形成するためのN型領域を形成する段階とを含み、

上記第1ないし第3バイポーラトランジスタは、上記N型ウェル領域を形成する段階で形成されたN型ウェル領域をコレクタとし、上記P型ウェル領域を形成する段階で上記N型コレクタ領域内に形成されるP型領域をベースとし、上記ソース、ドレンを形成するためのN型領域を形成する段階で上記P型ベース領域に形成されたN型領域をエミッタとするものであり、

上記第1ないし第3MOSFETはそれぞれ、上記N型ウェル領域上に形成されたP型領域をソース、ドレンとするPチャネルMOSFETである

半導体集積回路装置。

【請求項6】

請求項2乃至4のいずれかにおいて、

上記電流ミラー回路は、

上記第4MOSFETと、

ソースが上記電源電位に接続され、ゲートが上記第4MOSFETのゲートに共通接続され、第4MOSFETに流れる電流に対し同じ電流を流すように電流ミラー形態に接続された第5MOSFETと、

上記第5MOSFETのドレンと上記基準電位の間に接続された第6MOSFETと、

上記第2バイポーラトランジスタと第1抵抗素子で構成される電流路に対し並列接続された第7MOSFETと、

上記第1バイポーラトランジスタの電流路に対し並列接続された第8MOSFETとを含み、

上記第6ないし第8MOSFETのゲートを上記第5MOSFETのドレンに共通接続し、上記第7及び第8MOSFETを上記第6MOSFETに対しそれぞれ半分の電流を流す電流ミラー形態に接続して構成されたものである

半導体集積回路装置。

【請求項7】

請求項2乃至4のいずれかにおいて、

上記電流ミラー回路は、

上記第4MOSFETと、

ソースが上記電源電位に接続され、ゲートが上記第4MOSFETのゲートに共通接続

10

20

30

40

50

され、第4MOSFETに対し半分のサイズに形成され、ドレイン電流を電流ミラー形態で上記第3バイポーラトランジスタのコレクタ・ベース結合部に供給する第5MOSFETとを有する

半導体集積回路装置。

【請求項8】

請求項7において、

上記第4及び第5MOSFETのソースはそれぞれ第7及び第8抵抗素子を介して上記電源電位に接続されている

半導体集積回路装置。

【請求項9】

請求項2乃至4のいずれかにおいて、

上記電流ミラー回路は、

上記第4MOSFETと、

ソースが上記電源電位に接続され、ゲートが上記第4MOSFETのゲートに共通接続され、第4MOSFETと同じサイズに形成され、ドレイン電流を電流ミラー形態で供給する第5MOSFETと、

上記第5MOSFETのドレインと上記基準電位の間に接続された第6MOSFETと、

上記第2バイポーラトランジスタと第1抵抗素子で構成される電流路に対し並列接続された第7MOSFETと、

上記第1バイポーラトランジスタの電流路に対し並列接続された第8MOSFETとを有し、

上記第6乃至第8MOSFETのゲートを上記第5MOSFETのドレインに共通接続し、上記第7及び第8MOSFETを上記第6MOSFETに対し電流ミラー形態に接続して構成されたものである

半導体集積回路装置。

【請求項10】

請求項6ないし9のいずれかにおいて、

上記CMOS製造プロセスは、P型基板上にN型ウェル領域を形成する段階と、上記N型ウェル領域内にP型ウェル領域を形成する段階と、上記P型ウェル領域内にNチャネルMOSFETのソース、ドレインを形成するためのN型領域を形成する段階とを含み、

上記第1ないし第3バイポーラトランジスタは、上記N型ウェル領域を形成する段階で形成されたN型ウェル領域をコレクタとし、上記P型ウェル領域を形成する段階で上記N型コレクタ領域内に形成されるP型領域をベースとし、上記ソース、ドレインを形成するためのN型領域を形成する段階でP型ベース領域内に形成されたN型領域をエミッタとするものであり、

上記第1ないし第5MOSFETは、上記N型ウェル領域上に形成されたP型のソース、ドレインが形成されたPチャネルMOSFETである

半導体集積回路装置。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体集積回路装置に関し、例えば三重ウェル構造のCMOSプロセスで形成され、基準電圧発生回路を有するものに利用して有効な技術に関するものである。

【背景技術】

【0002】

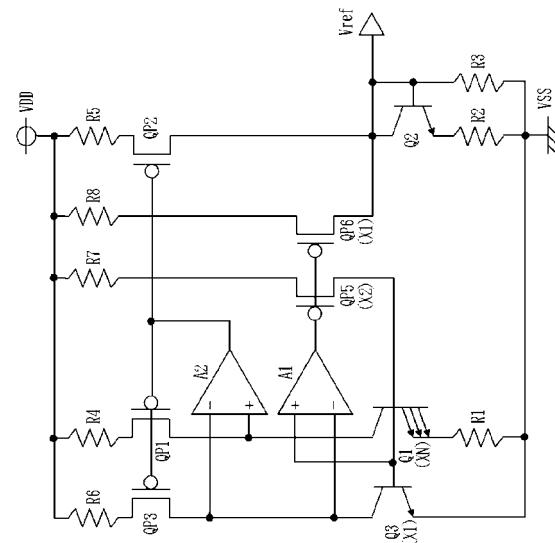

CMOSプロセスのバンドギャップ基準電圧発生回路として、例えば2007 Symposium on VLSI Circuits Digest of Technical Papers pp.96-97 (A Trimmig-Free CMOS Bandgap-Reference Circuit with Sub-1-V-Supply Voltage Operation)がある。同文献の基準電圧発生回路を図10に示す。同図に示された基準電圧発生回路は、差動增幅回路A1とA2

10

20

30

40

50

を用いて、差動増幅回路A1の持つオフセット電圧が基準電圧Vrefに与える影響を抑えるようにするものである。この構成では、バイポーラトランジスタQ1、Q3のコレクタ電流がコレクタ電位にほとんど依存しない活性化領域で動作させることで、差動増幅回路A1の差動入力部におけるオフセット電圧の影響を抑えることが出来る。

【非特許文献1】2007 Sympsium on VLSI Circuits Digest of Technical Papers pp.96-97 (A Trimmig-Free CMOS Bandgap-Reference Circuit with Sub-1-V-Supply Voltage Operation)

【発明の開示】

【発明が解決しようとする課題】

【0003】

10

本願発明者においては、上記非特許文献1に示された基準電圧発生回路において、素子の微細化等に伴う素子のプロセスバラツキにより次のような問題を有することを見い出した。CMOSプロセスを用いて低電圧・高精度の基準電圧（バンドギャップリファレンス）を実現するためには、差動（演算）増幅回路や電流ミラー回路などのペア素子におけるオフセット電圧による影響を抑えることが重要である。図11には、本願発明者により検討された前記図10の等価回路が示されている。差動増幅回路A1を構成する差動MOSFETのペア素子等によるオフセット電圧V1に関しては、図12に示したオフセット電圧V1と基準電圧Vrefとの特性のように改善されていることが認められる。

【0004】

20

しかしながら、図11の等価回路に示したように、図10の基準電圧発生回路においては、前記差動増幅回路A1の差動素子の他にも電流ミラー回路を構成するPチャネルMOSFETQ1～Q4のようなペア素子においても、それぞれオフセット電圧V2～V5が存在するはずである。このようなオフセット電圧V2～V5による基準電圧Vrefに対する影響を本願発明者によるコンピュータシミュレーションにより調べると図12の特性V2～V5のようになることが判明した。

【0005】

30

図12においては、上記各MOSFETQ1～Q4のしきい値電圧が目標値（0mV）に対してそれぞれ-10mV～+10mVの範囲で変動したことを想定し、それぞれのオフセット電圧V2～V5が基準電圧Vrefに与える影響を検証したものである。図12からは、MOSFETQ1のしきい値電圧のバラツキ（オフセット電圧V2）が基準電圧Vrefに最も大きな影響を及ぼし、次いでMOSFETQ2のしきい値電圧のバラツキ（V3）の影響が大きく、MOSFETQ4のしきい値電圧のバラツキ（V5）の影響は軽微であることが判る。つまり、前記図10の基準電圧発生回路においては、これら電流ミラー回路を構成するPチャネルMOSFETQ1～Q3のしきい値電圧のバラツキ（V2～V4）により大きく上記基準電圧Vrefが変動してしまうという問題を有する。

【0006】

40

前記図10に示した基準電圧発生回路においては、CMOSプロセスで形成されるバイポーラトランジスタの電流増幅率のプロセスバラツキに対しては何の配慮もなされていない。バイポーラトランジスタQ1～Q3は、同文献にも示されているように3重（トリプル）ウェル構造のNチャネルMOSFETを形成する半導体領域を利用して縦型構造のNPNトランジスタとされる。このトランジスタ構造は、NチャネルMOSFETのソース、ドレインを形成するための拡散層をエミッタとし、上記ソース、ドレイン領域が形成されるP型ウェル領域をベース領域とし、上記P型ウェルをP型基板から電気的に分離するための深い深さのN型ウェルをコレクタ領域として利用する。

【0007】

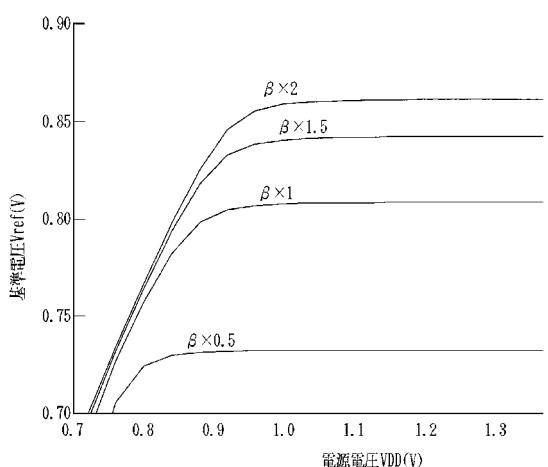

このため、通常のバイポーラトランジスタの製造プロセスで形成されるトランジスタに比べ、上記CMOSプロセスで形成されるトランジスタQ1～Q3の電流増幅率が大きく変動する。例えば、設計値に対して半分（×0.5）から2倍（×2）の範囲のような大きなバラツキを示すものと予測される。このような電流増幅率のバラツキ×

50

0.5 ~  $\times 2$  による基準電圧  $V_{ref}$  に対する影響を本願発明者によるコンピュータシミュレーションにより調べると図 13 の特性  $\times 0.5 ~ \times 2$  のように基準電圧  $V_{ref}$  の変動が生じることが判明した。

【0008】

この発明の 1 つの目的は、素子のプロセスバラツキの影響を抑制した基準電圧発生回路を有する半導体集積回路装置を提供することある。この発明の他の目的は、CMOS プロセスにより形成され、素子プロセスバラツキの影響を抑制し、低電圧動作に適した基準電圧発生回路を提供することにある。この発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

10

【0009】

本願において開示される 1 つの実施例は、以下の通りである。半導体集積回路装置に形成される基準電圧発生回路は、第 1 トランジスタとそれよりも大きなエミッタ面積を持つようにされた第 2 トランジスタを有する。第 1 差動増幅回路は、上記第 1 トランジスタのベースとコレクタ電圧が等しくなるように上記第 1 トランジスタと第 2 トランジスタのベース電流を形成する。第 1 抵抗素子は、上記第 2 トランジスタのエミッタと基準電位との間に設けられ、上記第 1 トランジスタと第 2 トランジスタとのエミッタ電流密度に対応して発生されたシリコンバンドギャップ電圧が印加される。第 3 トランジスタは、コレクタとベースとが結合され、エミッタと上記基準電位との間に第 2 抵抗素子が設けられ、上記結合されたコレクタ、ベースと上記基準電位との間に第 3 抵抗素子が設けられる。第 2 差動増幅回路は、上記第 1 と第 2 トランジスタのコレクタの電圧を受け、それが等しくなるよう上記第 1 ないし第 3 トランジスタのコレクタ電流をそれぞれ形成する第 1 ないし第 3 MOSFET のゲート電圧を制御する。上記第 1 抵抗素子と第 2 抵抗素子は、上記第 3 トランジスタの結合されたコレクタ、ベースから出力される基準電圧が温度依存性を持たないような抵抗比に設定される。上記第 1 ないし第 3 MOSFET のソース側に第 4 ないし第 6 抵抗素子をそれぞれ有する。

20

【0010】

本願において開示される他 1 つの実施例は、以下の通りである。半導体集積回路装置に形成される基準電圧発生回路は、第 1 トランジスタとそれよりもエミッタ面積が大きく形成された第 2 トランジスタとを有する。第 1 差動増幅回路は、上記第 1 トランジスタのベースとコレクタ電圧が等しくなるよう上記第 1 と第 2 トランジスタのベース電流を形成する。第 1 抵抗素子は、上記第 2 トランジスタのエミッタと基準電位との間に設けられ、上記第 1 トランジスタと第 2 トランジスタとのエミッタ電流密度に対応して発生されたシリコンバンドギャップ電圧が印加される。第 3 トランジスタは、コレクタとベースとが結合され、エミッタと上記基準電位との間に第 2 抵抗素子が設けられ、上記結合されたコレクタ、ベースと上記基準電位との間に第 3 抵抗素子が設けられる。第 2 差動増幅回路は、上記第 1 と第 2 トランジスタのコレクタの電圧を受け、それが等しくなるよう上記第 1 ないし第 3 トランジスタのコレクタ電流をそれぞれ形成する第 1 ないし第 3 MOSFET のゲート電圧を制御する。上記第 2 抵抗素子と第 3 抵抗素子は、上記第 3 トランジスタの結合されたコレクタ、ベースから出力される。上記第 1 抵抗素子と第 2 抵抗素子は、基準電圧が温度依存性を持たないような抵抗比に設定される。上記第 1 、第 2 トランジスタのベース電流は、上記第 1 差動増幅回路の出力電圧がゲートに供給された第 4 MOSFET のドレイン電流により形成され、上記第 4 MOSFET で検出された第 1 、第 2 トランジスタのベース電流に対応して、上記第 3 トランジスタのコレクタに供給される電流を増加させる電流ミラー回路が設けられる。

30

【発明の効果】

【0011】

第 1 ないし第 3 MOSFET のソース側に設けられた第 4 ないし第 6 抵抗素子により、これら第 1 ないし第 3 MOSFET に発生するオフセット電圧の影響を抑制することができる。電流ミラー回路により、上記第 1 、第 2 トランジスタのベース電流に対応して、上

40

50

記第3トランジスタのコレクタに供給される電流を増加させることにより、第3トランジスタにおける電流増幅率のバラツキの影響を抑制することができる。

【発明を実施するための最良の形態】

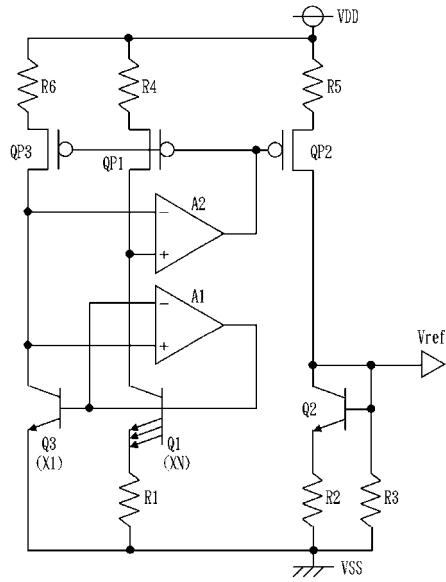

【0012】

図1には、この発明に係る基準電圧発生回路の一実施例の回路図が示されている。この実施例の基準電圧発生回路は、特に制限されないが、公知の3重ウェル構造を持つCMOS回路が形成される半導体集積回路装置において搭載される。

【0013】

トランジスタQ1ないしトランジスタQ3は、3重ウェル構造のCMOS回路を利用して形成されるNPN型バイポーラトランジスタである。例えば前記非特許文献1と同様に、P型基板上に形成された深い深さのN型ウェル領域をコレクタとし、上記深い深さのN型ウェル領域に形成されたP型ウェル領域をベースとし、上記P型ウェル領域に形成されたN型領域をエミッタとする縦型構造とされる。

10

【0014】

トランジスタQ3のエミッタ面積を1( $\times 1$ )とすると、トランジスタQ1のエミッタ面積は、N倍( $\times N$ )のように大きく形成される。トランジスタQ1とQ3のベースは、共通に接続される。トランジスタQ3のエミッタは、回路の接地電位(0V)VSSが与えられ、トランジスタQ1のエミッタと基準電位VSSとの間に抵抗R1が設けられる。トランジスタQ1とQ3に流れる電流を同一とし、トランジスタQ1とQ3のエミッタ電流密度差に対応したバンドギャップ電圧(トランジスタQ1とQ3のベース、エミッタ間電圧差)が上記抵抗R1に流れるようにされる。

20

【0015】

上記トランジスタQ1とQ3に同じ電流が流れるようにするために、差動増幅回路A1、A2及びPチャネルMOSFETQ1～Q3が設けられる。差動増幅回路A1の正相入力(+)と負相入力(-)には、トランジスタQ3のコレクタ電圧とベース電圧が供給される。この差動増幅回路A1の出力電流は、上記トランジスタQ1とQ3のベース電流とされる。これにより、差動増幅回路A1は、上記トランジスタQ3のコレクタとベースとが同電位となるようにトランジスタQ1、Q3のベース電流を形成する。

【0016】

差動増幅回路A2の正相入力(+)と負相入力(-)には、トランジスタQ1のコレクタ電圧とトランジスタQ1のコレクタ電圧が供給される。この差動増幅回路A2の出力電圧は、PチャネルMOSFETQ1ないしQ3のゲートに供給される。上記PチャネルMOSFETQ1とQ3のドレイン電流は、上記トランジスタQ1とQ3のコレクタに供給される。これにより、差動増幅回路A2とMOSFETQ1、Q3は、上記トランジスタQ1とQ3のコレクタが同電位となるようにMOSFETQ1、Q3のゲート電圧を形成する。MOSFETQ1ないしQ3は、同じサイズに形成されており、上記抵抗R1には上記バンドギャップ電圧に対応した定電流が流れ、これに対応して上記差動増幅回路A1、A2及びPチャネルMOSFETQ1ないしQ3により上記トランジスタQ1とQ3のベース、コレクタ電圧及びコレクタ電流が等しくなるよう設定される。

30

【0017】

この実施例では、特に制限されないが、回路素子数や消費電流の低減のために前記非特許文献1に示された図10の基準電圧発生回路のMOSFETQ4、トランジスタQ4が省略される。図10の回路では、差動増幅回路A1は、トランジスタQ3と同じ構成にされ、コレクタ、ベースが接続されたトランジスタQ4のベース電圧とトランジスタQ1のコレクタ電圧とを受けて両者が等しくなるように動作している。このことに着目し、図1の実施例では、直接的にトランジスタQ1のコレクタ電圧とベース電圧とを差動増幅回路A1に入力することにより、両者が一致させるようトランジスタQ1、Q3のベース電流を形成するものである。

【0018】

40

50

上記抵抗 R 1 で形成された定電流の温度補償のために、言い換えるならば、出力される基準電圧  $V_{ref}$  の温度補償のためにトランジスタ Q 2、抵抗 R 2, R 3 及び P チャネル MOSFET Q P 2 が設けられる。上記トランジスタ Q 2 は、コレクタとベースが接続され、その接続点から基準電圧  $V_{ref}$  が出力される。上記トランジスタ Q 2 のエミッタと基準電位  $V_{SS}$ との間には、上記抵抗 R 2 が設けられる。上記トランジスタ Q 2 の接続されたコレクタ、ベースと基準電位  $V_{SS}$ との間に抵抗 R 3 が設けられる。上記トランジスタ Q 2 のコレクタには、上記 P チャネル MOSFET Q P 2 のドレイン電流が供給される。上記抵抗 R 2 と R 3 は、上記基準電圧  $V_{ref}$  の温度補償のために、言い換えるならば、基準電圧  $V_{ref}$  が温度依存性を持たないような抵抗比に設定される。

## 【0019】

10

この実施例回路では、上記 P チャネル MOSFET Q P 1 ~ Q P 3 におけるしきい値電圧のバラツキに対応したオフセット電圧（後述する図 4 に示す  $V_2$  ~  $V_4$ ）による基準電圧  $V_{ref}$  の変動を抑制するために、ソースと電源電圧  $V_{DD}$ との間に抵抗 R 4 ~ R 6 がそれぞれ設けられる。

## 【0020】

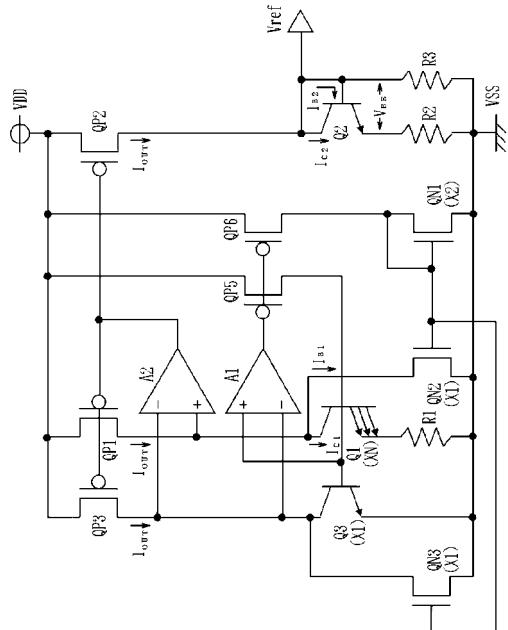

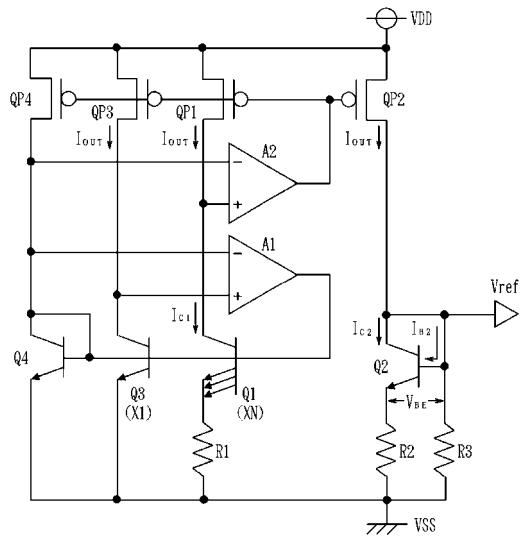

図 2 には、この発明に係る基準電圧発生回路の他の一実施例の回路図が示されている。この実施例は、前記図 1 と同様な構成にされたトランジスタ Q 1 ~ Q 3、抵抗 R 1 ~ R 3、差動增幅回路 A 1, A 2 及び P チャネル MOSFET Q P 1 ~ Q P 3 を有する基準電圧発生回路において、トランジスタ Q 1 ~ Q 3 における電流増幅率のバラツキによる基準電圧  $V_{ref}$  の変動を抑制するために、P チャネル MOSFET Q P 5, Q P 6 及び N チャネル MOSFET Q N 1 ~ Q N 3 が設けられる。

20

## 【0021】

上記 P チャネル MOSFET Q P 5 は、ゲートに上記差動增幅回路 A 1 の出力電圧が供給され、ソースには上記電源電圧  $V_{DD}$  が印加され、ドレイン電流が上記トランジスタ Q 1 と Q 3 のベースに供給される。これにより、MOSFET Q P 5 は、上記トランジスタ Q 1 と Q 3 に流れる合成ベース電流の検出素子として動作する。P チャネル MOSFET Q P 6 は、上記 MOSFET Q P 5 と同じサイズにされ、上記 P チャネル MOSFET Q P 5 とゲート及びソースが共通接続されることにより、電流ミラー形態にされて同じ電流を流すようにされる。この電流は、基準電位  $V_{SS}$  側に設けられた N チャネル MOSFET Q N 1 ~ Q N 3 で構成される電流ミラー回路に入力される。

30

## 【0022】

つまり、上記 P チャネル MOSFET Q P 6 のドレイン電流は、ダイオード接続された N チャネル MOSFET Q N 1 のドレインに供給される。この N チャネル MOSFET Q N 1 と電流ミラー形態にされた N チャネル MOSFET Q N 2 と Q N 3 は、そのサイズが MOSFET Q N 1 の 1/2 に設定されて、上記 MOSFET Q N 1 の半分の電流を流すようにされる。上記 MOSFET Q N 2 のドレインは、上記トランジスタ Q 1 のコレクタに接続される。上記 MOSFET Q N 3 のドレインは、上記トランジスタ Q 3 のコレクタに接続される。

## 【0023】

40

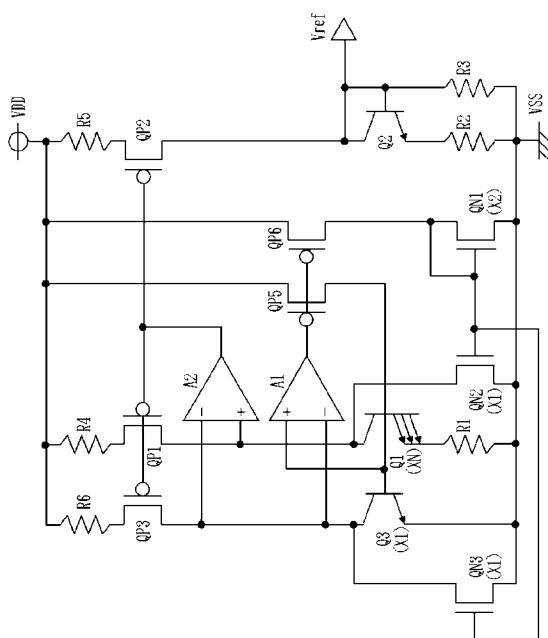

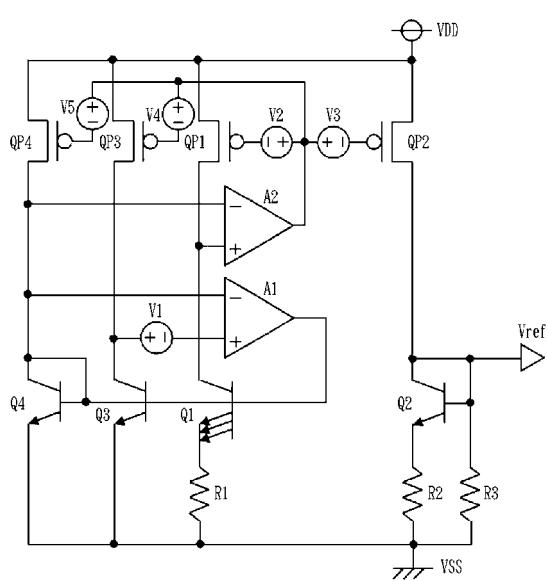

図 3 には、この発明に係る基準電圧発生回路の更に他の一実施例の回路図が示されている。この実施例は、前記図 2 の基準電圧発生回路において、図 1 の実施例のように P チャネル MOSFET Q P 1 ~ Q P 3 におけるしきい値電圧のバラツキに対応したオフセット電圧による基準電圧  $V_{ref}$  の変動を抑制するために、ソースと電源電圧  $V_{DD}$ との間に抵抗 R 4 ~ R 6 がそれぞれ設けられる。つまり、図 1 の実施例と図 2 の実施例を組み合わせて、上記 MOSFET Q P 1 ~ Q P 3 におけるプロセスバラツキによる基準電圧  $V_{ref}$  に対するオフセット電圧の影響と、トランジスタ Q 1 ~ Q 3 における電流増幅率のプロセスバラツキの影響をそれぞれ抑制するというものである。

## 【0024】

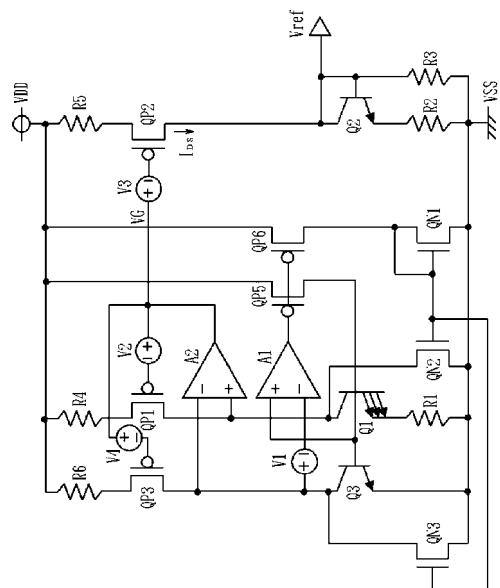

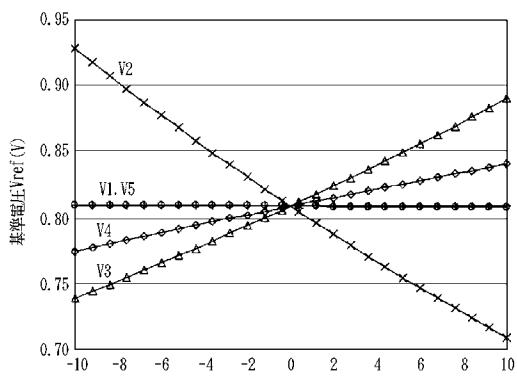

図 4 には、この発明を説明するための等価回路図が示されている。同図は、図 1 の実施例に対応した差動增幅回路における差動素子のプロセスバラツキ、電流ミラー MOSFE

50

T Q P 1 ~ Q P 3 のプロセスバラツキを検証するためのオフセット電圧 V 1 ~ V 4 が示されている。

【 0 0 2 5 】

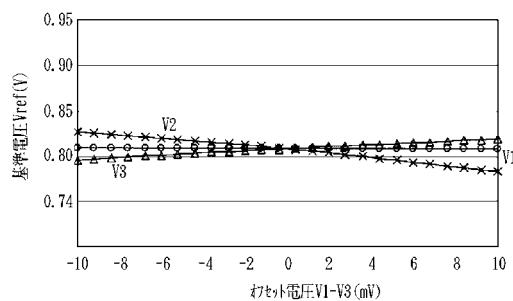

図 5 には、上記オフセット電圧 V 1 ~ V 4 による基準電圧 V ref への影響の特性図が示されている。図 5 は、上記オフセット電圧 V 1 ~ V 4 による基準電圧 V ref に対する影響を本願発明者によるコンピュータシミュレーションにより調べたものであり、前記図 1 2 と同様に上記各 M O S F E T Q P 1 ~ Q P 3 のしきい値電圧が目標値 ( 0 m V ) に対してそれぞれ - 1 0 m V ~ + 1 0 m V の範囲で変動したことを想定し、それぞれのオフセット電圧 V 1 ~ V 4 が基準電圧 V ref に与える影響を検証したものである。図 5 からは、基準電圧 V ref に最も大きな影響を及ぼす前記 M O S F E T Q P 1 のしきい値電圧のバラツキ ( オフセット電圧 V 2 ) においても大幅に抑制されることが判る。 10

【 0 0 2 6 】

このことを定量的には以下のように説明できる。例えば、図 4 において、M O S F E T Q P 2 について説明すると、ゲート電圧を V G とし、オフセット電圧 V 3 を V O S とし、ソースに設けられた抵抗 R 5 を R のように一般化すると、ドレイン電流を I D S とすると、次式 1 のように表すことができ、  $I_{DS} / V_{OS}$  を求めると次式 2 のように表すことができる。他の M O S F E T Q P 1 や Q P 3 についてのオフセット電圧 V 2 , V 4 においても同様である。

【 0 0 2 7 】

【 数 1 】

$$I_{DS} = \frac{1}{2} \cdot \frac{W}{L} \cdot \mu \cdot C_{OX} \cdot (V_G + V_{OS} - R \cdot I_{DS} - V_{TH})^2$$

【 0 0 2 8 】

【 数 2 】

$$\frac{\partial I_{DS}}{\partial V_{OS}} = \frac{1}{R} \cdot \left( 1 \pm \frac{1}{\sqrt{1 + 2 \cdot R \cdot \underbrace{\frac{W}{L} \cdot \mu \cdot C_{OX} \cdot (V_G + V_{OS} - V_{TH})}_{\text{この項は一般に} \ll 1}}} \right) \approx \frac{2}{R}$$

この項は一般に  $\ll 1$

【 0 0 2 9 】

上記式 2 において、  $I_{DS} / V_{OS}$  は、M O S F E T のチャネル幅とチャネル長とのサイズ比 W / L 、オフセット電圧 V OS に依存しないで抵抗 R に反比例する式 ( 2 / R ) で表れるものとなる。上記ドレイン電流を I DS は、トランジスタ Q 2 に供給されて基準電圧 V ref を形成するので、式 2 (  $I_{DS} / V_{OS}$  ) がオフセット電圧 V OS に依存しないことは基準電圧 V ref がオフセット電圧 V OS のバラツキの影響を受なくできることを意味する。上記抵抗 R の抵抗値がある程度大きくなると、抵抗 R のバラツキの影響も小さくすることができる。この構成では、W / L を小さくすることができるので低電圧動作に有利な回路となるものである。 40

【 0 0 3 0 】

ちなみに、前記図 1 0 の回路のように抵抗が存在しない場合には、ドレイン電流 I DS は、ド次式 3 のように表すことができ、  $I_{DS} / V_{OS}$  を求めると次式 4 のように表すことができる。この式 4 から、電流のオフセット電圧依存性は、サイズ比 W / L 、オフセット電圧 V OS に比例する。サイズ比 W / L を小さくすることは、変動量を小さくすることを意味するが、反面には低電圧動作を困難とするという別の弊害を生じるものである。

【 0 0 3 1 】

【数3】

$$I_{DS} = \frac{1}{2} \cdot \frac{W}{L} \cdot \mu \cdot C_{OX} \cdot (V_G + V_{OS} - V_{TH})^2$$

【0032】

【数4】

$$\frac{\partial I_{DS}}{\partial V_{OS}} = \frac{W}{L} \cdot \mu \cdot C_{OX} \cdot (V_G + V_{OS} - V_{TH})$$

【0033】

10

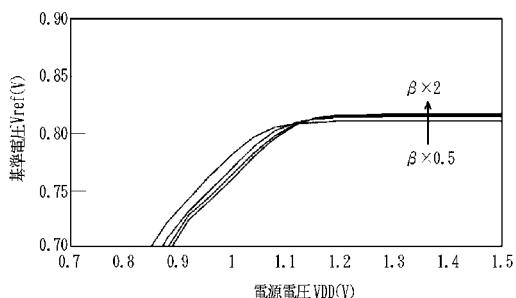

図6には、前記図2、図3の実施例に対応した上記トランジスタQ1～Q3の電流増幅率のプロセスバラツキによる基準電圧Vrefへの影響の特性図が示されている。図6は、トランジスタQ1～Q3の電流増幅率の設計値(中心値)に対して半分(×0.5)から2倍(×2)の範囲のような大きなバラツキによる基準電圧Vrefに対する影響を本願発明者によるコンピュータシミュレーションにより調べたものである。図6からは、上記基準電圧Vrefに対する電流増幅率のバラツキによる変動幅が大きく抑制されることが判る。

【0034】

このことは、定性的には次のように説明できる。図2において、トランジスタQ1、Q3に供給される電流I<sub>OUT</sub>には、MOSFET QP5によりトランジスタQ1、Q3のベース電流I<sub>B1</sub>、I<sub>B3</sub>を検知し、それをMOSFET QP6～QN1～QN2、QN3を経由して加算される。したがって、トランジスタQ2のコレクタから供給される電流I<sub>OUT</sub>は、上記トランジスタQ1のコレクタ電流I<sub>C1</sub>とベース電流I<sub>B1</sub>に対応したものとなる。したがって、トランジスタQ2のコレクタ電流I<sub>C2</sub>は上記トランジスタQ1のコレクタ電流I<sub>C1</sub>に等しく、トランジスタQ2のベース電流I<sub>B2</sub>は、上記トランジスタQ1のベース電流I<sub>B1</sub>に等しくできる。これらトランジスタQ1、Q2の電流増幅率にプロセスバラツキが生じるということは、上記のようにコレクタ側の電流が一定にされるからベース電流I<sub>B1</sub>やI<sub>B2</sub>が変化させられるものとなるが、上記の回路ではトランジスタQ1とQ2に流れるコレクタ電流及びベース電流が電流増幅率のバラツキに関係なく同じ条件となり、電流増幅率がばらついた場合のトランジスタQ2のコレクタ電流の変化量を抑えることができる、基準電圧Vrefの変動を抑えることが出来る。

20

【0035】

30

このことは、定量的には次のように説明できる。例えば、図2において、PチャネルMOSFET QP1～QP3のドレイン電流をI<sub>OUT</sub>とし、トランジスタQ1のコレクタ電流をI<sub>C1</sub>とし、ベース電流をI<sub>B1</sub>とし、トランジスタQ2のコレクタ電流をI<sub>C2</sub>とし、ベース電流をI<sub>B2</sub>とし、ベース、エミッタ間電圧をV<sub>BE</sub>とし、抵抗R1をR<sub>1</sub>とし、抵抗R2をR<sub>2</sub>とし、抵抗R3をR<sub>3</sub>とすると、ドレイン電流I<sub>OUT</sub>は、次式5のように表すことができ、基準電圧Vrefは、次式6のように表すことができる。

【0036】

【数5】

40

$$\begin{aligned} I_{OUT} &= I_{C1} + I_{B1} = I_{C2} + I_{B2} \\ &= \frac{1}{R_1} \cdot \frac{k \cdot T}{q} \cdot \ln(N) \end{aligned}$$

【0037】

## 【数6】

$$V_{\text{REF}} = \frac{R_3}{R_2 + R_3} \cdot \underbrace{\left\{ V_{\text{BE}} + \frac{R_2}{R_1} \cdot \frac{k \cdot T}{q} \cdot \ln(N) \right\)}_{\beta \text{ に依存しない}}$$

## 【0038】

式6において、基準電圧  $V_{\text{ref}}$  は、電流増幅率  $\beta$  に依存せず、抵抗比  $R_2 / R_1$  により 10

$V_{\text{BE}}$  の温度依存性をキャンセルさせることができる。

## 【0039】

ちなみに、図10の基準電圧発生回路においては、PチャネルMOSFET QP2からトランジスタ Q2 に供給される電流  $I_{\text{OUT}}$  は、次式7のように表すことができ、基準電圧  $V_{\text{ref}}$  は次式8のように表すことができる。上記式7及び式8において、いずれも電流増幅率  $\beta$  に依存するものであることが判る。

## 【0040】

定性的に説明すると、トランジスタ Q1 は、差動増幅回路 A1 からベース電流  $I_{B1}$  が供給されるので、コレクタ電流  $I_{C1}$  がそのまま PチャネルMOSFET QP2 を通して電流  $I_{\text{OUT}}$  としてトランジスタ Q2 のコレクタ側に供給される。しかしながら、トランジスタ Q2 においては、コレクタとベースが接続されており、上記 PチャネルMOSFET QP2 から供給される電流  $I_{\text{OUT}}$  は、トランジスタ Q2 のコレクタ電流  $I_{C2}$  とベース電流  $I_{B2}$  のように分配されて流れるものとなる。上記電流  $I_{C2}$  と  $I_{B2}$  の分配比は、電流増幅率  $\beta$  により決定されてコレクタ電流  $I_{C2}$  が変動することの結果、前記のように基準電圧  $V_{\text{ref}}$  が変動するものとなる。

## 【0041】

## 【数7】

$$I_{\text{OUT}} = I_{C1} = I_{C2} + I_{B2} = \frac{1}{R_1 \cdot \left( \frac{1}{\beta} + 1 \right)} \cdot \frac{k \cdot T}{q} \cdot \ln(N) \quad 30$$

## 【0042】

## 【数8】

$$V_{\text{REF}} = \frac{R_3}{R_2 + R_3} \cdot \underbrace{\left\{ V_{\text{BE}} + \frac{R_2}{R_1 \cdot \left( \frac{1}{\beta} + 1 \right)} \cdot \frac{k \cdot T}{q} \cdot \ln(N) \right\)}_{\beta \text{ に依存する}} \quad 40$$

## 【0043】

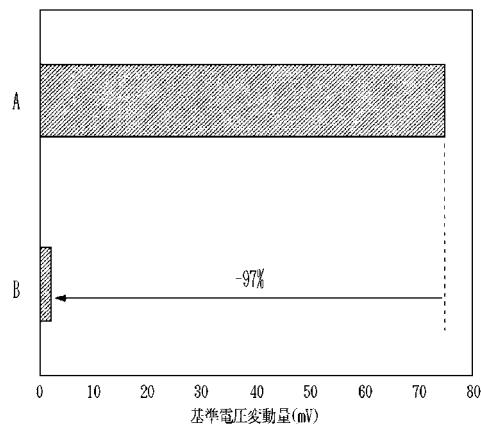

図7には、この発明の説明図が示されている。図7は、前記図10と図1の基準電圧発生回路におけるPチャネルMOSFET QP1～QP3のプロセスバラツキで発生するオフセット電圧によるワースト変動量を比較したものであり、図7のAは、前記図10の基準電圧発生回路におけるワースト変動量を示し、基準電圧  $V_{\text{ref}}$  の変動量が約120mVにもなってしまう。これに対して図7のBは、前記図1の基準電圧回路におけるワースト変動量を示し、基準電圧  $V_{\text{ref}}$  の変動量が20mV以下に抑制され、前記図10の回路に50

比べて 85% もの改善ができる。

【0044】

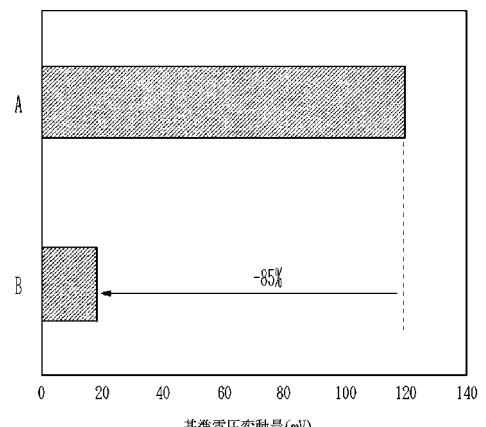

図 8 には、この発明の他の説明図が示されている。図 8 は、前記図 10 と図 1 の基準電圧発生回路における前記トランジスタ Q1 ~ Q3 の電流増幅率 のバラツキによるワースト変動量を比較したものであり、図 8 の A は、前記図 10 の基準電圧発生回路におけるワースト変動量を示し、基準電圧  $V_{ref}$  の変動量が約 75 mV にもなってしまう。これに対して図 8 の B は、前記図 2 の基準電圧回路におけるワースト変動量を示し、基準電圧  $V_{ref}$  の変動量が 3 mV 程度に抑制され、前記図 10 の回路に比べて約 97% もの改善ができる。

【0045】

図 3 の実施例回路では、上記 MOSFET QP1 ~ QP3 のオフセット電圧と、トランジスタ Q1 ~ Q3 の電流増幅率 のバラツキが上記のように共に改善される。つまり、図 10 の回路では、MOSFET QP1 ~ QP3 のオフセット電圧のバラツキにより 120 mV、電流増幅率 のバラツキにより 70 mV もそれぞれ変動するので、両方で 190 mV もの基準電圧  $V_{ref}$  の変動を考慮しなければならない。これに対して、図 3 の実施例回路では、両方でも 20 mV 程度にしかならないので、素子のプロセスバラツキの影響を大幅に抑制した基準電圧発生回路を得ることができる。

【0046】

図 9 には、このこの発明に係る基準電圧発生回路の更に他の一実施例の回路図が示されている。この実施例は、前記図 3 の実施例回路の変形例であり、トランジスタ Q1、Q3 のベース電流を検知する P チャネル MOSFET QP5 と電流ミラー形態にされる P チャネル MOSFET QP6 のドレイン電流を直接にトランジスタ Q2 のコレクタ、ベース接続点に供給するものである。P チャネル MOSFET QP5 は、トランジスタ Q1 と Q3 の 2 個のトランジスタのベース電流を流すので、P チャネル MOSFET QP6 のサイズを MOSFET QP5 のサイズに比べて 1/2 にすることにより、前記図 3 の実施例と同様にトランジスタ Q2 のコレクタとベース接続点に、上記トランジスタ Q1 のコレクタ電流  $I_{C1}$  とベース電流  $I_{B1}$  を供給することができる。これにより、前記図 3 の実施例と同様にトランジスタ Q2 のコレクタ電流  $I_{C2}$  は上記トランジスタ Q1 のコレクタ電流  $I_{C1}$  に等しく、トランジスタ Q2 のベース電流  $I_{B2}$  は、上記トランジスタ Q1 のベース電流  $I_{B1}$  に等しくできる。

【0047】

この実施例では、P チャネル MOSFET QP5、QP6 が前記 MOSFET QP1 ~ QP3 と同様な回路構成とされることから、P チャネル MOSFET QP5、QP6 におけるオフセット電圧が基準電圧  $V_{ref}$  に影響を及ぼすものと考えられる。したがって、これを抑制するために P チャネル MOSFET QP5、QP6 のソース側にも前記 P チャネル MOSFET QP1 ~ QP3 のソース側に設けられた抵抗 R4 ~ R6 と同様な抵抗 R7 と R8 が設けられる。この実施例は、前記図 3 の実施例と比較して電流バスが減り、低消費電力化、小面積化につながる。

【0048】

上記基準電圧発生回路を形成される半導体集積回路装置は、CMOS 回路で構成されるものが好適である。この場合、素子のプロセスバラツキに影響されない回路とができるることから、SOC 搭載メモリやマイクロプロセッサに有効なものとなる。これらの半導体集積回路装置は、低電圧化のニーズが高く、しかも高精度な基準電圧が必要であるからである。また、プロセスにより異なるに対応した再設計が不要になることから、ハードウェア IP (Intellectual Property) コアに利用して有効な技術となる。更に、プロセッサ等トリミングすることが難しい製品では、MOSFET のしきい値電圧や電流増幅率 のバラツキによる基準電圧の変動量が小さいので、トリミング回路を準備しておく必要が無いことから有効である。

【0049】

以上本発明者によってなされた発明を、前記実施形態に基づき具体的に説明したが、本

10

20

30

40

50

発明は、前記実施形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能である。例えば、トランジスタQ1～Q3は、前記のような3重ウェル構造のCMOSプロセスで形成される半導体領域で構成されるものの他、ラテラル構造のバイポーラトランジスタを用いるもの等種々の変形を探ることができる。負電圧を電源電圧とした場合には、トランジスタやMOSFETの導電型を逆にすればよい。上記抵抗R4～R8等は、前記のように比較的高い抵抗値にされる必要があるので、ポリシリコン抵抗等を利用することができる。

【産業上の利用可能性】

【0050】

この発明は、MOSFETで構成される半導体集積回路装置に搭載される基準電圧発生回路として広く利用でき、低電圧化のニーズが高く、しかも高精度な基準電圧を必要とするSOC搭載メモリやマイクロプロセッサ、ハードウェアIPコア製品、トリミングすることが難しい各種半導体集積回路装置等に利用して有効なものとなる。

10

【図面の簡単な説明】

【0051】

【図1】この発明に係る基準電圧発生回路の一実施例の回路図である。

【図2】この発明に係る基準電圧発生回路の他の一実施例の回路図である。

【図3】この発明に係る基準電圧発生回路の更に他の一実施例の回路図である。

【図4】この発明を説明するための等価回路図である。

【図5】図1のMOSFETのオフセット電圧のバラツキによる基準電圧への影響を示した特性図である。

20

【図6】図2のトランジスタの電流増幅率のバラツキによる基準電圧への影響を示した特性図である。

【図7】この発明の説明図である。

【図8】この発明の他の説明図である。

【図9】このこの発明に係る基準電圧発生回路の更に他の一実施例の回路図である。

【図10】従来の基準電圧発生回路の回路図である。

【図11】本願発明者により検討された図10の等価回路である。

【図12】図10のMOSFETのオフセット電圧のバラツキによる基準電圧への影響を示した特性図である。

30

【図13】図10のトランジスタの電流増幅率のバラツキによる基準電圧への影響を示した特性図である。

【符号の説明】

【0052】

A1, A2…差動増幅回路、Q1～Q4…トランジスタ、QP1～QP6…PチャネルMOSFET、QN1～QN3…NチャネルMOSFET、R1～R8…抵抗、

【 図 1 】

【 図 2 】

【 四 3 】

### 【図4】

【 四 5 】

【 四 6 】

【 四 8 】

【 义 7 】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

---

フロントページの続き

(72)発明者 ファン ダン ゴア

東京都小平市上水本町五丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

審査官 榎木澤 昌司

(56)参考文献 特開2004-310444 (JP, A)

特開2001-085548 (JP, A)

特開平08-184806 (JP, A)

特開昭63-175907 (JP, A)

特開2007-287095 (JP, A)

特開2005-130020 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 05 F 3 / 26 - 3 / 30