### (19) World Intellectual Property Organization International Bureau

#### (43) International Publication Date 1 May 2003 (01.05.2003)

#### **PCT**

## (10) International Publication Number WO 03/036850 A1

(51) International Patent Classification<sup>7</sup>: H04L 5/16, G06F 1/04

(21) International Application Number: PCT/US02/33706

(22) International Filing Date: 22 October 2002 (22.10.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/343,905 22 October 2001 (22.10.2001) US 60/376,947 30 April 2002 (30.04.2002) US

- (71) Applicant: RAMBUS INC. [US/US]; 4440 El Camino Real, Los Altos, CA 94022 (US).

- (72) Inventors: HAMPEL, Craig, E.; 5927 Dunn Avenue, San Jose, CA 95123 (US). PEREGO, Richard, E.; 5938 Pala Mesa Drive, San Jose, CA 95123 (US). SIDIROPOULOS, Stephanos, S.; 731 Ellsworth Street, Palo Alto, CA 94306 (US). TSERN, Ely, K.; 684 Riviera Drive, Los Altos, CA 94024 (US). WARE, Fredrick, A.; 13961 Fremont, Pines, Los Altos Hills, CA 94022 (US).

- (74) Agents: WILLIAMS, Gary, S. et al.; Pennie & Edmonds LLP, 1155 Avenue of the Americas, New York, NY 10036 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

[Continued on next page]

(54) Title: PHASE ADJUSTMENT APPARATUS AND METHOD FOR A MEMORY DEVICE SIGNALING SYSTEM

(57) Abstract: Apparatus and methods are disclosed for adjusting phase of data signals to compensate for phase offset variations between devices during normal operation. The phase of data signals are adjusted individually in each transmit data unit and receive data unit across multiple data slices with a common set of phase vector clock signals and a corresponding clock cycle count signal. The transmission of signal information between a first device (such as a memory controller) (205) and a second device (such as a memory component) (210) occurs without errors even when the accumulated delays between the first device and second device change by a half symbol time interval or more during operation of the system. The apparatus reduces the circuitry required, such as phase-lock-loops (255), for individually adjusting the phase of each transmit data unit and receive data unit across multiple data slices, which in turn results in reduction in complexity and cost of the system.

m MO~03/036850~A

## WO 03/036850 A1

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

# PHASE ADJUSTMENT APPARATUS AND METHOD FOR A MEMORY DEVICE SIGNALING SYSTEM

This application claims priority to U.S. provisional application 60/343,905, filed on October 22, 2001, and U.S. provisional application 60/376,947, filed on April 30, 2002, both of which are hereby incorporated by reference.

5

10

15

20

25

30

#### FIELD OF THE INVENTION

This invention generally relates to the field of digital circuits, and more particularly to an apparatus and method for phase adjustment and memory device signaling systems.

#### **BACKGROUND OF THE INVENTION**

Integrated circuits connect to and communicate with each other, typically using a bus with address, data and control signals. Today's complex digital circuits contain storage devices, finite-state machines, and other such structures that control the movement of information by various clocking methods. Transferred signals must be properly synchronized or linked so that information from a transmit point is properly communicated to and received by a receive point in a circuit.

The term "signal" refers to a stream of information communicated between two points within a system. For a digital signal, this information consists of a series of "symbols," with each symbol driven for an interval of time. In digital applications, the symbols are generally referred to as "bits" in which values are represented by "zero" and "one" symbols, although other symbol sets are possible. The values commonly used to represent the zero and one symbols are voltage levels, although other variations are possible.

In some cases, a signal will be given more than one name (using an index notation), with each index value representing the signal value present at a particular point on a wire. The two or more signal names on a wire represent the same information, with one signal value being a time-shifted version of the other. The time-shifting is the result of the propagation of voltage and current waveforms on a physical wire. Using two or more

signal names for the same signal information allows for easy accounting of the resulting propagation delays.

5

10

15

20

25

30

The term "wire" refers to the physical interconnection medium which connects two or more points within a system, and which serves as the conduit for the stream of information (the signal) communicated between the points. For example, but without limitation, a wire can be a copper wire, a metal (eg., copper) trace on a printed circuit board, or a fiber optic cable. A "bus" is a wire or a set of wires. These wires are collected together because they may share the same physical topology, or because they have related timing behavior, or for some other reason. The assignment of wires into a bus is often a notational convenience. The terms "line," "connection" and "interconnect" mean either a bus, wire or set of wires as appropriate to the context in which those terms are used.

The term "signal set" refers to one or more signals. Whenever a signal or signal set is described herein as being coupled to or attached to a device or component, it is to be understood that the device or component is coupled to a wire, set of wires or bus that carries the signal.

The mapping of a signal onto a physical wire involves tradeoffs related to system speed. The use of one physical wire per signal (single-ended signaling) uses fewer wires. The use of two physical wires per signal (differential signaling) permits shorter bit intervals. The mapping of signals onto physical wires can also involve optimization related to system resources. Two different signals can share the same wire (i.e., they are multiplexed) to minimize the number of physical wires. Typically, this must be done so that the potential timing conflicts that result are acceptable (in terms of system performance, for instance). The interval of time during which a bit or symbol is transmitted or received at a particular point on a wire or at a device interface is the "symbol time interval," "bit time," "bit time interval," "bit window," or "bit eye." These time interval terms for transmitting and receiving are used interchangeably. Usually, the bit interval for transmit signals must be greater than or equal to the bit interval for receive signals.

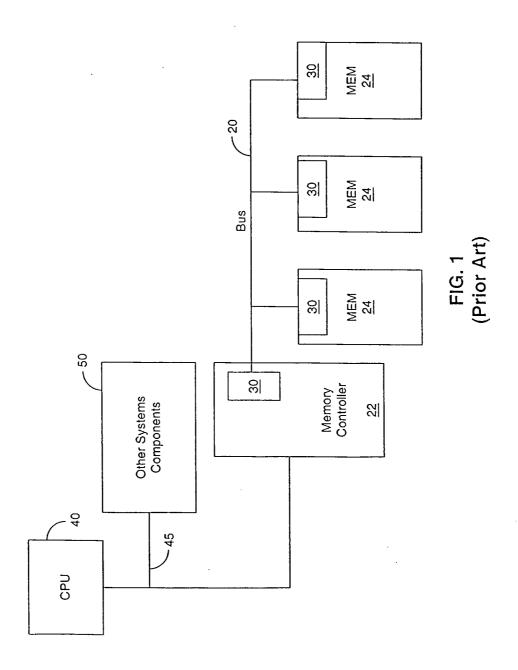

In FIG. 1, a bus 20 interconnects a memory controller 22 and memory components (MEMS) 24. Physically, the bus 20 comprises traces on a printed circuit board or wiring board, wires or cables and connectors. Each of these devices 22, 24 has a bus output

driver or transmitter circuit 30 that interfaces with the bus 20 to drive data signals onto the bus to send data to other integrated circuits. Each of these devices also has a receiver. In particular, the bus output drivers 30 in the memory controller 22 and MEMS 24 are used to transmit data over the bus 20. The bus 20 transmits signals at a rate that is a function of many factors such as the system clock speed, the bus length, the amount of current that the output drivers can drive, the supply voltages, the spacing and width of the wires or traces making up the bus, and the physical layout of the bus itself. Clock, or control, signals serve the purpose of marking the passage of time, thereby controlling the transfer of information from one storage location to another. The memory controller 22 is connected to a central processing unit (CPU) 40 and other system components 50, such as a graphics control unit, over bus 45.

5

10

15

20

25

30

As signals pass over a bus and through device interfaces, the signals experience propagation delays. Propagation delays are affected by variables such as temperature, supply voltage and process parameters (which determine physical characteristics of the devices sending and receiving the signals). For example, at a low operating temperature with a high supply voltage, signals may be transmitted with a relatively short delay. Alternatively, at a low supply voltage and high operating temperature, a significantly longer delay may be experienced by transmitted signals.

Variations in the process parameters, which result in variations in the performance of otherwise identical devices, cause devices either on a single bus, or devices on parallel buses to experience different signal propagation delays. The load on each bus, which depends on the number of devices connected to the bus, may also affect signal propagation. In sum, the phase relationships between transmitted and received signals, are affected by numerous factors, some of which may change during the operation of a system. Small changes in propagation delays can result in data transfer errors, especially in systems with very high bit (or more generally, symbol) transfer rates, and thus very short bit (or symbol) times. In order to account for actual propagation delays, it is desirable, especially in systems with very high bit (or symbol) transfer rates (e.g., without limitation, 250 Mb/s or higher) to synchronize signal transmitters and receivers, to account for actual propagation delays. The present invention provides systems and methods for dynamically synchronizing signal transmitters and receivers, even when the variations in propagation

delays caused by temperature, voltage, process and loading variations exceed an average symbol time interval. Normally, a variation in propagation delay of even a half symbol time interval will cause a memory system or data transfer system to fail, because movement of a half symbol time will cause the data sample point to move from the center of the data eye to the edge of the data eye. Change in the propagation delay of more than a half symbol time will, in conventional prior art systems, cause the wrong symbol to be sampled by the receiving device. In the present invention, such changes in propagation delay are automatically "calibrated out" by the use of dynamic propagation delay calibration apparatus and methods.

10

15

20

5

#### SUMMARY OF THE INVENTION

This invention generally relates to apparatus and methods for adjusting phase of data signals to compensate for phase-offset variations between devices during normal operation. Systems designed in accordance with the present invention allow for adjusting phase of data signals individually in each transmit data unit and receive data unit across multiple data slices with a common set of phase vector clock signals and a corresponding clock cycle count signal. One of the benefits of the invention is that the transmission of signal information between a first device (such as for example a memory controller) and a second device (such as for example a memory component) occurs without errors even when the accumulated delays between the first device and second device change by a half symbol time interval or more during operation of the system. Another benefit of the invention is the reduction of circuitry required, such as phase-lock-loops, for individually adjusting the phase of each transmit data unit and receive data unit across multiple data slices, which in turn results in reduction in complexity and cost of the system.

25

30

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

For a more complete understanding of the present invention and advantages thereof, reference is now made to the following description taken in conjunction with the accompanying drawings:

FIG. 1 is a block diagram of a prior art bus connecting a memory controller and a number of memory components.

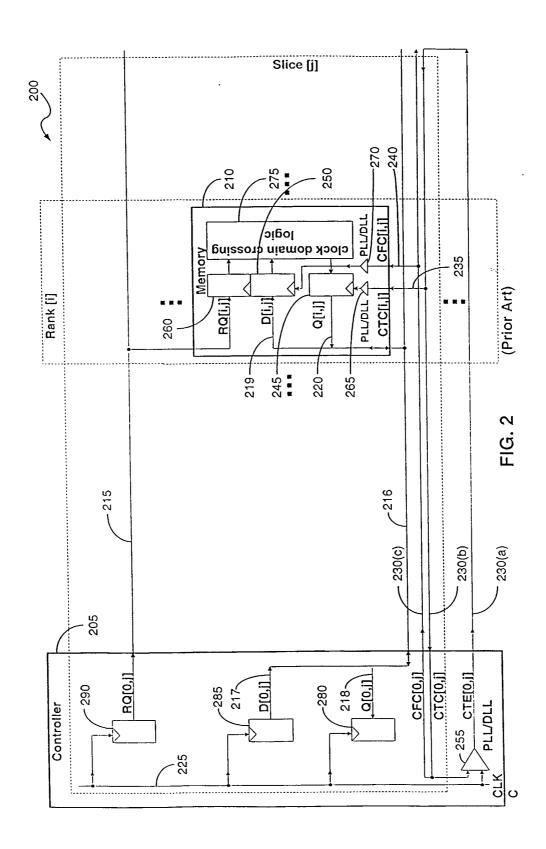

FIG. 2 is a block diagram of a prior art static mesochronous memory system connecting a controller and a memory.

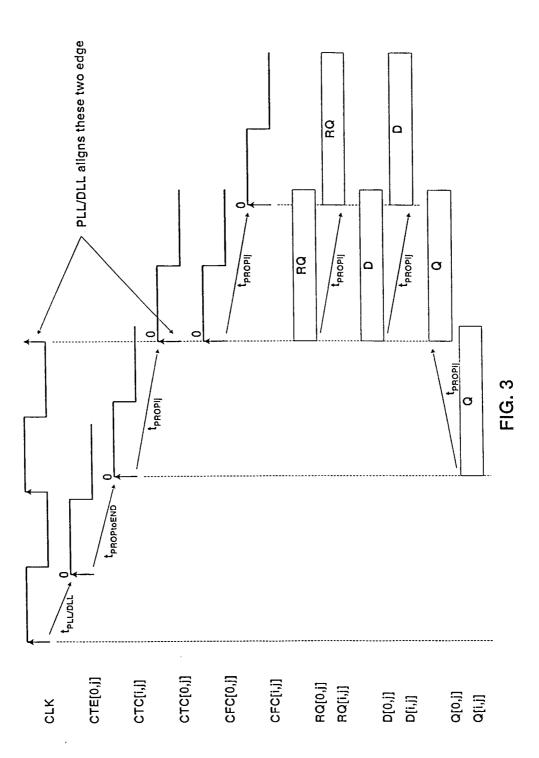

- FIG. 3 is a timing diagram for the signals of the static mesochronous memory system in FIG. 2.

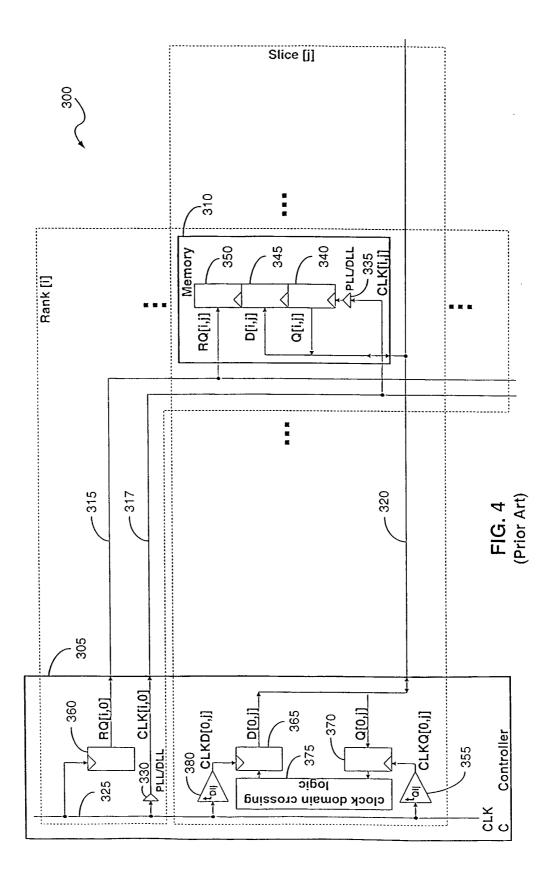

- FIG. 4 is second example of a block diagram of a prior art static mesochronous memory system connecting a controller and a memory.

5

10

15

25

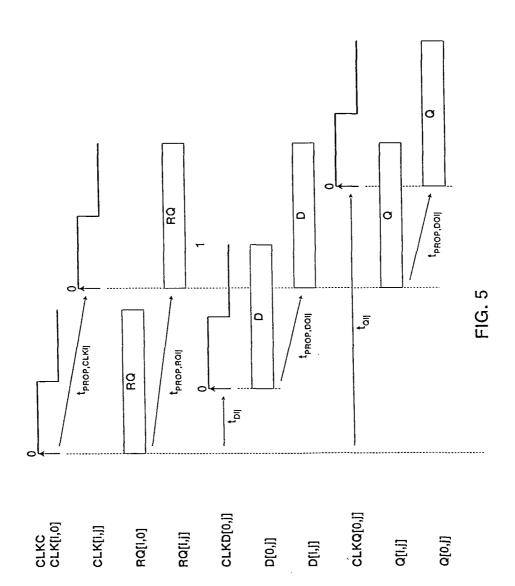

- FIG. 5 is a timing diagram for the signals of the static mesochronous memory system in FIG. 4.

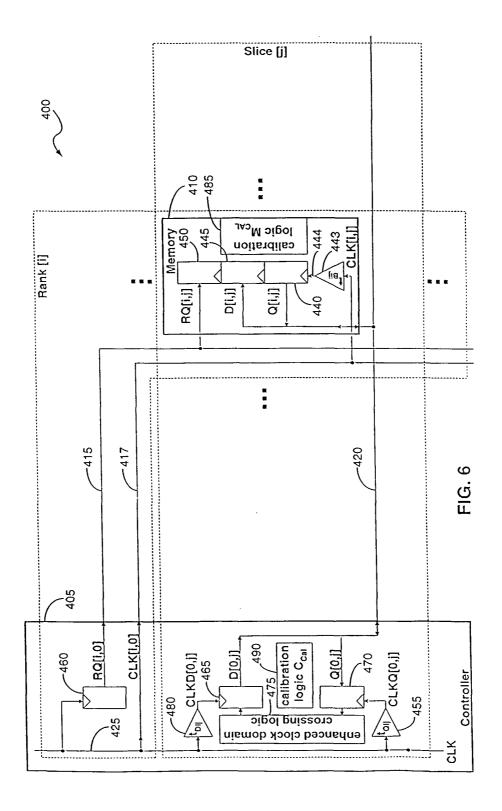

- FIG. 6 is a block diagram of a dynamic mesochronous memory system connecting a controller and a memory in accordance with a preferred embodiment of the present invention.

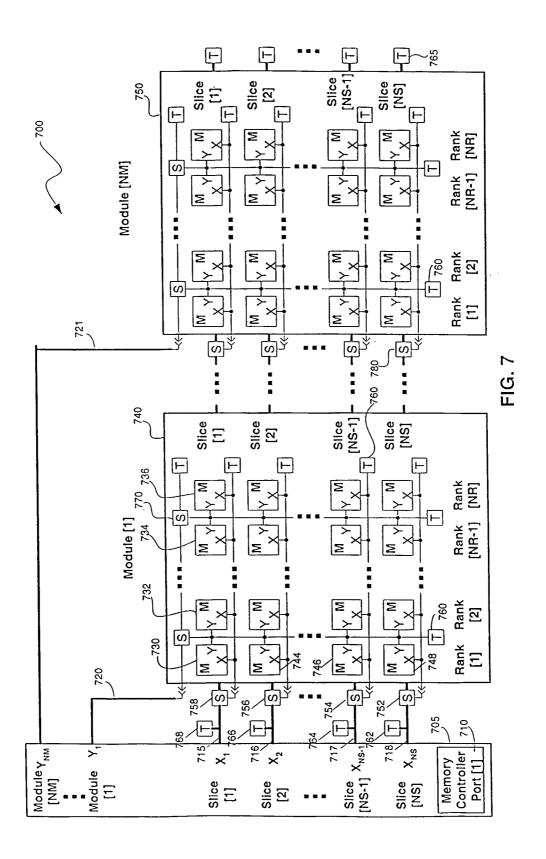

- FIG. 7 is a block diagram of a dynamic mesochronous memory system in accordance with an alternate preferred embodiment of the present invention.

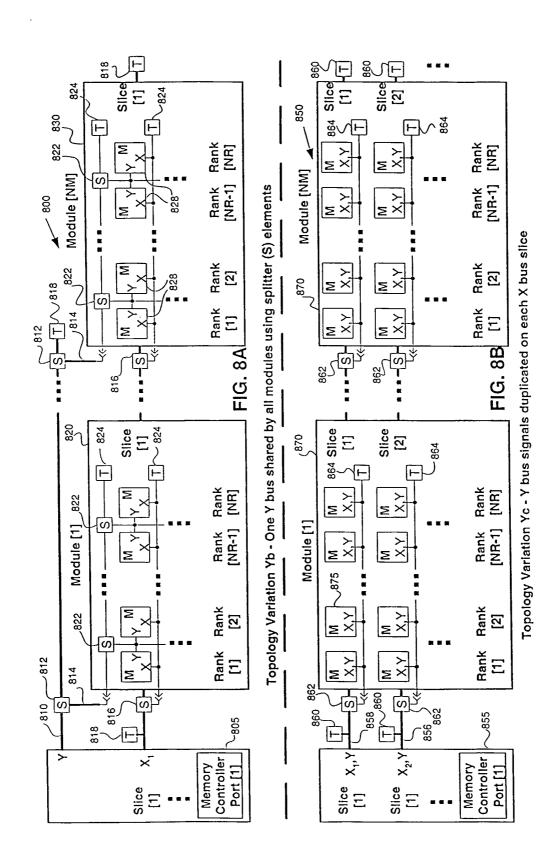

- FIGS. 8A and 8B depict dynamic mesochronous memory systems in which the X and Y buses are parallel to each other.

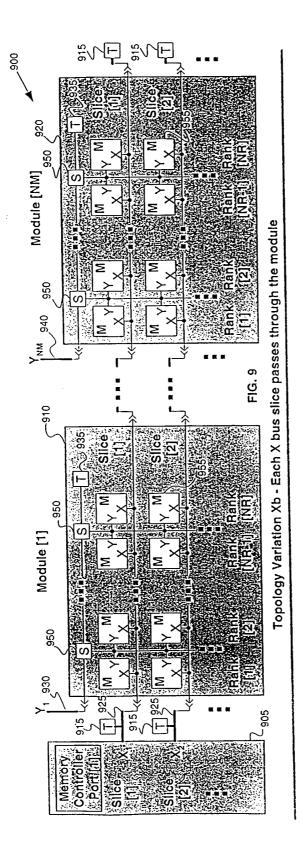

- FIG. 9 is block diagram of a dynamic mesochronous memory system in accordance with an alternate preferred embodiment of the present invention.

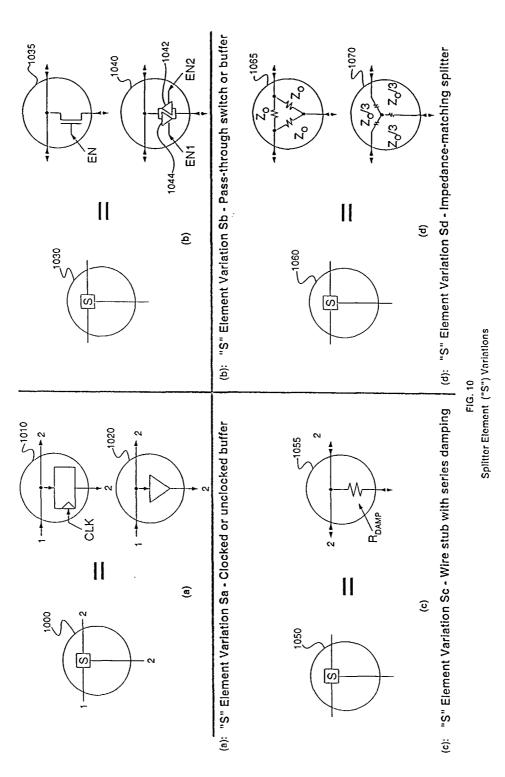

- FIG. 10 depicts sample splitting element configurations.

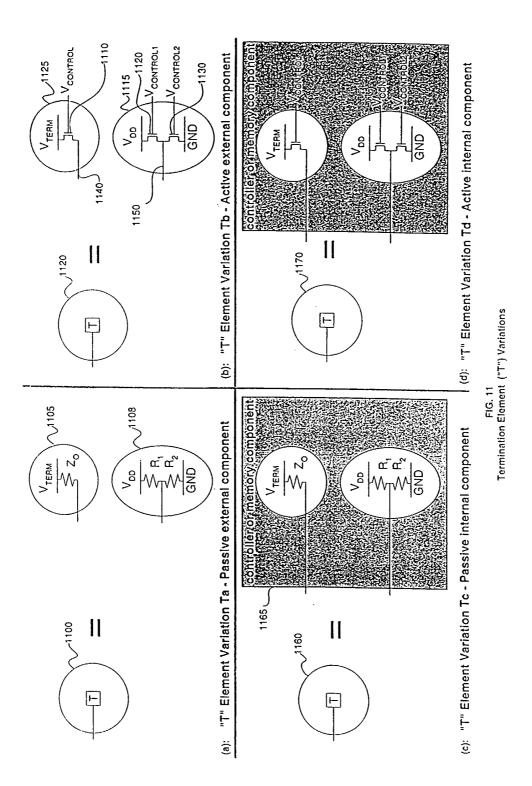

- FIG. 11 depicts sample internal and external termination component variations.

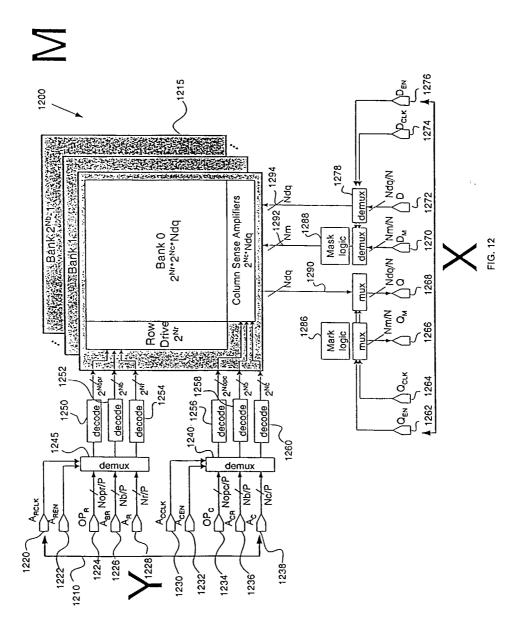

- FIG. 12 is logic diagram for a baseline system configuration 1200 for a component shown in the system topology diagrams.

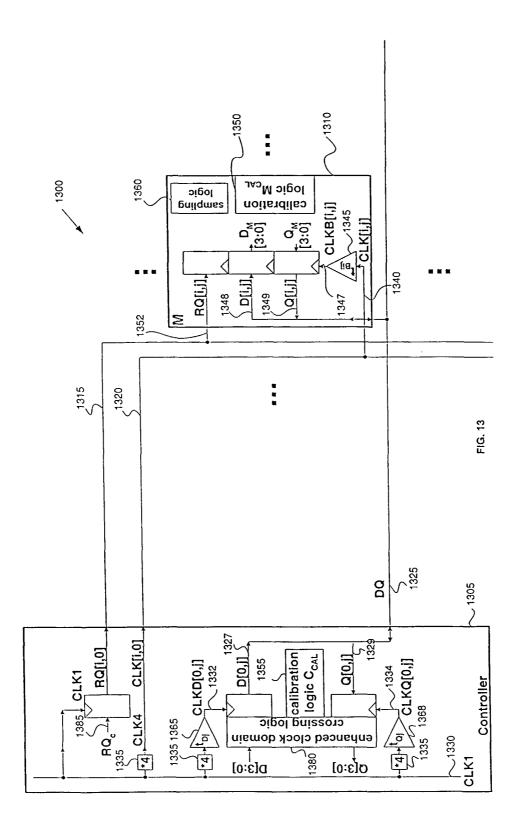

- FIG. 13 depicts a dynamic mesochronous memory system in accordance with an alternate preferred embodiment of the present invention.

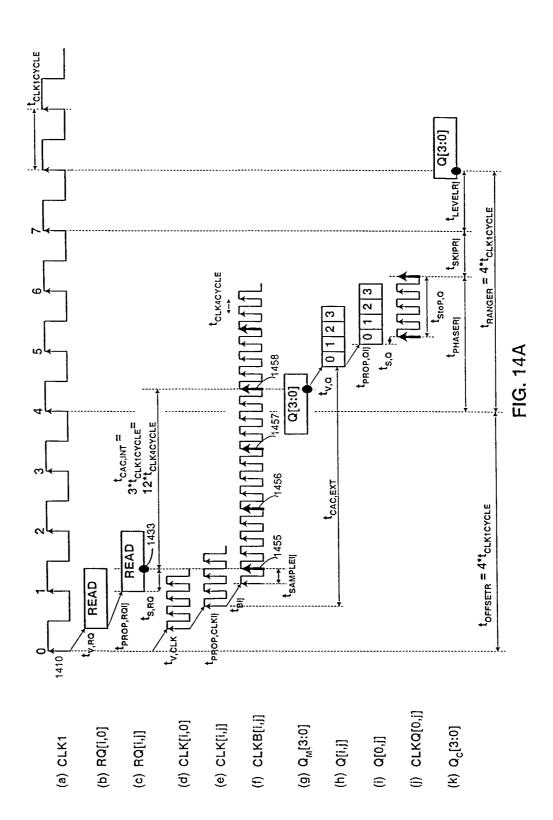

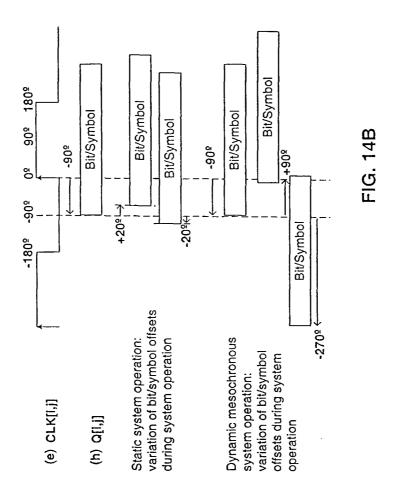

- FIGs. 14A and 14B depict a sequence of timing signals for a read transfer of the system topology of FIG. 13.

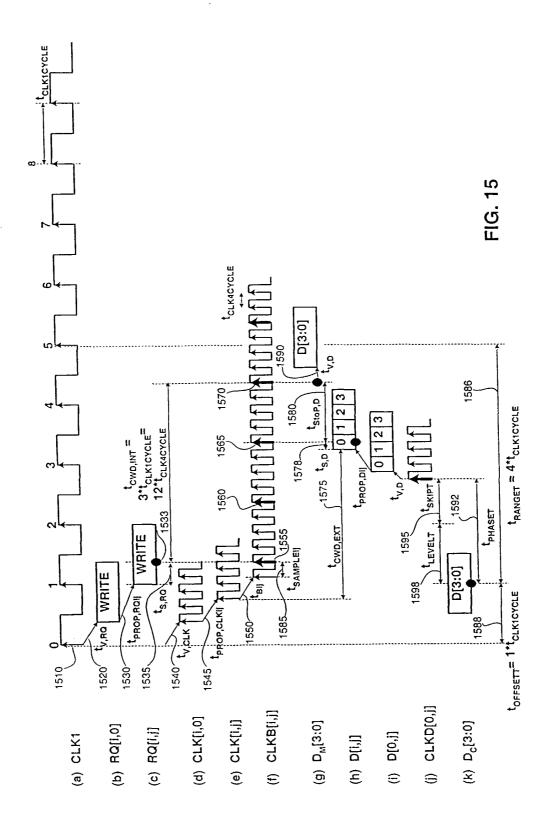

- FIG. 15 depicts a sequence of timing signals for a write transfer of the system topology of FIG. 13.

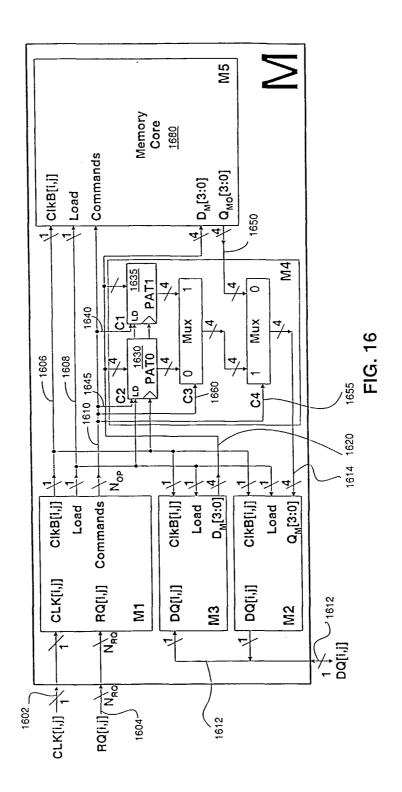

- FIG. 16 is block diagram of a memory system in accordance with a preferred embodiment.

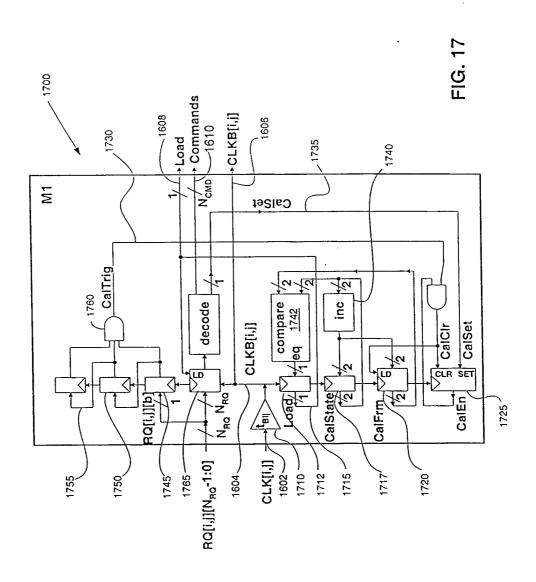

- FIG. 17 is logic diagram for a memory system of the preferred embodiment.

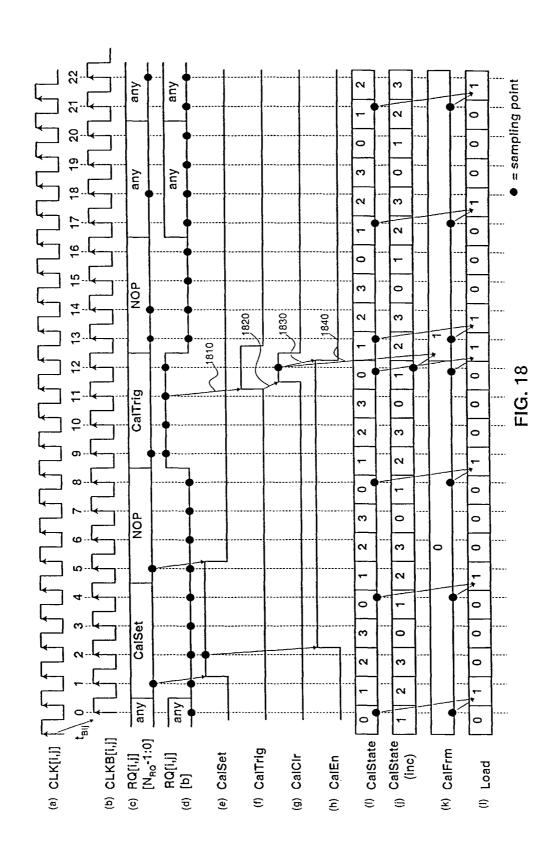

FIG. 18 shows a sequence of timing signals for block M1 of the memory system of FIG. 16.

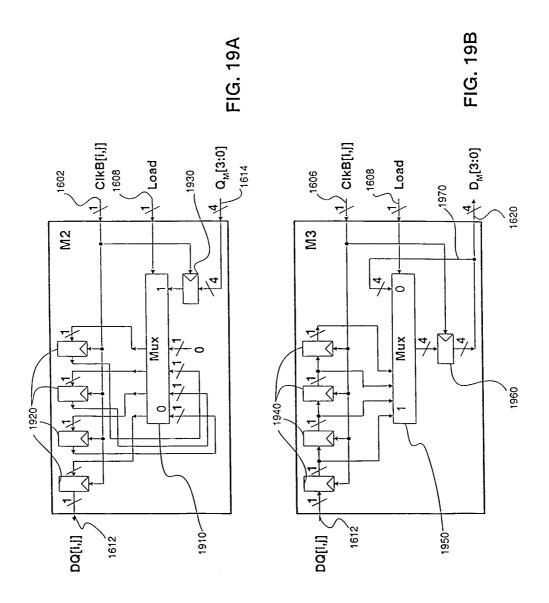

- FIG. 19A is a logic diagram of the M2 module in the memory system of FIG. 16 for transmitting read data on a bus.

- FIG. 19B is a logic diagram of the M3 module in the memory system of FIG. 16 for receiving write data.

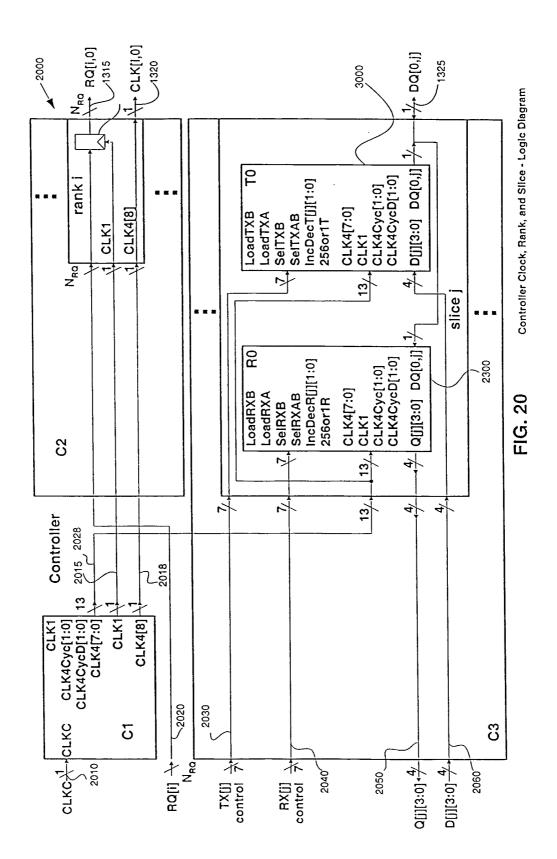

- FIG. 20 is a block diagram for a controller of the topology of FIG. 13 comprising three blocks, C1-C3, and interconnecting buses between the blocks.

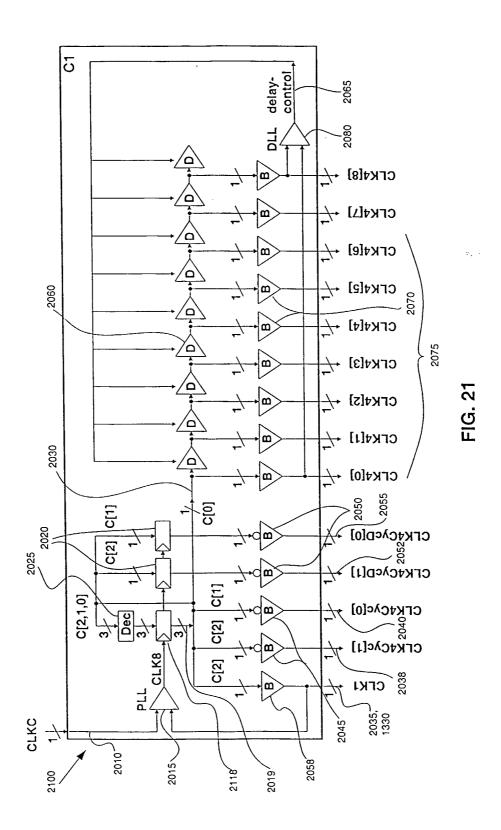

- FIG. 21 is a logic diagram for block C1 of FIG. 20.

5

10

15

20

25

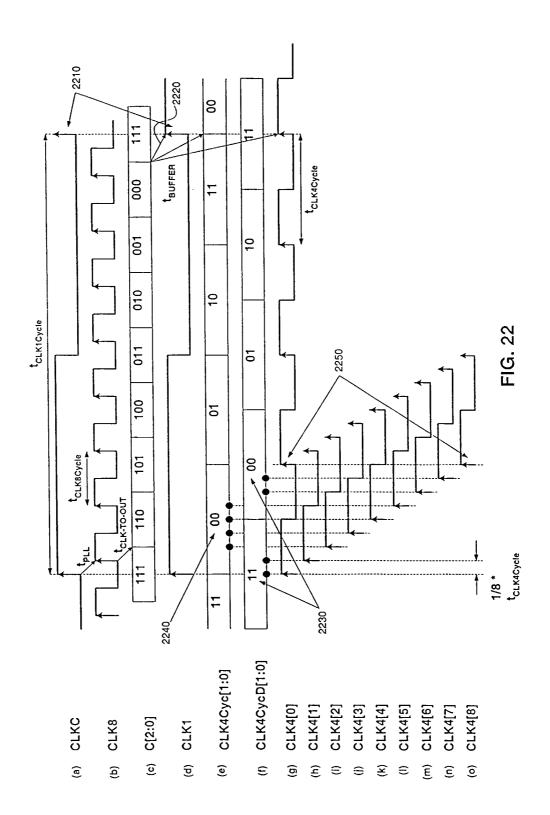

- FIG. 22 shows the clock generation sequence for block C1 of the controller.

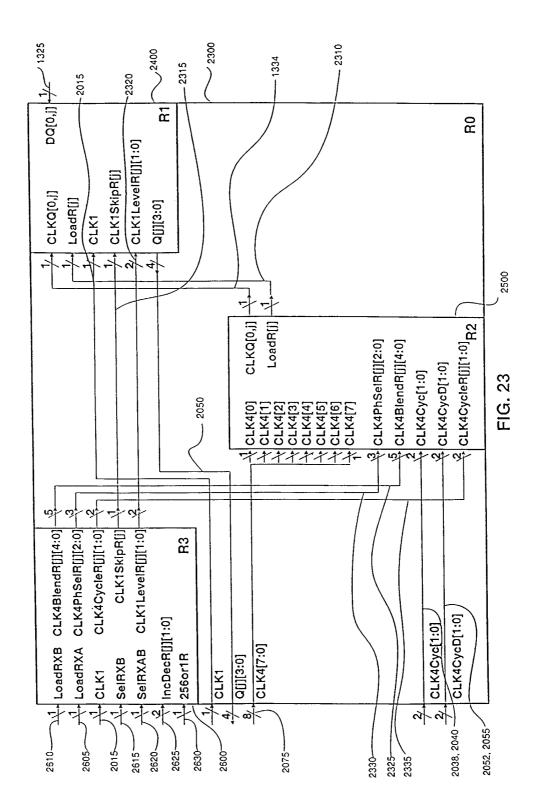

- FIG. 23 is a block diagram for the controller module responsible for receiving read data and comprising three blocks R1-R3, and interconnecting buses between the blocks.

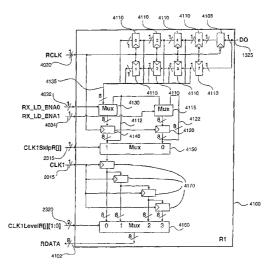

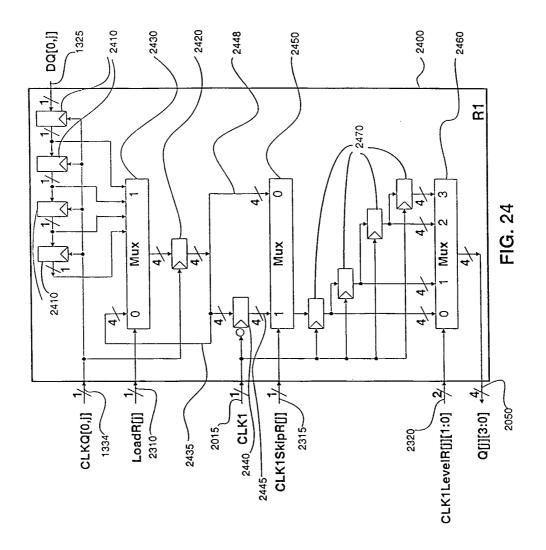

- FIG. 24 is a logic diagram for a block R1 of a controller module for receiving read data from a memory and inserting a programmable delay.

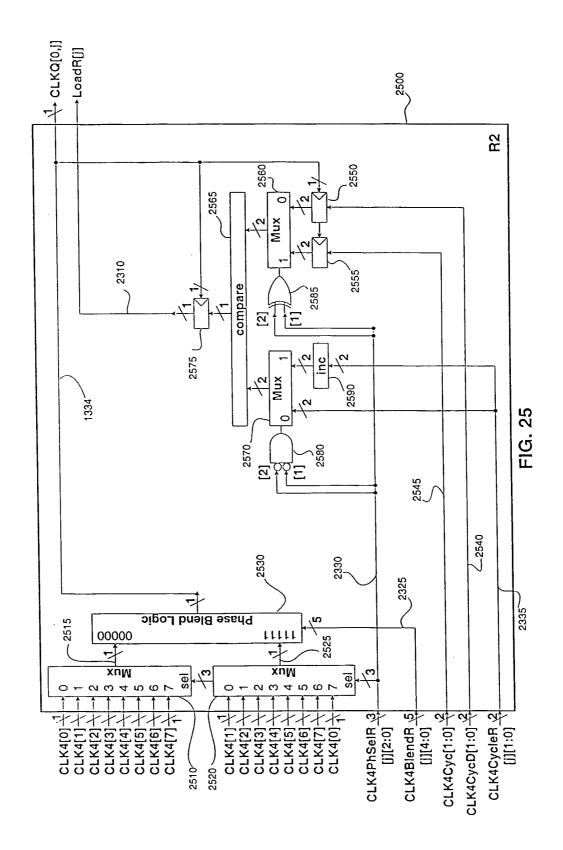

- FIG. 25 is logic diagram for a block R2 of a controller module for creating a clock for receiving read data.

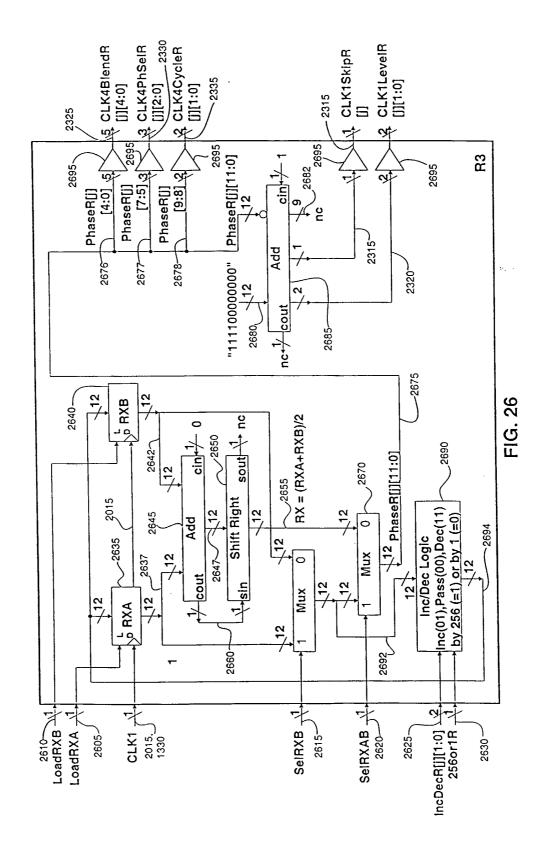

- FIG. 26 is logic diagram for a block R3 of a controller module for generating the value of a clock phase for receiving read data.

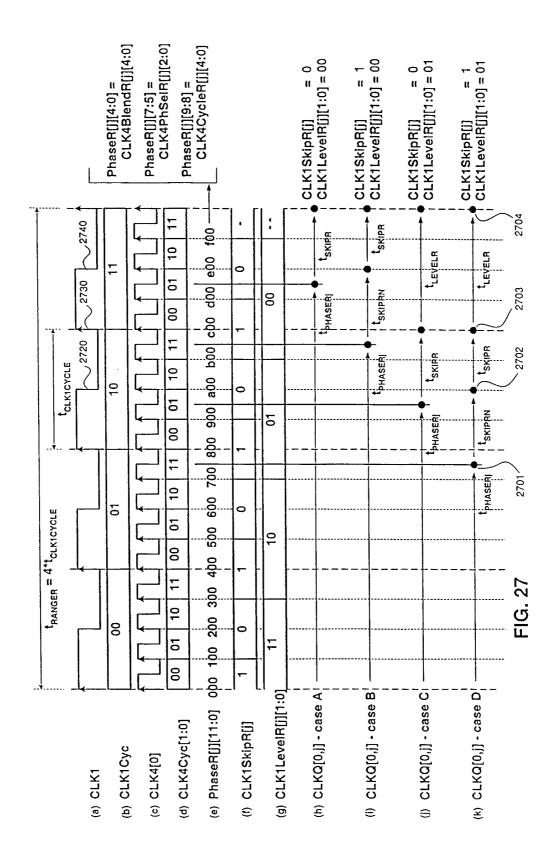

- FIG. 27 shows a sequence of receive timing signals illustrating four cases of alignment of a clock signal within a time interval and the generation of bus signals.

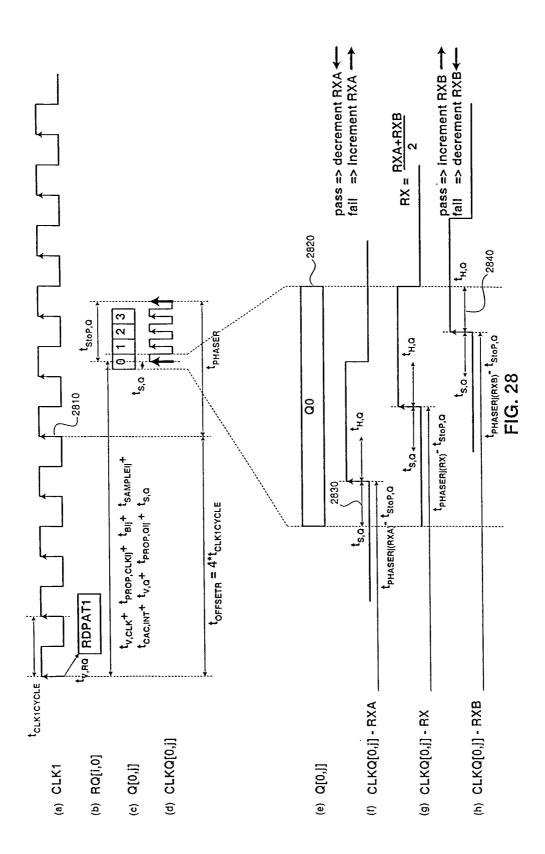

- FIG. 28 shows a sequence of timing signals that illustrate how timing values are related and maintained in RXA and RXB registers.

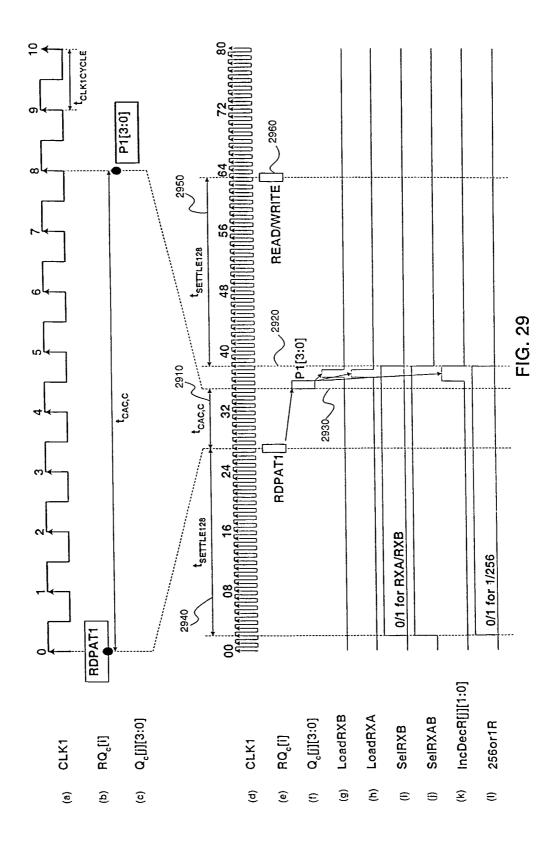

- FIG. 29 shows a sequence of receive timing signals that illustrate a calibration sequence for transferring bus signals.

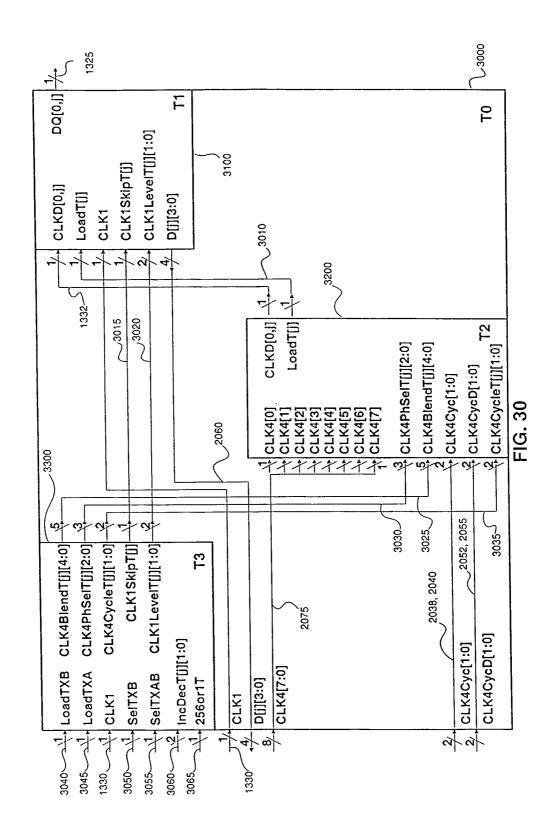

- FIG. 30 is a block diagram for a controller block T0, part of block C3, and responsible for transmitting write data.

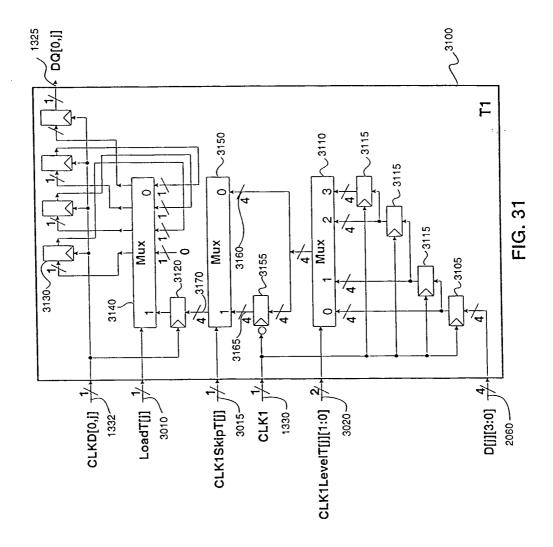

- FIG. 31 is a logic diagram for block T1, part of block T0, for transmitting write data and inserting a programmable delay.

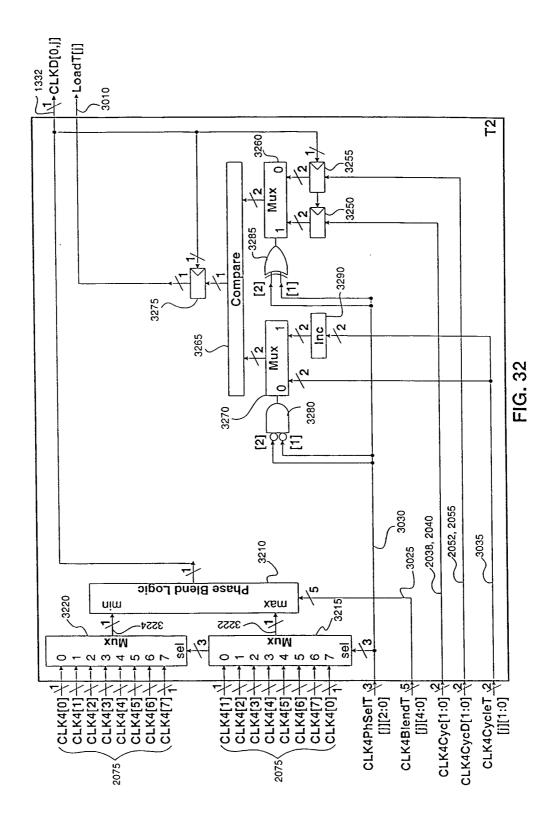

- FIG. 32 is a logic diagram for block T2, part of block T0, for creating a clock signal for transmitting write data.

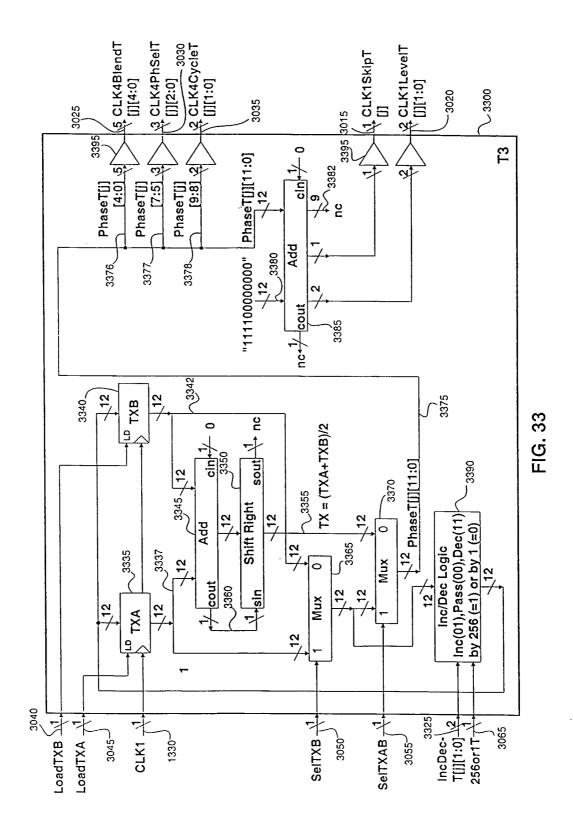

FIG. 33 is a logic diagram for block T3, part of block T0, for generating the value of a clock phase for transmitting write data.

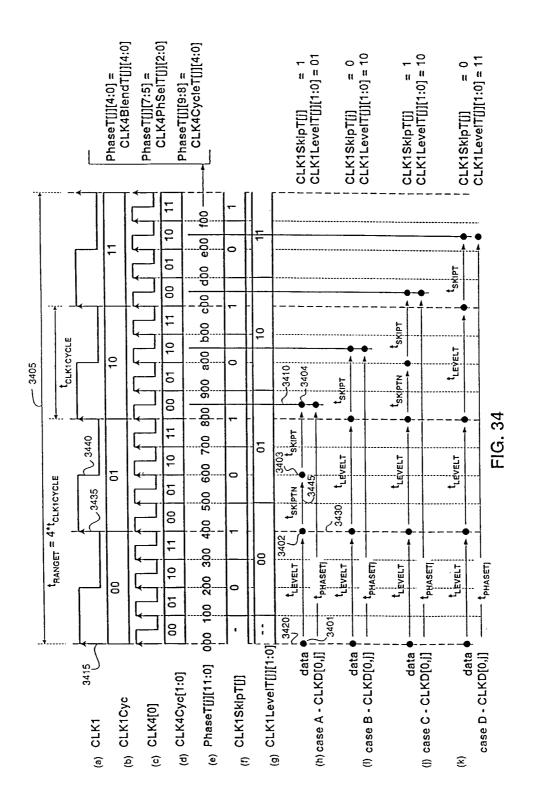

FIG. 34 shows a sequence of transmit timing signals illustrating four cases of alignment of a clock signal within a time interval and the generation of bus signals.

5

10

15

20

25

30

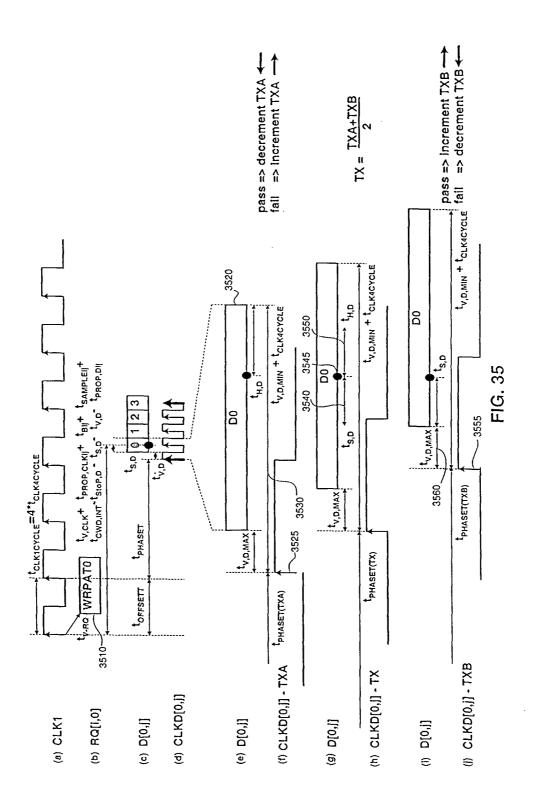

- FIG. 35 shows a sequence of timing signals that illustrate how timing values are related and maintained in TXA and TXB registers.

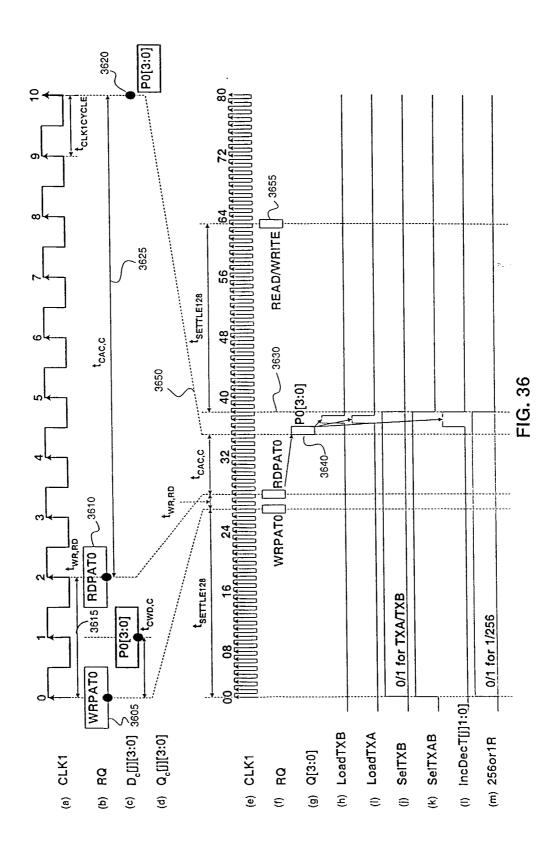

- FIG. 36 shows a sequence of transmit timing signals that illustrate a calibration sequence for transferring bus signals.

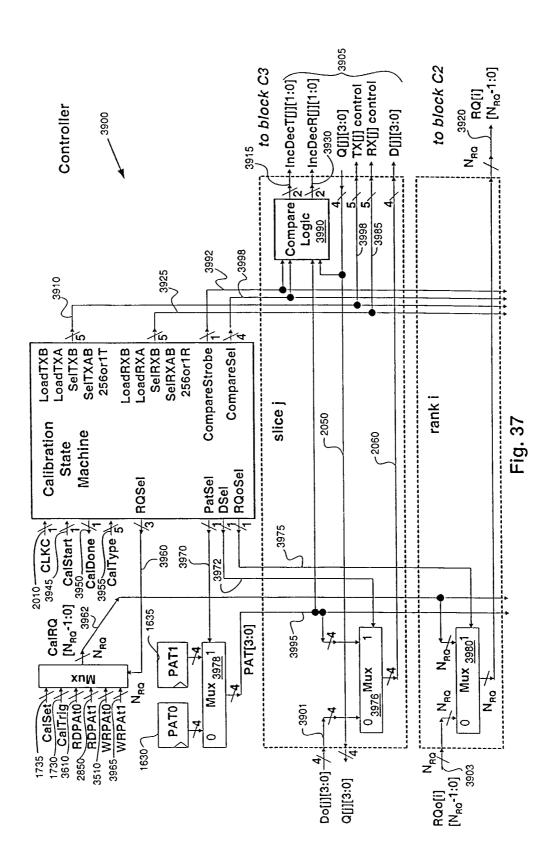

- FIG. 37 is a block diagram of the logic needed to perform the calibration processes of a preferred embodiment of the present invention.

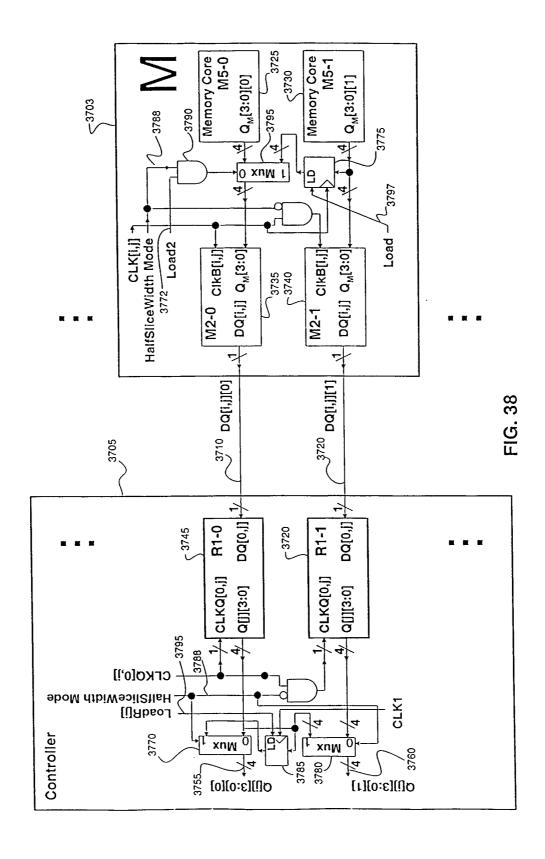

- FIG. 38 is a block diagram for a memory system to implement a power reduction mechanism.

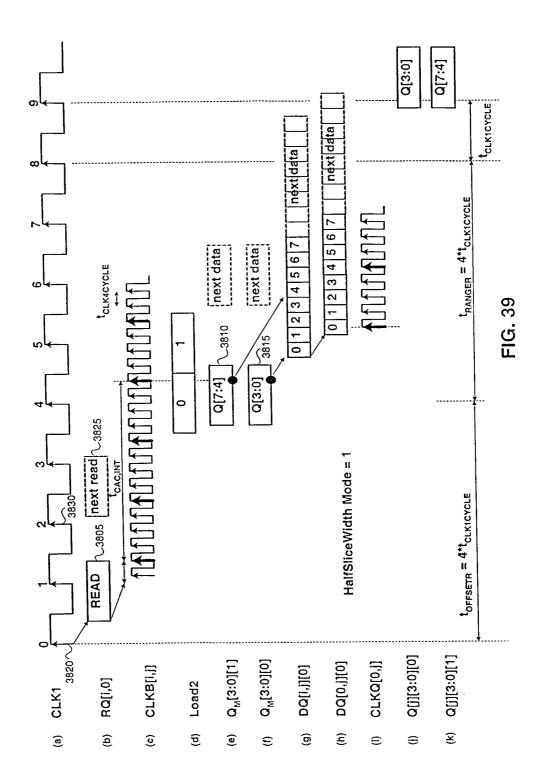

- FIG. 39 shows a sequence of timing signals for a read transaction in the memory system of FIG. 38.

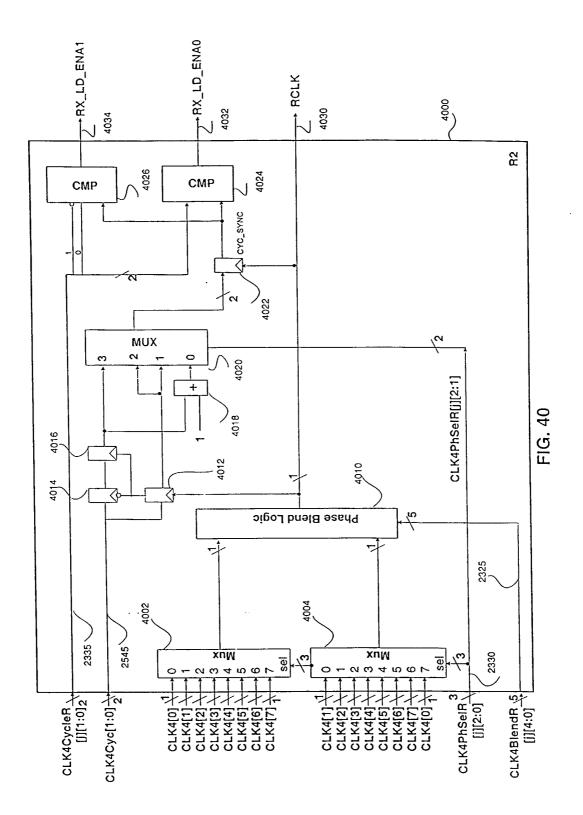

- FIG. 40 is another embodiment of a logic diagram of a controller module for createing a clock and control signals for receiving read data.

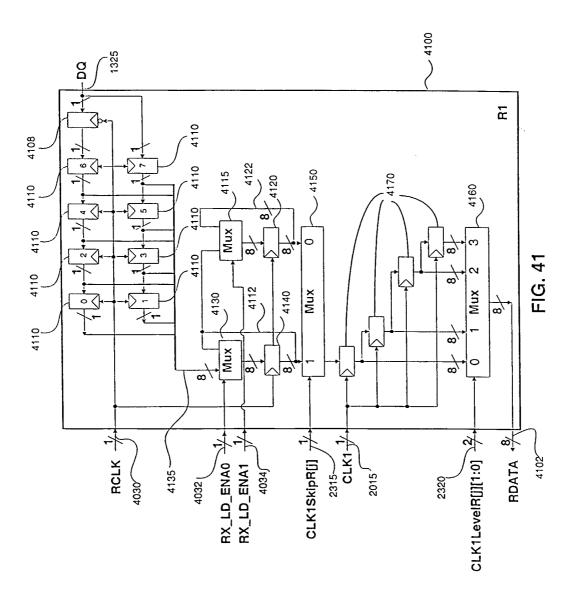

- FIG. 41 is another embodiment of a logic diagram of a controller module for receiving read data from a memory and inserting a programmable delay.

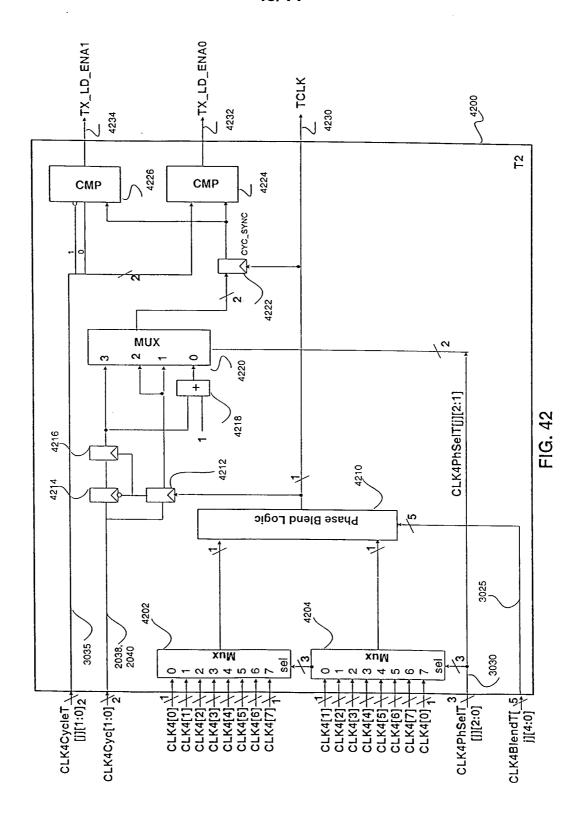

- FIG. 42 is another embodiment of a logic diagram of a controller module for creating a clock signal and control signals for transmitting write data.

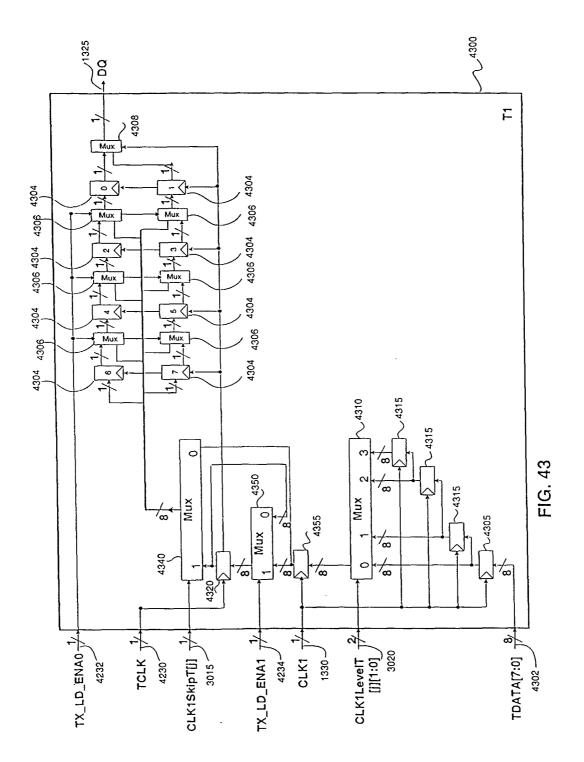

- FIG. 43 is another embodiment of a logic diagram of a controller module for transmitting write data and inserting a programmable delay.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The term "mesochronous" refers to a relationship between two signals having the same average rate or frequency, but which may have arbitrarily different phases. The term "mesochronous system" refers to a set of clocked components in which the clock signal for each clocked component has the same frequency, but can have a relative phase offset. The term "static mesochronous system" means that the relative phase offsets are fixed and do not vary during normal system operation. The approach of using fixed relative phase offsets that do not vary during normal system operation has been the method practiced in

prior art systems. The present invention is directed to "dynamic mesochronous systems" in which the phase offsets of the clocked components are allowed to drift over some range during system operation. The term "normal system operation" is used in this document to refer to ordinary memory access operations, such as read, write and refresh operations. Calibration operations, which are used to determine timing offsets required for successful

5

10

15

20

25

30

Calibration operations, which are used to determine timing offsets required for successful command and data transmission between the memory controller and memory components of a memory systems, are generally not considered to be normal memory operations. In the preferred embodiment, the calibration hardware in the memory controller is configured to perform calibration operations periodically, and/or during periods of little memory system usage, and such calibration operations are generally separated by periods during which normal memory operations are performed.

This document describes apparatus and techniques for managing the timing of signals within a system that can be beneficially applied to systems having a wide variety of signals, signal rates, time intervals, buses, signal-to-wire mappings, and so on. While the disclosed description will often identify a preferred embodiment or implementation to illustrate a concept, it should be understood that the concept is not limited to the embodiment or implementation employed in the discussion.

All of the variations of signal, symbol, bit, values, time intervals, buses, and signal-to-physical wire mapping are independent of the methods described in this document. This document describes a set of techniques for managing the timing of signals within a system that can be beneficially applied to all the variations described above. The following description will often choose a preferred variation to illustrate each concept. However, it should be understood that the concept under discussion is not limited to the particular variation that is employed in the discussion.

FIG. 2 shows an example of a prior art static mesochronous memory system 200. The memory system comprises a controller 205 communicating to and from memory 210 via unidirectional bus 215 and bi-directional bus 216. Bus 215 carries address and control information from the controller to the memory. Bus 216 carries data information from the controller to the memory during write operations and carries data information from the memory to the controller during read operations. Bus 215 is also referred to here as the RQ bus, and bus 216 is also referred to here as the DQ bus. This description will also refer

to separate D and Q signal sets, i.e., signal sets 217, 218 at the controller and signal sets 219, 220 at the memory, even though such signal sets share the same physical wires in this system.

5

10

15

20

25

30

Memory component 210 in FIG. 2, is one component of a two dimensional array of memory components, with ranks (rows) indexed by the variable "i" and slices (columns) indexed by the variable "j". Index values for the ranks are zero at the memory controller and assume integer values greater than zero as you move further away from the controller 205. In system 200, there is a single memory component in each rank. Other memory systems may have more than one memory component per rank. In this document, notation "[i,j]" is used to label a wire or bus at different physical points along a physical length. For example, the CTC[0,j] and CTC[i,j] signals are associated with two different points along the same physical wire. The notation is used throughout this document so that a wire or bus can be labeled or identified at any point along a signal transmission path.

Each slice of the memory components is attached to the DQ and RQ busses, which carry data signals and request signals, and to bus 230 (for receiving timing information or signals). Bus 230 (which is shown as three sub-buses 230(a), 230(b) and 230(c)), communicating a clock signal (CLK), carries timing information from the controller 205 to the memory component 210 so that information transfers on the other two buses can be coordinated.

The controller uses internal clock signal CLKC for its internal operations, including transmitting and receiving on the RQ and DQ buses. CLKC is routed so that it passes the memory controller and memory components a total of three times. Clock signal 225 is made up of three sub-signals: CTE (clock-to-end), CTC (clock-to-controller), and CFC (clock-from-controller). The controller drives the CTE signal, which travels to the end of the slice of components, and returns as CTC. CTC enters the controller, and leaves the controller (unbuffered) as CFC, and then travels back to the end of the slice. While a single pair of physical wires generally carries the three clock signals (with CTC and CFC being carried by the same physical wire), three different signal lines (i.e., wires) are shown in FIG. 2 for clarity.

CLKC is also used as a reference for the phase-loop lock (PLL) or delay-loop lock (DLL) circuit 255 that drives CTE[0,j] signals onto bus 230(a). The PLL/DLL circuit 255

internally generates the CTE[0,j] signal and adjusts the phase of the CTE[0,j] signal until the CTC[0,j] and CFC[0,j] signals have the same phase as the CLKC signal.

Memory components receive the CTC and CFC signals on buses 235 and 240, respectively. More specifically, each memory component has its own pair of clock input connections for receiving the CTC and CFC signals, respectively. The CTC[i,j] and CFC[i,j] signals that are received by a memory component [i,j] on buses 235, 240, respectively, have phases that are offset from CLKC and from each other due to propagation delays. The propagation delays on the clock bus 230 are essentially identical to propagation delays on the RQ and DQ busses, and thus the CTC[i,j] and CFC[i,j] signals are used by the memory component [i,j] to control the transmission of data signals on the DQ bus 216 and to control the receipt of control and data signals from the RQ and DQ busses, respectively.

5

10

15

20

25

30

The CTC and CFC signals on buses 235, 240 pass through PLL/DLL circuits 265, 270, respectively, within the memory component 210. Memory components use PLL or DLL circuits to ensure that the clock domains within the memory are phase-aligned with the external memory clock signals that provide the timing references. By phase aligning the clock signals in this fashion, memory sub-components 245, 250 receive timing information for transmitting and receiving on internal D and Q buses 219, 220.

Clock domain crossing logic 275 links the portions of the memory component 210 that operate in two clock domains. One domain is used for transmitting read data. The other domain is used for receiving write data and address/control information. Each memory component needs to pass information between the two clock domains, and this is controlled by the clock domain crossing logic 275.

FIG. 3 shows a timing diagram for system 200 (FIG. 2). The CLK signal 225 drives the PLL/DLL 255, which produces CTE[0,j] after a delay of t<sub>PLL/DLL</sub>. CTE[0,j] propagates to the end of the wire 230(a) and returns as the CTC signal to memory component [i,j]. The CTC[i,j] signal is delayed by t<sub>PROPtoEND</sub> relative to the CTE[0,j] signal. Read data Q[i,j] transmitted by the memory component to the controller is synchronized by the memory component [i,j] with the CTC[i,j] clock. The read data Q[i,j] signal set and the CTC[i,j] clock signal requires an additional delay of t<sub>PROPij</sub> to reach the controller to become Q[0,j] and CTC[0,j].

The PLL/DLL 255 adjusts the  $t_{PLL/DLL}$  delay so that the CTC[0,j] and CLK signals have the same phase alignment. This means that  $t_{PLL/DLL} + t_{PROPtoEND} + t_{PROPtj} = C*t_{CYCLE}$ , where C is an integer and denotes the number of CLK cycles required for the round trip of the clock signal from CTE[0,j] to CTC[0,j]. The CTC[0,j] signal becomes the CFC[0,j] signal and exits the controller. After a delay of  $t_{PROPtj}$  CFC[0,j] reaches a memory component as CFC[i,j], where it is used to receive the RQ[i,j] address/control information and D[i,j] write data information. The information on these two buses are delayed by  $t_{PROPtj}$  from the RQ[0,j] and D[0,j] buses, respectively.

5

10

15

20

25

30

In system 200, the controller is able to perform all transfer operations within the single clock domain of the CLKC signal. Each memory component, on the other hand, operates in two clock domains, as noted above. One domain is earlier in time than CLKC by  $t_{PROPij}$  and is used for transmitting read data. The other domain is later than CLKC by  $t_{PROPij}$  and is used for receiving write data and address/control information.

Note that in all of these cases of transfers on the RQ and DQ buses, the sampling (e.g., rising) edge of the clock that is used to receive a set of bits from a bus is shown as being aligned with the start of the valid window of the bits. In practice, the receiving clock will have its sampling edge aligned with the center of the valid window of the bits. The clock recovery circuits (PLL or DLL) present on both the controller and memory component can perform this alignment easily. For simplicity, this detail is not shown in the timing diagram. Although other static alignments of the clock with respect to the data may be used, one key point with respect to static systems is that the alignment does not change during system operation.

Phase offsets required for normal operation of system 200 are known or can be generated automatically by the system hardware. This determination of phase offsets can be done because the clock signals travel through a path that is essentially the same as the path of the data and address/control signals for which they provide a timing reference. The determination of phase offsets also requires that PLL or DLL circuits be used to maintain the static phase relationships.

In practice, such PLL or DLL circuits will not align the phase of two signals exactly; there will be some small error due to, for example, circuit jitter. Such jitter must be factored into the overall timing budget for transferring each bit of information on a

signal. This timing budget for transmitting and receiving a bit includes, for instance, setup and hold times of receive circuits and the variation of the output valid delay of the transmit circuits. However, the timing budget does not include a component for the round-trip propagation delay  $2*t_{PROPij}$  between the memory component and memory controller. The round-trip propagation delay  $2*t_{PROPij}$  is accounted for in the clock domain crossing logic 275. The accounting for round-trip propagation delay  $2*t_{PROPij}$  increases the latency of a read operation, but does not impact the bandwidth of read and write transfers. Such transfers will occur at a bandwidth that is determined by the circuits of the components, and not by the length of the wires that connect the components. The bandwidth determination based on circuit components is a critical factor in the advantage of static mesochronous systems over synchronous systems in which all components use clock signals that are at essentially the same phase. Since the transfers in the synchronous system must include the propagation delay term in the timing budget for a bit transfer, such inclusion of the delay term limits the bandwidth of transfers.

5

10

15

20

25

30

FIG. 4 shows a second example of a prior art static mesochronous memory system 300 comprising a controller 305 communicating to and from a memory component 310, which may be in an array of similar memory components. Like system 200, memory components form a two dimensional array, with ranks (rows) indexed by the variable "i" and slices (columns) indexed by the variable "j". As throughout this document, the index values are zero at the memory controller, and assume integer values greater than zero as you move further away from the controller. For example, in a system with a 2 x 3 array of memory components (i.e., three memory components in each of two ranks) the value of the "i" variable increases from zero at the controller to "1" for each of the three memory components in the first rank and to "2" for each of the three memory components in the second rank. Furthermore, in this exemplary system the value "j" increases from zero at the controller to "1" for each of the two memory components in the first slice, to "2" for each of the two memory components in the first slice, to "2" for each of the two memory components in the third slice.

Unlike system 200, in system 300 there can be more than a single memory component in each rank. Each rank of memory components is attached to an RQ bus 315 and a DQ bus 320. Other ranks are connected to different RQ buses and other slices are

connected to different DQ buses. The RQ bus 315 is unidirectional and carries address and control information from the controller to the rank of memory components. The CLK bus 317 is unidirectional and carries timing information from the controller to the memory components so that information transfers on the other two buses can be coordinated. The CLK bus 317 has the same topology as the RQ bus it accompanies. The slice of memory components is attached to DQ bus 320, which connects the controller and memory and is bi-directional, and carries data information from the controller to a memory component during write operations, and carries data information from a memory component to the memory controller during read operation.

5

10

15

20

25

30

The controller uses an internal clock CLKC, carried by internal bus 325, for its internal operations, including transmitting on the RQ bus 315. The CLKC signal is also used as a reference for the PLL or DLL circuit 330 that drives CLK[i,0]. The PLL/DLL 330 adjusts the phase of the CLK[i,0] signal to have the same phase as CLKC.

At the memory component 310, the CLK[i,j] signal is received offset in phase by a PLL or DLL circuit 335, which produces a buffered internal clock that is of essentially the same phase as received. This internal buffered clock signal is used to control transmission of read data onto the DQ bus 320 and to control the receipt of control and data signals from the RQ and DQ buses, as appropriate, generally to control the timing of operations performed by internal memory sub-components 340, 345 and 350. Because there is a single clock domain inside the memory component 310, there is no need for clock domain crossing logic in the memory component 310 as there was in system 200.

Instead, the clock domain crossing logic has been shifted to the controller 305 as clock domain crossing logic 375. The shift in logic 375 to the controller is because the write data D[0,j] transmit logic 365 and the read data Q[0,j] receive logic 370, must be operated in two clock domains, CLKD[0,j] and CLKQ[0,j], that have different phases than the CLKC domain used by the rest of the controller. As a result, phase adjustment logic is needed that delays CLKC by t<sub>Dij</sub> and t<sub>Qij</sub> to form the CLKD[0,j] and CLKQ[0,j] signals, respectively. The phase adjustment logic for the CLKD[0,j] and CLKQ[0,j] signals, are shown as circuit elements 380 and 355, respectively.

FIG. 5 shows a timing diagram for system 300 (FIG. 4). The CLK signal drives the PLL/DLL 330 to produce CLK[i,0]. The CLK[i,0] signal is delayed by t<sub>PROPCLKij</sub> as it

propagates to memory component [i,j] to become signal CLK[i,j]. The RQ[i,0] signal transmitted by controller element 360 is delayed by t<sub>PROPRQij</sub> as it propagates to memory component [i,j] to become the RQ[i,j] signal at internal memory component 350. The CLK and RQ buses are routed together, so that the two propagation delays are essentially the same.

5

10

15

20

25

30

In the controller, phase adjustment logic 380 delays CLK by  $t_{Dij}$  to form the CLKD[0,j] signal. This clock signal is used by the controller's data transmit element 365 to control the phase of the write data D[0,j]. The D[0,j] signal set is delayed by  $t_{PROPDij}$  as it propagates to memory component [i,j] to become signal set D[i,j]. The controller selects  $t_{Dij}$  so that  $t_{PROPCLKij} = t_{Dij} + t_{PROPDij}$ . There is also phase adjustment logic 355 in the controller that delays CLK by  $t_{Qij}$  to form the CLKQ[0,j] signal. This clock signal is used to receive the read data Q[0,j] at 370. The Q[i,j] signal set is delayed by  $t_{PROPQij}$  as it propagates from memory component [i,j] to become signal set Q[0,j]. The controller selects  $t_{Qij}$  so that  $t_{Qij} = t_{PROPCLKij} + t_{PROPQij}$ .

In the transfers on the RQ and DQ buses, the sampling (rising) edge of the clock that is used to receive a set of bits (or more generally, symbols) on a bus is shown aligned with the start of the valid window of the bits. In the real system, the receiving clock will typically have its sampling edge aligned with the center of the valid window of the bits. The clock recovery circuitry (PLL or DLL) that is present on both the memory controller and memory component can perform this alignment easily. Other static phase alignments of the signals on the CLK, RQ, and DQ buses are also possible. Memory components are able to perform all transfer operations within the single clock domain of the internal buffered clock signal. Each memory component will operate in its own unique clock domain. The phase of each clock domain will stay fixed relative to the phase of CLK in the controller; hence the reason for the term "static" mesochronous system.

The controller, on the other hand, has multiple clock domains. CLK is the principle domain, and CLKD[0,j] and CLKQ[0,j] are the domains (two for each slice [j]) used for transmitting and receiving, respectively. The phase offsets of CLKD[0,j] and CLKQ[0,j] are dependent, for example, upon the lengths of the wires that connect the components, and may have a range that is greater than the cycle time of CLK. Typically, the range of

phase offsets ( $t_{Dij}$  and  $t_{Qij}$ ) for CLKD and CLKQ is many times greater than the cycle time of CLK. The domain crossing logic 375 must accommodate these ranges of phase offsets.

Typically, the phase offsets or adjustment values  $t_{Dij}$  and  $t_{Qij}$  are determined at system initialization time. The values are stored and then used during normal system operation. Each rank [i] in the system needs its own set of phase adjustment values  $t_{Dij}$  and  $t_{Qij}$  that must be loaded prior to transferring data to or from a memory device in the rank. In practice, the PLL or DLL circuits of system 300 do not align the phase of two signals exactly, as there is always at least a small error because of circuit jitter, as described earlier. This jitter must be absorbed into the overall timing budget for transferring each bit of information.

5

10

15

20

25

30

As with system 200, the timing budget for transmitting and receiving a bit for system 300 does not include a budget allocation for the round-trip propagation delay,  $2*t_{PROPij}$ , between the memory component and controller. Instead, the round-trip propagation delay,  $2*t_{PROPij}$ , is accounted for by the clock domain crossing logic 375. The round-trip propagation delay increases the latency of read operations, but does not impact the bandwidth of read and write transfers. The transfers occur at a bandwidth that is determined by the circuits of the components, and not by the length of the signal wires that connect the components.

#### Dynamic Mesochronous Memory System

FIG. 6 shows an overview of a preferred embodiment of a dynamic mesochronous memory system 400 in accordance with the present invention. This system is topologically similar to system 300 with respect to the interconnection of components by buses and comprises a controller 405 for communicating to and from the memory components 410. In this system, there can be more than a single memory component in each rank and/or in each slice. Unless otherwise noted or described, reference numbers that differ by 100 for systems 300 and 400 represent circuit elements at the same topological locations and having at least some functional aspects in common, even if their internal design and operation differs substantially.

While the preferred embodiments will be described in terms of a memory controller and memory components, it is to be understood that the term "memory controller" includes any device that performs the functions of a memory controller described herein, and that the term "memory component" includes any device that performs the functions of a memory component or device described herein. For instance, if the functions of a memory controller are integrated with a central processing unit or with another controller device, the resulting device will be considered a "memory controller" in the context of the present invention. Similarly, if the memory storage, access and calibration functions of a memory device are integrated into another device, such as an application specific integrated circuit (ASIC), that device will be considered a "memory component" in the context of the present invention.

5

10

15

20

25

30

System 400 differs from system 300 in numerous respects. The following is a partial listing of significant differences between the two systems: (1) the memory component 410 has a clock buffer 443 instead of the PLL/DLL clock recovery circuits 330 and 335 of memory component 310; the clock buffer can have varying delay during system operation; (2) unlike memory component 310 and controller 305, the memory component 410 and controller 405 include calibration logic 485 and 490, respectively, to support a calibration process; (3) controller 405 includes enhanced clock domain crossing logic 475 to improve the efficiency of the calibration process. In addition, certain elements of the memory component 410, such as the RQ and DQ handling logic 450, 445, 440 include new logic or circuitry to support the calibration process. These new aspects of the memory component 410 and controller 405, as well as many others, are discussed below.

The clock signal used to time the transmission of signals (sometimes called requests) on the RQ[i,0] bus 415 is called CLK[i,0]. CLK[i,0] has essentially the same phase as CLKC. The CLK[i,j] signal that is received by memory component [i,j] will have a phase that is offset from CLKC. This CLK[i,j] signal is received by a simple clock buffer 443, which is much less complex and consumes much less power than the PLL or DLL circuits 330 and 335 in system 300. Buffer 443 produces a buffered internal clock CLKB[i,j] at 444 that is at a different phase than the CLK[i,j] signal, received by buffer 443. The CLKB[i,j] signal is used to transmit data onto the DQ bus 420, to receive signals (e.g., requests and data) from the RQ and DQ buses 415, 420, respectively, and to perform

all other internal operations in the memory 410. Because there is a single clock domain inside the memory, there is no need for clock domain crossing logic in the memory component, such as logic 275 of system 200.

Additionally, system 400 includes calibration logic 485 and 490. Calibration logic 485 is added to the memory 410, and logic 490 is added to the controller 405. The calibration logic circuits 485 and 490 operate in conjunction with one another so that delay variations during system operation are detected and complementary delay elements in logic 480, 455 are adjusted.

5

10

15

20

25

30

As in system 300, the write data D[0,j] transmit logic 465 and the read data Q[0,j] receive logic 470 must be operated in two clock domains, CLKD[0,j] and CLKQ[0,j], having different phases than the CLK signal domain used by the rest of the controller. As a result, there is phase adjustment logic 480 and 455 that delays CLK by t<sub>Dij</sub> and t<sub>Qij</sub>, respectively, to form the CLKD[0,j] and CLKQ[0,j] signals.

Also as in system 300, the values  $t_{Dij}$  and  $t_{Qij}$  are functions of the propagation delay parameters  $t_{PROPCLKij}$ ,  $t_{PROPDij}$ , and  $t_{PROPQij}$ . These propagation delay parameters are relatively insensitive to temperature and supply voltage changes. In system 300, once the values  $t_{Dij}$  and  $t_{Qij}$  have been generated during system initialization, they may be left static (unchanged) during system operation. But in system 400, the values  $t_{Dij}$  and  $t_{Qij}$  are also a function of the delay of the clock buffer  $t_{Bij}$  (as well as delay of other circuits such as the transmitters and receivers). This clock buffer delay will change during system operation because it is relatively sensitive to temperature and supply voltage changes. The values  $t_{Dij}$  and  $t_{Qij}$  that are generated during system initialization are dynamic (changing) during system operation, and a calibration process, using the calibration logic 485 and 490, keeps the values  $t_{Dij}$  and  $t_{Qij}$  updated.

In addition, enhancements are made to the clock domain crossing logic 475 in system 400 (relative to system 300) to improve the efficiency of the calibration process and so that the calibration process can be handled completely by hardware. Because the enhancement (i.e., hardware for implementing the calibration process) is implemented in hardware, primarily in the controller but also in the memory components, the performance of the system 400 is not significantly impacted by the overhead of the calibration process.

Within the memory component 410, receiver and transmitter circuits 440, 445, and 450 are able to perform all transfer operations within a single clock domain that is defined by the internal buffered clock signal generated by buffer 443. A clock domain is defined by a set of one or more clock signals that have the same frequency and phase. For convenience, a clock domain is often named using the name of the clock signal that defines the clock domain (e.g., "the CLK clock domain" is a clock domain defined by the CLK clock signal). Each memory component operates in its own clock domain, which may be unique for each memory component. The phase of the clock domain for each memory component can change relative to the phase of CLK in the controller; hence, the term "dynamic" mesochronous memory system.

5

10

15

20

25

30

The controller 405, on the other hand, has multiple clock domains defined by the CLK, CLKD[0,j] and CLKQ[0,j] clock signals. CLK on bus 425 is considered a principle clock domain, and CLKD[0,j] and CLKQ[0,j] are derived clock domains in that they are based on CLK by way of phase adjustment logic 480 and 455, respectively. CLKD[0,j] and CLKQ[0,j] are used for transmitting and receiving, respectively. The phase offsets  $t_{Dij}$  and  $t_{Qij}$  of CLKD[0,j] and CLKQ[0,j] are dependent upon the lengths of the wires that connect the components, parasitic capacitance along these wires, and upon the changing delay  $t_{Bij}$  of the memory component clock buffer 443. These phase offsets may have a range that is greater than the cycle time of CLK. In some cases the range may be many times greater. The domain crossing logic 475 accommodates these ranges of phase offsets and handles the phase offset range in hardware during calibration process updates.

Each rank [i] in the system will have its own set of phase adjustment values  $t_{Dij}$  and  $t_{Qij}$  that are loaded prior to transferring data to or from the rank. Each set of values are kept updated by the calibration process involving logic 485, 490.

The dynamic mesochronous system 400 has similar timing benefits to that of the static mesochronous system 300. For example, in system 400 the timing budget for transmitting and receiving a bit does not include the propagation delay  $t_{PROPij}$  between the memory component and controller. Instead, the round-trip propagation delay  $2*t_{PROPij}$  is accounted for in the clock domain crossing logic 475. This round-trip propagation delay increases the latency of a read operation, but does not impact the bandwidth of read and write transfers. The transfers occur at a bandwidth that is determined by the circuits of the

memory controller and memory components, and not by the length of the signal wires that connect the memory controller and memory components.

As noted, the clock recovery circuit 335 of the memory 310 is replaced by a simple clock buffer 443 in system 400. This change in system 400 results in a number of benefits. First, circuit area on the memory component is reduced. Additionally, the design complexity of the memory component is substantially reduced, particularly as the clock recovery circuit 335 often is a complex part of the memory design. Further, the standby power of the clock recovery circuit is eliminated. Standby power refers to the power dissipated when there are no read or write transfers taking place. Typically a PLL or DLL must dissipate some minimum amount of power to keep the output clock in phase with the input clock. In practice, this standby power requirement has made memory components with a DLL or PLL difficult to use in portable applications, where standby power is important.

5

10

15

20

25

30

System 400 introduces a memory system topology based on dynamic mesochronous clocking. A number of variations in system topology, element composition, and memory component organization are possible, and some preferred and representative variations will be described. Individual variations may, in general, be combined with any of the others to form composite variations. Any of the alternate systems formed from the composite variations can benefit from the method of dynamic mesochronous clocking.

FIG. 7 shows a baseline memory system topology 700. Topology 700 is similar to the topology of system 400, but with some modifications as described below.

The memory controller 705 is shown in FIG. 7. A single memory port 710, (labeled Port[1]) is shown, but the controller 705 could have additional memory ports. In general, a controller has other external signals and buses that are not directly related to the memory system(s), which for clarity purposes are not shown in FIG. 7.

The port 710 of the controller consists of two types of buses: the X bus and the Y bus. The X and Y buses are composed of wires for carrying different sets of signals and have different routing paths through the memory system. The X bus is depicted as comprising NS X buses shown as 715, 716, 717 and 718. System 700 also depicts the Y bus comprising the NM Y buses, shown as buses 720, 721. The NS X buses usually carries data signals and the NM Y buses usually carries address signals, but other signal

information configurations are possible. NM and NS are integers having values greater than zero.

Each of the NS X buses connect to the memory components along one "slice" (column). For example, the memory components along a slice are shown as components 730, 732, 734 and 736 in memory module 740. As shown, each of the NS X buses connect to one of the NS slices of each of the NM memory modules 740, 750. Typically, only the memory components along one slice will be active at a time, although variations to this are possible.

5

10

15

20

25

30

There are NM of the Y buses, with each Y bus connecting memory components on one "module" (set of ranks). For example, the memory components of the first rank (e.g., the leftmost rank shown in FIG. 7) are shown as components 730, 744, 746 and 748. Each of the NM memory modules can consist of NR ranks (rows) of memory components. Typically, all of the memory components of one rank of one module will be active at a time, although variations to this are possible. NM and NR are integers having values greater than zero. In some systems, the memory system may consist of NR ranks of memory components attached to the same printed circuit board (also called a wiring board) that holds the memory controller 705.

Each of the NM modules 740, 750 have a dedicated Y bus, i.e., one of the NM Y buses 720, 721, but typically most or all of the signals on a Y bus are duplicates of the signals on other Y buses. Some signals carried on the NM Y buses may be used to perform module or rank selection. These selection signals are generally not duplicated, but are dedicated to a particular module or rank.

Likewise, each of the NR ranks on a module connects to the module's dedicated Y bus. Typically, most or all of the signals composing the Y bus are connected to the memory components of each rank. Some signals on the NR ranks are used to perform rank selection. The rank selections signals are generally not duplicated, and connect to only the memory component(s) of one rank.

Generally, all signals transmitted on the X and Y buses are operated at the maximum signaling rates permitted by the signaling technology utilized. Maximum signaling rates often rely on the sequential connection of memory components to a physical wire by short stub wires branching from the physical wire. Maximum signaling

rates also imply careful impedance matching when signals are split (a physical wire becomes two physical wires) and when signals are terminated (the end of a physical wire is reached).

The Y bus signals on a module may pass through splitting elements (labeled "S" in the figures) in order to make duplicate copies of signals. Alternatively, the signals may connect sequentially to the memory components of one or more of the NR ranks (the figure shows sequential connection to two ranks). A module 740, 750 may contain as few as one or two ranks, in which case no splitting element is needed on the module at all.

Sample splitting element variations are shown in FIG. 10(a)-(d).

5

10

15

20

25

30

Returning to FIG. 7, the Y bus signals connect to termination elements 760 (labeled "T" in the figures) where the signals reach the end of a rank. Y bus signals are typically unidirectional, so termination elements are shown only at the memory end of the signals. If any Y bus signals were bi-directional, or if any Y bus signals drove information from memory to controller, then termination elements would be required on the controller end of the Y buses.

Sample bus termination element variations 760 are shown in FIG. 11(a)-(d).

Returning to FIG. 7, the X bus signals can pass through a splitting element on the same printed circuit board that holds the controller 705. One of the duplicate signals from a splitter, such as from splitter 752, 754, 756 or 758, enters one of the NM modules, such as module 740, and the other continues on the printed circuit board to the next module. The X bus signals connect sequentially to the memory components of each slice and end at a termination element such as on bus 765. Alternatively, if the system only contains a single memory module, no splitting elements would be needed for the X bus signals.

The X bus signals are typically bi-directional, so termination elements are needed at the controller end of each signal (e.g., where a termination element 762 connects to bus 718) as well as at the far end of the memory array. For any unidirectional X bus, termination elements would be required only at the end of the X bus that is opposite from the component that drives the signal.

Typically, all of the signals on the X bus are transmitted (or received) by all the memory components of each slice. In some embodiments, there may be some signals on

the X bus that are transmitted (or received) by only a subset of the memory components of a slice.

FIG. 8A shows a variation on the Y bus topology in which the controller 805 drives a single Y bus 810 to all the modules. A splitting element 812 is used to tap off a duplicate Y bus signal bus for each memory module, such as modules 820, 830. X bus splitters 816 sequentially connect the slices of each module. The use of external termination elements 818 is desirable when any X bus signals (on X buses  $X_1$  to  $X_{NS}$ , not separately shown) are bi-directional. Internal (i.e., internal to the modules 820, 822) splitter 822 and termination elements 824 are still used for each slice of each of the NM modules having NR ranks of memory components 828. In system 800 the controller drives fewer buses, but each Y bus signal will pass through a larger number of splitting elements. This increase in the number of splitting elements may impact signal integrity or propagation delay.

5

10

15

20

25

30

FIG. 8B shows a second variation on the Y bus topology in which the controller 855 drives the Y buses on the same group of physical wires 856, 858 as the X buses to the modules. In other words, the Y buses run parallel to the X buses in this embodiment. In system 850, there are no buses flowing along each of the NR ranks. There may be some signals in the X or Y bus used to perform a rank and module selection which connect to only a subset of the memory of a slice (only two slices are shown for simplicity). Alternatively, module and rank selection may be performed by comparing X or Y bus signals to an internal storage circuit (which may be located in each memory component) that contains the module or rank identification information. This method of module and rank selection could be used in any of the other topology variations. As with FIG. 8A, external termination elements 860 and external splitter elements 862 may be used, but only internal termination elements 864 are needed for each slice of the NM modules 870 having NR ranks of memory components 875.

System 900 in FIG. 9 shows a variation on the X bus topology of system 700 in which each X bus signal (e.g., on X bus 925) passes through one set of pins on each module and exits through a different set of pins. Controller 905 transmits X bus signals to memory modules 910, 920, and NM Y buses 930, 940 connect to each of the NM modules. No external splitting element is needed on the main printed circuit board, and

fewer internal termination elements 935 are needed on the modules. While extra pins are needed on each module, there is a reduction in the number of splitting and termination elements.

5

10

15

20

25

30

FIGS. 10A - 10D show some of the possible splitting element variations. In each of these figures, splitter element variations are shown where a single signal is split into two signals. In FIG. 10A, a splitter 1000 converts a single signal labeled "1" into two signals labeled "2", by the use of a clocked 1010 or unclocked 1020 buffer. In FIG. 10B, the signals are bi-directional, and signals can be split or combined. Generally, a single signal can pass through an enabled switch or buffer of the splitter 1030 to form two signals and any port can receive a signal component from any other port. Splitter element 1030 is a bi-directional buffer consisting of either a pass-through, non-restoring active switch 1035 with an enable control, or a pair of restoring buffers 1042, 1044 with a pair of enable controls in element 1040. Note that element 1030 could also be used for unidirectional signals.

Splitter element 1050 (FIG. 10C) is a unidirectional resistive device, implemented from either active or passive components. Splitter 1055 permits an attenuated signal to be passed to one of the output ports (labeled "2"), with the resistive value, R<sub>DAMP</sub>, chosen to limit the impedance mismatching that occurs. An alternative method would allow the characteristic impedance of the traces to be varied so that (in combination with a series resistance on one output port) there would be a smaller mismatch for unidirectional signals. Element 1060 (FIG. 10D) is a bi-directional power-splitting device, allowing the impedance to be closely matched for a signal originating on any of the three ports. The resistive devices, Z<sub>0</sub> in element 1065 or Z<sub>0</sub>/3 in element 1070, could be implemented from passive or active devices. FIGS. 10C and 10D are similar to FIG. 10B in that a signal input at any port can yield signals at the remaining two ports. Splitter element 1050 (FIG. 10C) utilizes a wire stub with series damping, and splitter element 1060 (FIG. 10D) utilizes an impedance- matching splitter. Like splitter element 1030 (FIG. 10B), the splitter elements 1050 and 1060 have bi-directional ports so that any port can be an input port and any port can receive a signal component from any other port.

FIGS. 11A to 11D show some of the possible termination element variations. Element 1100 (FIG. 11A) is a passive, external termination element. The element may be

implemented, for example, as a single device connected to a single termination voltage,  $V_{TERM}$ , or as two (or more) devices  $R_1$  and  $R_2$  in element 1108 connected to two (or more) termination voltages, such as  $V_{DD}$  and circuit ground. The termination element 1100 resides on a memory module or on a main printed circuit board.

5

10

15

20

25

30

Termination element 1120, shown in FIG. 11B, is an active, external termination element. It may be implemented, for example, as a single device 1110 in a termination element 1125 connected to a single termination voltage V<sub>TERM</sub>, or as two (or more) devices 1120 and 11320 in a termination element 1115 connected to two (or more) termination voltages, such as V<sub>DD</sub> and circuit ground. The termination element 1120 resides on a memory module or on a main printed circuit board. The voltage-current relationship needed for proper termination is generated by control voltage(s), which are maintained by an external circuit. Typically, the external circuit (not shown) measures a value that indicates whether the voltage-current relationship is optimal. If it is not, the external circuit makes an adjustment so the voltage-current relationship becomes more optimal.

Termination element 1160, shown in FIG. 11C, is a passive, internal termination element. This variation is similar to termination element 1100 except that termination element 1160 resides inside a memory component or inside the memory controller, both shown as component 1165. Termination element 1170, shown in FIG. 11D, is an active, internal termination element. The FIG. 11D variation is similar to termination element 1120 except that element 1170 resides inside a memory component or inside the memory controller, both shown as component 1175.

FIG. 12 shows a baseline system configuration 1200 for the memory component "M" that is shown in the system topology diagrams, such as element 730 in system 700. An X bus 1205 and a Y bus 1210 connect to memory component M. The X and Y buses correspond to the X and Y buses shown in topology FIGs. 7, 8A, 8B and 9. The memory component M contains interface logic for receiving and transmitting the signals carried by the X and Y buses. The memory component M also contains a memory core 1215 that consists of 2<sup>Nb</sup> independent banks. Here Nb is the number of bank address bits and is an integer greater than or equal to zero. The banks are capable of performing operations independent of one another, as long as the operations do not have resource conflicts, such as the simultaneous use of shared interface signals.

The Y Bus 1210 carries two signal sets: the row signal set 1220-1228 and the column signal set 1230-1238. Each group contains a timing signal (A<sub>RCLK</sub> 1220 and A<sub>CCLK</sub> 1230), an enable signal (A<sub>REN</sub> 1222 and A<sub>CEN</sub> 1232), an operation code signal set (OP<sub>R</sub> 1224 and OP<sub>C</sub> 1234), a bank address signal set (A<sub>BR</sub> 1226 and A<sub>CR</sub> 1236), and a row or column address signal set (A<sub>R</sub> 1228 and A<sub>C</sub> 1238). The number of signals carried by the signal sets are represented with a "/P", such as Nopr/P, Nopc/P, Nb/P, Nr/P, and Nc/P, respectively. The factor "P" is a serialization or multiplexing factor, indicating how many bits of a field are received serially on each signal. The demultiplexers 1240 and 1245 convert serial bits into parallel form. The P factors for Nopr, Nopc, Nr, Nc, and P may be integer values greater than zero. For example, there might be eight column address bits transmitted as two signals for the column address signal set, meaning that four column address bits are received sequentially on each signal. The P factor for this example would be four. Memory component 1200 (i.e., the baseline memory component) uses the same P factor for all the sub-buses of the Y bus, but different factor values could also be used for different sub-buses in the same memory component. Here, P is an integer greater than zero.

5

10

15

20

25

30

It is also possible that the signal sets could be multiplexed onto the same wires. The operation codes could be used to indicate which signal set is being received. For example, the bank address signal sets could share one set of wires, and the row and column address signal sets could share a second set of wires, and the operation code signal sets could share a third set of wires.

The six signal sets (i.e., signals 1224-28, 1234-38) are received by circuitry in the memory component 1200 that uses the timing signals ( $A_{RCLK}$  and  $A_{CCLK}$ ) as a timing reference for when a bit is present on a signal. These timing signals, for example, could be a periodic clock or they could be a non-periodic strobe. An event (i.e., a rising or falling edge) could correspond to each bit, or each event could signify the presence of two or more sequential bits (with clock recovery circuitry creating two or more timing events from one). In some implementations the six signal sets share a single timing signal.

The enable signals 1222 and 1232 indicate when the memory system 1200 needs to receive information on the associated signal sets. For example, an enable signal may be used to pass or block the timing signals entering the memory component, depending on the

value of the enable signal, or an enable signal might cause the operation code signal set to be interpreted as no-operation, or the enable signal may be used by logic circuitry to prevent information from being received when the value of the enable signal indicates that such information is not for receipt of the memory component 1200.

5

10

15

20

25

30

The enable signals can be used to select a first group of memory components and to deselect a second group, so that an operation will be performed by only the first group. For example, the enable signals can be used for rank selection or deselection. The enable signals can also be used to manage the power dissipation of a memory component in system 1200 by managing power state transitions. In some embodiments, the enable signals for the row and column signal groups could be shared. Further, each enable signal shown could be decoded or formed from two or more signals to facilitate the task of component selection and power management.

The de-multiplexed row operation code, row bank address, and row address are decoded by decoders 1250, 1252 and 1254, and one of the 2<sup>Nb</sup> independent banks is selected for a row operation. A row operation may include sense or precharge operations. In a sense operation, one of the 2<sup>Nr</sup> rows contained in a bank selected by outputs of the decoders is coupled to a column sense amplifier for the bank. For a precharge operation, a selected bank and its column sense amplifier are returned to a precharged state, ready for another sense operation.

The de-multiplexed column operation code, column bank address, and column address are decoded via decoders 1256, 1258 and 1260, and one of the 2<sup>Nb</sup> independent banks is selected for a column operation such as read or write. A column operation may only be performed upon a bank that has been sensed (not precharged). For a read operation, one of the 2<sup>Nc</sup> columns (with Ndq bits) contained in a column sense amplifier portion of the selected bank is read and transmitted on the Q signal set 1290 / 1268. For a write operation, Ndq bits received on the D signal set (i.e., signals 1270-76) is written into one of the 2<sup>Nc</sup> columns contained in the column sense amplifier portion of the selected bank, using the Nm mask bits on sub-bus 1292 to control which bits are written and which are left unchanged.

The X bus 1205 carries two sets of signals: the read signal set and the write signal set. The read signals include signals 1262-1268, and the write signals include signals

1270-1276. Each group contains a timing signal (Q<sub>CLK</sub> 1264 and D<sub>CLK</sub> 1274), an enable signal (Q<sub>EN</sub> 1262 and D<sub>EN</sub> 1276), a mark or mask signal set (Q<sub>M</sub> 1266 and D<sub>M</sub> 1270, respectively), and a data signal set (Q 1268 and D 1272). The number of signals in the signal sets are represented with a "/N", such as Ndq/N, Nm/N, and Ndq/N, respectively. The factor "N" is a serialization or multiplexing factor, indicating how many bits of a field are received or transmitted serially on each signal. The "mux" and "demux" blocks converts the bits from parallel-to-serial and serial-to-parallel form, respectively. The parameters Ndqr, Nm, and N may contain integer values greater than zero. This baseline memory system 1200 assumes that the read and write data signal sets have the same number of signals and use the same multiplexing factors. This might not be true in other memory components, and therefore the number of signals in each signal set may vary. In some embodiment, the read and write data signal sets are multiplexed onto the same wires.

5

10

15

20

25

30

The mark signal set provides a timing mark through mark logic 1286 to indicate the presence of read data. The mark signal set might have the same timing as the read data signal set, or it might be different. The mask signal set 1292 indicates whether a group of write data signals should be written or not written as determined by mask logic 1288. This baseline memory system assumes that the mark and mask signal sets have the same number of signals and use the same multiplexing factors. This assumption might not hold true in other embodiments. It is also possible that, in other embodiments, the mark and mask data signal sets could be multiplexed onto the same wires. In other embodiments, one or both of the mark and mask signal sets might not be implemented.

The data signal sets 1290, 1294 are received by circuitry 1284, 1278 that uses the timing signals ( $Q_{CLK}$  and  $D_{CLK}$ ) as a timing reference for when a bit is present on a signal. These timing signals could be, for example, a periodic clock, or they could be a non-periodic strobe or any other timing reference. An event (e.g., a rising or falling edge of a timing signal) could correspond to each bit, or each event could signify the presence of two or more sequential bits (with clock recovery circuitry creating two or more timing events from each received event). It is possible that the data signal sets could share a single timing signal. It is also possible that the X and Y buses could share a single timing signal.

The enable signals  $Q_{EN}$  and  $D_{EN}$  1262 and 1276 indicate when the memory component needs to receive information on the associated signal sets. For example, an enable signal might pass or block the timing signals entering the memory component, or it may be used to prevent information from being transmitted or received. The enable signals can be used for slice selection or for managing power state transitions.

5

10

15

20

25

30

FIG. 13 shows the overview topology of an alternate preferred dynamic mesochronous memory system 1300. System 1300 is topologically similar to system 400 with respect to the interconnection of components by buses. For example, memory components would still form a two dimensional array, with ranks (rows) indexed by the variable "i" and slices (columns) indexed by the variable "j", following the same notation as before. In system 1300, like system 400, there can be more than a single memory component in each rank. Each rank of memory components is attached to an RQ bus 1315 and a CLK bus 1320. RQ bus 1315 is unidirectional and carries address and control information from the controller to the memory components. CLK bus 1320 is unidirectional and carries timing information from the controller 1305 to the memory components 1310 so that information transfers on the other two signals sets can be coordinated.

Each slice of memory is attached to a DQ bus 1325. DQ bus 1325 is bi-directional, and carries data information from the controller 1305 to a memory component 1310 during write operations, and carries data information from a memory component to the controller during read operation. This description will also refer to the D and Q signal sets separately to include signal sets 1327 and 1329, respectively, even though the same physical wires are shared.

The CLK1 signal is also used as a reference to drive the CLK[i,0] signal on bus 1320, CLKD[0,j] signal on bus 1332 and CLKQ[0,j] signal on bus 1334. The frequency of the clock signals such as CLK4 and CLK[i,0] is an integer multiple of the frequency of CLK1 by way of frequency multiplier 1335 (which is a 4X frequency multiplier in a preferred embodiment). This multiplication is done so that the frequency of CLK[i,0] matches the frequency of the clock used to transmit and receive write data D and read data Q.

The clock signal CLK1 is used to transmit signals on the RQ[i,0] bus 1315. When frequency multiplier 1335 is a 4X multiplier, the rate at which bits are transferred on the RQ bus is one fourth the rate at which bits are transferred on the D and Q signal sets. This transfer rate differential is consistent with the fact that a relatively small amount of address and control information is needed for transferring a relatively large block of read or write data. Other transfer rate differentials between RQ and DQ are possible.

5

10

15

20

25

30

The CLK[i,j] signal 1340 that is received by memory component [i,j] 1310 will have a phase that is offset from CLK[i,0]. The CLK[i,j] signal is received by a simple clock buffer 1345. This buffer 1345 produces a buffered internal clock signal CLKB[i,j] on bus 1347 that is at a different phase than the CLK[i,j] signal. This CLKB[i,j] signal is used to transmit on signal set 1349 to the DQ bus 1325, to receive from the RQ and DQ buses, and to perform all other internal operations in the memory component. Because there is a single clock domain (i.e., CLKB[i,j]) inside the memory component 1310, there is no need for clock domain crossing logic in the memory component as there was in system PA1 (of FIG. 2). In addition, calibration logic 1350 ("M<sub>CAL</sub>") has been added to the memory component 1310. In system 1300, this logic 1350 is used in conjunction with the calibration logic 1355 ("C<sub>CAL</sub>") that has been added to the controller 1305.

Because the internal clock CLKB[i,j] of the memory component runs at four times the rate of the RQ[i,j] bus 1352, it is possible to use sampling logic 1360 within the memory to adjust for unknown skew between the internal clock signal CLKB[i,j] on bus 1347 and the bit signals on RQ interface line 1352 that is caused by the buffer delay t<sub>Bij</sub>.

As in the controller of system 400, write data D[0,j] transmit logic and the read data Q[0,j] receive logic must be operated in two different clock domains (CLKD[0,j] and CLKQ[0,j]) that have different phases than the CLK1 domain that the rest of the controller uses. As a result, there is phase adjustment logic 1365 and 1368 that delays CLK1 by t<sub>Dij</sub> and t<sub>Qij</sub>, respectively, to form the CLKD[0,j] and CLKQ[0,j] signals, respectively. Because of the multipliers 1335, CLKD[0,j] and CLKQ[0,j] are also four times the frequency of CLK1.

As in system 400, the values  $t_{Dij}$  and  $t_{Qij}$  are functions of the propagation delay parameters  $t_{PROPCLKij}$ ,  $t_{PROPDij}$ , and  $t_{PROPQij}$ . These propagation delay parameters are relatively insensitive to temperature and supply voltage changes. Values  $t_{Dij}$  and  $t_{Qij}$  are

also a function of the delay  $t_{Bij}$  of the memory component's clock buffer 1345 as well as other delays such as those associated with transmit and receive circuits. The clock buffer delay will change during system operation because it is relatively sensitive to temperature and supply voltage changes. The programmable values  $t_{Dij}$  and  $t_{Qij}$  that are generated during system initialization are dynamically updated during system operation, and a calibration process (using the calibration logic  $M_{CAL}$  and  $C_{CAL}$ ) is needed to keep the values updated.

5

10

15

20

25

30

In system 1300, enhancements have been made to the clock domain crossing logic 1380 so that the calibration process is handled completely by hardware. Such enhancements are useful to insure that the performance of the system is not significantly impacted by the overhead of the calibration process.

Some of the important differences between system 300 (FIG. 4) and system 1300 are listed below:

- (1) System 1300 has a clock buffer 1345 (which can have variable delay during system operation), rather than a PLL/DLL clock recovery circuit on the memory component;

- (2) System 1300 has calibration logic 1350 and 1355 to the memory component and controller, respectively, to support a calibration process;

- (3) System 1300 has enhanced clock domain crossing logic 1380 to improve the efficiency of the calibration process;

- (4) Signal transmission on the RQ bus 1315 may be at a lower frequency than the CLK and DQ buses (one fourth the rate of the CLK1 signal in this example); and

- (5) System 1300 includes sampling logic 1360 in the memory component for the RQ bus.

- FIG. 14A shows the timing of a read transfer for system 1300. As noted, the controller 1305 uses an internal clock signal CLK1, 1330, for its internal operations. Rising edge 0, 1410, of the CLK1 signal 14(a) samples the signal on the internal  $RQ_C$  bus 1385 with a register and causes the register to drive the sampled signal value onto the RQ[i,0] bus 1315 after the delay  $t_{V,RQ}$ . This delay is the output valid delay (the clock-to-output delay) of the register and driver that samples RQ and drives it out of the controller. The address and control information associated with the read command is denoted by the

label "READ" in the figure. The RQ[i,0] signals on the RQ bus 1315 propagate to memory component [i,j] after a propagation delay  $t_{PROP,RQij}$  to become the RQ[i,j] signals, where they are received by the memory component. The setup time of the signal on bus RQ[i,j] is  $t_{S,RQ}$ , measured to the rising edge 1455 of CLKB[i,j] that causes sampling to be performed by the sampling logic 1360.