【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成18年10月5日(2006.10.5)

【公開番号】特開2000-150906(P2000-150906A)

【公開日】平成12年5月30日(2000.5.30)

【出願番号】特願平11-240758

【国際特許分類】

|        |        |           |

|--------|--------|-----------|

| H 01 L | 29/786 | (2006.01) |

| G 09 F | 9/30   | (2006.01) |

| G 02 F | 1/1368 | (2006.01) |

| H 01 L | 21/336 | (2006.01) |

【F I】

|        |        |         |

|--------|--------|---------|

| H 01 L | 29/78  | 6 1 9 A |

| G 09 F | 9/30   | 3 3 8   |

| G 02 F | 1/1368 |         |

| H 01 L | 29/78  | 6 1 2 Z |

| H 01 L | 29/78  | 6 2 7 A |

【手続補正書】

【提出日】平成18年8月22日(2006.8.22)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

絶縁表面に形成されたゲート電極と、

前記ゲート電極を覆って形成され、絶縁性有機樹脂でなる平坦化膜と前記平坦化膜上の

絶縁性無機膜とでなる積層膜を有するゲート絶縁膜と、

前記ゲート絶縁膜を覆う半導体層とを有し、

前記半導体層は結晶性半導体膜で形成されていることを特徴とする半導体装置。

【請求項2】

絶縁表面上に形成されたゲート電極と、

前記ゲート電極上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、チャネル形成領域、ソース領域、ドレイン領域を有す

る半導体層と、

を有する薄膜トランジスタを用いた回路を有し、

前記半導体層は結晶性半導体膜で形成され、

前記ゲート電極と前記半導体層で挟まれた前記ゲート絶縁膜の部分には、前記ゲート電

極に接する絶縁性有機樹脂でなる平坦化膜と、前記平坦化膜上の絶縁性無機膜とが積層さ

れていることを特徴とする半導体装置。

【請求項3】

請求項2において、

前記平坦化膜の膜厚は、その上に前記チャネル形成領域が存在する部分よりも、その上

に前記ソース領域及び前記ドレイン領域が存在する部分のほうが厚いことを特徴とする半

導体装置。

【請求項4】

請求項2において、

前記半導体層は、前記チャネル形成領域と前記ソース領域との間、及び前記チャネル形成領域と前記ドレイン領域との間にそれぞれ低濃度不純物領域を有し、

前記平坦化膜の膜厚は、その上に前記チャネル形成領域が存在する部分よりも、その上に前記低濃度不純物領域が存在する部分のほうが厚いことを特徴とする半導体装置。

【請求項 5】

請求項 2 乃至 4 のいずれか 1 項において、

前記半導体層上には絶縁膜でなる保護膜が接して形成され、

前記ソース領域及び前記ドレイン領域に添加されている導電型を付与する不純物が、前記保護膜の少なくとも一部に添加されていることを特徴とする半導体装置。

【請求項 6】

請求項 2 乃至 5 のいずれか 1 項において、

前記保護膜は、前記ソース領域及び前記ドレイン領域上に存在しないことを特徴とする半導体装置。

【請求項 7】

請求項 6 において、

前記保護膜のチャネル長方向の幅は、前記チャネル長より広いことを特徴とする半導体装置。

【請求項 8】

請求項 2 乃至 7 のいずれか 1 項において、

前記薄膜トランジスタを用いた回路は、アクティブマトリクス基板のマトリクス回路であり、前記薄膜トランジスタには画素電極が接続されていることを特徴とする半導体装置。

【請求項 9】

請求項 8 に記載のアクティブマトリクス基板を用いたことを特徴とする液晶表示装置。

【請求項 10】

請求項 9 に記載の液晶表示装置を用いたことを特徴とする電子機器。

【請求項 11】

請求項 1 乃至 8 のいずれか 1 項において、

前記平坦化膜はベンゾシクロブテン、ポリイミド又はアクリルで形成されていることを特徴とする半導体装置。

【請求項 12】

絶縁表面にゲート配線を形成する工程と、

前記ゲート配線を覆って絶縁性有機樹脂でなる平坦化膜を塗布法で形成する工程と、

前記平坦化膜に接して絶縁性無機膜を形成する工程と、

前記絶縁性無機膜上に非晶質成分を有する半導体膜を形成する工程と、

前記非晶質成分を有する半導体膜を結晶化して結晶性半導体膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【請求項 13】

絶縁表面に形成された薄膜トランジスタを用いた回路を有する半導体装置の製造方法において、

絶縁表面にゲート配線を形成する工程と、

前記ゲート配線を覆って絶縁性有機樹脂でなる平坦化膜を塗布法で形成する工程と、

前記平坦化膜に接して絶縁性無機膜を形成する工程と、

前記絶縁性無機膜上に非晶質成分を有する半導体膜を形成する工程と、

前記非晶質成分を有する半導体膜に接して保護膜を形成する工程と、

前記非晶質成分を有する半導体膜を結晶化して結晶性半導体膜を形成する工程と、

前記保護膜の少なくとも一部を通過させて前記結晶性半導体膜に不純物を添加して、ソース領域、ドレイン領域を形成する工程と、

を有し、

前記絶縁性無機膜、前記非晶質成分を有する半導体膜、及び前記保護膜を、大気開放せ

ずに順次積層して形成することを特徴とする半導体装置の製造方法。

【請求項 1 4】

請求項1 2 又は 1 3に記載の平坦化膜を形成する工程において、前記平坦化膜をベンゾシクロブテン、ポリイミド又はアクリルで形成することを特徴とする半導体装置の製造方法。

【請求項 1 5】

請求項1 2 乃至 1 4のいずれか 1 項に記載の結晶性半導体膜を形成する工程は、前記非晶質成分を有する半導体膜に 400 nm 以下の波長のレーザ光又は強光を照射することにより行うことを特徴とする半導体装置の製造方法。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】0 0 0 6

【補正方法】変更

【補正の内容】

【0 0 0 6】

また、TFT の構造として、代表的にボトムゲート型（代表的には、逆スタガ型）とトップゲート型（代表的には、コプラナ型）が知られている。ボトムゲート型は基板上にゲート配線（電極）、ゲート絶縁膜、半導体層がこの順序で積層され、トップゲート型は逆に半導体層、ゲート絶縁膜、ゲート配線（電極）の順で積層されている。

【手続補正 3】

【補正対象書類名】明細書

【補正対象項目名】0 0 1 4

【補正方法】変更

【補正の内容】

【0 0 1 4】

また、多結晶シリコンを用いた TFT では、オフ電流が大きいことが問題となっている。オフ電流の原因は、TFT がオフ状態の時に、ドレイン電極 9 に印加された電圧が、チャネル形成領域 6 C、ドレイン領域 6 D との接合部に集中するために、この接合部分でトラップを介して電流が漏れるためだと考えられている。

【手続補正 4】

【補正対象書類名】明細書

【補正対象項目名】0 0 2 4

【補正方法】変更

【補正の内容】

【0 0 2 4】

なお、上記構成において、非晶質成分を有する半導体膜とは、結晶性のない非結晶性半導体膜、又は結晶性を有するが 100 nm 以上のオーダーの結晶粒が殆どない半導体薄膜であって、具体的には非晶質半導体膜、微結晶半導体膜を指す。微結晶半導体膜は、数 nm ~ 数十 nm の大きさの結晶粒を含む微結晶と非晶質との混相状態の半導体膜である。

【手続補正 5】

【補正対象書類名】明細書

【補正対象項目名】0 0 5 4

【補正方法】変更

【補正の内容】

【0 0 5 4】

実施形態 1 と同様、基板 20 を用意し、基板 20 表面に下地膜 21 を形成する。下地膜 21 表面上に、上述した導電性材料でなる膜を成膜し、テーパー状にパターニングして、ゲート配線 22 を形成する。次に、ゲート配線 22 を覆って、ゲート絶縁膜 23 を形成する。まず、スピンドルコータを用いて、平坦化膜 23 a として、BCB、ポリイミド、アクリルなどの絶縁性有機樹脂膜を形成する。次に、スパッタ法又は CVD 法により、平坦化膜 2

3 a 上に  $\text{SiO}_2$  膜、  $\text{SiN}_y$  膜、  $\text{SiO}_x \text{N}_y$  膜等の絶縁性無機膜 2 3 b を積層する。

(図 2 (A))

【手続補正 6】

【補正対象書類名】明細書

【補正対象項目名】0 0 5 5

【補正方法】変更

【補正の内容】

【0 0 5 5】

次に、非晶質成分を有する半導体膜 2 4 と、  $\text{SiO}_2$  、  $\text{SiN}_y$  、又は  $\text{SiO}_x \text{N}_y$  でなる保護膜 2 5 を大気開放しないで積層する。成膜手段としては、 CVD 法、スパッタ法を用いることができる。大気に曝さないことで、半導体膜 2 4 - 保護膜 2 5 界面にも大気からの汚染物質が付着しないようにする。半導体膜 2 4 、保護膜 2 5 は同一チャンバーで連続成膜してもよいし、マルチタスク型のスパッタ装置又は CVD 装置を用いて、それぞれ専用のチャンバーで成膜してもよい。

【手続補正 7】

【補正対象書類名】明細書

【補正対象項目名】0 0 6 8

【補正方法】変更

【補正の内容】

【0 0 6 8】

次に、  $\text{SiO}_2$  、  $\text{SiN}_y$  又は  $\text{SiO}_x \text{N}_y$  から選ばれた絶縁膜の単層膜又は多層膜でなる層間絶縁膜 4 0 を形成し、ソース / ドレイン領域 3 5 、 3 6 に対するコンタクトホールを形成し、金属膜を成膜しパターニングして、信号線となるソース配線 4 1 、 ドレイン電極 4 2 を形成する。

【手続補正 8】

【補正対象書類名】明細書

【補正対象項目名】0 0 8 3

【補正方法】変更

【補正の内容】

【0 0 8 3】

以下、図 7 に示す装置を用いて、膜 1 0 3 ~ 1 0 6 の積層膜を形成する方法を説明する。まず、スピンドルで BCB 溶液を塗布・乾燥処理済みの基板を加熱室 3 0 7 に移動する。加熱室 3 0 7 を窒素雰囲気とし、 2 5 0 で焼成して、 BCB 膜 1 0 3 を形成する。次に、ロボットアーム 3 1 0 により基板を CVD 室 3 0 4 へ移動し、原料ガスに  $\text{SiH}_4$  と  $\text{N}_2\text{O}$  を反応ガスに用いて、基板温度 3 0 0 で  $\text{SiO}_x \text{N}_y$  膜（絶縁性無機膜） 1 0 4 を成膜する。そして、  $\text{SiH}_4$  だけを供給して、基板温度 3 0 0 で非晶質シリコン膜 1 0 5 を成膜する。再び、  $\text{SiH}_4$  と  $\text{N}_2\text{O}$  を供給して、基板温度 3 0 0 で  $\text{SiO}_x \text{N}_y$  膜（保護膜） 1 0 6 を成膜する。成膜済みの基板をロードロック室 3 0 2 又は 3 0 3 へと移動して、装置から搬出する。

【手続補正 9】

【補正対象書類名】明細書

【補正対象項目名】0 0 8 4

【補正方法】変更

【補正の内容】

【0 0 8 4】

ここでは、1つの CVD 室 3 0 4 で膜 1 0 4 ~ 1 0 6 を連続成膜して、基板移動に伴う温度変化や汚染を回避するようにしたが、工程のスループットや装置のガス供給系等の設計などを鑑みて、絶縁性無機膜 1 0 4 、半導体膜 1 0 5 、保護膜 1 0 5 を個別の CVD 室で成膜してもよい。また、半導体膜である非晶質シリコン膜 1 0 5 と、絶縁膜である無機膜 1 0 4 を保護膜 1 0 6 とで成膜する CVD 室を分けてもよい。

**【手続補正10】****【補正対象書類名】**明細書**【補正対象項目名】**0099**【補正方法】**変更**【補正の内容】****【0099】**

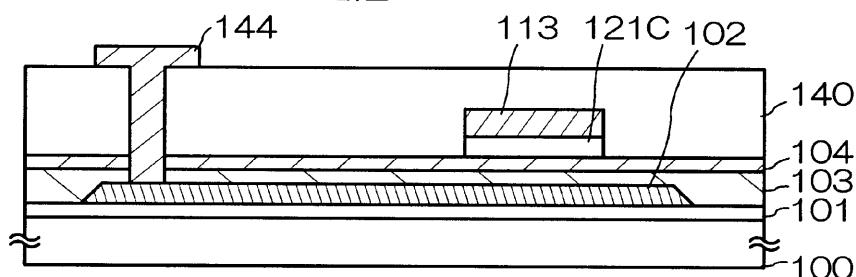

本実施例では、ゲート配線102をテープ状にしたため、実施形態2で述べたようにゲート配線102の傾斜部と平面部ではBCB膜103の膜厚が異なるので、ゲート寄生容量がチャネル形成領域から外側になるほど小さくなる。よって、オフ状態において、チャネル形成領域121C、131Cに印加されている電圧を寄生容量が小さい部分に分散させることができる。特に、Pチャネル型TFTではゲート配線102にオーバーラップしているが、このオーバーラップ部分の寄生容量はチャネル形成領域131Cよりも小さいため、チャネル形成領域131Cとソース／ドレイン領域131S、131Dの接合部に集中する電圧を緩和することができ、オフ電流を小さくすることができる。

**【手続補正11】****【補正対象書類名】**明細書**【補正対象項目名】**0104**【補正方法】**変更**【補正の内容】****【0104】**

フォトレジストマスク151、保護膜152をマスクにして、リンイオンをプラズマドーピング法により添加して、多結晶シリコン膜にN型の不純物領域153を選択的に形成する。（図8（B））

**【手続補正12】****【補正対象書類名】**明細書**【補正対象項目名】**0108**【補正方法】**変更**【補正の内容】****【0108】**

なお、ボロン添加工程で、加速電圧、ドーザ量、ドーピング回数等の条件を適宜設定することにより、P<sup>+</sup>型領域161のうち保護膜152で覆われている領域のボロン濃度を小さくして、P<sup>-</sup>型領域とすることもできる。

**【手続補正13】****【補正対象書類名】**明細書**【補正対象項目名】**0112**【補正方法】**変更**【補正の内容】****【0112】**

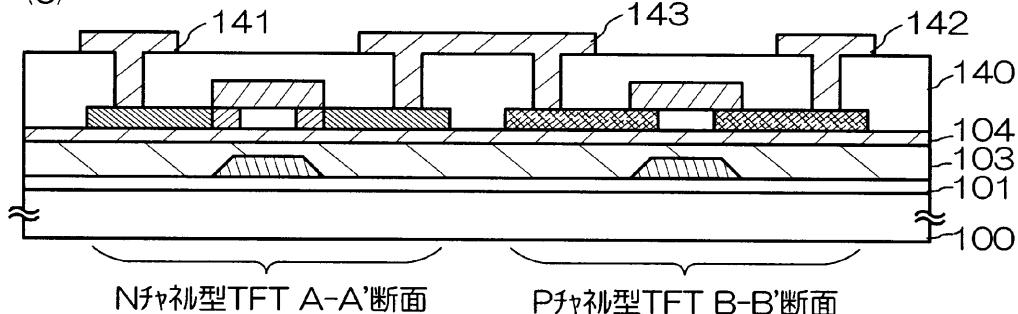

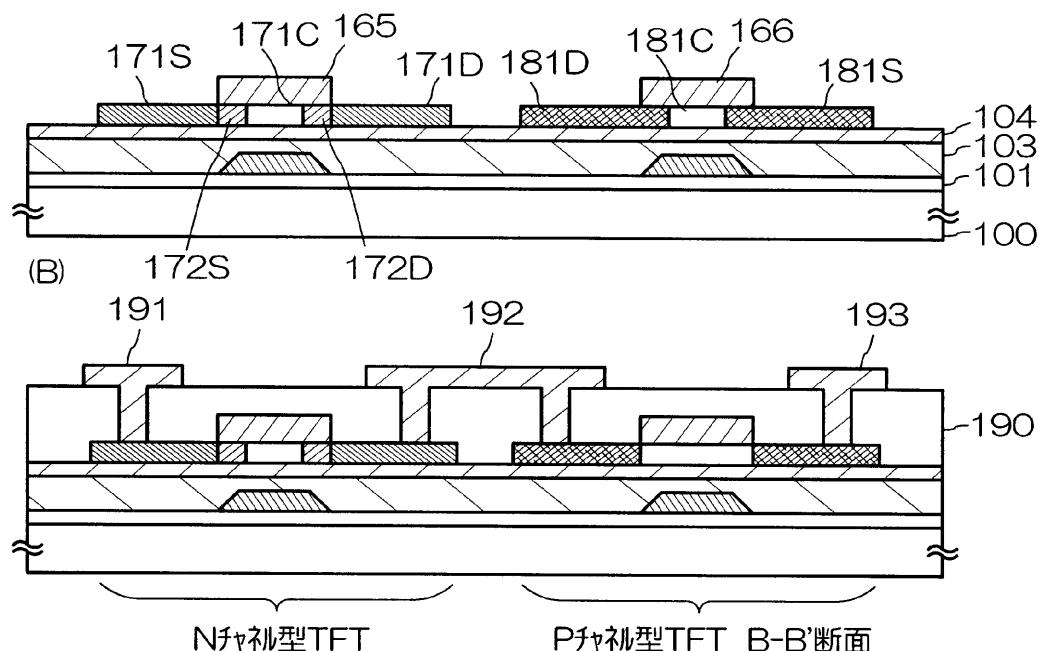

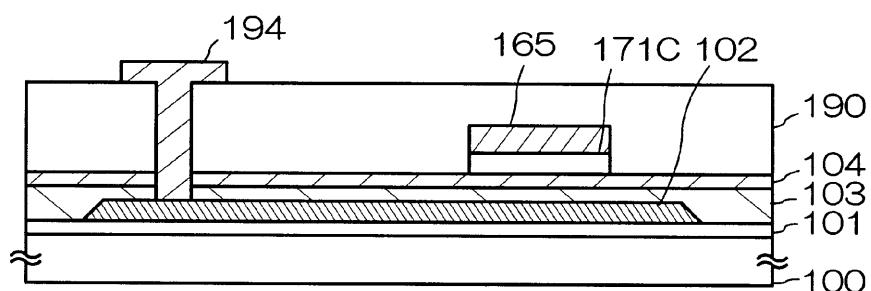

次に、半導体層を覆う層間絶縁膜190を形成する。ここでは、50nm厚のSiNy膜と、900nm厚のSiO<sub>2</sub>膜とでなる積層膜を形成する。層間絶縁膜190にソース／ドレイン領域に対するコンタクトホールと、ゲートコンタクト部に対してコンタクトホールを形成する。更に、ゲートコンタクト部において、SiO<sub>x</sub>N<sub>y</sub>でなる絶縁性無機膜104、BCBでなる平坦化膜103をエッチングしてゲート配線102に達するコンタクトホールを形成する。次に、150nm厚のTi膜／300nm厚のAl膜／100nm厚のTi膜でなる積層膜を形成しパターニングして、配線191～193、及び取出し電極194を形成して、CMOS回路を完成する。（図9（B））

**【手続補正14】****【補正対象書類名】**明細書**【補正対象項目名】**0129**【補正方法】**変更

**【補正の内容】****【0129】**

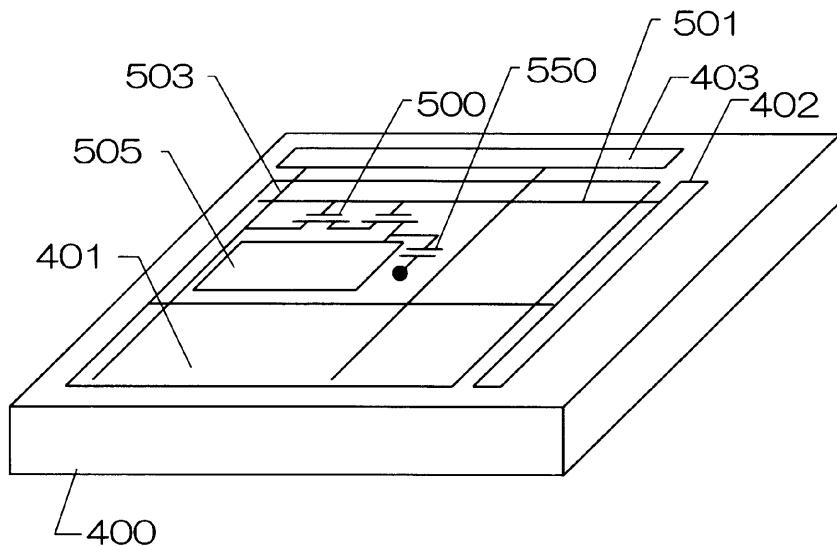

走査線 501 は画素マトリクス回路 401 の行ごとに形成され、信号線 503 は列ごとに形成されている。走査線 501、信号線の交差部近傍には、配線 501、503 に接続された画素 TFT500 が形成されている。画素 TFT500 には画素電極 505、コンデンサーである保持容量 550 が接続されている。

**【手続補正15】**

【補正対象書類名】明細書

【補正対象項目名】0130

【補正方法】変更

**【補正の内容】****【0130】**

まず、実施例 1 の TFT の製造工程に従って、駆動回路 402、403 の N チャネル型 TFT、P チャネル型 TFT、画素マトリクス回路 401 の画素 TFT500 を完成する。

**【手続補正16】**

【補正対象書類名】図面

【補正対象項目名】図 6

【補正方法】変更

**【補正の内容】**

## 【図6】

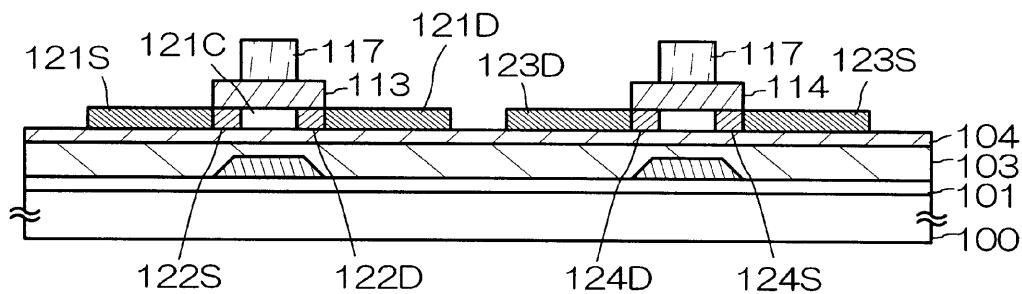

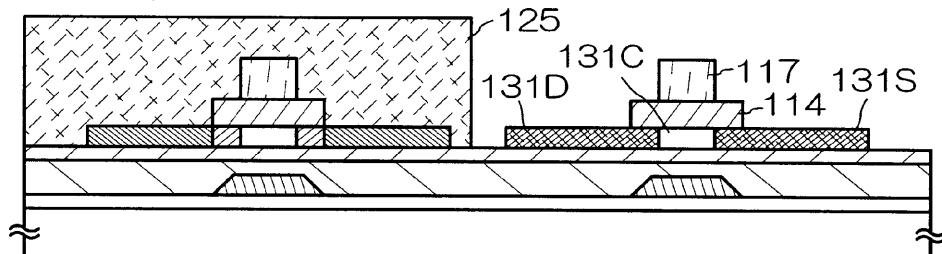

(A) N型領域の形成

(B) P型領域の形成

(C)

(D) Nチャリ型TFT C-C'断面

100:ガラス基板 101:下地膜 102:ゲート配線 103:平坦化膜(BCB膜)

104:絶縁性無機膜(SiOxNy膜) 106,113,114:保護膜(SiOxNy膜)

117,125:フォトレジストマスク

121S:N-領域(N<sup>+</sup>型領域) 121D:P-領域(N<sup>+</sup>型領域) 121C:チャリ形成領域122S,122D,124S,124D:低濃度不純物領域(N<sup>-</sup>型領域)131S:P-領域(P<sup>+</sup>型領域) 131D:P-領域(P<sup>+</sup>型領域) 131C:チャリ形成領域

140:層間絶縁膜 141-144:配線

## 【手続補正17】

【補正対象書類名】図面

【補正対象項目名】図9

【補正方法】変更

【補正の内容】

## 【図9】

(A) 半導体層のパターニング

(C) Nチャル型TFT

165,166:保護膜(SiO<sub>x</sub>N<sub>y</sub>膜)171S:Y-ス領域(N<sup>+</sup>型領域) 171D:ドレイン領域(N<sup>+</sup>型領域) 171C:チャル形成領域172S,172D:低濃度不純物領域(N<sup>-</sup>型領域)181S:Y-ス領域(P<sup>+</sup>型領域) 181D:ドレイン領域(P<sup>+</sup>型領域) 181C:チャル形成領域

## 【手続補正18】

【補正対象書類名】図面

【補正対象項目名】図12

【補正方法】変更

【補正の内容】

【図12】

400: 基板

401: 画素マトリクス回路

402: 走査線駆動回路、403: 信号線駆動回路

500: 画素TFT

501: 走査線 503: 信号線 505: 画素電極 550: 保持容量