(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 10 2007 010 882 B4 2009.01.29

(12)

## Patentschrift

(21) Aktenzeichen: 10 2007 010 882.8

(51) Int Cl.<sup>8</sup>: H01L 21/58 (2006.01)

(22) Anmelddatum: 06.03.2007

H01L 23/48 (2006.01)

(43) Offenlegungstag: 25.09.2008

H01L 21/60 (2006.01)

(45) Veröffentlichungstag

der Patenterteilung: 29.01.2009

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(73) Patentinhaber:

Infineon Technologies AG, 81669 München, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

DE10 2005 001713 A1

DE 42 35 908 A1

EP 13 50 588 A2

JP 05-2 91 314 A

In Vakuumlötanlagen: Oxidations- und lunkerfreies

Löten. In: Elektronik Produktion und Prüftechnik (EPP), ISSN 0943-0962, Nov. 1994, S. 38-40; Energie sparendes Lötverfahren für lunkerfreie Verbindung:

Im Vakuum löten. In: Elektronik Produktion und Prüftechnik (EPP), ISSN 0943-0962, Juni 2001, S. 24;

(74) Vertreter:

Westphal, Mussgnug & Partner, 80331 München

(72) Erfinder:

Gabler, Volker, 59519 Möhnesee, DE; Licht,

Thomas, Dr., 59581 Warstein, DE

(54) Bezeichnung: **Verfahren zur Herstellung einer Lötverbindung zwischen einem Halbleiterchip und einem Substrat**

(57) Zusammenfassung: Die Erfindung betrifft ein Verfahren zur Herstellung einer Lötverbindung (1) zwischen einem Halbleiterchip (2) und einem Substrat (3). Das Substrat (3) weist einen lötbaren Oberflächenbereich (4), auf dem eine Lotschicht (5) angeordnet ist, auf. Der Halbleiterchip (2) ist mit seiner Rückseite (10) auf der Lotschicht (5) fixiert, wobei die Lotschicht (5) ein Lotmaterial (6) aufweist, das mehrfach aufschmelzbar und vacuumfest ist. Zur Herstellung der Lötverbindung (1) wird zunächst der Halbleiterchip (2) mittels eines Bondverfahrens auf dem Oberflächenbereich (4) fixiert. Anschließend wird die gebondete Lötverbindung (1) in einem Vakuumlötofen (20) bei schmelzflüssigem Zustand der Lotschicht (5) evakuiert, um eine lunkerfreie Lotschicht (5) zu erreichen.

**Beschreibung****HINTERGRUND**

**[0001]** Die Erfindung betrifft ein Verfahren zur Herstellung einer Lötverbindung zwischen einem Halbleiterchip und einem Substrat. Ein derartiges Substrat weist üblicherweise einen lötbaren Oberflächenbereich auf, auf dem eine Lotmaterialschicht angeordnet ist. Der Halbleiterchip ist mit seiner Rückseite auf der Lotmaterialschicht fixiert. Diese Fixierung wird mit Hilfe eines Diebondverfahrens erreicht. Die Diebondtechnologie ist jedoch für große Chipflächen über 25 mm<sup>2</sup> Größe und für große Verlustleistungsdichten ungeeignet, da sich beim Diebonden Lunker bilden, die eine inhomogene Stromverteilung in der Lotschicht verursachen, wodurch lokale Überhitzungen auftreten können, welche beim Betrieb eines Halbleiterbauelements ein Ablösen des Halbleiterchips von dem Substrat bewirken können. Außerdem besteht die Gefahr, dass bei nachfolgenden Fertigungsschritten, die sich an das Diebonden anschließen, die in den Lunkern eingeschlossenen flüchtigen Substanzen bei erhöhter Temperatur einen derartigen Druck ausüben, dass die Lotmaterialschicht beschädigt wird.

**[0002]** Somit ist die Fertigung auf kleinfächige Chips beschränkt, bei denen mit geringen Verlustleistungsdichten zu rechnen ist, so dass Restlunker der Diebondtechnologie in der Lotmaterialschicht der Lötverbindung toleriert werden können. Für große Verlustleistungsdichten werden deshalb Löttechnologien mit einem Vakumschritt unter Verwendung von Lötpasten oder vorgestanzten Lötplättchen eingesetzt, wobei für den Vakuumlötschritt kostenintensive Präparationen der stoffschlüssig zu verbindenden Komponenten getroffen werden müssen, um beispielsweise sicherzustellen, dass Halbleiterchip, Lötplättchen und vorgesehener Oberflächenbereich des Substrats kongruent ausgerichtet bleiben und sich im Vakuumlötschritt nicht dejustieren.

**[0003]** JP 05-291 314 A lehrt, einen nackten Chip zunächst vorläufig auf eine Wärmesenke zu löten und nach Inspektion ein abermaliges Aufschmelzen in einem Vakuumofen durchzuführen.

**[0004]** DE 4235908 A1 offenbart ein Verfahren zum Auflöten eines scheibenförmigen Halbleiterkörpers auf einen Träger, wobei der Träger zunächst mit einem Lotformteil und anschließend mit dem Halbleiterkörper belegt wird. Der Halbleiterkörper wird vor dem Verlöten mit dem Träger durch eine Reibbewegung mit einer senkrecht zur Verbindungsebene wirkenden Kraft auf das Lotformteil aufgelegt und justiert. Dabei besteht eine punktuelle Verbindung zwischen dem Halbleiterkörper und dem aufgelegten Lotformteil. Abschließend wird die so entstandene Anordnung in einem Ofenprozess auf eine derartige

Temperatur erhitzt, dass der Halbleiterkörper und der Träger miteinander verlötet werden.

**[0005]** Das Dokument mit dem Titel „Oxidations- und lunkerfreies Löten“ in Elektronik Produktion und Prüftechnik (EPP), ISSN 0943-0962, November 1994, Seite 38–40, beschreibt Vakuumlötanlagen für das Löten von Chips, wie zum Beispiel Leistungsbauenteile, auf ein Substrat oder direkt auf einen Kühlkörper. Als übliche benetzende Oberflächen werden dabei Kupfer, Silber, Nickel und Nickel/Palladium/Gold und als Lote SnAg, PbSnAg, PbSn und PbSnIn angegeben.

**[0006]** Das Dokument mit dem Titel „Im Vakuum löten“, in Elektronik Produktion und Prüftechnik (EPP), ISSN 0943-0962, Juni 2001, Seite 24, beschreibt eine Durchlaufanlage und ein Batchverfahren, bei dem mehrere Halbleiterchips auf einem Substrat aufgebracht werden.

**[0007]** DE 10 2005 001 713 A1 offenbart ein Verfahren zum Herstellen eines Verbindungsaufbaus, der ein erstes und ein zweites Verbindungsteil aufweist, die mit einem sich dazwischen befindenden Lot verbunden sind. Das Verfahren weist die Schritte eines beidseitigen Umfassens der Lotschicht zwischen dem ersten und dem zweiten Verbindungsteil, eines Dekomprimierens des ersten und des zweiten Verbindungsteils mit der Lotschicht hinunter zu einem ersten Druck bei einem Aufrechterhalten einer ersten Temperatur, welche kleiner als ein Solidus des Lots ist, eines Erwärmens des ersten und zweiten Verbindungsteils mit der Lotschicht hinauf zu einer zweiten Temperatur bei einem Aufrechterhalten des ersten Drucks, wobei die zweite Temperatur höher als ein Liquidus des Lots ist, eines Komprimierens des ersten und des zweiten Verbindungsteils mit der Lotschicht hinauf zu einem zweiten Druck bei einem Aufrechterhalten der zweiten Temperatur, wobei der zweite Druck höher als der erste Druck ist, und eines Verfestigens des Lots bei einem Aufrechterhalten des zweiten Drucks auf.

**[0008]** EP 1350588 A2 offenbart ein Verfahren zur Herstellung eines Halbleiterbauelements, das eine geringe Anzahl von Hohlräumen in seinen Lötverbindungsschichten aufweist, bei dem unter Verwendung eines kurzzeitigen Lötprozesses ein Laminat, zum Beispiel aus Keramik das eine strukturierte Metallbeschichtung und Kontaktanschlussflächen aufweist, verlötet wird. Das Laminat weist eine metallisierte Leiterbahnschicht auf. Das Laminat einschließlich einer Metallbasis, einer Lotschicht, einem Isoliersubstrat, einer zweiten Lotschicht und ein Siliziumchip werden in einem Schmelzofen angeordnet. Nach dem Evakuieren des Schmelzofens wird dieser mit Wasserstoff gefüllt, bis der Druck in diesem höher ist als der Umgebungsdruck. Nach dem Erwärmen und Schmelzen des Lots, wird der Schmelzofen evaku-

iert, um Hohlräume im Lot zu entfernen. Danach wird erneut Wasserstoff eingeleitet, um die Ausformung tunnelähnlicher Löcher zu verhindern und um eine gleichmäßige Lotübergangsschicht zu erzielen. Das Laminat wird dann schnell abgekühlt, um die Lotstruktur feiner auszubilden.

**[0009]** Aufgabe der vorliegenden Erfindung ist es daher, ein Verfahren zur Herstellung einer Lotverbindung anzugeben, das die oben beschriebenen Verfahren nach dem Stand der Technik verbessert und eine Kostenoptimierung des Herstellungsprozesses ermöglicht.

**[0010]** Die Aufgabe wird gelöst durch ein Verfahren zur Herstellung einer Lotverbindung gemäß Anspruch 1. Ausgestaltungen und Weiterbildungen des Erfindungsgedankens sind Gegenstand von Unteransprüchen.

## ÜBERBLICK

**[0011]** Es wird ein Verfahren zur Herstellung, einer Lotverbindung zwischen einem Halbleiterchip und einem Substrat vorgestellt, bei dem das Substrat einen lötbaren Oberflächenbereich aufweist, auf dem eine Lotmaterialschicht angeordnet ist. Der Halbleiterchip ist mit seiner Rückseite auf der Lotmaterialschicht fixiert, wobei die Lotmaterialschicht ein Lotmaterial aufweist, das mehrfach aufschmelzbar und vakuumfest ist, wobei zum Diebonden und Vakuumerschmelzen ein Durchlaufverfahren verwendet wird.

## KURZBESCHREIBUNG DER FIGUREN

**[0012]** Ausführungsbeispiele der Erfindung werden nachfolgend mit Bezug auf die beigefügten Figuren beschrieben.

### Kurze Figurenbeschreibung

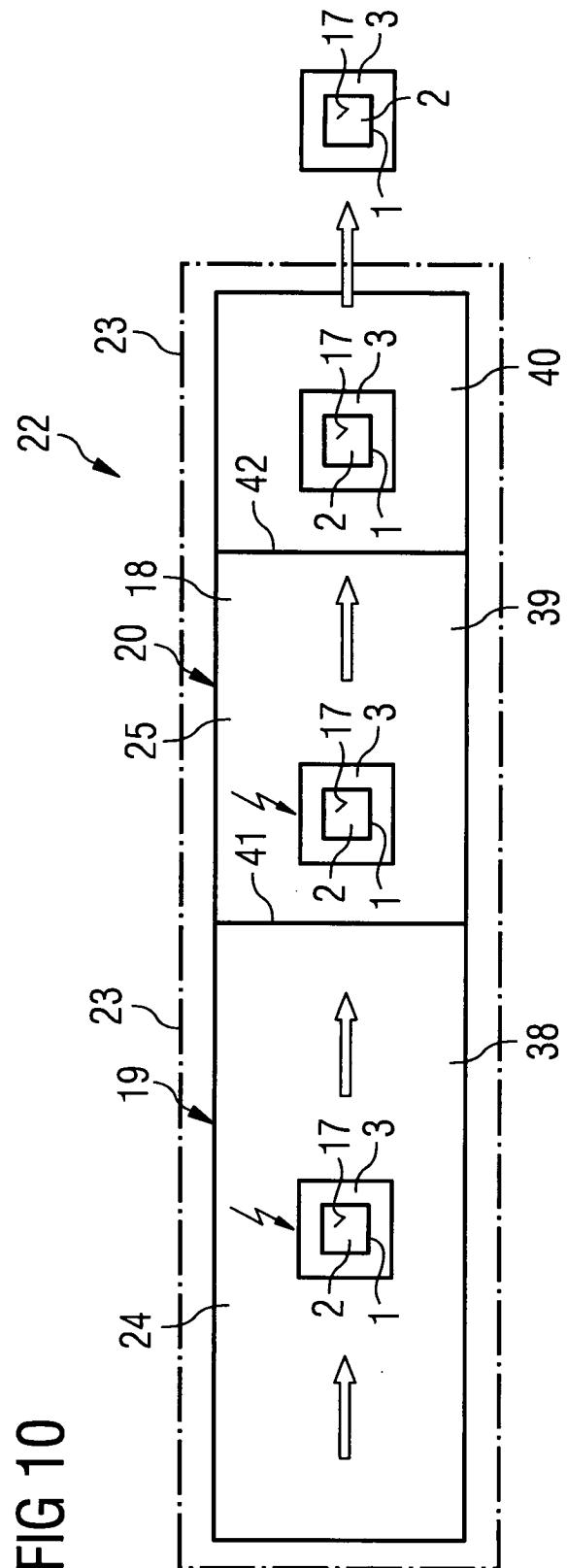

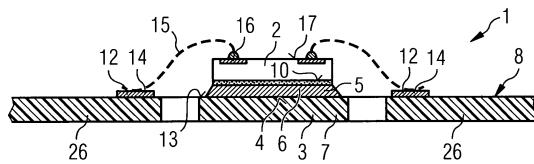

**[0013]** [Fig. 1](#) zeigt einen schematischen Querschnitt durch eine beispielhafte Lötverbindung;

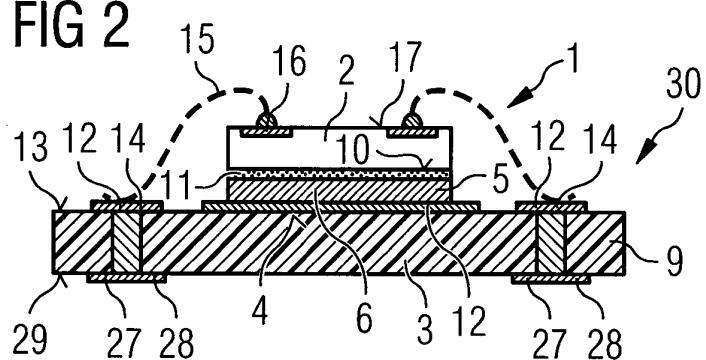

**[0014]** [Fig. 2](#) zeigt einen schematischen Querschnitt durch eine beispielhafte Lötverbindung;

**[0015]** [Fig. 3](#) bis [Fig. 7](#) zeigen Prinzipskizzen von Komponenten bei der Herstellung einer Lötverbindung;

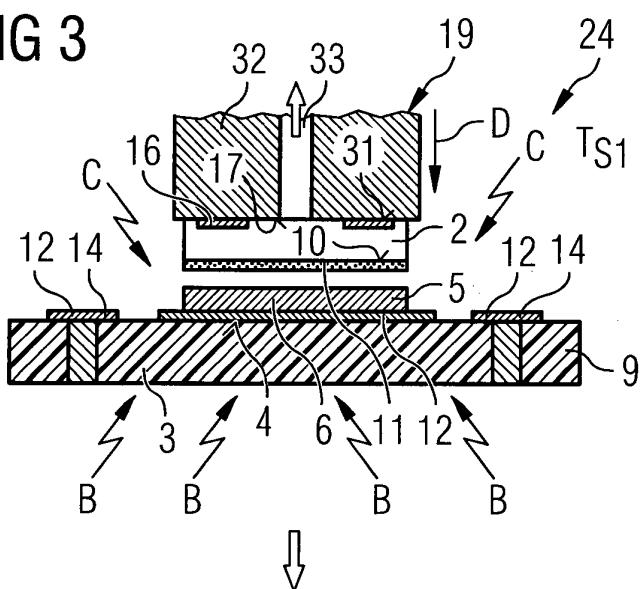

**[0016]** [Fig. 3](#) zeigt eine Prinzipskizze einer Diebondposition eines Diebonders mit einem Halbleiterchip und einem Substrat;

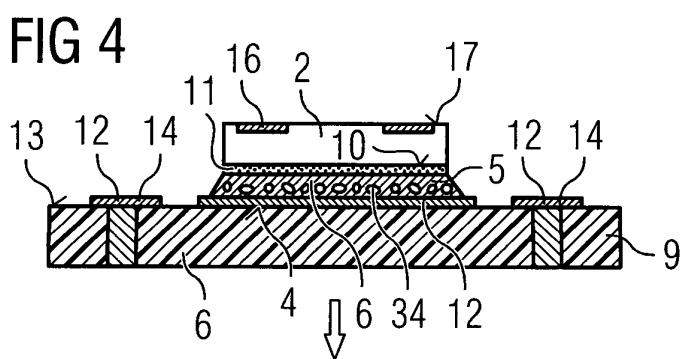

**[0017]** [Fig. 4](#) zeigt eine Prinzipskizze einer Lötverbindung nach Abschluss des Diebondverfahrens;

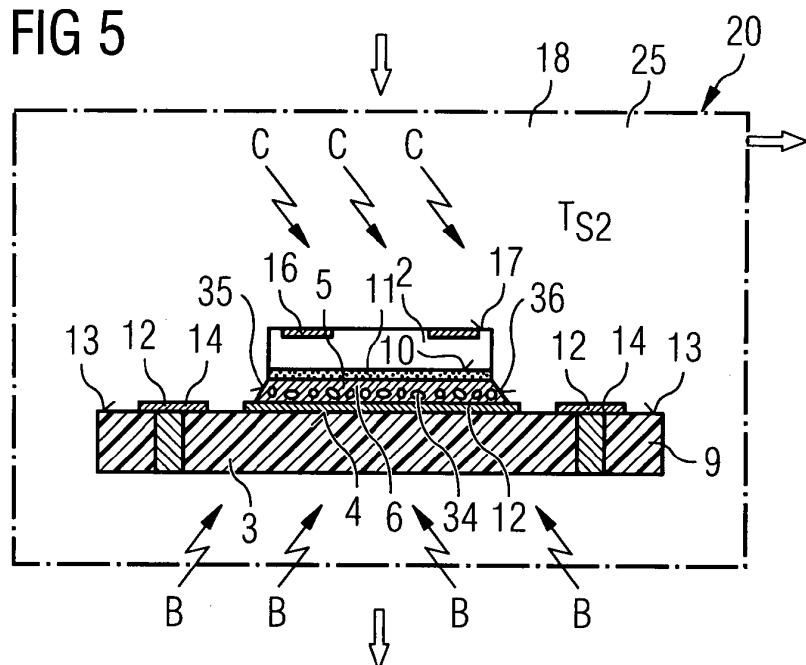

**[0018]** [Fig. 5](#) zeigt eine Prinzipskizze nach dem Einbringen der Lötverbindung gemäß [Fig. 4](#) in einen Va-

kuumlötofen;

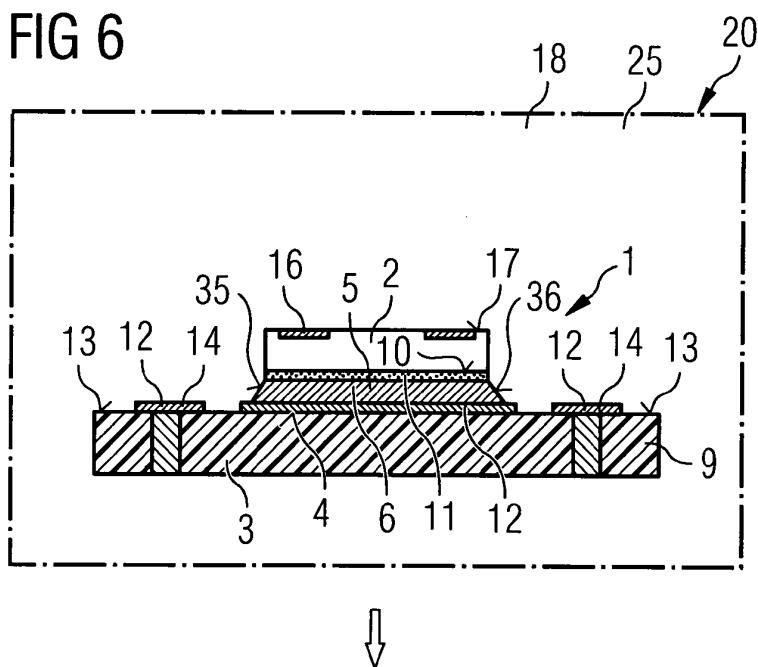

**[0019]** [Fig. 6](#) zeigt eine Prinzipskizze der Lötverbindung nach Abschluss eines Evakuierungsschritts;

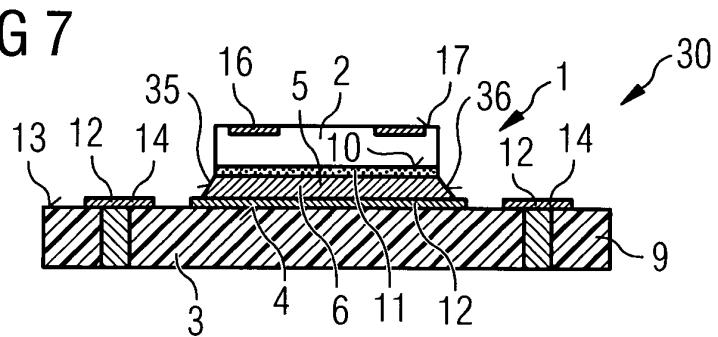

**[0020]** [Fig. 7](#) zeigt eine Prinzipskizze der Lötverbindung nach Entnahme derselben aus dem Vakuumlötofen;

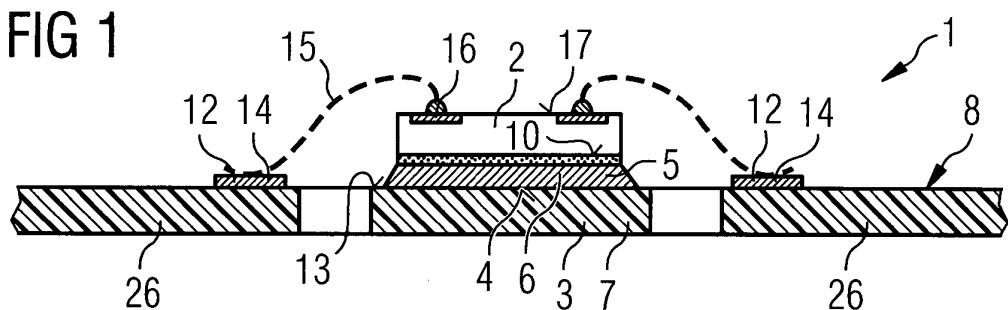

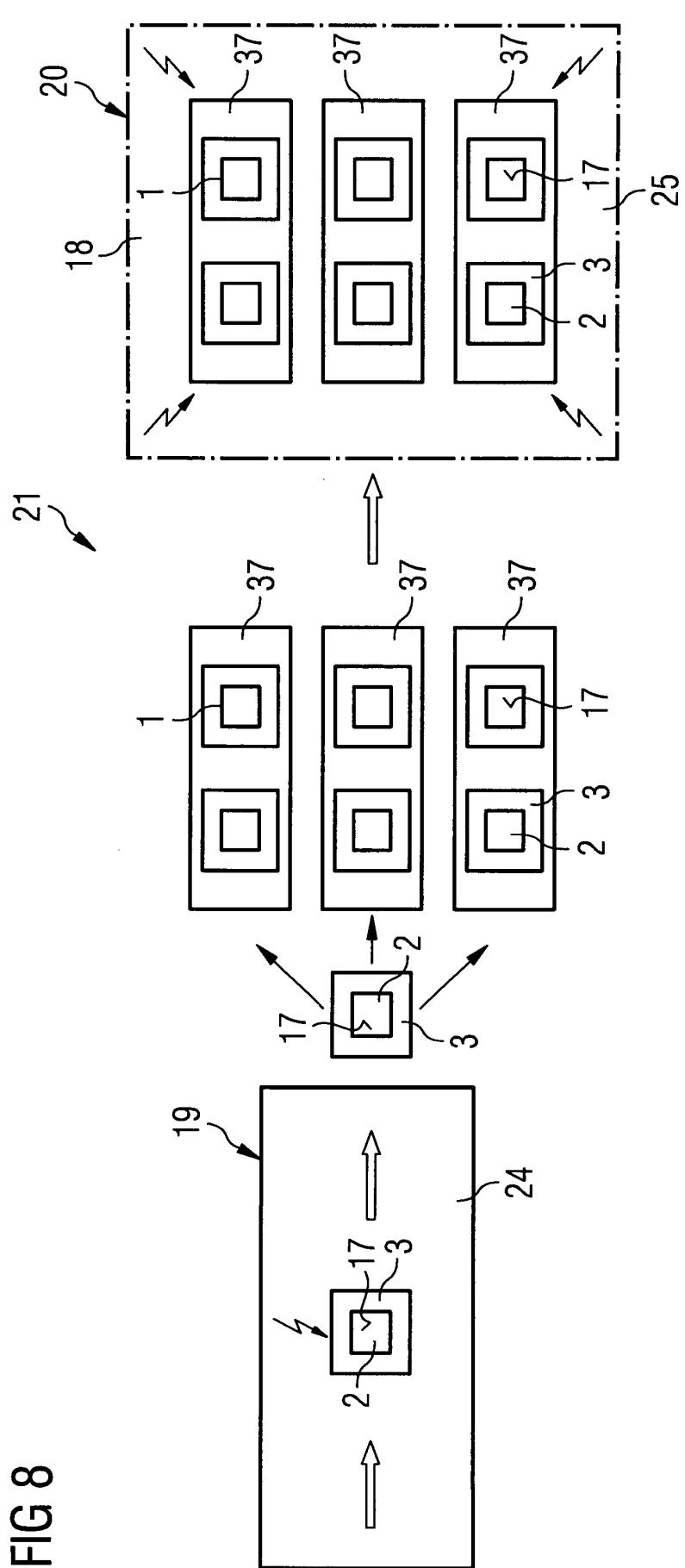

**[0021]** [Fig. 8](#) zeigt eine Prinzipskizze eines Batchverfahrens zur Herstellung von Lötverbindungen;

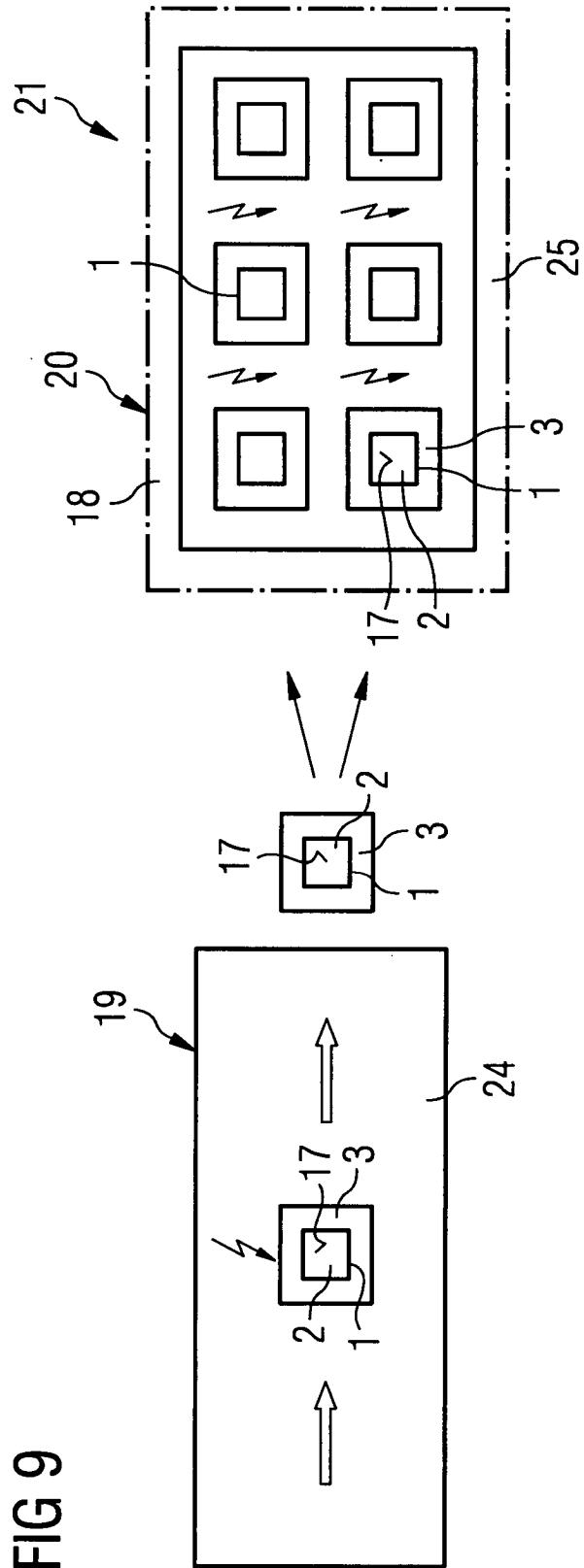

**[0022]** [Fig. 9](#) zeigt eine Prinzipskizze eines weiteren Batchverfahrens zur Herstellung von Lötverbindungen;

**[0023]** [Fig. 10](#) zeigt eine Prinzipskizze eines Durchlaufverfahrens zur Herstellung von Lötverbindungen.

**[0024]** Figur zeigt einen schematischen Querschnitt durch eine beispielhaft hergestellte Lötverbindung 1. Die Lötverbindung 1 ist zwischen einem Halbleiterchip 2 und einem Substrat 3 angeordnet, wobei das Substrat 3 einen lötbaren Oberflächenbereich 4 aufweist. Auf diesem lötbaren Oberflächenbereich 4 ist eine Lotmaterialschicht 5 angeordnet, die ein Lotmaterial 6 aufweist, das mehrfach aufschmelzbar und vakuumfest ist. Beim vorliegenden Ausführungsbeispiel weist das Lotmaterial 6 einen Stoff aus der Gruppe SnAg, PbSnAg, PbSn oder PbSnIn auf, wobei das Substrat 3 mit dem Oberflächenbereich 4 von einer Chipinsel 7 eines Flachleiterrahmens 8 gebildet wird. Ein derartiger Flachleiterrahmen 8 weist neben der Chipinsel 7 beispielsweise die Chipinsel 7 umgebende Flachleiter 26 auf, die in Außenflachleiter, welche Außenanschlüsse eines Halbleiterbauteils bilden, übergehen.

**[0025]** Unter mehrfach aufschmelzbar wird ein Lotmaterial verstanden, dass bei einem mehrfachen Erschmelzen und Erstarren im Wechsel keinen gravierenden Gefüge- oder Struktur- oder kristallinen oder chemischen Veränderungen unterliegt. Unter vakuumfest wird ein Lotmaterial verstanden, dass nach Entweichen von flüchtigen Substanzen im Vakuum einen zusammenhängenden Schmelzfilm aus nicht flüchtigen Lotmaterialkomponenten bildet.

**[0026]** Die Flachleiter 26 können innerhalb eines hier nicht gezeigten Gehäuses eine Beschichtung 12 aufweisen, welche die Bondbarkeit des Flachleitermaterials, das beispielsweise Kupfer oder eine Kupferlegierung aufweist, verbessert. Die flächige Erstreckung der Chipinsel 7 und damit auch die flächige Erstreckung des Oberflächenbereichs 4 ist in dieser Ausführungsform größer als die flächige Erstreckung der Rückseite 10 des Halbleiterchips 2, der mit Hilfe der Lotmaterialschicht 5 auf der Chipinsel 7 fixiert ist.

**[0027]** Dabei weist die Lotmaterialschicht 5 keinerlei

Lunker auf und ist frei von flüchtigen Substanzen. Außerdem weist die Lotmaterialschicht **5** und die Chipinsel **7** eine höhere thermische Leitfähigkeit auf als der Halbleiterchip **2** aus einem Siliziumkristall, so dass diese Lötverbindung **1** in dieser Ausführungsform der Erfindung die Ableitung der Verlustwärme des Halbleiterchips fördert und somit für Leistungs-halbleiterchips geeignet ist. Entsprechend weist der Oberflächenbereich **4** bzw. die Chipinsel **7** und der Halbleiterchip **2** eine Fläche A mit  $A \geq 25 \text{ mm}^2$  auf. Weiterhin ist es vorgesehen, für deutlich größere Leistungen von Leistungshalbleitern eine Fläche A mit  $A \geq 225 \text{ mm}^2$  für den Oberflächenbereich **4** und den Halbleiterchip **2** bereitzustellen.

**[0028]** Die Lunkerfreiheit der Lotmaterialschicht **5** ist für nachfolgende Bondverfahren von Vorteil, bei denen Kontaktflächen **16** auf der Oberseite **17** des Halbleiterchips über Bondverbindungen **15** mit den Flachleitern **26** bei Kontaktanschlussflächen **14** der Flachleiter **26** zu verbinden sind. In [Fig. 1](#) sind schematisch derartige Verbindungselemente **15** mit gestrichelten Linien dargestellt.

**[0029]** [Fig. 2](#) zeigt einen schematischen Querschnitt durch eine weitere beispielhafte Lötverbindung **30**. Komponenten mit gleichen Funktionen wie in [Fig. 1](#) werden mit gleichen Bezeichnungen gekennzeichnet und nicht extra erörtert. Bei einem Ausführungsbeispiel weist das Substrat **3** ein Isolationsmaterial **9** auf. Dieses Isolationsmaterial **9** kann eine Keramik beispielsweise in Form einer auch mehrlagigen Keramikplatte sein, die höhere Temperaturfestigkeiten aufweist als Kunststoffe. Sind jedoch die Temperaturanforderungen geringer, so kann das Substrat **3** auch einen Kunststoffkörper oder eine Kunststoffplatte aufweisen.

**[0030]** Zu diesem Ausführungsbeispiel ist auf der Oberseite **13** des Substrats aus einem Isolationsmaterial **9** eine strukturierte Metallbeschichtung **12** angeordnet, die einen lötaren Oberflächenbereich **4** für die Aufnahme der Lotmaterialschicht **5** und den Halbleiterchip **2** und zusätzlich Kontaktanschlussflächen **14** für entsprechende Verbindungselemente **15** zu den Kontaktflächen **16** auf der Oberseite **17** des Halbleiterchips **2** aufweist. Durch das Substrat **3** aus einem Isolationsmaterial **9** können Durchkontakte **27** elektrische Verbindungen zu Außenkontaktflächen **28** herstellen, die auf einer Unterseite **29** des Substrats **3** angeordnet sind, und über die von der Unterseite **29** aus auf die Kontaktflächen **16** des Halbleiterchips **2** zugegriffen werden kann, sobald die hier mit gestrichelten Linien dargestellten Verbindungselemente **15** sowie die Lötverbindung **5** fertiggestellt sind.

**[0031]** Die strukturierte Metallbeschichtung **12** auf dem Substrat **3** weist einen der Stoffe Kupfer, Silber, Nickel, Nickel/Palladium/Gold oder Legierungen der-

selben auf. Diese Materialien haben sich als lötbare Schichten im Oberflächenbereich **4** bewährt, so dass sich auf ihnen eine Lotmaterialschicht **5** beim Aufheizen ausbreiten kann. Zur Verbesserung der Lötbarkeit des Halbleitermaterials des Halbleiterchips **2** ist auf der Rückseite **10** des Halbleiterchips **2** eine Beschichtung **11** aufgebracht, die aus einem der Stoffe Aluminium, Gold, Silber oder Palladium/Gold oder Legierungen derselben bestehen kann.

**[0032]** Auf einem derartigen Substrat **3** können auch mehrere Lötverbindungen **30** angeordnet sein, mit denen stoffschlüssig mehrere Halbleiterchips **2** auf dem Substrat **3** fixiert sind. Mehrere Halbleiterchips **2** auf einem derartigen Substrat **3** werden häufig für Halbleitermodule für unterschiedliche technische und elektronische Schaltungen aufgebracht und über entsprechende Lötverbindungen **30** fixiert.

**[0033]** [Fig. 3](#) bis [Fig. 7](#) zeigen Prinzipskizzen von Komponenten bei der Herstellung einer Lötverbindung **30**. Dazu zeigt [Fig. 3](#) eine Prinzipskizze einer Diebondposition **24** eines standardisierten Diebonders **19** mit einem Halbleiterchip **2**, der von einer Vakuumpipette gehalten und vorjustiert wird. Dazu wird ein Unterdruck in Pfeilrichtung A an der Auflagefläche **31** eines Diebondstempels **32** mit Hilfe einer zentralen Bohrung **33** im Diebondstempel **32** erzeugt, so dass der Halbleiterchip **2** mit seiner Oberseite **17** an der Auflagefläche **31** anliegt. Die Rückseite **10** des Halbleiterchips **2** schwebt mit der Rückseitenbeschichtung **11**, die beispielsweise einen Stoff der Gruppe Aluminium, Gold, Silber oder Palladium/Gold oder Legierungen derselben aufweist, über dem Oberflächenbereich **4** mit der Lotmaterialschicht **5** nach dem Ausrichten des Substrats **3** mit dem Oberflächenbereich **4** in die Diebondposition **24**.

**[0034]** Vor dem Einbringen des Substrats **3**, das bei diesem Beispiel ein Isolationsmaterial **9** aufweist und aus einer Keramikplatte oder einer Kunststoffplatte besteht, wurde auf die Oberseite **13** des Substrats **3** eine strukturierte Metallbeschichtung aufgebracht, wofür zunächst das Substrat **3** mit einem Metall ganzflächig beschichtet und anschließend photolithographisch eine strukturierte Lackmaske aufgebracht wird. Zur Strukturierung dieser ganzflächigen Metallbeschichtung wird dann ein Trocken- oder Nassätzerverfahren durchgeführt, bei dem die Lackmaske die zu bildende strukturierende Metallbeschichtung **12** schützt, und wobei anschließend die Lackmaske wieder entfernt wird. Die Metallbeschichtung **12** wird dazu aus einem Stoff der Gruppe Kupfer, Silber, Nickel, Nickel/Palladium/Gold oder Legierungen derselben aufgebracht. Die ganzflächige Beschichtung kann durch ein Plattieren des Isolationsmaterials **9** des Substrats **3** mittels einer Metallfolie erfolgen oder durch ein Kaschieren des Isolationsmaterials **9** unter Abscheiden von Metallen in einem elektrolytischen Bad durchgeführt werden.

**[0035]** Andere Möglichkeiten die ganzflächige Metallbeschichtung zu strukturieren bestehen darin, mittels eines Laserstrahls bzw. eines Laserschreibstrahls die ganzflächige Metallbeschichtung zu strukturieren. Auch können Verfahren eingesetzt werden, die auf das Isolationsmaterial **9** des Substrats **3** mittels Druckverfahren eine bereits strukturierte Metallbeschichtung **12** aufbringen, ohne dass vorher eine ganzflächige Metallisierung der Oberfläche **13** des Substrats **3** erforderlich ist. Als derartige Druckverfahren können ein Siebdruckprozess oder ein Schablonendruckprozess oder ein Strahldruckverfahren eingesetzt werden. Bei dem Strahldruckverfahren wird ähnlich einem Tintenstrahlverfahren die strukturierte Metallbeschichtung derart aufgebracht, dass der erforderliche Oberflächenbereich **4** für die Lötverbindung **30** gleichzeitig mit den in [Fig. 3](#) gezeigten Kontaktanschlussflächen **14** entsteht.

**[0036]** Damit ist jedoch die Präparierung des Substrats **3** nicht abgeschlossen. Es wird vielmehr vor dem Einbringen des Substrats **3** in die Diebondposition **24** auf den durch die Strukturierung der Metallbeschichtung **12** entstandenen Oberflächenbereich **4** eine Lotmaterialschicht **5** aufgebracht, die einen Stoff aus der Gruppe SnAg, PbSnAg, PbSn oder PbSnIn aufweisen kann, der sich auf dem lötbaren Oberflächenbereich **4** des Substrats **3** verteilen kann.

**[0037]** In der Diebondposition **24** wird nach Ausrichten des Diebondstempels **32** mit dem Halbleiterchip **2** auf den Oberflächenbereich **4** die Lotmaterialschicht **5** durch eine erste Erwärmung in Pfeilrichtung C und/oder in Pfeilrichtung B bei einer Schmelztemperatur  $T_{S1}$  erschmolzen und anschließend die Rückseite **10** mit der Rückseitenbeschichtung **11** des Halbleiterchips **2** in Pfeilrichtung D auf die Lotmaterialschicht **5** abgesenkt.

**[0038]** Da zusätzlich durch Ultraschallschwingungen des Diebondstempels **32** sonare Energie in die sich bildende Lötverbindung eingebracht wird, kann zunächst eine vollständige Aufschmelzung des Lotmaterials **6** durch thermische Energie unterbleiben, so dass sich eine schmelzflüssige Lotschicht erst durch Überlagerung der thermischen und der sonaren Energie bildet. Dabei können sich durch leichtflüchtige Komponenten des Lotmaterials **6** Lunker in der Lotmaterialschicht **5** beim Diebondverfahren bilden. Dieses ist nachteilig bei hohen Leistungsdichten des Halbleiterbauelements und bei entsprechend großflächigen Halbleiterchips **2** mit Flächen  $A \geq 25 \text{ mm}^2$  oder auch Flächen  $A \geq 225 \text{ mm}^2$ .

**[0039]** Anstelle der Beschichtung des Oberseitenbereichs **4** des Substrats **3** mit einem Lotmaterial **6** kann auch vor dem Bondverfahren die Rückseite **10** bzw. die Rückseitenbeschichtung **11** des Halbleiterchips **2** mit einem Lotmaterial **6** beschichtet werden.

**[0040]** [Fig. 4](#) zeigt eine Prinzipskizze einer Lötverbindung **30** nach Abschluss des Diebondverfahrens, so dass der Halbleiterchip **2** nun stoffschlüssig mit dem Substrat **3** nach einem Erstarren des Lotmaterials **6** zu einer Lotmaterialschicht **5** zwischen dem Oberflächenbereich **4** des Substrats **3** und der Rückseite **10** des Halbleiterchips **2** stoffschlüssig verbunden ist. In [Fig. 4](#) sind die sich im Diebondverfahren bildenden Lunker **34** lediglich prinzipiell angedeutet und stellen im Lötmaterial **6** Agglomerationen oder Cluster von leichtflüchtigen Komponenten des Lotmaterials **6** dar, deren Größe im Submikrometerbereich liegen kann.

**[0041]** [Fig. 5](#) zeigt eine Prinzipskizze nach dem Einbringen der Lötverbindung **30** gemäß [Fig. 4](#) in einen Vakuumlötofen **20**. Durch entsprechende Wärmezufluhr in Pfeilrichtung B und/oder C in einem Heizraum **18** des Vakuumlötofens **20** wird das Lotmaterial **6** mit den Lunkern **34** ein zweites Mal erschmolzen, so dass beim Evakuieren des Volumens des Vakuumlötofens **20** in Pfeilrichtung E die flüchtigen Komponenten, die in den Lunkern **34** enthalten sind, aus dem Volumen der Vakuumofenposition **25** in Pfeilrichtung E abgepumpt werden. Dazu kann es erforderlich werden, dass die Schmelztemperatur des Lotmaterials **6** geringfügig überschritten wird, um eine entsprechende Bewegung in dem Schmelzspalt zwischen Halbleiterchip **2** und Oberflächenbereich **4** des Substrats **3** herzustellen, so dass über entsprechende Oberflächenspannungsdifferenzen des schmelzflüssigen Lotmaterials **6** die Lunker **34** in die Randzonen **35** und **36** der Lötmaterialschicht **5** transportiert werden.

**[0042]** [Fig. 6](#) zeigt eine Prinzipskizze der Lötverbindung **30** nach Abschluss eines Evakuierungsschritts in der Vakuumofenposition **25**, wobei nun die Lotmaterialschicht **5** vollständig lunkerfrei ist, so dass, wie [Fig. 7](#) zeigt, die Lötverbindung **30** aus einer Lötmaterialschicht **5**, einem Halbleiterchip **2** und einem Substrat **3** aus dem Vakuumlötofen **20**, wie sie in den [Fig. 5](#) und [Fig. 6](#) gezeigt wird, entnommen werden kann und nun die Lötverbindung **30** aus diesen drei Komponenten weiteren Fertigungsschritten zugeführt werden kann und lunkerfrei für die Weiterverarbeitung sowie für das fertige Bauelement zur Verfügung steht.

**[0043]** Die [Fig. 8](#) bis [Fig. 10](#) zeigen unterschiedliche Möglichkeiten zur Herstellung von Lötverbindungen, wobei eine Kombination aus Diebondfixierung eines Halbleiterchips mittels eines Diebonder und einem Vakuumlötofen, ein Batchverfahren oder ein Durchlaufverfahren möglich ist.

**[0044]** [Fig. 8](#) zeigt eine Prinzipskizze eines üblichen Batchverfahrens **21** zur Herstellung von Lötverbindungen **1** oder **30**, wie sie in den [Fig. 1](#) und [Fig. 2](#) zu sehen sind. Bei diesem Batchverfahren **21** wird zunächst in einem standardisierten Diebonder **19**

durchlaufend Halbleiterchip **2** nach Halbleiterchip auf einem Substrat **3** mittels des Diebondverfahrens in einer Diebondposition **24** fixiert. Anschließend werden diese Substrate **3** mit Halbleiterchips **2** auf Substraträgerplatten bzw. Basisplatten **37** zusammen gestellt, die in ihrer Größe und Menge den Möglichkeiten und Kapazitäten eines Vakuumlötofens **20** entsprechen, so dass in dem Heizraum **18** des Lötofens **20** die Basisplatten **37** angeordnet werden können. Anschließend werden unter Aufheizen und Evakuieren die zwischen den Halbleiterchips **2** und den Substraten **3** angeordneten fixierenden Lotmaterial schichten von Lunkern befreit. Bei diesem Beispiel eines Batchverfahrens **21** können beispielsweise gleichzeitig neun Halbleiterchips **2** aufgeheizt und evakuiert werden, wobei abhängig von der Gestaltung des **18** Heizraumes diese Anzahl pro Batch bzw. Fertigungslos beliebig erhöht werden kann.

**[0045]** [Fig. 9](#) zeigt eine Prinzipskizze eines weiteren Beispiels eines Batchverfahrens **21** zur Herstellung von Lötverbindungen **1** oder **30**, wobei auch hier in einer Diebondposition **24** ein standardisierter Diebonder **19** einzelne Halbleiterchips **2** nacheinander auf Substraten **3** in einem ersten Aufheizschritt fixiert, die anschließend einzeln in einem Heizraum **18** eines Vakuumlötofens **20** gestapelt, mit einem zweiten Aufheizschritt aufgeheizt und mittels Evakuieren derart bearbeitet werden, dass lunkerfreie Lotmaterial schichten zwischen Halbleiterchips **2** und Substraten **3** entstehen.

**[0046]** [Fig. 10](#) zeigt eine Prinzipskizze eines Durchlaufverfahrens **22** zur Herstellung von Lötverbindungen **1** und **30**. Bei diesem Durchlaufverfahren sind der Diebonder **19** und der Vakuumlötofen **20** in einer kontinuierlichen Fertigungsanlage **23** angeordnet, wobei zwischen den einzelnen Bereichen **38**, **39** und **40** Vakumschleusen **41** und **42** beispielsweise aus Vakumschiebern angeordnet sind. Diese Vakumschleusen **41** bzw. **42** ermöglichen, dass im ersten Bereich **38** der Diebonder **19** unter Inertgasatmosphäre arbeitet, während im zweiten Bereich **39** ein Aufheizen unter Vakuum wie in einem Vakuumlötofen **20** möglich ist und schließlich im Bereich **40** ein Erstarren der nun lunkerfreien Lotmaterialschicht unter Inertgas oder Vakuum ermöglicht wird, bevor die Lötverbindung **1** der Fertigungsanlage **23** entnommen wird. Eine derartige Fertigungsanlage **23** hat den Vorteil, dass Energie gespart werden kann, da ein vollständiges Abkühlen der Kombination aus Halbleiterchip, Lotmaterial und Substrat auf Raumtemperatur, wie bei den obigen Batchverfahren zwischen dem Bondschnitt und dem Evakuierungsschnitt in den Bereichen **38** und **39** nicht erforderlich ist.

### Patentansprüche

1. Verfahren zur Herstellung einer Lötverbindung (**1**), mit den Schritten:

- Bereitstellen eines Substrats (**3**) mit einem lötbaren Oberflächenbereich (**4**); Bereitstellen eines Halbleiterchips (**2**) mit einer Oberseite (**17**) und einer lötbaren Rückseite (**10**);

- Aufbringen eines Lotmaterials (**6**) auf den lötbaren Oberflächenbereich (**4**) oder die lötbare Rückseite (**10**);

- stoffschlüssiges Verbinden des Halbleiterchips (**2**) mit dem Substrat (**3**) unter einem ersten Erschmelzen und Erstarren des Lotmaterials (**6**) zu einer Lot materialschicht (**5**) zwischen dem Oberflächenbereich (**4**) und der Rückseite (**10**), wobei zum stoffschlüssigen Verbinden des Halbleiterchips (**2**) mit dem Substrat (**3**) ein Diebondverfahren eingesetzt wird;

- Einbringen des stoffschlüssigen Verbundes in einen evakuierbaren Heizraum (**18**);

- zweites Erschmelzen des Lotmaterials (**6**) unter Vakuum mit Abpumpen flüchtiger Substanzen aus der Lotmaterialschicht (**5**), wobei das erste und das zweite Erschmelzen bei gleicher Schmelztemperatur ( $T_{S1} = T_{S2}$ ) des Lotmaterials (**6**) erfolgt und zum Dieboden und Vakuumerschmelzen ein Durchlaufverfahren (**22**) verwendet wird, bei dem mehrere Halbleiterchips (**2**) hintereinander in einer kontinuierlichen Fertigungsanlage (**23**), die mindestens eine Diebondposition (**24**) und eine Vakuumofenposition (**25**) aufweist, kontinuierlich bearbeitet werden, und anschließendem Erstarren des Lotmaterials (**6**) zu einer Lötverbindung (**1**).

2. Verfahren nach Anspruch 1, wobei zum stoffschlüssigen Verbinden des Halbleiterchips (**2**) mit dem Substrat (**3**) ein standardisierter Diebonder (**19**) eingesetzt wird.

3. Verfahren nach Anspruch 1 oder 2, wobei zum zweiten Erschmelzen des Lotmaterials (**6**) unter Vakuum ein standardisierter Vakuumlötofen (**20**) eingesetzt wird.

4. Verfahren nach einem der Ansprüche 1 bis 3, wobei zum Aufbringen eines Lotmaterials (**6**) auf den lötbaren Oberflächenbereich (**4**) oder die lötbare Rückseite (**10**) ein flussmittelarmes Lotmaterial aufgebracht wird.

5. Verfahren nach einem der Ansprüche 1 bis 3, wobei als Lotmaterial (**6**) auf den lötbaren Oberflächenbereich (**4**) oder auf die lötbare Rückseite (**10**) ein Stoff aus der Gruppe SnAg, PbSnAg, PbSn oder PbSnIn aufgebracht wird.

6. Verfahren nach einem der Ansprüche 1 bis 5, wobei eine Lötverbindung (**1**) zwischen dem Oberflächenbereich (**4**) und dem Halbleiterchip (**2**) mit einer Fläche  $A \geq 25 \text{ mm}^2$  hergestellt wird.

7. Verfahren nach einem der Ansprüche 1 bis 5, wobei eine Lötverbindung (**1**) zwischen dem Oberflächenbereich (**4**) und dem Halbleiterchip (**2**) mit einer

Fläche A  $\geq 225 \text{ mm}^2$  hergestellt wird.

8. Verfahren nach einem der Ansprüche 1 bis 7, wobei eine Lötverbindung (1) zwischen dem Oberflächenbereich (4) und einem Leistungshalbleiterchip hergestellt wird.

9. Verfahren nach einem der Ansprüche 1 bis 8, wobei als Oberflächenbereich (4) des Substrats (3) der Lötverbindung (1) eine Chipinsel (7) eines Flachleiterrahmens (8) eingesetzt wird.

10. Verfahren nach einem der Ansprüche 1 bis 8, wobei vor dem Aufbringen eines Lotmaterials (6) auf den Oberflächenbereich (4), der Oberflächenbereich (4) mit einem Stoff der Gruppe Kupfer, Silber, Nickel, Nickel/Palladium/Gold oder Legierungen derselben beschichtet wird.

11. Verfahren nach einem der Ansprüche 1 bis 10, wobei als Substrat (3) eine Keramikplatte eingesetzt wird.

12. Verfahren nach einem der Ansprüche 1 bis 10, wobei als Substrat (3) eine Kunststoffplatte eingesetzt wird.

13. Verfahren nach einem der Ansprüche 1 bis 12, wobei vor dem Herstellen der Lötverbindung (1) die Rückseite (10) des Halbleiterchips (2) mit einem Stoff der Gruppe Aluminium, Gold, Silber oder Palladium/Gold oder Legierungen derselben beschichtet wird.

14. Verfahren nach einem der Ansprüche 1 bis 13, wobei der Halbleiterchip (2) aus einem Siliziumkristallwafer hergestellt wird.

15. Verfahren nach einem der Ansprüche 1 bis 14, wobei vor dem Herstellen von Lötverbindungen (1) auf das Substrat (3) eine strukturierte Metallbeschichtung (12), die mindestens eine Chipinsel (7) und Kontaktanschlussflächen (14) für Verbindungselemente (15) zu Kontaktflächen (16) des Halbleiterchips (2) aufweist, aufgebracht wird.

16. Verfahren nach Anspruch 15, wobei zum Aufbringen einer strukturierten Metallbeschichtung (12) das Substrat mit einem Metall ganzflächig beschichtet und anschließend photolithographisch eine strukturierte Lackmaske aufgebracht wird.

17. Verfahren nach Anspruch 15 oder Anspruch 16, wobei zum Aufbringen einer strukturierten Metallbeschichtung ein Trocken- oder Nassätzverfahren durchgeführt wird, bei dem die Lackmaske die zu bildende strukturierende Metallbeschichtung schützt, und wobei abschließend die Lackmaske entfernt wird.

18. Verfahren nach Anspruch 16, wobei die ganzflächige Metallbeschichtung mittels Laserstrahl strukturiert wird.

19. Verfahren nach Anspruch 15, wobei die strukturierte Metallbeschichtung (12) mittels Druckverfahren aufgebracht wird.

20. Verfahren nach Anspruch 15, wobei die strukturierte Metallbeschichtung (12) mittels Siebdruckverfahren aufgebracht wird.

21. Verfahren nach Anspruch 15, wobei die strukturierte Metallbeschichtung (12) mittels Schablonendruckverfahren aufgebracht wird.

22. Verfahren nach Anspruch 15, wobei die strukturierte Metallbeschichtung (12) mittels Strahldruckverfahren aufgebracht wird.

Es folgen 4 Blatt Zeichnungen

## Anhängende Zeichnungen

**FIG 1****FIG 2****FIG 3****FIG 4**

**FIG 5**

**FIG 6**

**FIG 7**

FIG 8