# (10) **DE 10 2005 029 493 B4** 2014.10.16

(12)

## **Patentschrift**

(21) Aktenzeichen: 10 2005 029 493.6

(22) Anmeldetag: 24.06.2005(43) Offenlegungstag: 23.02.2006

(45) Veröffentlichungstag

der Patenterteilung: 16.10.2014

(51) Int Cl.: **H01L 27/115** (2006.01)

**H01L 21/8247** (2006.01) **G11C 16/04** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

10/918,335

13.08.2004 US

(73) Patentinhaber:

Infineon Technologies AG, 81669 München, DE

(74) Vertreter:

Kindermann, Patentanwälte, 85598 Baldham, DE

(72) Erfinder:

Kakoschke, Ronald, 81475 München, DE; Nirschl, Thomas, 81673 München, DE; Schrüfer, Klaus, 85598 Baldham, DE; Shum, Danny Pak-Chum, Poughkeepsie, N.Y., US

(56) Ermittelter Stand der Technik:

siehe Folgeseiten

# (54) Bezeichnung: Integrierte Speicherschaltungsanordnung mit Tunnel-Feldeffekttransistoren und zugehöriges Verfahren

(57) Hauptanspruch: Speicherschaltungsanordnung (10) mit:

einer Vielzahl Speicherzellen, die in einer Matrix angeordnet sind, welche Zeilen aus Speicherzellen und Spalten aus Speicherzellen enthält.

jede Speicherzelle enthält mindestens einen Zelltransistor (T01 bis Tm, n),

jeder Zelltransistor (T01 bis Tm, n) enthält einen ersten dotierten Bereich und einen zweiten dotierten Bereich, wobei entweder der erste dotierte Bereich ein Drainbereich (D) und der zweite dotierte Bereich ein Sourcebereich (S) ist oder wobei alternativ der erste dotierte Bereich ein Sourcebereich (S) und der zweite dotierte Bereich ein Drainbereich (D) ist,

einer Vielzahl von Wortleitungen (WL0 bis WLm), wobei jede Wortleitung mit Speicherzellen einer Zeile verbunden ist, einer Vielzahl von ersten Bitleitungen (20 bis 24), wobei jede erste Bitleitung mit Speicherzellen einer Spalte verbunden ist,

die ersten dotierten Bereiche haben einen anderen Dotiertyp als die zweiten dotierten Bereiche,

einem gemeinsamen zweiten dotierten Bereich (S), der Speicherzellen gemeinsam ist, die in einer Spalte aneinandergrenzen,

dadurch gekennzeichnet, dass ein erster Abstand (A0) zwischen Floating Gates der Transistoren (T00 bis Tm, n) der in einer Spalte an einem gemeinsamen zweiten dotierten Bereich (S) aneinander grenzenden Speicherzellen kleiner als ein zweiter Abstand (A2) zwischen Floating Gates von Transistoren (T00 bis Tm, n) ist, die an einen gemeinsamen ersten dotierten Bereich in der gleichen Spalte angrenzen, und durch eine Steuerschaltung für eine Lesebetriebsart,

wobei die Zelltransistoren Tunnel-Feldeffekttransistoren sind.

und wobei die Steuerschaltung in der Lesebetriebsart einen Tunnelstrom durch einen Tunnel-Übergang zwischen einem an dem einen Source- oder Drainbereich des Tunnel-Feldeffekttransistors beginnenden Inversionskanal und dem anderen Source- oder Drainbereich des Tunnel-Feldeffekttransistors fließen lässt, wobei der Tunnelstrom in diesem Übergang durch in einem Floatinggate gespeicherte Ladungen beeinflusst wird.

# (10) **DE 10 2005 029 493 B4** 2014.10.16

### (56) Ermittelter Stand der Technik:

| DE | 199 43 390       | <b>A</b> 1 |

|----|------------------|------------|

| US | 6 181 601        | B1         |

| US | 6 424 000        | B1         |

| US | 2003 / 0 075 773 | <b>A</b> 1 |

| US | 2003 / 0 111 672 | <b>A</b> 1 |

| US | 2003 / 0 139 011 | <b>A</b> 1 |

| US | 5 420 060        | Α          |

| US | 6 143 607        | Α          |

| JP | H06- 326 323     | Α          |

### **Beschreibung**

[0001] Die Erfindung betrifft eine Speicherschaltungsanordnung, die eine Vielzahl Speicherzellen enthält, die in einer Matrix angeordnet sind. Die Matrix enthält Zeilen aus Speicherzellen und Spalten aus Speicherzellen. Jede Speicherzelle enthält einen oder mehrere Zelltransistoren. Jeder Zelltransistor enthält einen ersten dotierten Bereich und einen zweiten dotierten Bereich, wobei der erste dotierte Bereich bspw. ein Drainbereich und der zweite dotierte Bereich ein Sourcebereich ist. Alternativ ist der erste dotierte Bereich ein Sourcebereich und der zweite dotierte Bereich ist ein Drainbereich. Der Speicher enthält außerdem eine Vielzahl Wortleitungen und eine Vielzahl erste Bitleitungen. Jede Wortleitung ist mit Speicherzellen einer Zeile dieser Matrix verbunden. Jede erste Bitleitung ist mit Speicherzellen einer Spalte der Matrix verbunden.

[0002] Mit immer kleiner und hochentwickelt werdender Elektronik werden Schaltungsanordnungen mit immer kleineren Abmessungen wünschenswerter. Insbesondere ist ständig Forschung darauf gerichtet, verschiedene Arten von Speicherschaltungsanordnungen zu verkleinern. Jedoch gibt es mit herkömmlichen Technologien bestimmte Probleme. Einige dieser Probleme betreffen die Nichtskalierbarkeit des Tunneloxids bzw. Tunneldielektrikums, Kurzkanaleffekte und andere Schwellspannungsunterschiede. Die Skalierung kann außerdem eine Verkürzung der Ladungshaltezeit, eine Verkleinerung des Kopplungsverhältnisses oder eine Vergrößerung des Leckstroms zwischen Speicherzellen in derselben Spalte bewirken. Außerdem vergrößern komplizierte Designregeln zum Verkleinern der Speicherarchitektur auch die Herstellungsschwierigkeiten und Kosten.

[0003] Aus der US 6 143 607 A sind die Merkmale des Oberbegriffs des Anspruchs 1 bzw. des Anspruchs 11 zu entnehmen. Aus der US 6 143 607 A bzw. der US 6 181 601 B1 ist eine Speicherzelle bekannt, die programmiert wird mit Band-zu-Band-Tunneln und die gelesen wird mit gate-induziertem Drain-Leckstrom (GIDL). Aus der US 6 424 000 B1 ist eine Speicherzelle mit Programmierelement bekannt, in dem ein rückwarts gerichteter Durchbruch auftritt. Aus der US 2003 /0 139 011 A1 ist eine vertikale Speicherzelle bekannt. Die Speicherzelle kann eine Diode enthalten, die mit einem Gate versehen ist Aus der US 5 420 060 A und der US 2003/0 075 773 A1 sind Speicherelemente bekannt.

**[0004]** Aus der Entgegenhaltung JP 06326323 A ist ein nichtflüchtig speichernder Tunneltransistor bekannt. Aus der DE 199 43 390 A1 ist ein Halbleiterbauelement bekannt, nämlich ein vertikaler Tunneltransistor, der jedoch nicht als Speicherzelle verwendet wird. Aus der US 2003/0111672 A1 ist ein

nichtflüchtig speichernder Speicher bekannt. Abstände zwischen den Speicherzellen einer Spalte sind gemäß den Figuren gleich.

[0005] Es ist Aufgabe der Erfindung, eine Speicherschaltungsanordnung anzugeben, die insbesondere auf einfache Art hergestellt werden kann und die eine Verkleinerung der Zellgröße gestattet. Außerdem soll ein Verfahren zur Herstellung einer solchen Schaltungsanordnung angegeben werden. Die auf die Speicherschaltungsanordnung bezogene Aufgabe wird durch eine Speicherschaltungsanordnung mit den im Patentanspruch 1 angegebenen Merkmalen gelöst. Weiterbildungen sind in den Unteransprüchen angegeben.

[0006] Die erfindungsgemäße Speicherschaltungsanordnung enthält mindestens einen Zelltransistor, der einen Sourcebereich und einen Drainbereich mit voneinander verschiedenen Dotiertypen hat. Somit ist dieser Transistor ein Tunnel-Feldeffekt-Transistor (TFET), bei dem ein pn-Übergang durchtunnelt wird, der sich zwischen einem Kanal und einem der Source-/Drainbereiche bildet. Der Kanal ist ein Inversionskanal, der sich in einem intrinsischen Bereich eines p-i-n-Bereichs (p-dotiert, intrinsisch dotiert, n-dotiert) des Transistors bildet. An Stelle des intrinsischen Bereichs kann auch ein schwach p-dotierter oder ein schwach n-dotierter Bereich verglichen mit der Dotierstoffkonzentration in den Source-/Drainbereichen verwendet werden. Die Source-/Drainbereiche dienen zum Anlegen externer Spannungen und unterscheiden sich deshalb von sogenannten "Halos" oder Taschendotierbereichen (pockets) in der Nähe des Kanals des Transistors. Der Tunnelstrom kann vom Gate des Transistors aus beeinflusst werden, insbesondere vom Floating Gate eines Floating Gate Transistors.

[0007] Bei einer Ausgestaltung ist nur ein Auswahltransistor oder nur ein Speicher-Transistor einer Speicherzelle ein TFET, wohingegen ein anderer Transistor oder mehrere andere Transistoren der Speicherzelle Feldeffekt-Transistoren mit dem gleichen Dotiertyp im Sourcebereich und im Drainbereich sind. Alternativ sind alle Transistoren einer Speicherzelle TFETs.

[0008] Gemäß einer alternativen Ausgestaltung enthält eine Speicherzelle nur einen Tunnel-Feldeffekt-Transistor in einer Flash-Speicherzelle. Diese Eintransistor-Flash-Speicherzelle lässt sich weiter verkleinern, ohne dass die von Feldeffekt-Transistoren mit Source- und Drainbereichen vom gleichen Dotiertyp bekannten Probleme auftreten.

**[0009]** Bei einer Ausgestaltung sind die ersten Bereiche und die zweiten Bereiche Halbleiterbereiche, z. B. einkristalline Bereiche. Silizium, andere Elementhalbleitermaterialen oder Verbindungshalbleiterma-

terialien können für die Halbleiterbereiche verwendet werden. Die ersten Bereiche können beispielsweise n-dotierte Bereiche sein, während die zweiten Bereiche p-dotierte Bereiche sind.

[0010] Gemäß einer Weiterbildung enthält die Speicherschaltungsanordnung eine Vielzahl zweiter Bitleitungen. Jede zweite Bitleitung ist mit den zweiten dotierten Bereichen der Zelltransistoren einer Spalte elektrisch leitfähig verbunden. Zwei Bitleitungen werden in Speicherschaltungsanordnungen wie SRAMs (Static Random Access Memory) und in elektrisch löschbaren Nurlesespeichern (EEPROMs – Electrically Erasable Programmable Read Only Memory) verwendet, während beispielsweise in DRAMs (Dynamic Random Access Memory) nur eine Bitleitung je Speicherzelle verwendet wird.

**[0011]** Gemäß einem anderen Ausführungsbeispiel sind die ersten Bitleitungen erhöhte (raised) Bitleitungen, die oberhalb der Speicherzellen angeordnet sind bzw. die über die Speicherzellen angehoben sind, und die zweiten Bitleitungen sind vergrabene Bitleitungen, die unterhalb der Speicherzellen angeordnet sind. Bei dieser Weiterbildung ist die Zellgröße kleiner als mit Bitleitungen, die lateral zu einander angeordnet sind.

[0012] Gemäß einer nächsten Weiterbildung enthält jede Speicherzelle einen Speicherzelltransistor. Jede erste Bitleitung ist mit den ersten dotierten Bereichen der Zelltransistoren einer Spalte verbunden. Jede zweite Bitleitung ist mit den zweiten dotierten Bereichen der Zelltransistoren einer Spalte verbunden. Speicherschaltungsanordnungen mit nur einem Transistor je Speicherzelle benötigen die kleinste Zellgröße bzw. Zellfläche im Vergleich zu Zellen, die zwei oder mehr als zwei Transistoren haben. Außerdem gestatten die zwei Bitleitungen Betriebsarten mit einer kleineren Fehlerrate und einer großen Geschwindigkeit.

[0013] Bei einer nächsten Weiterbildung ist die vergrabene Bitleitung eine isolierende dotierte Wanne. welche auch die Substratbereiche, Sourcebereiche und Drainbereiche der Speicherzellen einer Spalte enthält. Die Kombination eines Tunnel-Feldeffekt-Transistors und einer vergrabenen Bitleitung erlaubt die Bildung einer guten elektrischen Verbindung zwischen der vergrabenen Bitleitungswanne und den Sourcegebieten. Weil die Wanne und die mit Hilfe der Wanne verbunden dotierten Bereiche den gleichen Dotiertyp haben, sind keine zusätzlichen Maßnahmen erforderlich, um eine gute elektrische Verbindung herzustellen, d. h. eine Verbindung mit einem kleinen Ohmschen Widerstand. Die Dotierstoffkonzentration in der vergrabenen Bitleitung gewährleistet eine gute Leitfähigkeit. Die maximale Dotierstoffkonzentration der vergrabenen Bitleitung kann beispielsweise mindestens eine Größenordnung bzw. eine

Zehnerpotenz geringer gewählt werden, als die maximale Dotierstoffkonzentration des Sourcebereichs, um die Ausbildung eines flachen Inversionskanals in dem Kanalbereich zu ermöglichen. Bei einem weiteren Ausführungsbeispiel ist der Dotiertyp der Wanne der gleiche wie der Dotiertyp der zweiten dotierten Bereiche, die z. B. die Sourcebereiche sind.

[0014] Gemäß einer nächsten Weiterbildung enthalten die ersten dotierten Bereiche schwach dotierte Bereiche und stark dotierte Bereiche, und die zweiten dotierten Bereiche enthalten nur stark dotierte Bereiche und keine schwach dotierten Bereiche. Auf diese Art ist es möglich, einen kleinen Dotierstoffkonzentrationsgradient auf einer Seite des Transistors zu haben, beispielsweise auf der Seite mit der höheren Spannung. Gleichzeitig ist es möglich, die für den zweiten dotierten Bereich benötigte Größe bzw. Fläche durch das Weglassen des schwach dotierten Bereichs auf der anderen Seite des Transistors zu verringern.

[0015] Gemäß einer nächsten Weiterbildung sind sowohl die ersten dotierten Bereiche als auch die zweiten dotierte Bereiche silizidiert. In diesem Fall sind keine Maßnahmen erforderlich, um die Silizidierung des zweiten dotierten Bereichs zu verhindern. Alternativ sind nur die ersten dotierten Bereiche silizidiert, während die zweiten dotierten Bereiche nicht silizidiert sind. Zur Silizidierung der zweiten dotierten Bereiche ist also kein Halbleitermaterial erforderlich. deshalb haben die zweiten dotierten Bereiche einen kleinen Anschlusswiderstand.

[0016] Gemäß einer anderen Weiterbildung ist mindestens eine der ersten Bitleitungen oder eine der zweiten Bitleitungen eine unterhalb der Speicherzellen vergrabene Bitleitung. Wenn beide Bitleitungen vergrabene Bitleitungen sind, so ist keine metallische Bitleitung erforderlich. Wenn nur eine vergrabene Bitleitung verwendet wird, ist der laterale Versatz zwischen Spalten klein und der Querschnitt der Bitleitungen lässt sich größer wählen als in dem Fall mit zwei vergrabenen Bitleitungen, wobei vorausgesetzt wird, dass das gleiche laterale Gebiet belegt wird.

[0017] Bei einer nächsten Weiterbildung ist ein gemeinsamer zweiter dotierter Bereich für Speicherzellen gemeinsam, die innerhalb einer Spalte aneinander grenzen. Ein erster Abstand zwischen den Floating Gates dieser Transistoren ist kleiner als ein zweiter Abstand zwischen den Floating Gates von Transistoren, die an einen gemeinsamen ersten dotierten Bereich in der gleichen Spalte angrenzen. Der erste Abstand ist bei einer Weiterbildung gleich der minimalen Strukturbreite in der Speicherschaltungsanordnung. Dies ist möglich, weil zusätzliche Maßnahmen für die elektrische Verbindung des zweiten dotierten Bereichs mit der vergrabenen Bitleitung nicht verwendet werden müssen. Es ist ausreichend, einen

stark dotierten Verbindungsstreifen in die vergrabene Bitleitungswanne zu dotieren. Der Verbindungsstreifen hat den gleichen Dotiertyp wie die Wanne. Deshalb sind silizidierte Gebiete nicht erforderlich, die mit anderen Bereichen überlappen.

[0018] Außerdem wird ein Verfahren zur Herstellung einer Speicherschaltungsanordnung in einem Halbleitersubstrat angegeben. Die Speicherschaltungsanordnung enthält ein solches Speicherfeld mit einer Vielzahl Speicherzelltransistoren, in dem die Transistoren in Zeilen und Spalten angeordnet sind. Das Verfahren kann insbesondere für die Herstellung der erfindungsgemäßen Speicherschaltungsanordnung bzw. einer ihrer Weiterbildungen genutzt werden. Deshalb gelten die oben erwähnten technischen Wirkungen auch für das erfindungsgemäße Verfahren und dessen Weiterbildungen.

**[0019]** Im Folgenden werden Ausführungsbeispiele der Erfindung an Hand der beiliegenden Zeichnungen erläutert. Darin zeigen:

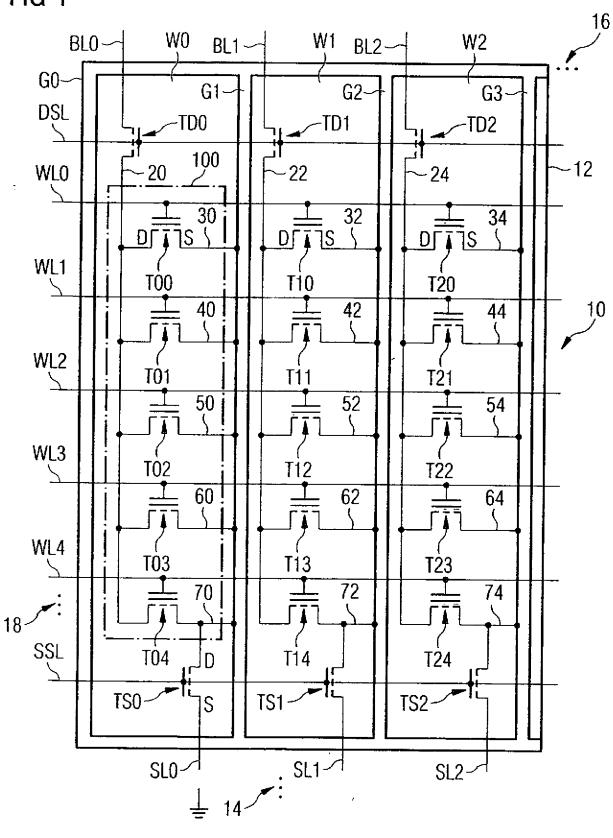

**[0020] Fig.** 1 einen Ausschnitt des Schaltplans eines Speicherzellengebiets in einem Flash-EEPROM (Electrically Erasable Programmable Read Only Memory),

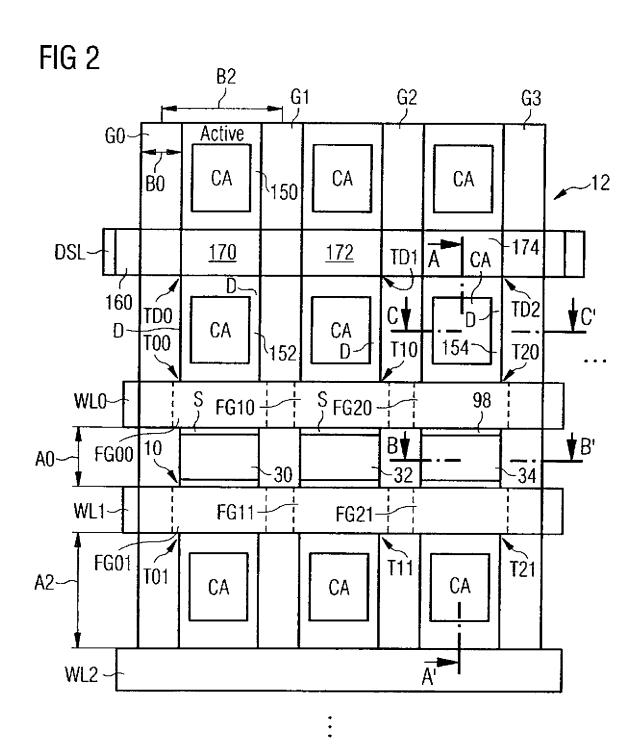

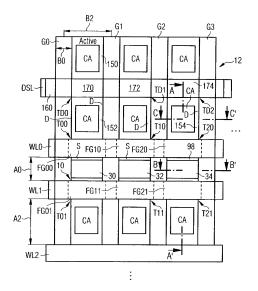

[0021] Fig. 2 eine Draufsicht auf das Speicherzellengebiet,

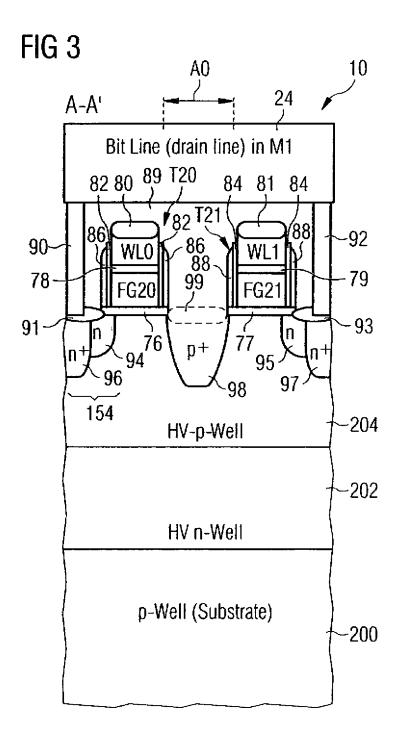

[0022] Fig. 3 eine Querschnittsansicht entlang der in Fig. 2 gezeigten Schnittlinie A-A',

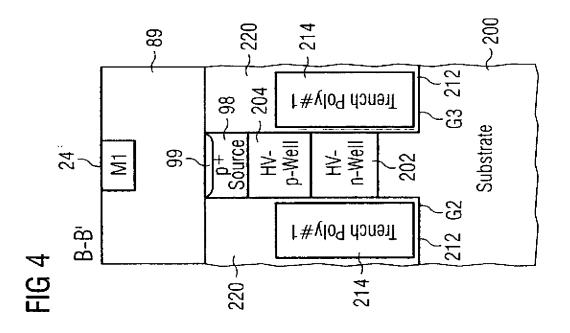

[0023] Fig. 4 eine Querschnittsansicht entlang der in Fig. 2 gezeigten Schnittlinie B-B', und

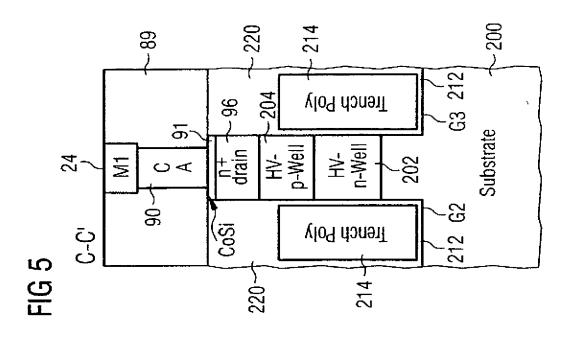

**[0024] Fig.** 5 eine Querschnittsansicht entlang der in **Fig.** 2 gezeigten Schnittlinie C-C'.

**[0025]** Obwohl hier ein Flash-EEPROM beschrieben wird, kann die Speicherschaltungsanordnung z. B. ein EEPROM mit selektivem Löschen, ein EPROM, ein ROM (Read Only Memory) oder eine andere Speicherschaltungsanordnung sein. Jede Speicherzelle kann nur einen einzigen Transistor, wie z. B. einen Floating-Gate-Transistor im Falle eines EEPROM oder eines Flash-EEPROM's, oder mehrere Transistoren enthalten.

[0026] Fig. 1 ist ein Ausschnitt eines Schaltplans einer integrierten Speicherschaltungsanordnung 10, die eine Vielzahl Speichersegmentgebiete 12, 14 enthält. Die Speichersegmentgebiete 12, 14 werden auf die gleiche Art hergestellt. Deshalb wird im Folgenden nur der Aufbau des Speichersegmentsgebiets 12 näher erläutert. Die Speicherschaltungsanordnung 10 enthält eine Vielzahl globaler Bitleitungen BL0 bis BLm, von denen drei globale Bitleitungen BL0, BL1

und BL2 in **Fig.** 1 dargestellt sind. Weitere globale Bitleitungen **16** sind durch Punkte dargestellt.

[0027] Das Speichersegmentgebiet 12 enthält eine Zeile aus Drain-Auswahltransistoren TD0 bis TDm, von denen in Fig. 1 drei Drain-Auswahltransistoren TD0, TD1 und TD2 dargestellt sind. Die Gates der Drain-Auswahltransistoren TD0, TD1 und TD2 sind elektrisch mit einer Drain-Auswahlleitung DSL verbunden, die in Zeilenrichtung angeordnet ist.

[0028] Weiterhin enthält das Speichersegmentgebiet 12 eine Vielzahl Speicherzelltransistoren T01 bis Tmn, von denen in Fig. 1 fünfzehn Speicherzelltransistoren T00 bis T24 dargestellt sind. Der erste Index m bezeichnet die Spalte, in der der betreffende Speicherzelltransistor angeordnet ist. Der zweite Index n bezeichnet die Zeile, in der der betreffende Speicherzelltransistor angeordnet ist. Beispielsweise ist der Speicherzelltransistor T12 in der Spalte mit dem Index 1 und in der Zeile mit dem Index 2 angeordnet, wobei hier die Zählung der Zeilen bzw. der Spalten mit 0 beginnt.

**[0029]** Die Gateelektroden der Speicherzelltransistoren jeder Zeile des Speichersegmentgebiets **12** sind jeweils mit einer Wortleitung WL0 bis WLn elektrisch leitfähig verbunden. In **Fig.** 1 sind fünf Wortleitungen WL0 bis WL4 dargestellt. Weitere Wortleitungen **18** sind durch Punkte dargestellt.

**[0030]** Die Speicherzelltransistoren T00 bis T24 sind Floating Gate Transistoren. Elektrische Ladungen werden in dem Floating Gate gespeichert, das elektrisch isoliert ist. Das Floating Gate ist entweder elektrisch leitfähig oder elektrisch isolierend.

[0031] Das Speichersegmentgebiet 12 enthält Source-Auswahltransistoren TS0 bis TSn, von denen in Fig. 1 drei Source-Auswahltransistoren TS0 bis TS2 dargestellt sind. Die Gateelektroden der Source-Auswahltransistoren TS0 bis TS2 sind elektrisch leitfähig mit einer Source-Auswahlleitung SSL verbunden.

[0032] Das Speichersegmentgebiet 12 enthält außerdem elektrisch isolierende Wannen W0 bis Wm, von denen in Fig. 1 drei isolierende Wannen W0 bis W2 dargestellt sind. Die isolierenden Wannen W0 bis Wm werden durch elektrisch isolierende Gräben G0 bis G(m + 1) begrenzt, von denen in Fig. 1 vier isolierende Gräben G0 bis G3 dargestellt sind. Beispielsweise ist der isolierende Graben G1 zwischen der isolierenden Wanne W0 und der isolierenden Wanne W1 angeordnet.

**[0033]** In jeder isolierenden Wanne W0 bis W2 sind Speicherzelltransistoren einer Spalte, ein Drain-Auswahltransistor und ein Source-Auswahltransistor angeordnet. Die Drain-Auswahltransistoren und die Source-Auswahltransistoren werden zur Auswahl der

Speicherzelltransistoren genutzt. Beispielsweise enthält die isolierende Wanne W0 den Drain-Auswahltransistor TD0, die Speicherzelltransistoren T00 bis T04 und den Source-Auswahltransistor TS0. Die Anordnung der Transistoren in jeder isolierenden Wanne W0 bis Wm ist gleich. Deshalb wird im Folgenden nur die Anordnung der Transistoren in der isolierenden Wanne W0 näher erläutert.

[0034] Die Drain-Elektrode des Drain-Auswahltransistors TD0 ist elektrisch leitfähig mit der Bitleitung BL0 verbunden. Die Sourceelektrode des Drain-Auswahltransistor TD0 ist elektrisch leitfähig mit den Drainelektroden der Speicherzelltransistoren T00 bis T04 über die erhöhte Drainleitung 20 verbunden, die auch als Bitleitung bezeichnet wird. Die erhöhte Drainleitung 20 ist oberhalb der isolierenden Wanne W0 in der ersten Metallisierungslage M1 angeordnet. Damit wird die erhöhte Bitleitung oberhalb der isolierenden Wanne W0 hergestellt, nachdem die isolierende Wanne W0 hergestellt worden ist. Die erhöhte Drainleitung 20 besteht beispielsweise aus einem elektrisch leitfähigem Material, wie Aluminium, Kupfer, einer Aluminiumlegierung oder einer Kupferlegierung.

[0035] Die Sourceelektroden der Speicherzelltransistoren T00 bis T04 sind elektrisch mit der isolierenden Wanne W0 mit Hilfe von Kontaktabschnitten 30, 40, 50, 60 bzw. 70 verbunden. Deshalb hat die isolierende Wanne W0 die Funktion einer vergrabenen Sourceleitung oder einer vergrabenen Bitleitung, die in einem einkristallinen Halbleitersubstrat vergraben ist. Hingegen wird zu der oben erwähnten erhöhten Bitleitung die vergrabene Bitleitung, d. h. die isolierende Wanne W0, unterhalb einer oder mehrerer Schichten angeordnet, wie z. B. der Metalllage M1.

[0036] Die Sourceelektrode des Drain-Auswahltransistors TS0 ist mit einer globalen Sourceleitung SL0 verbunden, die auch als globale Bitleitung bezeichnet wird. Die globale Sourceleitung SL0 ist in der Metalllage M2 oberhalb der erhöhten Drainleitung 20 angeordnet. Die anderen isolierenden Wannen W1, W2 usw. haben globale Sourceleitungen SL1, SL2 usw.

[0037] Die Verwendung der lokalen Drainleitungen 20, 22 und 24 gestattet die Bildung von Minisektoren 100, die nur die Speicherzellen eines Spaltenabschnitts, aber nicht der gesamten Spalte enthalten. Eine solche Anordnung ist hinsichtlich der Leistungsaufnahme der Speicherschaltungsanordnung 10 und hinsichtlich der Schreibgeschwindigkeit, der Lesegeschwindigkeit und der Löschgeschwindigkeit der Speicherzellen günstig.

[0038] Fig. 2 zeigt eine Draufsicht auf das Speichersegmentgebiet 12. Gleiche Bezugszeichen werden für die gleichen Bestandteile in allen Figuren verwendet. Eine Breite B0 der Isoliergräben G0 bis G3

ist kleiner als 150 nm. Im Ausführungsbeispiel beträgt die Breite B0 100 nm. Ein Abstand B2 zwischen den Mittellinien zweier benachbarter Isoliergräben ist kleiner als 300 nm. Im Ausführungsbeispiel ist der Abstand B2 gleich 250 nm. Der Abstand B2 wird auch als Bitleitungsversatz bezeichnet, da der Abstand zwischen einander benachbarten erhöhten Drainleitungen 20, 22 oder 24 oder zwischen einander benachbarten vergrabenen Sourceleitungen den gleichen Wert hat. Um die Herstellung eines so kleinen Abstandes 32 zu ermöglichen, können die Drain-Auswahltransistoren TD0 bis TD2 und die Source-Auswahltransistoren TS0 bis TS2 beispielsweise als Mehrfachgate-Transistoren ausgebildet werden, wie z. B. als Doppelgate-Transistoren oder als Dreifachgate-Transistoren. Bei einem weiteren Ausführungsbeispiel enthalten auch die Mehrfachgate-Transistoren jeweils mehr als ein Gate zwischen nur einem Sourcebereich und einen Drainbereich oder zwischen mehreren Sourcebereichen und mehreren Drainbereichen.

[0039] In Fig. 2 sind Floating Gates FG00 bis FG21 der Speicherzelltransistoren T01 bis T21 dargestellt. Kontaktgebiete CA zu Sourcegebieten S oder zu Draingebieten D der Auswahltransistoren und der Speicherzelltransistoren sind beispielsweise etwas kleiner als die kontaktierten Sourcegebiete S oder Draingebiete D.

**[0040]** Die Halbleiter-Sourcebereiche S der Speicherzelltransistoren T00 bis T21 haben einen anderen Dotiertyp als die Halbleiter-Drainbereiche D dieser Transistoren T00 bis T21. Wenn die Sourcebereiche S den n Dotiertyp haben, haben die Drainbereiche D den p Dotiertyp, bzw. umgekehrt.

[0041] Die Drainbereiche D und die Sourcebereiche S der Speicherzelltransistoren T00 bis T21 werden mit zwei selbstausrichtenden Implantationen hergestellt, nachdem die Drain-Auswahlleitung DSL, die Wortleitungen WL0 bis WLm und die Source-Auswahlleitung SSL hergestellt worden sind. Die Drainbereiche D werden dotiert, wobei beispielsweise eine Maske verwendet wird, die die Sourcebereiche bedeckt. Dennoch ist die Dotierung der Drainbereiche selbstausrichtend zu den Gateelektroden der Speicherzelltransistoren, wenn die Kanten der Maske oberhalb der Gateelektroden angeordnet werden, beispielsweise mit der Kante entlang der Mittellinie auf der Deckfläche der Gateelektroden.

**[0042]** Der Drain-Auswahltransistor TD0 hat beispielsweise sowohl ein n-Typ Draingebiet **150** und ein n-Typ Sourcegebiet **152**, welches auch die Drain-Elektrode des Speicherzelltransistors T00 ist, d. h. sie sind vom gleichen Dotierstofftyp. Die Drain-Elektroden der Speicherzelltransistoren T00 bis T21 sind auch vom n-Typ, z. B. die Drain-Elektrode **154** des Speicherzelltransistors T20, jedoch sind die Source-

gebiete der Speicherzelltransistoren T00 bis T21 vom p-Typ, z. B. die Sourceelektrode **98** des Speicherzelltransistors T20. Deshalb sind die Speicherzelltransistoren T00 bis T21 Tunneltransistoren, die nicht nur Löschen und Schreiben gestatten, sondern auch Lesen. In der Lesebetriebsart fließt ein Tunnelstrom durch einen Tunnelübergang zwischen einem Inversionskanal und dem Sourcebereich. Der Tunnelstrom in diesem Übergang wird durch die im Floating Gate gespeicherte Ladung beeinflusst. Somit ist das Erfassen der im Floating Gate gespeicherten Ladung möglich.

[0043] Oberhalb der Drain-Auswahlleitung DSL ist eine optionale Leitung 160 angeordnet, die elektrisch von der Drain-Auswahlleitung 160 durch eine isolierende Schicht getrennt ist. Die Drain-Auswahlleitung DSL enthält die Steuergates 170, 172 bzw. 174 der Drain-Auswahltransistoren TD0, TD1 bzw. TD2.

[0044] Fig. 2 zeigt außerdem die Lage dreier Querschnitte:

- der Querschnitt A-A' liegt in Spaltenrichtung und schneidet die Mittellinie der isolierenden Wanne wa

- Der Querschnitt B-B' liegt in Zeilenrichtung und schneidet den Kontaktabschnitt 34 des Speicherzelltransistors T20.

- Der Querschnitt C-C' liegt ebenfalls in Zeilenrichtung und schneidet den Drainbereich 154 des Speicherzelltransistors T20.

**[0045]** Alle drei Querschnitte A-A', B-B' und C-C' liegen in Ebenen, die jeweils parallel zu der Normalenrichtung der Oberfläche des Halbleitersubstrats liegen, das zur Herstellung der Speicherschaltungsanordnung **10** verwendet wird.

[0046] Weiterhin ist ein Abstand A0 zwischen Floating Gates, die einander benachbart in der Spaltenrichtung sind und die an den gleichen Sourcebereich angrenzen, die minimale Strukturbreite in der Speicherschaltungsanordnung 10. Beispielsweise beträgt die Breite 100 nm (Nanometer) für eine 130 nm Technologie, d. h. eine Technologie, welche eine Wellenlänge von 130 nm zum Bestrahlen von Fotoresist während der Herstellung verwendet, oder die Breite beträgt 70 nm für eine 90 nm Technologie. Alternativ ist der Abstand A0 kleiner als die minimale Strukturbreite zuzüglich einem Zwischenraumabstand von beispielsweise 10 Prozent der minimalen Strukturbreite. Ein Abstand A2 zwischen Floating Gates, die in Spaltenrichtung einander benachbart sind und die an denselben Drainbereich angrenzen, ist größer als die minimale Strukturbreite zuzüglich 10 Prozent dieser Breite, insbesondere ist der Abstand A2 größer als der Abstand A0. Der Abstand A0 kann kleiner als der Abstand A2 ausgeführt werden, weil keine schwach dotierten Bereiche (LDD) für die Sourcebereiche der Speicherzelltransistoren T00 bis T24 erforderlich sind. Die LDD-Bereiche können weggelassen werden, weil kein Überlapp der LDD-Bereiche durch Silizid erforderlich ist. Das Silizid muss auch nicht die vergrabenen Verbindungsstreifen überlappen, um einen elektrischen Kontakt zu den vergrabenen Verbindungsstreifen herzustellen. Die Verbindungsstreifen werden durch die p-Wanne kontaktiert, d. h. durch die vergrabene Bitleitung. Außerdem ist der Abstand A0 klein, weil kein Kontaktgebiet zu diesem Sourcebereich erforderlich ist. Der Grund für den kleinen Abstand A0 wird unten an Hand der **Fig.** 3 näher erläutert.

**[0047] Fig.** 3 zeigt eine Querschnittsansicht entlang der Schnittlinie A-A' der **Fig.** 2. Die Speicherschaltungsanordnung **10** ist in und an einem einkristallinen Halbleitersubstrat **200** angeordnet, das beispielsweise aus schwach p dotiertem Silizium besteht.

[0048] In dem Halbleitersubstrat 200 sind eine n-dotierte Schicht 202 und eine p-dotierte Schicht 204 durch eine Dotiertechnik hergestellt worden, beispielsweise durch Implantation. Die n-dotierte Schicht 202 liegt tiefer in dem Substrat 200 als die p-dotierte Schicht 204. Die n-dotierte Schicht 202 ist zwischen dem Substrat 200 p-Bereich und der p-dotierten Schicht 204 angeordnet. In der Nachbarschaft des Querschnitts A-A' bilden die Schichten 202 und 204 die isolierende Wanne W2, weil sie durch die isolierenden Gräben G2 und G3 begrenzt werden, die in Fig. 3 nicht dargestellt sind, die aber vor und hinter dem Querschnitt A-A' angeordnet sind.

**[0049]** Im Ausführungsbeispiel ist die Dotierstoffkonzentration im Substrat **200** gleich 10<sup>15</sup> Dotierstoffatome je cm³ (Kubikzentimeter). Die maximale Dotierstoffkonzentration der n-dotierten Schicht **202** ist größer als 10<sup>16</sup> Dotierstoffatome je cm³, aber kleiner als 10<sup>20</sup> Dotierstoffatome je cm³. Die maximale Dotierstoffkonzentration der p-dotierten Schicht **204** liegt im Bereich von 10<sup>16</sup> Dotierstoffatomen je cm³ bis 10<sup>18</sup> Dotierstoffatomen je cm³.

**[0050]** Wie in **Fig.** 3 dargestellt ist, enthält der Gatestapel des Speicherzelltransistors T20, T21 in der folgenden Reihenfolge mit zunehmendem Abstand vom Substrat **200**:

- 1) ein Floating Gate-Dielektrikum 76, 77, wie

z. B. ein Oxid oder ein nitridiertes Oxid mit einer

Schichtdicke von bspw. 9 nm,

- 2) das Floating Gate FG20, FG21, bestehend aus polykristallinem Silizium mit einer Schichtdicke von bspw. 100 nm,

- 3) ein Steuergate-Dielektrikum 78, 79, wie z. B. ein ONO-Dielektrikum, das aus einem Stapel mit drei Schichten gebildet wird, nämlich einer Oxidschicht, einer Nitridschicht oder einer Oxinitridschicht und einer Oxidschicht. Die Dicke der ONO-Schicht beträgt bspw. 10 nm.

- 4) Ein Steuergate, das aus einem Abschnitt der Wortleitung WL0, WL1 gebildet wird, die aus polykristallinem Silizium hergestellt ist und eine Dicke von bspw. 100 nm hat, und

- 5) einem silizidierten Bereich 80, 81, der aus einer Metallsiliziumlegierung besteht, wie z. B. aus Kobaltsilizid, an der Deckfläche des Gatestapels.

[0051] Die Seitenwände des Floating Gates FG20, FG21, des Steuergate-Dielektrikums 78, 79 und des Steuergates (Wortleitung WL0, WL1) sind mit einem Dielektrikum 82, 84 bedeckt, z. B. einem thermischen Oxid. Seitenwandspacer 86, 88, die beispielsweise aus Oxid oder Nitrid bestehen, sind angrenzend an das Dielektrikum 82, 84 angeordnet. Die Seitenwandspacer 86, 88 sind Einfach- oder Doppelsparer. Doppelseitenwandspacer werden bevorzugt zur Bildung der LDD- und HDD-Dotierstoffbereiche verwendet, die unten genauer erklärt werden. Einfachspacer werden verwendet, wenn nur HDD-Bereiche verwendet werden.

[0052] Die Gatestapel der Speicherzelltransistoren T20 und T21, die Seitenwanddielektrika 82, 84 und die Seitenwandspacer 86, 88 werden von einer dielektrischen Schicht 89 umgeben, beispielsweise einer Siliziumoxidschicht, einer TEOS-Schicht (TetraEthylOrthoSilikat) oder einer Silikatglasschicht, wie einer BPSG-Schicht (BorPhosphorSilikatGlas). Alternativ wird eine dielektrische Schicht 89 mit einer kleinen relativen Dielektrizitätskonstante k verwendet.

[0053] Die dielektrische Schicht 89 enthält auch das Metall M1 und somit auch die erhöhte Drainleitung 24. Ein Metallkontakt 90 befindet sich in einem Kontaktloch, das sich durch die dielektrische Schicht 89 von der Drainleitung 84 zu einem silizidierten Bereich 81 auf der Deckfläche des Drainbereiches 154 des Transistors T20 erstreckt. Ein Metallkontakt 92 befindet sich zwischen der Drainleitung 24 und einem silizidierten Bereich 93 auf der Deckfläche des Drainbereichs des Transistors T21.

[0054] Die Drainbereiche D der Speicherzelltransistoren T20, T21 enthalten n-dotierte LDD-Bereiche 94, 95 und n-dotierte HDD-Bereiche 96, 97. Die maximale Dotierstoffkonzentration in den LDD-Bereichen 94, 95 ist beispielsweise größer als oder gleich 10<sup>17</sup> cm<sup>-3</sup> und kleiner als 10<sup>19</sup> cm<sup>-3</sup>. In den HDD-Bereichen ist die maximale Dotierstoffkonzentration dagegen größer als oder gleich 10<sup>19</sup> cm<sup>-3</sup>.

**[0055]** Beide Speicherzelltransistoren T20 und T21 haben einen gemeinsamen Sourcebereich S. Im Ausführungsbeispiel enthält der gemeinsame Sourcebereich nur einen stark p-dotierten Sourcebereich **98**, der eine maximale Dotierstoffkonzentration größer als oder gleich 10<sup>19</sup> cm<sup>-3</sup> hat. Keine Metallkontakte führen zu den gemeinsamen Sourcebereichen S,

98. Die Sourcebereiche werden mit dem Streifen der Schicht 204 elektrisch verbunden, der zwischen benachbarten Gräben G2, G3 liegt. Weil kein Metallkontakt zu dem Sourcebereich 98 führt, ist ein silizidiertes Gebiet auf der Deckfläche dieses Bereiches 98 nicht erforderlich. Damit befindet sich kein silizidiertes Gebiet auf der Deckfläche des Sourcebereiches 98 gemäß einem ersten Ausführungsbeispiel. In einem alternativen Ausführungsbeispiel befindet sich dagegen ein silizidierter Bereich 99 auf der Deckfläche des Sourcebereiches 98, weil keine weiteren Schritte erforderlich sind, um die Bildung eines Silizides 99 zu vermeiden, wenn andere Bereiche silizidiert werden, beispielsweise 80, 81 und 91, 93. Ein silizidierter Bereich ist z. B. vorteilhaft, wenn der Sourcebereich ein stark dotiertes Gebiet und ein schwach dotiertes Gebiet enthält.

[0056] Fig. 4 zeigt eine Querschnittsansicht entlang der Schnittlinie B-B' der Fig. 2. Fig. 5 zeigt eine Querschnittsansicht entlang der Schnittlinie C-C' der Fig. 2. Wie in den Fig. 4 und Fig. 5 dargestellt, sind die Gräben G0 bis G3 elektrisch gegen das Substrat 200 am Grabenboden und an den Grabenseitenwänden mit Hilfe eines Randdielektrikums 212 isoliert, beispielsweise einem Randoxid. Das Randdielektrikum 212 hat eine Dicke, die im Vergleich zu der Breite der Gräben G0, G1 usw. klein ist. In einem Ausführungsbeispiel beträgt die Dicke des Randdielektrikums 212 nur 20 nm, d. h. sie ist kleiner als ein Drittel der Grabenbreite. Die tieferen Abschnitte der Gräben G0 bis G3 sind beispielsweise mit polykristallinem Silizium 214 gefüllt. In den gezeigten Ausführungsbeispielen sind etwa zwei Drittel jedes Grabens G0 bis G3 mit polykristallinem Silizium 214 gefüllt. Die oberen Bereiche der Gräben G0 bis G3 sind mit einem dielektrischen Material 220 gefüllt, beispielsweise mit Siliziumoxid. Die oberen Bereiche können gemeinsam mit flachen Gräben geätzt werden, die außerhalb des Speichersegmentgebietes 12, 14 liegen, beispielsweise in der Steuerschaltung, den Wortleitungstreibern, den Bitleitungstreibern oder den Leseverstärkern. Das zweite Ätzen der oberen Bereiche der Gräben und der flachen Gräben kann gleichzeitig ausgeführt werden, wenn eine eingebettete Speicherschaltungsanordnung 10 hergestellt wird, die mit einem Logikschaltkreis eingebettet ist, z. B. mit einem Prozessor. In einem alternativen Ausführungsbeispiel sind die Gräben nur mit einem Material gefüllt oder die oberen Bereiche der Gräben G0 bis G3 sind ebenfalls mit polykristallinem Silizium gefüllt.

[0057] Bei einem Ausführungsbeispiel liegt die Tiefe der Gräben G0 bis G3 im Bereich von 0,9 bis 1,5  $\mu$ m, beispielsweise bei 1  $\mu$ m. Die Gräben G0 bis G3 erstrecken sich durch die Schicht 204 und auch durch die Schicht 202. Bei einem alternativen Ausführungsbeispiel befinden sich die Böden der Gräben G0 bis G3 in der Schicht 202.

[0058] Wie ebenfalls in den Fig. 4 und Fig. 5 dargestellt ist, endet der p-dotierte Sourcebereich 98 des Speicherzelltransistors T20 in dem Streifen der p-dotierten Schicht 204, der die vergrabene Sourceleitung für Transistor T20 bildet. Der n-dotierte Drainbereich 96 des Speicherzelltransistors T20 endet ebenfalls in dem Streifen der p-dotierten Schicht 204, der die vergrabene Sourceleitung bildet.

[0059] Hinsichtlich der verschiedenen Betriebsarten werden für den Transistor T11 die Programmierbetriebsart, die Löschbetriebsart und die Lesebetriebsart erläutert. Bei anderen Ausführungsbeispielen werden Spannungswerte anderer Polaritäten und anderer Werte verwendet. In einem speziellen Ausführungsbeispiel werden Spannungen verwendet, die nur im Bereich von +50 Prozent bis -50 Prozent von den Spannungen im Ausführungsbeispiel abweichen. Außerdem kann die Aufteilung der Spannungen bzw. das Splitting bei gleicher Potentialdifferenz anders sein, beispielsweise +8,5 Volt und -8,5 Volt können an Stelle von +14 Volt und -3 Volt verwendet werden. Zusätzlich oder an Stelle der Spannungsaufteilung kann die absolute Spannungsdifferenz auch beispielsweise im Bereich von +50 Prozent bis -50 Prozent geändert werden.

**[0060]** Während des Programmierens liegen am Transistor T11 die folgenden Spannungen an:

- +14 Volt an der Steuergateelektrode, und

- 3 Volt am Sourcebereich, am Substratbereich und am Drainbereich.

**[0061]** Unter diesen Bedingungen fließt ein Tunnelstrom von einem Inversionskanal in dem Substrat durch das gesamte Gebiet des Tunnel-Dielektrikums in das Floating Gate des Transistors T11.

**[0062]** Während des Programmierens liegen an Transistoren derselben Zeile wie der Transistor T11 aber in einer anderen Spalte als der Transistor T11, z. B. am Transistor T21, die folgenden Spannungen an:

- +14 Volt an der Gateelektrode, und

- +3 Volt an dem Sourcebereich, dem Substratbereich und dem Drainbereich.

**[0063]** Unter diesen Bedingungen fließt kein Tunnelstrom zum Floating Gate im Transistor T11, weil die Spannungsdifferenz zu klein ist.

**[0064]** Während des Programmierens liegen an Transistoren derselben Spalte wie der Transistor T11 aber in einer anderen Zeile als Transistor T11, z. B. am Transistor T12, die folgenden Spannungen an:

- 0 Volt oder -3 Volt an der Gateelektrode, und

- –3 Volt am Sourcebereich, am Substratbereich und am Drainbereich.

[0065] Während des Programmierens liegen an Transistoren einer anderen Zeile als Transistor T11

und in einer anderen Spalte als Transistor T11, z. B. am Transistor T22, die folgenden Spannungen an:

- 0 Volt an der Steuergateelektrode, und

- +3 Volt an dem Sourcebereich, dem Substratbereich und dem Drainbereich.

[0066] Während des Löschens werden alle Speicherzellen eines Speichersegmentgebietes 12, 14 oder eines Minisektors 100 gleichzeitig gelöscht. Alternativ werden nur die Speicherzellen gelöscht, die mit einer Wortleitung oder mit einem Abschnitt einer Wortleitung verbunden sind. Bei einem weiteren Ausführungsbeispiel wird nur eine einzige Zelle gelöscht, ohne dass andere Zellen gelöscht werden. Zum Löschen aller Transistoren T00 bis T24 haben alle diese Transistoren die gleichen Spannungen. Beispielsweise sind die Spannungen für den Transistor T11:

- -- 14 Volt an dem Steuergate, und

- +3 Volt am Sourcebereich, am Drainbereich und an dem Substrat.

**[0067]** Während des Löschens fließt ein Tunnelstrom in die umgekehrte Richtung im Vergleich zu dem Tunnelstrom während des Programmierens.

[0068] In der Lesebetriebsart gilt für Transistor T11:

- +2.5 Volt an der Gateelektrode,

- 0 Volt an dem Sourcebereich und dem Substratbereich, und 1 Volt oder 1,2 Volt an dem Drainbereich.

**[0069]** Unter diesen Bedingungen wird der Drain-Strom oder die Schwellspannung des Transistors T11 erfasst und verstärkt.

[0070] Andere Arten von EEPROM-Zellen werden ebenfalls verwendet, beispielsweise sogenannte "Splitgate"-Zellen oder ETOX-Zellen (EPROM-TunnelOxid). Andere Programmierbetriebsarten, Lesebetriebsarten oder Löschbetriebsarten sind ebenfalls möglich, wie z. B. das Programmieren mittels "heißen"-Elektronen im Kanal (Channel Hot Electron – CHE).

[0071] Aufgrund einer Hartmaske, wie z. B. einer TEOS-Hartmaske, auf der Deckfläche der Steuergates oder der Wortleitungen WL0 bis WL2, werden Herstellungstechnologien wie eine Doppelimplantation oder eine Gegenimplantation der Steuergates vermieden. Dies führt zu einer Austrittsarbeitsfunktion, die sehr gut gesteuert werden kann, so dass nur eine kleine Schwellspannungsabweichung und eine kleine Stromabweichung zwischen den Zelltransistoren auftritt.

[0072] Obwohl die herkömmliche Flash-Skalierung ihre Grenzen erreicht hat, kann die Verwendung der hier beschriebenen Ausführungsbeispiele die weitere Verkleinerung bis zur 65 nm Generation und dahinter ermöglichen. Für die Zellflächenskalierung kann

das Weglassen von Kontakten immer wichtiger werden. für einen schnellen Zugriff dagegen kann es vorteilhaft sein, Source- und Drain-Kontakte an jeder Zelle zu verwenden, einschließlich von Metallverbindungen. Deshalb können zwei Bitleitungen (BL) je Speicherzelle für Flash-Speicherarchitekturen wünschenswert sein, die für einen schnellen Zugriff geeignet sind, beispielsweise die UCP-Flash-Zelle (Uniform Channel Programming). Jedoch könnte als Folge des Verwendens dieser zwei Metallleitungen die Zellgröße in einer Richtung durch den Versatz zwischen den zwei M1 Leitungen bzw. durch den Metall M1 Versatz begrenzt sein. Weil das Metall M2 üblicherweise für Bitleitungen verwendet wird und das Metall M1 für sogenannte "landing pads" könnte die Zellfläche außerdem in x-Richtung durch das Zweifache des Metall M2 Versatzes begrenzt sein.

[0073] Die Grenze für die Skalierung der Flash-Zelltransistoren könnte außerdem nachteilig aufgrund der Nichtskalierbarkeit des Tunneloxids beeinflusst werden. Beispielsweise werden Kurzkanaleffekte schwerwiegender als bei herkömmlichen Transistorschaltungsanordnungen. Kleine Durchgriffsspannungen und Streuungen der Schwellspannung Vt aufgrund von sogenannten "Roll Off" und Leckströmen könnten große Probleme bei der Verkleinerung der Transistorlänge sein. Jedoch können all diese Beschränkungen mit Hilfe der obigen Ausführungsbeispiele überwunden werden.

**[0074]** Die Verwendung der vergrabenen Verbindungsstreifen in einer sogenannten SNOR-Architektur hat die folgenden Vorteile:

- jeder Sourcebereich ist mit der isolierten p-Wanne durch einen Kurzschluss, bspw. durch einen CoSi-Kurzschluss kurzgeschlossen, der auch als vergrabener Verbindungsstreifen bzw. als buried strap bezeichnet wird.

- die isolierenden p-Wannen ersetzen die metallischen Sourceleitungen (BBL Buried BitLine Concept).

- die Skalierung des Bitleitungsversatzes ist nicht mehr durch den M2-Versatz begrenzt. Bisher war der Bitline-Versatz gleich dem Zweifachen des M2-Versatzes. Die Ausführungsbeispiele zeigen einen einfachen Weg, um einen elektrischen Kontakt zwischen der Source und der p-Wanne herzustellen.

**[0075]** Durch die Verwendung der Ausführungsbeispiele wird Folgendes erreicht:

- zwei Kontakte je Zelle und Bitleitung werden vermieden und die weitere Verkleinerung der Zellgröße ist möglich.

- kein Silizidüberlapp ist auf der Sourceseite erforderlich und er ist optional auf der Drainseite für vergrabene Bitleitungen.

- Eine weitere Skalierung der Zelltransistoren ist möglich, obwohl es dagegen schwerwiegende Gründe gab:

- die Hauptprobleme bei der Skalierung von Flash-Zellen sind die Kurzkanaleffekte und die Skalierung der Oxiddicke. Um den Kanal besser steuern zu können, ist eine Skalierung der Tunnelbzw. Gateoxiddicke wünschenswert.

- Die Skalierung würde jedoch eine erhebliche Erhöhung der sogenannten "Moving Bits"-Rate und eine Verringerung der Haltezeit hervorrufen.

- Außerdem würde die Verkleinerung der Tunneloxiddicke das Koppelverhältnis verringern.

- Bei kurzen Transistorlängen verschlechtert das Leckstromproblem das Lesen der Zelle. Leckstrom verursachende Zellen in derselben Spalte tragen zum Strom der zu lesenden Zelle bei.

[0076] Dies sind die Hauptvorteile des neuen Ansatzes:

- er spart Sourcekontaktfläche und erlaubt somit eine kleinere Zellgröße.

- Ein silizidierter Verbindungsstreifen zwischen der "n+"-Matrix und dem "p+"-Wannenkontakt wird entbehrlich. Es gibt inhärent eine gute Verbindung zwischen "p+"-Source und p-Wanne.

- Die Skalierung des Tunneloxids bzw. Gateoxid wird entbehrlich. Deshalb können eine kleine "Moving Bit"-Rate und (!) eine gute Haltezeit beibehalten werden während das Kopplungsverhältnis groß bleibt.

- Das Leckstromproblem wird auf pin-Übergänge (p-dotiert, intrinsisch, n-dotiert) reduziert. In pin-Übergängen ist der Leckstrom auch für kurze Kanäle sehr klein. In dem Ausführungsbeispiel wurde der intrinsische Bereich durch einen schwach dotierten p-Bereich ersetzt, obwohl auch ein schwach dotierter n-Bereich an Stelle des i-Bereichs verwendet werden kann.

- Aufgrund der pin-Struktur des TFET (Tunneling Field Effect Transistor) werden die Durchbruchsspannung und die Durchtrittsspannung des Bauelementes im Vergleich zu einem Standard MOSFET (MetallOxide Semiconductor) oder einem FET mit isoliertem Gate (IGFET) vergrößert.

- Eine Verringerung des Kurzkanaleffektes aufgrund der höheren Durchgriffsspannung wird erreicht. Somit gestattet das neue Bauelement eine weitere Skalierung der Kanallän ge.

[0077] Mit anderen Worten ausgedrückt, werden "n+"-Sourcebereiche eines NMOS-Zellentransistors durch "p+"-Sourcebereiche ersetzt. Deshalb arbeitet der Zellentransistor als TFET. Um den Transistor zu skalieren, ist nun keine oder nur eine verringerte Skalierung der Oxiddicke erforderlich. Dies ermöglicht einen einfach zu verwirklichenden Kurzschluss zwischen Source und p-Wanne, der eine BBL-Architek-

tur (Buried BitLine) favorisiert. Eine weitere Skalierung der Kanallänge ist nun wieder möglich.

**[0078]** Bei anderen Ausführungsbeispielen werden andere Materialien ebenso verwendet wie andere Abmessungen, Dotierungen, Spannungen und andere Anzahlen im Vergleich zu den oben genannten Angaben. Ebenso lassen sich die oben erwähnten Ausführungsbeispiele herstellen durch die Verwendung von üblichen Anlagen und Techniken.

#### **Patentansprüche**

- 1. Speicherschaltungsanordnung (**10**) mit: einer Vielzahl Speicherzellen, die in einer Matrix angeordnet sind, welche Zeilen aus Speicherzellen und Spalten aus Speicherzellen enthält,

- jede Speicherzelle enthält mindestens einen Zelltransistor (T01 bis Tm, n),

- jeder Zelltransistor (T01 bis Tm, n) enthält einen ersten dotierten Bereich und einen zweiten dotierten Bereich, wobei entweder der erste dotierte Bereich ein Drainbereich (D) und der zweite dotierte Bereich ein Sourcebereich (S) ist oder wobei alternativ der erste dotierte Bereich ein Sourcebereich (S) und der zweite dotierte Bereich ein Drainbereich (D) ist,

- einer Vielzahl von Wortleitungen (WL0 bis WLm), wobei jede Wortleitung mit Speicherzellen einer Zeile verbunden ist.

- einer Vielzahl von ersten Bitleitungen (20 bis 24), wobei jede erste Bitleitung mit Speicherzellen einer Spalte verbunden ist.

- die ersten dotierten Bereiche haben einen anderen Dotiertyp als die zweiten dotierten Bereiche,

- einem gemeinsamen zweiten dotierten Bereich (S), der Speicherzellen gemeinsam ist, die in einer Spalte aneinandergrenzen,

- dadurch gekennzeichnet, dass ein erster Abstand (A0) zwischen Floating Gates der Transistoren (T00 bis Tm, n) der in einer Spalte an einem gemeinsamen zweiten dotierten Bereich (S) aneinander grenzenden Speicherzellen kleiner als ein zweiter Abstand (A2) zwischen Floating Gates von Transistoren (T00 bis Tm, n) ist, die an einen gemeinsamen ersten dotierten Bereich in der gleichen Spalte angrenzen, und durch eine Steuerschaltung für eine Lesebe-

- wobei die Zelltransistoren Tunnel-Feldeffekttransistoren sind.

triebsart.

und wobei die Steuerschaltung in der Lesebetriebsart einen Tunnelstrom durch einen Tunnel-Übergang zwischen einem an dem einen Source- oder Drainbereich des Tunnel-Feldeffekttransistors beginnenden Inversionskanal und dem anderen Source- oder Drainbereich des Tunnel-Feldeffekttransistors fließen lässt, wobei der Tunnelstrom in diesem Übergang durch in einem Floatinggate gespeicherte Ladungen beeinflusst wird.

- 2. Schaltungsanordnung (**10**) nach Anspruch 1, gekennzeichnet durch eine Vielzahl zweiter Bitleitungen (W0 bis W2), wobei jede zweite Bitleitung (W0 bis W2) mit Speicherzellen einer Spalte verbunden ist, deren Speicherzellen auch mit einer der ersten Bitleitungen verbunden sind.

- 3. Schaltungsanordnung (10) nach Anspruch 2, dadurch gekennzeichnet, dass die ersten Bitleitungen (20 bis 24) erhöhte Bitleitungen sind, die über die Speicherzellen angehoben sind, und dass die zweiten Bitleitungen (W0 bis W2) vergrabene Bitleitungen sind.

- 4. Schaltungsanordnung (10) nach Anspruch 2 oder 3, dadurch gekennzeichnet, dass jede Speicherzelle einen Zelltransistor (T01 bis Tm, n) enthält, wobei jede erste Bitleitung mit den ersten dotierten Bereichen (D) der Zelltransistoren einer Spalte und jede zweite Bitleitung mit den zweiten dotierten Bereichen (S) der Zelltransistoren einer Spalte verbunden ist.

- 5. Schaltungsanordnung (10) nach Anspruch 3 oder 4, dadurch gekennzeichnet, dass jede vergrabene Bitleitung (W0 bis W2) eine isolierende dotierte Wanne (204) ist, die die Substratbereiche der Zelltransistoren (T01 bis Tm, n) einer Spalte enthält.

- 6. Schaltungsanordnung (10) nach Anspruch 5, dadurch gekennzeichnet, dass der Dotiertyp jeder Wanne (W0 bis W2) der gleiche Dotiertyp ist, den auch die zweiten dotierten Bereiche (S) haben.

- 7. Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die ersten dotierten Bereiche (D) schwach dotierte LDD-Bereiche (94, 95) sowie stark dotierte Bereiche und die zweiten dotierten Bereiche (S) nur stark dotierte Bereiche (98) enthalten.

- 8. Schaltungsanordnung (10) nach einem der vorhergehenden Ansprüche, dadurch gekennzeichnet, dass die ersten dotierten Bereiche (D) und die zweiten dotierten Bereiche (S) silizidiert sind (91, 93, 99).

- 9. Schaltungsanordnung (10) nach einem der Ansprüche 1 bis 7, dadurch gekennzeichnet, dass die ersten dotierten Bereiche (D) silizidiert (91, 93) und die zweiten dotierten Bereiche (S) nicht silizidiert sind.

- 10. Schaltungsanordnung (10) nach Anspruch 2 oder 3, dadurch gekennzeichnet, dass mindestens eine der ersten Bitleitungen oder der zweiten Bitleitungen eine unterhalb der Speicherzellen vergrabene Bitleitung ist.

11. Verfahren zur Herstellung einer Speicherschaltungsanordnung in einem Halbleitersubstrat (200), wobei die Schaltungsanordnung (10) ein Speicherzellenfeld enthält, das seinerseits eine Vielzahl von Speicherzelltransistoren enthält, die in Zeilen und Spalten angeordnet sind, das Verfahren enthält die folgenden Schritte:

Ausbilden einer Vielzahl von Wortleitungen (WL0 bis WL4), wobei jede Wortleitung (WL0 bis WL4) mit Speicherzellen einer Zeile verbunden ist,

Ausbilden von ersten dotierten Bereichen und zweiten dotierten Bereichen in jeder Spalte, wobei die ersten dotierten Bereiche Drainbereiche (D) und die zweiten dotierten Bereiche Sourcebereiche (S) sind, oder wobei alternativ die ersten dotierten Bereiche Sourcebereiche (S) und die zweiten dotierten Bereiche Drainbereiche (D) sind, und wobei die ersten Dotierbereiche einen ersten Dotiertyp haben und die zweiten Dotierbereiche einen zweiten Dotiertyp haben, der verschieden von dem ersten Dotiertyp ist, und

Ausbilden einer Vielzahl von ersten Bitleitungen (20 bis 24), wobei jede erste Bitleitung (20 bis 24) mit Speicherzellen einer Spalte verbunden ist,

wobei gemeinsame zweite dotierten Bereiche (S) für Speicherzellen ausgebildet werden, die in einer Spalte jeweils an einem zweite dotierten Bereich (S) aneinandergrenzen,

dadurch gekennzeichnet, dass ein erster Abstand (A0) zwischen Floating Gates der Transistoren (T00 bis Tm, n) der in einer Spalte an einem gemeinsamen zweiten dotierten Bereich (S) aneinander grenzenden Speicherzellen kleiner als ein zweiter Abstand (A2) zwischen Floating Gates von Transistoren (T00 bis Tm, n) ist, die an einen gemeinsamen ersten dotierten Bereich in der gleichen Spalte angrenzen, und durch eine Steuerschaltung für eine Lesebetriebsart.

wobei die Zelltransistoren Tunnel-Feldeffekttransistoren sind.

und wobei die Steuerschaltung in der Lesebetriebsart einen Tunnelstrom durch einen Tunnel-Übergang zwischen einem an dem einen Source- oder Drainbereich des Tunnel-Feldeffekttransistors beginnenden Inversionskanal und dem anderen Source- oder Drainbereich des Tunnel-Feldeffekttransistors fließen lässt, wobei der Tunnelstrom in diesem Übergang durch in einem Floatinggate gespeicherte Ladungen beeinflusst wird.

12. Verfahren nach Anspruch 11, gekennzeichnet durch die Schritte:

Ausbilden einer ersten Wanne (204) des zweiten Dotiertyps,

Ausbilden einer zweiten Wanne (202) des ersten Dotiertyps tiefer liegend als die erste Wanne (204) oder die erste Wanne (204) umgebend, und

Ausbilden von tiefen Gräben (60 bis 62), die tief genug sind, um die erste Wanne (204) oder die erste

Wanne (204) und die zweite Wanne (202) zu durchdringen.

- 13. Verfahren nach Anspruch 12, **dadurch ge-kennzeichnet**, dass die erste Wanne (**204**) die Sourcebereiche (S), die Drainbereiche (D) und Substratbereiche der Speicherzelltransistoren (T00 bis Tm, n) einer Spalte enthält.

- 14. Verfahren nach einem der Ansprüche 11 bis 13, gekennzeichnet durch den Schritt: Silizidieren der ersten dotierten Bereiche (D) und der zweiten dotierten Bereiche (S).

- 15. Verfahren nach Anspruch 14, **dadurch ge-kennzeichnet**, dass das Silizidieren in einem selbst-ausrichtenden Silizidierverfahren erfolgt.

- 16. Verfahren nach einem der Ansprüche 12 bis 15, gekennzeichnet durch den Schritt: Silizidieren der ersten dotierten Bereiche (D), jedoch nicht der zweiten dotierten Bereiche (S), vorzugsweise in einem selbstausrichtenden Silizidierverfahren.

- 17. Verfahren nach einem der Ansprüche 11 bis 16, gekennzeichnet durch den Schritt: Silizidieren von Steuergates (WL0 bis WL2) der Speicherzellen.

- 18. Verfahren nach Anspruch 17, wobei ein selbstausrichtendes Silizidierverfahren verwendet wird.

- 19. Verfahren nach einem der Ansprüche 11 bis 17, gekennzeichnet durch den Schritt: Verwenden einer Hartmaske auf der Oberfläche der Steuergates als Maske für eine selbstausrichtende Dotierung der ersten dotierten Bereiche (D) und der zweiten dotierten Bereiche (S).

Es folgen 4 Seiten Zeichnungen

## Anhängende Zeichnungen

FIG 1