(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5366517号

(P5366517)

(45) 発行日 平成25年12月11日(2013.12.11)

(24) 登録日 平成25年9月20日(2013.9.20)

|               |                                |

|---------------|--------------------------------|

| (51) Int.Cl.  | F 1                            |

| HO 1 L 21/02  | (2006.01) HO 1 L 27/12 B       |

| HO 1 L 27/12  | (2006.01) HO 1 L 29/78 6 2 7 D |

| HO 1 L 21/336 | (2006.01) HO 1 L 29/78 6 2 7 A |

| HO 1 L 29/786 | (2006.01) HO 1 L 29/78 6 1 3 Z |

請求項の数 3 (全 55 頁)

(21) 出願番号 特願2008-303618 (P2008-303618)

(22) 出願日 平成20年11月28日 (2008.11.28)

(65) 公開番号 特開2009-158939 (P2009-158939A)

(43) 公開日 平成21年7月16日 (2009.7.16)

審査請求日 平成23年9月9日 (2011.9.9)

(31) 優先権主張番号 特願2007-311910 (P2007-311910)

(32) 優先日 平成19年12月3日 (2007.12.3)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 土屋 薫

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に第1の無機絶縁膜を形成し、

前記第1の無機絶縁膜上に第1の半導体素子層を形成し、

前記第1の半導体素子層上に第2の無機絶縁膜を形成し、

前記第2の無機絶縁膜を平坦化処理し、

第2の基板上に第2の剥離層をスパッタリング法により形成し、

前記第2の剥離層を逆スパッタリング法により平坦化処理し、

前記平坦化処理された第2の剥離層上に第3の無機絶縁膜をスパッタリング法により形成し、

前記第3の無機絶縁膜上に第2の半導体素子層を形成し、

前記第2の半導体素子層に第1の保持基板を接着し、

前記第2の剥離層において、前記第3の無機絶縁膜及び前記第2の半導体素子層を前記第2の基板より剥離し、

前記剥離により前記第3の無機絶縁膜に残存した前記第2の剥離層を除去することにより、前記第3の無機絶縁膜を露出し、

前記平坦化処理された第2の無機絶縁膜と、前記露出された第3の無機絶縁膜とを接合することにより、前記第2の無機絶縁膜及び前記第3の無機絶縁膜を介して前記第1の半導体素子層と前記第2の半導体素子層とを積層し、

前記第1の保持基板を前記第2の半導体素子層より剥離し、

10

20

前記第2の無機絶縁膜及び前記第3の無機絶縁膜を貫通するコンタクトホールを形成し、

前記コンタクトホールに配線層を形成することにより、前記第1の半導体素子層に設けられた第1のトランジスタと前記第2の半導体素子層に設けられた第2のトランジスタとを電気的に接続し、

前記第2の半導体素子層及び前記配線層上に樹脂層を形成し、

前記樹脂層上に第2の保持基板を接着することを特徴とする半導体装置の作製方法。

**【請求項2】**

第1の基板上に第1の剥離層をスパッタリング法により形成し、

前記第1の剥離層を逆スパッタリング法により平坦化処理し、

前記平坦化処理された第1の剥離層上に第1の無機絶縁膜をスパッタリング法により形成し、

前記第1の無機絶縁膜上に第1の半導体素子層を形成し、

前記第1の半導体素子層上に第2の無機絶縁膜を形成し、

前記第2の無機絶縁膜を平坦化処理し、

第2の基板上に第2の剥離層をスパッタリング法により形成し、

前記第2の剥離層を逆スパッタリング法により平坦化処理し、

前記平坦化処理された第2の剥離層上に第3の無機絶縁膜をスパッタリング法により形成し、

前記第3の無機絶縁膜上に第2の半導体素子層を形成し、

前記第2の半導体素子層に第1の保持基板を接着し、

前記第2の剥離層において、前記第3の無機絶縁膜及び前記第2の半導体素子層を前記第2の基板より剥離し、

前記剥離により前記第3の無機絶縁膜に残存した前記第2の剥離層を除去することにより、前記第3の無機絶縁膜を露出し、

前記平坦化処理された第2の無機絶縁膜と、前記露出された第3の無機絶縁膜とを接合することにより、前記第2の無機絶縁膜及び前記第3の無機絶縁膜を介して前記第1の半導体素子層と前記第2の半導体素子層とを積層し、

前記第1の保持基板を前記第2の半導体素子層より剥離し、

前記第2の無機絶縁膜及び前記第3の無機絶縁膜を貫通するコンタクトホールを形成し、

前記コンタクトホールに配線層を形成することにより、前記第1の半導体素子層に設けられた第1のトランジスタと前記第2の半導体素子層に設けられた第2のトランジスタとを電気的に接続し、

前記第2の半導体素子層及び前記配線層上に樹脂層を形成し、

前記樹脂層上に第2の保持基板を接着し、

前記第1の剥離層において、前記第1の基板を前記第1の無機絶縁膜より剥離することを特徴とする半導体装置の作製方法。

**【請求項3】**

請求項1または請求項2において、

前記平坦化処理された第2の無機絶縁膜及び前記露出された第3の無機絶縁膜の双方にプラズマ処理を行った後、前記平坦化処理された第2の無機絶縁膜と、前記露出された第3の無機絶縁膜とを接合することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、多層構造を有する半導体装置の作製方法に関する。

**【背景技術】**

**【0002】**

半導体装置の技術分野では、より微細化及び高集積化により、高性能化、低消費電力化を

10

20

30

40

50

図られてきた。半導体集積回路の集積度を向上させるため、集積回路（半導体素子層）を多層構造とした多層集積回路が提案されている。

#### 【0003】

このような多層集積回路の作製例としては、基板上に設けられた第1の半導体素子層上に有機材料の層間絶縁物を形成し、層間絶縁物上に第2の半導体素子層を積層して形成する方法が報告されている（例えば、特許文献1参照。）。

#### 【0004】

また、他の多層集積回路の作製例としては、別基板上にそれぞれ形成された第1の半導体素子層と第2の半導体素子層とを素子層同士が接するように、エポキシ樹脂によって接着し、多層構造とする方法が報告されている（例えば、特許文献2参照。）。

10

#### 【0005】

【特許文献1】特開平5-335482号公報

【特許文献2】特開2001-189419号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0006】

しかし、上記のように半導体素子層間に有機材料の層間絶縁物や樹脂などの接着層を設けると半導体装置が厚く、大型化してしまう。また半導体素子層間の電気的接続も難しくなるといった問題がある。

#### 【0007】

従って、より高集積化され、薄型化及び小型化された半導体装置を作製することを目的の一とする。また、半導体装置において、高性能化、低消費電力化を目的の一とする。

20

#### 【課題を解決するための手段】

#### 【0008】

半導体素子を含む層（以下、半導体素子層という）を複数積層し、多層構造を有する半導体装置を作製する。半導体素子層は、剥離層及び下地膜である無機絶縁膜が設けられた基板（以下、半導体素子を作製する基板であるので作製基板ともいう）上に形成され、剥離層を用いて作製基板より他の基板（一時的に半導体素子層を保持するために保持基板ともいう）側に剥離される。上層の半導体素子層となる半導体素子層を作製基板より剥離後、半導体素子層側に残存する剥離層を除去し、半導体素子層の下地膜として機能する無機絶縁膜を露出する。露出した無機絶縁膜に平坦化処理を行ってもよい。

30

#### 【0009】

一方、下層の半導体素子層となる他の基板に形成された半導体素子層は、半導体素子層上に平坦化された無機絶縁層を形成する。

#### 【0010】

平坦化された無機絶縁膜と無機絶縁層とを密着させることにより接合し、下層の半導体素子層と上層の半導体素子層とを積層する。

#### 【0011】

また、露出した無機絶縁膜及び平坦化された無機絶縁層の少なくともいずれか一方に活性化のためのプラズマ処理を行うことが好ましい。勿論、無機絶縁膜及び平坦化された無機絶縁層両方にプラズマ処理を行ってもよい。

40

#### 【0012】

表面を活性化するプラズマ処理によって、室温乃至400の温度であっても異種材料間の接合を形成することが容易となる。従って低温プロセスで多層構造の半導体装置を作製することができる。また半導体素子層間を接着するために、接着剤などの有機材料を用いず、半導体素子層間を薄膜の無機絶縁層及び無機絶縁膜で接合するため、半導体装置を薄型化、小型化することができる。

#### 【0013】

積層する半導体素子層間に設けられる無機絶縁層が薄膜であるため、単結晶半導体層間に設ける無機絶縁層を貫通して形成される配線層も作製しやすく歩留まりや生産性を高くす

50

ることができる。従って、積層する半導体素子同士の電気的接続において、形状不良による電気的不良などを軽減し、信頼性の高い半導体装置を作製することができる。

#### 【0014】

さらに、異なる機能を持つ複数の回路を設ける半導体装置においては、複数設けられる半導体素子に対して、それぞれ用いられる用途によって要求される電気的特性や機能が様々に異なる。よって、それぞれの必要とされる機能や電気特性を有する半導体素子を作製する必要がある。

#### 【0015】

それぞれの半導体素子の必要とされる機能や電気特性を向上させるためには、半導体素子を構成する薄膜の材料や膜厚などの作製条件を最適化することが好ましい。

10

#### 【0016】

本発明では、それぞれ他基板に別工程によって作製された半導体素子層を積層して集積化するため、他層の半導体素子層の作製条件に影響を受けず、最適化された条件（材料、膜厚及び素子構造）でそれぞれ特性の高い半導体素子層を形成することができる。従って、複数の半導体素子の多層構造を有する半導体装置も高性能化することができる。

#### 【0017】

本発明では、単結晶半導体基板より分離させ転置した単結晶半導体層を用いる。そのため、単結晶半導体基板を選択することによって、トランジスタにおける結晶面方位及びチャネル長方向の結晶軸を制御することができる。

#### 【0018】

トランジスタのチャネルを流れるキャリアにとって最も移動度が高くなる単結晶半導体層の結晶面方位、結晶軸を適用することにより、キャリアの有効質量が減少し、トランジスタの移動度を向上させることができる。よって、トランジスタの高性能化が可能となる。

20

#### 【0019】

平坦化処理としては、研磨処理やエッティング処理を行えばよく、勿論、研磨処理及びエッティング処理を両方行ってもよい。研磨処理としては、化学的機械研磨（Chemical Mechanical Polishing : CMP）法や液体ジェット研磨法を用いることができる。エッティング処理としては、ウェットエッティング、ドライエッティング、またはその両方を適宜用いることができる。プラズマ処理によって平坦化処理を行ってもよい。例えば、逆スパッタリング法を用いることができる。

30

#### 【0020】

また、基板上に剥離層を形成後、無機絶縁膜を成膜する前に、剥離層に平坦化処理を行ってもよい。平坦化処理を行った剥離層上に無機絶縁膜を形成すると、剥離層を除去することによって露出する無機絶縁膜の接合面の平坦性を高くすることができる。

#### 【0021】

本明細書において、転置（転載ともいう）とはある基板に形成された半導体素子層を、該基板より剥離し、他の基板に移しかえることをいう。つまり半導体素子層を設ける場所を他の基板へ移動するとも言える。

#### 【0022】

ゲート絶縁層、絶縁層、絶縁膜などを間に挟んで積層する下層の単結晶半導体層と上層の単結晶半導体層とは、該ゲート絶縁層、無機絶縁層、及び無機絶縁膜を貫通する配線層によって電気的に接続する。下層の単結晶半導体層と上層の単結晶半導体層とが重なって積層される場合、配線層は上層の単結晶半導体層を貫通して下層の単結晶半導体層と接して形成されてもよい。積層する単結晶半導体層が重なり合うように密に積層されると、より高集積化された半導体装置とすることができます。

40

#### 【0023】

半導体素子を積層構造とすることができますため、より高集積化された半導体装置とすることができます。高集積化することによって回路面積が縮小し、配線容量が減少するため低消費電力化を図ることができます。

#### 【0024】

50

下層の半導体素子上に形成される上層の半導体素子の形成において、下層の半導体素子を覆う層間絶縁層を形成し、層間絶縁層上に単結晶半導体層と接合する絶縁層を形成する。よって上層の半導体素子の単結晶半導体層と絶縁層との接合を容易に行うことができ、半導体装置の信頼性を向上させることができ、歩留まりも良くなる。

#### 【0025】

本発明の半導体装置の作製方法の一形態は、第1の基板上に第1の剥離層を形成し、前記第1の剥離層を平坦化処理し、前記平坦化処理された第1の剥離層上に第1の無機絶縁膜を形成し、前記第1の無機絶縁膜上に第1の半導体素子層を形成する。前記第1の半導体素子層上に無機絶縁層を形成し、前記無機絶縁層を平坦化処理する。第2の基板上に第2の剥離層を形成し、前記第2の剥離層を平坦化処理し、前記平坦化処理された第2の剥離層上に第2の無機絶縁膜を形成し、前記第2の無機絶縁膜上に第2の半導体素子層を形成する。前記第2の半導体素子層に保持基板を接着し、前記第2の半導体素子層、及び前記第2の無機絶縁膜を第2の基板より剥離する。前記第2の無機絶縁膜に残存する前記第2の剥離層を除去し前記第2の無機絶縁膜を露出する。前記平坦化処理された無機絶縁層と前記露出された第2の無機絶縁膜とを接合して、前記第1の半導体素子層と前記第2の半導体素子層とを前記無機絶縁層及び前記第2の無機絶縁膜を介して積層する。前記第1の半導体素子層及び前記第2の半導体素子層は単結晶半導体層を含み、単結晶半導体基板に脆弱化層を形成し、前記単結晶半導体基板を前記脆弱化層で分離して、前記単結晶半導体層を前記第1の無機絶縁膜及び前記第2の無機絶縁膜上に形成する。

#### 【0026】

また、本発明の半導体装置の作製方法の他の一形態は、第1の半導体素子層と第2の半導体素子層とを無機絶縁層及び第2の無機絶縁膜を介して積層した後、保持基板を第2の半導体素子層より剥離する。次に無機絶縁層及び第2の無機絶縁膜を貫通し積層された第1の半導体素子層及び第2の半導体素子層を電気的に接続する配線層を形成する。

#### 【0027】

また、本発明の半導体装置の作製方法の他の一形態は、無機絶縁層及び第2の無機絶縁膜を貫通し積層された第1の半導体素子層及び第2の半導体素子層を電気的に接続する配線層を形成した後、第2の半導体素子層及び配線層上に樹脂層を形成する。次に、樹脂層に第2の保持基板を接着し、第1の基板より第2の保持基板側に第1の無機絶縁膜を剥離する。

#### 【0028】

なお、本発明において、半導体装置とは、半導体特性を利用することで機能しうる装置を指す。本発明を用いて半導体素子（トランジスタ、メモリ素子やダイオードなど）を含む回路を有する装置や、プロセッサ回路を有するチップなどの半導体装置を作製することができる。

#### 【発明の効果】

#### 【0029】

低温プロセスで多層構造の半導体装置を作製することができる。また半導体素子層間を接着するために、接着剤などの有機材料を用いず、半導体素子層間を薄膜の無機絶縁層及び無機絶縁膜で接合するため、半導体装置を薄型化、小型化することができる。

#### 【0030】

積層する半導体素子層間に設けられる無機絶縁層が薄膜であるため、単結晶半導体層間に設ける無機絶縁層を貫通して形成される配線層も作製しやすく歩留まりや生産性を高くすることができる。従って、積層する半導体素子同士の電気的接続において、形状不良による電気的不良などを軽減し、信頼性の高い半導体装置を作製することができる。

#### 【0031】

また、それぞれ他基板に別工程によって作製された半導体素子層を積層して集積化するため、他層の半導体素子層の作製条件に影響を受けず、最適化された条件（材料、膜厚及び素子構造）でそれぞれ特性の高い半導体素子層を形成することができる。従って、複数の半導体素子の多層構造を有する半導体装置も高性能化することができる。

10

20

30

40

50

**【発明を実施するための最良の形態】**

**【0032】**

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

**【0033】**

(実施の形態1)

10

本実施の形態では、より高集積化、薄型化、及び小型化を付与することを目的とした半導体装置、及び半導体装置の作製方法を、図1乃至図4、及び図10を用いて詳細に説明する。

**【0034】**

本実施の形態では、半導体装置の一例としてCMOS(相補型金属酸化物半導体：Complementary Metal Oxide Semiconductor)について説明する。

**【0035】**

本実施の形態における半導体装置は半導体素子層の積層による多層構造である。半導体素子層は作製時の基板より剥離され、他の半導体素子層上に絶縁層同士の接合によって積層される。なお、本明細書では半導体素子層が作製される基板を作製基板ともいう。従って、半導体素子層は作製基板に剥離層を介して形成される。本実施の形態では、2層の積層構造を有する半導体装置を例に示す。積層する上層及び下層の半導体素子層は積層構造を貫通する配線層によって電気的に接続する。

20

**【0036】**

本実施の形態では、単結晶半導体基板より分離され、作製基板上に接合された単結晶半導体層を有する半導体素子を半導体素子層に用いる。

**【0037】**

まず、絶縁表面を有する基板である作製基板上に、単結晶半導体基板より単結晶半導体層を設ける方法を図18乃至図21を用いて説明する。

30

**【0038】**

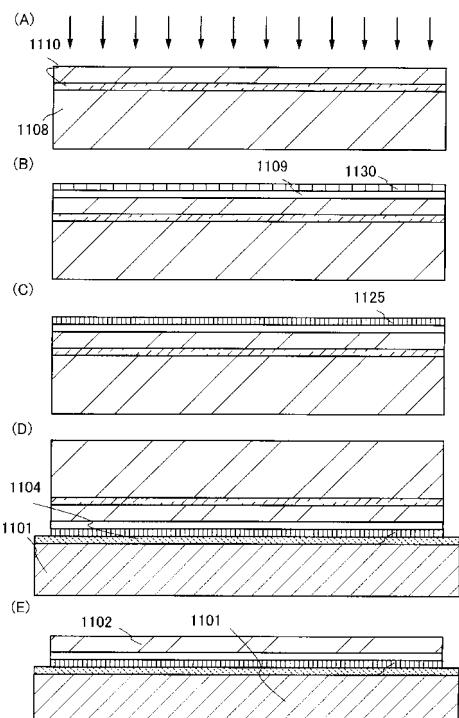

図20(A)に示す単結晶半導体基板1108は清浄化されており、その表面から電界で加速されたイオンを所定の深さに添加し、脆弱化層1110を形成する。イオンの添加は作製基板に転置する単結晶半導体層の厚さを考慮して行われる。イオンを添加する際の加速電圧はこのような厚さを考慮して、単結晶半導体基板1108に添加されるようにする。本発明では、単結晶半導体基板へイオンを添加し、イオンにより微小な空洞を有するよう脆弱化された領域を脆弱化層という。

**【0039】**

単結晶半導体基板1108には、市販の単結晶半導体基板を用いることができ、例えば、単結晶シリコン基板、単結晶ゲルマニウム基板、単結晶シリコンゲルマニウム基板など、第4族元素でなる単結晶半導体基板を用いることができる。また、ガリウムヒ素やインジウムリン等の化合物半導体基板も用いることができる。半導体基板として多結晶半導体基板を用いてもよい。もちろん、単結晶半導体基板は、円形のウエハに限定されるものではなく、様々な形状の単結晶半導体基板を用いることができる。例えば、円形、長方形、五角形、六角形などの多角形の基板を用いることができる。もちろん、市販の円形状の単結晶半導体ウエハを単結晶半導体基板に用いることも可能である。円形状の単結晶半導体ウエハには、シリコンやゲルマニウムなどの半導体ウエハ、ガリウムヒ素やインジウムリンなどの化合物半導体ウエハなどがある。単結晶半導体ウエハの代表例は、単結晶シリコンウエハであり、直径5インチ(125mm)、直径6インチ(150mm)、直径8インチ(200mm)、直径12インチ(300mm)サイズ、直径400mm、直径450

40

50

mmの円形のウエハを用いることができる。また、長方形の単結晶半導体基板は、市販の円形状の単結晶半導体ウエハを切断することで形成することができる。基板の切断には、ダイサー或いはワイヤソー等の切断装置、レーザ切断、プラズマ切断、電子ビーム切断、その他任意の切断手段を用いることができる。また、基板として薄片化する前の半導体基板製造用のインゴットを、その断面が長方形になるように直方体状に加工し、この直方体状のインゴットを薄片化することでも、長方形形状の単結晶半導体基板を製造することができる。また、単結晶半導体基板の厚さは特に限定されないが、単結晶半導体基板を再利用することを考慮すれば、厚い方が1枚の原料ウエハからより多くの単結晶半導体層を形成することができるため、好ましい。市場に流通している単結晶シリコンウエハの厚さは、そのサイズはSEMI規格に準じており、例えば直径6インチのウエハは膜厚625μm、直径8インチのウエハは膜厚725μm、直径12インチのウエハは775μmとされている。なお、SEMI規格のウエハの厚さは公差±25μmを含んでいる。もちろん、原料となる単結晶半導体基板の厚さはSEMI規格に限定されず、インゴットをスライスするときに、その厚さを適宜調節することができる。もちろん、再利用された単結晶半導体基板1108を用いるときには、その厚さは、SEMI規格よりも薄くなる。作製基板上に得られる単結晶半導体層は母体となる半導体基板を選択することによって決定することができる。

#### 【0040】

また、単結晶半導体基板1108は、作製する半導体素子（本実施の形態においては電界効果トランジスタ）によって、結晶面方位を選択すればよい。例えば、結晶面方位として{100}面、{110}面など有する単結晶半導体基板を用いることができる。

#### 【0041】

本実施の形態は、単結晶半導体基板の所定の深さに水素、ヘリウム、又はフッ素をイオン添加し、その後熱処理を行って表層の単結晶半導体層を剥離するイオン添加剥離法で形成するが、ポーラスシリコン上に単結晶シリコンをエピタキシャル成長させた後、ポーラスシリコン層をウォータージェットで劈開して剥離する方法を適用しても良い。

#### 【0042】

単結晶半導体基板1108として単結晶シリコン基板を用い、希フッ酸で表面を処理し、自然酸化膜の除去と表面に付着するゴミ等の汚染物も除去して単結晶半導体基板1108表面を清浄化する。

#### 【0043】

脆弱化層1110は、イオンをイオンドーピング法（ID法と略記する）やイオン注入法（II法と略記する）によって添加（導入）すればよい。脆弱化層1110は水素、ヘリウム若しくはフッ素に代表されるハロゲンのイオンを添加することで形成される。ハロゲン元素としてフッ素イオンを添加する場合にはソースガスとしてBF<sub>3</sub>を用いれば良い。なお、イオン注入とはイオン化したガスを質量分離して半導体に添加する方式をいう。

#### 【0044】

例えば、イオン注入法を用いて、イオン化した水素ガスを質量分離し、H<sup>+</sup>のみ、（又はH<sub>2</sub><sup>+</sup>のみ）を選択的に加速して添加することができる。

#### 【0045】

イオンドープ法は、イオン化したガスを質量分離せずに、プラズマ中で複数種のイオン種を作り、それらを加速して単結晶半導体基板にドープする。例えば、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含む水素では、ドープされるイオンは、代表的にH<sub>3</sub><sup>+</sup>イオンが50%以上、例えばH<sub>3</sub><sup>+</sup>イオンが80%、他のイオン（H<sup>+</sup>、H<sub>2</sub><sup>+</sup>イオン）が20%、が一般的である。H<sub>3</sub><sup>+</sup>イオンのイオン種のみとして添加することもここではイオンドープとする。

#### 【0046】

また、一又は複数の同一の原子から成る質量の異なるイオンを添加してもよい。例えば、水素イオンを添加する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくことが好ましい。水素イオンを添加する場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくと添加効率を高め

10

20

30

40

50

ることができ、添加時間を短縮することができる。このような構成とすることで、剥離を容易に行うことができる。

#### 【0047】

以下、イオンドーピング法とイオン注入法について詳細に説明する。イオンドーピング法に用いるイオンドーピング装置（ID装置ともいう）では、プラズマ空間が大きく、大量のイオンを単結晶半導体基板に添加することができる。一方、イオン注入法に用いるイオン注入装置（II装置ともいう）は、プラズマから取り出したイオンを質量分析して特定のイオン種だけを半導体基板に打ち込めるという特徴があり、基本的に点ピ-ムをスキャンさせて処理する。

#### 【0048】

10

プラズマ発生方法としては、どちらの装置も、例えば、フィラメントを熱して出てくる熱電子によりプラズマ状態を作っている。しかし、生成される水素イオン（H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>）が半導体基板に添加される（打ち込まれる）際の水素イオン種の割合は、イオンドーピング法とイオン注入法で大きく異なる。

#### 【0049】

H<sub>3</sub><sup>+</sup>をより多く打ち込むという観点からすれば、イオン注入装置よりイオンドーピング装置を用いる方が好ましいといえる。

#### 【0050】

单結晶シリコン基板に水素イオンやフッ素イオンのようなハロゲンイオンを添加した場合、添加されたフッ素が、シリコン結晶格子内のシリコン原子をノックアウトする（追い出す）ことによって空白部分を効果的に作り出し、脆弱化層に微小な空洞を作る。この場合、比較的低温の熱処理によって脆弱化層に形成された微小な空洞の体積変化が起こり、脆弱化層に沿って劈開することにより薄い单結晶半導体層を形成することができる。フッ素イオンを添加した後に、水素イオンを添加して空洞内に水素を含ませるようにも良い。单結晶半導体基板から薄い单結晶半導体層を剥離するために形成する脆弱化層は、脆弱化層に形成された微小な空洞の体積変化を利用して劈開をするので、このようにフッ素イオンや水素イオンの作用を有効利用することが好ましい。

#### 【0051】

また、单結晶半導体基板と上記单結晶半導体層と接合する無機絶縁膜（又は絶縁層）との間に、保護層を形成してもよい。保護層は、窒化シリコン層、酸化シリコン層、窒化酸化シリコン層、又は酸化窒化シリコン層から選ばれた一層又は複数の層による積層構造により形成することができる。これらの層は、单結晶半導体基板に脆弱化層が形成される前に单結晶半導体基板上に形成することができる。また、单結晶半導体基板に脆弱化層を形成した後に单結晶半導体基板上に形成してもよい。

#### 【0052】

脆弱化層の形成に当たってはイオンを高ドーズ条件で添加する必要があり、单結晶半導体基板1108の表面が粗くなってしまう場合がある。そのためイオンが添加される表面に窒化シリコン膜、窒化酸化シリコン膜、若しくは酸化シリコン膜などによりイオン添加に対する保護層を50nm乃至200nmの厚さで設けておいても良い。

#### 【0053】

40

例えば、单結晶半導体基板1108上に保護層としてプラズマCVD法により酸化窒化シリコン膜（膜厚5nm～300nm、望ましくは30nm～150nm（例えば50nm））と窒化酸化シリコン膜（膜厚5nm～150nm、望ましくは10nm～100nm（例えば50nm））の積層を形成する。一例としては、单結晶半導体基板1108上に酸化窒化シリコン膜を膜厚50nm形成し、該酸化窒化シリコン膜上に窒化酸化シリコン膜を膜厚50nm形成し、積層する。酸化窒化シリコン膜は有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜でもよい。

#### 【0054】

また、单結晶半導体基板1108を脱脂洗浄し、表面の酸化膜を除去して熱酸化を行ってもよい。熱酸化としては通常のドライ酸化でも良いが、酸化雰囲気中にハロゲンを添加し

10

20

30

40

50

た酸化を行うことが好ましい。例えば、酸素に対し H C l を 0 . 5 ~ 1 0 体積 % ( 好ましくは 3 体積 % ) の割合で含む雰囲気中で、 7 0 0 以上 の温度で熱処理を行う。好適には 9 5 0 ~ 1 1 0 0 の温度で熱酸化を行うと良い。処理時間は 0 . 1 ~ 6 時間、好ましくは 0 . 5 ~ 3 . 5 時間とすれば良い。形成される酸化膜の膜厚としては、 1 0 n m ~ 1 0 0 0 n m ( 好ましくは 5 0 n m ~ 2 0 0 n m ) 、例えば 1 0 0 n m の厚さとする。

#### 【 0 0 5 5 】

ハロゲンを含むものとしては H C l の他に、 H F 、 N F 3 、 H B r 、 C l 2 、 C l F 3 、 B C l 3 、 F 2 、 B r 2 などから選ばれた一種又は複数種を適用することができる。

#### 【 0 0 5 6 】

このような温度範囲で熱処理を行うことで、ハロゲン元素によるゲッタリング効果を得ることができる。ゲッタリングとしては、特に金属不純物を除去する効果がある。すなわち、塩素の作用により、金属などの不純物が揮発性の塩化物となって気相中へ離脱して除去される。単結晶半導体基板 1 1 0 8 の表面を化学的機械研磨 ( C M P ) 処理をしたものに対しては有効である。また、水素は単結晶半導体基板 1 1 0 8 と形成される無機絶縁膜 ( 又は絶縁層 ) の界面の欠陥を補償して界面の局在準位密度を低減する作用を奏し、単結晶半導体基板 1 1 0 8 と無機絶縁膜 ( 又は絶縁層 ) の界面が不活性化されて電気的特性が安定化する。

10

#### 【 0 0 5 7 】

この熱処理により形成される酸化膜中にハロゲンを含ませることができる。ハロゲン元素は  $1 \times 1 0 ^{17} / \text{cm}^3$  ~  $5 \times 1 0 ^{20} / \text{cm}^3$  の濃度で含まれることにより金属などの不純物を捕獲して単結晶半導体基板 1 1 0 8 の汚染を防止する保護層としての機能を発現させることができる。

20

#### 【 0 0 5 8 】

脆弱化層 1 1 1 0 を形成する際、加速電圧と全イオン数は、単結晶半導体基板上に堆積した膜の厚さと、目的とする単結晶半導体基板より分離して作製基板上に転置される単結晶半導体層の膜厚と、添加するイオン種によって調整することができる。

#### 【 0 0 5 9 】

例えば、イオンドーピング法で原料として水素ガスを用い、加速電圧を 4 0 k V 、全イオン数  $2 \times 1 0 ^{16} \text{ ions} / \text{cm}^2$  でイオンを添加して脆弱化層を形成することができる。保護層の膜厚を厚くすれば、同一条件でイオンを添加し脆弱化層を形成した場合、目的とする単結晶半導体基板より分離して作製基板上に転置 ( 転載 ) される単結晶半導体層として、膜厚の薄い単結晶半導体層を形成することができる。例えば、イオン種 ( H + 、 H 2 + 、 H 3 + イオン ) の割合にもよるが、上記条件で脆弱化層を形成するとし、保護層として単結晶半導体基板上に酸化窒化シリコン膜 ( 膜厚 5 0 n m ) と窒化酸化シリコン膜 ( 膜厚 5 0 n m ) を保護層として積層する場合、作製基板に転置される単結晶半導体層の膜厚は約 1 2 0 n m となり、単結晶半導体基板上に酸化窒化シリコン膜 ( 膜厚 1 0 0 n m ) と窒化酸化シリコン膜 ( 膜厚 5 0 n m ) を保護層として積層する場合は、作製基板に転置される単結晶半導体層の膜厚は約 7 0 n m となる。

30

#### 【 0 0 6 0 】

ヘリウム ( H e ) や水素を原料ガスにする場合、加速電圧を 1 0 k V ~ 2 0 0 k V の範囲で、ドーズ量を  $1 \times 1 0 ^{16} \text{ ions} / \text{cm}^2$  ~  $6 \times 1 0 ^{16} \text{ ions} / \text{cm}^2$  の範囲で添加し脆弱化層を形成することができる。ヘリウムを原料ガスにすると、質量分離を行わなくても H e + イオンを主なイオンとして添加することができる。また、水素を原料ガスとすると H 3 + イオンや H 2 + イオンを主なイオンとして添加することができる。イオン種は、プラズマの生成方法、圧力、原料ガス供給量、加速電圧によっても変化する。

40

#### 【 0 0 6 1 】

脆弱化層形成の例としては、単結晶半導体基板上に酸化窒化シリコン膜 ( 膜厚 5 0 n m ) 、窒化酸化シリコン膜 ( 膜厚 5 0 n m ) 、及び酸化シリコン膜 ( 膜厚 5 0 n m ) を保護層として積層し、水素を加速電圧 4 0 k V 、ドーズ量  $2 \times 1 0 ^{16} \text{ ions} / \text{cm}^2$  で添加し単結晶半導体基板に脆弱化層を形成する。その後保護層の最上層である該酸化シリコン

50

膜上に接合面を有する絶縁層として酸化シリコン膜（膜厚50nm）を形成する。脆弱化層形成の他の例としては、単結晶半導体基板上に酸化シリコン膜（膜厚100nm）、及び窒化酸化シリコン膜（膜厚50nm）を保護層として積層し、水素を加速電圧40kV、ドーザ量 $2 \times 10^{16}$  ions/cm<sup>2</sup>で添加し単結晶半導体基板に脆弱化層を形成する。その後保護層の最上層である該窒化酸化シリコン膜上に接合面を有する絶縁層として酸化シリコン膜（膜厚50nm）を形成する。なお、上記酸化窒化シリコン膜及び窒化酸化シリコン膜はプラズマCVD法により形成すればよく、上記酸化シリコン膜は有機シランガスを用いてCVD法により形成すればよい。

#### 【0062】

また、無機絶縁膜と単結晶半導体基板との間に絶縁層を形成してもよい。絶縁層は無機絶縁膜側、あるいは単結晶半導体基板側どちらか一方でもよいし、両方に形成してもよい。接合を形成する面に形成する絶縁層は平滑面を有し親水性表面を形成する。該絶縁層としては、酸化シリコン膜を用いることができる。酸化シリコン膜としては有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。

#### 【0063】

有機シランガスとしては、珪酸エチル（TEOS：化学式Si(OCH<sub>3</sub>)<sub>4</sub>）、トリメチルシラン（TMS：(CH<sub>3</sub>)<sub>3</sub>SiH）、テトラメチルシラン（化学式Si(CH<sub>3</sub>)<sub>4</sub>）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシラン（SiH(OCH<sub>3</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等のシリコン含有化合物を用いることができる。なお、原料ガスに有機シランを用いて化学気相成長法により酸化シリコン層を形成する場合、酸素を付与するガスを混合させることができ。酸素を付与するガスとしては、酸素、亜酸化窒素、二酸化窒素等を用いることができる。さらに、アルゴン、ヘリウム、窒素又は水素等の不活性ガスを混合させてもよい。

#### 【0064】

また、接合を形成する面に形成する絶縁層として、モノシラン、ジシラン、又はトリシラン等のシランを原料ガスに用いて化学気相成長法により形成される酸化シリコン膜を適用することもできる。この場合も、酸素を付与するガスや不活性ガス等を混合させることができ。また、単結晶半導体層と接合する絶縁層となる酸化シリコン膜は、塩素を含んでいてもよい。なお、本明細書において、化学気相成長（CVD；Chemical Vapour Deposition）法は、プラズマCVD法、熱CVD法、光CVD法を範疇に含む。

#### 【0065】

その他、接合を形成する面に形成する絶縁層として、酸化性雰囲気下において熱処理することにより形成される酸化シリコン、酸素ラジカルの反応により成長する酸化シリコン、酸化性の薬液により形成されるケミカルオキサイドなどを適用することもできる。絶縁層として、シロキサン（Si-O-Si）結合を含む絶縁層を適用してもよい。また、前記有機シランガスと、酸素ラジカル又は窒素ラジカルとを反応させて絶縁層を形成してもよい。

#### 【0066】

無機絶縁膜、絶縁層において、接合を形成する面の表面は、算術平均粗さRaが0.8nm未満、二乗平均平方根粗さRmsが0.9nm未満が望ましく、Raが0.4nm以下、Rmsが0.5nm以下がより望ましく、さらにはRaが0.3nm以下、Rmsが0.4nm以下がより望ましい。例えば、Raが0.27nm、Rmsが0.34nmである。本明細書においてRaは算術平均粗さであり、Rmsは二乗平均平方根粗さであり、測定範囲は2μm<sup>2</sup>、又は10μm<sup>2</sup>である。

#### 【0067】

無機絶縁膜と単結晶半導体基板とを接合するに際し、接合を形成する面の一方若しくは双

10

20

30

40

50

方に、好ましくは有機シランを原材料として成膜した酸化シリコン膜でなる絶縁層を設けると強固な接合を形成することができる。

#### 【0068】

本実施の形態では、図20(B)で示すように無機絶縁膜と接合を形成する面に絶縁層1104として酸化シリコン膜を形成する。酸化シリコン膜としては有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。化学気相成長法による成膜では、単結晶半導体基板に形成した脆弱化層1110から脱ガスが起こらない温度として、例えば350℃以下(具体的な例としては300℃)の成膜温度が適用される。また、単結晶半導体基板から単結晶半導体層を剥離する熱処理は、成膜温度よりも高い熱処理温度が適用される。10

#### 【0069】

本実施の形態では、作製基板上で半導体素子層を形成後、半導体素子層を作製基板より剥離するため、作製基板と半導体素子層との間に剥離層を設ける。よって単結晶半導体基板より分離して接合される単結晶半導体層は、作製基板上に設けられた剥離層及び無機絶縁膜上に形成される。剥離層表面に凹凸を有すると、単結晶半導体基板と作製基板との接合工程において、接合面の接触面積が小さくなり、十分な接合強度を確保することが困難である。そのため、剥離層を平坦化する工程が必要である。

#### 【0070】

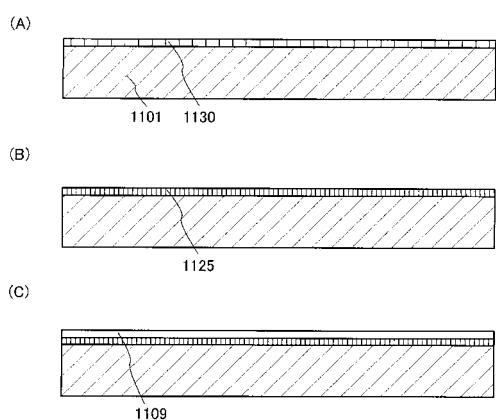

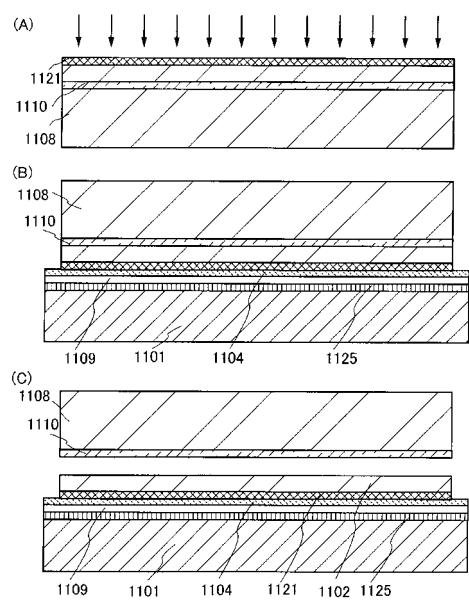

図18(A)において作製基板1101上に剥離層1130が形成されている。剥離層1130に平坦化処理を行うことによって表面が平坦化された剥離層1125を形成する(図18(B)参照。)。平坦化された剥離層1125上に無機絶縁膜1109を形成すると、無機絶縁膜1109表面も平坦性を高くすることができる(図18(C)参照。)20

#### 【0071】

平坦化処理としては、研磨処理やエッティング処理を行えばよく、勿論、研磨処理及びエッティング処理を両方行ってもよい。研磨処理としては、化学的機械研磨(CMP)法や液体ジェット研磨法を用いることができる。エッティング処理としては、ウェットエッティング、ドライエッティング、またはその両方を適宜用いることができる。

#### 【0072】

またプラズマ処理によって平坦化処理を行ってもよい。例えば、逆スパッタリング法を用いることができる。逆スパッタリング法にて平坦化処理を行うと、無機絶縁膜や無機絶縁層の形成から平坦化までを同一装置内にて行うことができるため、スループットが向上し、好ましい。30

#### 【0073】

逆スパッタリング法は、例えば、高真空のチャンバーに不活性ガス、例えばArガスを導入し、被処理面に対して電界をかけることでプラズマ状態として行う。プラズマ中には電子とArの陽イオンが存在し、陰極方向にArの陽イオンが加速される。加速されたArの陽イオンは被処理面をスパッタする。このとき、該被処理面の凸部から優先的にスパッタされる。被処理面からスパッタされた粒子は、被処理面の別の場所に付着する。このとき、該被処理面の凹部に優先的に付着する。このように凸部を削り、凹部を埋めることで被処理面の平坦性が向上すると考えられる。40

#### 【0074】

本実施の形態では、剥離層をスパッタリング法で形成し、逆スパッタリング法によって平坦化処理を行う。

#### 【0075】

作製基板には、剥離層との間に不純物元素の拡散を防止する窒化シリコン膜又は窒化酸化シリコン膜をブロッキング層(バリア層ともいう)として設けてもよい。さらに応力を緩和する作用のある絶縁膜として酸化窒化シリコン膜を組み合わせても良い。

#### 【0076】

図20(C)は作製基板1101上に設けられた無機絶縁膜1109と単結晶半導体基板50

1108の絶縁層1104が形成された面とを密接させ、この両者を接合させる態様を示す。無機絶縁膜1109表面は平坦化された剥離層1125上に設けられているために表面は高い平坦性を有している。接合を形成する面は、十分に清浄化しておく。作製基板1101上に設けられた無機絶縁膜1109と単結晶半導体基板1108の絶縁層1104が形成された面は、メガソニック洗浄などによって清浄化すればよい。また、メガソニック洗浄後にオゾン水で洗浄し、有機物の除去と表面の親水性向上を行ってもよい。

#### 【0077】

作製基板1101上の無機絶縁膜1109と絶縁層1104とを対向させて、一箇所を外部から押しつけると、局所的に接合面同士の距離が縮まる事によるファン・デル・ワールス力の強まりや水素結合の寄与によって、お互いに引きつけ合う。更に、隣接した領域でも対向する作製基板1101上の無機絶縁膜1109と絶縁層1104との間の距離が縮まるので、ファン・デル・ワールス力が強く作用する領域や水素結合が関与する領域が広がる事によって、接合（ボンディングともいう）が進行し接合面全域に接合が広がる。例えば、押しつける圧力は、100kPa～5000kPa程度とすればよい。また、支持基板と半導体基板とを重ねるように配置し、重ねる基板の重みでも接合を広げることもできる。

10

#### 【0078】

良好な接合を形成するために、表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。このような表面処理により200乃至400の温度であっても異種材料間の接合を形成することが容易となる。

20

#### 【0079】

また、作製基板と絶縁層との接合界面の接合強度を向上させるために、加熱処理を行うと好ましい。例えば、オーブンや炉などで70～350（例えば200で2時間）の温度条件で熱処理を行う。

#### 【0080】

図20(D)において、作製基板1101と単結晶半導体基板1108を貼り合わせた後、加熱処理を行い脆弱化層1110を劈開面として単結晶半導体基板1108を作製基板1101から剥離する。例えば、400～700の熱処理を行うことにより、脆弱化層1110に形成された微小な空洞の体積変化が起こり、脆弱化層1110に沿って劈開することが可能となる。絶縁層1104は無機絶縁膜1109を介して作製基板1101と接合しているので、作製基板1101上には単結晶半導体基板1108と同じ結晶性の単結晶半導体層1102が残存することとなる。

30

#### 【0081】

400～700の温度域での熱処理は、前述の接合強度を向上させるための熱処理と同じ装置で連続して行ってもよいし、別の装置で行ってもよい。例えば炉で2002時間熱処理した後に、600近傍まで昇温し2時間保持し、400から室温までの温度域に降温した後炉より取り出す。また、熱処理は室温から昇温してもよい。また、炉で2002時間熱処理した後に、瞬間熱アニール(RTA)装置によって600～700の温度域で、1分間～30分間（例えば6007分間、6507分間）熱処理を行ってもよい。

40

#### 【0082】

400～700の温度域での熱処理により、絶縁層と作製基板との接合は水素結合から共有結合に移行し、脆弱化層に添加された元素が析出し圧力が上昇し、単結晶半導体基板より単結晶半導体層を剥離することができる。熱処理を行った後は作製基板と単結晶半導体基板は、一方が他方に載っている状態であり、大きな力を加えずに作製基板と単結晶半導体基板を離すことができる。例えば、上方に載っている基板を真空チャックで持ち上げることにより簡単に離すことができる。この際、下側の基板の真空チャックやメカニカ

50

ルチャックで固定しておくと水平方向のずれがなく作製基板及び単結晶半導体基板の両基板を離すことができる。

#### 【0083】

なお、図20、図21においては、単結晶半導体基板1108が作製基板1101より小さいサイズの例を示すが、本発明はそれに限定されず、単結晶半導体基板1108と作製基板1101が同じサイズであってもよいし、単結晶半導体基板1108が作製基板1101より大きいサイズであってもよい。

#### 【0084】

図21は作製基板側に絶縁層を設けて単結晶半導体層を形成する工程を示す。図21(A)は保護層1121として酸化シリコン膜が形成された単結晶半導体基板1108に電界で加速されたイオンを所定の深さに添加し、脆弱化層1110を形成する工程を示している。イオンの添加は図20(A)の場合と同様である。単結晶半導体基板1108の表面に保護層1121を形成しておくことでイオン添加によって表面がダメージを受け、平坦性が損なわれるのを防ぐことができる。また、保護層1121によって、単結晶半導体基板1108から形成される単結晶半導体層1102に対する不純物の拡散防止効果を発現する。

10

#### 【0085】

図21(B)は、無機絶縁膜1109及び絶縁層1104が形成された作製基板1101と単結晶半導体基板1108の保護層1121が形成された面を密着させて接合を形成する工程を示している。作製基板1101上の絶縁層1104と単結晶半導体基板1108の保護層1121を密着させることにより接合が形成される。

20

#### 【0086】

その後、図21(C)で示すように単結晶半導体基板1108を剥離する。単結晶半導体層を剥離する熱処理は図20(D)の場合と同様にして行う。このようにして図21(C)で示す絶縁層を介して単結晶半導体層を有する本発明のSOI構造の半導体基板を得ることができる。

#### 【0087】

また、単結晶半導体基板より分離し、作製基板に転置された単結晶半導体層は、分離工程およびイオン照射工程によって、結晶欠陥が生じ、また、その表面は平坦性が損なわれ、凹凸が形成されてしまう場合がある。単結晶半導体層を用いて半導体素子としてトランジスタを作製する場合、このような凹凸のある単結晶半導体層の上面に薄く、絶縁耐圧性の高いゲート絶縁層を形成することは困難である。また、単結晶半導体層に結晶欠陥があると、ゲート絶縁層との局在界面準位密度が高くなるなど、トランジスタの性能および信頼性に影響を与える。

30

#### 【0088】

従って単結晶半導体層にレーザ光のような電磁波を照射し、結晶欠陥を低減させることができほしい。電磁波を照射することによって、単結晶半導体層の少なくとも一部の領域を溶融させ、単結晶半導体層中の結晶欠陥を低減させることができる。なお、電磁波の照射前に単結晶半導体層表面に形成された酸化膜(自然酸化膜、あるいはケミカル酸化膜)を希フッ酸で除去するとよい。

40

#### 【0089】

電磁波は単結晶半導体層に高いエネルギーを供給できるものであればよく、好適にはレーザ光を用いることができる。

#### 【0090】

またエネルギーの供給は、高エネルギーを有する粒子を照射などによって単結晶半導体層に衝突させ、主として熱伝導によって行うこともできる。高エネルギーを有する粒子を提供する熱源としては、プラズマを用いることができる、常圧プラズマ、高圧プラズマ、熱プラズマジェット、ガスバーナーなどの炎を用いることができる、又、他の熱源としては電子ビームなどを用いることができる。

#### 【0091】

50

電磁波の波長は、単結晶半導体層に吸収される波長とする。その波長は、電磁波の表皮深さ(skin depth)などを考慮して決定することができる。例えば、電磁波の波長は190nm～600nmを用いることができる。また、電磁波のエネルギーは、電磁波の波長、電磁波の表皮深さ、照射する単結晶半導体層の膜厚などを考慮して決定することができる。

#### 【0092】

レーザ光を発振するレーザは、連続発振レーザ、疑似連続発振レーザ及びパルス発振レーザを用いることができる。部分溶融させるためパルス発振レーザが好ましい。例えば、KrFレーザなどのエキシマレーザ、Arレーザ、Krレーザなどの気体レーザがある。その他、固体レーザとして、YAGレーザ、YVO<sub>4</sub>レーザ、YLFレーザ、YAlO<sub>3</sub>レーザ、GdVO<sub>4</sub>レーザ、KGWレーザ、KYWレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、Y<sub>2</sub>O<sub>3</sub>レーザなどがある。なお、エキシマレーザはパルス発振レーザであるが、YAGレーザなどの固体レーザには、連続発振レーザにも、疑似連続発振レーザにも、パルス発振レーザにもなるものがある。なお、固体レーザにおいては、基本波の第2高調波～第5高調波を適用するのが好ましい。また、GaN、GaAs、GaAlAs、InGaAsP等の半導体レーザも用いることができる。

#### 【0093】

また、電磁波のエネルギーを単結晶半導体層に照射できるならば、ランプ光を用いてよい。例えば、紫外線ランプ、ブラックライト、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプから射出された光を用いてよい。上記ランプ光を用いたフラッシュアニールを用いてよい。ハロゲンランプやキセノンランプなどを好適に用いて行うフラッシュアニールは極短時間の処理でよいため、作製基板の温度上昇を抑えることができる。

#### 【0094】

電磁波の形状や電磁波の進路を調整するため、シャッター、ミラー又はハーフミラー等の反射体、シリンドリカルレンズや凸レンズなどによって構成される光学系が設置されているよい。

#### 【0095】

なお、電磁波の照射方法は、選択的に電磁波を照射してもよいし、光(電磁波)をXY軸方向に走査して光(電磁波)を照射することができる。この場合、光学系にポリゴンミラーやガルバノミラーを用いることが好ましい。

#### 【0096】

電磁波の照射は、大気雰囲気のような酸素を含む雰囲気、または窒素雰囲気のような不活性雰囲気で行うことができる。不活性雰囲気中で電磁波を照射するには、気密性のあるチャンバー内で電磁波を照射し、このチャンバー内の雰囲気を制御すればよい。チャンバーを用いない場合は、電磁波の被照射面に窒素ガスなど不活性ガスを吹き付けることで、窒素雰囲気を形成することもできる。

#### 【0097】

さらに、電磁波照射などの高エネルギーを供給され、結晶欠陥を低減された単結晶半導体表面に研磨処理を行ってよい。研磨処理によって単結晶半導体層表面の平坦性を高めることができる。

#### 【0098】

研磨処理としては、化学的機械研磨(CMP)法や液体ジェット研磨法を用いることができる。なお、研磨処理前に単結晶半導体層表面を洗浄し、清浄化する。洗浄は、メガソニック洗浄や2流体ジェット洗浄等を用いればよく、洗浄により単結晶半導体層表面のゴミ等を除去する。また、希フッ酸を用いて単結晶半導体層表面上の自然酸化膜等を除去して単結晶半導体層を露出させると好適である。

#### 【0099】

また、電磁波を照射する前にも単結晶半導体層表面に研磨処理(又はエッチング処理)を行ってよい。

10

20

30

40

50

**【0100】**

本実施の形態において、単結晶半導体基板1108として単結晶シリコン基板を適用した場合は、単結晶半導体層1102として単結晶シリコン層を得ることが可能である。また、本実施の形態の半導体装置の製造方法は、プロセス温度を700以下とすることができるため、作製基板1101としてガラス基板を適用することができる。すなわち、従来の薄膜トランジスタと同様にガラス基板上に形成することができ、かつ単結晶シリコン層を半導体層に適用することが可能となる。これらのことにより、高速動作が可能で、サブスレッショルド値が低く、電界効果移動度が高く、低消費電圧で駆動可能など高性能、高信頼性のトランジスタをガラス基板等の作製基板上に作製することができる。

**【0101】**

10

図3及び図4のトランジスタ211、230の含む単結晶半導体層283、284は、単結晶半導体基板より分離されて作製基板200、220に転置された単結晶半導体層である。単結晶半導体層283、284は、図20(D)における単結晶半導体層1102を所望の形状に加工することによって形成することができる。なお、図3、図4、及び図20において、作製基板1101は基板200、220に、剥離層1125は剥離層201、221に、無機絶縁膜1109は無機絶縁膜202、222に、絶縁層1104は絶縁層280、281にそれぞれ対応している。なお、ここでは図20(D)に対応する構成のSOI構造を有する半導体基板を適用する例を示すが、本明細書で示すその他の構成のSOI構造を有する半導体基板も適用できる。

**【0102】**

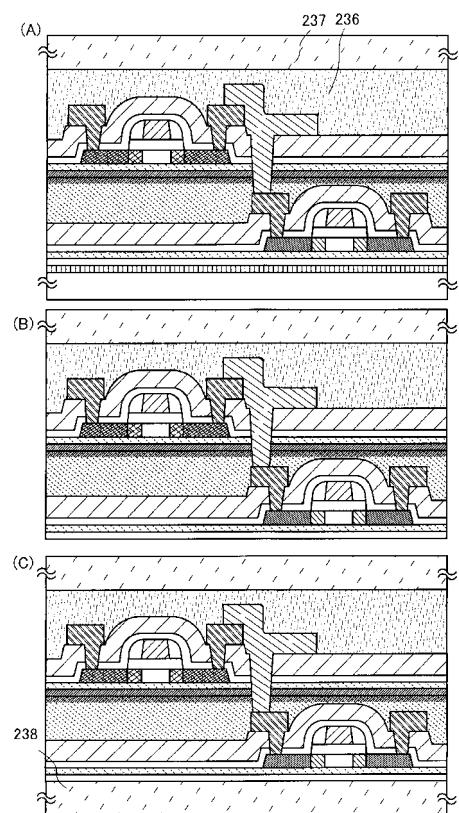

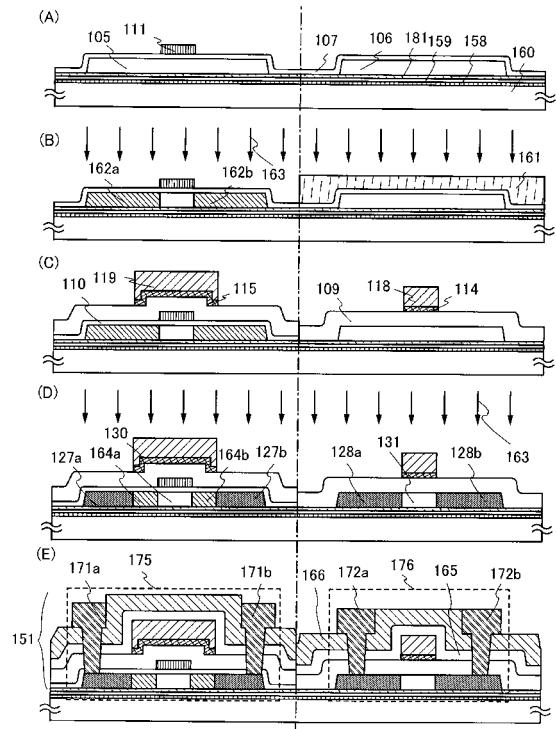

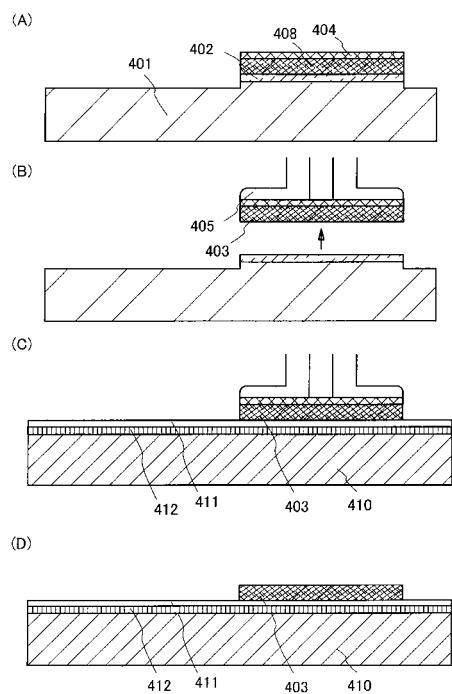

20

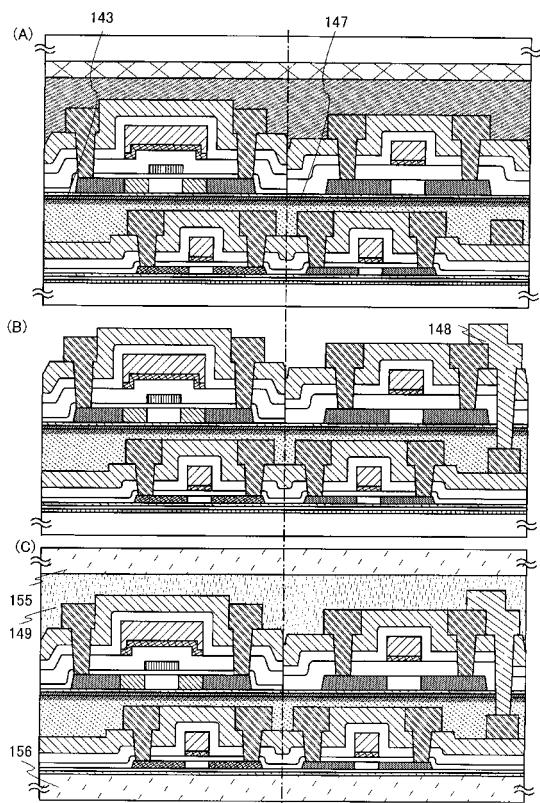

作製基板である絶縁表面を有する基板200上に剥離層201を介して、無機絶縁膜202、絶縁層280、トランジスタ211、絶縁膜212、絶縁膜213が設けられ、半導体素子層250が形成されている。トランジスタ211は薄膜トランジスタであり、ソース領域又はドレイン領域204a、204b、ソース領域又はドレイン領域204a、204bより低濃度不純物領域である不純物領域205a、205b、及びチャネル形成領域206を含む単結晶半導体層283、ゲート絶縁層207、ゲート電極層208、サイドウォール構造の絶縁層209a、209bを含む。ソース領域又はドレイン領域204a、204bはソース電極層又はドレイン電極層として機能する配線層210a、210bと接し、電気的に接続している。本実施の形態では、トランジスタ211はnチャネル型薄膜トランジスタであり、ソース領域又はドレイン領域204a、204b、LDD(Lightly Doped Drain)領域である不純物領域205a、205bにn型を付与する不純物元素(例えばリン(P)やヒ素(As)等)を含む。

**【0103】**

30

半導体素子層250のトランジスタ211等によって生じる凹凸を平坦化するため、無機絶縁層214を形成する(図3(B)参照。)。無機絶縁層214に平坦化処理を行い、平坦化処理された無機絶縁層215を形成する(図3(C)参照。)。

**【0104】**

40

平坦化処理された無機絶縁層215は、他基板で作製された半導体素子層との接合面となるため、本実施の形態では無機絶縁層215に活性化のためのプラズマ処理を行い、表面が改質処理された無機絶縁層216を形成する(図3(D)参照。)。以上の工程で下層となる半導体素子層250の接合前の工程が完了する。

**【0105】**

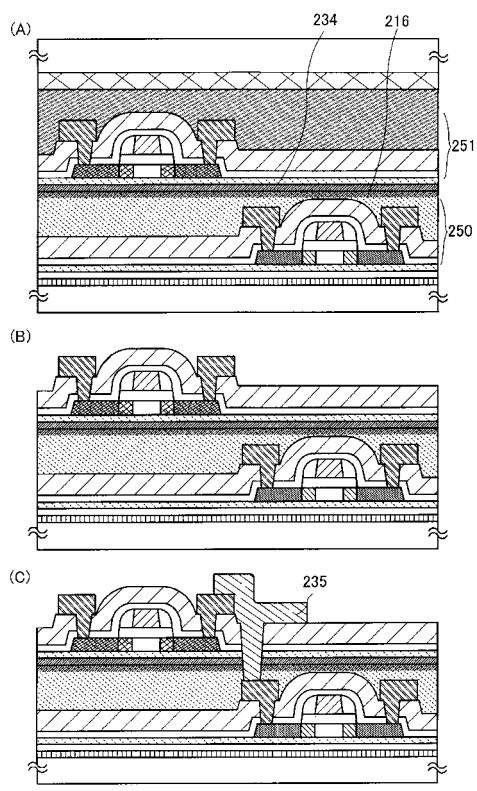

一方、半導体素子層250上に積層する上層の半導体素子層251の作製工程を、図4を用いて説明する。

**【0106】**

作製基板である絶縁表面を有する基板220上に剥離層221を介して、無機絶縁膜222、絶縁層281、単結晶半導体層284を含むトランジスタ230、絶縁膜223、絶縁膜224が設けられ、半導体素子層251が形成されている。トランジスタ230は、トランジスタ211と同様な構成を有する薄膜トランジスタであるが、本実施の形態では、トランジスタ211と逆導電型のpチャネル型薄膜トランジスタとする。従って、トランジ

50

ンジスタ 230 は、ソース領域又はドレイン領域、LDD 領域である不純物領域に p 型を付与する不純物元素（例えばボロン（B）やアルミニウム（Al）やガリウム（Ga）等）を含む。

#### 【0107】

半導体素子層 251 上に樹脂層 231 を設け、粘着層 232 によって保持基板 233 を接着する（図 4（B）参照。）。なお、本明細書において、粘着層とは、一時的に異種材料同士を接着する機能を有する膜をいい、粘着層は光又は熱により剥離可能なものとする。

#### 【0108】

剥離層 221 を用いて半導体素子層 251 を基板 220 より剥離する。よって半導体素子層 251 は、保持基板 233 側に設けられる（図 4（C）参照。）。

10

#### 【0109】

なお、他の基板への転置工程は、基板と半導体素子層の間に剥離層及び絶縁層を形成し、剥離層及び絶縁層の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化して、当該半導体素子層を剥離する方法、耐熱性の高い基板と半導体素子層の間に水素を含む非晶質珪素膜を設け、レーザ光の照射またはエッティングにより当該非晶質珪素膜を除去することで、当該半導体素子層を剥離する方法、基板と半導体素子層の間に剥離層及び絶縁層を形成し、剥離層及び絶縁層の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化し、剥離層の一部を溶液や NF<sub>3</sub>、 BrF<sub>3</sub>、 ClF<sub>3</sub> 等のフッ化ハロゲンガスによりエッティングで除去した後、脆弱化された金属酸化膜において剥離する方法、素子形成層が形成された基板を機械的に削除又は溶液や NF<sub>3</sub>、 BrF<sub>3</sub>、 ClF<sub>3</sub> 等のフッ化ハロゲンガスによるエッティングで除去する方法等を適宜用いることができる。また、剥離層として窒素、酸素や水素等を含む膜（例えば、水素を含む非晶質珪素膜、水素含有合金膜、酸素含有合金膜など）を用い、剥離層にレーザ光を照射して剥離層内に含有する窒素、酸素や水素をガスとして放出させ半導体素子層と基板との剥離を促進する方法を用いてよい。

20

#### 【0110】

上記剥離方法を組み合わせることでより容易に転置工程を行うことができる。つまり、レーザ光の照射、ガスや溶液などによる剥離層へのエッティング、鋭いナイフやメスなどによる機械的な削除を行い、剥離層と半導体素子層とを剥離しやすい状態にしてから、物理的な力（機械等による）によって剥離を行うこともできる。

30

#### 【0111】

また、剥離層及び無機絶縁膜との界面に液体を浸透させて作製基板から半導体素子層を剥離してもよい。

#### 【0112】

半導体素子層 251 と剥離層 221 との間に形成される無機絶縁膜 222 に残存する剥離層 221 を除去し、無機絶縁膜 222 の平坦な面を露出する（図 4（D）参照。）。凹凸形状に残存する剥離層 221 を無機絶縁膜 222 表面より除去することによって、無機絶縁膜 222 表面は平坦化されるが、さらに無機絶縁膜 222 表面に平坦化処理を行ってもよい。例えば、剥離層 221 としてタンゲステン膜を用いて、無機絶縁膜 222 表面に平坦化処理としてフッ化三塩素ガスによるエッティング処理などを行うことができる。

40

#### 【0113】

また、基板 220 上に剥離層 221 を形成後、無機絶縁膜 222 を成膜する前に、剥離層 221 に平坦化処理を行ってもよい。平坦化処理を行った剥離層 221 上に無機絶縁膜 222 を形成すると、剥離層 221 を除去することによって露出する無機絶縁膜 222 の表面の平坦性を高くすることができる。

#### 【0114】

平坦化処理としては、研磨処理やエッティング処理を行えばよく、勿論、研磨処理及びエッティング処理を両方行ってもよい。研磨処理としては、化学的機械研磨（CMP）法や液体ジェット研磨法を用いることができる。エッティング処理としては、ウェットエッティング、ドライエッティング、またはその両方を適宜用いることができる。またプラズマ処理によつ

50

て平坦化処理を行ってもよい。例えば、逆スパッタリング法を用いることができる。

#### 【0115】

露出された無機絶縁膜222は、他基板で作製された半導体素子層との接合面となるため、本実施の形態では、無機絶縁膜222に活性化のためのプラズマ処理を行い、表面が改質処理された無機絶縁膜234を形成する（図4（E）参照。）。以上の工程で上層となる半導体素子層251の接合前の工程が完了する。

#### 【0116】

作製基板上に無機絶縁膜を介して形成された半導体素子層は剥離層によって作製基板より剥離され、無機絶縁膜が露出する。露出した無機絶縁膜と下層の半導体素子層上に設けられた平坦な無機絶縁層とを接合し、下層の半導体素子層と上層の半導体素子層とを接合する。露出した無機絶縁膜222と下層の半導体素子層250上に設けられた平坦な無機絶縁層215の接合面は少なくともどちらか一方に活性化のためのプラズマ処理を行うことが好ましい。本実施の形態では、接合面両方にプラズマ処理を行う例を示す。

10

#### 【0117】

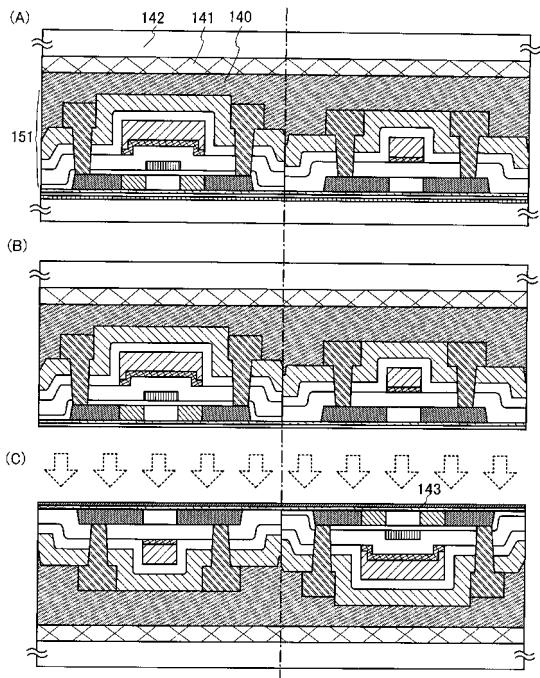

平坦化され、活性化のためのプラズマ処理を施された無機絶縁膜234と無機絶縁層216とを密着させることにより接合し、下層の半導体素子層250と上層の半導体素子層251とを積層する（図1（A）参照。）。

#### 【0118】

表面を活性化するプラズマ処理によって、室温乃至400 の温度であっても異種材料間の接合を形成することが容易となる。従って低温プロセスで多層構造の半導体装置を作製することができる。また半導体素子層間を接着するために、接着剤などの有機材料を用いず、半導体素子層間を薄膜の無機絶縁層及び無機絶縁膜で接合するため、半導体装置を薄型化、小型化することができる。

20

#### 【0119】

また、無機絶縁膜234、無機絶縁層216、絶縁層において、接合を形成する面は、十分に清浄化しておくことが好ましい。なお、メガソニック洗浄などによって清浄化することができる。また、メガソニック洗浄後にオゾン水で洗浄し、有機物の除去と表面の親水性向上を行ってもよい。

#### 【0120】

無機絶縁膜234と無機絶縁層216とを対向させて、一箇所を外部から押しつけると、局所的に接合面同士の距離が縮まる事によるファン・デル・ワールス力の強まりや水素結合の寄与によって、お互いに引きつけ合う。更に、隣接した領域でも対向する無機絶縁膜234と無機絶縁層216との間の距離が縮まるので、ファン・デル・ワールス力が強く作用する領域や水素結合が関与する領域が広がる事によって、接合（ボンディングともいう）が進行し接合面全域に接合が広がる。例えば、押しつける圧力は、100kPa～5000kPa程度とすればよい。また、無機絶縁膜234と無機絶縁層216とを重ねるように配置し、重ねる基板の重みでも接合を広げることもできる。

30

#### 【0121】

良好な接合を形成するために、表面を活性化する他の方法として、接合を形成する面に原子ビーム若しくはイオンビームを照射してもよい。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、ラジカル処理を行ってもよい。

40

#### 【0122】

また、無機絶縁膜234と無機絶縁層216との接合界面の接合強度を向上させるために、加熱処理を行うと好ましい。例えば、オーブンや炉などで70 ～350 （例えば200 で2時間）の温度条件で熱処理を行うとよい。

#### 【0123】

また、無機絶縁膜234と無機絶縁層216との間に絶縁層を形成してもよい。絶縁層は無機絶縁膜234側、あるいは無機絶縁層側どちらか一方でもよいし、両方に形成してもよい。この場合、平坦化処理及び活性化のプラズマ処理は接合面となる絶縁層に行う。接

50

合を形成する面に形成する絶縁層は平滑面を有し親水性表面を形成する。該絶縁層としては、酸化シリコン膜を用いることができる。酸化シリコン膜としては有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。その他に、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。

#### 【0124】

有機シランガスとしては、珪酸エチル(TEOS: 化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ )、トリメチルシラン(TMS:  $(\text{CH}_3)_3\text{SiH}$ )、テトラメチルシラン(化学式  $\text{Si}(\text{CH}_3)_4$ )、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシラン( $\text{SiH}(\text{OC}_2\text{H}_5)_3$ )、トリスジメチルアミノシラン( $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ )等のシリコン含有化合物を用いることができる。なお、原料ガスに有機シランを用いて化学気相成長法により酸化シリコン層を形成する場合、酸素を付与するガスを混合させることが好ましい。酸素を付与するガスとしては、酸素、亜酸化窒素、二酸化窒素等を用いることができる。さらに、アルゴン、ヘリウム、窒素又は水素等の不活性ガスを混合させてもよい。

10

#### 【0125】

また、接合を形成する面に形成する絶縁層として、モノシラン、ジシラン、又はトリシラン等のシランを原料ガスに用いて化学気相成長法により形成される酸化シリコン膜を適用することもできる。この場合も、酸素を付与するガスや不活性ガス等を混合させることができが好ましい。また、単結晶半導体層と接合する絶縁層となる酸化シリコン膜は、塩素を含んでいてもよい。

20

#### 【0126】

その他、接合を形成する面に形成する絶縁層として、酸化性雰囲気下において熱処理することにより形成される酸化シリコン、酸素ラジカルの反応により成長する酸化シリコン、酸化性の薬液により形成されるケミカルオキサイドなどを適用することもできる。絶縁層として、シロキサン( $\text{Si}-\text{O}-\text{Si}$ )結合を含む絶縁層を適用してもよい。また、前記有機シランガスと、酸素ラジカル又は窒素ラジカルとを反応させて絶縁層を形成してもよい。

#### 【0127】

無機絶縁膜、無機絶縁層、絶縁層において、接合を形成する面の表面は、算術平均粗さRaが0.8nm未満、二乗平均平方根粗さRmsが0.9nm未満が望ましく、Raが0.4nm以下、Rmsが0.5nm以下がより望ましく、さらにはRaが0.3nm以下、Rmsが0.4nm以下がより望ましい。例えば、Raが0.27nm、Rmsが0.34nmである。本明細書においてRaは算術平均粗さであり、Rmsは二乗平均平方根粗さであり、測定範囲は2μm<sup>2</sup>、又は10μm<sup>2</sup>である。

30

#### 【0128】

無機絶縁膜234と無機絶縁層216とを接合するに際し、接合を形成する面の一方若しくは双方に、好ましくは有機シランを原材料として成膜した酸化シリコン膜でなる絶縁層を設けると強固な接合を形成することができる。

40

#### 【0129】

次に、樹脂層231、粘着層232、及び保持基板233を半導体素子層250及び半導体素子層251積層より剥離し除去する(図1(B)参照。)。本実施の形態では、樹脂層231に水溶性樹脂を用い、樹脂層を溶解させて除去することによって粘着層232及び保持基板233を剥離する。樹脂層231には他の可溶性樹脂や可塑性樹脂なども用い、化学的、又は物理的に樹脂層231を半導体素子層251より剥離すればよい。

#### 【0130】

絶縁膜224、絶縁膜223、無機絶縁膜234、無機絶縁層216を貫通する開口(コントクトホール)を形成し、トランジスタ230とトランジスタ211とを電気的に接続する配線層235を形成する(図1(C)参照。)。

#### 【0131】

50

半導体素子層 251 及び配線層 235 上に樹脂層 236 を形成し、樹脂層 236 上に可撓性基板 237 を設ける(図2(A)参照。)。剥離層 201 を用いて基板 200 を剥離し、除去する(図2(B)参照。)。無機絶縁膜 202 表面に残存する剥離層はエッティングなどによって除去し、平坦化してもよい。無機絶縁膜 202 を更に他の半導体素子層上に設けられた無機絶縁層と接合する場合は、平坦化することが好ましい。本実施の形態では、無機絶縁膜 202 と接して可撓性基板 238 を設け、多層構造の半導体素子層を封止する(図2(C)参照。)。可撓性基板は接着層によって接着して設けてよい。

#### 【0132】

本実施の形態で作製した半導体装置は、可撓性基板上に設けることで、可撓性を有する半導体装置とすることができる。

10

#### 【0133】

なお、半導体素子層の多層構造において、最下層の半導体素子層を作製する基板より剥離せず、そのまま支持基板(封止基板)として用いる場合、最下層の半導体素子層と基板間に剥離層を設けなくてもよい。

#### 【0134】

作製基板である基板 200、220、保持基板 233 としては、ガラス基板、石英基板、サファイア基板、セラミック基板、表面に絶縁層が形成された金属基板などを用いることができる。また、本実施の形態の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよいし、フィルムのような可撓性基板を用いても良い。

20

#### 【0135】

基板上で平坦化処理を行う場合、基板の平坦性が高い方が好ましいので、たわみの少なく平坦性の高い石英基板や、シリコン基板などの金属基板などを用いることが好ましい。逆に作製基板より剥離層を用いて半導体素子層を剥離する場合、形状が半導体素子層にあわせて変形しやすいフィルムやシートなどの可撓性基板を用いることが好ましい。作製基板より可撓性のフィルムに半導体素子層を一旦剥離して、再度平坦性が高いたわみにくい金属基板などに半導体素子を剥離し、接着してもよい。半導体装置の作製工程において、その行う工程に合わせて作製基板及び保持基板を適宜選択することができる。

#### 【0136】

可撓性基板 237、238 のような、可撓性基板(フレキシブルな基板ともいう)としては、P E T(ポリエチレンテレフタレート)、P E N(ポリエチレンナフタレート)、P E S(ポリエーテルスルホン)、ポリプロピレン、ポリプロピレンサルファイド、ポリカーボネート、ポリエーテルイミド、ポリフェニレンサルファイド、ポリフェニレンオキサイド、ポリサルフォン、ポリフタールアミド等からなる基板、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニルなどからなるフィルム、纖維質な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、無機蒸着フィルム、紙類等)と、接着性合成樹脂フィルム(アクリル系合成樹脂、エポキシ系合成樹脂等)との積層フィルムなどを用いることができる。フィルムが被処理体と接着する際は、フィルムの最表面に設けられた接着層か、又は最外層に設けられた層(接着層ではない)を用いて接着する。フィルムの種類によって条件を選択し、加熱処理や加圧により接着することができる。また、基板に接着層が設けられていてもよい。接着層は、熱硬化樹脂、紫外線硬化樹脂、エポキシ樹脂系接着剤、樹脂添加剤等の接着剤を含む層に相当する。

30

#### 【0137】

また、可撓性基板としては、プリプレグを用いることで、後に作製される半導体装置の点圧、線圧による破壊を防ぐことが可能である。プリプレグの代表例としては、ポリビニルアルコール系纖維、ポリエステル系纖維、ポリアミド系纖維、ポリエチレン系纖維、アラミド系纖維、ポリパラフェニレンベンゾピスオキサゾール纖維、ガラス纖維、または炭素纖維等の纖維体に、エポキシ樹脂、不飽和ポリエステル樹脂、ポリイミド樹脂、フッ素樹脂等のマトリックス樹脂を有機溶剤で希釈したワニスを含浸させた後、乾燥して有機溶剤を揮発させてマトリックス樹脂を半硬化させたものである。

40

#### 【0138】

50

ゲート絶縁層、無機絶縁層、無機絶縁膜などを間に挟んで積層する下層の単結晶半導体層と上層の単結晶半導体層とは、該ゲート絶縁層、無機絶縁層、無機絶縁膜を貫通する配線層によって電気的に接続する。下層の単結晶半導体層と上層の単結晶半導体層とが重なって積層される場合、配線層は上層の単結晶半導体層を貫通して下層の単結晶半導体層と接して形成されてもよい。積層する単結晶半導体層が重なり合うように密に積層されると、より高集積化された半導体装置とすることができる。

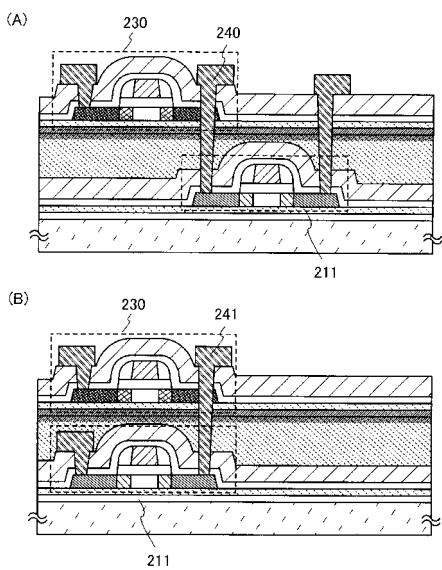

#### 【0139】

下層の単結晶半導体層と上層の単結晶半導体層とが重なって積層する半導体装置の例を図10(A)(B)に示す。図10(A)において、下層の半導体素子であるトランジスタ211の単結晶半導体層のソース領域又はドレイン領域、及び上層の半導体素子であるトランジスタ230の単結晶半導体層のソース領域又はドレイン領域は重なって積層している。トランジスタ211及びトランジスタ230を電気的に接続する配線層240は、絶縁膜224、223、無機絶縁膜234、トランジスタ230の単結晶半導体層のソース領域又はドレイン領域、無機絶縁層216、及び絶縁膜213、212を貫通し、トランジスタ211の単結晶半導体層のソース領域又はドレイン領域に達して形成されている。

10

#### 【0140】

図10(A)のトランジスタ211の単結晶半導体層とトランジスタ230の単結晶半導体層とは一部重なるように形成する例であるが、図10(B)に示すように同じマスクなどを用いて、単結晶半導体層同士をほぼ重ねて形成してもよい。単結晶半導体層同士が重なる領域が大きいほどより高集積化することはできる。図10(B)の半導体装置においては、トランジスタ211とトランジスタ230とは絶縁層を介してほぼ同位置に重なるように積層している。トランジスタ211及びトランジスタ230を電気的に接続する配線層241も、絶縁膜224、223、無機絶縁膜234、トランジスタ230の単結晶半導体層のソース領域又はドレイン領域、無機絶縁層216、及び絶縁膜213、212を貫通し、トランジスタ211の単結晶半導体層のソース領域又はドレイン領域に達して形成されている。

20

#### 【0141】

本発明の半導体装置は、3次元的に半導体素子を積層し高集積化した構造を有するため、半導体素子は同一絶縁層に接して隣接して配置される他、上下方向に層間絶縁層を介して異なる絶縁層に接して積層することができる。従って、半導体装置における半導体素子の配置の自由度が広く、より高集積化、高性能化を達成することができる。半導体素子として電界効果トランジスタはもちろん、単結晶半導体層を用いる記憶素子なども適用することができ、多用途に渡って要求される機能を満たす半導体装置を作製し、提供することができる。

30

#### 【0142】

剥離層201、221は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)、珪素(Si)から選択された元素、又は元素を主成分とする合金材料、又は前記元素を主成分とする化合物材料からなる層を、単層又は積層して形成する。珪素を含む層の結晶構造は、非晶質、微結晶、多結晶のいずれの場合でもよい。なお、ここでは、塗布法は、スピンドルコート法、液滴吐出法、ディスペ nsンス法を含む。

40

#### 【0143】

剥離層201、221が单層構造の場合、好ましくは、タンゲステン層、モリブデン層、又はタンゲステンとモリブデンの混合物を含む層を形成する。又は、タンゲステンの酸化物若しくは酸化窒化物を含む層、モリブデンの酸化物若しくは酸化窒化物を含む層、又はタンゲステンとモリブデンの混合物の酸化物若しくは酸化窒化物を含む層を形成する。なお、タンゲステンとモリブデンの混合物とは、例えば、タンゲステンとモリブデンの合金に相当する。

50

## 【0144】

剥離層201、221が積層構造の場合、好ましくは、1層目としてタングステン層、モリブデン層、又はタングステンとモリブデンの混合物を含む層を形成し、2層目として、タングステン、モリブデン又はタングステンとモリブデンの混合物の酸化物、窒化物、酸化窒化物又は窒化酸化物を形成する。

## 【0145】

剥離層201、221として、タングステンを含む層とタングステンの酸化物を含む層の積層構造を形成する場合、タングステンを含む層を形成し、その上層に酸化物で形成される絶縁層を形成することで、タングステンを含む層と絶縁層との界面に、タングステンの酸化物を含む層が形成されることを活用してもよい。さらには、タングステンを含む層の表面を、熱酸化処理、酸素プラズマ処理、オゾン水等の酸化力の強い溶液での処理等を行ってタングステンの酸化物を含む層を形成してもよい。またプラズマ処理や加熱処理は、酸素、窒素、一酸化二窒素、一酸化二窒素単体、あるいは前記ガスとその他のガスとの混合気体雰囲気下で行ってもよい。これは、タングステンの窒化物、酸化窒化物及び窒化酸化物を含む層を形成する場合も同様であり、タングステンを含む層を形成後、その上層に窒化珪素層、酸化窒化珪素層、窒化酸化珪素層を形成するとよい。10

## 【0146】

また、上記の工程によると、基板200、220に接するように剥離層201、221を形成しているが、本発明はこの工程に制約されない。基板200、220に接するよう下地となる絶縁層を形成し、その絶縁層に接するように剥離層201、221を設けてよい。20

## 【0147】

無機絶縁膜202、222は、スパッタリング法やプラズマCVD法、塗布法、印刷法等により、無機化合物を用いて単層又は積層で形成する。無機化合物の代表例としては、珪素酸化物又は珪素窒化物が挙げられる。珪素酸化物及び珪素窒化物の代表例としては、酸化珪素、酸化窒化珪素、窒化珪素、窒化酸化珪素等が該当する。

## 【0148】

本明細書において、酸化窒化シリコン(珪素)膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)及び水素前方散乱法(HFS: Hydrogen Forward Scattering)を用いて測定した場合に、濃度範囲として酸素が50~70原子%、窒素が0.5~1.5原子%、Siが2.5~3.5原子%、水素が0.1~1.0原子%の範囲で含まれるものという。また、窒化酸化シリコン(珪素)膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS及びHFSを用いて測定した場合に、濃度範囲として酸素が5~30原子%、窒素が2.0~5.5原子%、Siが2.5~3.5原子%、水素が1.0~3.0原子%の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、Si及び水素の含有比率が上記の範囲内に含まれるものとする。30

## 【0149】

さらには、無機絶縁膜202、222を積層構造としても良い。例えば、無機化合物を用いて積層してもよく、代表的には、酸化珪素、窒化酸化珪素、及び酸化窒化珪素を積層して形成しても良い。

## 【0150】

ゲート絶縁層207は酸化珪素、若しくは酸化珪素と窒化珪素の積層構造で形成すればよい。ゲート絶縁層207は、プラズマCVD法や減圧CVD法により絶縁膜を堆積することで形成しても良いし、プラズマ処理による固相酸化若しくは固相窒化で形成すると良い。単結晶半導体層を、プラズマ処理により酸化又は窒化することにより形成するゲート絶縁層は、緻密で絶縁耐圧が高く信頼性に優れているためである。例えば、亜酸化窒素(N<sub>2</sub>O)をArで1~3倍(流量比)に希釈して、10~30Paの圧力にて3~5kWの50

マイクロ波(2.45GHz)電力を印加して単結晶半導体層の表面を酸化若しくは窒化させる。この処理により1nm~10nm(好ましくは2nm~6nm)の絶縁膜を形成する。さらに亜酸化窒素(N<sub>2</sub>O)とシラン(SiH<sub>4</sub>)を導入し、10~30Paの圧力にて3~5kWのマイクロ波(2.45GHz)電力を印加して気相成長法により酸化窒化シリコン膜を形成してゲート絶縁層を形成する。固相反応と気相成長法による反応を組み合わせることにより界面準位密度が低く絶縁耐圧の優れたゲート絶縁層を形成することができる。

#### 【0151】

また、ゲート絶縁層207として、二酸化ジルコニウム、酸化ハフニウム、二酸化チタン、五酸化タンタルなどの高誘電率材料を用いても良い。ゲート絶縁層205に高誘電率材料を用いることにより、ゲートリーコ電流を低減することができる。10

#### 【0152】

ゲート電極層208は、CVD法やスパッタ法、液滴吐出法などを用いて形成することができる。ゲート電極層は、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Baから選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、単層構造でも複数層の構造でもよく、例えば、窒化タンゲステン膜とモリブデン膜との2層構造としてもよいし、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金(Al-Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金(Al-Si)膜に代えてアルミニウムとチタンの合金膜(Al-Ti)を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。20

#### 【0153】

ゲート電極層に可視光に対して透光性を有する透光性の材料を用いることもできる。透光性の導電材料としては、インジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、有機インジウム、有機スズ、酸化亜鉛等を用いることができる。また、酸化亜鉛(ZnO)を含むインジウム亜鉛酸化物(IZO(Indium Zinc Oxide))、酸化亜鉛(ZnO)、ZnOにガリウム(Ga)をドープしたもの、酸化スズ(SnO<sub>2</sub>)、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物なども用いてもよい。30

#### 【0154】

ゲート電極層を形成するのにエッティングにより加工が必要な場合、マスクを形成し、ドライエッティングまたはウェットエッティングにより加工すればよい。ICP(Inductive Coupled Plasma:誘導結合型プラズマ)エッティング法を用い、エッティング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節することにより、電極層をテーパー形状にエッティングすることができる。なお、エッティング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>もしくはCCl<sub>4</sub>などを代表とする塩素系ガス、CF<sub>4</sub>、SF<sub>6</sub>もしくはNF<sub>3</sub>などを代表とするフッ素系ガス又はO<sub>2</sub>を適宜用いることができる。40

#### 【0155】

ゲート電極層、単結晶半導体層を覆う絶縁層を形成した後、これをRIE(Reactive Ion Etching:反応性イオンエッティング)法による異方性のエッティングによって加工し自己整合的にサイドウォール構造の絶縁層209a、209bを形成すればよい。ここで、絶縁層について特に限定はなく、TEOS(Tetra-Ethyl-Ortho-Silicate)若しくはシラン等と、酸素若しくは亜酸化窒素等とを反応させて形成した段差被覆性のよい酸化珪素であることが好ましい。絶縁層は熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD、スパッタリング等の方法によって50

形成することができる。

**【0156】**

本実施の形態では、シングルゲート構造を説明したが、ダブルゲート構造などのマルチゲート構造でもよい。この場合、単結晶半導体層の上方、下方にゲート電極層を設ける構造でも良く、単結晶半導体層の片側（上方又は下方）にのみ複数ゲート電極層を設ける構造でもよい。

**【0157】**

また、トランジスタのソース領域及びドレイン領域にシリサイドを設ける構造としてもよい。シリサイドは単結晶半導体層のソース領域及びドレイン領域上に導電膜を形成し、加熱処理、G R T A法、L R T A法等により、露出されたソース領域及びドレイン領域の単結晶半導体層中の珪素と導電膜とを反応させて形成する。レーザ照射やランプによる光照射によってシリサイドを形成しても良い。シリサイドを形成する導電膜の材料としては、チタン(T i)、ニッケル(N i)、タングステン(W)、モリブデン(M o)、コバルト(C o)、ジルコニウム(Z r)、H f(ハフニウム)、タンタル(T a)、バナジウム(V)、ネオジム(N d)、クロム(C r)、白金(P t)、パラジウム(P d)等を用いることができる。

10

**【0158】**

配線層210a、配線層210b、配線層235は、P V D法、C V D法、蒸着法等により導電膜を成膜した後、所望の形状にエッチングして形成することができる。また、印刷法、電解メッキ法等により、所定の場所に選択的にソース電極層又はドレイン電極層を形成することができる。更にはリフロー法、ダマシン法を用いても良い。ソース電極層又はドレイン電極層の材料は、A g、A u、C u、N i、P t、P d、I r、R h、W、A l、T a、M o、C d、Z n、F e、T i、Z r、B a等の金属、S i、G e等の半導体又はその合金、若しくはその窒化物を用いて形成すればよい。また透光性の材料も用いることができる。

20

**【0159】**

また、透光性の導電性材料であれば、インジウム錫酸化物(I T O)、酸化珪素を含むインジウム錫酸化物(I T S O)、酸化亜鉛(Z n O)を含むインジウム亜鉛酸化物(I Z O(indium zinc oxide))、酸化亜鉛(Z n O)、Z n Oにガリウム(G a)をドープしたもの、酸化スズ(S n O<sub>2</sub>)、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物などを用いることができる。

30

**【0160】**

絶縁膜212、213、223、224、無機絶縁層214は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウムその他の無機絶縁性材料を用いることができる。

**【0161】**

積層する半導体素子（例えばC M O S構造におけるnチャネル型トランジスタとpチャネル型トランジスタの積層順）の積層順は限定されず、導電型の種類も時自由に組み合わせることができる。積層するトランジスタは両方n型であってもよく、両方p型であってもよい。また同じ層に複数のトランジスタを設け、同じ層に導電型の異なるnチャネル型トランジスタ及びpチャネル型トランジスタを両方設けてもよい。

40

**【0162】**

本実施の形態では2層の積層構造を示すが、より多層の積層構造としてもよい。複数の半導体素子は基板上に設けられた絶縁層と単結晶半導体層を接合することによって、積層することができる。

**【0163】**

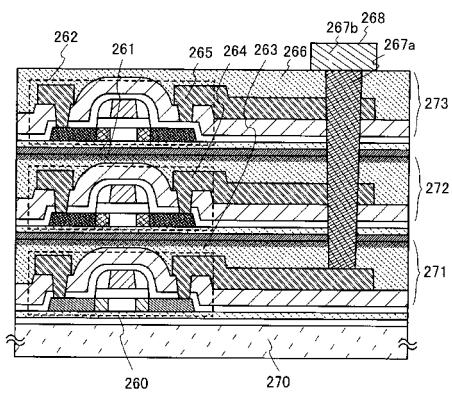

多層構造の例として3層の半導体素子層を積層する例を図17に示す。図17の半導体装置は、基板270側より、トランジスタ260を含む半導体素子層271、トランジスタ261を含む半導体素子層272、及びトランジスタ262を含む半導体素子層273の

50

積層構造を有している。半導体素子層 271、半導体素子層 272、及び半導体素子層 273は、3層を貫通する配線層 268によって電気的に接続されている。配線層 268は、トランジスタ 260の配線層 263、トランジスタ 261の配線層 264、及びトランジスタ 262の配線層 265に接して形成され、コンタクトホールである開口を埋めるように埋込配線層である配線層 267aを形成した後、埋込配線層上に引き回し配線層である配線層 267bを形成した積層構造となっている。埋込配線層は、開口にバリアメタル膜やシード膜を形成しても良い。なお、266は無機絶縁層を示す。

#### 【0164】

配線層を形成するコンタクトホールが多層の積層構造にわたって形成される場合、コンタクトホールの側面がテーパー角度を複数有する場合がある。例えば、エッチング工程を複数の段階にわけてエッチングガスを変えて行う場合、そのエッチング条件によって開口のテーパー角や径などの形状が異なる場合がある。10

#### 【0165】

従って、本発明を用いた本実施の形態では、低温プロセスで多層構造の半導体装置を作製することができる。また半導体素子層間を接着するために、接着剤などの有機材料を用いず、半導体素子層間を薄膜の無機絶縁層及び無機絶縁膜で接合するため、半導体装置を薄型化、小型化することができる。

#### 【0166】

積層する半導体素子層間に設けられる無機絶縁層が薄膜であるため、単結晶半導体層間に設ける無機絶縁層を貫通して形成される配線層も作製しやすく歩留まりや生産性を高くすることができる。従って、積層する半導体素子同士の電気的接続において、形状不良による電気的不良などを軽減し、信頼性の高い半導体装置を作製することができる。20

#### 【0167】

また、それぞれ他基板に別工程によって作製された半導体素子層を積層して集積化するため、他層の半導体素子層の作製条件に影響を受けず、最適化された条件（材料、膜厚及び素子構造）でそれぞれ特性の高い半導体素子層を形成することができる。従って、複数の半導体素子の多層構造を有する半導体装置も高性能化することができる。

#### 【0168】

従って、本発明の半導体装置は、3次元的に半導体素子を積層し高集積化した構造を有する。従って、半導体装置における半導体素子の配置の自由度が広く、より高集積化、高性能化を達成することができる。半導体素子としては電界効果トランジスタはもちろん、単結晶半導体層を用いる記憶素子なども適用することができ、多用途に渡って要求される機能を満たす半導体装置を作製し、提供することができる。30

#### 【0169】

##### (実施の形態 2 )

本実施の形態では、実施の形態 1において、単結晶半導体基板より作製基板へ単結晶半導体層を接合する工程の異なる例を図 19 を用いて示す。従って、実施の形態 1と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

#### 【0170】

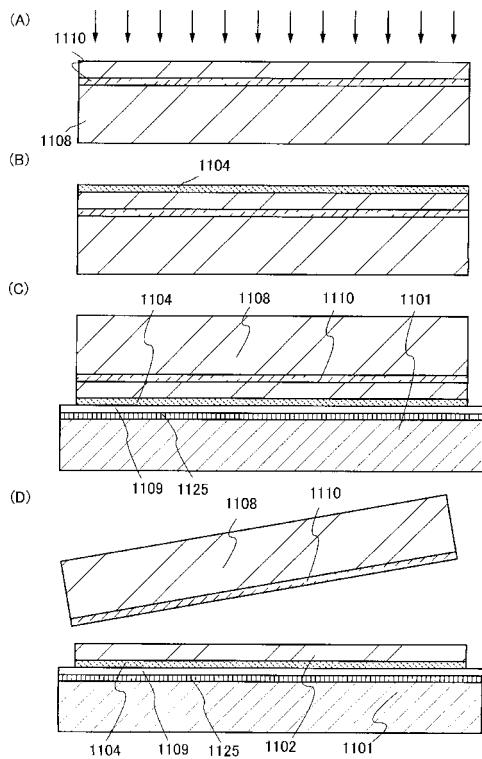

図 19 (A) に示す単結晶半導体基板 1108 は清浄化されており、その表面から電界で加速されたイオンを所定の深さに添加し、脆弱化層 1110 を形成する。40

#### 【0171】

次に、脆弱化層 1110 が設けられた単結晶半導体基板 1108 上に無機絶縁膜 1109 を形成し、無機絶縁膜 1109 上に剥離層 1130 を形成する（図 19 (B) 参照。）。このように剥離層を単結晶半導体基板側に設けてもよい。つまり、剥離層及び無機絶縁膜は、作製基板と単結晶半導体層との間に設ければよい。

#### 【0172】

実施の形態 1 と同様に剥離層 1130 に平坦化処理を行い、平坦化された剥離層 1125 を形成する（図 19 (C) 参照。）。

#### 【0173】

10

20

30

40

50

絶縁層 1104 が形成された作製基板 1101 と単結晶半導体基板 1108 の平坦化された剥離層 1125 が形成された面を密着させて接合を形成する（図 19 (D) 参照。）。作製基板 1101 上の絶縁層 1104 と単結晶半導体基板 1108 の剥離層 1125 を密着させることにより接合が形成される。

#### 【0174】

絶縁層 1104 は、作製基板 1101 側に形成してもよいし、剥離層 1125 側に形成してもよく、両方に形成してもよい。また、作製基板 1101 と剥離層 1125 とを直接接合できる場合は、絶縁層 1104 を設けなくてもよい。

#### 【0175】

その後、図 19 (E) で示すように単結晶半導体基板 1108 を剥離し、作製基板 110 10 上に単結晶半導体層 1102 を形成する。このようにして剥離層を介して単結晶半導体層を有する本発明の SOI 構造の半導体基板を得ることができる。

#### 【0176】

本実施の形態において、単結晶半導体基板 1108 として単結晶シリコン基板を適用した場合は、単結晶半導体層 1102 として単結晶シリコン層を得ることが可能である。また、本実施の形態の半導体装置の製造方法は、低温プロセスとすることができる。よって、高速動作が可能で、サブスレッショルド値が低く、電界効果移動度が高く、低消費電圧で駆動可能など高性能、高信頼性のトランジスタを作製基板上に作製することができる。

#### 【0177】

本実施の形態は実施の形態 1 と適宜組み合わせて実施することが可能である。

20

#### 【0178】

##### (実施の形態 3)

本実施の形態では、実施の形態 1 において、単結晶半導体基板より作製基板へ単結晶半導体層を接合する工程の異なる例を示す。従って、実施の形態 1 と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

#### 【0179】

本実施の形態は、単結晶半導体基板より単結晶半導体層を転置する際、単結晶半導体基板を選択的にエッチング（溝加工ともいう）し、作製する半導体素子の大きさに複数に分割された複数の単結晶半導体層を、作製基板に転置する。従って、作製基板には、複数の島状の単結晶半導体層を形成することができる。予め、素子サイズの単結晶半導体層に加工して転置するために、単結晶半導体層単位で作製基板に転置することができ、単結晶半導体基板の大きさや形状に制限を受けない。そのために大型の作製基板への単結晶半導体層の転置がより効率よく行うことができる。

30

#### 【0180】

さらに、作製基板上に形成された単結晶半導体層に対して、エッチングを行い、単結晶半導体層の形状を加工、修正し精密に制御してもよい。これにより、レジストマスク形成時の露光の回り込みなどによるパターンズレや、転置時の貼り合わせ工程による位置ズレなどによる単結晶半導体層の形成位置の誤差や形状不良を修正することができる。

#### 【0181】

従って、作製基板に所望の形状の複数の単結晶半導体層を、歩留まりよく形成することができる。よって、大面積基板により精密な高性能の半導体素子及び集積回路を有する半導体装置を高スループットで生産性よく作製することができる。

40

#### 【0182】

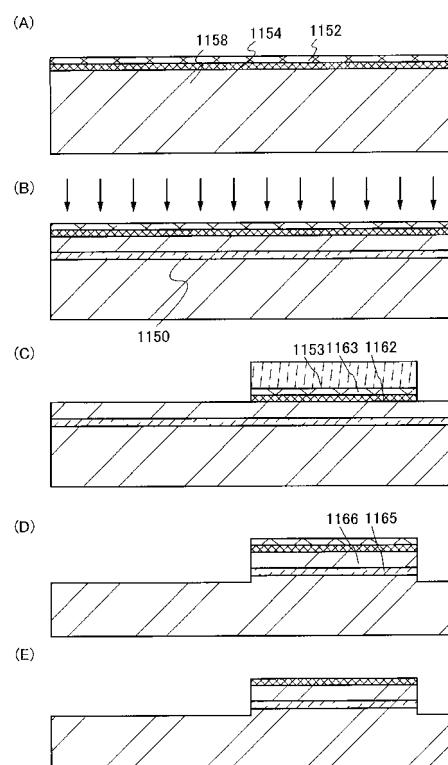

図 25 (A) において、単結晶半導体基板 1158 上に保護層 1154 と窒化シリコン膜 1152 が形成された状態を示している。窒化シリコン膜 1152 は、単結晶半導体基板 1158 を溝加工する際のハードマスクとして用いる。窒化シリコン膜 1152 は、シリコンとアンモニアを用いて気相成長法により堆積させることで形成すれば良い。

#### 【0183】

次に、イオンを添加し、単結晶半導体基板 1158 の全面に脆弱化層 1150 を形成する（図 25 (B) 参照。）。イオンの添加は作製基板に転置する単結晶半導体層の厚さを考

50

慮して行われる。イオンを添加する際の加速電圧はこのような厚さを考慮して、単結晶半導体基板 1158 の深部に添加されるようにする。この処理によって単結晶半導体基板 1158 の表面から一定の深さの領域に脆弱化層 1150 が形成される。

【 0184 】

溝加工は、半導体素子の単結晶半導体層の形状を考慮して行われる。すなわち半導体素子の単結晶半導体層が作製基板に転置できるように、その部位が凸状部として残存するよう<sup>10</sup>に単結晶半導体基板 1158 に対して溝加工を行う。

【 0185 】

フォトトレジストでマスク 1153 を形成する。マスク 1153 を用いて、窒化シリコン膜 1152 及び保護層 1154 をエッティングし、保護層 1162、及び窒化シリコン層 1163 を形成する（図 25（C）参照。）。

【 0186 】

次いで、窒化シリコン層 1163 をハードマスクとして単結晶半導体基板 1158 のエッティングを行い、脆弱化層 1165、単結晶半導体層 1166 を有する単結晶半導体基板 1158 を形成する（図 25（D）参照。）。本発明では、脆弱化層及び溝加工によって凸状に加工された単結晶半導体基板の一部である半導体領域を図 25（D）のように単結晶半導体層 1166 という。

【 0187 】

単結晶半導体基板 1158 をエッティングする深さは、作製基板に転置する単結晶半導体層の厚さを考慮して適宜設定される。当該単結晶半導体層の厚さは水素イオンを添加する深さで設定することが可能である。単結晶半導体基板 1158 に形成する溝の深さは、脆弱化層よりも深くなるように形成することが好ましい。この溝加工において、溝の深さを脆弱化層よりも深く加工することで、脆弱化層を剥離すべき単結晶半導体層の領域のみに残すことができる。<sup>20</sup>

【 0188 】

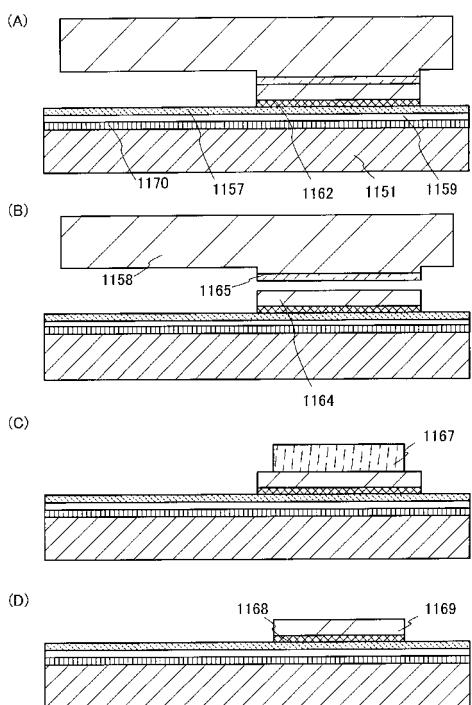

表面の窒化シリコン層 1163 を除去する（図 25（E）参照。）。そして、単結晶半導体基板 1158 における保護層 1162 の表面と作製基板 1151 を接合させる（図 26（A）参照。）。

【 0189 】

作製基板 1151 の表面には、剥離層 1170、無機絶縁膜 1159 及び絶縁層 1157 が形成されている。無機絶縁膜 1159 は作製基板 1151 からナトリウムイオンなどの不純物が拡散して単結晶半導体層を汚染するのを防止する機能がある。一方、絶縁層 1157 は、保護層 1162 と接合を形成するために設けられている。<sup>30</sup>

【 0190 】

接合は、表面が清浄化された単結晶半導体基板 1158 側の保護層 1162 と、作製基板側の絶縁層 1157 が密接することにより形成される。接合の形成は室温で行うことが可能である。この接合は原子レベルで行われ、ファン・デル・ワールス力が作用して室温で強固な接合が形成される。単結晶半導体基板 1158 には溝加工がされているので、単結晶半導体層を形成する凸状部が作製基板 1151 と接すこととなる。

【 0191 】

単結晶半導体基板 1158 と作製基板 1151 の間で接合を形成した後、熱処理を行うことにより、図 26（B）で示すように単結晶半導体基板 1158 から単結晶半導体層 1164 を剥離して作製基板 1151 に固定することができる。単結晶半導体層の剥離は、脆弱化層 1150 に形成された微少な空洞の体積変化が起こり、脆弱化層 1150 に沿って破断面を発生させることにより行う。その後、接合をさらに強固なものとするために、熱処理を行うことが好ましい。このようにして、絶縁表面上に単結晶半導体層が形成される。図 26（B）では単結晶半導体層 1164 が作製基板 1151 上に接合された状態を示している。<sup>40</sup>

【 0192 】

本実施の形態は、予め、素子サイズの単結晶半導体層に加工して転置するために、単結晶

10

20

30

40

50

半導体層単位で作製基板に転置することができ、単結晶半導体基板の大きさや形状に制限を受けない。従って、単結晶半導体基板上で様々な形状の単結晶半導体層を形成することができる。例えば、エッティングの際に用いる露光装置のマスク毎、該マスクパターンを形成するための露光装置（ステッパー）毎、大型基板より切り出す半導体装置のパネル又はチップサイズ毎に、自由に単結晶半導体層を形成することができる。

#### 【0193】

単結晶半導体層 1164 をそのまま半導体素子の単結晶半導体層として用いてもよいし、さらにエッティングを行い、形状を加工してもよい。

#### 【0194】

図 26 (C) (D) に転置された単結晶半導体層 1164 にさらにエッティングを行い、形状を加工する例を示す。マスク 1167 を、単結晶半導体層 1164 の不要部分である周辺部分を露出して形成する。

10

#### 【0195】

マスク 1167 を用いて、単結晶半導体層 1164 をエッティングし、単結晶半導体層 1169 を形成する。本実施の形態では、単結晶半導体層下の保護層 1162 も単結晶半導体層と共にエッティングし、保護層 1168 とする（図 26 (D) 参照。）。このように、作製基板に転置した後さらに形状を加工することによって、作製工程で生じた形成領域のズレや、形状不良などを修正することができる。

#### 【0196】

本実施の形態は実施の形態 1 及び 2 と適宜組み合わせて実施することが可能である。

20

#### 【0197】

##### (実施の形態 4)

本実施の形態では、実施の形態 1 において、単結晶半導体基板より作製基板へ単結晶半導体層を接合する工程の異なる例を示す。従って、実施の形態 1 と同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

#### 【0198】

本実施の形態では、単結晶半導体基板より単結晶半導体層を分離してから、作製基板に接合する例を示す。

#### 【0199】

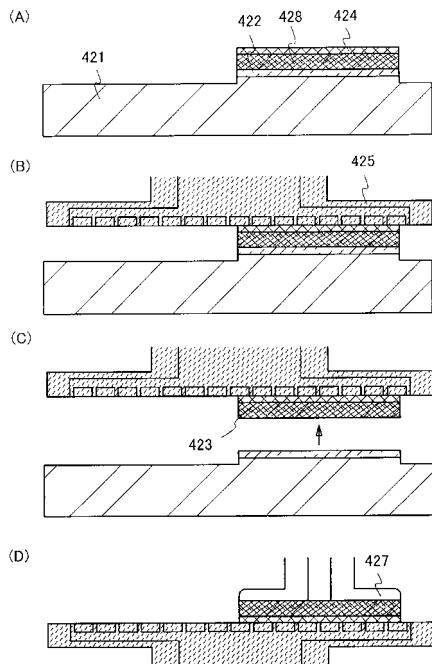

実施の形態 2 の図 25 で示したように、単結晶半導体基板に脆弱化層を形成し、溝を形成する。溝加工は、半導体素子の単結晶半導体層の形状を考慮して行われる。すなわち半導体素子の単結晶半導体層が作製基板に転載できるように、その部位が凸状部として残存するように単結晶半導体基板 401 に対して溝加工を行う。図 22 (A) において、単結晶半導体基板 401、脆弱化層 402、単結晶半導体基板の一部である単結晶半導体層 408、絶縁膜 404 が形成されている。本実施の形態では、酸化珪素を絶縁膜 404 として用いる。

30

#### 【0200】

次に、熱処理を行うことにより、脆弱化層 402 において隣接する微少ボイドどうしが結合して、微少ボイドの体積が増大する。その結果、脆弱化層 402 において単結晶半導体基板 401 が劈開し、単結晶半導体層 408 が、絶縁膜 404 と共に、単結晶半導体基板 401 から剥離する。熱処理は、例えば 400 乃至 600 の温度範囲内で行えば良い。

40

#### 【0201】

なお、熱処理は、マイクロ波などの高周波による誘電加熱を用いて行っても良い。上記誘電加熱による熱処理は、高周波発生装置において生成された周波数 300 MHz 乃至 3 THz の高周波を単結晶半導体基板 401 に照射することで行うことができる。具体的には、例えば、2.45 GHz のマイクロ波を 900 W、14 分間照射することで、脆弱化層において隣接する微少ボイドどうしを結合させ、最終的に単結晶半導体基板 401 を劈開させることができる。

#### 【0202】

50

そして、図22(B)に示すように、コレット405を単結晶半導体層408上に形成された絶縁膜404に固着させ、単結晶半導体層408を単結晶半導体基板401から引き離す。上記熱処理による単結晶半導体基板401の劈開が不完全である場合でも、コレット405を用いて力を加えることで、単結晶半導体層408を単結晶半導体基板401から完全に剥離させ、単結晶半導体層403を得ることができる。コレット405として、真空チャック、メカニカルチャックなどのチャック、先端に接着剤が付着したマイクロニードルなど、単結晶半導体層408の一つに選択的に固着させることができる手段を用いる。図22(B)では、コレット405として真空チャックを用いる場合を例示している。

## 【0203】

10

また、マイクロニードルに付着させる接着剤として、エポキシ系接着剤、セラミック系接着剤、シリコーン系接着剤、低温凝固剤などを用いることができる。低温凝固剤は、例えばMW-1(株式会社エミネントサプライ製)を用いることができる。MW-1は、凝固点が17度であり、それ以下の温度(好ましくは、10度以下)で接着効果を有し、17度以上(好ましくは25度程度)では接着効果を有さない。

## 【0204】

なお、単結晶半導体基板401を劈開させる前に、単結晶半導体基板401に水素化処理を行うようにしても良い。水素化処理は、例えば、水素雰囲気中において350、2時間程度行う。

## 【0205】

20

次に、図22(C)に示すように、単結晶半導体層403の剥離により露出した面が作製基板410側を向くように、単結晶半導体層403と作製基板410とを貼り合わせる。本実施の形態では、作製基板410上に剥離層412、無機絶縁膜411が形成されており、無機絶縁膜411と単結晶半導体層403とが接合することで、単結晶半導体層403と作製基板410とを貼り合わせることができる。単結晶半導体層403と無機絶縁膜411とを接合させた後、該接合をさらに強固にするため、400乃至600の熱処理を行うのが好ましい。

## 【0206】

接合の形成はファン・デル・ワールス力を用いて行われているため、室温でも強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、作製基板410は様々なものを用いることが可能である。例えば作製基板410としては、アルミニノシリケートガラスバリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラスなどのガラス基板の他、石英基板、サファイア基板などの基板を用いることが出来る。さらに作製基板410として、シリコン、ガリウムヒ素、インジウムリリンなどの単結晶半導体基板などを用いることができる。或いは、ステンレス基板を含む金属基板を作製基板410として用いても良い。

30

## 【0207】

なお、無機絶縁膜411と単結晶半導体層403との間にさらに絶縁層を設けてもよい。

## 【0208】

なお、単結晶半導体層403を作製基板410上に貼り合わせる前または貼り合わせた後に、単結晶半導体層403の剥離により露出した面に、レーザ光の照射による熱アニールを施しても良い。単結晶半導体層403を作製基板410上に貼り合わせる前に熱アニールを施すと、剥離により露出した面が平坦化され、接合の強度をより高めることができる。また、単結晶半導体層403を作製基板410上に貼り合わせた後に熱アニールを施すと、単結晶半導体層403が一部溶解し、接合の強度をより高めることができる。

40

## 【0209】

また、単結晶半導体層403を作製基板410上に接合のみによって貼り合わせるのではなく、単結晶半導体層403に10MHz~1THz程度の高周波数の振動を加えることで、単結晶半導体層403と作製基板410の間に摩擦熱を生じさせ、該熱により単結晶半導体層403を部分的に溶解させ、単結晶半導体層403を作製基板410上に貼り合

50

わせるようにしても良い。

【0210】

なお、MW-1を低温凝固剤として用いる場合、まず低温凝固剤が接着効果を有しない温度（例えば25度程度）において、マイクロニードルの先端に付着した低温凝固剤を、絶縁膜404に接触させる。次に、低温凝固剤が接着効果を有する温度（例えば5度程度）まで温度を下げる、低温凝固剤を凝固させることで、マイクロニードルと絶縁膜404とを固着させる。そして、単結晶半導体基板401から引き離した単結晶半導体層403を、作製基板410上に貼り合わせた後、再び接着効果を有しない温度（例えば25度程度）まで低温凝固剤の温度を高めることで、マイクロニードルを単結晶半導体層403から引き離すことができる。

10

【0211】

単結晶半導体層403上の絶縁膜404を除去し、作製基板410及び無機絶縁膜411上に島状の単結晶半導体層403が形成される（図22（D）参照。）。単結晶半導体層403にさらにエッチングをし、形状を加工してもよい。

【0212】

図22のように、劈開により露出される単結晶半導体層の表面を作製基板側に向けると、より平坦性の高い側の表面がゲート絶縁膜に接するため、単結晶半導体層とゲート絶縁膜の間の界面準位密度を低く、なつかつ均一にすることができる。よって、ゲート絶縁膜に接する単結晶半導体層の表面を平坦化するための研磨を省略、もしくは研磨時間を短縮化することができ、コストを抑えスループットを向上させることができる。

20

【0213】

なお、劈開により露出される単結晶半導体層の表面と、ゲート絶縁膜とが接するように、単結晶半導体層を作製基板上に貼り合わせることもできる。この例を図23及び図24を用いて説明する。

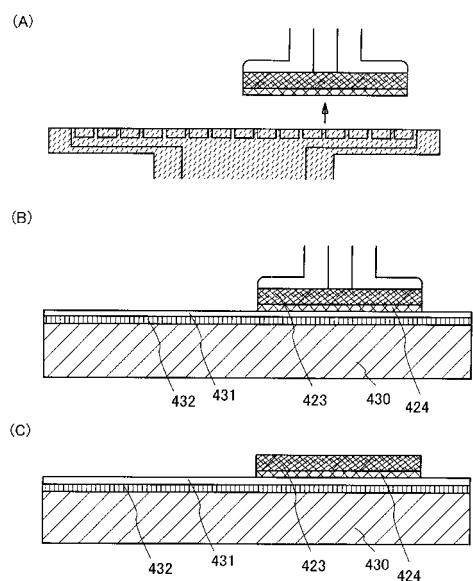

【0214】

図23（A）において、図22（A）と同様に、単結晶半導体基板421、脆弱化層422、単結晶半導体基板の一部である単結晶半導体層428、絶縁膜424が形成されている。本実施の形態では、酸化珪素を絶縁膜424として用いる。

【0215】

次に、図23（B）に示すように単結晶半導体基板421を保持手段425に固着させる。単結晶半導体基板421の固着は、単結晶半導体層428が保持手段425側を向くように行う。保持手段425として、後の熱処理に耐えることができ、なつかつ複数の単結晶半導体層（図23では単結晶半導体層428）と重なるように固着させることができる大型の真空チャックまたはメカニカルチャック、具体的には多孔質真空チャック、非接触式真空チャックなどを用いることができる。本実施の形態では、真空チャックを保持手段425として用いる例を示す。

30

【0216】

次に、熱処理を行うことにより、脆弱化層422において隣接する微少ボイドどうしが結合して、微少ボイドの体積が増大する。その結果、図23（C）に示すように、脆弱化層422において単結晶半導体基板421が劈開し、単結晶半導体基板421の一部であった単結晶半導体層428が、単結晶半導体層423となり、絶縁膜424と共に、単結晶半導体基板421から剥離する。熱処理は、例えば400乃至600の温度範囲内で行えば良い。

40

【0217】

なお、熱処理は、マイクロ波などの高周波による誘電加熱を用いて行っても良い。

【0218】

また、単結晶半導体基板421を劈開させる前に、単結晶半導体基板421に水素化処理を行うようにしても良い。

【0219】

そして、図23（D）及び図24（A）に示すように、コレット427を単結晶半導体層

50

423の劈開により露出した面に固着させ、単結晶半導体層423を保持手段425から引き離す。コレット427として、真空チャック、メカニカルチャックなどのチャック、先端に接着剤が付着したマイクロニードルなど、単結晶半導体層423に選択的に固着させることができる手段を用いる。図23(D)及び図24(A)では、コレット427として真空チャックを用いる場合を例示している。

#### 【0220】

なお、本実施の形態では、コレット427が単結晶半導体層423の劈開により露出した面に固着している例を示しているがコレット427により傷つくのを防ぐために、絶縁膜などの保護膜を形成しても良い。ただし、上記保護膜は、後に作製基板430に単結晶半導体層423を貼り合わせた後に、除去する。

10

#### 【0221】

また、マイクロニードルに付着させる接着剤として、エポキシ系接着剤、セラミック系接着剤、シリコーン系接着剤、低温凝固剤などを用いることができる。

#### 【0222】

次に、図24(B)に示すように、絶縁膜424が作製基板430側を向くように、すなわち劈開により露出した面の反対側の面が作製基板430側を向くように、単結晶半導体層423と作製基板430とを貼り合わせる。本実施の形態では、作製基板430上に剥離層432、無機絶縁膜431が形成されており、絶縁膜424と無機絶縁膜431とが接合することで、単結晶半導体層423と作製基板430とを貼り合わせることができる(図24(C)参照。)。絶縁膜424と無機絶縁膜431とを接合させた後、該接合をさらに強固にするため、400乃至600の熱処理を行うのが好ましい。

20

#### 【0223】

接合の形成はファン・デル・ワールス力を用いて行われているため、室温でも強固な接合が形成される。なお、上記接合は低温で行うことが可能であるため、作製基板430は様々なものを用いることが可能である。

#### 【0224】

なお、単結晶半導体基板は、反りや撓みを有している場合や、端部に弱冠丸みを帯びている場合がある。また、単結晶半導体基板から単結晶半導体層を剥離するために水素又は希ガス、或いは水素イオン又は希ガスイオンを添加する際、単結晶半導体基板の端部において上記ガスまたはイオンの添加を十分に行うことができない場合もある。そのため、単結晶半導体基板の端部に位置する部分は、半導体膜を剥離するのが難しく、単結晶半導体基板を作製基板に貼り合わせた後に単結晶半導体基板を劈開して半導体膜を形成する場合、単結晶半導体層間の間隔が数mm～数cmとなってしまう。しかし、本実施の形態では、単結晶半導体基板を作製基板に貼り合わせる前に、単結晶半導体基板を劈開させて単結晶半導体層を形成している。よって、単結晶半導体層を作製基板上に貼り合わせる際、単結晶半導体層間の間隔を、数十μm程度に小さく抑えることができ、単結晶半導体層間の隙間をまたぐように半導体装置を作製することが容易となる。

30

#### 【0225】

本実施の形態の半導体装置の作製方法では、複数の単結晶半導体基板を用いて一つの作製基板に複数の単結晶半導体層を貼り合わせることができるので、高スループットで処理を行うことができる。また、半導体素子の有する極性に合わせて半導体膜の面方位を適宜選択することができるので、半導体素子の移動度を高めることができ、より高速駆動が可能な半導体装置を提供することができる。

40

#### 【0226】

また、単結晶半導体基板の複数箇所において劈開することで複数の単結晶半導体層を形成し、該複数の単結晶半導体層を作製基板上に貼り合わせることができるので、半導体装置における半導体素子の極性及びレイアウトに合わせて、複数の各単結晶半導体層を貼り合わせる位置を選択することができる。

#### 【0227】

本実施の形態は、実施の形態1及び2と適宜組み合わせて実施することが可能である。

50

## 【0228】

(実施の形態5)

本実施の形態では、より高集積化、薄型化、及び小型化を付与することを目的とした半導体装置、及び半導体装置の作製方法においてメモリを有する半導体装置の一例に関して図面を用いて説明する。

## 【0229】

本実施の形態の半導体装置はメモリにメモリセルアレイ及びメモリセルアレイを駆動する駆動回路部を有する。メモリセルアレイに設けられるメモリ素子及び制御用薄膜トランジスタは駆動電圧が高く電圧に対して高耐性を求められ、一方駆動回路部に設けられる薄膜トランジスタは高速動作を求められるため、メモリセルアレイの半導体素子層と駆動回路部の半導体素子層とを別々の基板で作製する。別々な基板で作製されたメモリセルアレイの半導体素子層と駆動回路部の半導体素子層とを、本発明を用いて積層して多層構造の半導体装置を作製する。

10

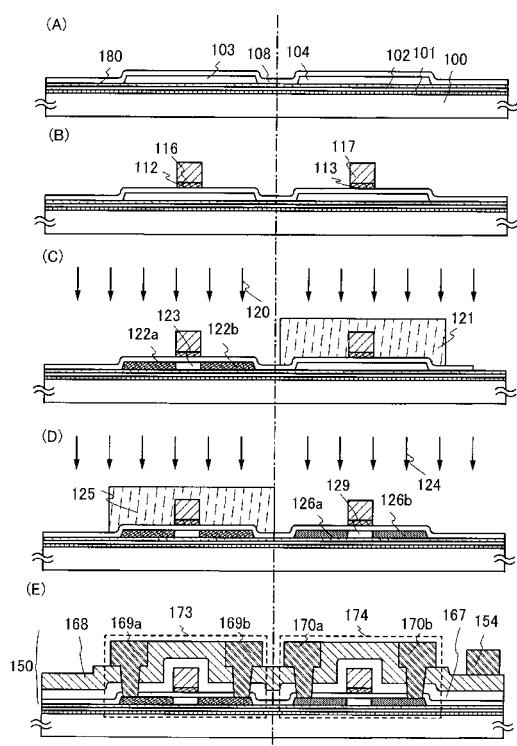

## 【0230】

本実施の形態では、駆動回路部の半導体素子層を下層に、メモリセルアレイの半導体素子層を上層にして半導体装置を作製する。まず、下層の駆動回路部の半導体素子層の作製工程を図5及び図6を用いて説明する。

## 【0231】

絶縁表面を有する作製基板である基板100の上に剥離層101を形成し、剥離層101上に無機絶縁膜102を形成する。無機絶縁膜102は下地膜としても機能する。

20

## 【0232】

次いで、無機絶縁膜102上に絶縁層180を介して実施の形態1と同様に単結晶半導体基板より分離され、基板100上に接合された単結晶半導体層103、104を形成する。無機絶縁膜102と単結晶半導体層103、104とを直接接合させて、絶縁層180を設けない構成としてもよい。

## 【0233】

単結晶半導体層103、104には、しきい値電圧を制御するためにnチャネル型電界効果トランジスタ及びpチャネル型電界効果トランジスタの形成領域に合わせて、硼素、アルミニウム、ガリウムなどのp型不純物、若しくはリン、砒素などのn型不純物を添加してもよい。

30

## 【0234】

駆動回路部に設けられる単結晶半導体層103、及び単結晶半導体層104の膜厚は、メモリセルアレイに設けられる単結晶半導体層より薄く、5nm以上30nm以下、より好ましくは10nm以上20nm以下とすればよい。

## 【0235】

単結晶半導体層を薄膜化することで、短チャネル効果を抑制しすることが可能となる。また、トランジスタのしきい値電圧を小さくすることが可能であり、低電圧駆動をすることができる。単結晶半導体層の端部には傾斜角(テーパー角)を設けてもよい。

## 【0236】

エッティング加工は、プラズマエッティング(ドライエッティング)又はウェットエッティングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッティングが適している。エッティングガスとしては、CF<sub>4</sub>、NF<sub>3</sub>、Cl<sub>2</sub>、BCl<sub>3</sub>、などのフッ素系又は塩素系のガスを用い、HeやArなどの不活性ガスを適宜加えても良い。また、大気圧放電のエッティング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスクを形成する必要はない。

40

## 【0237】

単結晶半導体層上の酸化膜を除去し、単結晶半導体層103、単結晶半導体層104を覆うゲート絶縁層108を形成する(図5(A)参照。)。ゲート絶縁層108はプラズマCVD法またはスパッタ法などを用いて形成することができる。駆動回路部に設けられる薄膜トランジスタのゲート絶縁層108の膜厚は、1nm以上10nm以下、より好まし

50

くは 5 nm 程度とすればよい。ゲート絶縁層 108 の薄膜化すると、駆動回路部においてトランジスタを低電圧で高速に動作させる効果がある。

#### 【0238】

ゲート絶縁層 108 は酸化珪素、若しくは酸化珪素と窒化珪素の積層構造で形成すればよい。ゲート絶縁層 108 は、プラズマ CVD 法や減圧 CVD 法により絶縁膜を堆積することで形成しても良いし、プラズマ処理による固相酸化若しくは固相窒化で形成すると良い。単結晶半導体層を、プラズマ処理により酸化又は窒化することにより形成するゲート絶縁層は、緻密で絶縁耐圧が高く信頼性に優れているためである。

#### 【0239】

また、ゲート絶縁層 108 として、高誘電率材料を用いても良い。ゲート絶縁層 108 に高誘電率材料を用いることにより、ゲートリーク電流を低減することができる。高誘電率材料としては、二酸化ジルコニウム、酸化ハフニウム、二酸化チタン、五酸化タンタルなどを用いることができる。また、プラズマ処理による固相酸化により酸化シリコン層を形成しても良い。

#### 【0240】

また、薄い酸化珪素膜の形成方法としては、GRTA 法、LRTA 法等を用いて半導体領域表面を酸化し、熱酸化膜を形成することで、膜厚の薄い酸化珪素膜を形成することもできる。なお、低い成膜温度でゲートリーク電流の少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。

#### 【0241】

次いで、ゲート絶縁層 108 上にゲート電極層として用いる膜厚 20 ~ 100 nm の第 1 の導電膜と、膜厚 100 ~ 400 nm の第 2 の導電膜とを積層して形成する。第 1 の導電膜及び第 2 の導電膜は、スパッタリング法、蒸着法、CVD 法等の手法により形成することができる。第 1 の導電膜及び第 2 の導電膜はタンタル (Ta)、タンゲステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al)、銅 (Cu)、クロム (Cr)、ネオジム (Nd) から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、第 1 の導電膜及び第 2 の導電膜としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu 合金を用いてもよい。また、2 層構造に限定されず、例えば、第 1 の導電膜として膜厚 50 nm のタンゲステン膜、第 2 の導電膜として膜厚 500 nm のアルミニウムとシリコンの合金 (Al-Si) 膜、第 3 の導電膜として膜厚 30 nm の窒化チタン膜を順次積層した 3 層構造としてもよい。また、3 層構造とする場合、第 1 の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第 2 の導電膜のアルミニウムとシリコンの合金 (Al-Si) 膜に代えてアルミニウムとチタンの合金膜 (Al-Ti) を用いてもよいし、第 3 の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。本実施の形態では、第 1 の導電膜として窒化タンタルを膜厚 30 nm 形成し、第 2 の導電膜としてタンゲステン (W) を膜厚 370 nm 形成する。

#### 【0242】

本実施の形態の駆動回路部に設けられる薄膜トランジスタは、メモリセルアレイに設けられる薄膜トランジスタよりチャネル長が短い方が好ましい。本実施の形態の駆動回路部に設けられる薄膜トランジスタのチャネル長は 0.1 μm ~ 1 μm が好ましい。

#### 【0243】

次に、前記第 1 の導電膜と第 2 の導電膜をそれぞれエッチングして、第 1 のゲート電極層 112、113 及び第 2 のゲート電極層 116、117 を形成する。その後、単結晶半導体層 104 を覆うマスク 121 を形成する。マスク 121、第 1 のゲート電極層 112、第 2 のゲート電極層 116 をマスクとして p 型を付与する不純物元素 120 を添加し、p 型不純物領域 122a、p 型不純物領域 122b を形成する。本実施の形態では、不純物元素としてボロン (B) を用いる。ここでは、p 型不純物領域 122a、p 型不純物領域 122b に p 型を付与する不純物元素が  $1 \times 10^{20} \sim 5 \times 10^{21} / \text{cm}^3$  程度の濃度で含まれるように添加する。また、単結晶半導体層 103 にチャネル形成領域 123 が形

10

20

30

40

50

成される(図5(C)参照。)。

**【0244】**

p型不純物領域122a、p型不純物領域122bは高濃度p型不純物領域であり、ソース領域、ドレイン領域として機能する。

**【0245】**

次に、単結晶半導体層103を覆うマスク125を形成する。マスク125、第1のゲート電極層113、第2のゲート電極層117をマスクとしてn型を付与する不純物元素124を添加し、n型不純物領域126a、n型不純物領域126bを形成する。本実施の形態では、不純物元素としてリン(P)を用いる。ここでは、n型不純物領域126a、n型不純物領域126bにn型を付与する不純物元素が $5 \times 10^{19} \sim 5 \times 10^{20} / cm^3$ 程度の濃度で含まれるように添加する。また、単結晶半導体層104にチャネル形成領域129が形成される(図5(D)参照。)。

**【0246】**

n型不純物領域126a、n型不純物領域126bは高濃度n型不純物領域であり、ソース領域、ドレイン領域として機能する。

**【0247】**

マスク125をO<sub>2</sub>アッシングやレジスト剥離液により除去し、酸化膜も除去する。その後、ゲート電極層の側面を覆うように、絶縁膜、いわゆるサイドウォールを形成してもよい。サイドウォールは、プラズマCVD法や減圧CVD(LPCVD)法を用いて、珪素を有する絶縁膜により形成することができる。

**【0248】**

不純物元素を活性化するために加熱処理、強光の照射、又はレーザ光の照射を行ってもよい。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と単結晶半導体層との界面へのプラズマダメージを回復することができる。

**【0249】**

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、絶縁膜167と絶縁膜168との積層構造とする。絶縁膜167と絶縁膜168は、スパッタ法、またはプラズマCVDを用いた窒化珪素膜、窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の珪素を含む絶縁膜を単層または3層以上の積層構造として用いても良い。

**【0250】**

さらに、窒素雰囲気中で、300～550で1～12時間の熱処理を行い、単結晶半導体層を水素化する工程を行う。好ましくは、400～500で行う。この工程は層間絶縁層である絶縁膜167に含まれる水素により単結晶半導体層のダンギングボンドを終端する工程である。本実施の形態では、410度( )で1時間加熱処理を行う。

**【0251】**

絶縁膜167、絶縁膜168としては他に窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイアモンドライカーボン(DLC)、窒素含有炭素膜(CN)その他の無機絶縁性材料を含む物質から選ばれた材料で形成することができる。また、シロキサン樹脂を用いてもよい。なお、シロキサン樹脂とは、Si-O-Si結合を含む樹脂に相当する。

**【0252】**

次いで、レジストからなるマスクを用いて絶縁膜167、絶縁膜168、ゲート絶縁層108に単結晶半導体層に達するコンタクトホール(開口部)を形成する。エッチングは、用いる材料の選択比によって、一回で行っても複数回行っても良い。エッチングによって、絶縁膜168、絶縁膜167、ゲート絶縁層108を除去し、ソース領域又はドレイン領域であるp型不純物領域122a、p型不純物領域122b、n型不純物領域126a、n型不純物領域126bに達する開口部を形成する。エッチングは、ウェットエッチングでもドライエッチングでもよく、両方用いてもよい。ウェットエッチングのエッチャン

10

20

30

40

50

トは、フッ素水素アンモニウム及びフッ化アンモニウムを含む混合溶液のようなフッ酸系の溶液を用いるとよい。エッチング用ガスとしては、 $\text{Cl}_2$ 、 $\text{BCl}_3$ 、 $\text{SiCl}_4$ もしくは $\text{CCl}_4$ などを代表とする塩素系ガス、 $\text{CF}_4$ 、 $\text{SF}_6$ もしくは $\text{NF}_3$ などを代表とするフッ素系ガス又は $\text{O}_2$ を適宜用いることができる。また用いるエッチング用ガスに不活性気体を添加してもよい。添加する不活性元素としては、 $\text{He}$ 、 $\text{Ne}$ 、 $\text{Ar}$ 、 $\text{Kr}$ 、 $\text{Xe}$ から選ばれた一種または複数種の元素を用いることができる。

#### 【0253】

開口部を覆うように導電膜を形成し、導電膜をエッチングして各ソース領域又はドレイン領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層である配線層169a、配線層169b、配線層170a、配線層170bを形成する。また、配線層169a、配線層169b、配線層170a、配線層170bと同じ工程で配線層154を形成する。配線層154は、後工程で上層の半導体素子層151と下層の半導体素子層150とを電気的に接続するための配線として機能する。配線層は、PVD法、CVD法、蒸着法等により導電膜を成膜した後、所望の形状にエッチングして形成することができる。また、液滴吐出法、印刷法、電解メッキ法等により、所定の場所に選択的に導電層を形成することができる。更にはリフロー法、ダマシン法を用いても良い。ソース電極層又はドレイン電極層の材料は、 $\text{Ag}$ 、 $\text{Au}$ 、 $\text{Cu}$ 、 $\text{Ni}$ 、 $\text{Pt}$ 、 $\text{Pd}$ 、 $\text{Ir}$ 、 $\text{Rh}$ 、 $\text{W}$ 、 $\text{Al}$ 、 $\text{Ta}$ 、 $\text{Mo}$ 、 $\text{Cd}$ 、 $\text{Zn}$ 、 $\text{Fe}$ 、 $\text{Ti}$ 、 $\text{Zr}$ 、 $\text{Ba}$ 等の金属、及び $\text{Si}$ 、 $\text{Ge}$ 、又はその合金、若しくはその窒化物を用いて形成する。また、これらの積層構造としても良い。本実施の形態では、チタン( $\text{Ti}$ )を膜厚60nm形成し、窒化チタン膜を膜厚40nm形成し、アルミニウムを膜厚700nm形成し、チタン( $\text{Ti}$ )を膜厚200nm形成して積層構造とし、所望な形状に加工する。10

#### 【0254】

以上の工程で駆動回路部として、p型不純物領域を有するpチャネル型薄膜トランジスタである薄膜トランジスタ173、n型不純物領域を有するnチャネル型薄膜トランジスタである薄膜トランジスタ174を有する半導体素子層150を作製することができる(図5(E)参照。)。

#### 【0255】

半導体素子層150の薄膜トランジスタ173、174等によって生じる凹凸を平坦化するため、無機絶縁層145を形成する(図6(A)参照。)。無機絶縁層145に平坦化処理を行い、平坦化処理された無機絶縁層146を形成する(図6(B)参照。)。本実施の形態では、平坦化処理としてCMP法による研磨処理を行う。30

#### 【0256】

平坦化処理された無機絶縁層146は、他基板で作製された半導体素子層との接合面となるため、本実施の形態では、無機絶縁層146に活性化のためのプラズマ処理を行い、表面が改質処理された無機絶縁層147とする(図6(C)参照。)。以上の工程で下層となる半導体素子層150の接合前の工程が完了する。

#### 【0257】

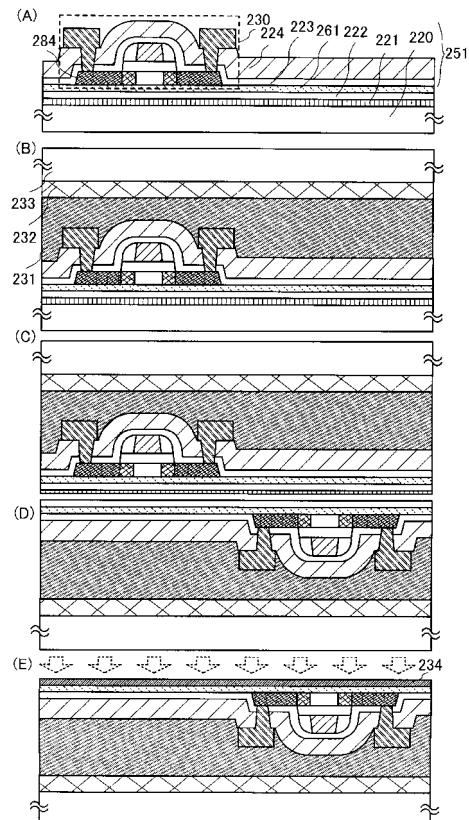

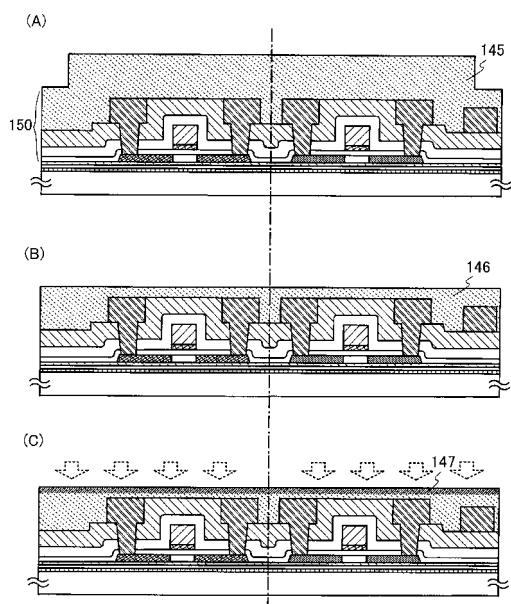

次に、上層のメモリセルアレイの半導体素子層の作製工程を図7及び図8を用いて説明する。なお、駆動回路部の半導体素子層と同様な機能を有する部分には同様の材料及び工程を用いて形成すればよく、その繰り返しの説明は省略する。40

#### 【0258】

絶縁表面を有する作製基板である基板160の上に剥離層158を形成し、剥離層158上に無機絶縁膜159を形成する。無機絶縁膜159は下地膜としても機能する。

#### 【0259】

次いで、無機絶縁膜159上に絶縁層181を介して実施の形態1と同様に単結晶半導体基板より分離され、基板160上に接合された単結晶半導体層105、106を形成する。無機絶縁膜159と単結晶半導体層105、106とを直接接合させて、絶縁層181を設けない構成としてもよい。

#### 【0260】

50

単結晶半導体層 105、106 には、しきい値電圧を制御するために n チャネル型電界効果トランジスタ及び p チャネル型電界効果トランジスタの形成領域に合わせて、硼素、アルミニウム、ガリウムなどの p 型不純物、若しくはリン、砒素などの n 型不純物を添加してもよい。

#### 【0261】

メモリセルアレイに設けられる単結晶半導体層 105 及び単結晶半導体層 106 の膜厚は、駆動回路部に設けられる単結晶半導体層より厚く、25 nm 以上 100 nm 以下、より好ましくは 50 nm 以上 60 nm 以下とすればよい。

#### 【0262】

エッチング加工は、プラズマエッチング（ドライエッチング）又はウェットエッチングのどちらを採用しても良い。 10

#### 【0263】

単結晶半導体層 105、106 上に絶縁膜 107 を形成する。絶縁膜 107 は酸化シリコン若しくは酸化シリコンと窒化シリコンの積層構造で形成すればよい。絶縁膜 107 は、プラズマ CVD 法や減圧 CVD 法により絶縁層を堆積することで形成しても良いが、好ましくはプラズマ処理による固相酸化若しくは固相窒化で形成すると良い。単結晶半導体層（代表的にはシリコン層）を、プラズマ処理により酸化又は窒化することにより形成した絶縁層は、緻密で絶縁耐圧が高く信頼性に優れているためである。絶縁膜 107 は、電荷蓄積層 111 に電荷を注入するためのトンネル絶縁層として用いるので、このように丈夫であるものが好ましい。この絶縁膜 107 は 1 nm ~ 20 nm、好ましくは 3 nm ~ 6 nm の厚さに形成することが好ましい。 20

#### 【0264】

プラズマ処理により形成される好適な絶縁膜 107 の一例は、酸化雰囲気下のプラズマ処理により単結晶半導体層上に 3 nm ~ 6 nm の厚さで酸化珪素層を形成し、その後窒素雰囲気下でその酸化珪素層の表面を窒化プラズマで処理した窒素プラズマ処理層を形成する。具体的には、まず、酸素雰囲気下でのプラズマ処理により単結晶半導体層上に 3 nm ~ 6 nm の厚さで酸化珪素層を形成する。その後、続けて窒素雰囲気下でプラズマ処理を行うことにより酸化珪素層の表面又は表面近傍に窒素濃度の高い窒素プラズマ処理層を設ける。なお、表面近傍とは、酸化珪素層の表面から概略 0.5 nm ~ 1.5 nm の深さをいう。例えば、窒素雰囲気下でプラズマ処理を行うことによって、酸化珪素層の表面からほぼ 1 nm の深さに窒素を 20 ~ 50 原子% の割合で含有した構造となる。 30

#### 【0265】

単結晶半導体層の代表例としての珪素層の表面をプラズマ処理で酸化することで、界面に歪みのない緻密な酸化層を形成することができる。また、当該酸化層をプラズマ処理で窒化することで、表層部の酸素を窒素に置換して窒化層を形成すると、さらに緻密化することができる。それにより絶縁耐圧が高い絶縁層を形成することができる。

#### 【0266】

いずれにしても、上記のようなプラズマ処理による固相酸化処理若しくは固相窒化処理を用いることで、耐熱温度が 700 以下のガラス基板を用いても、950 ~ 1050 で形成される熱酸化膜と同等な絶縁層を得ることができる。すなわち、不揮発性メモリ素子のトンネル絶縁層として信頼性の高いトンネル絶縁層を形成することができる。 40

#### 【0267】

電荷蓄積層 111 を絶縁膜 107 上に形成する。この電荷蓄積層 111 は、単層でもよいし、複数の層を積層して設けてもよい。

#### 【0268】

電荷蓄積層 111 としては、半導体材料または導電性材料の層または粒子で形成し浮遊ゲートとすることができる。半導体材料としては、シリコン、シリコングルマニウム等がある。シリコンを用いる場合、アモルファスシリコンやポリシリコンを用いることができる。さらには、リンがドープされたポリシリコンを用いることができる。導電性材料としては、タンタル（Ta）、チタン（Ti）、モリブデン（Mo）、タングステン（W）から 50

選ばれた元素、前記元素を主成分とする合金、前記元素を組み合わせた合金膜（代表的にはMo-W合金膜、Mo-Ta合金膜）、あるいは導電性を付与した珪素膜で形成すれば良い。このような材料から成る導電層の下には窒化タンタル、窒化タングステン、窒化チタン、窒化モリブデンなどの窒化物、タングステンシリサイド、チタンシリサイド、モリブデンシリサイドなどのシリサイドを形成しておいても良い。更には、上記半導体材料同士、導電性材料同士、または半導体材料及び導電性材料の積層構造としてもよい。例えば、シリコン層及びゲルマニウム層の積層構造としてもよい。

## 【0269】

また、電荷蓄積層111として、絶縁性であり、電荷を保持するトラップを有する層で形成することもできる。このような材料の代表例として、代表的にはシリコン化合物、ゲルマニウム化合物がある。シリコン化合物としては、窒化珪素、酸窒化珪素、水素が添加された酸窒化珪素等がある。ゲルマニウム化合物としては、窒化ゲルマニウム、酸素が添加された窒化ゲルマニウム、窒素が添加された酸化ゲルマニウム、酸素及び水素が添加された窒化ゲルマニウム、窒素及び水素が添加された酸化ゲルマニウム等のゲルマニウム化合物等がある。

10

## 【0270】

次に単結晶半導体層106を覆うマスク161を形成する。マスク161、電荷蓄積層111をマスクとしてn型を付与する不純物元素163を添加し、n型不純物領域162a、n型不純物領域162bを形成する。本実施の形態では、不純物元素としてn型を付与する不純物元素であるリン(P)を用いる。ここでは、n型不純物領域162a、n型不純物領域162bに、n型を付与する不純物元素が $1 \times 10^{17} \sim 5 \times 10^{18} / \text{cm}^3$ 程度の濃度で含まれるように添加する。

20

## 【0271】

マスク161を除去し、絶縁膜107をエッチング加工して、絶縁層110を形成する。

## 【0272】

単結晶半導体層106上の酸化膜を除去し、単結晶半導体層105、単結晶半導体層106、絶縁層110、電荷蓄積層111を覆うゲート絶縁層109を形成する。メモリセルアレイにおいてはゲート絶縁層109の膜厚が厚いと、薄膜トランジスタ及びメモリ素子の高電圧に対する耐性が高くすることができ、信頼性を高めることができる。

30

## 【0273】

なお、単結晶半導体層105の上方に形成されたゲート絶縁層109は、後に完成するメモリ素子においてコントロール絶縁層として機能するが、単結晶半導体層106上に形成される薄膜トランジスタにおいてはゲート絶縁層として機能するために本明細書では、ゲート絶縁層109とよぶこととする。

## 【0274】

本発明の半導体装置において、メモリセルアレイに設けられる薄膜トランジスタのゲート絶縁層109の膜厚は、50nm以上150nm以下、より好ましくは60nm以上80nm以下とすればよい。

## 【0275】

次いで、ゲート絶縁層109上にゲート電極層を形成する。本実施の形態では、第1の導電膜と第2の導電膜との積層を所望の形状に加工し、第1のゲート電極層114、第2のゲート電極層118、第1の制御ゲート電極層115、及び第2の制御ゲート電極層119を形成する(図7(C)参照。)。

40

## 【0276】

本実施の形態では第1のゲート電極層、第2のゲート電極層(第1の制御ゲート電極層、第2の制御ゲート電極層)を垂直な側面を有して形成する例を示すが、本発明はそれに限定されず、第1のゲート電極層及び第2のゲート電極層(第1の制御ゲート電極層、第2の制御ゲート電極層)両方がテーパー形状を有していてもよいし、どちらか一方のゲート電極層(第1の制御ゲート電極層、第2の制御ゲート電極層)の一層のみがテーパー形状を有し、他方は異方性エッチングによって垂直な側面を有していてもよい。テーパー角度

50

も積層するゲート電極層間で異なっていても良いし、同一でもよい。テーパー形状を有することによって、その上に積層する膜の被覆性が向上し、欠陥が軽減されるので信頼性が向上する。

#### 【0277】

ゲート電極層（及び制御ゲート電極層）を形成する際のエッチング工程によって、ゲート絶縁層108、109は多少エッチングされ、膜厚が減る（いわゆる膜減り）ことがある。

#### 【0278】

本実施の形態のメモリセルアレイに設けられる薄膜トランジスタのチャネル長の長さは1μm～5μm（より好ましくは1μm～3μm）が好ましい。

10

#### 【0279】

次に第1のゲート電極層114a、第2のゲート電極層118、第1の制御ゲート電極層115、及び第2の制御ゲート電極層119をマスクとしてn型を付与する不純物元素163を添加し、n型不純物領域164a、n型不純物領域164b、n型不純物領域127a、n型不純物領域127b、n型不純物領域128a、n型不純物領域128bを形成する。本実施の形態では、不純物元素としてリン（P）を用いる。ここでは、n型不純物領域127a、n型不純物領域127b、n型不純物領域128a、n型不純物領域128bにn型を付与する不純物元素が $5 \times 10^{19} \sim 5 \times 10^{20} / \text{cm}^3$ 程度の濃度で含まれるように添加する。また、単結晶半導体層105にチャネル形成領域130、及び単結晶半導体層106にチャネル形成領域131が形成される（図7（D）参照。）。

20

#### 【0280】

n型不純物領域127a、n型不純物領域127b、n型不純物領域128a、n型不純物領域128bは高濃度n型不純物領域であり、ソース領域、ドレイン領域として機能する。一方、n型不純物領域164a、n型不純物領域164bは低濃度不純物領域であり、LDD（Lightly Doped Drain）領域となる。

#### 【0281】

次いで、ゲート電極層、制御ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、絶縁膜165と絶縁膜166との積層構造とする。絶縁膜165と絶縁膜166は、スパッタ法、またはプラズマCVDを用いた窒化珪素膜、窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の珪素を含む絶縁膜を単層または3層以上の積層構造として用いても良い。

30

#### 【0282】

さらに、窒素雰囲気中で、300～550℃で1～12時間の熱処理を行い、単結晶半導体層を水素化する工程を行う。

#### 【0283】

次いで、レジストからなるマスクを用いて絶縁膜166、絶縁膜167、ゲート絶縁層109、絶縁層110に単結晶半導体層に達するコンタクトホール（開口部）を形成する。エッチングによって、絶縁膜166、絶縁膜167、ゲート絶縁層109、絶縁層110を除去し、ソース領域又はドレイン領域であるn型不純物領域127a、n型不純物領域127b、n型不純物領域128a、n型不純物領域128bに達する開口部を形成する。

40

#### 【0284】

開口部を覆うように導電膜を形成し、導電膜をエッチングして各ソース領域又はドレイン領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層である配線層171a、配線層171b、配線層172a、配線層172bを形成する。

#### 【0285】

以上の工程でメモリセルアレイとしてn型不純物領域を有するメモリ素子175、n型不純物領域を有するnチャネル型薄膜トランジスタである薄膜トランジスタ176を有する半導体素子層151を作製することができる（図7（E）参照。）。

#### 【0286】

50

半導体素子層 151 上に樹脂層 140 を設け、粘着層 141 によって保持基板 142 を接着する（図 8（A）参照。）。

#### 【0287】

剥離層 158 を用いて半導体素子層 151 を基板 160 より剥離する。よって半導体素子層 151 は保持基板側に設けられる。半導体素子層 151 と剥離層 158 との間に形成される無機絶縁膜 159 に残存する剥離層 158 を除去し、無機絶縁膜 159 の平坦な面を露出する（図 8（B）参照。）。凹凸形状に残存する剥離層 158 を無機絶縁膜 159 表面より除去することによって、無機絶縁膜 159 表面は平坦化されるが、さらに無機絶縁膜 159 表面に平坦化処理を行ってもよい。例えば、剥離層 158 としてタンゲステン膜を用いて、無機絶縁膜 159 表面に平坦化処理としてフッ化三塩素ガスによるエッチング処理などを行うことができる。10

#### 【0288】

また、基板 160 上に剥離層 158 を形成後、無機絶縁膜 159 を成膜する前に、剥離層 158 に平坦化処理を行ってもよい。平坦化処理を行った剥離層 158 上に無機絶縁膜 159 を形成すると、剥離層 158 を除去することによって露出する無機絶縁膜 159 の表面の平坦性を高くすることができます。

#### 【0289】

平坦化処理としては、研磨処理やエッチング処理を行えばよく、勿論、研磨処理及びエッチング処理を両方行ってもよい。研磨処理としては、化学的機械研磨（CMP）法や液体ジェット研磨法を用いることができる。エッチング処理としては、ウェットエッチング、ドライエッチング、またはその両方を適宜用いることができる。またプラズマ処理によって平坦化処理を行ってもよい。例えば、逆スパッタリング法を用いることができる。20

#### 【0290】

露出された無機絶縁膜 159 は、他基板で作製された半導体素子層との接合面となるため、本実施の形態では無機絶縁膜 159 に活性化のためのプラズマ処理を行い、表面が改質処理された無機絶縁膜 143 を形成する（図 8（C）参照。）。以上の工程で上層となる半導体素子層 151 の接合前の工程が完了する。

#### 【0291】

作製基板上に無機絶縁膜を介して形成された半導体素子層は剥離層によって作製基板より剥離され、無機絶縁膜が露出する。露出した無機絶縁膜と下層の半導体素子層上に設けられた平坦な無機絶縁層とを接合し、下層の半導体素子層と上層の半導体素子層とを接合する。露出した無機絶縁膜 143 と下層の半導体素子層 150 上に設けられた平坦な無機絶縁層 147 の接合面は少なくともどちらか一方にプラズマ処理を行い活性化すると好ましい。本実施の形態では、接合面両方にプラズマ処理を行う例を示す。30

#### 【0292】

平坦化され、プラズマ処理を施された無機絶縁膜 143 と無機絶縁層 147 とを密着させることにより接合し、下層の半導体素子層 150 と上層の半導体素子層 151 とを積層する（図 9（A）参照。）。

#### 【0293】

表面を活性化するプラズマ処理によって、室温乃至 400 の温度であっても異種材料間の接合を形成することが容易となる。従って低温プロセスで多層構造の半導体装置を作製することができる。また半導体素子層間を接着するために、接着剤などの有機材料を用いず、半導体素子層間を薄膜の無機絶縁層及び無機絶縁膜で接合するため、半導体装置を薄型化、小型化することができる。40

#### 【0294】

次に、樹脂層 140、粘着層 141、及び保持基板 142 を半導体素子層 150 及び半導体素子層 151 積層より剥離し除去する。本実施の形態では、樹脂層 140 に水溶性樹脂を用い、樹脂層を溶解させて除去することによって粘着層 141 及び保持基板 142 を剥離する。樹脂層 140 には他の可溶性樹脂や可塑性樹脂なども用い、化学的、又は物理的に樹脂層 140 を半導体素子層 151 より剥離すればよい。50

## 【0295】

絶縁膜166、絶縁膜165、ゲート絶縁層109、無機絶縁膜143、無機絶縁層147を貫通する開口（コンタクトホール）を形成し、上層の薄膜トランジスタ176と配線層154とを電気的に接続する配線層148を形成する（図9（B）参照。）。配線層148により、上層のメモリセルアレイの半導体素子層151と下層の駆動回路部の半導体素子層150とを電気的に接続することができる。

## 【0296】

半導体素子層151及び配線層148上に樹脂層149を形成し、樹脂層149上に可撓性基板155を設ける。剥離層101を用いて基板100を剥離し、除去する。無機絶縁膜102表面に残存する剥離層はエッティングなどによって除去し、平坦化してもよい。10 無機絶縁膜102を更に他の半導体素子層上に設けられた無機絶縁層と接合する場合は、平坦化することが好ましい。本実施の形態では、無機絶縁膜102と接して可撓性基板156を設け、多層構造の半導体素子層を封止する（図9（C）参照。）。可撓性基板は接着層によって接着して設けてもよい。

## 【0297】

本実施の形態で作製した半導体装置は、可撓性基板上に設けることで、可撓性を有する半導体装置とすることができる。

## 【0298】

チャネル形成領域の膜厚が厚いとチャネル長が短い場合には、ソース - ドレイン間の電界の影響により、ゲート電圧がしきい値電圧以下のサブスレッシュルド領域でチャネル形成領域中の下側を電流が流れる。そのため、サブスレッシュルド値が上昇し、しきい値電圧が低下する。チャネル形成領域の膜厚を薄くすることにより、チャネル形成領域中の下側の電流が流れる経路が遮断されるために、漏れ電流が抑えられる。そのため、サブスレッシュルド値の上昇が抑えられ、しきい値電圧の低下も抑えられる。そのため、チャネル形成領域の膜厚を薄くすることにより、チャネル長の短い領域でのしきい値電圧のマイナスシフトが抑えられ、かつ、サブスレッシュルド値が小さい薄膜トランジスタを作製することができる。サブスレッシュルド値が小さくなっているため、ゲート電圧0Vでのソース - ドレイン間に流れる電流を抑えつつ、しきい値電圧を下げることができる。20

## 【0299】

駆動回路部の半導体素子層における薄膜トランジスタ173、174の単結晶半導体層の薄膜化は、チャネル形成領域の全域を空乏層化するように作用し、短チャネル効果を抑制することができる。また、薄膜トランジスタのしきい値電圧を小さくすることができる。それにより、駆動回路部に設けられた薄膜トランジスタにおいて、微細化と高性能化を実現することができる。よって、半導体装置の低電圧駆動が可能となり低消費電力化を実現することができる。また、薄膜トランジスタは、単結晶半導体層（又は、さらにゲート絶縁層も）を薄膜化することによって、微細化できるため、駆動回路部及び制御回路部の面積の縮小が可能となり、半導体装置をより小型化することができる。30

## 【0300】

一方、メモリセルアレイに設けられたメモリ素子175、薄膜トランジスタ176は、単結晶半導体層（又は、さらにゲート絶縁層も）を駆動回路部と比べ厚く保つことによって、駆動電圧に対する耐圧性が高くすることができる、高信頼性とすることができます。40

## 【0301】

それぞれ他基板に別工程によって作製された半導体素子層を積層して集積化するため、他層の半導体素子層の作製条件に影響を受けず、最適化された条件（材料、膜厚及び素子構造）でそれぞれ特性の高い半導体素子層を形成することができる。従って、複数の半導体素子の多層構造を有する半導体装置も高性能化することができる。

## 【0302】

さらに単結晶半導体基板より分離させ転置した単結晶半導体層を用いるため、単結晶半導体基板を選択することによって、トランジスタにおける結晶面方位及びチャネル長方向の結晶軸を制御することができる。50

**【0303】**

トランジスタのチャネルを流れるキャリアにとって最も移動度が高くなる単結晶半導体層の結晶面方位、結晶軸を適用することにより、キャリアの有効質量が減少し、トランジスタの移動度を向上させることができる。よって、トランジスタの高性能化が可能となる。

**【0304】**

本発明を用いた本実施の形態では、低温プロセスで多層構造の半導体装置を作製することができる。また半導体素子層間を接着するために、接着剤などの有機材料を用いず、半導体素子層間を薄膜の無機絶縁層及び無機絶縁膜で接合するため、半導体装置を薄型化、小型化することができる。

**【0305】**

積層する半導体素子層間に設けられる無機絶縁層が薄膜であるため、単結晶半導体層間に設ける無機絶縁層を貫通して形成される配線層も作製しやすく歩留まりや生産性を高くすることができる。従って、積層する半導体素子同士の電気的接続において、形状不良による電気的不良などを軽減し、信頼性の高い半導体装置を作製することができる。

**【0306】**

従って、本発明の半導体装置は、3次元的に半導体素子を積層し高集積化した構造を有する。従って、半導体装置における半導体素子の配置の自由度が広く、より高集積化、高性能化を達成することができる。半導体素子としては電界効果トランジスタはもちろん、単結晶半導体層を用いる記憶素子なども適用することができ、多用途に渡って要求される機能を満たす半導体装置を作製し、提供することができる。

10

**【0307】****(実施の形態6)**

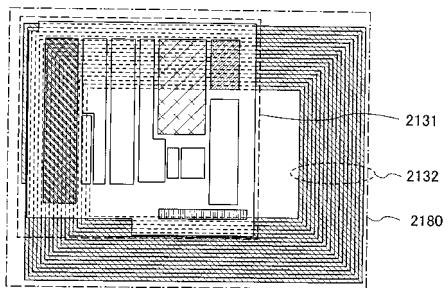

本実施の形態では、より高集積化、薄型化、及び小型化を付与することを目的とした半導体装置の例について説明する。詳しくは半導体装置の一例として、マイクロプロセッサ及び非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について説明する。

**【0308】**

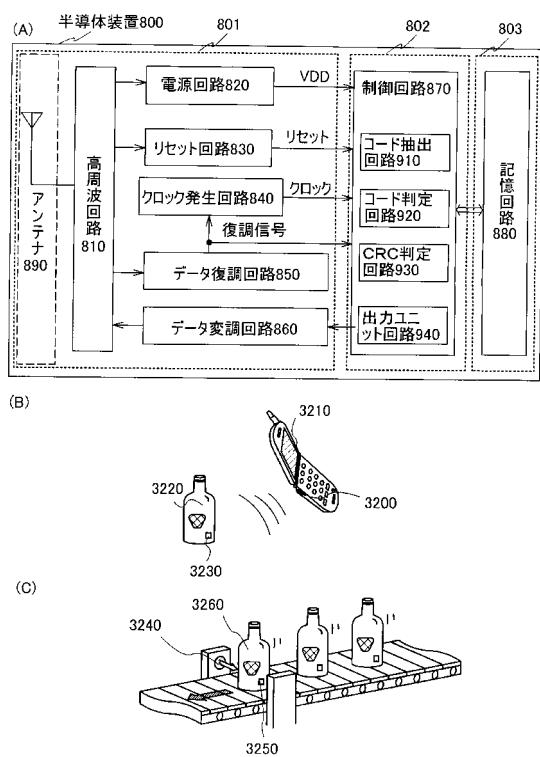

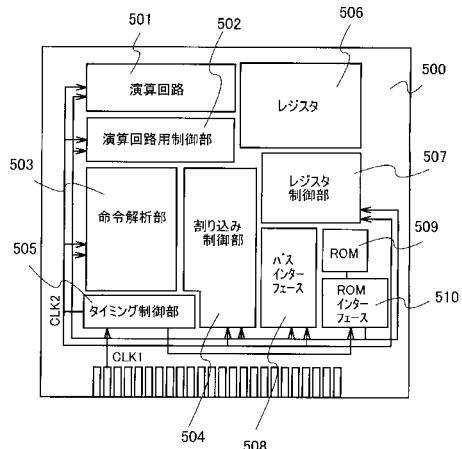

図15は半導体装置の一例として、マイクロプロセッサ500の一例を示す。このマイクロプロセッサ500は、上記実施の形態に係る半導体装置により製造されるものである。このマイクロプロセッサ500は、演算回路501(Arithmetic logic unit。ALUともいう。)、演算回路制御部502(ALU Controller)、命令解析部503(Instruction Decoder)、割り込み制御部504(Interrupt Controller)、タイミング制御部505(Timing Controller)、レジスタ506(Register)、レジスタ制御部507(Register Controller)、バスインターフェース508(Bus I/F)、読み出し専用メモリ509、及びメモリインターフェース510(ROM I/F)を有している。

20

**【0309】**

バスインターフェース508を介してマイクロプロセッサ500に入力された命令は、命令解析部503に入力され、デコードされた後、演算回路制御部502、割り込み制御部504、レジスタ制御部507、タイミング制御部505に入力される。演算回路制御部502、割り込み制御部504、レジスタ制御部507、タイミング制御部505は、デコードされた命令に基づき各種制御を行う。具体的に演算回路制御部502は、演算回路501の動作を制御するための信号を生成する。また、割り込み制御部504は、マイクロプロセッサ500のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタ制御部507は、レジスタ506のアドレスを生成し、マイクロプロセッサ500の状態に応じてレジスタ506の読み出しや書き込みを行う。タイミング制御部505は、演算回路501、演算回路制御部502、命令解析部503、割り込み制御部504、レジスタ制御部507の動作のタイミングを制御する信号を生成する。例えばタイミング制御部505は、基準クロック

30

40

50

ク信号 C L K 1 を元に、内部クロック信号 C L K 2 を生成する内部クロック生成部を備えており、クロック信号 C L K 2 を上記各種回路に供給する。なお、図 15 に示すマイクロプロセッサ 500 は、その構成を簡略化して示した一例にすぎず、実際にはその用途によって多種多様な構成を備えることができる。

#### 【 0 3 1 0 】

マイクロプロセッサ 500において、演算回路 501 及び演算回路用制御部 502 は半導体素子層 551 に形成されており、レジスタ 506 及びレジスタ制御部 507 は半導体素子層 552 に形成されており、命令解析部 503、割り込み制御部 504、タイミング制御部 505、及びバスインターフェース 508 は半導体素子層 553 に形成されており、ROM 509 及び ROM インターフェース 510 は半導体素子層 554 に形成されている。本発明を用いて、別々の作製基板において形成された半導体素子層 551、半導体素子層 552、半導体素子層 553、及び半導体素子層 554 が多層構造に積層され、積層を貫通する配線層によって電気的に接続されている。10

#### 【 0 3 1 1 】

それぞれ他基板に別工程によって作製された半導体素子層を積層して集積化するため、他層の半導体素子層の作製条件に影響を受けず、最適化された条件（材料、膜厚及び素子構造）でそれぞれ特性の高い半導体素子層を形成することができる。従って、複数の半導体素子の多層構造を有する半導体装置も高性能化することができる。

#### 【 0 3 1 2 】

このようなマイクロプロセッサ 500 は、基板上に接合された結晶方位が一定の単結晶半導体層によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。20

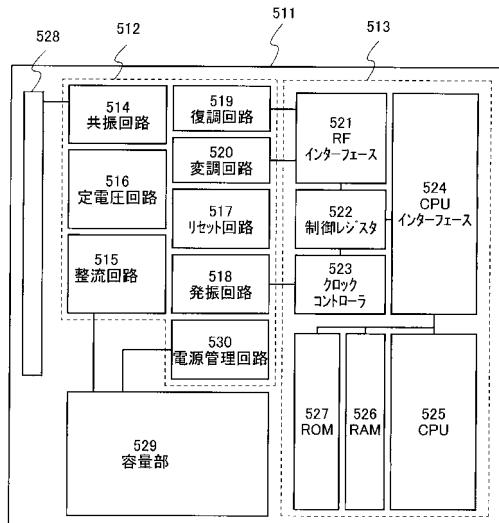

#### 【 0 3 1 3 】

次に、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について図 16 を参照して説明する。図 16 は無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「R F C P U」という）の一例を示す。R F C P U 511 は、アナログ回路部 512 とデジタル回路部 513 を有している。アナログ回路部 512 として、共振容量を有する共振回路 514、整流回路 515、定電圧回路 516、リセット回路 517、発振回路 518、復調回路 519 と、変調回路 520 を有している。デジタル回路部 513 は、R F インターフェース 521、制御レジスタ 522、クロックコントローラ 523、インターフェース 524、中央処理ユニット 525、ランダムアクセスメモリ 526、読み出し専用メモリ 527 を有している。30

#### 【 0 3 1 4 】

このような構成の R F C P U 511 の動作は概略以下の通りである。アンテナ 528 が受信した信号は共振回路 514 により誘導起電力を生じる。誘導起電力は、整流回路 515 を経て容量部 529 に充電される。この容量部 529 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部 529 は R F C P U 511 と一緒に形成されている必要はなく、別部品として R F C P U 511 を構成する絶縁表面を有する基板に取り付けられていれば良い。

#### 【 0 3 1 5 】

リセット回路 517 は、デジタル回路部 513 をリセットし初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 518 は、定電圧回路 516 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。ローパスフィルタで形成される復調回路 519 は、例えば振幅変調（A S K）方式の受信信号の振幅の変動を二値化する。変調回路 520 は、送信データを振幅変調（A S K）方式の送信信号の振幅を変動させて送信する。変調回路 520 は、共振回路 514 の共振点を変化させることで通信信号の振幅を変化させている。クロックコントローラ 523 は、電源電圧又は中央処理ユニット 525 における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 530 が行っている。4050

**【 0 3 1 6 】**

アンテナ 5 2 8 から R F C P U 5 1 1 に入力された信号は復調回路 5 1 9 で復調された後、R F インターフェース 5 2 1 で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ 5 2 2 に格納される。制御コマンドには、読み出し専用メモリ 5 2 7 に記憶されているデータの読み出し、ランダムアクセスメモリ 5 2 6 へのデータの書き込み、中央処理ユニット 5 2 5 への演算命令などが含まれている。中央処理ユニット 5 2 5 は、インターフェース 5 2 4 を介して読み出し専用メモリ 5 2 7 、ランダムアクセスメモリ 5 2 6 、制御レジスタ 5 2 2 にアクセスする。インターフェース 5 2 4 は、中央処理ユニット 5 2 5 が要求するアドレスより、読み出し専用メモリ 5 2 7 、ランダムアクセスメモリ 5 2 6 、制御レジスタ 5 2 2 のいずれかに対するアクセス信号を生成する機能を有している。

10

**【 0 3 1 7 】**

中央処理ユニット 5 2 5 の演算方式は、読み出し専用メモリ 5 2 7 に O S (オペレーティングシステム) を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、残りの演算をプログラムを使って中央処理ユニット 5 2 5 が実行する方式を適用することができる。

**【 0 3 1 8 】**

R F C P U 5 1 1 において、共振回路 5 1 4 、定電圧回路 5 1 6 、整流回路 5 1 5 、復調回路 5 1 9 、変調回路 5 2 0 、リセット回路 5 1 7 、発振回路 5 1 8 、電源管理回路 5 3 0 、容量部 5 2 9 、及びアンテナ 5 2 8 は半導体素子層 5 6 1 に形成されており、R F インターフェース 5 2 1 、制御レジスタ 5 2 2 、クロックコントローラ 5 2 3 、C P U インターフェース 5 2 4 、C P U 5 2 5 、R A M 5 2 6 、及びR O M 5 2 7 は半導体素子層 5 6 2 に形成されている。本発明を用いて、別々の作製基板において形成された半導体素子層 5 6 1 、及び半導体素子層 5 6 2 が多層構造に積層され、積層を貫通する配線層によって電気的に接続されている。

20

**【 0 3 1 9 】**

それぞれ他基板に別工程によって作製された半導体素子層を積層して集積化するため、他層の半導体素子層の作製条件に影響を受けず、最適化された条件(材料、膜厚及び素子構造)でそれぞれ特性の高い半導体素子層を形成することができる。従って、複数の半導体素子の多層構造を有する半導体装置も高性能化することができる。

30

**【 0 3 2 0 】**

また、半導体装置において回路や構造の変更を行いたい場合、各半導体素子層毎で対応することができるため、半導体装置の設計において非常に広い選択性を有することができる。

**【 0 3 2 1 】**

このような R F C P U 5 1 1 は、基板上に接合されたそれぞれ結晶面方位が一定の単結晶半導体層によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。それにより、電力を供給する容量部 5 2 9 を小型化しても長時間の動作を保証することができる。

40

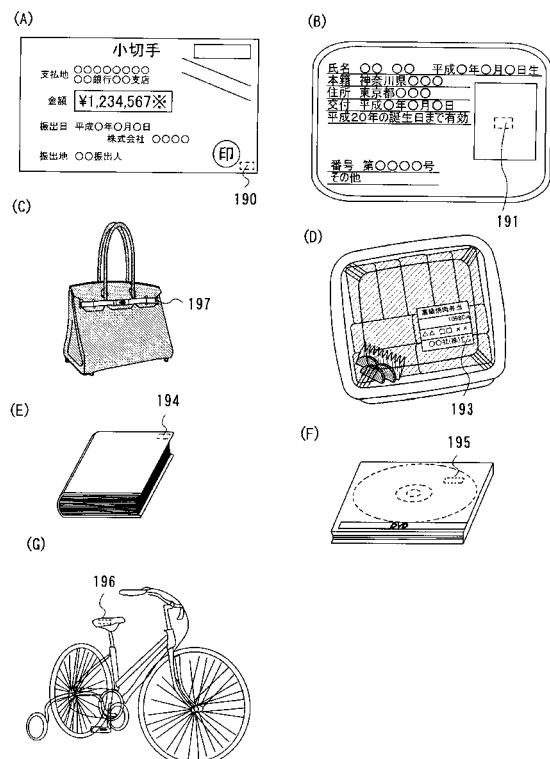

**【 0 3 2 2 】****( 実施の形態 7 )**

本実施の形態では、上記実施の形態で示した半導体装置の使用形態の一例について説明する。具体的には、非接触でデータの入出力が可能である半導体装置の適用例に関して、図面を用いて以下に説明する。非接触でデータの入出力が可能である半導体装置は利用の形態によって、R F I D タグ、I D タグ、I C タグ、I C チップ、R F タグ、無線タグ、電子タグまたは無線チップとも呼ばれる。

**【 0 3 2 3 】**

本実施の形態で示す半導体装置の上面構造の一例について、図 1 2 を参照して説明する。

50

図12に示す半導体装置2180は、メモリ部やロジック部を構成する複数のトランジスタ等の素子が設けられた薄膜集積回路2131と、アンテナとして機能する導電層2132を含んでいる。アンテナとして機能する導電層2132は、薄膜集積回路2131に電気的に接続されている。薄膜集積回路2131には、上記実施の形態1で示したトランジスタを適用することができる。

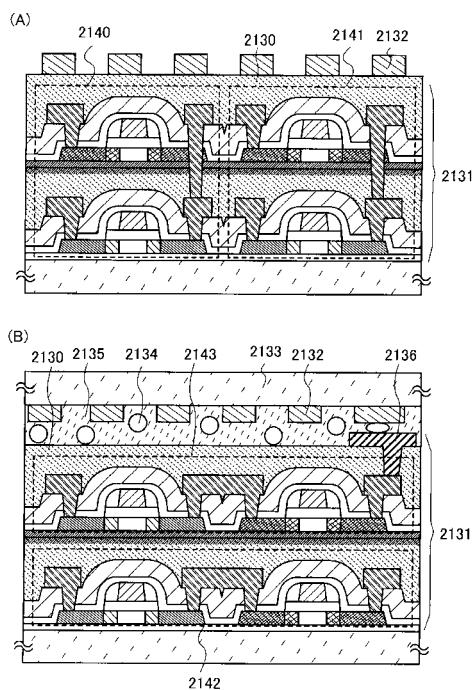

#### 【0324】

また、図13(A)、(B)に図12の断面の模式図を示す。アンテナとして機能する導電層2132は、メモリ部及びロジック部を構成する素子の上方に設ければよく、例えば、上記実施の形態で示した電界効果トランジスタと同様に作製することのできるCMOS構造2140、2141の上方に、絶縁層2130を介してアンテナとして機能する導電層2132を設けることができる(図13(A)参照)。他にも、アンテナとして機能する導電層2132を基板2133に別に設けた後、当該基板2133及び薄膜集積回路2131を、導電層2132が間に位置するように貼り合わせて設けることができる(図13(B)参照)。図13(B)では、絶縁層2130上に設けられた導電層2136とアンテナとして機能する導電層2132とが、接着性を有する樹脂2135中に含まれる導電性粒子2134を介して電気的に接続されている例を示す。

10

#### 【0325】

本実施の形態で示す半導体装置の断面構造を図13(A)(B)に示す。CMOS構造2140、2141、2142、2143に含まれるトランジスタは、サイドウォール構造の側壁絶縁層を有しており、単結晶半導体層にチャネル形成領域と高濃度不純物領域であるソース領域及びドレイン領域との間に低濃度不純物領域を含んでいる。CMOS構造2140、2141は積層する下層のトランジスタと上層のトランジスタとによって形成されており、CMOS構造2142、2143は同じ無機絶縁膜に接して並列して形成されたトランジスタによって形成され、CMOS構造2142及びCMOS構造2143が積層する例である。本実施の形態における半導体装置は半導体素子層の積層による多層構造である。作製基板上に無機絶縁膜を介して形成された半導体素子層は剥離層によって作製基板より剥離され、無機絶縁膜が露出する。露出した無機絶縁膜と下層の半導体素子層上に設けられた平坦な無機絶縁層とを接合し、下層の半導体素子層と上層の半導体素子層とを接合する。露出した無機絶縁膜と下層の半導体素子層上に設けられた平坦な無機絶縁層の接合面は少なくともどちらか一方は活性化のためのプラズマ処理を行うことが好ましい。本実施の形態では、接合面両方にプラズマ処理を行う例を示す。

20

#### 【0326】

本実施の形態において、CMOS構造2140、2141、2142、2143に含まれるトランジスタの単結晶半導体層は、作製工程において単結晶半導体基板より分離されて作製基板に転置された単結晶半導体層である。本実施の形態では、単結晶半導体層と無機絶縁膜との間に絶縁層を設けずに、単結晶半導体層と無機絶縁膜とが直接接合する構成となっている。このように、単結晶半導体層と無機絶縁膜との間に接合を強固にするために設ける絶縁層は、設けても設けなくてもよい。

30

#### 【0327】

従って、本発明を用いた本実施の形態では、低温プロセスで多層構造の半導体装置を作製することができる。また半導体素子層間を接着するために、接着剤などの有機材料を用いず、半導体素子層間を薄膜の無機絶縁層及び無機絶縁膜で接合するため、半導体装置を薄型化、小型化することができる。

40

#### 【0328】

積層する半導体素子層間に設けられる無機絶縁層が薄膜であるため、単結晶半導体層間に設ける無機絶縁層を貫通して形成される配線層も作製しやすく歩留まりや生産性を高くすることができる。従って、積層する半導体素子同士の電気的接続において、形状不良による電気的不良などを軽減し、信頼性の高い半導体装置を作製することができる。

#### 【0329】

さらに単結晶半導体基板より分離させ転置した単結晶半導体層を用いるため、単結晶半導

50

体基板を選択することによって、トランジスタにおける結晶面方位及びチャネル長方向の結晶軸を制御することができる。

#### 【0330】

トランジスタのチャネルを流れるキャリアにとって最も移動度が高くなる単結晶半導体層の結晶面方位、結晶軸を適用することにより、キャリアの有効質量が減少し、トランジスタの移動度を向上させることができる。よって、トランジスタの高性能化が可能となる。

#### 【0331】

また、それぞれ他基板に別工程によって作製された半導体素子層を積層して集積化するため、他層の半導体素子層の作製条件に影響を受けず、最適化された条件（材料、膜厚及び素子構造）でそれぞれ特性の高い半導体素子層を形成することができる。従って、複数の半導体素子の多層構造を有する半導体装置も高性能化することができる。10

#### 【0332】

従って、本発明の半導体装置は、3次元的に半導体素子を積層し高集積化した構造を有する。従って、半導体装置における半導体素子の配置の自由度が広く、より高集積化、高性能化を達成することができる。半導体素子としては電界効果トランジスタはもちろん、単結晶半導体層を用いる記憶素子なども適用することができ、多用途に渡って要求される機能を満たす半導体装置を作製し、提供することができる。

#### 【0333】

なお、本実施の形態では、アンテナとして機能する導電層2132をコイル状に設け、電磁誘導方式または電磁結合方式を適用する例を示すが、本発明の半導体装置はこれに限られずマイクロ波方式を適用することも可能である。マイクロ波方式の場合は、用いる電磁波の波長によりアンテナとして機能する導電層2132の形状を適宜決めればよい。20

#### 【0334】