(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-77424

(P2005-77424A)

(43) 公開日 平成17年3月24日(2005.3.24)

(51) Int.Cl.<sup>7</sup>

GO2F 1/1368

GO2F 1/1343

F |

GO 2 F 1/1368

GO2F 1/1343

### テーマコード（参考）

2 H 0 9 2

審査請求 未請求 請求項の数 11 O.L. (全 16 頁)

|           |                              |            |                                                       |

|-----------|------------------------------|------------|-------------------------------------------------------|

| (21) 出願番号 | 特願2003-209552 (P2003-209552) | (71) 出願人   | 502356528                                             |

| (22) 出願日  | 平成15年8月29日 (2003.8.29)       |            | 株式会社 日立ディスプレイズ<br>千葉県茂原市早野3300番地                      |

|           |                              | (74) 代理人   | 100083552<br>弁理士 秋田 収喜                                |

|           |                              | (72) 発明者   | 小野 記久雄<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内           |

|           |                              | (72) 発明者   | 桶 隆太郎<br>千葉県茂原市早野3300番地 株式会社<br>日立ディスプレイズ内            |

|           |                              | F ターム (参考) | 2H092 GA14 HA04 JA24 JB42 JB57<br>JB68 JB69 NA22 PA09 |

(54) 【発明の名称】 液晶表示装置

(57) 【要約】

【課題】薄膜トランジスタのゲート電位がオンからオフに変化する際に、画素電極の電位が著しく低下してしまう動作点悪化の不都合を解消した液晶表示装置を得る。

【解決手段】基板上の画素領域に、第1スイッチング素子を介して信号が供給される第1電極と、第2スイッチング素子を介して信号が供給される第2電極とを備え、該第1電極と第2電極の間の電位差で液晶を挙動させるものであって、

第1電極は、外部からの電源線との間に絶縁膜を介して構成される第1保持容量素子の一方の電極とともに、第2電極は、外部からの電源線との間に絶縁膜を介して構成される第2保持容量素子の一方の電極とする。

## 【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

基板上の画素領域に、第1スイッチング素子を介して信号が供給される第1電極と、第2スイッチング素子を介して信号が供給される第2電極とを備え、該第1電極と第2電極の間の電位差で液晶を挙動させるものであって、

第1電極は、外部からの電源線との間に絶縁膜を介して構成される第1保持容量の一方の電極とともに、第2電極は、外部からの電源線との間に絶縁膜を介して構成される第2保持容量の一方の電極とすることを特徴とする液晶表示装置。

**【請求項 2】**

第1電極と第2電極は透光性の導電膜で構成され、それらは絶縁膜を介して異なる層として形成されているとともに、一方の電極は画素領域の大部分の領域に形成され、他方の電極は該一方の電極に重ねられた電極群によって形成されていることを特徴とする請求項1に記載の液晶表示装置。 10

**【請求項 3】**

第1保持容量の他方の電極を構成する外部からの電源線は第1ドレイン信号線であり、第2保持容量の他方の電極を構成する外部からの電源線は第2ドレイン信号線であることを特徴とする請求項1、2のいずれかに記載の液晶表示装置。

**【請求項 4】**

第1保持容量の他方の電極を構成する外部からの電源線と第2保持容量の他方の電極を構成する外部からの電源線は容量信号線であることを特徴とする請求項1、2のいずれかに記載の液晶表示装置。 20

**【請求項 5】**

基板上の画素領域に、第1ドレイン信号線から第1スイッチング素子を介して信号が供給される第1電極と、第2ドレイン信号線から第2スイッチング素子を介して信号が供給される第2電極とを備え、該第1電極と第2電極の間の電位差で液晶を挙動させるものであって、

前記第1電極および第2電極は、前記第1ドレイン信号線および第2ドレイン信号線に対して絶縁膜を介して異なる層に形成されているとともに、

その一部が前記第1ドレイン信号線および第2ドレイン信号線に重ねられて構成されていることを特徴とする液晶表示装置。 30

**【請求項 6】**

第1電極はその一部において前記第1ドレイン信号線および第2ドレイン信号線のそれぞれと重ねられて構成され、第2電極はその一部において前記第1ドレイン信号線および第2ドレイン信号線のそれぞれと重ねられて構成されていることを特徴とする請求項5に記載の液晶表示装置。

**【請求項 7】**

第1電極の第1ドレイン信号線と重ねられる部分と第2電極の第1ドレイン信号線と重ねられる部分はほぼ同じ個所であり、第1電極の第2ドレイン信号線と重ねられる部分と第2電極の第2ドレイン信号線と重ねられる部分はほぼ同じ個所であることを特徴とする請求項6に記載の液晶表示装置。 40

**【請求項 8】**

第1電極の第1ドレイン信号線と重ねられる部分、第2電極の第1ドレイン信号線と重ねられる部分、第1電極の第2ドレイン信号線と重ねられる部分、それぞれ第2電極の第2ドレイン信号線と重ねられる部分は、それぞれ保持保持容量を構成することを特徴とする請求項6、7のいずれかに記載の液晶表示装置。

**【請求項 9】**

第1電極の第1ドレイン信号線と重ねられる部分の保持保持容量の容量値と第1電極の第2ドレイン信号線と重ねられる部分の保持保持容量の容量値はほぼ等しく、かつ、第2電極の第1ドレイン信号線と重ねられる部分の保持保持容量の容量値と第2電極の第2ドレイン信号線と重ねられる部分の保持保持容量の容量値はほぼ等しいことを特徴とする請求 50

項 8 に記載の液晶表示装置。

【請求項 10】

第 1 保持保持容量と第 2 保持保持容量のそれぞれの容量値はほぼ等しいことを特徴とする請求項 4 に記載の液晶表示装置。

【請求項 11】

第 1 電極と第 2 電極は透光性の導電膜で構成され、それらは絶縁膜を介して異なる層として形成されているとともに、一方の電極は画素領域の大部分の領域に形成され、他方の電極は該一方の電極に重ねられた電極群によって形成されていることを特徴とする請求項 5 に記載の液晶表示装置。

【発明の詳細な説明】

10

【0001】

【発明の属する技術分野】

本発明は液晶表示装置に関する。

【0002】

【従来の技術】

液晶を介して対向配置される各基板のうち一方の基板の液晶側の各画素領域に、画素電極と対向電極とを備え、これら各電極との間に基板とほぼ平行な電界を発生せしめて当該画素領域の液晶の光透過率を制御するものが知られている。

【0003】

20

このうち、前記各電極はそれぞれ絶縁膜を介して配置され、そのうちの一方の電極は画素領域の周辺を除く中央部の全域に形成されているとともに、他方の電極は該一方の電極に重ね合わされていわゆる櫛歯状の電極群として形成され、かつこれらの電極は透光性の導電層で構成したものが知られている。

【0004】

このような液晶表示装置はたとえば特許文献 1 に開示され、いわゆるインプレーンスイッチング型の液晶表示装置と称されている。

【0005】

30

また、上記構成において、一方の電極にはゲート信号線からの走査信号によってオンされる第 1 の薄膜トランジスタを介して第 1 のドレイン信号線からの第 1 の映像信号が供給されるとともに、他方の電極にはやはり前記走査信号によってオンされる第 2 の薄膜トランジスタを介して第 2 のドレイン信号線からの第 2 の映像信号が供給されるように構成したものが特許文献 2 に開示されている。

【0006】

このように構成された液晶表示装置は、一つの画素中に設けた 2 個の薄膜トランジスタに對して、2 本のドレイン信号線を配置し、一方の薄膜トランジスタには一方のドレイン信号線からの一方の電圧を、他方の薄膜トランジスタには他方のトレンイン信号線からの他方の電圧を印加し、これらの 2 つの電圧のほぼ中点電位に相当する基準電位に対して、一方の電圧を正極に、他方の電圧を負極にして、これらを 1 つのフレーム期間の電圧としている。

【0007】

40

この動作により、画素内の方の電極と他方の電極の差電圧が液晶に印加され、これに液晶電圧の交流化のために次のフレーム期間には一方の電極と他方の電極の極性を入れ替えるようにしている。

【0008】

これにより、たとえば 1 画素中に 1 個の薄膜トランジスタを配置させたインプレーンスイッチング型で該薄膜トランジスタに接続された画素電極の電位を他方の電極の電位に対して上下に交流化した方式のものに比べ、交流化された差電圧をほぼ半分にできることになる。

【0009】

このことから、液晶の駆動電圧を低減でき低消費電力の液晶表示装置を得ることができる

50

。

【0010】

【特許文献1】

特開2002-90781号公報

【特許文献2】

特開2000-338462号公報

【0011】

【発明が解決しようとする課題】

しかしながら、このような構成であっても、液晶表示装置の画面が大型化した場合、消費電力が増加することはもちろんのこと、画素電極を一方の電極としゲート信号線あるいは容量信号線を他方の電極とする保持保持容量の値が増加し、これが表示パターンによって一方の極性のみを充電するモードとなって該ゲート信号線あるいは容量信号線の配線遅延が増加し、背景に対して四角ウインドウパターンを表示した際に該ゲート信号線あるいは容量信号線の方向にいわゆるクロストークと称される帯状の影ができてしまうということが指摘されている。10

【0012】

一方、一画素中に2個の薄膜トランジスタを形成した上記従来の液晶表示装置は、一方の電極と他方の電極を絶縁膜を介して積層させた構造の容量素子を備えたものである。この構造からなる液晶表示装置は、ゲート信号線とたとえば平行に配置された固定の電位が印加される容量信号線がなく、上述したクロストークは発生しない。しかし、該容量素子は、2個の各薄膜トランジスタの出力電圧を前記の各電極に接続されただけの構成となっている。このため、薄膜トランジスタにゲートオフ電圧が印加されている保持期間中において該容量素子の電位はフローティング状態となって固定されておらず、他の電位を有するゲート信号線等との間の寄生容量に応じて振られてしまうという不都合が生じる。20

【0013】

特に、該薄膜トランジスタのゲート電位がオンからオフに変化する際に、ゲート信号線の一部で構成されるゲート電極とソース電極との間に発生する寄生容量によって電極電位が著しく低下してしまうという動作点悪化の不都合が発生することが本発明者自らの実験で明らかになっている。30

【0014】

さらに、上記各2個の薄膜トランジスタからの出力電圧をそれぞれ電極へ伝達させ、これをゲート信号線と同層の配線で構成された容量信号線と絶縁膜を介して該電極の間に容量素子を構成することを考えた場合、容量信号線が下層にそれぞれの電極を上層に配置することによってのいわゆる画素の開口率の低下を免れ得ない。30

【0015】

本発明は、このような事情に基づいてなされたものであり、その目的は、薄膜トランジスタのゲート電位がオンからオフに変化する際に、画素電極の電位が著しく低下してしまう動作点悪化の不都合を解消した液晶表示装置を提供することにある。40

【0016】

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。40

【0017】

手段1.

本発明による液晶表示装置は、たとえば、基板上の画素領域に、第1スイッチング素子を介して信号が供給される第1電極と、第2スイッチング素子を介して信号が供給される第2電極とを備え、該第1電極と第2電極の間の電位差で液晶を挙動させるものであって、第1電極は、外部からの電源線との間に絶縁膜を介して構成される第1保持容量素子の一方の電極とともに、第2電極は、外部からの電源線との間に絶縁膜を介して構成される第2保持容量素子の一方の電極とすることを特徴とするものである。50

**【 0 0 1 8 】**

手段 2 .

本発明による液晶表示装置は、たとえば、手段 1 の構成を前提とし、第 1 電極と第 2 電極は透光性の導電膜で構成され、それらは絶縁膜を介して異なる層として形成されているとともに、一方の電極は画素領域の大部分の領域に形成され、他方の電極は該一方の電極に重ねられた電極群によって形成されていることを特徴とするものである。

**【 0 0 1 9 】**

手段 3 .

本発明による液晶表示装置は、たとえば、手段 1 、 2 のいずれかの構成を前提とし、第 1 保持容量の他方の電極を構成する外部からの電源線は第 1 ドレイン信号線であり、第 2 保持容量の他方の電極を構成する外部からの電源線は第 2 ドレイン信号線であることを特徴とするものである。 10

**【 0 0 2 0 】**

手段 4 .

本発明による液晶表示装置は、たとえば、手段 1 、 2 のいずれかの構成を前提とし、第 1 保持容量の他方の電極を構成する外部からの電源線と第 2 保持容量の他方の電極を構成する外部からの電源線は容量信号線であることを特徴とするものである。

**【 0 0 2 1 】**

手段 5 .

本発明による液晶表示装置は、たとえば、基板上の画素領域に、第 1 ドレイン信号線から第 1 スイッチング素子を介して信号が供給される第 1 電極と、第 2 ドレイン信号線から第 2 スイッチング素子を介して信号が供給される第 2 電極とを備え、該第 1 電極と第 2 電極の間の電位差で液晶を挙動させるものであって、 20

前記第 1 電極および第 2 電極は、前記第 1 ドレイン信号線および第 2 ドレイン信号線に対して絶縁膜を介して異なる層に形成されているとともに、

その一部が前記第 1 ドレイン信号線および第 2 ドレイン信号線に重ねられて構成されていることを特徴とするものである。

**【 0 0 2 2 】**

手段 6 .

本発明による液晶表示装置は、たとえば、手段 5 の構成を前提とし、第 1 電極はその一部において前記第 1 ドレイン信号線および第 2 ドレイン信号線のそれぞれと重ねられて構成され、第 2 電極はその一部において前記第 1 ドレイン信号線および第 2 ドレイン信号線のそれぞれと重ねられて構成されていることを特徴とするものである。 30

**【 0 0 2 3 】**

手段 7 .

本発明による液晶表示装置は、たとえば、手段 6 の構成を前提とし、第 1 電極の第 1 ドレイン信号線と重ねられる部分と第 2 電極の第 1 ドレイン信号線と重ねられる部分はほぼ同じ個所であり、第 1 電極の第 2 ドレイン信号線と重ねられる部分と第 2 電極の第 2 ドレイン信号線と重ねられる部分はほぼ同じ個所であることを特徴とするものである。

**【 0 0 2 4 】**

手段 8 .

本発明による液晶表示装置は、たとえば、手段 6 、 7 のいずれかの構成を前提とし、第 1 電極の第 1 ドレイン信号線と重ねられる部分、第 2 電極の第 1 ドレイン信号線と重ねられる部分、第 1 電極の第 2 ドレイン信号線と重ねられる部分、それぞれ第 2 電極の第 2 ドレイン信号線と重ねられる部分は、それぞれ保持容量素子を構成することを特徴とするものである。 40

**【 0 0 2 5 】**

手段 9 .

本発明による液晶表示装置は、たとえば、手段 8 の構成を前提とし、第 1 電極の第 1 ドレイン信号線と重ねられる部分の保持容量素子の容量値と第 1 電極の第 2 ドレイン信号線と 50

重ねられる部分の保持容量素子の容量値はほぼ等しく、かつ、第2電極の第1ドレイン信号線と重ねられる部分の保持容量素子の容量値と第2電極の第2ドレイン信号線と重ねられる部分の保持容量素子の容量値はほぼ等しいことを特徴とするものである。

【0026】

手段10.

本発明による液晶表示装置は、たとえば、手段4の構成を前提とし、第1保持容量素子と第2保持容量素子のそれぞれの容量値はほぼ等しいことを特徴とするものである。

【0027】

手段11.

本発明による液晶表示装置は、たとえば、手段5の構成を前提とし、第1電極と第2電極は透光性の導電膜で構成され、それらは絶縁膜を介して異なる層として形成されているとともに、一方の電極は画素領域の大部分の領域に形成され、他方の電極は該一方の電極に重ねられた電極群によって形成されていることを特徴とするものである。 10

【0028】

なお、本発明は以上の構成に限定されず、本発明の技術思想を逸脱しない範囲で種々の変更が可能である。

【0029】

【発明の実施の形態】

以下、本発明による液晶表示装置の実施例を図面を用いて説明をする。

【0030】

実施例1.

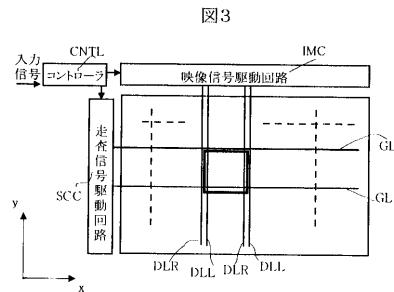

図3は、本発明による液晶表示装置の一実施例を示す平面図である。まず、液晶を介して互いに対向配置される各基板のうち一方の基板G L S 1の液晶側の面には、そのx方向に延在しy方向に並設されるゲート信号線G Lが形成され、また、y方向に延在しx方向に並設されるドレイン信号線D Lが形成されている。 20

【0031】

ここで、これら各ドレイン信号線D Lは、その隣接方向に近接、遠接、近接、……を繰り返して配置され、これにより、隣接される一対のゲート信号線G Lと遠接される一対のドレイン信号線D Lとで囲まれた矩形の領域（図中太字で囲まれた部分）を画素領域として形成される。 30

【0032】

各画素領域には、その画素領域における画素を含んでx方向に並設される画素群を選択するたとえば図中下側のゲート信号線G Lからの走査信号が供給されるとともに、図中左側のドレイン信号線D L（第1のドレイン信号線D L L）からの第1の映像信号と図中右側のドレイン信号線D L（第2のドレイン信号線D L R）からの第2の映像信号とが供給されるようになっている。この画素領域の詳細な構成は後に詳述する。

【0033】

前記各ゲート信号線G Lは、例えばその一端において走査信号駆動回路S C Cに接続され、この走査信号駆動回路S C Cによって、順次走査信号が供給されるようになっている。また、ドレイン信号線D Lは、たとえばその一端において映像信号駆動回路I M Cに接続され、この映像信号駆動回路I M Cによって、前記走査信号の供給のタイミングに合わせて映像信号が供給されるようになっている。 40

【0034】

なお、走査信号駆動回路S C Cおよび映像信号駆動回路I M Cには、コントローラC N T Lからの信号によって駆動され、該コントローラC N T Lには外部から画像信号等の入力信号が供給されるようになっている。

【0035】

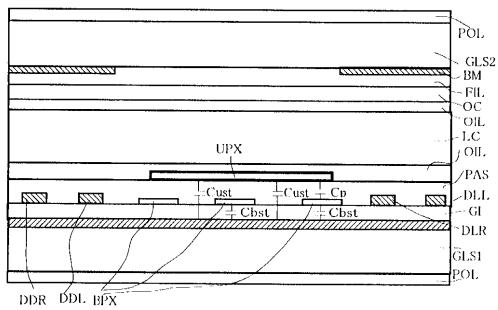

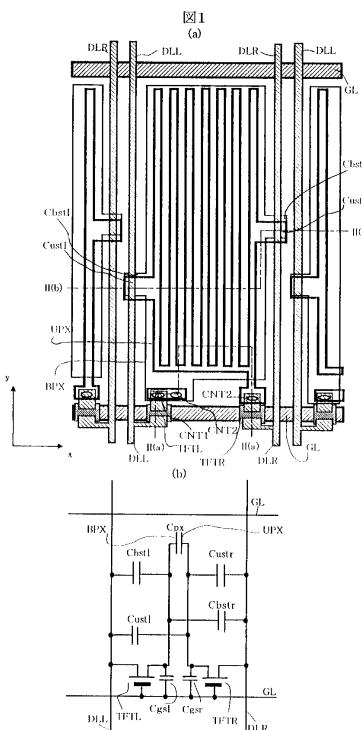

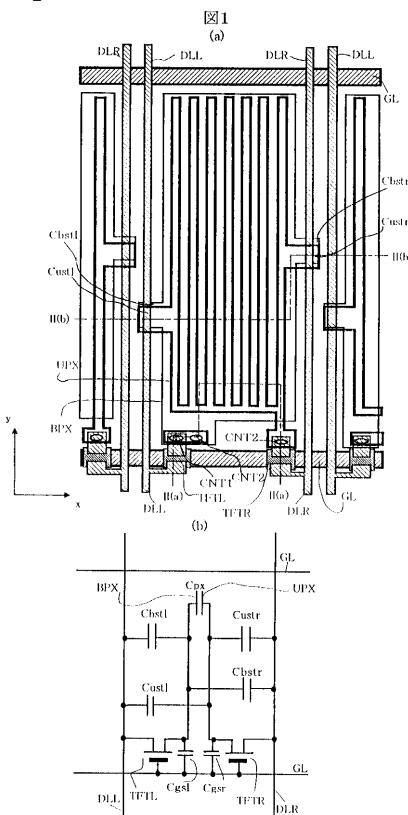

図1(a)は前記画素領域における構成の一実施例を示す平面図である。また、図1(b)は図1(a)の構成と幾何学的に対応させて描いた等価回路図である。さらに、図2(a)は図1(a)のI I (a) - I I (a)における断面図、図2(b)は図1(a)の 50

I I ( b ) - I I ( b ) における断面図を示している。

【 0 0 3 6 】

まず、たとえば透明基板 G L S 1 の表面にその x 方向に延在し y 方向に並設されるゲート信号線 G L が形成されている。このゲート信号線 G L は後述する第 1 のドレイン信号線 D L L 、第 2 のドレイン信号線 D L R とで画素領域を囲むようにして形成されるようになっている。

【 0 0 3 7 】

該画素領域にはその僅かな周辺を除く中央部の領域の全域にわたって第 1 の画素電極 B P X が形成され、この第 1 の画素電極 B P X のゲート信号線 G L と直行する方向の各辺のそれぞれの一部には該ゲート信号線 G L の延在方向と平行に延在する延在部が形成され、それぞれの延在部は後述する第 1 のドレイン信号線 D L L 、および第 2 のドレイン信号線 D L R に重ねられるようにして形成されている。

【 0 0 3 8 】

この第 1 の画素電極 B P X はたとえば透光性の導電層で形成され、その材料として、たとえば、ITO (Indium Tin Oxide) 、ITZO (Indium Tin Zinc Oxide) 、IZO (Indium Zinc Oxide) 、Sn O<sub>2</sub> (酸化スズ) 、In<sub>2</sub>O<sub>3</sub> (酸化インジウム) 等が選択される。

【 0 0 3 9 】

第 1 の画素電極 B P X の図中左側に形成された延在部は保持容量 C b s t l の一方の電極を構成するようになっており、第 2 の画素電極 U P X の図中右側に形成された延在部は保持容量 C b s t r の一方の電極を構成するようになっている。ここで、保持容量 C b s t l の他方の電極は後述する第 1 のドレイン信号線 D L L となり、保持容量 C b s t r の他方の電極は後述する第 2 のドレイン信号線 D L R となる。

【 0 0 4 0 】

このようにゲート信号線 G L および第 1 の画素電極 B P X が形成された透明基板 G L S 1 表面には、該ゲート信号線 G L および第 2 の画素電極 U P X をも被って第 1 の絶縁膜 G I が形成されている。

【 0 0 4 1 】

そして、この第 1 の絶縁膜 G I を介して画素領域内にある前記ゲート信号線 G L の上面には、該ゲート信号線 G L の延在方向に沿って離間された 2 個の薄膜トランジスタ T F T L 、T F T R が形成されている。ここで、一方の薄膜トランジスタ T F T L を第 1 の薄膜トランジスタ、他方の薄膜トランジスタ T F T R を第 2 の薄膜トランジスタと称する。

【 0 0 4 2 】

これら各第 1 の薄膜トランジスタ T F T L 、第 2 の薄膜トランジスタ T F T R は、いずれも構造が同一となっており、それらは、第 1 絶縁膜 G I 上に半導体層 A S を形成し、この半導体層 A S 上にドレイン電極とソース電極を形成することによって、前記ゲート信号線 G L の一部をゲート電極、第 1 の絶縁膜 G I をゲート絶縁膜とする逆スタガ構造の MIS (Metal Insulator Semiconductor) トランジスタが形成される。

【 0 0 4 3 】

ここで、各第 1 の薄膜トランジスタ T F T L 、第 2 の薄膜トランジスタ T F T R のドレイン電極およびソース電極は、第 1 のドレイン信号線 D L L 、第 2 のドレイン信号線 D L R の形成と同時に形成されるようになっている。

【 0 0 4 4 】

まず、第 1 の薄膜トランジスタ T F T L のドレイン電極は前記ドレイン信号線 D L L の一部がその半導体層 A S の表面にまで延在されて形成され、このドレイン電極に対して該第 1 の薄膜トランジスタ T F T L のチャネル長に相当する長さに離間されてソース電極 S D が形成されている。このソース電極 S D は第 1 の画素電極 B P X と接続させるため画素領域内に若干延在するようにして形成されている。同様に、第 2 の薄膜トランジスタ T F T R のドレイン電極は前記第 2 のドレイン信号線 D L R の一部がその半導体層 A S の表面に

10

20

30

40

50

まで延在されて形成され、このドレイン電極に対して該薄膜トランジスタTFTのチャネル長に相当する分だけ離間されてソース電極SDが形成されている。このソース電極SDは後述する第2の画素電極UPXと接続されるため画素領域内に若干延在するようにして形成されている。

【0045】

このように、各第1の薄膜トランジスタTFTL、第2の薄膜トランジスタTFTRが形成された基板GLS1の表面には、該第1の薄膜トランジスタTFTL、第2の薄膜トランジスタTFTRをも被って、第2の絶縁膜PASが形成されている。この第2の絶縁膜PASは前記各薄膜トランジスタTFTの液晶との直接の接触を回避させるための保護膜として機能するようになっている。10

【0046】

そして、この第2絶縁膜PASの表面には、前記第2の電極BPXと重ね合わされるようにして、たとえば図中y方向に延在しx方向に並設される複数の帯状の電極群からなる第2の画素電極UPXがたとえば透光性の導電層で形成されている。

【0047】

ここで、この第2の画素電極UPXを構成する電極群の前記薄膜トランジスタTFTR側の端部は、それぞれ共通に接続されたパターンとなっているとともに、その一部が該第2の薄膜トランジスタTFTRのソース電極SDの上方にまで延在され、その下層の第2絶縁膜PASおよび第1の絶縁膜GIを貫通するスルーホールCNT2を通して該ソース電極に接続されている。20

【0048】

この場合、前記第1の薄膜トランジスタTFTLのソース電極SDと第1の画素電極BPXとの接続において、第2の絶縁膜PASに形成されたコンタクトホールCNT1、第2の絶縁膜PASおよび第1の絶縁膜GIを貫通して形成されたコンタクトホールCNT2を通して、前記第2の画素電極UPXの材料と同じ材料層SITOでなされている。

【0049】

さらに、第2の画素電極UPXを構成する電極群のうち、第1のドレイン信号線DLLに隣接する電極はその一部が該第1のドレイン信号線DLLに重ね合わされるように延在され、この第2の画素電極と該第1のドレイン信号線DLLとの間に保持容量Cust1が形成され、第2のドレイン信号線DLRに隣接する第2の画素電極UPXはその一部が該第2のドレイン信号線DLRに重ね合わされるように延在され、この第2の画素電極と該第2のドレイン信号線DLRとの間に保持容量Custrが形成されている。30

【0050】

また、前記保持容量Cust1は上述した保持容量Cbst1の形成個所とほぼ同じ個所に形成され、前記保持容量Custrは上述した保持容量Cbsrの形成個所とほぼ同じ個所に形成されている。

【0051】

そして、このように形成された基板GLS1の表面には、少なくとも画素領域の集合である液晶表示部の全域を被って配向膜OILが形成され、この配向膜OILは液晶と直接に接触されて該液晶の分子の初期配向方向を決定するようになっている。

【0052】

このように構成された液晶表示装置において、当該画素領域は第1のドレイン信号線DLL、第2のドレイン信号線DLRおよび走査配線GLに囲まれた内側の領域から構成される。

【0053】

表示の動作電圧は、前記第1のドレイン信号線DLLの信号電圧を、ゲート信号線GLにゲートオン電圧が印加された期間、すなわち選択期間に、第1の薄膜トランジスタTFTLからコンタクトCNT1及びCNT2を経て画素面積のほぼ全域を占有するプレーン状の第1の画素電極BPXに、前記と同じゲートオン期間に、第2のドレイン信号線DLRの信号電圧を、第2の薄膜トランジスタTFTRからコンタクトCNT2を経て第2の画40

50

素電極 U P X にそれぞれ印加される。上記第 1 の電極 B P X と第 2 の画素電極 U P X からの電圧で液晶を駆動するようになっている。

#### 【0054】

そして、上記第 1 の電極 B P X と第 2 の電極 U P X は第 1 の絶縁膜 G I および第 2 の絶縁膜 P A S を介して重畳されそれ自身で画素容量からなる保持容量 C p を構成している。この保持容量 C p は、前記第 1 の画素電極 B P X が第 1 のドレイン信号線 D L L 及び第 2 のドレイン信号線 D L R の下部に第 1 の絶縁膜 G I を介して延在し、それぞれの保持容量 C b s t l , C b s t r をドレイン信号線 D L と構成する。他方、第 2 の画素電極 U P X は第 1 のドレイン信号線 D L L 及び第 2 のドレイン信号線に第 2 の絶縁膜 P A S を介してその上部に延在し、保持容量 C u s t l , C u s t r を構成する。

10

#### 【0055】

図 1 ( b ) は、上述した画素の構成に対応させて描いた等価回路図を示しており、ここで、 C g s l , C g s r は、それぞれ第 1 の薄膜トランジスタ T F T L の寄生容量、第 2 の薄膜トランジスタ T F T R の寄生容量を示している。

#### 【0056】

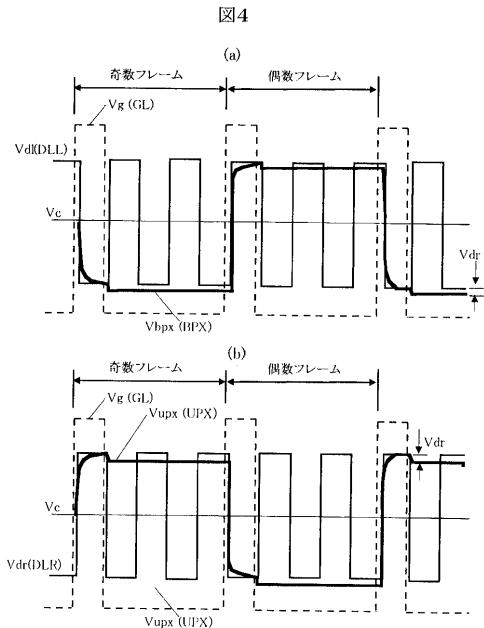

図 4 ( a )、( b ) は上述した構成の画素に供給される各信号の駆動波形を示している。この駆動波形を用いて、上述した保持容量 C b s t l , C u s t l , C b s t r , C u s t r の果たすべき効果を説明する。

#### 【0057】

図 4 ( a ) は前記第 1 の薄膜トランジスタ T F T L の駆動波形、図 4 ( b ) は前記第 2 の薄膜トランジスタ T F T R の駆動波形を示した図である。

20

#### 【0058】

図 4 ( a )、( b ) における走査 ( ゲート ) 電圧 V g は共通であり、それぞれの図には第 1 のドレイン信号線 D L L の電圧 V d l と第 2 のドレイン信号線 D L R の電圧 V d r が明示されている。また、それぞれの図には、第 1 の薄膜トランジスタ T F T L , 第 2 の薄膜トランジスタ T F T R の出力である第 1 の画素電極 B P X 及び第 2 の画素電極 U P X のソース電圧 V b p x , V u p x も明示されている。

#### 【0059】

ソース電圧 V b p x , V u p x はゲート電圧 V g がオンからオフに低下する際に、次の式 1 に示すような電圧降下 ( V b ) を起こす。

30

#### 【0060】

【数 1】  $V_b = (C_{g s l} + C_{g s r}) / (C_{b s t l} + C_{u s t l} + C_{b s t r} + C_{u s t r} + C_{g s l} + C_{g s r}) \times V_g$  ( 式 1 )

この式 1 から明らかのように、上記低下電圧には画素容量 C p は含まれない。これは画素容量 C p は 1 画素に 2 個の薄膜トランジスタ T F T を形成した場合はフローティング電位となり、上記電圧降下に影響を及ぼさないためである。そして、上記電圧降下は各ドレイン信号線 D L との間の保持容量 C b s t l , C u s t l , C b s t r , C u s t r がなければその値は V g に等しくなり、ソース電位はゲートのオフ電圧以下になり誤動作することになる。

#### 【0061】

一方、図 4 ( a )、( b ) で明らかとなるように、一方の信号線電圧 V d l と他方の信号線電圧 V d r は常に基準電圧 V c に対して対称となっているので、4 つの保持容量値すなわち、 C b s t l , C u s t l , C b s t r , C u s t r をほぼ同じ値で設定できればソース電圧 V b p x , V u p x はドレイン電圧振幅に対しても安定に動作するようになる。

40

#### 【0062】

さらに、このような動作を図 2 に示す断面図を用いてさらに詳述する。

#### 【0063】

まず、図 2 ( a ) に示す断面図において、ゲート信号線 G L にいわゆるオフゲート信号が供給される際は、第 1 の画素電極 B P X と第 2 の画素電極 U P X はそれに蓄積されている電荷がフローティング状態となる。

50

## 【0064】

すなわち、第1のドレイン信号線D<sub>L</sub>Lからの第1の映像信号は、コンタクトホールC<sub>N</sub>T<sub>1</sub>、コンタクトホールC<sub>N</sub>T<sub>2</sub>を通して画素領域の全域を占有する第1の画素電極B<sub>P</sub>Xへ供給されるようになる。一方、第2のドレイン信号線D<sub>L</sub>Rからの第2の映像信号は、コンタクトホールC<sub>N</sub>T<sub>2</sub>から第2の画素電極U<sub>P</sub>Xへ供給されるようになる。

## 【0065】

第1の薄膜トランジスタT<sub>F</sub>T<sub>L</sub>および第2の薄膜トランジスタT<sub>F</sub>T<sub>R</sub>は、それぞれ、透明基板G<sub>L</sub>S<sub>1</sub>上にゲート信号線G<sub>L</sub>をゲート電極、その上部にたとえばSiNで形成されゲート絶縁膜となる第1の絶縁膜G<sub>I</sub>、たとえばアモルファスシリコンからなる半導体層A<sub>S</sub>、第1の薄膜トランジスタT<sub>F</sub>T<sub>L</sub>において電位取り出しのための第1のドレイン信号線D<sub>L</sub>L、第2の薄膜トランジスタT<sub>F</sub>T<sub>R</sub>において電位取り出しのための第2のドレイン信号線D<sub>L</sub>R、さらに、これら上部にたとえばSiNで被覆された第2の絶縁膜P<sub>A</sub>Sで構成されている。10

## 【0066】

液晶表示は第1の画素電極B<sub>P</sub>X、および第2の画素電極U<sub>P</sub>Xの間に発生する電界が液晶L<sub>C</sub>にも及び、これにより液晶L<sub>C</sub>が電圧に応じて透過率が変化することになる。ここで、前記第1の画素電極B<sub>P</sub>X上には、第1の絶縁膜G<sub>I</sub>及び第2の絶縁膜P<sub>A</sub>Sの積層膜を挟んで、第2の画素電極U<sub>P</sub>Xが重なっており、この部分において大きな画素容量C<sub>p</sub>を構成する。

## 【0067】

しかし、この画素容量C<sub>p</sub>は、ゲート信号線G<sub>L</sub>のオフ状態では第1の薄膜トランジスタT<sub>F</sub>T<sub>L</sub>および第2の薄膜トランジスタT<sub>F</sub>T<sub>R</sub>がそれぞれオフとなり、いわゆる電源配線であるゲート信号線G<sub>L</sub>、第1のドレイン信号線D<sub>L</sub>L、あるいは第2のドレイン信号線D<sub>L</sub>Rと意図的に容量接続されていないため、この容量に蓄えられた電荷はフローティング状態となる。20

## 【0068】

図2(b)は、一画素に備えられる前記保持容量素子C<sub>ust</sub>1、C<sub>bst</sub>1、C<sub>ust</sub>r、C<sub>bst</sub>rの構成が示されている。

## 【0069】

まず、第1のドレイン信号線D<sub>L</sub>Lの信号電圧は第1の画素電極B<sub>P</sub>Xに、第2のドレイン信号線D<sub>L</sub>Rの信号電圧は第2の画素電極U<sub>P</sub>Xに伝えられることは上述した通りである。30

## 【0070】

前記第1の画素電極B<sub>P</sub>Xは、その一方の辺の一部において第1のドレイン信号線D<sub>L</sub>Lと、他方の辺の一部において第2のドレイン信号線D<sub>L</sub>Rと、第1の絶縁膜G<sub>I</sub>を介して重畠されるようにして延在している。これにより、第1のドレイン信号線D<sub>L</sub>Lとの交差部分に保持容量C<sub>bst</sub>1、第2のドレイン信号線D<sub>L</sub>Rとの交差部分に保持容量C<sub>bst</sub>rを構成している。

## 【0071】

ここで、第1の画素電極B<sub>P</sub>Xは、第1のドレイン信号線D<sub>L</sub>Lの左側に隣接する画素領域の第2のドレイン信号線D<sub>L</sub>Rと重なることなく延在され、第2のドレイン信号線D<sub>L</sub>Rの右側に隣接する画素領域の第1のドレイン信号線D<sub>L</sub>Lと重なることなく延在されている。40

## 【0072】

また、前記第2の画素電極U<sub>P</sub>Xは、その一方の辺の一部において第1のドレイン信号線D<sub>L</sub>Lと、他方の辺の一部において第2のドレイン信号線D<sub>L</sub>Rと、第2の絶縁膜P<sub>A</sub>Sを介して重畠されるようにして延在している。これにより、第1のドレイン信号線D<sub>L</sub>Lとの交差部分に保持容量C<sub>ust</sub>1、第2のドレイン信号線D<sub>L</sub>Rとの交差部分に保持容量C<sub>ust</sub>rを構成している。

## 【0073】

10

20

30

40

50

ここで、第2の画素電極UPXは、第1のドレイン信号線DLLの左側に隣接する画素領域の第2のドレイン信号線DLRと重なることなく延在され、第2のドレイン信号線DLLの右側に隣接する画素領域の第1のドレイン信号線DLLと重なることなく延在されている。

#### 【0074】

前記第1のドレイン信号線DLLの近傍に形成された保持容量Cust1及びCbst1と第2のドレイン信号線DLRの近傍に形成された保持容量Custr1及びCbsr1の平面配置は、図1(a)に示したように、各ドレイン信号線DLの形成領域であって同じ位置ではなく入れ子状態で互い違いに配置されている。これは開口率の向上と同一平面内でのショート不良を低減するために有効だからである。10

#### 【0075】

一方、保持容量Cust1、Cbst1、Custr1、Cbsr1のそれぞれの値は、各ドレイン信号線DLと第1の絶縁膜GIあるいは第2の絶縁膜PASを挟んで形成された画素電極PXの交差面積で設定されるが、安定動作を図る上では、それらの値はほぼ等しく構成することが望ましい。

#### 【0076】

すなわち、第1の画素電極BPXと第2の画素電極UPXで構成される画素容量Cpに蓄えられる大きな電荷は第1の薄膜トランジスタTFTLおよび第2の薄膜トランジスタTFTTRを駆動させるゲート信号線GLの走査信号がオフの場合にフローティング状態になる。20

#### 【0077】

従って、例えば第1のドレイン信号線DLLと第1の画素電極BPXの間に保持容量Cbst1だけしか形成されていない場合、保持期間中に該保持容量Cbst1を介して、第1の画素電極BPXのソース電位は大きく第1のドレイン信号線DLLの電位に応じて大きく変動してしまうことになる。

#### 【0078】

本実施例による画素の駆動では、第1のドレイン信号線DLLにおける映像信号の振幅と第2のドレン信号線DLRにおける映像信号の振幅は、その絶対値は同じで、振幅の方向は逆に設定されている。このため、第2のドレン信号線DLRと第1の画素電極BPXとの間に保持容量Cbsr1を形成することによって、各映像信号の振幅に対する第1の画素電極BPXの電位変動は抑えられることになる。30

#### 【0079】

同様に、第2の画素電極UPXのソース電位の安定化のために保持容量Cust1とCustr1をほぼ同じ値に設定されることで動作を安定させることができる。

#### 【0080】

実施例2.

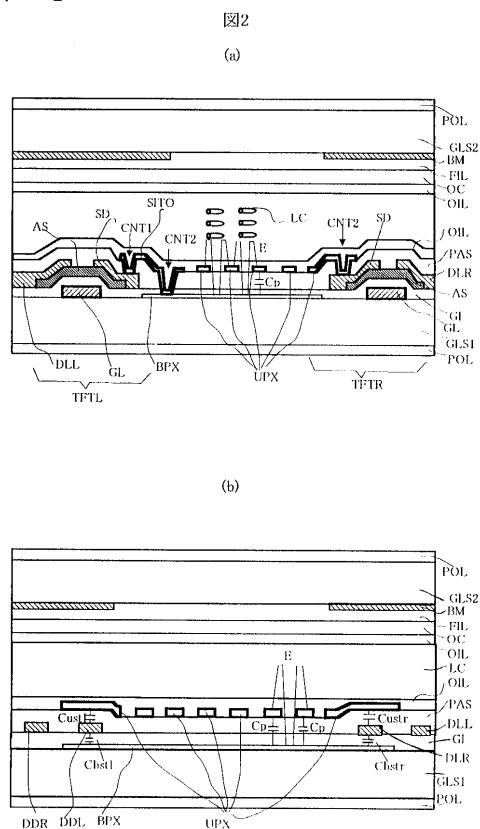

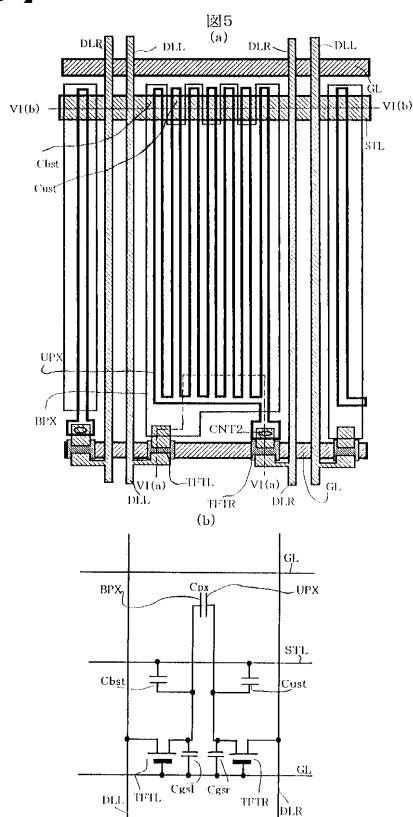

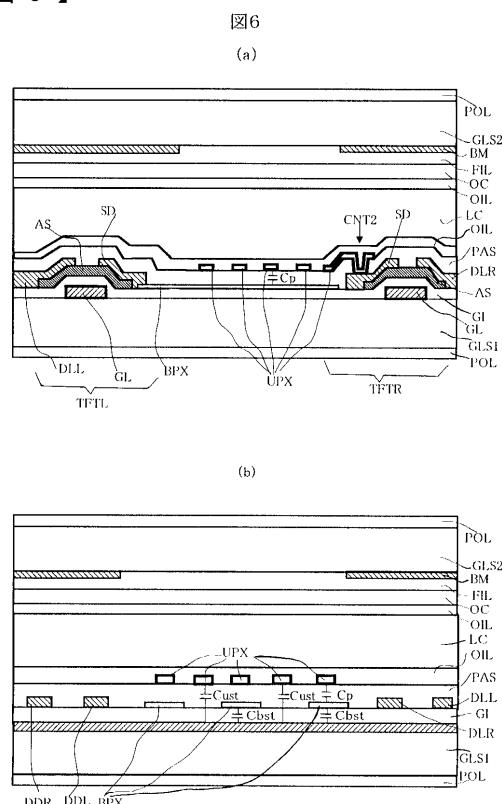

図5(a)は前記画素領域における構成の他の実施例を示す平面図である。また、図5(b)は図1(a)の構成と幾何学的に対応させて描いた等価回路図である。さらに、図6(a)は図5(a)のVI(a)-VI(a)における断面図、図6(b)は図5(a)のVI(b)-VI(b)における断面図を示している。40

#### 【0081】

図5(a)は実施例1の図1(a)に対応する図であり、該図1(a)の場合と比較して異なる構成は、第1の画素電極BPXを一方の電極とする保持容量Cbstの他方の電極として、また、第2の画素電極UPXを一方の電極とする保持容量Custの他方の電極として、それぞれ、ゲート信号線GLとほぼ平行に配置されて形成された保持容量信号線STLを用いて構成したことにある。

#### 【0082】

ここで、該保持容量信号線STLはゲート信号線GLの形成の際に同時に形成される信号線となっている。このため、保持容量信号線STLを被う第1の絶縁膜GIの表面には第1の画素電極BPXが形成され、この第1の画素電極BPXを被う第2の絶縁膜の表面に50

は第2の画素電極UPXが形成される層構造をなしている。

【0083】

そして、保持容量配線STLはその延在方向に沿って、第1の画素電極BPXと第2の画素電極UPXのいずれもが重なった領域、第1の画素電極BPXのみが積層された領域を交互に形成するように構成されている。

【0084】

ここで、前者の領域は第1の画素電極BPXの電位、すなわち第1のドレイン信号線DL-Lからの映像信号が第1の薄膜トランジスタTFTLを通して供給される信号電位の動作を安定化するために形成した保持容量Cbstを構成し、後者の領域は第2の画素電極UPXの電位、すなわち第2のドレイン信号線DLRからの映像信号を第2の薄膜トランジスタTFTRを通して供給される信号電位を安定化するために形成した保持容量Custを構成している。

【0085】

さらに、このような動作を図6に示す断面図を用いてさらに詳述する。

【0086】

図6(a)において、第1のドレイン信号線DL-Lからの映像信号はゲート信号線GLにオン電圧(走査信号)を印加した場合に第1の薄膜トランジスタTFTLがオンし、そのソース電極SDを経て第1の画素電極BPXへ供給される。一方、第2のドレイン信号線DLRからの映像信号は同様に第2の薄膜トランジスタTFTRのオン状態時に、そのソース電極SDを経て第2の画素電極UPXに供給される。

【0087】

第1の薄膜トランジスタTFTLおよび第2の薄膜トランジスタTFTRは同じ走査信号(電圧)に対してオンされるので上記各薄膜トランジスタからの映像信号は、第2の画素電極UPX、第1の画素電極BPX、第2の絶縁膜PASから構成される画素容量Cpに充電され、この電荷による液晶中の電界でインプレーンの液晶動作が可能となる。

【0088】

また、図6(b)において、保持容量信号線STLはゲート信号線GLと同層に形成され、この保持容量信号線STLの上層に形成される第1の画素電極BPXと第2の画素電極UPXとの間には、該保持容量信号線STLの走行方向に沿って、保持容量Custと保持容量Cbstとが交互に形成されている。

【0089】

第1の画素電極BPXは画素領域の僅かな周辺を除く中央部の全域に形成され、これをそのまま、保持容量信号線STL上に第1の絶縁膜GIを介して延在させた場合、第1の画素電極BPXに対する保持容量のみが形成されてしまい、走査信号がオンからオフに低下する際に第2の画素電極UPXが寄生容量の影響で動作点が低下してしまうことになる。

【0090】

このことから、前記第1の画素電極BPXは、保持容量信号線STL上において、該保持容量信号線STLの走行方向に沿って並設された複数の切り欠きを設け、該切り欠きが形成されていない部分にて保持容量Cbstを形成するとともに、該切り欠きの部分において第2の画素電極UPXを延在させ、この延在部と前記保持容量信号線STLとの間に保持容量Custを形成している。

【0091】

ここで、保持容量CustとCbstはその容量値をほぼ同一の値に設定させることができが最も安定する。第1の画素電極BPXと第2の画素電極UPXと保持容量信号線STLの間に介在される絶縁膜の厚さが異なるので、前記値の設定は第1の画素電極BPXと保持容量信号線STLの交差面積、および第2の画素電極UPXと保持容量信号線STLの交差面積をそれぞれ調整することが望ましい。

【0092】

このことから、本実施例では、第2の画素電極UPXと保持容量信号線STLの交差面積が、第1の画素電極BPXと保持容量信号線STLの交差面積より大きくなる。

10

20

30

40

50

## 【0093】

また、本実施例では保持容量信号線 S T L と第 2 の画素電極 U P X との間の誘電体膜は第 1 の絶縁膜 G I と第 2 の絶縁膜 P A S の積層体となり、保持容量信号線 S T L と第 1 の画素電極 B P X との間の誘電膜は第 1 の絶縁膜 G I のみである。アモルファスシリコンで薄膜トランジスタを構成する場合、一般に、下層の絶縁膜より上層の絶縁膜の成膜に必要とする温度は高くなる。従って、第 1 の絶縁膜 G I は第 2 の絶縁膜 P A S より良質な膜となる。両者を積層した場合、それぞれ単層膜よりショート不良に対する冗長性は高まることになる。従って、本実施例の保持容量に対するショート不良は、第 2 の絶縁膜 P A S からなる単独膜を保持容量とした実施例 1 の場合に比べてショート不良率が低減できるという効果を奏する。

10

## 【0094】

実施例 3.

図 7 は、前記画素領域における構成の他の実施例を示す断面図で、図 6 ( b ) に対応した図となっている。

## 【0095】

図 6 ( b ) の場合と比較して異なる構成は、第 2 の画素電極 U P X が保持容量信号線 S T L 上にて該保持容量信号線 S T L の走行方向に沿って互いに接続された構成となっていることがある。この保持容量信号線 S T L と重畠する部分およびその近傍を除いた部分において前記第 2 の画素電極 U P X は複数の電極が並設された電極群で構成されていることは図 6 ( b ) の場合と同様となっている。

20

## 【0096】

これにより、第 2 の画素電極 U P X は、保持容量信号線 S T L の上方において、第 1 の画素電極 B P X と重畠する部分が形成されるが、重畠しない部分においては該保持容量信号線 S T L との間に保持容量 C u s t が形成されることになる。

## 【0097】

そして、この保持容量 C u s t は、該保持容量信号線 S T L と第 2 の画素電極 U P X との重畠面積を大きくとれる構成となっていることから、その容量の値を大きくできる。

## 【0098】

このため、該保持容量 C u s t を所定の値に設定する際には、該保持容量配線 S T L の線幅を狭く構成でき、結果として画素の開口率を向上させることができるようになる。

30

## 【0099】

すなわち、保持容量信号線 S T L の走行方向に沿って、保持容量 C b s t と C u s t が交互に隙間なく配置される構成となり、該保持容量 C b s t と C u s t のそれぞれの容量値を等しく設定するのにもその設計を容易にすることができます。また、この実施例において、第 1 の画素電極 B P X の切欠き数は特に制約されないことはいうまでもない。

## 【0100】

上述した各実施例はそれぞれ単独に、あるいは組み合わせて用いても良い。それぞれの実施例での効果を単独であるいは相乗して奏することができるからである。

## 【0101】

## 【発明の効果】

以上説明したことから明らかなように、本発明による液晶表示装置によれば、その薄膜トランジスタのゲート電位がオンからオフに変化する際に、画素電極の電位が著しく低下してしまう動作点悪化の不都合を解消させることができる。

40

## 【図面の簡単な説明】

【図 1】本発明による液晶表示装置の画素の一実施例を示す平面図、それに対応する等価回路図である。

【図 2】図 1 の I I ( a ) - I I ( a ) 線、および I I ( b ) - I I ( b ) 線における断面図である。

【図 3】本発明による液晶表示装置の一実施例を示す平面図である。

【図 4】本発明による液晶表示装置の画素に供給される信号の波形とそのタイミングチャ

50

ートである。

【図5】本発明による液晶表示装置の画素の他の実施例を示す平面図、それに対応する等価回路図である。

【図6】図5のV<sub>I</sub>(a) - V<sub>I</sub>(a)線、およびV<sub>I</sub>(b) - V<sub>I</sub>(b)線における断面図である。

【図7】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

#### 【符号の説明】

GLS...透明基板、GL...ゲート信号線、DLL...第1のドレイン信号線、DLR...第2のドレイン信号線、TFTL...第1の薄膜トランジスタ、TFTR...第2の薄膜トランジスタ、BPX...第1の画素電極、UPX...第2の画素電極、GI...第1の絶縁膜、PAS...第2の絶縁膜、AS...半導体層、OIL...配向膜、LC...液晶、Custl, Cbstl, Custr, Cbstr...保持容量。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

図7