(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6082317号

(P6082317)

(45) 発行日 平成29年2月15日(2017.2.15)

(24) 登録日 平成29年1月27日(2017.1.27)

(51) Int.Cl.

G06F 12/08 (2016.01)

G06F 1/32 (2006.01)

F 1

G06F 12/08 5 7 9

G06F 12/08 5 5 3 B

G06F 1/32 Z

請求項の数 6 (全 34 頁)

(21) 出願番号 特願2013-113575 (P2013-113575)

(22) 出願日 平成25年5月30日 (2013.5.30)

(65) 公開番号 特開2014-6894 (P2014-6894A)

(43) 公開日 平成26年1月16日 (2014.1.16)

審査請求日 平成28年5月19日 (2016.5.19)

(31) 優先権主張番号 特願2012-126064 (P2012-126064)

(32) 優先日 平成24年6月1日 (2012.6.1)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 原 裕

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 滝谷 亮一

最終頁に続く

(54) 【発明の名称】中央処理装置および中央処理装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

キャッシュメモリと、電源制御部と、演算装置と、を有し、

前記キャッシュメモリは、複数のキャッシュラインを有し、

前記キャッシュラインは、データフィールドと、タグフィールドと、を有し、

前記データフィールドは、主記憶装置のデータの一部を保存する機能を有し、

前記タグフィールドは、バリッドビットを有し、

前記タグフィールドは、前記データフィールドに保存されたデータの管理情報を保存する機能を有し、

前記バリッドビットは、前記データフィールドに保存されたデータおよび前記タグフィールドに保存された管理情報を有効か否かの情報を保存する機能を有し、

前記電源制御部は、前記データフィールド、前記タグフィールドおよび前記バリッドビットへの電源供給状態を決定する機能を有し、

前記演算装置は、前記バリッドビットに保存されたデータが有効か否かの第1の判断および、必要とするデータのアドレスが前記タグフィールドに保存されたデータと一致するか否かの第2の判断を行い、

前記演算装置は、前記第1の判断の結果および前記第2の判断の結果を前記電源制御部に出力する機能を有し、

前記データフィールド、前記タグフィールドおよび前記バリッドビットは、電源電圧の供給が行われない状況でも書き込まれた情報を保存するメモリセルを用いて構成され、

10

20

前記電源制御部は、

前記演算装置から前記キャッシュメモリへのデータ送受が行われない第1の場合において、

前記データフィールド、前記タグフィールドおよび前記バリッドビットへの電源電圧供給を停止状態とする処理を行い、

前記演算装置から前記キャッシュメモリへのデータ送受が行われる第2の場合において、

前記バリッドビットへの電源電圧供給と、

前記第1の判断によって前記バリッドビットに保存されたデータが有効と判断された前記キャッシュラインの前記タグフィールドへの電源電圧供給と、

前記第2の判断によって必要とするデータのアドレスが前記タグフィールドに保存されたデータと一致すると判断された前記キャッシュラインの前記データフィールドへの電源電圧供給とを行う、

ことを特徴とする中央処理装置。

#### 【請求項2】

請求項1において、

前記電源制御部が、

前記演算装置により前記第1の判断が行われた後、または前記第1の判断時に、前記バリッドビットへの電源電圧供給の停止を行うことを特徴とする中央処理装置。

#### 【請求項3】

請求項1または請求項2において、

前記電源制御部が、

前記演算装置により前記第2の判断が行われた後、または前記第2の判断時に、前記タグフィールドへの電源電圧供給の停止を行うことを特徴とする中央処理装置。

#### 【請求項4】

キャッシュメモリと、電源制御部と、演算装置と、を有し、

前記キャッシュメモリは、複数のキャッシュラインを有し、

前記キャッシュラインは、データフィールドと、タグフィールドと、を有し、

前記データフィールドは、主記憶装置のデータの一部を保存する機能を有し、

前記タグフィールドは、バリッドビットを有し、

前記タグフィールドは、前記データフィールドに保存されたデータの管理情報を保存する機能を有し、

前記バリッドビットは、前記データフィールドに保存されたデータおよび前記タグフィールドに保存された管理情報が有効か否かの情報を保存する機能を有し、

前記電源制御部は、前記データフィールド、前記タグフィールドおよび前記バリッドビットへの電源供給状態を決定する機能を有し、

前記演算装置は、前記バリッドビットに保存されたデータが有効か否かの第1の判断および、必要とするデータのアドレスが前記タグフィールドに保存されたデータと一致するか否かの第2の判断を行い、

前記演算装置は、前記第1の判断の結果および前記第2の判断の結果を前記電源制御部に出力する機能を有し、

前記データフィールド、前記タグフィールドおよび前記バリッドビットは、電源電圧の供給が行われない状況でも書き込まれた情報を保存するメモリセルを用いて構成され、

前記演算装置から前記キャッシュメモリへのデータ送受が行われない第1の場合においては、

前記電源制御部は、前記データフィールド、前記タグフィールドおよび前記バリッドビットへの電源電圧供給を停止し、

前記演算装置から前記キャッシュメモリへのデータ送受が行われる第2の場合においては、

第1の処理として、前記電源制御部が、前記バリッドビットに対して電源電圧供給を行

10

20

30

40

50

い、

第2の処理として、前記演算装置が、前記第1の判断を行った結果を前記電源制御部に出力し、

第3の処理として、前記電源制御部が、前記第2の処理にて有効と判断された前記キャッシュラインの前記タグフィールドに対して電源電圧供給を行い、

第4の処理として、前記演算装置が、前記第2の判断を行った結果を前記電源制御部に出力し、

第5の処理として、前記電源制御部が、前記第4の処理にて一致と判断された前記キャッシュラインの前記データフィールドに対して電源電圧供給を行い、

第6の処理として、前記演算装置が、前記第4の処理にて電源電圧供給が行われた前記データフィールドのデータを読み出す、

ことを特徴とする中央処理装置の駆動方法。

【請求項5】

請求項4において、

前記演算装置により前記第1の判断が行われた後、または前記第1の判断時に、前記バーリッドビットへの電源電圧供給を停止することを特徴とする中央処理装置の駆動方法。

【請求項6】

請求項4または請求項5において、

前記演算装置により前記第2の判断が行われた後、または前記第2の判断時に、前記タグフィールドへの電源電圧供給を停止することを特徴とする中央処理装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、中央処理装置および中央処理装置の駆動方法に関する。

【背景技術】

【0002】

中央処理装置(CPU: Central Processing Unit。中央演算処理装置などとも言われる。)は、その用途によって多種多様な構成を有しているが、ストアドプログラム方式と呼ばれるアーキテクチャがCPUの主流となっている。ストアドプログラム方式のCPUでは、命令及び上記命令の実行に必要なデータが半導体記憶装置(以下、単に記憶装置と記載する。)に格納されており、上記命令及びデータが記憶装置から順次読み込まれることで、命令が実行される。

【0003】

上述の記憶装置には、データや命令を記憶するための主記憶装置の他に、高速でデータの書き込みと読み出しができるキャッシュメモリがある。キャッシュメモリは、情報処理装置の演算装置(演算部とも言える。)または制御装置(制御部とも言える。)と、主記憶装置の間に介在し、低速な主記憶装置へのアクセスを減らして演算処理を高速化させることを目的として、情報処理装置に設けられている。通常は、キャッシュメモリとしてはSRAM(Static Random Access Memory)などが用いられる。例えば、特許文献1では、SRAMなどの揮発性メモリと、不揮発性メモリとを併用するキャッシュメモリの構成について記載されている。

【0004】

中央処理装置内に設けられるキャッシュメモリの容量は年々増加する傾向にある。これに伴い、中央処理装置の全消費電力のうちキャッシュメモリの消費電力の占める割合が飛躍的に大きくなっているため、キャッシュメモリの消費電力を低減する様々な方法が提案されている。

【0005】

例えば、キャッシュメモリをいくつかのブロックに分割し、過去の履歴情報などから使用頻度の少ないブロック(ラインとも表現できる。)を低いしきい値電圧で動作させる方法などが提案されている。また、アクセスされる見込みの少ないキャッシュラインへの電

10

20

30

40

50

源供給を停止するといった方法も提案されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008-276646号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述の背景技術における思想は、キャッシュメモリは常に動作させておくことが前提であり、その中で、供給する電源電圧を下げる、あるいは電源供給自体を停止する、といった消費電力低減手段をキャッシュメモリの一部（以下、選択箇所とも記載する。）について行うため、キャッシュメモリの選択箇所以外については常に電力を消費している状態にある。

【0008】

このため、キャッシュメモリの使用状況（例えば、データ処理量が増加し、キャッシュメモリの選択箇所が非常に少ない状態など。）により、中央処理装置の消費電力低減効果に大きなバラツキが生じる。

【0009】

上述のような技術的背景を鑑み、本発明は、消費電力の低減された中央処理装置を提供することを目的の一つとする。

10

【0010】

また、上述の中央処理装置の駆動方法を提供することを目的の一つとする。

【課題を解決するための手段】

【0011】

本発明は、中央処理装置の消費電力を削減する方法として、上述にて記載したキャッシュメモリの選択箇所以外において消費される電力に着目し、当該電力を低減することで、中央処理装置の消費電力低減を行うことを技術的思想としている。

【0012】

具体的には、まず、中央処理装置に設けられるキャッシュメモリを、主記憶装置のデータの一部を保存するデータフィールド、データフィールドに保存されたデータの管理情報を保存するタグフィールドならびに、タグフィールドに含まれ、データフィールドに保存されたデータおよびタグフィールドに保存された管理情報が有効か否かの情報を保存するバリッドビットを有する構造とし、データフィールド、タグフィールドおよびバリッドビットの構成要素であるメモリセルを、電力の供給が行われない状況でも書き込まれた情報の保存が可能な不揮発性のメモリセルとした。

30

【0013】

そして、中央処理装置に電源制御部を設け、中央処理装置の備える演算装置からキャッシュメモリへのアクセス（読み出し要求など。）が無い状態では、電源制御部がデータフィールド、タグフィールドおよびバリッドビットへの電源電圧供給を常に停止状態とし、キャッシュメモリへのアクセスが行われた場合において、電源制御部がデータフィールド、タグフィールドおよびバリッドビットに対して選択的に電源電圧供給を行える構造とした。

40

【0014】

なお、「データフィールドに対して電源電圧供給を行う」とは、「データフィールドの構成要素であるメモリセルへの電源電圧供給を行う」と言い換えることもできる。また、タグフィールドおよびバリッドビットについても同様のことが言える。

【0015】

中央処理装置を上述の構造とすることにより、一般的な中央処理装置と比較して消費電力を低減できる概念を、図7および図8を用いて簡単に説明する。

【0016】

50

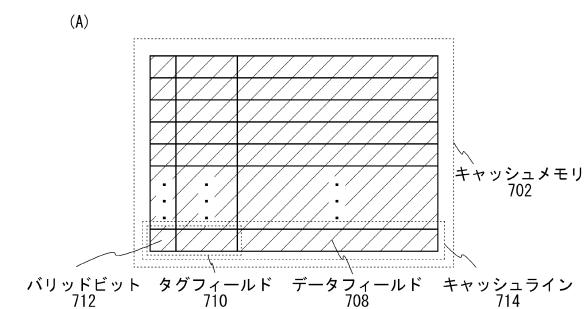

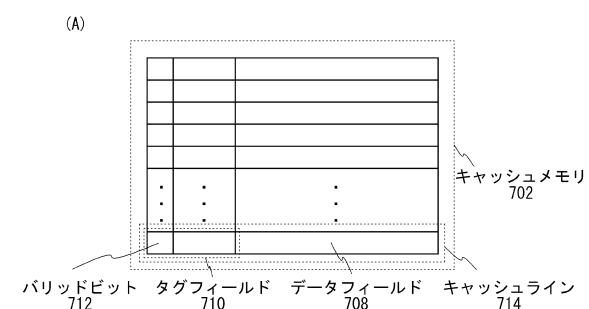

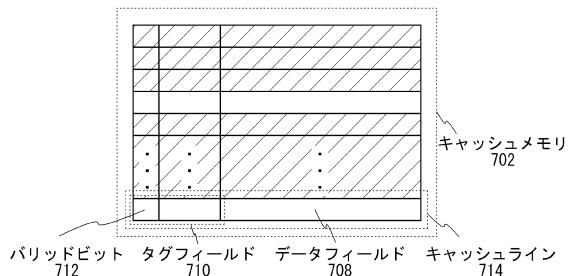

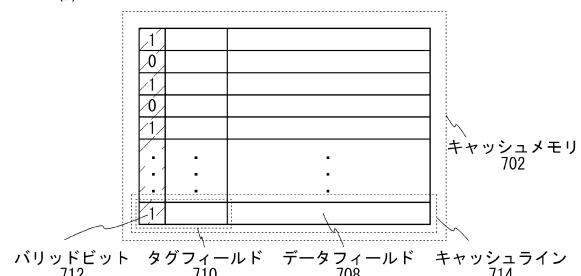

図7および図8は、データフィールド708、タグフィールド710、バリッドビット712を有するキャッシュライン714を複数備えたキャッシュメモリ702における動作状況の概念図を示すものであり、図7が一般的な中央処理装置、図8が本明細書等に記載の中央処理装置の動作状況の概念図である。なお、図7および図8において、斜線の記載されている部分は電源電圧が供給されており、斜線の記載されていない部分には電源電圧が供給されていないことを表している。

#### 【0017】

図7に示すようにキャッシュメモリ702の備えるデータフィールド708、タグフィールド710およびバリッドビット712は、電源電圧の供給が行われない状況では書き込まれた情報が変化してしまう揮発性のメモリセル（例えば、SRAM（Static Random Access Memory）など。）が用いられている。レジスタ、キャッシュメモリ等は、電源電圧の供給が途絶えるとデータを消失してしまう揮発性の記憶装置である。）を用いて構成されることが一般的である。したがって、図7（A）に示すように、キャッシュメモリ702の外部（例えば、演算装置など。）からアクセスが行われていない状態でも、大小の差異はあるもののデータフィールド708（データフィールド708の備えるメモリセル、とも表現できる。）、タグフィールド710（タグフィールド710の備えるメモリセル、とも表現できる。）、バリッドビット712（バリッドビット712の備えるメモリセル、とも表現できる。）には常に電源電圧が供給されている。

#### 【0018】

キャッシュメモリ702の消費電力を低減する方法として、キャッシュメモリ702の外部からアクセスがほとんど行われない（例えば、演算装置からの読み出し要求がほとんどない。）キャッシュライン714に対しての電源電圧供給を停止する（図7（B）参照）。なお、電源電圧供給を完全に停止するのではなく、保存されたデータの状態を保持できるだけの最低限の電源電圧供給を行うという方法もある。）といった動作が行われることもあるが、当該動作が行われていないキャッシュライン714については消費電力が発生し続いていることに変わりはない。

#### 【0019】

これに対し、本明細書等に記載のキャッシュメモリは、データフィールド708、タグフィールド710およびバリッドビット712を備えるキャッシュラインが複数存在する点については一般的なキャッシュメモリに準ずるが、データフィールド708、タグフィールド710およびバリッドビット712が電源電圧の供給が行われない状況でも書き込まれた情報の保存が可能な不揮発性のメモリセルを用いて構成されているため、キャッシュメモリ702の外部（例えば、演算装置など。）からデータ送受が行われていない状態では、図8（A）のように全てのキャッシュライン714の電源電圧の供給を停止することができる。

#### 【0020】

また、本明細書等では、キャッシュメモリ702の外部からデータ送受信が行われた場合についてのキャッシュメモリ702の立ち上げ状態（電源供給状態とも表現できる。）についても、消費電力の低減が可能な新たな提案を行っている。ここでは、立ち上げ状態についての概念の一例を、図8（B）を用いて以下にて説明する。

#### 【0021】

まず、キャッシュメモリ702に備えられたバリッドビット712に対して電源電圧供給を行い、いずれのキャッシュラインに有効なデータが保存されているかを判断し（図8（B）参照。図8（B）では、データ”1”が有効なデータであるとする。）、データが有効であると判断されたキャッシュラインのタグフィールドのみに対して電源電圧供給を行う。

#### 【0022】

そして、タグフィールドに保存されているデータを用いて、必要としているデータ（例えば、演算装置が読み出し要求を求めているデータ。）がいずれのデータフィールドに保

10

20

30

40

50

存されているかを判断し、必要としているデータが保存されていると判断されたデータフィールドのみに対して電源電圧供給を行う。

【0023】

これにより、電源電圧供給を抑制しながらも、必要としているデータにアクセスすることができるため、中央処理装置の消費電力を低減することができる。

【0024】

なお、上述のように一部のデータフィールドやタグフィールドのみに選択的に電源電圧供給を行うには、中央処理装置に電力を供給する電源装置とキャッシュメモリの間に電源制御部を設け、中央処理装置内に設けられた演算装置を用いて電源制御部を適宜動作させる構造とすればよい。

10

【0025】

また、演算装置は、電源制御部の動作状態を制御するだけでなく、キャッシュメモリ102に保存されたデータについての判断（例えば、有効なデータがいずれのキャッシュラインに存在するかの判断など。）も行う。

【0026】

すなわち、本発明の一態様は、主記憶装置のデータの一部を保存するデータフィールド、データフィールドに保存されたデータの管理情報を保存するタグフィールドならびに、タグフィールドに含まれ、データフィールドに保存されたデータおよびタグフィールドに保存された管理情報が有効か否かの情報を保存するバリッドビットと、を有するキャッシュラインを複数備えたキャッシュメモリと、データフィールド、タグフィールドおよびバリッドビットへの電源供給状態を決定する電源制御部と、バリッドビットに保存されたデータが有効か否かの第1の判断および、必要とするデータのアドレスがタグフィールドに保存されたデータと一致するか否かの第2の判断を行い、また、第1の判断の結果および第2の判断の結果を電源制御部に出力する演算装置と、を備え、データフィールド、タグフィールドおよびバリッドビットは、電源電圧の供給が行われない状況でも書き込まれた情報を保存するメモリセルを用いて構成され、電源制御部が、演算装置からキャッシュメモリへのデータ送受が無い状態では、データフィールド、タグフィールドおよびバリッドビットへの電源電圧供給を停止状態とし、演算装置からキャッシュメモリへのデータ送受が行われた場合において、バリッドビットへの電源電圧供給と、第1の判断によって前記バリッドビットに保存されたデータが有効であると判断されたキャッシュラインのタグフィールドへの電源電圧供給と、前記第2の判断によって必要とするデータのアドレスが前記タグフィールドに保存されたデータと一致すると判断された前記キャッシュラインのデータフィールドへの電源電圧供給を行う中央処理装置である。

20

【0027】

中央処理装置を上述の構造とすることにより、一部のデータフィールドやタグフィールドのみに選択的に電源電圧供給を行うことができるため、中央処理装置の消費電力を低減できる。

【0028】

なお、上述構造において、電源制御部を、演算装置により第1の判断が行われた後、または第1の判断時に、バリッドビットへの電源電圧供給の停止を行う構造とすることにより、中央処理装置の消費電力を更に低減できるため好ましい。

30

【0029】

また、上述構造において、電源制御部が、演算装置により第2の判断が行われた後、または第2の判断時に、タグフィールドへの電源電圧供給の停止を行う構造とすることにより、中央処理装置の消費電力を更に低減できるため好ましい。

【0030】

また、本発明の一態様は、主記憶装置のデータの一部を保存するデータフィールド、データフィールドに保存されたデータの管理情報を保存するタグフィールドならびに、タグフィールドに含まれ、データフィールドに保存されたデータおよびタグフィールドに保存された管理情報が有効か否かの情報を保存するバリッドビットと、を有するキャッシュラ

40

50

インを複数備えたキャッシュメモリと、データフィールド、タグフィールドおよびバリッドビットへの電源供給状態を決定する電源制御部と、バリッドビットに保存されたデータが有効か否かの第1の判断、および必要とするデータのアドレスがタグフィールドに保存されたデータと一致するか否かの第2の判断を行い、また、第1の判断の結果および第2の判断の結果を電源制御部に出力する演算装置と、を備え、データフィールド、タグフィールドおよびバリッドビットは、電源電圧の供給が行われない状況でも書き込まれた情報を保存するメモリセルを用いて構成され、電源制御部が演算装置からキャッシュメモリへのデータ送受が無い状態では、電源制御部はデータフィールド、タグフィールドおよびバリッドビットへの電源電圧供給を停止し、演算装置がキャッシュメモリに保存されたデータの読み出しを行う場合において、第1の処理として、電源制御部がバリッドビットに対して電源電圧供給を行い、第2の処理として、演算装置が第1の判断を行って当該結果を電源制御部に出力し、第3の処理として、電源制御部が第2の処理にて有効と判断されたキャッシュラインのタグフィールドに対して電源電圧供給を行い、第4の処理として、演算装置が第2の判断を行って当該結果を電源制御部に出力し、第5の処理として電源制御部が第4の処理にて一致と判断されたキャッシュラインのデータフィールドに対して電源電圧供給を行い、第6の処理として、演算装置が第4の処理にて電源電圧供給が行われたデータフィールドのデータを読み出すことを特徴とする、中央処理装置の駆動方法である。

。

#### 【0031】

中央処理装置を上述の駆動方法を用いて動作させることにより、一部のデータフィールドやタグフィールドのみに選択的に電源電圧供給を行うことができるため、中央処理装置の消費電力を低減できる。

20

#### 【0032】

なお、上述の駆動方法に加えて、演算装置により第1の判断が行われた後、または第1の判断時にバリッドビットへの電源電圧供給の停止、あるいは、演算装置により第2の判断が行われた後、または第2の判断時にタグフィールドへの電源電圧供給の停止、のいずれか一方あるいは両方を行うことにより、中央処理装置の消費電力を更に低減できる。

#### 【発明の効果】

#### 【0033】

本明細書等に記載のように、データフィールド、タグフィールドおよびバリッドビットの構成要素であるメモリセルを不揮発性のメモリセルとし、また、演算装置からキャッシュメモリへのアクセスが無い状態では、データフィールド、タグフィールドおよびバリッドビットへの電源電圧供給を常に停止状態とし、キャッシュメモリへのアクセスが行われた場合において、電源制御部を用いてデータフィールド、タグフィールドおよびバリッドビットに対して選択的に電源電圧供給を行える構造とすることにより、演算装置からキャッシュメモリへのアクセスが生じた場合のみ、キャッシュメモリの一部を動作させて必要な処理（キャッシュメモリから演算装置へのデータ読み出しなど。）を行うことができるため、中央処理装置の消費電力を大幅に削減することができる。

30

#### 【図面の簡単な説明】

#### 【0034】

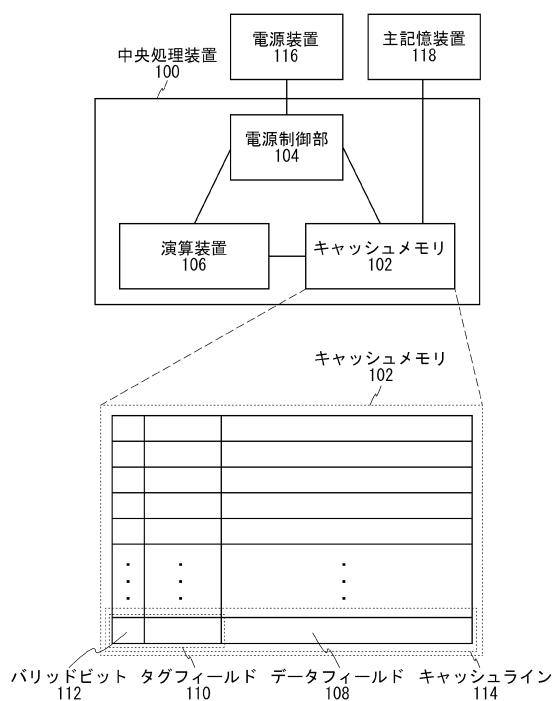

【図1】中央処理装置の構成を説明する図。

40

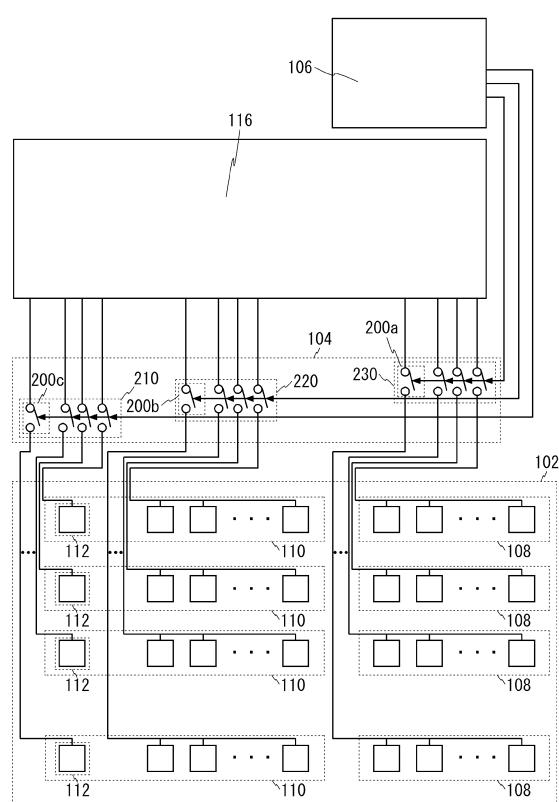

【図2】電源制御部の一例を説明する図。

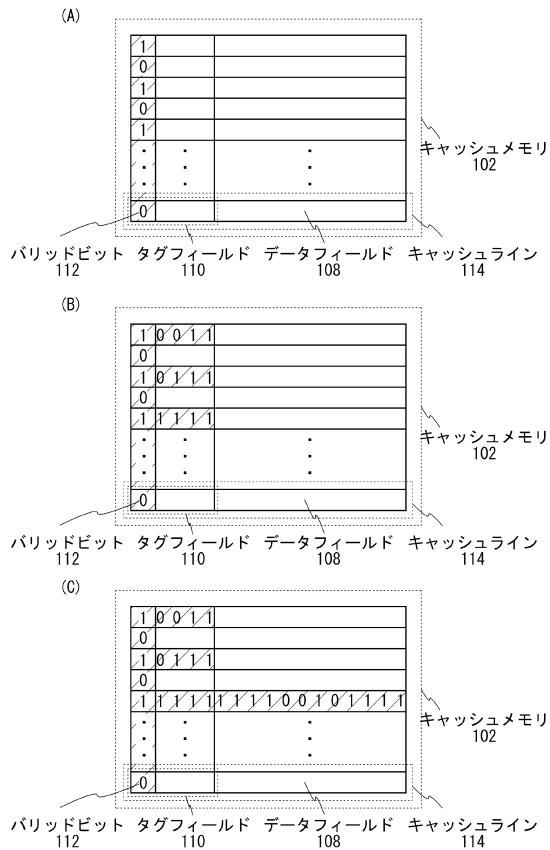

【図3】キャッシュメモリ内での電源供給状態の概念を説明する図。

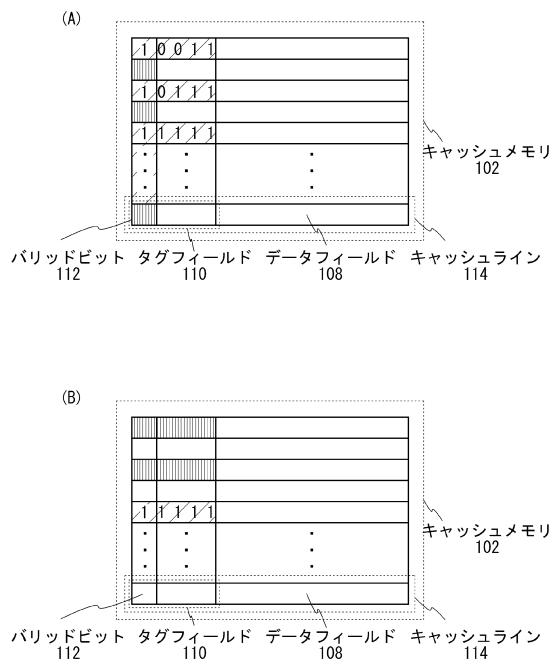

【図4】キャッシュメモリ内での電源供給状態の概念を説明する図。

【図5】不揮発性メモリセルの構造の一例を説明する図。

【図6】不揮発性メモリセルの構造の一例を説明する図。

【図7】キャッシュメモリ内での電源供給状態の概念を説明する図。

【図8】キャッシュメモリ内での電源供給状態の概念を説明する図。

【図9】中央処理装置を備えた電子機器を説明する図。

#### 【発明を実施するための形態】

10

20

30

40

50

**【 0 0 3 5 】**

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

**【 0 0 3 6 】**

なお、以下に説明する実施の形態において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。

**【 0 0 3 7 】**

また、図面等において示す各構成の、位置、大きさ、範囲などは、理解を容易にするため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

**【 0 0 3 8 】**

なお、本明細書等においてノードとは、回路を構成する素子の電気的な接続を可能とする素子（例えば、配線など）のことをいう。したがって、”Aが接続されたノード”とは、Aと電気的に接続され、且つAと同電位と見なせる配線のことをいう。なお、配線の途中に電気的な接続を可能とする素子（例えば、スイッチ、トランジスタ、容量素子、インダクタ、抵抗素子、ダイオードなど）が1個以上配置されていても、Aと同電位と見なせればその配線はAが接続されたノードと見なせる。

10

20

**【 0 0 3 9 】****( 実施の形態 1 )**

本実施の形態では、図1および図2を用いて中央処理装置の構成を説明すると共に、当該中央処理装置の駆動方法の一例を、図3を用いて説明する。

**【 0 0 4 0 】****< 中央処理装置の構成例 >**

図1は、本明細書等に記載の中央処理装置の構成の一例を表す図である。

**【 0 0 4 1 】**

図1に示すように、中央処理装置100は、内部にキャッシュメモリ102、電源制御部104および演算装置106を備えている。

30

**【 0 0 4 2 】**

そして、中央処理装置100は電源装置116および主記憶装置118と接続されており、キャッシュメモリ102および演算装置106は電源制御部104を介して電源装置116から電源電圧が供給されるとともに、主記憶装置118のデータの一部がキャッシュメモリ102に保存されている。

**【 0 0 4 3 】**

キャッシュメモリ102には、主記憶装置118のデータの一部を保存するデータフィールド108、データフィールド108に保存されたデータの管理情報を保存するタグフィールド110ならびに、タグフィールド110に含まれ、データフィールド108およびタグフィールド110に格納されたデータが有効か否かの情報を保存するバリッドビット112を有するキャッシュライン114が備えられている。なお、データフィールド108、タグフィールド110およびバリッドビット112は、電源制御部104を介して電源装置116からの電源電圧供給が行われない状況でも書き込まれた情報の保存が可能な不揮発性のメモリセルを用いて構成されている。なお、本明細書等ではバリッドビット112はタグフィールド110に含まれると記載しているが、必ずしもタグフィールド110に含まれる必要はなく、バリッドビット112とタグフィールド110が独立に存在していてもよい。

40

**【 0 0 4 4 】**

不揮発性のメモリセルとしては、例えば、フラッシュメモリ、磁気抵抗メモリ（MRA

M : Magnetoresistive Random Access Memory）

50

、強誘電体メモリ(FeRAM: Ferroelectric Random Access Memory)、抵抗変化型メモリ(ReRAM: Resistance Random Access Memory)などを用いることができる。

#### 【0045】

また、メモリセルの構成要素の一部に、酸化物半導体材料を半導体層(少なくともチャネルが形成される領域。)に用いたトランジスタ(当該トランジスタを、本明細書等ではOSトランジスタとも記載する。)を使用する構成とすることで、不揮発性の特性を備えるメモリセルとすることができます。

#### 【0046】

なお、OSトランジスタを構成要素の一部に使用した、不揮発性の特性を備えるメモリセルの構造については、実施の形態3にて詳細な説明を行う。

10

#### 【0047】

上述のように、キャッシュメモリ102を、データフィールド108、タグフィールド110およびバリッドビット112を備えた構造とし、データフィールド108、タグフィールド110およびバリッドビット112が電源電圧の供給が行われない状況でも書き込まれた情報の保存が可能な不揮発性のメモリセルを用いて構成されているため、キャッシュメモリ102の外部(例えば、演算装置106など。)からアクセスが行われていない状態では、全てのデータフィールド108、タグフィールド110およびバリッドビット112への電源電圧供給を停止することができる。

#### 【0048】

20

電源制御部104は、演算装置106からの信号に基づいて、電源装置116から供給される電源電圧をキャッシュメモリ102のいずれの部分に供給するか、また、いずれの部分への電源電圧供給を停止するかを決定する機能を有している。

#### 【0049】

電源制御部104は、上述の機能を有していればその構造に特段の限定はなく、回路構成等については実施者が適宜決定すればよい。

#### 【0050】

例えば、図2に示すように、データフィールド108を構成する複数のメモリセルの各々に接続された電源線に、演算装置106からの指示により導通および非導通の選択が可能なスイッチ素子200aを設け、タグフィールド110を構成する複数のメモリセルの各々に接続された電源線に、演算装置106からの指示により導通および非導通の選択が可能なスイッチ素子200bを設け、バリッドビット112を構成するメモリセルに接続された電源線に、演算装置106からの指示により導通および非導通の選択が可能なスイッチ素子200cを設け、これらのスイッチ素子200a乃至スイッチ素子200cをまとめて電源制御部104とすればよい。

30

#### 【0051】

なお、図2に記載の回路構成では、データフィールド108、タグフィールド110およびバリッドビット112の全てがライン単位で電源制御が可能であるが、バリッドビット112は必ずしもライン単位で電源制御が可能である必要はなく、例えば、電源制御部104により全ラインのバリッドビット112に対して電源供給を同時に実行する、あるいは同時に停止するといった構造であってもよい。

40

#### 【0052】

また、図2に記載の回路構成は、あくまでも電源制御部104の構成の一例であるため、電源制御部104の構造が当該構造に限定されるものではなく、上述したように、演算装置106からの信号に基づいて、電源装置116から供給される電源電圧をキャッシュメモリ102のいずれの部分に供給するか、また、いずれの部分への電源電圧供給を停止するかを決定する機能を有していればよい。

#### 【0053】

上述のように、電源制御部104が演算装置106からの指示により、データフィールド108、タグフィールド110およびバリッドビット112に対しての電源装置116

50

からの電源供給状態を制御できる構造とすることにより、電源装置 116 からキャッシュメモリ 102 への電源電圧供給量を抑制しながらも、演算装置 106 が必要としているデータにアクセスすること（データや命令などの情報を取得／更新するためのアクセス）ができるため、中央処理装置 100 の消費電力を低減することができる。

#### 【0054】

演算装置 106 は、バリッドビット 112 に保存されたデータが有効か否かの判断（以下、第 1 の判断と記載する。）および、演算装置 106 が必要とするデータの管理情報がタグフィールド 110 に保存されたデータの管理情報と一致するか否かの判断（以下、第 2 の判断と記載する。）を行い、また、第 1 の判断の結果および第 2 の判断の結果を電源制御部 104 に出力する機能を備えている。10

#### 【0055】

以上が、本実施の形態における中央処理装置の構造である。

#### 【0056】

< 中央処理装置の駆動方法例 >

次に、中央処理装置 100 の駆動方法の一例について図 3 を用いて説明する。なお、図 3 は、本実施の形態に記載の駆動方法を行うことにより、キャッシュメモリ 102 内において電源供給状態がどのように変化するかを模式的に示した図である。

#### 【0057】

以下に記載する駆動方法は、キャッシュメモリ 102 のデータフィールド 108 に主記憶装置 118 のデータの一部が保存されているものとし、演算装置 106 がデータフィールド 108 に保存されたデータを読み出す処理についての説明を行う。20

#### 【0058】

まず、第 1 の処理として、演算装置 106 が必要なデータの読み出し処理を開始することが決定した時点で、演算装置 106 から電源制御部 104 に対して当該決定を伝える信号を出力し、当該信号を受けた電源制御部 104 は、キャッシュメモリ 102 の備える全ラインのバリッドビット 112 に対して電源電圧供給を開始する（図 3（A）参照。）。

#### 【0059】

上述のように、キャッシュメモリ 102 の備える全ラインのバリッドビット 112 に対して電源電圧供給を行うには、例えば図 2 の回路図を用いて説明すると、電源制御部 104 に備えられた複数のスイッチ素子のうち、範囲 210 のスイッチ素子（つまり、バリッドビット 112 と接続された電源線に備えられたスイッチ素子 200c。）を全て導通状態とすればよい。30

#### 【0060】

これにより、各ラインのバリッドビット 112 の不揮発性メモリセルに保持されたデータが読み出し可能な状態となる。

#### 【0061】

なお、以下ではデータ “1” が有効なデータ、データ “0” が無効なデータを表すものとする。

#### 【0062】

次に、第 2 の処理として、各ラインのバリッドビット 112 に保存されたデータが有効（データ “1”）か或いは無効（データ “0”）かを演算装置 106 が第 1 の判断を行い、当該判断結果を伝える信号を電源制御部 104 に出力する。40

#### 【0063】

そして、第 3 の処理として、第 1 の判断結果を伝える信号を受けた電源制御部 104 は、キャッシュメモリ 102 の備える複数のタグフィールド 110 のうち、バリッドビット 112 のデータが有効であるラインのタグフィールド 110 に対して電源電圧供給を開始する（図 3（B）参照。）。

#### 【0064】

上述のように、バリッドビット 112 のデータが有効であるラインのタグフィールド 110 に対して電源電圧供給を行うには、例えば図 2 の回路図を用いて説明すると、範囲 250

20のスイッチ素子のうち、バリッドビット112のデータが有効であるラインのタグフィールド110と接続されたスイッチ素子200bを導通状態とすればよい。

【0065】

これにより、電源電圧供給が開始されたタグフィールド110の不揮発性メモリセルに保存されたデータが読み出し可能となる。

【0066】

次に、第4の処理として、演算装置106が、演算装置106の必要とするデータについての管理情報（以下では、当該管理情報が”1111”であるものとして説明を行う。）と、電源供給が行われているタグフィールド110の管理情報を比較し、演算装置106の必要とするデータがキャッシュライン114のいずれかに保存されているかの第2の判断を行い、演算装置106の必要とするデータが保存されているデータフィールド108がいずれであるかを伝える信号を電源制御部104に出力する。

10

【0067】

上述のように、演算装置106の必要とするデータが保存されているデータフィールド108に対して電源電圧供給を行うには、例えば図2の回路図を用いて説明すると、範囲230のスイッチ素子のうち、演算装置106の必要とするデータが保存されているデータフィールド108と接続されたスイッチ素子200aを導通状態とすればよい。

【0068】

そして、第5の処理として、第2の判断結果を伝える信号を受けた電源制御部104は、キャッシュメモリ102の備える複数のデータフィールド108のうち、演算装置106が必要とするデータが保存されているデータフィールド108に対して電源電圧供給を開始する（図3（C）参照。）。

20

【0069】

次に、第6の処理として、演算装置106が、電源電圧供給が行われているデータフィールド108に保存されたデータを読み出す。そして、第6の処理が行われた後に、キャッシュメモリ102への電源供給を停止する。キャッシュメモリ102の備えるメモリセルは不揮発性のメモリセルを用いて構成されているため、電源供給を停止してもデータを保存し続けることができる。

【0070】

以上が、本実施の形態における中央処理装置の駆動方法である。

30

【0071】

<本実施の形態の効果>

上述のように、データフィールド108、タグフィールド110およびバリッドビット112の構成要素であるメモリセルを不揮発性のメモリセルとし、また、演算装置106からキャッシュメモリ102へのアクセスが無い状態では、データフィールド108、タグフィールド110およびバリッドビット112への電源電圧供給を常に停止状態とし、キャッシュメモリ102へのアクセスが行われた場合において、電源制御部104を用いてデータフィールド108、タグフィールド110およびバリッドビット112に対して選択的に電源電圧供給を行える構造とすることにより、演算装置106からキャッシュメモリ102へのアクセスが生じた場合のみ、キャッシュメモリの一部を動作させて必要な処理を行うことができるため、中央処理装置の消費電力を大幅に削減することができる。

40

【0072】

そして、上述中央処理装置の駆動方法については、（1）電源制御部104を用いてバリッドビット112に対して電源電圧供給を行い、（2）演算装置106により複数のバリッドビット112のいずれが有効であるかを判断し、（3）有効であると判断されたキャッシュライン114のタグフィールド110のみに電源電圧供給を行い、（4）電源電圧供給が行われているタグフィールド110のうちのいずれに演算装置106の必要とするデータが保存されているかを演算装置106が判断し、（5）当該タグフィールド110を含むキャッシュライン114に備えられたデータフィールド108のみに電源電圧供給を行い、（6）演算装置106が、電源電圧供給が行われているデータフィールド10

50

8からデータを読み出す、といった駆動方法を採用すればよい。

**【0073】**

(実施の形態2)

本実施の形態では、実施の形態1に記載した中央処理装置100において、実施の形態1とは異なる駆動方法および、当該駆動方法を用いることによるメリットについて、図4を用いて説明する。

**【0074】**

本実施の形態に記載の駆動方法は、実施の形態1にて記載した中央処理装置と基本的には同様の構造を用いて行うことができるが、電源制御部の制御動作が一部異なっている。

10

**【0075】**

実施の形態1の電源制御部104は、図3(A)に示すように、バリッドビット112に対して電源電圧供給を行った後においても、全てのバリッドビット112に対して電源電圧供給を行い続ける、といった制御動作を行っている。

**【0076】**

また、図3(B)に示すように、選択されたタグフィールド110に対して電源電圧供給を行った後においても、選択されたタグフィールド110の全てに対して電源電圧供給を行い続ける、といった制御動作を行っている。

**【0077】**

中央処理装置100としてこのような制御動作の電源制御部104を用いた場合、電源制御部104は第1の判断(バリッドビット112に保存されたデータが有効か否かの判断。)、第2の判断(必要とするデータのアドレスがタグフィールドに保存されたデータと一致するか否かの判断。)および当該判断に基づいた電源電圧供給、という動作を行うのみでよいため、キャッシュメモリ102からのデータを高速に読み出したい場合などにおいて有効であると言える。

20

**【0078】**

これに対し、本実施の形態では、制御動作を一部変更した電源制御部104を用いることにより、中央処理装置100の消費電力を実施の形態1よりも更に少なくすることを目的としており、中央処理装置100に高い省電力性能を求める場合において有効であると言える。

**【0079】**

30

以下にて、制御動作を一部変更した電源制御部104を用いた場合における、中央処理装置100の駆動方法の一例について図4を用いて説明する。なお、図4は、本実施の形態に記載の駆動方法を行うことにより、キャッシュメモリ102内における電源供給状態がどのように変化するかを示した図である。

**【0080】**

なお、以下に記載する駆動方法は、実施の形態1にて記載した駆動方法と異なる部分を中心として記載するため、実施の形態1と同様の駆動方法を採用できる箇所については、詳細な説明を省略している。

**【0081】**

また、本実施の形態の説明は、実施の形態1と同様にキャッシュメモリ102に主記憶装置118のデータの一部が保存されているものとして説明を行う。

40

**【0082】**

まず、実施の形態1と同様に第1の処理を行い、バリッドビット112に電源電圧供給を行う。

**【0083】**

次に、第2の処理(各ラインのバリッドビット112に保存されたデータに基づいて演算装置106が第1の判断を行い、当該判断結果を伝える信号を電源制御部104に出力する。)を行うのだが、本実施の形態に記載の駆動方法では、第2の処理における第1の判断終了後または第1の判断時に、演算装置106が、有効なデータが保存されていない(データ"0"が保存されている、とも言える。)バリッドビット112への電源供給を停

50

止する信号を電源制御部 104 に出力し、当該信号を受けた電源制御部 104 が有効なデータが保存されていないバリッドビット 112 への電源電圧供給を停止する（以下、当該動作を第 7 の処理とも記載する。）。

#### 【0084】

上述の処理が行われることで、キャッシュメモリ 102 内での電源電圧供給状態は、図 4 (A) に示すように斜線の記載されている部分に電源電圧が供給される。

#### 【0085】

実施の形態 1 に記載の駆動方法を用いた場合、図 4 (A) の斜線部以外に、図 4 (A) の縦線部についても電源電圧供給が行われているが、上述第 7 の処理を行うことにより、縦線部への電源電圧供給を停止することができるため、中央処理装置 100 の消費電力を 10 低減することができる。

#### 【0086】

なお、第 7 の処理は、第 1 の判断終了時から第 2 の判断開始前の間に行えばよく、第 2 の処理にて行われる第 1 の判断終了後または第 1 の判断時に行われることが好ましい。つまり、中央処理装置 100 の消費電力低減効果を高めるには、タグフィールド 110 への電源電圧供給を行う前に、バリッドビット 112 の不要箇所（有効なデータが保存されていない箇所。）の電源電圧供給を停止することが好ましい。

#### 【0087】

次に、実施の形態 1 と同様に第 3 の処理を行い、上述第 2 の処理にて有効と判断されたバリッドビット 112 と同じラインのタグフィールド 110 に電源電圧供給を行う。

#### 【0088】

次に、第 4 の処理（電源電圧供給が行われているタグフィールド 110 に保存された管理情報に基づいて演算装置 106 が第 2 の判断を行い、当該判断結果を伝える信号を電源制御部 104 に出力する。）を行うのだが、本実施の形態に記載の駆動方法では、第 4 の処理における第 2 の判断終了後または第 2 の判断時に、演算装置 106 が必要とするデータが保存されているライン以外のタグフィールド 110 への電源供給を停止する信号を電源制御部 104 に出力し、当該信号を受けた電源制御部 104 が、演算装置 106 が必要とするデータが保存されていないラインのタグフィールド 110 への電源電圧供給を停止する（以下、当該動作を第 8 の処理とも記載する。）。

#### 【0089】

上述の処理により、キャッシュメモリ 102 内における電源電圧供給状態は、図 4 (B) に示すように斜線の記載されている部分に電源電圧が供給される。

#### 【0090】

実施の形態 1 に記載の駆動方法を用いた場合、図 4 (B) の斜線部以外に、図 4 (B) の縦線部についても電源電圧供給が行われているが、上述第 8 の処理を行うことにより、縦線部への電源電圧供給を停止することができるため、中央処理装置 100 の消費電力を 30 低減することができる。

#### 【0091】

なお、第 8 の処理は、第 2 の判断終了時から第 6 の処理開始間に行えばよく、第 4 の処理にて行われる第 2 の判断終了後または第 2 の判断時に行われることが好ましい。つまり、中央処理装置 100 の消費電力低減効果を高めるには、データフィールド 108 に保存されたデータを読み出す前に、タグフィールド 110 の不要箇所（演算装置 106 が必要とするデータが保存されているライン以外のタグフィールド 110。）の電源電圧供給を停止することが好ましい。

#### 【0092】

その後、実施の形態 1 と同様に、第 5 の処理および第 6 の処理を行った後に、キャッシュメモリ 102 への電源供給を停止する。キャッシュメモリ 102 の備えるメモリセルは不揮発性のメモリセルを用いて構成されているため、電源供給を停止してもデータを保存し続けることができる。

#### 【0093】

10

20

30

40

50

以上が、本実施の形態における中央処理装置の駆動方法である。

#### 【0094】

なお、本実施の形態では、中央処理装置100の消費電力低減効果を高めるために、第7の処理および第8の処理の両方を行う駆動方法について記載したが、必ずしも両方を行う必要はなく、第7の処理または第8の処理のいずれか一方のみを行ってもよい。第7の処理または第8の処理のいずれか一方を行うか、あるいは両方を行うかについては、中央処理装置100に必要とされる消費電力や動作速度を鑑み、実施者が適宜選択すればよい。

#### 【0095】

<本実施の形態の効果>

10

上述のように、電源制御部104に、制御動作として上述の第7の処理および第8の処理を行う電源制御部104を用い、上述の駆動方法にて中央処理装置を駆動することにより、消費電力を低く抑えることができる。

#### 【0096】

(実施の形態3)

本実施の形態では、実施の形態1にて記載した、OSトランジスタを構成要素の一部に使用した、不揮発性の特性を備えるメモリセルの構造についての説明を記載する。

#### 【0097】

不揮発性の特性を備えるメモリセルとしては、例えば図5に示す構成を挙げることができる。

20

#### 【0098】

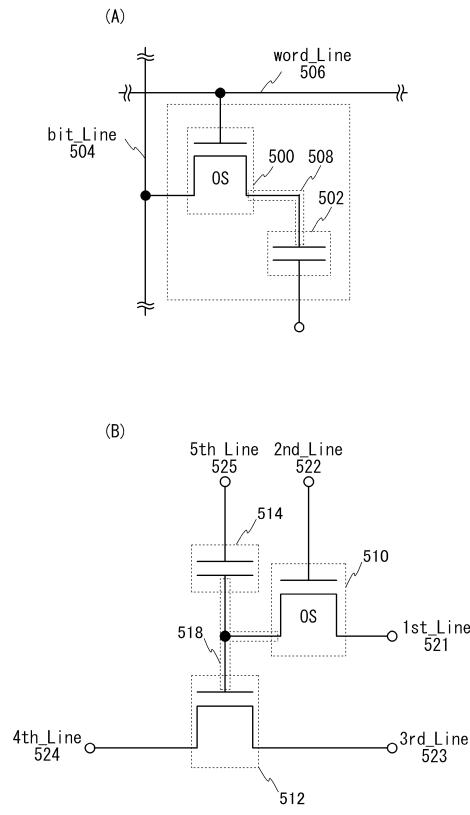

図5(A)は、不揮発性の特性を備えるメモリセルの構造の一例であり、トランジスタ500と容量素子502が直列に接続されている。構造自体はDRAMなどで一般的に用いられている回路構成であるが、トランジスタ500としてOSトランジスタが用いられている。そして、トランジスタ500のソースおよびドレインの一方がビット線504に、ゲートがワード線506と接続されている。また、容量素子502を構成する一方の電極はトランジスタ500のソースおよびドレインの他方と接続されており、他方の電極は定電位(例えば接地電位など。)に接続されている。

#### 【0099】

トランジスタ500に用いられる酸化物半導体材料を用いた半導体層は、エネルギーギャップが3.0電子ボルト以上であり、シリコンのバンドギャップ(1.1電子ボルト)と比較して非常に大きい。

30

#### 【0100】

トランジスタのオフ抵抗(トランジスタがオフ状態の時における、ソースとドレイン間の抵抗をいう。)は、チャネルが形成される半導体層における熱的に励起するキャリアの濃度に反比例する。ドナーやアクセプタによるキャリアが全く存在しない状態(真性半導体)であっても、シリコンの場合にはバンドギャップが1.1電子ボルトであるため、室温(300K)での熱励起キャリアの濃度は $1 \times 10^{11} \text{ cm}^{-3}$ 程度である。

#### 【0101】

一方、例えばバンドギャップが3.2電子ボルトの半導体(酸化物半導体を想定。)の場合では熱励起キャリアの濃度は $1 \times 10^{-7} \text{ cm}^{-3}$ 程度となる。電子移動度が同じ場合、抵抗率は、キャリア濃度に反比例するので、バンドギャップ3.2電子ボルトの半導体の抵抗率は、シリコンより18桁も大きい。

40

#### 【0102】

このようなバンドギャップの広い酸化物半導体材料を半導体層に適用したOSトランジスタは極めて低いオフ電流を実現できる。

#### 【0103】

したがって、図5(A)のように容量素子502に接続されたトランジスタ500(容量素子への信号の入出力を管理するトランジスタ、とも表現できる。)をOSトランジスタとし、まず、ワード線506からの信号によりトランジスタ500をオン状態とし、ビ

50

ット線 504 からの信号を、容量素子 502 を構成する電極の一方に与えた状態で、ワード線 506 からの信号によりトランジスタ 500 をオフ状態とする。これにより、メモリセルに電源の供給が行われない状況でもトランジスタ 500 のソースおよびドレインの他方と容量素子 502 を構成する電極の一方の間の領域（図中のノード 508 に相当。）に、ビット線 504 を通して入力された信号を長期間保持できる（書き込み。）。

#### 【0104】

その後、ワード線 506 からの信号によりトランジスタ 500 をオン状態とすることでき、ノード 508 に保存されたデータを読み出すことができる（読み出し。）。なお、信号読み出しに際し、当該信号が微小な場合は、必要に応じて出力経路にセンスアンプなどの信号増幅器を設けてもよい。

10

#### 【0105】

図 5 (B) は、不揮発性の特性を備えるメモリセルの構造の一例であり、第 1 のトランジスタ 510、第 2 のトランジスタ 512 および容量素子 514 を有し、第 1 のトランジスタ 510 のソースおよびドレインの一方が第 1 の配線 521 (1st Line) と、ゲートが第 2 の配線 522 (2nd Line) 接続され、トランジスタ 512 のソースおよびドレインの一方が第 3 の配線 523 (3rd Line) と、他方が第 4 の配線 524 (4th Line) と接続されている。また、容量素子 514 を構成する電極の一方が第 1 のトランジスタ 510 のソースおよびドレインの他方ならびに第 2 のトランジスタ 512 のゲートと接続されており、電極の他方は第 5 の配線 525 (5th Line) に接続されている。

20

#### 【0106】

図 5 (B) のように、第 1 のトランジスタ 510 は OS トランジスタであるため、第 2 の配線 522 からの信号により第 1 のトランジスタ 510 をオン状態とし、第 1 の配線 521 からの信号を第 2 のトランジスタ 512 のゲートおよび容量素子 514 を構成する電極の一方に与えた状態で、第 2 の配線 522 からの信号により第 1 のトランジスタ 510 をオフ状態とする。これにより、メモリセルに電源の供給が行われない状況でも第 1 のトランジスタ 510 のソースおよびドレインの他方、第 2 のトランジスタ 512 のゲートおよび容量素子 514 を構成する電極の一方の間の領域（図中のノード 518 に相当。）に、第 1 の配線 521 を通して入力された信号を長期間保持できる（書き込み。）。

#### 【0107】

30

データの読み出しについては、まず第 3 の配線 523 に所定の電位（定電位）を与えた状態で、第 5 の配線 525 に適切な電位（読み出し電位）を与えると、ノード 518 に保持された電荷量に応じて、第 4 の配線 524 は異なる電位をとる。一般に、トランジスタ 512 を n チャネル型とすると、トランジスタ 512 のゲート電極に High レベル電荷が与えられている場合の見かけのしきい値電圧  $V_{th-H}$  は、トランジスタ 512 のゲート電極に Low レベル電荷が与えられている場合の見かけのしきい値電圧  $V_{th-L}$  より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ 512 を「オン状態」とするために必要な第 5 の配線 525 の電位をいうものとする。したがって、第 5 の配線 525 の電位を  $V_{th-H}$  と  $V_{th-L}$  の間の電位  $V_0$  とすることにより、トランジスタ 512 のゲートに与えられた電荷を判別できる。例えば、書き込みにおいて、High レベルの電荷が与えられていた場合には、第 5 の配線 525 の電位が  $V_0 (> V_{th-H})$  となれば、トランジスタ 512 は「オン状態」となる。Low レベルの電荷が与えられていた場合には、第 5 の配線 525 の電位が  $V_0 (< V_{th-L})$  となつても、トランジスタ 512 は「オフ状態」のままである。このため、第 4 の配線 524 の電位を観ることで、保持されている情報を読み出すことができる。

40

#### 【0108】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、トランジスタ 512 のゲートの状態にかかわらずトランジスタ 512 が「オフ状態」となるような電位、つまり、 $V_{th-H}$  より小さい電位を第 5 の配線 525 に与えればよい。または、トランジ

50

スタ 512 のゲートの状態にかかわらずトランジスタ 512 が「オン状態」となるような電位、つまり、 $V_{th\_L}$  より大きい電位を第 5 の配線 525 に与えればよい。

#### 【0109】

OSトランジスタであるトランジスタ 500 や第 1 のトランジスタ 510 は、シリコンなどの薄膜トランジスタと同様の装置や方法を用いることが可能であり、新たな設備投資や作製方法検討の負担が少ないという長所もある。また、OSトランジスタは、半導体層として酸化物半導体材料以外を用いたトランジスタ（例えば、半導体層として単結晶シリコンを用いたトランジスタなど。）と積層させた構造とすることができる。

#### 【0110】

ここで、図 5 (B) に記載の回路構成において、第 1 のトランジスタ 510 として OSトランジスタを、第 2 のトランジスタ 512 として活性層に単結晶シリコンを用いたトランジスタを積層させた構造のメモリセル断面の一例を図 6 に示す。10

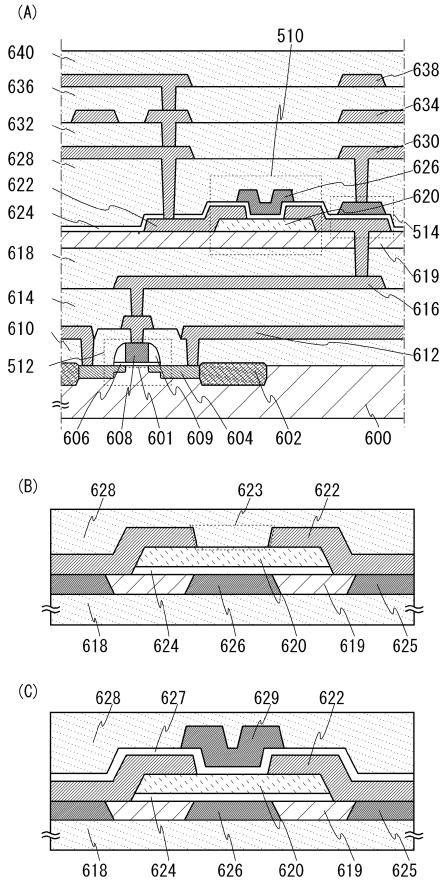

#### 【0111】

図 6 に示すメモリセルにおいて、単結晶シリコン基板 600 上に、第 2 のトランジスタ 512 が設けられ、前記第 2 のトランジスタ 512 上に第 1 のトランジスタ 510 が設けられている。

#### 【0112】

第 2 のトランジスタ 512 は、単結晶シリコン基板 600 中に設けられた、ソースまたはドレインとして機能する低抵抗領域 604 と、単結晶シリコン基板 600 中に位置し、低抵抗領域 604 に挟まれた領域に形成されるチャネル形成領域 601 と、チャネル形成領域 601 上のゲート絶縁膜 606 と、ゲート絶縁膜 606 を挟んでチャネル形成領域 601 上に設けられたゲート電極 608 を含んで構成されている。20

#### 【0113】

なお、第 2 のトランジスタ 512 は、単結晶シリコン基板 600 中に設けられた分離層 602 により他のトランジスタと分離されており、第 2 のトランジスタ 512 の低抵抗領域 604 は第 2 のトランジスタ 512 を覆う層間膜 610 上に設けられた導電膜 612 と電気的に接続されている。また、ゲート電極 608 には、側壁を覆う側壁絶縁膜 609 が設けられている。

#### 【0114】

分離層 602、低抵抗領域 604、ゲート絶縁膜 606、ゲート電極 608、側壁絶縁膜 609、層間膜 610 および導電膜 612 に用いる材料や形成方法については特段の限定はなく、公知の技術を用いることができる。30

#### 【0115】

第 1 のトランジスタ 510 は、絶縁膜 619 上に設けられた酸化物半導体膜 620 と、酸化物半導体膜 620 と電気的に接続され、第 1 のトランジスタ 510 のソースやドレインとして機能する導電膜 622 と、酸化物半導体膜 620 上に設けられたゲート絶縁膜 624 と、ゲート絶縁膜 624 を挟んで酸化物半導体膜 620 上に設けられたゲート電極 626 を含んで構成されている。

#### 【0116】

絶縁膜 619 としては、スパッタリング法、真空蒸着法やスパッタリング法などの物理気相成長法 (PVD : Physical Vapor Deposition) やプラズマ CVD 法などの化学気相成長法 (CVD : Chemical Vapor Deposition) を用いて、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、窒化酸化アルミニウムなどの無機絶縁膜を成膜して用いることができる。40

#### 【0117】

なお、絶縁膜 619 は加熱処理により酸素を放出する膜が形成されていることが好ましい。これは、第 1 のトランジスタ 510 において、チャネル形成領域に酸素欠損が存在すると、酸素欠損に起因して電荷が生じる場合がある。一般に酸化物半導体膜の酸素欠損は一部がドナーとなりキャリアである電子を放出する。この結果、トランジスタのしきい値50

電圧がマイナス方向にシフトしてしまうためである。

#### 【0118】

絶縁膜619を加熱処理により酸素を放出する膜とすることで、加熱処理によって酸素供給膜中の酸素の一部を放出できるので、酸化物半導体膜に酸素を供給し、酸化物半導体膜中の酸素欠損を補填することができるため、トランジスタのしきい値電圧のマイナス方向へのシフトを抑制できる。特に、酸素供給膜中に少なくとも化学量論的組成を超える量の酸素が存在することが好ましい。例えば、酸素供給膜として酸化シリコンを用いる場合、 $\text{SiO}_{2+}$ （ただし、 $> 0$ ）で表される酸化シリコン膜を用いることが好ましい。なお、このような化学量論的組成よりも酸素を過剰に含む領域（以下、酸素過剰領域と記載する場合もある。）は、酸素供給膜の少なくとも一部に存在していればよい。

10

#### 【0119】

なお、上述の「加熱処理により酸素を放出する膜」とは、TDS（Thermal Desorption Spectroscopy：昇温脱離ガス分光法）分析にて、520まで加熱した際、酸素原子に換算された酸素の放出量が $1.0 \times 10^{19}$  atoms/cm<sup>2</sup>以上、好ましくは $3.0 \times 10^{19}$  atoms/cm<sup>2</sup>以上、さらに好ましくは $1.0 \times 10^{20}$  atoms/cm<sup>2</sup>以上、さらに好ましくは $3.0 \times 10^{20}$  atoms/cm<sup>2</sup>以上であることをいう。

#### 【0120】

ここで、TDS分析を用いた酸素の放出量の測定方法について、以下に説明する。

#### 【0121】

TDS分析による気体の放出量は、その気体イオンに由来するピークの面積に比例する。このため、試料のピークの面積と標準試料のピークの面積との比により、気体の放出量を計算することができる。標準試料のピークの面積は、所定の原子密度を有する試料から放出された気体のイオンに由来するピーク面積に対する原子密度の割合である。

20

#### 【0122】

例えば、標準試料である所定の密度の水素を含むシリコンウェハのTDS分析結果、および測定試料である絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量（ $N_{\text{O}_2}$ ）は、式（1）で求めることができる。ここで、TDS分析で質量電荷比（M/z）が32で検出されるイオンの全てが酸素分子由来と仮定する。M/zが32のものとしてはCH<sub>3</sub>O<sup>+</sup>が挙げられるが、存在する可能性が低いため無視することができる。また、酸素原子の同位体であるM/zが17の酸素原子およびM/zが18の酸素原子を含む酸素分子についても、自然界における極めて小さいため考慮しない。

30

#### 【0123】

##### 【数1】

$$N_{\text{O}_2} = \frac{N_{\text{H}_2}}{S_{\text{H}_2}} \times S_{\text{O}_2} \times \alpha \quad (1)$$

#### 【0124】

$N_{\text{H}_2}$ は、標準試料から脱離した水素分子を密度で換算した値である。 $S_{\text{H}_2}$ は、標準試料を用いて検出された水素イオンのピーク面積である。ここで、標準試料の基準値を、 $N_{\text{H}_2} / S_{\text{H}_2}$ とする。 $S_{\text{O}_2}$ は、絶縁膜を用いて検出された酸素イオンのピーク面積である。は、TDS分析におけるスペクトル強度に影響する係数である。式（1）の詳細に関しては、特開平6-275697公報を参照する。なお、測定は、例えば電子科学株式会社製の昇温脱離分析装置EMD-WA1000S/Wを用い、標準試料として $1 \times 10^{16}$  atoms/cm<sup>2</sup>の水素原子を含むシリコンウェハを用いて行うことができる。

40

#### 【0125】

TDS分析において、酸素の一部は酸素原子として検出される。酸素分子と酸素原子の比率は、酸素分子のイオン化率から算出することができる。定数 $\alpha$ は酸素分子のイオン化率を含むため、酸素分子の放出量をから酸素原子の放出量を見積もることができる。

#### 【0126】

50

なお、 $N_{O_2}$  は酸素分子の放出量である。酸素原子に換算したときの放出量は、酸素分子の放出量の 2 倍となる。

#### 【0127】

膜中への酸素の導入は、酸素雰囲気下による熱処理や、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、酸素を含む雰囲気下で行うプラズマ処理などを用いることができる。

#### 【0128】

また、過剰酸素を含む絶縁膜の水素濃度が、 $7.2 \times 10^{20} \text{ atoms/cm}^3$  以上である場合には、トランジスタの初期特性のバラツキが増大、トランジスタの電気特性の L 長依存性が増大し、さらに外部ストレスによって、大きく劣化するため、過剰酸素を含む絶縁膜の水素濃度は、 $7.2 \times 10^{20} \text{ atoms/cm}^3$  未満とすることが好ましい。<sup>10</sup> 即ち、酸化物半導体膜の水素濃度は  $5 \times 10^{19} \text{ atoms/cm}^3$  以下、かつ、過剰酸素を含む絶縁膜の水素濃度は、 $7.2 \times 10^{20} \text{ atoms/cm}^3$  未満とすることが好ましい。水素濃度の低い膜を形成する方法については、後述にて詳細を記載する。

#### 【0129】

なお、加熱処理により酸素供給膜から酸化物半導体膜に酸素を供給する場合、酸素供給膜から放出される酸素が酸化物半導体膜に効率的に供給されるように、酸素供給膜の下層（つまり、酸素供給膜の酸化物半導体膜と接する面とは逆の面。）に酸素透過性や水蒸気透過性（水分透過性とも表現できる。）の低い膜（以下、バリア膜と記載する場合もある。）を形成することが好ましい。例えば、酸素供給膜の下層にバリア膜として、酸化アルミニウム膜、酸化窒化アルミニウム膜、窒化酸化アルミニウム膜などを形成すればよい。<sup>20</sup> なお、酸化アルミニウム膜を用いる場合、膜を高密度（膜密度  $3.2 \text{ g/cm}^3$  以上、好みくは  $3.6 \text{ g/cm}^3$  以上）とすることが好ましい。

#### 【0130】

酸化物半導体膜 620 に用いる酸化物半導体材料としては、少なくともインジウム（In）を含む。特に In と亜鉛（Zn）を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム（Ga）を有することが好ましい。また、スタビライザーとしてスズ（Sn）を有することが好ましい。また、スタビライザーとしてハフニウム（Hf）を有することが好ましい。また、スタビライザーとしてアルミニウム（Al）を有することが好ましい。また、スタビライザーとしてジルコニウム（Zr）を有することが好ましい。<sup>30</sup>

#### 【0131】

また、他のスタビライザーとして、ランタノイドである、ランタン（La）、セリウム（Ce）、プラセオジム（Pr）、ネオジム（Nd）、サマリウム（Sm）、ユウロピウム（Eu）、ガドリニウム（Gd）、テルビウム（Tb）、ジスプロシウム（Dy）、ホルミウム（Ho）、エルビウム（Er）、ツリウム（Tm）、イッテルビウム（Yb）、ルテチウム（Lu）のいずれか一種あるいは複数種を有してもよい。

#### 【0132】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である In - Zn 系酸化物、In - Mg 系酸化物、In - Ga 系酸化物、三元系金属の酸化物である In - Ga - Zn 系酸化物（IGZO とも表記する）、In - Al - Zn 系酸化物、In - Sn - Zn 系酸化物、In - Hf - Zn 系酸化物、In - La - Zn 系酸化物、In - Ce - Zn 系酸化物、In - Pr - Zn 系酸化物、In - Nd - Zn 系酸化物、In - Sm - Zn 系酸化物、In - Eu - Zn 系酸化物、In - Gd - Zn 系酸化物、In - Tb - Zn 系酸化物、In - Dy - Zn 系酸化物、In - Ho - Zn 系酸化物、In - Er - Zn 系酸化物、In - Tm - Zn 系酸化物、In - Yb - Zn 系酸化物、In - Lu - Zn 系酸化物、四元系金属の酸化物である In - Sn - Ga - Zn 系酸化物、In - Hf - Ga - Zn 系酸化物、In - Al - Ga - Zn 系酸化物、In - Sn - Al - Zn 系酸化物、In - Sn - Hf - Zn 系酸化物、In - Hf - Al - Zn 系酸化物を用いることができる。<sup>40</sup>

**【0133】**

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

**【0134】**

また、酸化物半導体として、 $InMO_3(ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素又は複数の金属元素を示す。また、酸化物半導体として、 $In_2SnO_5(ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。

**【0135】**

以下では、酸化物半導体膜の構造について説明する。

**【0136】**

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜などをいう。

**【0137】**

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

**【0138】**

微結晶酸化物半導体膜は、例えば、1 nm以上10 nm未満の大きさの微結晶（ナノ結晶ともいう。）を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。

**【0139】**

CAAC-OS膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が100 nm未満の立方体内に収まる大きさである。従って、CAAC-OS膜に含まれる結晶部は、一辺が10 nm未満、5 nm未満または3 nm未満の立方体内に収まる大きさの場合も含まれる。CAAC-OS膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、CAAC-OS膜について詳細な説明を行う。

**【0140】**

CAAC-OS膜を透過型電子顕微鏡（TEM：Transmission Electron Microscope）によって観察すると、結晶部同士の明確な境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0141】**

CAAC-OS膜を、試料面と平行な方向からTEMによって観察（断面TEM観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状を有しており、CAAC-OS膜の被形成面または上面と平行に配列する。

**【0142】**

一方、CAAC-OS膜を、試料面と垂直な方向からTEMによって観察（平面TEM観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0143】**

これらの断面TEM観察および平面TEM観察より、CAAC-OS膜の結晶部は配向性を有していることがわかる。

10

20

30

40

50

## 【0144】

C AAC - OS 膜に対し、X線回折(XRD : X-Ray Diffraction)装置を用いて構造解析を行うと、例えば $InGaN_4O_4$ の結晶を有するAAC - OS膜のout-of-plane法による解析では、回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、 $InGaN_4O_4$ の結晶の(009)面に帰属されることから、AAC - OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に垂直な方向を向いていることが確認できる。

## 【0145】

一方、AAC - OS膜に対し、c軸に垂直な方向からX線を入射させるin-plane法による解析では、2θが56°近傍にピークが現れる場合がある。このピークは、 $InGaN_4O_4$ の結晶の(110)面に帰属される。 $InGaN_4O_4$ の単結晶酸化物半導体膜であれば、2θを56°近傍に固定し、試料面の法線ベクトルを軸(c軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが6本観察される。これに対し、AAC - OS膜の場合は、2θを56°近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

## 【0146】

以上のことから、AAC - OS膜では、異なる結晶部間ではa軸およびb軸の配向は不規則であるが、c軸配向性を有し、かつc軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面TEM観察で確認された層状に配列した金属原子の各層は、結晶のab面に平行な面である。

## 【0147】

なお、結晶部は、AAC - OS膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、AAC - OS膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、AAC - OS膜の形状をエッチングなどによって変化させた場合、結晶のc軸がAAC - OS膜の被形成面または上面の法線ベクトルと平行にならないこともある。

## 【0148】

また、AAC - OS膜中の結晶化度が均一でなくてもよい。例えば、AAC - OS膜の結晶部が、AAC - OS膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、AAC - OS膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

## 【0149】

なお、 $InGaN_4O_4$ の結晶を有するAAC - OS膜のout-of-plane法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、AAC - OS膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。AAC - OS膜は、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

## 【0150】

C AAC - OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

## 【0151】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、AAC - OS膜のうち、二種以上を有する積層膜であってもよい。

## 【0152】

また、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

## 【0153】

10

20

30

40

50

また、C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

【0154】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など。）を低減すればよい。また、成膜ガス中の不純物濃度（水素、水、二酸化炭素および窒素など。）を低減すればよい。具体的には、露点が - 80 以下、好ましくは - 100 以下、さらに好ましくは - 120 以下である成膜ガスを用いる。

【0155】

また、成膜時の基板加熱温度を高めることで、基板付着後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

【0156】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30 体積%以上、好ましくは 100 体積%とする。成膜ガス中の酸素割合を高めることで、C A A C - O S 膜中に余分な原子（例えば、希ガス原子など。）が含まれないため、C A A C - O S 膜が形成されやすくなる。

【0157】

スパッタリング用ターゲットの一例として、In - Ga - Zn - O 化合物ターゲットについて以下に示す。

【0158】

In<sub>X</sub>O<sub>Y</sub> 粉末、GaO<sub>Y</sub> 粉末およびZnO<sub>Z</sub> 粉末を所定の mol 数比で混合し、加圧処理後、1000 以上 1500 以下の温度で加熱処理をすること多結晶である In - Ga - Zn - O 化合物ターゲットとする。なお、X、Y および Z は任意の正数である。ここで、所定の mol 数比は、例えば、In<sub>X</sub>O<sub>Y</sub> 粉末、GaO<sub>Y</sub> 粉末およびZnO<sub>Z</sub> 粉末が、2 : 2 : 1、8 : 4 : 3、3 : 1 : 1、1 : 1 : 1、4 : 2 : 3 または 3 : 1 : 2 である。なお、粉末の種類、およびその混合する mol 数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。

【0159】

なお、酸化物半導体膜 620 中の酸素欠損をできるだけ少なくことが好ましいため、成膜雰囲気中のガス種に占める酸素ガスの割合が高い状態で成膜することが好ましく、装置内に酸素を導入することが可能で、かつ、ガス流量の調整ができるスパッタリング装置を用いることが好ましいといえる。そして、スパッタリング装置の成膜チャンバー内への導入ガスは、全体の 90 % 以上を酸素ガスとして、酸素ガスに加えて他のガスを用いる場合は、当該ガスは希ガスを用いることが望ましい。また、より好ましくは成膜チャンバー内への導入ガスを酸素ガスのみとし、成膜雰囲気中のガス種に占める酸素ガスの割合を極力 100 % に近づけることが望ましい。

【0160】

また、酸化物半導体膜 620 に水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体膜 620 において、水素濃度は、 $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 未満、好ましくは  $1 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $5 \times 10^{-7}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{-6}$  atoms / cm<sup>3</sup> 以下とすることが望ましい。なお、上述の酸化物半導体膜 620 中の水素濃度は、二次イオン質量分析法 (SIMS: Secondary Ion Mass Spectrometry) で測定されるものである。

【0161】

10

20

30

40

50

上述の理由により、酸化物半導体膜 620 を成膜する際に用いるガスとしては、水、水素、水酸基又は水素化物などの不純物が含まれないことが好ましい。または、純度が 6 N 以上好ましくは 7 N 以上（即ち、ガス中の不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下）のガスを用いることが好ましい。

#### 【 0162 】

また、酸化物半導体膜 620 を成膜するにあたり、成膜室内の水分（水、水蒸気、水素、水酸基または水素化物を含む）を除去するために、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段は、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水 ( $H_2O$ ) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜 620 に含まれる水素、水分などの不純物の濃度を低減できる。10

#### 【 0163 】

なお、酸化物半導体膜 620 は、複数の酸化物半導体膜が積層された構造でもよい。例えば、酸化物半導体膜 620 を、第 1 の酸化物半導体膜、第 2 の酸化物半導体膜および第 3 の酸化物半導体膜の積層として、各々を異なる組成としてもよい。例えば、第 1 の酸化物半導体膜および第 3 の酸化物半導体膜に三元系金属の酸化物を用い、第 2 の酸化物半導体膜に二元系金属の酸化物を用いてもよい。また、同一成分を含む材料を用いることが好ましい。同一成分を含む材料を用いる場合、第 1 の酸化物半導体膜の結晶層を種として第 1 の酸化物半導体膜上に第 2 の酸化物半導体膜を形成できるため、第 2 の酸化物半導体膜の結晶成長が行いややすくなる。なお、第 3 の酸化物半導体膜についても同様のことが言える。また、同一成分を含む材料である場合には、密着性などの界面物性や電気的特性も良好である。20

#### 【 0164 】

また、第 1 の酸化物半導体膜、第 2 の酸化物半導体膜および第 3 の酸化物半導体膜の構成元素を同一とし、組成を異ならせててもよい。例えば、第 1 の酸化物半導体膜および第 3 の酸化物半導体膜の原子数比を  $In : Ga : Zn = 1 : 1 : 1$  とし、第 2 の酸化物半導体膜の原子数比を  $In : Ga : Zn = 3 : 1 : 2$  としてもよい。また、第 1 の酸化物半導体膜および第 3 の酸化物半導体膜の原子数比を  $In : Ga : Zn = 1 : 3 : 2$  とし、第 2 の酸化物半導体膜の原子数比を  $In : Ga : Zn = 3 : 1 : 2$  としてもよい。30

#### 【 0165 】

この時、第 2 の酸化物半導体膜は  $In > Ga$  の含有率を  $In > Ga$  とするといい。また第 1 の酸化物半導体膜および第 3 の酸化物半導体膜の  $In > Ga$  の含有率を  $In > Ga$  とするといい。

#### 【 0166 】

酸化物半導体では主として重金属の s 軌道がキャリア伝導に寄与しており、 $In$  の含有率を多くすることにより s 軌道のオーバーラップが多くなる傾向があるため、 $In > Ga$  の組成となる酸化物は  $In > Ga$  の組成となる酸化物と比較して高い移動度を備える。また、 $Ga$  は  $In$  と比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、 $In > Ga$  の組成となる酸化物は  $In > Ga$  の組成となる酸化物と比較して安定した特性を備える。40

#### 【 0167 】

絶縁膜 619 やゲート絶縁膜 624 と接しない第 2 の酸化物半導体膜に  $In > Ga$  の組成となる酸化物半導体を適用し、絶縁膜 619 やゲート絶縁膜 624 と接する第 1 の酸化物半導体膜や第 3 の酸化物半導体膜に  $In > Ga$  の組成となる酸化物半導体を適用することで、トランジスタの移動度および信頼性を高めることが可能となる。

#### 【 0168 】

なお、酸化物半導体膜に接して酸化物半導体膜とは異なる膜（図中では、絶縁膜 619 やゲート絶縁膜 624 など。）を形成する際に、酸化物半導体膜に接して形成される膜か50

ら酸化物半導体膜中に不純物が拡散する恐れがある。たとえば、絶縁膜619やゲート絶縁膜624中に含まれるシリコンやカーボンなどが酸化物半導体膜中に拡散すると、トランジスタの電気特性に悪影響を及ぼす可能性がある。

#### 【0169】

しかしながら、上述のように高い移動度を備える酸化物半導体膜（つまり、酸化物半導体膜のうち、キャリアパスとして主に機能する部分。）を酸化物半導体膜に接する膜（図中では、絶縁膜619やゲート絶縁膜624など。）から離すことにより、不純物拡散に起因したトランジスタの電気特性の悪影響を抑制することができる。

#### 【0170】

なお、酸化物半導体膜620を形成するための膜を成膜した後、または、酸化物半導体膜620を形成した後に、酸化物半導体膜に対して、以下に記載する「脱水化処理（脱水素化処理）」および「過酸化処理」を行ってもよい。勿論、当該処理を行わなくても酸化物半導体膜620を活性層として用いたトランジスタの電気特性が良好であるなら、当該処理は必ずしも行う必要はない。10

#### 【0171】

##### <脱水化処理（脱水素化処理）についての説明>

脱水化処理（脱水素化処理）としては、300以上700以下、または基板の歪み点未満の温度で基板を加熱すればよい。当該熱処理を行うことで、過剰な水素（水や水酸基を含む）を除去することが可能である。

#### 【0172】

熱処理装置は電気炉、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いることができる。例えば、LRTA（Lamp Rapid Thermal Anneal）装置、GRTA（Gas Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性ガスが用いられる。20

#### 【0173】

例えば、当該熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出すGRTA処理を行ってもよい。GRTA処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。30

#### 【0174】

なお、不活性ガス雰囲気としては、窒素、または希ガス（ヘリウム、ネオン、アルゴン等）を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.9999%）以上（すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下）とする。40

#### 【0175】

##### <過酸化処理についての説明>

上述の脱水化又は脱水素化処理を行うと、酸化物半導体膜を構成する主成分材料である酸素が同時に脱離して減少してしまうおそれがある。よって、脱水化又は脱水素化処理を行った場合、酸化物半導体膜中に、酸素を供給することが好ましい。

#### 【0176】

酸化物半導体膜中の酸素欠損を補填する方法としては、例えば、酸化物半導体膜に対して脱水化処理（脱水素化処理）を行った後、同じ炉に高純度の酸素ガス、一酸化二窒素ガ50

ス、高純度の亜酸化窒素ガス、又は超乾燥エア（C R D S（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が20 ppm（露点換算で-55以下、好ましくは1 ppm以下、より好ましくは10 ppb以下の空気）を導入すればよい。酸素ガスまたは一酸化二窒素ガスに、水、水素などが含まれないことが好ましい。または、熱処理装置に導入する酸素ガスまたは一酸化二窒素ガスの純度を、6N以上好ましくは7N以上（即ち、酸素ガスまたは一酸化二窒素ガス中の不純物濃度を1 ppm以下、好ましくは0.1 ppm以下）とすることが好ましい。なお、上述の加熱処理の際に装置内の圧力を高圧状態とすることにより、酸化物半導体膜中に酸素を効率的に添加することができる。

## 【0177】

10

また、酸化物半導体膜中の酸素欠損を補填する他の方法としては、例えば、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いて、酸化物半導体膜に酸素（少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む）を添加する方法を用いることもできる。

## 【0178】

上述のように、成膜後の酸化物半導体膜には、脱水化処理（脱水素化処理）を行い水素もしくは水分を酸化物半導体から除去して不純物が極力含まれないように高純度化し、脱水化処理（脱水素化処理）によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給（過酸素化とも表現できる。）して酸素欠損を補填することができる。

20

## 【0179】

導電膜622としては、真空蒸着法やスパッタリング法などの物理気相成長法（PVD：Physical Vapor Deposition）やプラズマCVD法などの化学気相成長法（CVD：Chemical Vapor Deposition）を用いて、タンタル（Ta）、タンクステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ネオジム（Nd）から選ばれた元素、又は前記元素を主成分とする合金材料もしくは化合物材料を含む膜で形成すればよい。また、導電膜としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、Ag Pd Cu合金膜を用いてもよい。

## 【0180】

30

ただし、酸化物半導体膜620と接する金属膜（つまり、導電膜622）として酸素親和性の高い金属を用いると、酸化物半導体膜620から酸素を引き抜きやすく、酸化物半導体膜620が変質してしまう恐れがある。

## 【0181】

そのため、酸化物半導体膜620に接する導電膜622には、酸素親和性の低い金属を用いることが好ましい。例えば、タンクステン膜、チタン膜またはモリブデン膜を用いることができる。導電膜622が積層構造である場合、少なくとも導電膜622の酸化物半導体膜620と接する層に酸素親和性の低い金属を用い、その他の層については上述の材料、例えばアルミニウムや銅などの低抵抗な導電性材料を用いることが好ましい。

## 【0182】

40

ゲート絶縁膜624は、絶縁膜619の説明にて記載した方法および材料を用いて形成すればよく、絶縁膜619と同様に加熱処理により酸素を放出する膜であることが好ましい。

## 【0183】

ゲート電極626は、導電膜622の説明にて記載した方法および材料を用いて形成すればよい。

## 【0184】

なお、ゲート電極626は、少なくともゲート絶縁膜624と接する面に、酸化物半導体膜620として用いる膜よりも仕事関数の大きな膜を用いることが好ましい。当該膜としては、窒素を含むIn-Ga-Zn-O膜、窒素を含むIn-Sn-O膜、窒素を含む

50

In-Ga-O膜、窒素を含むIn-Zn-O膜、窒素を含むSn-O膜、窒素を含むIn-O膜、金属窒化膜（InN、SiNなど）などの、窒素を含む金属酸化物膜などを用いることができる。これらの膜は5eV（電子ボルト）以上、好ましくは5.5eV（電子ボルト）以上の仕事関数を有し、当該膜をゲート電極として用いた場合、トランジスタのしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子（本実施の形態等では、第1のトランジスタ510が、ノーマリーオフのスイッチング素子に相当。）を実現できる。

#### 【0185】

なお、図6(A)のように、第2のトランジスタ512が形成された層と、第1のトランジスタ510が形成された層の間に、複数の層間膜（図中では、層間膜614および層間膜618。）や導電膜（図中では、導電膜616。）を形成してもよい。

10

#### 【0186】

層間膜614、層間膜618および導電膜616については、層間膜や導電膜として一般的に用いられる、公知の方法および材料を用いて形成すればよい。なお、層間膜618上には第1のトランジスタ510を形成するため、層間膜618形成後に平坦化処理（例えばCMP処理など。）を行い、層間膜618表面の平坦性を高めることが好ましい。

#### 【0187】

OSトランジスタは、他のトランジスタとの間に複数の層や導電膜を挟んで形成することができ、回路構成の自由度を高めることができる。

20

#### 【0188】

また、図6(A)のように、第1のトランジスタ510上に、複数の層間膜（図中では、層間膜628、層間膜632、層間膜636および層間膜640。）や導電膜（図中では、導電膜630、導電膜634および導電膜638。）を形成してもよい。

#### 【0189】

層間膜628、層間膜632、層間膜636および層間膜640、ならびに、導電膜630、導電膜634および導電膜638については、層間膜や導電膜として一般的に用いられる、公知の方法および材料を用いて形成すればよい。

#### 【0190】

OSトランジスタは上述のように上層に複数の層や導電膜を形成することができるため、OSトランジスタと他のトランジスタとの接続に用いる貫通配線の膜厚方向の長さを短くすることができ、このような点からも回路構成の自由度を高めることができると見える。また、貫通配線の形成自体も行いやすいと言える。

30

#### 【0191】

なお、上述では第1のトランジスタ510の構造として、酸化物半導体膜620上にソースやドレインとして機能する導電膜622およびゲート電極626が形成された、いわゆるTGTG（トップゲートトップコンタクト）構造を記載したが、当該構造に限定されることはない。

#### 【0192】

例えば、ソースやドレインとして機能する導電膜622が酸化物半導体膜620の下に形成されたTGB（トップゲートボトムコンタクト）構造でもよい。

40

#### 【0193】

また、図6(B)のように、ゲート絶縁膜624を挟んで酸化物半導体膜620の下にゲート電極626が形成されたBGTG（ボトムゲートトップコンタクト）構造でもよいし、図6(B)においてソースやドレインとして機能する導電膜622が酸化物半導体膜620の下に形成されたBGB（ボトムゲートボトムコンタクト）構造でもよい。

#### 【0194】

ソースやドレインとして機能する導電膜622は、図6(B)のようにゲート電極626と同じ材料により形成されている導電膜625と直接接続し、導電膜622を用いてソースやドレインの引き回しを行ってもよいし、導電膜625を用いてソースやドレインの引き回しを行ってもよい。導電膜625を用いて配線引き回しを行う場合、図6(A)の

50

ように導電膜 622 を上層に取り出す（例えば、導電膜 622 を、導電膜 630 を用いて層間膜 628 上に取り出す。）ことなく配線引き回しを行うことも可能となるため、マスクの使用枚数を低減する効果がある。また、導電膜 622 と導電膜 625 の両方を用いて引き回しを行うことにより、配線抵抗をより低減することができる。勿論、図 6 (A) と同様に、導電膜 625 を形成しない構造としてもよい。

#### 【0195】

なお、導電膜 622 と導電膜 625 を直接接続するには、少なくとも導電膜 625 上のゲート絶縁膜 624 を除去する必要があり、当該除去処理によりゲート電極 626 が剥き出し（つまり、ゲート電極 626 表面に膜が形成されていない状態。）になる場合がある。この場合、エッチング処理等により導電膜 622 を形成する際に、ゲート電極 626 がエッチングされて消失しないように、導電膜 622 よりもエッチングされにくい材料を少なくともゲート電極 626 の表面に形成することが好ましい。10

#### 【0196】

また、図 6 (C) のように、絶縁膜 627 を挟んで酸化物半導体膜 620 の上にバックゲート電極 629 形成された構造でもよい。バックゲート電極 629 を有する構造とすることにより、仮に第 1 のトランジスタ 510 がノーマリーオン状態（ここでは、電源電圧の供給が無い時にトランジスタがオン状態であることを示している。）であったとしても、バックゲート電極 629 に適宜電源電圧供給を行うことにより、第 1 のトランジスタ 510 のしきい値をシフトさせてノーマリーオフ状態（ここでは、電源電圧の供給が無い時にトランジスタがオフ状態であることを示している。）に保つことができる。20

#### 【0197】

なお、導電膜を加工して導電膜 622 を形成する際に、電子線描画装置（電子ビーム露光装置、EB (Electron Beam) 露光装置などとも言われる。）を用いることにより導電膜 622 間の距離（領域 623 に相当。）を狭くすることができるため、微細化された第 1 のトランジスタ 510 を形成しやすい。

#### 【0198】

以上が、OS トランジスタを構成要素の一部に使用した、不揮発性の特性を備えるメモリセルの構造についての説明である。

#### 【0199】

#### (実施の形態 4 )

本明細書に開示する中央処理装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、テレビ、モニタ等の表示装置、照明装置、デスクトップ型或いはノート型の情報端末、ワードプロセッサ、DVD (Digital Versatile Disc) などの記録媒体に記憶された静止画または動画を再生する画像再生装置、ポータブル CD プレーヤ、ラジオ、テープレコーダ、ヘッドホンステレオ、ステレオ、コードレス電話子機、トランシーバ、携帯無線機、携帯電話、自動車電話、携帯型ゲーム機、電卓、携帯情報端末、電子手帳、電子書籍、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、エアコンディショナーなどの空調設備、食器洗い器、食器乾燥器、衣類乾燥器、布団乾燥器、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA 保存用冷凍庫、煙感知器、放射線測定器、透析装置等の医療機器、などが挙げられる。さらに、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用ロボット、電力貯蔵システム等の産業機器も挙げられる。また、石油を用いたエンジンや、非水系二次電池からの電力を用いて電動機により推進する移動体なども、電気機器の範疇に含まれるものとする。上記移動体として、例えば、電気自動車 (EV)、内燃機関と電動機を併せ持ったハイブリッド車 (HEV)、プラグインハイブリッド車 (PHEV)、これらのタイヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、小型または大型船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船が挙げられる。これらの電子機器の具体例を図 9 に示す。304050

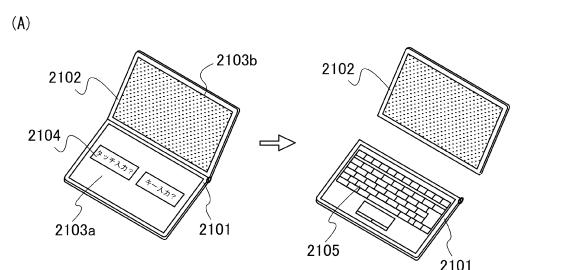

**【0200】**

図9(A)は、携帯型の情報端末であり、筐体2101、筐体2102、第1の表示部2103a、第2の表示部2103bなどによって構成されている。筐体2101と筐体2102の内部には、電子部品の一つとして中央処理装置が組み込まれている。当該中央処理装置として、上述実施の形態にて記載した中央処理装置の構造や駆動方法を適用することにより、携帯型の情報端末の低消費電力化を実現できる。

**【0201】**

なお、第1の表示部2103aおよび第2の表示部2103bの少なくとも一方は、タッチ入力機能を有するパネルとなっており、例えば図9(A)の左図のように、第1の表示部2103aに表示される選択ボタン2104により「タッチ入力」を行うか、「キーボード入力」を行うかを選択できる。選択ボタンは様々な大きさで表示できるため、幅広い世代の人が使いやすさを実感できる。ここで、例えば「タッチ入力」を選択した場合、図9(A)の右図のように第1の表示部2103aにはキーボード2105が表示される。これにより、従来の情報端末と同様に、キー入力による素早い文字入力などが可能となる。

10

**【0202】**

また、図9(A)に示す携帯型の情報端末は、図9(A)の右図のように、第1の表示部2103aを備える筐体2101と、第2の表示部2103bを備える筐体2102を分離することができる。このため、必要に応じて筐体2101のみ、または筐体2102のみを取り外して、より軽量な携帯型の情報端末として用いることができる。

20

**【0203】**

図9(A)に示す携帯型の情報端末は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。

**【0204】**

また、図9(A)に示す携帯型の情報端末は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

30

**【0205】**

さらに、図9(A)に示す筐体2101や筐体2102にアンテナやマイク機能や無線機能を持たせ、携帯電話として用いてもよい。

**【0206】**

図9(B)は、電子書籍の一例を示している。例えば、電子書籍2120は、筐体2121および筐体2123の2つの筐体で構成されている。筐体2121および筐体2123は、軸部2122により一体とされており、該軸部2122を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

**【0207】**

筐体2121には表示部2125が組み込まれ、筐体2123には表示部2127が組み込まれている。表示部2125および表示部2127は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部(図9(B)では表示部2125)に文章を表示し、左側の表示部(図9(B)では表示部2127)に画像を表示することができる。

40

**【0208】**

筐体2121と筐体2123の内部には、電子部品の一つとして中央処理装置が組み込まれている。当該中央処理装置として、上述実施の形態にて記載した中央処理装置の構造や駆動方法を適用することにより、電子書籍2120の低消費電力化を実現できる。

**【0209】**

また、図9(B)では、筐体2121に操作部などを備えた例を示している。例えば、

50

筐体 2121において、電源 2126、操作キー 2128、スピーカー 2129などを備えている。操作キー 2128により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子（イヤホン端子、USB 端子など）、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍 2120は、電子辞書としての機能を持たせた構成としてもよい。

#### 【0210】

また、電子書籍 2120は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とともに可能である。

10

#### 【0211】

図9(C)は、スマートフォンであり、筐体 2130と、ボタン 2131と、マイクロフォン 2132と、タッチパネルを備えた表示部 2133と、スピーカー 2134と、カメラ用レンズ 2135と、を具備し、携帯型電話機としての機能を有する。

#### 【0212】

筐体 2130の内部には、電子部品の一つとして中央処理装置が組み込まれている。当該中央処理装置として、上述実施の形態にて記載した中央処理装置の構造や駆動方法を適用することにより、スマートフォンの低消費電力化を実現できる。

#### 【0213】

表示部 2133は、使用形態に応じて表示の方向が適宜変化する。また、表示部 2133と同一面上にカメラ用レンズ 2135を備えているため、テレビ電話が可能である。スピーカー 2134及びマイクロフォン 2132は音声通話に限らず、テレビ電話、録音、再生などが可能である。

20

#### 【0214】

また、外部接続端子 2136はACアダプタ及びUSBケーブルなどの各種ケーブルと接続可能であり、充電及び情報端末などとのデータ通信が可能である。また、外部メモリスロット（図示せず）に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。

#### 【0215】

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。

30

#### 【0216】

図9(D)は、デジタルビデオカメラであり、筐体 2141、表示部 2142、操作スイッチ 2143、バッテリー 2144などによって構成されている。

#### 【0217】

筐体 2141の内部には、電子部品の一つとして中央処理装置が組み込まれている。当該中央処理装置として、上述実施の形態にて記載した記憶装置の構造や駆動方法を適用することにより、デジタルビデオカメラの低消費電力化を実現できる。

#### 【0218】

図9(E)は、テレビジョン装置の一例を示している。テレビジョン装置 2150は、筐体 2151に表示部 2153が組み込まれている。表示部 2153により、映像を表示することが可能である。また、ここでは、スタンド 2155により筐体 2151を支持した構成を示している。

40

#### 【0219】

筐体 2151の内部には、電子部品の一つとして中央処理装置が組み込まれている。当該中央処理装置として、上述実施の形態にて記載した中央処理装置の構造や駆動方法を適用することにより、テレビジョン装置 2150の低消費電力化を実現できる。

#### 【0220】

テレビジョン装置 2150の操作は、筐体 2151が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機か

50

ら出力する情報を表示する表示部を設ける構成としてもよい。

【0221】

なお、テレビジョン装置2150は、受信機やモ뎀などを備えた構成とする。受信機により一般的なテレビ放送の受信を行うことができ、さらにモ뎀を介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

【0222】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

10

【0223】

|      |           |    |

|------|-----------|----|

| 100  | 中央処理装置    |    |

| 102  | キャッシュメモリ  |    |

| 104  | 電源制御部     |    |

| 106  | 演算装置      |    |

| 108  | データフィールド  |    |

| 110  | タグフィールド   |    |

| 112  | バリッドビット   |    |

| 114  | キャッシュライン  |    |

| 116  | 電源装置      | 20 |

| 118  | 主記憶装置     |    |

| 200a | スイッチ素子    |    |

| 200b | スイッチ素子    |    |

| 200c | スイッチ素子    |    |

| 210  | 範囲        |    |

| 220  | 範囲        |    |

| 230  | 範囲        |    |

| 500  | トランジスタ    |    |

| 502  | 容量素子      |    |

| 504  | ビット線      | 30 |

| 506  | ワード線      |    |

| 508  | ノード       |    |

| 510  | トランジスタ    |    |

| 512  | トランジスタ    |    |

| 514  | 容量素子      |    |

| 518  | ノード       |    |

| 521  | 第1の配線     |    |

| 522  | 第2の配線     |    |

| 523  | 第3の配線     |    |

| 524  | 第4の配線     | 40 |

| 525  | 第5の配線     |    |

| 600  | 単結晶シリコン基板 |    |

| 601  | チャネル形成領域  |    |

| 602  | 分離層       |    |

| 604  | 低抵抗領域     |    |

| 606  | ゲート絶縁膜    |    |

| 608  | ゲート電極     |    |

| 609  | 側壁絶縁膜     |    |

| 610  | 層間膜       |    |

| 612  | 導電膜       | 50 |

|           |          |    |

|-----------|----------|----|

| 6 1 4     | 層間膜      |    |

| 6 1 6     | 導電膜      |    |

| 6 1 8     | 層間膜      |    |

| 6 1 9     | 絶縁膜      |    |

| 6 2 0     | 酸化物半導体膜  |    |

| 6 2 2     | 導電膜      |    |

| 6 2 3     | 領域       |    |

| 6 2 4     | ゲート絶縁膜   |    |

| 6 2 5     | 導電膜      |    |

| 6 2 6     | ゲート電極    | 10 |

| 6 2 7     | 絶縁膜      |    |

| 6 2 8     | 層間膜      |    |

| 6 2 9     | バックゲート電極 |    |

| 6 3 0     | 導電膜      |    |

| 6 3 2     | 層間膜      |    |

| 6 3 4     | 導電膜      |    |

| 6 3 6     | 層間膜      |    |

| 6 3 8     | 導電膜      |    |

| 6 4 0     | 層間膜      |    |

| 7 0 2     | キャッシュメモリ | 20 |

| 7 0 8     | データフィールド |    |

| 7 1 0     | タグフィールド  |    |

| 7 1 2     | バリッドビット  |    |

| 7 1 4     | キャッシュライン |    |

| 2 1 0 1   | 筐体       |    |

| 2 1 0 2   | 筐体       |    |

| 2 1 0 3 a | 第1の表示部   |    |

| 2 1 0 3 b | 第2の表示部   |    |

| 2 1 0 4   | 選択ボタン    |    |

| 2 1 0 5   | キー ボード   | 30 |

| 2 1 2 0   | 電子書籍     |    |

| 2 1 2 1   | 筐体       |    |

| 2 1 2 2   | 軸部       |    |

| 2 1 2 3   | 筐体       |    |

| 2 1 2 5   | 表示部      |    |

| 2 1 2 6   | 電源       |    |

| 2 1 2 7   | 表示部      |    |

| 2 1 2 8   | 操作キー     |    |

| 2 1 2 9   | スピーカー    |    |

| 2 1 3 0   | 筐体       | 40 |

| 2 1 3 1   | ボタン      |    |

| 2 1 3 2   | マイクロフォン  |    |

| 2 1 3 3   | 表示部      |    |

| 2 1 3 4   | スピーカー    |    |

| 2 1 3 5   | カメラ用レンズ  |    |

| 2 1 3 6   | 外部接続端子   |    |

| 2 1 4 1   | 筐体       |    |

| 2 1 4 2   | 表示部      |    |

| 2 1 4 3   | 操作スイッチ   |    |

| 2 1 4 4   | バッテリー    | 50 |

2 1 5 0 テレビジョン装置

2 1 5 1 筐体

2 1 5 3 表示部

2 1 5 5 スタンド

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(B)

(B)

【図9】

---

フロントページの続き

(56)参考文献 特開2006-190341(JP,A)

特開2003-45189(JP,A)

特開平9-26913(JP,A)

特開2002-236616(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 08

G 06 F 1 / 32

G 06 F 12 / 00