(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6264852号

(P6264852)

(45) 発行日 平成30年1月24日(2018.1.24)

(24) 登録日 平成30年1月5日(2018.1.5)

(51) Int.Cl.

F 1

|            |           |            |     |

|------------|-----------|------------|-----|

| HO3L 7/081 | (2006.01) | HO3L 7/081 | 120 |

| HO3L 7/10  | (2006.01) | HO3L 7/10  | 140 |

| HO3K 5/135 | (2006.01) | HO3K 5/135 |     |

請求項の数 15 (全 26 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2013-235911 (P2013-235911) |

| (22) 出願日  | 平成25年11月14日 (2013.11.14)     |

| (65) 公開番号 | 特開2015-95860 (P2015-95860A)  |

| (43) 公開日  | 平成27年5月18日 (2015.5.18)       |

| 審査請求日     | 平成28年4月26日 (2016.4.26)       |

|           |                                                              |

|-----------|--------------------------------------------------------------|

| (73) 特許権者 | 514315159<br>株式会社ソシオネクスト<br>神奈川県横浜市港北区新横浜2丁目10番<br>23        |

| (74) 代理人  | 100099759<br>弁理士 青木 篤                                        |

| (74) 代理人  | 100119987<br>弁理士 伊坪 公一                                       |

| (74) 代理人  | 100133835<br>弁理士 河野 努                                        |

| (74) 代理人  | 100135976<br>弁理士 宮本 哲夫                                       |

| (72) 発明者  | 松田 篤<br>神奈川県横浜市港北区新横浜2丁目10番<br>23 富士通セミコンダクター株式会社内<br>最終頁に続く |

(54) 【発明の名称】タイミング調整回路および半導体集積回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、を有し、

前記スタートアップ回路は、

前記入力クロック信号が第1周波数のときは、前記第2クロックを第2の数だけカウントして停止し、

前記入力クロック信号が前記第1周波数よりも高い第2周波数のときは、前記第2クロックを前記第2の数よりも多い第3の数だけカウントして停止する、

ことを特徴とするタイミング調整回路。

## 【請求項 2】

前記スタートアップ回路は、

起動後において、前記電圧制御遅延線から前記第2クロックが生成されるまでの期間において、前記制御電圧を、ロック電圧の近傍となるように調整する、

ことを特徴とする請求項1に記載のタイミング調整回路。

10

20

## 【請求項 3】

前記スタートアップ回路は、

前記第2クロックを第1の数だけカウントして停止するようになっている、ことを特徴とする請求項1または請求項2に記載のタイミング調整回路。

## 【請求項 4】

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、を有し、

前記スタートアップ回路は、

前記第2クロックを第1の数だけカウントして停止するようになっており、

前記スタートアップ回路は、

前記第2クロックをカウントする前記第1の数のフリップフロップと、

起動時を示す起動信号および前記第1の数のフリップフロップの出力の論理を取る論理回路と、

前記論理回路の出力信号により制御され、前記制御電圧のレベルを調整するトランジスタと、を含む、

ことを特徴とするタイミング調整回路。

## 【請求項 5】

前記スタートアップ回路は、

前記入力クロック信号が前記第1周波数のとき、前記第2の数だけカウントする第4の数の第1フリップフロップと、

前記入力クロック信号が前記第2周波数のとき、前記第1フリップフロップと協働して前記第3の数だけカウントする第5の数の第2フリップフロップと、

起動時を示す起動信号および前記第1フリップフロップの出力の論理を取る第1論理回路と、

前記入力クロック信号が第1周波数か第2周波数かに基づいて、前記第1フリップフロップのみ使用するか、前記第1フリップフロップおよび前記第2フリップフロップの両方を使用するかを制御する第2論理回路と、

前記第1論理回路の出力信号により制御され、前記制御電圧のレベルを調整するトランジスタと、を含む、

ことを特徴とする請求項1に記載のタイミング調整回路。

## 【請求項 6】

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、を有し、

前記電圧制御遅延線は、それぞれが前記制御電圧に基づいて遅延量が変化する、縦列接続された複数の遅延ユニットを有し、

前記縦列接続された複数の遅延ユニットにおける初段の遅延ユニットには、前記入力クロック信号が入力され、

n および m を正の整数で、n < m として

前記第1クロックは、前記複数段の遅延ユニットにおける n 段目の遅延ユニットから出力され、

10

20

30

40

50

前記第2クロックは、前記複数段の遅延ユニットにおけるm段目の遅延ユニットから出力され、

前記入力クロック信号は、容量を介して前記初段の遅延ユニットに入力される、

ことを特徴とするタイミング調整回路。

【請求項7】

前記入力クロック信号は、差動の入力クロック信号であり、

前記容量は、

前記初段の遅延ユニットの正論理の入力に設けられ、正論理の入力クロック信号を受け取る第1容量と、

前記初段の遅延ユニットの負論理の入力に設けられ、負論理の入力クロック信号を受け取る第2容量と、を含む、

ことを特徴とする請求項6に記載のタイミング調整回路。

【請求項8】

さらに、

前記初段の遅延ユニットの前記正論理の入力と負論理の出力の間に設けられた第1抵抗と、

前記初段の遅延ユニットの前記負論理の入力と正論理の出力の間に設けられた第2抵抗と、を含む、

ことを特徴とする請求項7に記載のタイミング調整回路。

【請求項9】

さらに、

起動していないとき、前記初段の遅延ユニットの差動出力信号におけるコモンモード電圧を、固定電圧に制御し、起動後は、前記初段の遅延ユニットの差動出力端子をフローティング状態にするコモン電圧制御回路を有する、

ことを特徴とする請求項7または請求項8に記載のタイミング調整回路。

【請求項10】

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、

前記第1クロックをマスクする第1マスク回路と、

前記第2クロックをマスクする第2マスク回路と、を有し、

前記第2マスク回路の出力信号は、前記第1マスク回路の出力信号よりも前に出力される、

ことを特徴とするタイミング調整回路。

【請求項11】

さらに、

前記第1クロックをマスクする第1マスク回路と、

前記第2クロックをマスクする第2マスク回路と、を有し、

前記第2マスク回路の出力信号は、前記第1マスク回路の出力信号よりも前に出力され、

前記第1マスク回路および前記第2マスク回路は、前記トランジスタが制御される信号を受け取ってマスク制御を行う、

ことを特徴とする請求項4または請求項5に記載のタイミング調整回路。

【請求項12】

タイミング調整回路と、

前記タイミング調整回路により生成された多相クロックを受け取って処理する内部回路

10

20

30

40

50

と、を有する半導体集積回路装置であって、

前記タイミング調整回路は、

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、を有し、

前記スタートアップ回路は、

10

前記入力クロック信号が第1周波数のときは、前記第2クロックを第2の数だけカウントして停止し、

前記入力クロック信号が前記第1周波数よりも高い第2周波数のときは、前記第2クロックを前記第2の数よりも多い第3の数だけカウントして停止する、

ことを特徴とする半導体集積回路装置。

【請求項13】

タイミング調整回路と、

前記タイミング調整回路により生成された多相クロックを受け取って処理する内部回路と、を有する半導体集積回路装置であって、

前記タイミング調整回路は、

20

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、を有し、

前記スタートアップ回路は、

前記第2クロックを第1の数だけカウントして停止するようになっており、

前記スタートアップ回路は、

30

前記第2クロックをカウントする前記第1の数のフリップフロップと、

起動時を示す起動信号および前記第1の数のフリップフロップの出力の論理を取り論理回路と、

前記論理回路の出力信号により制御され、前記制御電圧のレベルを調整するトランジスタと、を含む、

ことを特徴とする半導体集積回路装置。

【請求項14】

タイミング調整回路と、

前記タイミング調整回路により生成された多相クロックを受け取って処理する内部回路と、を有する半導体集積回路装置であって、

前記タイミング調整回路は、

40

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、を有し、

前記電圧制御遅延線は、それぞれが前記制御電圧に基づいて遅延量が変化する、縦列接続された複数の遅延ユニットを有し、

50

前記縦列接続された複数の遅延ユニットにおける初段の遅延ユニットには、前記入力クロック信号が入力され、

n および m を正の整数で、n < m として

前記第 1 クロックは、前記複数段の遅延ユニットにおける n 段目の遅延ユニットから出力され、

前記第 2 クロックは、前記複数段の遅延ユニットにおける m 段目の遅延ユニットから出力され、

前記入力クロック信号は、容量を介して前記初段の遅延ユニットに入力される、

ことを特徴とする半導体集積回路装置。

【請求項 15】

10

タイミング調整回路と、

前記タイミング調整回路により生成された多相クロックを受け取って処理する内部回路と、を有する半導体集積回路装置であって、

前記タイミング調整回路は、

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第 1 クロックと前記電圧制御遅延線からの第 2 クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第 1 電圧および第 2 電圧の間で連続的に変化させるスタートアップ回路と、

前記第 1 クロックをマスクする第 1 マスク回路と、

前記第 2 クロックをマスクする第 2 マスク回路と、を有し、

前記第 2 マスク回路の出力信号は、前記第 1 マスク回路の出力信号よりも前に出力される、

ことを特徴とする半導体集積回路装置。

【発明の詳細な説明】

【技術分野】

【0001】

この出願で言及する実施例は、タイミング調整回路および半導体集積回路装置に関する

30

。

【背景技術】

【0002】

近年、コンピュータやその他の情報処理機器に使用する半導体記憶装置(例えば、D R A M : Dynamic Random Access Memory)およびプロセッサ等は、その性能向上が顕著である。それに伴って、ボードに搭載されたチップ間や 1 つのチップ内における複数の素子や回路ブロック間の信号伝送を正確で高速に行わなければならない。

【0003】

そこで、例えば、受信側にタイミング調整回路(例えば、D L L 回路 : Delay Locked Loop Circuit)を設け、この D L L 回路により入力クロック信号を遅延させて多相クロックを生成し、データを適切なタイミングで取り込む(判定する)ものが知られている。

40

【0004】

或いは、コンピュータのバスを始めとする高速インターフェースにおいて、シリアルデータおよびパラレルデータを相互変換する S e r D e s (S E R I A L I Z E R / D E S E R I A L I Z E R) が知られているが、この S e r D e s に対しても D L L 回路が適用されている。

【0005】

D L L 回路は、縦列接続された複数の遅延ユニットを有し、例えば、第 1 遅延ユニットからの信号(0°)と、第 1 遅延ユニットよりも後段の第 2 遅延ユニットからの信号(360°)の位相差が零になるように制御する。

【0006】

50

そして、第1遅延ユニットと第2遅延ユニット間の各遅延ユニットからの信号を利用して、位相の異なる複数の信号(多相クロック)を生成する。なお、D L L回路(タイミング調整回路)は、S e r D e sだけでなく、様々な電子回路(半導体集積回路装置)に対して幅広く適用されている。

【0 0 0 7】

ところで、従来、タイミング調整回路としては、様々なものが提案されている。

【先行技術文献】

【特許文献】

【0 0 0 8】

【特許文献1】特開2010-114873号公報

10

【特許文献2】特開2006-025131号公報

【特許文献3】特開2011-055482号公報

【非特許文献】

【0 0 0 9】

【非特許文献1】Kwon, Jae-Wook, et al., "A 3.0 Gb/s clock data recovery circuits based on digital DLL for clock-embedded display interface," ESSCIRC (ESSCIRC), 2012 Proceedings of the, IEEE, September 2012

【発明の概要】

【発明が解決しようとする課題】

【0 0 1 0】

20

前述したように、例えば、縦列接続された複数の遅延ユニットを有するD L L回路は、例えば、S e r D e sを始めとして様々な電子回路に適用されている。このようなD L L回路が適用された電子回路において、例えば、電源を投入するスタートアップ時には、D L L回路における位相周波数検出器(P F D: Phase Frequency Detector: 位相検出器)が誤動作する虞がある。

【0 0 1 1】

すなわち、D L L回路の入力信号(入力クロック信号)の周波数が高くなると、P F Dの動作可能範囲が狭くなり、例えば、スタートアップ時等において、P F Dが誤動作するため、タイミング調整された出力信号の生成が困難になる虞がある。

【課題を解決するための手段】

30

【0 0 1 2】

一実施形態によれば、電圧制御遅延線と、位相検出器と、制御電圧生成回路と、スタートアップ回路と、を有するタイミング調整回路が提供される。

【0 0 1 3】

前記電圧制御遅延線は、入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成し、前記位相検出器は、基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する。

【0 0 1 4】

前記制御電圧生成回路は、検出された前記位相差に基づいて前記制御電圧を生成し、前記スタートアップ回路は、起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させる。前記スタートアップ回路は、前記入力クロック信号が第1周波数のときは、前記第2クロックを第2の数だけカウントして停止し、前記入力クロック信号が前記第1周波数よりも高い第2周波数のときは、前記第2クロックを前記第2の数よりも多い第3の数だけカウントして停止する。

40

【発明の効果】

【0 0 1 5】

開示のタイミング調整回路および半導体集積回路装置は、入力クロック信号が高速化しても、誤動作を生じることなく、タイミング調整された出力信号を生成することができるという効果を奏する。

【図面の簡単な説明】

50

## 【0016】

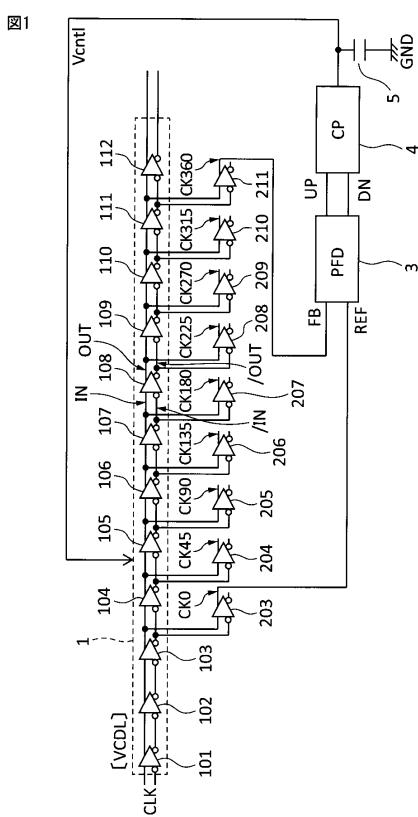

【図1】図1は、タイミング調整回路の一例を示すブロック図である。

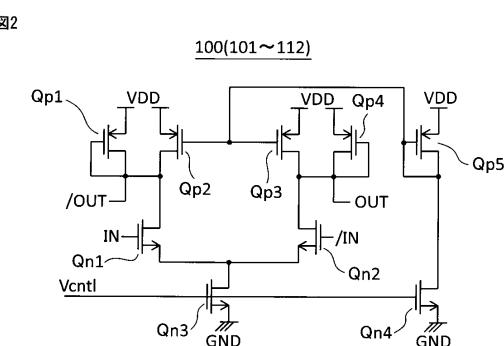

【図2】図2は、図1に示すタイミング調整回路における遅延ユニットの一例を示す回路図である。

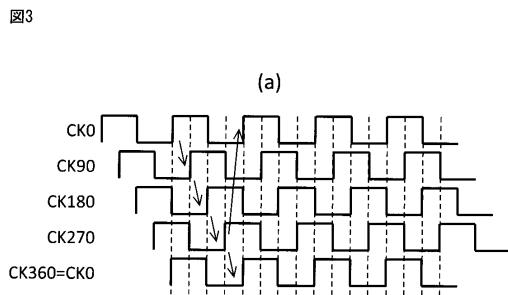

【図3】図3は、図1に示すタイミング調整回路の動作を説明するための図である。

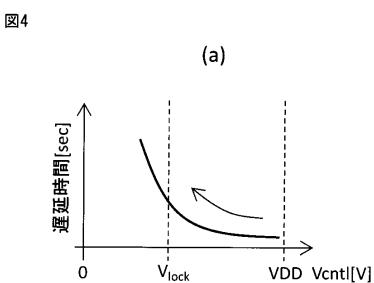

【図4】図4は、図1に示すタイミング調整回路におけるスタートアップ時の遅延を説明するための図である。

【図5】図5は、図1に示すタイミング調整回路における位相周波数検出器の異なる入力クロック信号に対する動作を説明するための図である。

【図6】図6は、図1に示すタイミング調整回路における位相周波数検出器の正常動作状態と誤動作状態を説明するための図である。 10

【図7】図7は、タイミング調整回路の第1実施例を示すブロック図である。

【図8】図8は、図7に示す第1実施例のタイミング調整回路におけるスタートアップ回路を抜き出して示す回路図である。

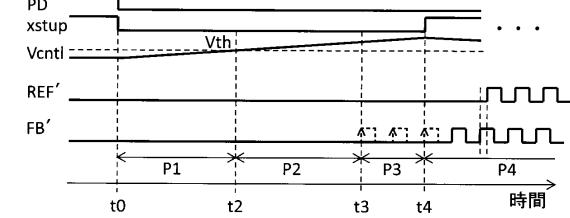

【図9】図9は、図8に示すスタートアップ回路の動作を説明するためのタイミング図である。

【図10】図10は、タイミング調整回路の第2実施例を示すブロック図である。

【図11】図11は、図10に示す第2実施例のタイミング調整回路の動作を説明するための図である。

【図12】図12は、タイミング調整回路の第3実施例を示すブロック図である。 20

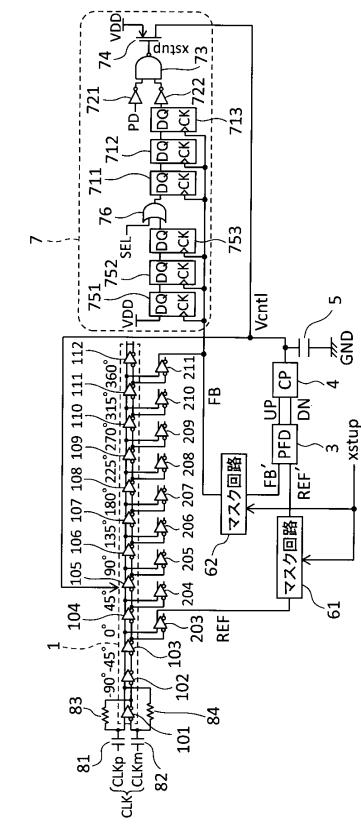

【図13】図13は、タイミング調整回路の第4実施例を示すブロック図である。

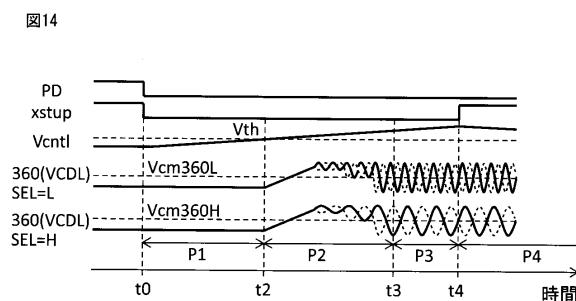

【図14】図14は、図13に示す第4実施例のタイミング調整回路の動作を説明するための図である。

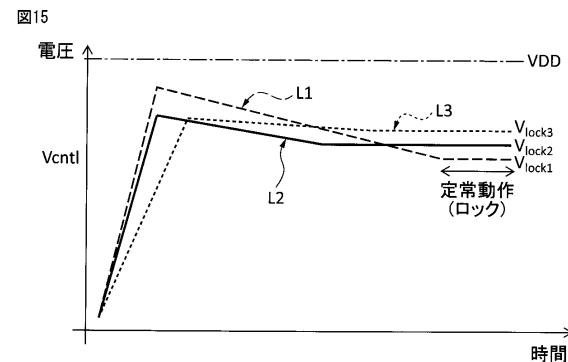

【図15】図15は、各実施例のタイミング調整回路による効果を説明するための図である。

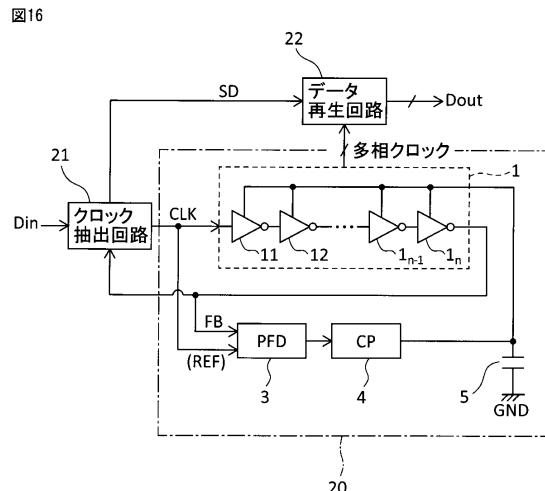

【図16】図16は、本実施例のタイミング調整回路が適用される半導体集積回路装置の一例を示すブロック図である。

## 【発明を実施するための形態】

## 【0017】

まず、タイミング調整回路および半導体集積回路装置の実施例を詳述する前に、タイミング調整回路の一例およびその問題点を図1～図6を参照して説明する。 30

## 【0018】

図1は、タイミング調整回路(DLL回路)の一例を示すブロック図である。図1において、参照符号1は電圧制御遅延線(VCDL: Voltage Controlled Delay Line)、101～112は遅延ユニット、そして、203～211は波形整形ユニットを示す。また、参照符号3は位相周波数検出器(PFD: 位相検出器)、4はチャージポンプ(CP: Charge Pump)、そして、5は容量を示す。

## 【0019】

図1に示されるように、VCDL1は、縦列接続された複数の遅延ユニット101～112を有し、遅延ユニット103～111の出力信号は、それぞれ対応する波形整形ユニット203～211を介して出力される。 40

## 【0020】

波形整形ユニット203～211は、例えば、遅延ユニット103～111の出力信号の振幅レベルを一般的な論理レベルまで増幅して出力するバッファ回路とされている。バッファ回路は、例えば、CMOS(Complementary Metal-Oxide Semiconductor)バッファ回路である。

## 【0021】

ここで、波形整形ユニット203の出力信号、すなわち、遅延ユニット103の出力信号(位相が0°の信号)を波形整形した信号(CKO: 参照クロック信号)REFは、PFD3の一方の入力に与えられる。

## 【0022】

また、波形整形ユニット211の出力信号、すなわち、遅延ユニット111の出力信号(位相が360°の信号)を波形整形した信号(C K360:フィードバッククロック信号)F Bは、PFD3の他方の入力に与えられる。

【0023】

PFD(位相周波数検出器)3は、入力された波形整形ユニット203の出力信号(参照クロック信号)REFと波形整形ユニット211の出力信号(フィードバッククロック信号)FBの位相差を検出してアップ信号UPまたはダウン信号DNをCP4に出力する。

【0024】

CP(チャージポンプ)4は、PFD3からの信号UP, DNに従って容量5に保持される電荷量を制御する。すなわち、制御電圧Vcntlは、参考クロック信号REFとフィードバッククロック信号FBの位相が同期する(360°(=0°)になる)ように制御される。

10

【0025】

図1において、遅延ユニット(第1遅延ユニット)103と遅延ユニット(第2遅延ユニット)111の間には、7個の遅延ユニット104~110が設けられている。そして、第1遅延ユニット103の出力信号CK0に対応する信号REFと第2遅延ユニット111の出力信号CK360に対応する信号FBの位相を同期させるように制御することで、八相クロックCK0, CK45, CK90, ..., CK360を得ることができる。

【0026】

すなわち、nおよびmを正の整数で、n < mとすると、例えば、参考クロック信号REFは、n段目の遅延ユニットから出力され、フィードバッククロック信号FBは、m段目の遅延ユニットから出力されることになる。

20

【0027】

図2は、図1に示すタイミング調整回路における遅延ユニットの一例を示す回路図であり、図3は、図1に示すタイミング調整回路の動作を説明するための図である。ここで、図3(a)は、信号CK0, CK90, CK180, CK270, CK360の関係を示し、図3(b)は、制御電圧Vcntlと遅延時間の関係を示す。

【0028】

図2に示されるように、遅延ユニット100(101~112)は、全て同様の回路構成とされ、pチャネル型MOS(pMOS)トランジスタQp1~Qp5およびnチャネル型MOS(nMOS)トランジスタQn1~Qn4を有する。

30

【0029】

ここで、対応関係を示す一例として、図1における遅延ユニット108に注目すると、図2に示す遅延ユニット100(108)における入力の差動対トランジスタQn1およびQn2のゲートが、差動入力INおよび/INに対応する。ここで、入力INは、正論理(非反転論理)の入力を示し、/INは、負論理(反転論理)の入力を示す。

【0030】

また、トランジスタQp2のドレイン(トランジスタQp1のゲートおよびドレイン)とトランジスタQn1のドレインの接続ノードが負論理(反転論理)の出力/OUTに対応する。さらに、トランジスタQp3のドレイン(トランジスタQp4のゲートおよびドレイン)とトランジスタQn2のドレインの接続ノードが正論理(非反転論理)の出力OUTに対応する。

40

【0031】

図2に示されるように、制御電圧Vcntlは、nMOSトランジスタQn3およびQn4のゲートに印加され、トランジスタQn3およびQn4の駆動能力(流れる電流)は、制御電圧Vcntlの電圧レベルにより制御される。

【0032】

ここで、制御電圧Vcntlの電圧レベルが高くなると、トランジスタQn3は十分にオンし、また、トランジスタQn4も十分にオンしてトランジスタQp2およびQp3のゲート電圧が低くなる。これにより、遅延ユニット100の駆動能力が大きくなつて遅延時間が短くなる。逆に、制御電圧Vcntlのレベルが低くなると、遅延ユニット100による遅延時間が長くなる。

50

## 【0033】

すなわち、図3(b)に示されるように、制御電圧  $V_{cnt1}$  は、初期状態で零 ( $V_{cnt1} = 0$ ) とされ、このとき、VCDL1(遅延ユニット101～112)は、信号を伝搬しない。また、PFD3に入力される参照クロック信号REFおよびフィードバッククロック信号FBは、零 ( $REF = 0$ ,  $FB = 0$ ) のまま遷移しない。従って、制御電圧  $V_{cnt1}$  は、初期状態 ( $V_{cnt1} = 0$ ) を維持する。

## 【0034】

それぞれの遅延ユニット100(101～112)は、例えば、制御電圧  $V_{cnt1}$  のレベル(電圧)が、トランジスタQn3およびQn4の閾値電圧  $V_{th}$  を超えると動作を開始し、高電位になるに従って駆動能力が大きくなつて、遅延時間が短くなる。

10

## 【0035】

なお、波形整形ユニット203～211は、全て同様の回路構成とされ、各波形整形ユニットによる遅延時間も一定になつてゐる。従って、例えば、DLL回路(タイミング調整回路)がロックしたときは、各波形整形ユニット203～211から出力される八相クロックは、遅延ユニット103～111から出力される互いに位相が45°だけ異なる八相クロックCK0, CK45, CK90, ..., CK360に対応することになる。

## 【0036】

次に、説明を簡略化するために、各波形整形ユニット203～211による一定の遅延時間を省いて、遅延ユニット103～111による出力信号を、多相クロックCK0～CK360とみなして説明する。

20

## 【0037】

すなわち、図3(a)を参照して、図1における遅延ユニット103, 105, 107, 109, 111の出力信号を、波形整形ユニット203, 205, 207, 209, 211の出力信号(クロック信号CK0, CK90, CK180, CK270, CK360)として説明する。

## 【0038】

信号CK0は、入力クロック信号CLKを3段の遅延ユニット101～103で遅延した信号である。ここで、入力クロック信号CLKは、例えば、正論理および負論理の差動(相補)の入力クロック信号を表している。

## 【0039】

信号CK90は、入力クロック信号CLKを5段の遅延ユニット101～105で遅延した信号、すなわち、遅延ユニット103の出力信号CK0をさらに2段の遅延ユニット104, 105で遅延した信号である。

30

## 【0040】

さらに、信号CK180は、入力クロック信号CLKを7段の遅延ユニット101～107で遅延した信号、すなわち、遅延ユニット105の出力信号CK90をさらに2段の遅延ユニット106, 107で遅延した信号である。そして、他の信号CK270, CK360(=CK0)も同様に、遅延ユニットにより順次遅延することで生成される。

## 【0041】

なお、図3(a)では、四相クロックCK0(CK360), CK90, CK180, CK270を示しているが、八相クロックCK0, CK45, CK90, ..., CK360、或いは、他の多相クロックに関しても、遅延ユニットの段数等を変更することで、同様に生成することができる。

40

## 【0042】

図1および図2を参照して説明した DLL回路(タイミング調整回路)は、入力クロック信号CLKを順次遅延させることで、多相(八相)クロック信号を生成する。ここで、制御電圧  $V_{cnt1}$  は、全ての遅延ユニット101～112(100)におけるトランジスタQn3およびQn4のゲートに印加され、この制御電圧  $V_{cnt1}$  のレベルをフィードバック制御することにより、信号REFおよびFBを同期させるようになっている。

## 【0043】

このように、参照クロック信号REFとフィードバッククロック信号FBの位相を同期させる(零にする)ことにより、遅延ユニット103～111から互いに位相が45°だけ異なる

50

8つの信号(八相クロック：多相クロック)が得られることになる。

【0044】

なお、遅延ユニット101～112および波形整形ユニット203～211は、差動構成とされているが、シングルエンド構成であってもよい。また、VCDL1の構成、第1遅延ユニット103と第2遅延ユニット111間に設ける遅延ユニットの段数、並びに、遅延ユニットおよび波形整形ユニットの回路構成等は、様々に変更することができるは言うまでもない。

【0045】

ところで、前述した図2において、スタートアップ時に、制御電圧 Vcntl = 0 Vとした場合、VCDL1を構成する各遅延ユニット101～112(100)が動作しないため、図1に示すDLL回路(タイミング調整回路)は起動しない。そこで、スタートアップ時に、制御電圧 Vcntl として電源電圧(高電位電源電圧) VDD を与える場合を、図4を参照して説明する。

【0046】

図4は、図1に示すタイミング調整回路におけるスタートアップ時の遅延を説明するための図であり、図4(a)は、制御電圧 Vcntl と遅延時間の関係を示し、図4(b)は、起動時(t0)における制御電圧 Vcntl の時間変化を示す。

【0047】

まず、制御電圧 Vcntl として電源電圧(高電位電源電圧) VDD を与え、そこから制御電圧 Vcntl のレベルを低下させると、例えば、1つの遅延ユニット100(101～112)における遅延時間は、図4(a)のように変化する。

【0048】

また、起動時の制御電圧 Vcntl として電源電圧 VDD を与え、そこから上述したタイミング調整回路(DLL回路)によるフィードバック制御を行うことにより、制御電圧 Vcntl は、安定した多相クロックを生成するロック電圧 Vlock まで図4(b)のように変化する。

【0049】

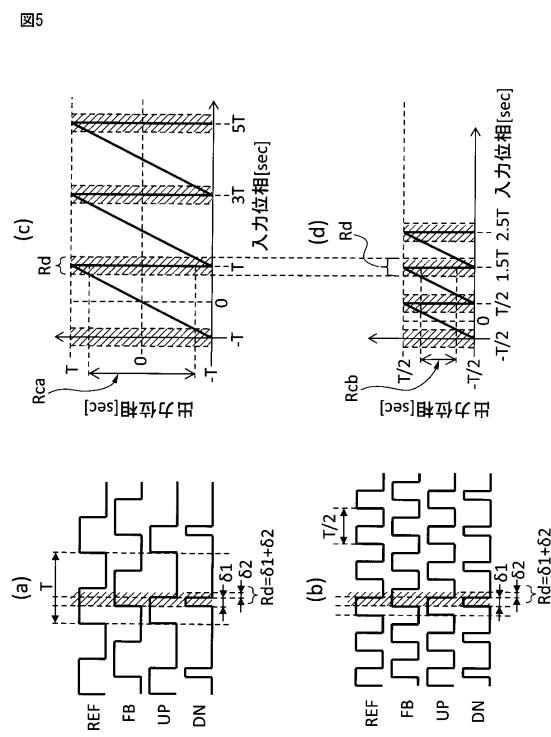

図5は、図1に示すタイミング調整回路における位相周波数検出器の異なる入力クロック信号に対する動作を説明するための図である。

【0050】

図5(a)および図5(c)は、入力クロック信号 CLK が第1周波数の場合を示し、図5(b)および図5(d)は、入力クロック信号 CLK が第1周波数の2倍の第2周波数の場合を示す。ここで、入力クロック信号 CLK の周波数としては、例えば、数GHz～数十GHz程度が想定される。

【0051】

また、図5(a)および図5(b)は、PFD3の入力信号REF, FB および出力信号UP, DNを示し、図5(c)および図5(d)は、PFD3の入力位相と出力位相の関係を示す。なお、図5(a)および図5(b)は、参照クロック信号REFは、フィードバッククロック信号FBの立ち上がりタイミングよりも先に立ち上がる(REFの方がFBよりも位相が進んでいる)場合を示す。

【0052】

ここで、起動時における制御として、例えば、VCDL1による遅延制御を開始するときの制御電圧 Vcntl は、ロック電圧 Vlock よりも高い電圧とされる。そのため、参照クロック信号REFは、所定期間マスクされ、フィードバッククロック信号FBが出力された(立ち上がった)後に参照クロック信号REFが出力されるようになっている。

【0053】

すなわち、図1では省略されているが、例えば、起動時において、参照クロック信号REFをフィードバッククロック信号FBよりも後に出力するために、後述する図7におけるマスク回路61, 62に相当する回路が設けられている。なお、REFがFBよりも後に出力されるとき、PFD3からは、最初にダウン信号DNが出力されることになる。

【0054】

さらに、アップ信号UPおよびダウン信号DNが両方とも出力されない状態を避けるた

10

20

30

40

50

めに、図5(a)および図5(b)に示されるように、通常、信号UPおよびDNが両方とも出力される同時オン期間 1を設けることも行われる。なお、参照符号 2は、PFD3が信号REFおよびFBの遷移(立ち上がりタイミング)から位相差を検出して信号(パルス)UP, DNを制御するまでのセットアップ期間を示す。

【0055】

図5(a)と図5(b)の比較から明らかなように、入力クロック信号CLKの周波数が2倍になつても(周期Tが半分のT/2になつても)、信号UP, DNが同時に出力される同時オン期間 1、および、PFD3のセットアップ期間 2は、変化しない。

【0056】

すなわち、図5(c)と図5(d)の比較から明らかなように、入力クロック信号CLKの周波数が2倍になつても、PFD3が正しく動作しない非動作範囲Rd( $= 1 + 2$ )は、変化しない。そして、PFD3の出力位相において、入力クロック信号CLKの周波数が2倍になったときの正常動作範囲(動作可能位相範囲)は、RcaからRcbへ大幅に低下することになる。

【0057】

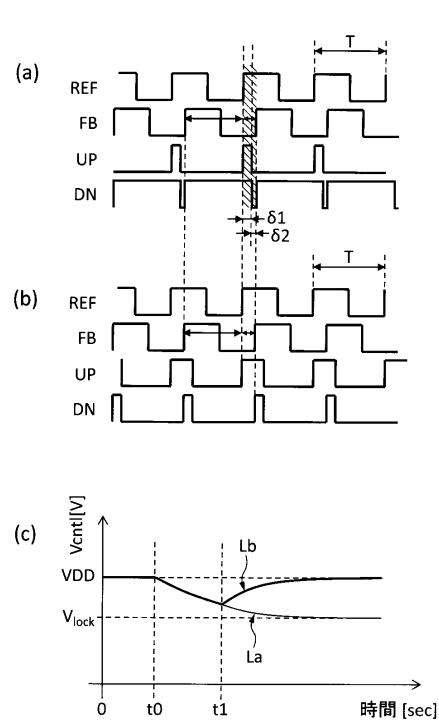

図6は、図1に示すタイミング調整回路における位相周波数検出器の正常動作状態と誤動作状態を説明するための図である。ここで、図6(a)および図6(b)は、PFD(位相周波数検出器)3の入出力信号REF, FB, UP, DNを示し、図6(a)は、正常動作状態を示し、図6(b)は、誤動作状態を示す。

【0058】

また、図6(c)は、正常動作状態および誤動作状態における制御電圧Vcntlの時間変化を示す。なお、図6(c)において、曲線Laは、正常動作状態における制御電圧Vcntlの時間変化を示し、曲線Lbは、誤動作状態における制御電圧Vcntlの時間変化を示す。また、図6(c)において、参照符号t0は、起動時のタイミングを示し、t1は、誤動作が生じたタイミングを示す。

【0059】

なお、図6では、制御電圧Vcntlを、高電位の電源電圧VDDから、安定した多相クロックを生成するロック電圧Vlockまで低下させる場合を示し、参照クロック信号REFは、フィードバッククロック信号FBの立ち上がりタイミングよりも先に立ち上がる。すなわち、REFの方がFBよりも位相が進んでいる。

【0060】

まず、図6(a)に示されるように、正常動作状態において、制御電圧Vcntlは、ロック電圧Vlockよりも高い電源電圧VDDから低くなるように制御される。すなわち、REFの立ち上がりタイミングは、FBの立ち上がりタイミングよりも先なので、高レベル『H』の期間の長いパルス信号DNが出力される。なお、前述したように、参照符号1は、信号UP, DNが同時に出力される同時オン期間を示し、2は、PFD3のセットアップ期間を示す。

【0061】

そして、図6(a)に示すようなフィードバック制御が正常に行われることにより、例えば、図6(c)中の曲線Laに示されるように、制御電圧Vcntlは、電源電圧VDDから低下するように制御され、ロック電圧Vlockに収束することになる。

【0062】

一方、図6(b)に示されるように、誤動作状態において、例えば、PFD3が、REFの立ち上がりタイミングを、FBの立ち上がりタイミングよりも後であると判定して処理を行うと、『H』の期間が信号DNよりも長いパルス信号UPが出力される。

【0063】

なお、例えば、1 + 2の区間において、参照クロック信号REFまたはフィードバッククロック信号FBの次のエッジが立ち上がる場合に、上述した誤動作状態が生じ得る。

【0064】

10

20

30

40

50

すなわち、例えば、図6(c)中の曲線Lbに示されるように、タイミングt1で、REFの立ち上がりタイミングがFBの立ち上がりタイミングよりも後であると判定すると、制御電圧Vcntlは、上昇するように制御されて電源電圧VDDに張り付いてしまう。その結果、DLL回路は、タイミング調整された出力信号の生成が困難になる。

【0065】

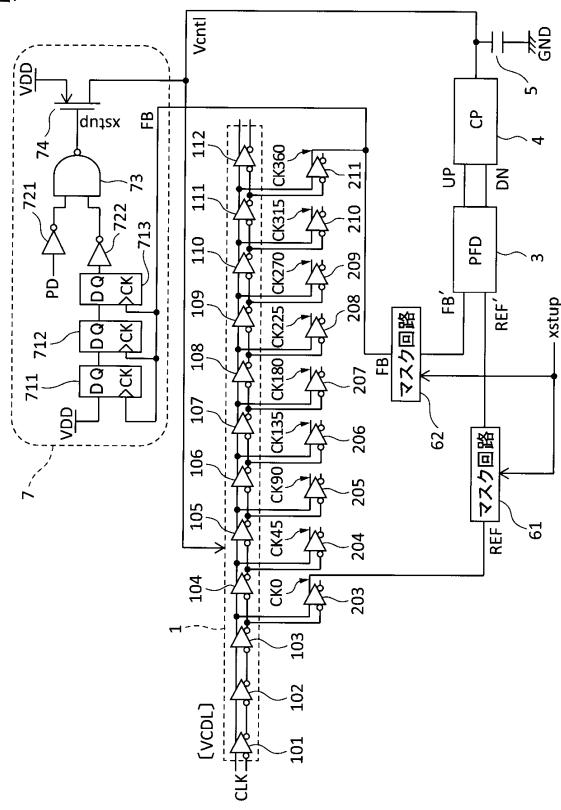

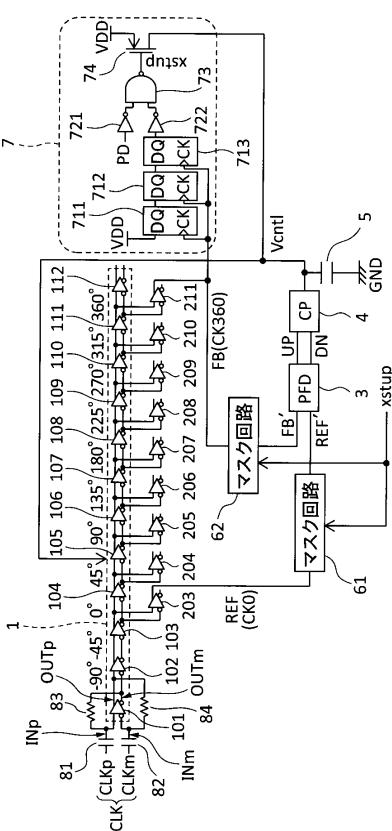

以下、タイミング調整回路および半導体集積回路装置の実施例を、添付図面を参照して詳述する。図7は、タイミング調整回路の第1実施例を示すブロック図である。

【0066】

図7において、参照符号1は電圧制御遅延線(VCDL)、101～112は遅延ユニット、203～211は波形整形ユニット、そして、3は位相周波数検出器(PFD:位相検出器)を示す。また、参照符号4はチャージポンプ(CP)、5は容量、61, 62はマスク回路、そして、7はスタートアップ回路を示す。

【0067】

図7と前述した図1の比較から明らかなように、第1実施例のタイミング調整回路(DLL回路)は、図1に示すタイミング調整回路に対して、スタートアップ回路7が追加されている。

【0068】

なお、図7では、 NANDゲート73の出力信号(トランジスタ74のゲート信号xstop)により制御されるマスク回路61, 62が設けられ、フィードバッククロック信号FB'が出力された後に参照クロック信号REFが出力されるようになっている。

【0069】

VCDL1は、縦列接続された複数の遅延ユニット101～112を有し、遅延ユニット103～111の出力信号は、それぞれ対応する波形整形ユニット203～211を介してクロック信号(多相クロック)CK0～CK360として出力される。

【0070】

ここで、第1実施例のタイミング調整回路において、遅延ユニット101～112および波形整形ユニット203～211は、例えば、図1を参照して説明したタイミング調整回路と同様のもの、或いは、知られている様々なものを適用することができる。具体的に、各遅延ユニット101～112としては、例えば、図2に示す遅延ユニット100をそのまま適用することができる。

【0071】

波形整形ユニット203～211は、例えば、遅延ユニット103～111の出力信号の振幅レベルを一般的な論理レベルまで増幅して出力するバッファ回路とされている。ここで、バッファ回路は例えば、CMOSバッファ回路である。遅延ユニット103の出力信号(位相が0°の信号)を波形整形ユニット203により波形整形した信号(CK0:参照クロック信号)REFは、マスク回路61で所定期間マスクされ、信号REF'としてPFD3の一方の入力に与えられる。

【0072】

また、遅延ユニット111の出力信号(位相が360°の信号)を波形整形ユニット211により波形整形した信号(CK360:フィードバッククロック信号)FBは、マスク回路62で所定期間マスクされ、信号FB'としてPFD3の他方の入力に与えられる。

【0073】

PFD3は、入力された参照クロック信号REF'과フィードバッククロック信号FB'の位相差を検出してアップ信号UPまたはダウン信号DNをCP4に出力する。ここで、マスク回路61, 62は、起動時において、信号FB'が出力された(立ち上がった)後に信号REF'が出力されるようにマスク制御するためのもので、例えば、NANDゲート73の出力信号(xstop)により制御される。

【0074】

CP4は、PFD3からの信号UP, DNに従って容量5に保持される電荷量を制御する。すなわち、制御電圧Vcntlは、参照クロック信号REF(REF')とフィードバック

10

20

30

40

50

クロック信号 F B ( F B ' )の位相が同期する(  $360^\circ$  ( =  $0^\circ$  )になる)ように制御される。

【 0 0 7 5 】

なお、図 7 においても、図 1 を参照して説明したのと同様に、第 1 遅延ユニット 103 と第 2 遅延ユニット 111 の間に設ける遅延ユニットの段数は、7 つに限定されるものではなく、所望の多相クロックを生成することができる。また、回路構成も、差動ではなくシングルエンド構成としてもよいのはいうまでもない。

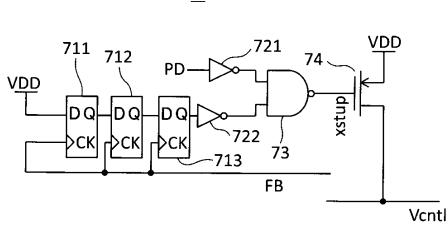

【 0 0 7 6 】

スタートアップ回路 7 は、例えば、縦列接続された 3 段のフリップフロップ 711 ~ 713、インバータ 721, 722、 NAND ゲート 73 および pMOS トランジスタ 74 を有する。このスタートアップ回路 7 により、起動時において、制御電圧 V cntl を、目的とするターゲット電圧(ロック電圧) V lock の近傍の電圧になるように制御する。

【 0 0 7 7 】

これにより、例えば、入力クロック信号 C L K の周波数が高くて P F D 3 の動作可能位相範囲が狭い場合でも、 P F D 3 は誤動作することなく、 D D L 回路(タイミング調整回路)はタイミング調整された出力信号を生成することを可能にする。

【 0 0 7 8 】

図 8 は、図 7 に示す第 1 実施例のタイミング調整回路におけるスタートアップ回路を抜き出して示す回路図であり、図 9 は、図 8 に示すスタートアップ回路の動作を説明するためのタイミング図である。

【 0 0 7 9 】

図 8 に示されるように、スタートアップ回路 7 において、縦列接続された 3 段のフリップフロップ 711 ~ 713 における初段のフリップフロップ 711 のデータ入力端子 D は、高電位の電源線に接続され、高電位電源電圧 V DD が印加されるようになっている。

【 0 0 8 0 】

なお、各フリップフロップ 711 ~ 713 のクロック端子 C K には、マスク回路 62 の出力信号 F B ' ではなく、波形整形ユニット 211 の出力信号 C K 360(フィードバッククロック信号 F B )が直接入力されている。

【 0 0 8 1 】

初段のフリップフロップ 711 のデータ出力端子 Q は、2 段目のフリップフロップ 712 のデータ入力端子 D に接続され、また、2 段目のフリップフロップ 712 のデータ出力端子 Q は、3 段目のフリップフロップ 713 のデータ入力端子 D に接続されている。3 段目のフリップフロップ 713 のデータ出力端子 Q からの出力信号は、インバータ 722 を介して NAND ゲート 73 の一方の入力に供給されている。

【 0 0 8 2 】

NAND ゲート 73 の他方の入力には、起動信号(パワーダウン信号) P D をインバータ 721 で論理反転した信号が供給され、NAND ゲート 73 の出力信号は、トランジスタ 74 のゲート信号 xstop としてトランジスタ 74 を制御するようになっている。

【 0 0 8 3 】

ここで、起動信号 P D は、起動時(  $t_0$  )において、高レベル『 H 』から低レベル『 L 』に立ち下がる信号である。また、各フリップフロップ 711 ~ 713 のデータ出力( Q )は、初期状態で『 L 』になっており、起動時  $t_0$  においても『 L 』に維持されている。従って、インバータ 722 の出力信号は『 H 』になっている。

【 0 0 8 4 】

図 9 に示されるように、例えば、タイミング  $t_0$  において、起動信号 P D が『 H 』から『 L 』に立ち下がる(パワーダウンが解除される)と、NAND ゲート 73 の入力信号が両方とも『 H 』になるため、NAND ゲート 73 の出力信号は『 L 』になる。

【 0 0 8 5 】

すなわち、トランジスタ 74 のゲート信号 xstop が『 H 』から『 L 』に立ち下がり、トランジスタ 74 がオンし、制御電圧 V cntl は連続的に変化し、徐々に上昇する。

10

20

30

40

50

## 【0086】

ここで、タイミング  $t_0$  から  $t_2$  までの期間  $P_1$  では、制御電圧  $V_{cntl}$  は、連続的に上昇し続けるが、例えば、図2を参照して説明した各遅延ユニット100(101～112)におけるnMOSトランジスタ  $Q_{n3}, Q_{n4}$  の閾値電圧  $V_{th}$  よりも低い( $V_{cntl} < V_{th}$ )。そのため、 $VCDL1$  における各遅延ユニット101～112は、信号伝搬を行わない。

## 【0087】

次に、タイミング  $t_2$  において、制御電圧  $V_{cntl}$  が閾値電圧  $V_{th}$  を超える( $V_{cntl} > V_{th}$ )と、遅延ユニット101～112が活性化され、それぞれ入力信号に対して制御電圧  $V_{cntl}$  に従った遅延量を与えて出力信号として出力する信号伝搬動作が開始される。

## 【0088】

ここで、期間  $P_2$  では、制御電圧  $V_{cntl}$  はさらに連続的に上昇し続けるが、遅延ユニット111(波形整形ユニット211)まで信号が伝えられず、タイミング  $t_3$  において、波形整形ユニット211からフィードバッククロック信号  $FB(CK360)$  が出力される。

## 【0089】

そして、期間  $P_3$  では、タイミング  $t_3$  から出力されたフィードバッククロック信号  $FB$  を、スタートアップ回路7におけるフリップフロップ711～713で処理し、信号  $FB$  の3個目の立ち上がりタイミング  $t_4$  において、トランジスタ74をオフする。

## 【0090】

すなわち、3段のフリップフロップ711～713のクロック入力  $CK$  には、フィードバッククロック信号  $FB$  が入力され、その信号  $FB$  の3個目の立ち上がりタイミング  $t_4$  でフリップフロップ713のデータ出力( $Q$ )が『L』から『H』に変化する。

## 【0091】

これにより、インバータ722の出力が『H』から『L』に変化し、 NANDゲート73の出力信号( $xstup$ )が『L』から『H』に立ち上がってトランジスタ74がオフし、スタートアップ回路7が停止する。

## 【0092】

この起動時におけるスタートアップ回路7(トランジスタ74)の動作により、制御電圧  $V_{cntl}$  は、目的とするロック電圧  $V_{lock}$  の近傍の電圧になる。なお、トランジスタ74がオフするタイミング  $t_4$  以後の動作、すなわち、期間  $P_4$  における動作は、例えば、図1～図5を参照して説明したのと同様である。

30

## 【0093】

なお、スタートアップ回路7が停止するタイミング  $t_4$  において、制御電圧  $V_{cntl}$  は、ロック電圧  $V_{lock}$  の近傍で  $V_{lock}$  よりも高い電圧( $V_{cntl} > V_{lock}$ )に設定されるのが好ましい。

## 【0094】

この制御電圧  $V_{cntl}$  の設定を、適切な  $V_{cntl} > V_{lock}$  とするには、例えば、スタートアップ回路7におけるフリップフロップ(711～713)の段数やpMOSトランジスタ74のサイズを調整する。或いは、後に図10を参照して説明するように、 $VCDL1$  の入力に設ける容量81, 82の値を調整することで、適切な  $V_{cntl} > V_{lock}$  を実現することもできる。

40

## 【0095】

すなわち、フリップフロップ(711～713)の段数を増加すれば、スタートアップ回路7が動作している期間を長くすることができ、また、トランジスタ74のサイズを大きくすれば、制御電圧  $V_{cntl}$  をプルアップする駆動能力を大きくすることができる。なお、 $VCDL1$  の入力に設ける容量81, 82の値を大きくすれば、スタートアップ回路7が動作している期間を長くすることができる。

## 【0096】

このように、第1実施例のタイミング調整回路によれば、例えば、入力クロック信号  $CLK$  の周波数が高くて  $PFD3$  の動作可能位相範囲が狭い場合でも、制御電圧  $V_{cntl}$  が電源電圧  $VDD$  に張り付くような誤動作をなくして正常に動作させることが可能になる。

50

## 【0097】

以上において、スタートアップ回路7は、起動時以外は動作しない、すなわち、トランジスタ74は、起動時以外はオフしているため、タイミング制御回路が通常動作を行っているときには、多相クロックの生成動作に影響を与えることはない。

## 【0098】

なお、前述したように、参照クロック信号REFおよびフィードバッククロック信号FBは、マスク回路61および62により所定期間マスクされ、PFD3に与えられる信号FB'が出力された後に、信号REF'が出力されるように制御されている。

## 【0099】

すなわち、タイミングt4でスタートアップ回路7による起動時の制御電圧Vcntlの設定が行われた後、まず、フィードバッククロック信号FB'が立ち上がり、その後、参照クロック信号REF'が立ち上がるようになっている。この場合、PFD3からは、最初にダウン信号DNが出力されることになる。これは、以下に述べる他の実施例でも同様である。

## 【0100】

図10は、タイミング調整回路の第2実施例を示すブロック図である。図10と上述した図7の比較から明らかなように、第2実施例のタイミング調整回路は、第1実施例のタイミング調整回路に対して、容量81, 82および抵抗83, 84が追加されている。

## 【0101】

すなわち、第2実施例のタイミング調整回路において、VCDL(電圧制御遅延線)1における初段の遅延ユニット101の差動入力INp, INmには、容量81, 82を介して差動のクロック信号CLKp, CLKmが入力されている。すなわち、入力クロック信号CLK(CLKp, CLKm)は、容量結合を介してVCDL1(初段の遅延ユニット101)に入力されるようになっている。

## 【0102】

さらに、初段の遅延ユニット101において、正論理の入力INpと負論理の出力OUTmの間に抵抗83を設けると共に、負論理の入力INmと正論理の出力OUTpの間に抵抗84を設け、コモンモード電圧Vcmを所定の電圧レベルに近づけるようになっている。

## 【0103】

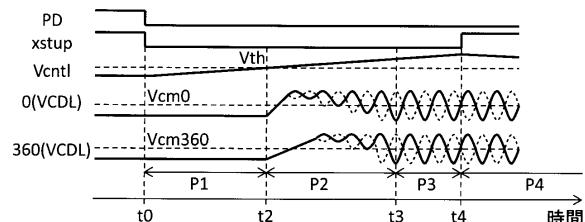

図11は、図10に示す第2実施例のタイミング調整回路の動作を説明するための図である。図11において、参照符号0(VCDL)およびVcm0は、遅延ユニット103の差動出力信号およびそのコモン電圧を示し、360(VCDL)およびVcm360は、遅延ユニット111の差動出力信号およびそのコモン電圧を示す。

## 【0104】

図11に示されるように、タイミングt0でスタートアップ回路7が起動(トランジスタ74がオン)すると、期間P1において、制御電圧Vcntlは徐々に上昇するが、閾値電圧Vthよりも低いので、遅延ユニット101～112による信号伝搬はおこなわれない。

## 【0105】

次に、タイミングt2において、Vcntl > Vthになると、遅延ユニット101～112による信号伝搬が開始される。しかしながら、図11の期間P2に示されるように、遅延ユニット103, 111の差動出力信号0(VCDL), 360(VCDL)およびコモン電圧Vcm0, Vcm360は、信号の伝搬は行われるが波形整形ユニット203, 211に信号を伝えることが困難になる。

## 【0106】

すなわち、初段の遅延ユニット101に設けた容量81, 82により、遅延ユニット111の差動出力信号360(VCDL)は、コモン電圧Vcm360が安定しないために小振幅の信号となり、波形整形ユニット(CMOSバッファ)211を駆動することが困難になる。そのため、コモン電圧Vcm360が安定して波形整形ユニット211を駆動してフィードバッククロック信号FBが出力されるタイミングt3までの期間が長くなる。

## 【0107】

なお、トランジスタ74がオフ(スタートアップ回路7が停止)するタイミングt4以後

10

20

30

40

50

の動作、すなわち、期間 P 4 における動作は、例えば、図 1 ~ 図 5 を参照して説明したのと同様である。

【 0 1 0 8 】

このように、第 2 実施例のタイミング調整回路は、容量結合を介して V C D L 1 (初段の遅延ユニット 101) に入力クロック信号 C L K を入力することにより、スタートアップ回路 7 が動作している期間を長くすることができる。これは、例えば、スタートアップ回路 7 におけるフリップフロップ 711 ~ 713 の段数の低減を可能にする。

【 0 1 0 9 】

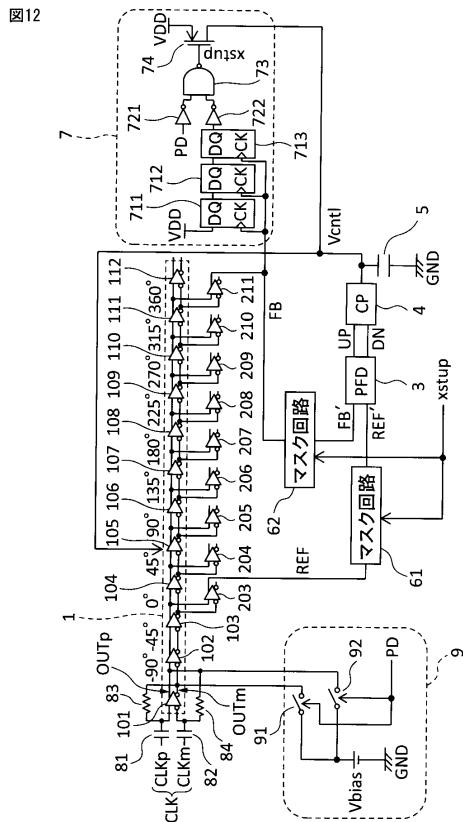

図 1 2 は、タイミング調整回路の第 3 実施例を示すブロック図である。図 1 2 と上述した図 1 0 の比較から明らかなように、第 3 実施例のタイミング調整回路は、第 2 実施例のタイミング調整回路に対して、コモン電圧制御回路 9 が追加されている。 10

【 0 1 1 0 】

図 1 2 に示されるように、コモン電圧制御回路 9 は、起動信号(パワーダウン信号) P D を使用してスイッチ 9 1 , 9 2 を制御するようになっている。

【 0 1 1 1 】

すなわち、図 1 0 を参照して説明した第 2 実施例では、起動時において、例えば、遅延ユニット 103 の差動出力信号 0(VCDL) におけるコモン電圧 V cm0 、および、遅延ユニット 111 の差動出力信号 360(VCDL) におけるコモン電圧 V cm360 は、安定していない。

【 0 1 1 2 】

そこで、タイミング調整回路が起動していないとき(パワーダウン時)において、初段の遅延ユニット 101 の差動出力信号のコモン電圧( V cm-90 )を所定の電圧レベル( V bias )に固定する。すなわち、タイミング調整回路が起動していないとき、起動信号 P D は『 H 』となっており、この『 H 』の起動信号 P D によりスイッチ 9 1 , 9 2 をオンする。 20

【 0 1 1 3 】

そして、タイミング t 0 で起動信号 P D が『 H 』から『 L 』に立ち下がるのを受けてスイッチ 9 1 , 9 2 をオフする。すなわち、タイミング調整回路が起動したら、スイッチ 9 1 , 9 2 をオフして、コモン電圧(初段の遅延ユニット 101 の差動出力端子 O U T p , O U T m )をフローティング状態にする。

【 0 1 1 4 】

これにより、起動時のコモン電圧を所定の電圧レベル( V bias )にすることで、例えば、図 1 1 における期間 P 2 の長さを安定させることができる。すなわち、容量結合を介して初段の遅延ユニット 101 にクロック信号 C L K を入力したことによるスタートアップ回路 7 の動作期間を認識して回路設計等を行うことが可能になる。 30

【 0 1 1 5 】

図 1 3 は、タイミング調整回路の第 4 実施例を示すブロック図である。図 1 3 と前述した図 1 0 の比較から明らかなように、第 4 実施例のタイミング調整回路は、第 2 実施例のタイミング調整回路において、スタートアップ回路 7 の構成が異なっている。

【 0 1 1 6 】

すなわち、第 4 実施例のタイミング調整回路は、入力クロック信号 C L K ( C L K p , C L K m )の周波数に応じて、スタートアップ回路 7 におけるフリップフロップの段数を制御し、スタートアップ回路 7 が動作する期間を制御するようになっている。 40

【 0 1 1 7 】

図 1 3 に示されるように、第 4 実施例のタイミング調整回路において、スタートアップ回路 7 は、図 1 0 の回路構成に加えて、さらに、縦列接続された 3 段のフリップフロップ 751 ~ 753 およびオアゲート 7 6 を含む。

【 0 1 1 8 】

各フリップフロップ 751 ~ 753 のクロック端子 C K には、フィードバッククロック信号 F B が入力され、初段のフリップフロップ 751 のデータ入力端子 D には、高電位電源電圧 V D D が印加されるようになっている。

【 0 1 1 9 】

初段のフリップフロップ751のデータ出力端子Qは、2段目のフリップフロップ752のデータ入力端子Dに接続され、また、2段目のフリップフロップ752のデータ出力端子Qは、3段目のフリップフロップ753のデータ入力端子Dに接続されている。3段目のフリップフロップ753のデータ出力端子Qからの出力信号は、オアゲート76の一方の入力に供給されている。

【0120】

なお、オアゲート76の他方の入力には、選択信号SELが供給され、図10のスタートアップ回路7におけるフリップフロップ711のデータ入力端子Dには、高電位電源電圧VDDではなく、オアゲート76の出力信号が供給されるようになっている。

【0121】

図14は、図13に示す第4実施例のタイミング調整回路の動作を説明するための図である。図14において、選択信号SELが高レベル『H』のとき(SEL = H)の入力クロック信号CLK(CLKp, CLKm)の周波数をf1とすると、選択信号SELが低レベル『L』のとき(SEL = L)の入力クロック信号CLKの周波数はf1 × 2になっている。

【0122】

また、参照符号Vcm360Hは、入力クロック信号CLKの周波数がf1のときにおける遅延ユニット111の差動出力信号のコモン電圧を示し、Vcm360Lは、クロック信号CLKの周波数がf1 × 2のときにおける遅延ユニット111の差動出力信号のコモン電圧を示す。

【0123】

図14に示されるように、例えば、入力クロック信号CLKの周波数がf1のとき、選択信号SELは『H』とされ、オアゲート76の出力信号は『H』になる。従って、フリップフロップ711のデータ入力端子Dは、『H』になるため、スタートアップ回路7は、前述した図10と同様に機能する。すなわち、フィードバッククロック信号FBの3回目の立ち上がりタイミングでスタートアップ回路7を停止する。

【0124】

一方、例えば、入力クロック信号CLKの周波数がf1 × 2のとき、選択信号SELは『L』とされ、オアゲート76の出力信号は、フリップフロップ753のデータ出力端子Qの信号レベルに従って変化する。従って、フリップフロップ711のデータ入力端子Dには、フリップフロップ753のデータ出力端子Qの信号が入力され、6段のフリップフロップ751～753, 711～713が縦列接続されることになる。すなわち、フィードバッククロック信号FBの6回目の立ち上がりタイミングでスタートアップ回路7を停止する。

【0125】

これにより、例えば、CLKの周波数がf1のとき、および、f1の2倍のときに関わらず、スタートアップ回路7により制御電圧Vcntlを調整する期間を適切に設定することができる。なお、フリップフロップ段数の切り替えは、入力クロク信号CLKの2つの異なる周波数に対応させて切り替えるものに限定されないのはもちろんである。

【0126】

このように、第4実施例のタイミング調整回路によれば、例えば、異なる周波数の入力クロク信号CLKが適用される場合でも、起動時に制御電圧Vcntlの調整を行うためのスタートアップ回路7のオン期間を適切に設定することが可能になる。

【0127】

図15は、各実施例のタイミング調整回路による効果を説明するための図である。図15において、参照符号L1は、動作速度が速い(駆動能力が大きい)トランジスタによる制御電圧Vcntlと時間の関係を示し、L3は、動作速度が遅い(駆動能力が小さい)トランジスタによる制御電圧Vcntlと時間の関係を示す。なお、L2は、動作速度が中間のトランジスタによる制御電圧Vcntlと時間の関係を示す。

【0128】

ところで、半導体を製造する場合、例えば、トランジスタの特性がばらつくことがある。本実施例のタイミング調整回路によれば、トランジスタの特性に関わらず、制御電圧Vcntlを目的とする定常動作を行うロック電圧Vlockに設定することが可能なのが分かる。

10

20

30

40

50

## 【0129】

すなわち、図15中のL1に示されるように、製造されたタイミング調整回路のトランジスタの動作速度が速い場合には、制御電圧V<sub>cnt1</sub>を、その動作速度の速いトランジスタによるタイミング調整回路に適したロック電圧V<sub>lock1</sub>に設定することができる。

## 【0130】

また、図15中のL3に示されるように、製造されたタイミング調整回路のトランジスタの動作速度が遅い場合には、制御電圧V<sub>cnt1</sub>を、その動作速度の遅いトランジスタによるタイミング調整回路に適したロック電圧V<sub>lock3</sub>に設定することができる。

## 【0131】

さらに、図15中のL2に示されるように、製造されたタイミング調整回路のトランジスタの動作速度が中間の場合には、制御電圧V<sub>cnt1</sub>を、その動作速度が中間のトランジスタによるタイミング調整回路に適したロック電圧V<sub>lock2</sub>に設定することができる。 10

## 【0132】

このように、各実施例のタイミング調整回路によれば、トランジスタの特性がばらついていても、制御電圧V<sub>cnt1</sub>を、トランジスタの特性に適したロック電圧V<sub>lock</sub>(V<sub>lock1</sub>～V<sub>lock3</sub>)の近傍の電圧に調整することができる。

## 【0133】

これにより、例えば、入力クロック信号C<sub>L</sub>Kの周波数が高くてPFD3の動作可能位相範囲が狭い場合でも、PFD3の誤動作をなくしてタイミング調整回路を正常に動作させることができる。 20

## 【0134】

図16は、本実施例のタイミング調整回路が適用される半導体集積回路装置の一例を示すブロック図であり、クロックデータリカバリー(CDR:Clock Data Recovery)回路を示すものである。

## 【0135】

図16に示されるように、CDR回路は、タイミング調整回路(DLL回路)20、クロック抽出回路21およびデータ再生回路22を有する。ここで、上述した各実施例のタイミング調整回路は、回路20として適用される。なお、図16では、遅延ユニット101～112および波形整形ユニット203～211は、インバータ(遅延素子)11～1nとして描かれている。 30

## 【0136】

外部から入力されたシリアルデータD<sub>in</sub>は、クロック抽出回路21によりクロック信号C<sub>L</sub>Kとデータ信号(データ成分)S<sub>D</sub>に分離され、クロック信号C<sub>L</sub>Kは、タイミング調整回路20に入力される。

## 【0137】

タイミング調整回路20は、クロック信号C<sub>L</sub>Kを受け取って互いに位相の異なる複数のクロック(多相クロック)を生成してデータ再生回路22(内部回路)に出力する。データ再生回路22は、クロック抽出回路21からのデータ成分S<sub>D</sub>を受け取り、多相クロックに従ってレベル判定を行い、所定のパラレルデータD<sub>out</sub>を出力する。

## 【0138】

ここで、データ再生回路22は、例えば、タイミング調整回路20から受け取る多相クロックが八相クロックのとき、シリアルのデータ成分S<sub>D</sub>を八相クロックの立ち上がりタイミングで取り込んで8ビットのパラレルデータD<sub>out</sub>を出力する。なお、データ成分S<sub>D</sub>(シリアルデータD<sub>in</sub>)のビットレートがA[bps]のとき、パラレルデータD<sub>out</sub>のビットレートはA/8[bps]になる。 40

## 【0139】

なお、図16に示すCDR回路は、本実施例のタイミング調整回路が適用される半導体集積回路装置の單なる一例であり、本実施例のタイミング調整回路は、例えば、多相クロックを使用する様々な半導体集積回路装置に対して幅広く適用することができる。

## 【0140】

50

20

30

40

50

以上、実施形態を説明したが、ここに記載したすべての例や条件は、発明および技術に適用する発明の概念の理解を助ける目的で記載されたものであり、特に記載された例や条件は発明の範囲を制限することを意図するものではない。また、明細書のそのような記載は、発明の利点および欠点を示すものでもない。発明の実施形態を詳細に記載したが、各種の変更、置き換え、変形が発明の精神および範囲を逸脱することなく行えることが理解されるべきである。

【0141】

以上の実施例を含む実施形態に關し、さらに、以下の付記を開示する。

(付記1)

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、10

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連続的に変化させるスタートアップ回路と、を有する、

ことを特徴とするタイミング調整回路。

【0142】

(付記2)

前記スタートアップ回路は、20

起動後において、前記電圧制御遅延線から前記第2クロックが生成されるまでの期間において、前記制御電圧を、ロック電圧の近傍となるように調整する、

ことを特徴とする付記1に記載のタイミング調整回路。

【0143】

(付記3)

前記ロック電圧は、前記電圧制御遅延線が定常動作を行っている時の前記制御電圧のレベルに基づいて規定される、

ことを特徴とする付記2に記載のタイミング調整回路。

【0144】

(付記4)

前記スタートアップ回路は、30

前記制御電圧を、前記ロック電圧よりも高い電圧となるように調整する、

ことを特徴とする付記2または付記3に記載のタイミング調整回路。

【0145】

(付記5)

前記スタートアップ回路は、

前記第2クロックを第1の数だけカウントして停止するようになっている、

ことを特徴とする付記1乃至付記4のいずれか1項に記載のタイミング調整回路。

【0146】

(付記6)

前記スタートアップ回路は、40

前記入力クロック信号をカウントする前記第1の数のフリップフロップと、

起動時を示す起動信号および前記第1の数のフリップフロップの出力の論理を取る論理回路と、

前記論理回路の出力信号により制御され、前記制御電圧のレベルを調整するトランジスタと、を含む、

ことを特徴とする付記5に記載のタイミング調整回路。

【0147】

(付記7)

前記スタートアップ回路は、50

前記入力クロック信号が第1周波数のときは、前記第2クロックを第2の数だけカウントして停止し、

前記入力クロック信号が前記第1周波数よりも高い第2周波数のときは、前記第2クロックを前記第2の数よりも多い第3の数だけカウントして停止する、

ことを特徴とする付記1乃至付記5のいずれか1項に記載のタイミング調整回路。

【0148】

(付記8)

前記スタートアップ回路は、

前記入力クロック信号が前記第1周波数のとき、前記第2の数だけカウントする第4の数の第1フリップフロップと、

前記入力クロック信号が前記第2周波数のとき、前記第1フリップフロップと協働して前記第3の数だけカウントする第5の数の第2フリップフロップと、

起動時を示す起動信号および前記第1フリップフロップの出力の論理を取る第1論理回路と、

前記入力クロック信号が第1周波数か第2周波数かに基づいて、前記第1フリップフロップのみ使用するか、前記第1フリップフロップおよび前記第2フリップフロップの両方を使用するかを制御する第2論理回路と、

前記第1論理回路の出力信号により制御され、前記制御電圧のレベルを調整するトランジスタと、を含む、

ことを特徴とする付記7に記載のタイミング調整回路。

【0149】

(付記9)

前記電圧制御遅延線は、

入力クロック信号を受け取り、第1遅延量を与えて前記第1クロックを生成し、前記第1遅延量よりも大きい第2遅延量を与えて前記第2クロックを生成する、

ことを特徴とする付記1乃至付記8のいずれか1項に記載のタイミング調整回路。

【0150】

(付記10)

前記制御電圧生成回路は、

前記第1クロックと前記第2クロックの位相が同期するような前記制御電圧を生成する、

ことを特徴とする付記9に記載のタイミング調整回路。

【0151】

(付記11)

前記電圧制御遅延線は、それぞれが前記制御電圧に基づいて遅延量が変化する、縦列接続された複数の遅延ユニットを有し、

前記縦列接続された複数の遅延ユニットにおける初段の遅延ユニットには、前記入力クロック信号が入力され、

$n$ および $m$ を正の整数で、 $n < m$ として

前記第1クロックは、前記複数段の遅延ユニットにおける $n$ 段目の遅延ユニットから出力され、

前記第2クロックは、前記複数段の遅延ユニットにおける $m$ 段目の遅延ユニットから出力される、

ことを特徴とする付記1乃至付記10のいずれか1項に記載のタイミング調整回路。

【0152】

(付記12)

前記入力クロック信号は、容量を介して前記初段の遅延ユニットに入力される、

ことを特徴とする付記11に記載のタイミング調整回路。

【0153】

(付記13)

10

20

30

40

50

前記入力クロック信号は、差動の入力クロック信号であり、

前記容量は、

前記初段の遅延ユニットの正論理の入力に設けられ、正論理の入力クロック信号を受け取る第1容量と、

前記初段の遅延ユニットの負論理の入力に設けられ、負論理の入力クロック信号を受け取る第2容量と、を含む、

ことを特徴とする付記12に記載のタイミング調整回路。

【0154】

(付記14)

さらに、

10

前記初段の遅延ユニットの前記正論理の入力と負論理の出力の間に設けられた第1抵抗と、

前記初段の遅延ユニットの前記負論理の入力と正論理の出力の間に設けられた第2抵抗と、を含む、

ことを特徴とする付記13に記載のタイミング調整回路。

【0155】

(付記15)

さらに、

起動していないとき、前記初段の遅延ユニットの差動出力信号におけるコモンモード電圧を、固定電圧に制御し、起動後は、前記初段の遅延ユニットの差動出力端子をフローティング状態にするコモン電圧制御回路を有する、

20

ことを特徴とする付記13または付記14に記載のタイミング調整回路。

【0156】

(付記16)

さらに、

前記第1クロックをマスクする第1マスク回路と、

前記第2クロックをマスクする第2マスク回路と、を有し、

前記第2マスク回路の出力信号は、前記第1マスク回路の出力信号よりも前に出力される、

ことを特徴とする付記1乃至付記15のいずれか1項に記載のタイミング調整回路。

30

【0157】

(付記17)

さらに、

前記第1クロックをマスクする第1マスク回路と、

前記第2クロックをマスクする第2マスク回路と、を有し、

前記第2マスク回路の出力信号は、前記第1マスク回路の出力信号よりも前に出力され、

前記第1マスク回路および前記第2マスク回路は、前記トランジスタが制御される信号を受け取ってマスク制御を行う、

ことを特徴とする付記6または付記8に記載のタイミング調整回路。

40

【0158】

(付記18)

タイミング調整回路と、

前記タイミング調整回路により生成された多相クロックを受け取って処理する内部回路と、を有する半導体集積回路装置であって、

前記タイミング調整回路は、

入力クロック信号を受け取り、制御電圧に基づいて遅延量を変化させた多相クロックを生成する電圧制御遅延線と、

基準になる第1クロックと前記電圧制御遅延線からの第2クロックの位相差を検出する位相検出器と、

50

検出された前記位相差に基づいて前記制御電圧を生成する制御電圧生成回路と、

起動後の一定期間のみ動作して、前記制御電圧を、第1電圧および第2電圧の間で連

続的に変化させるスタートアップ回路と、を有する、

ことを特徴とする半導体集積回路装置。

## 【符号の説明】

( 0 1 5 9 )

- |                       |                           |    |

|-----------------------|---------------------------|----|

| 1                     | 電圧制御遅延線( V C D L )        |    |

| 3                     | 位相周波数検出器( P F D : 位相検出器 ) |    |

| 4                     | チャージポンプ( C P )            |    |

| 5 , 8 1 , 8 2         | 容量                        | 10 |

| 7                     | スタートアップ回路                 |    |

| 9                     | コモン電圧制御回路                 |    |

| 6 1 , 6 2             | マスク回路                     |    |

| 7 3                   | NAND ゲート                  |    |

| 7 4                   | p M O S トランジスタ            |    |

| 7 6                   | オアゲート                     |    |

| 8 3 , 8 4             | 抵抗                        |    |

| 9 1 , 9 2             | スイッチ                      |    |

| 101 ~ 112             | 遅延ユニット                    |    |

| 203 ~ 211             | 波形整形ユニット                  | 20 |

| 711 ~ 713 , 751 ~ 753 | フリップフロップ                  |    |

| 721 , 722             | インバータ                     |    |

〔 1 〕

〔 図 2 〕

【図3】

【図4】

【図5】

【図6】

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

審査官 橋本 和志

(56)参考文献 特開2003-204261(JP, A)

米国特許第7262647(US, B2)

特開2006-287641(JP, A)

特開2005-311543(JP, A)

(58)調査した分野(Int.Cl., DB名)

H03L 7/081

H03K 5/135

H03L 7/10