(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-217774

(P2005-217774A)

(43) 公開日 平成17年8月11日(2005.8.11)

(51) Int.CI.<sup>7</sup>

**H03K 17/284**

**H02M 1/00**

**H03F 3/217**

**H03F 3/26**

**H03K 17/16**

F 1

H03K 17/284

H02M 1/00

H03F 3/217

H03F 3/26

H03K 17/16

テーマコード(参考)

5H74O

5J055

5J056

5J500

審査請求 未請求 請求項の数 14 O L (全 24 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2004-21840 (P2004-21840)

平成16年1月29日 (2004.1.29)

(71) 出願人 000237592

富士通テン株式会社

兵庫県神戸市兵庫区御所通1丁目2番28号

(74) 代理人 100075557

弁理士 西教 圭一郎

(74) 代理人 100072235

弁理士 杉山 翌至

(74) 代理人 100101638

弁理士 廣瀬 峰太郎

(72) 発明者 小松 和弘

兵庫県神戸市兵庫区御所通1丁目2番28号 富士通テン株式会社内

最終頁に続く

(54) 【発明の名称】スイッチング回路

## (57) 【要約】

【課題】 環流動作が可能で、しかも確実に貫通電流を禁止することができるスイッチング回路を提供する。

【解決手段】 ローサイド側のNチャネルMOSトランジスタ23, 22をオン状態からオフ状態に遷移させる入力信号の印加時を基準に、環流側スイッチング手段であるハイサイド側のNチャネルMOSトランジスタ24, 21を、駆動側スイッチング手段であるNチャネルMOSトランジスタ23, 22のターンオフ時間 $t_{off}$ を含む時間の経過後に、オン状態となるようにスイッチング駆動する。負荷25をPWM制御しながら、貫通電流を確実に禁止することができる。環流電流は、環流側スイッチング手段であるNチャネルMOSトランジスタ24, 21に、逆相PWM制御で、低損失で流すことができる。

【選択図】 図1

(b)

**【特許請求の範囲】****【請求項 1】**

電源から供給される電流を負荷に供給する経路を断続するスイッチング制御が行われる駆動側スイッチング手段と、負荷からの環流電流を流す経路を断続するスイッチング制御が行われる環流側スイッチング手段とを、電源に対して直列に接続し、駆動側スイッチング手段と環流側スイッチング手段との接続部に負荷が接続されるスイッチング回路であつて、

駆動側スイッチング手段のスイッチング制御用の入力信号を監視する監視手段と、

監視手段が監視する駆動側スイッチング手段をオン状態からオフ状態に遷移させる入力信号の印加時を基準に、環流側スイッチング手段を、駆動側スイッチング手段のターンオフ時間を含む時間の経過後に、オン状態となるようにスイッチング駆動するためのディレイ時間を設定するディレイ手段とを含むことを特徴とするスイッチング回路。10

**【請求項 2】**

前記監視手段は、前記入力信号を、前記負荷の接地位置の電位を基準とする前記駆動側スイッチング手段への入力電圧として監視することを特徴とする請求項 1 記載のスイッチング回路。

**【請求項 3】**

前記駆動側スイッチング手段のスイッチング制御用の入力信号は、入力用抵抗を介して印加され、20

前記監視手段は、該入力用抵抗を介して印加される入力信号を監視することを特徴とする請求項 1 または 2 記載のスイッチング回路。

**【請求項 4】**

前記監視手段は、前記入力信号を、前記入力用抵抗の両端電圧として監視することを特徴とする請求項 3 記載のスイッチング回路。

**【請求項 5】**

前記監視手段は、前記入力信号の電圧を弁別し、前記駆動用スイッチング手段がオン状態に駆動されているかオフ状態に駆動されているかを表す論理信号を出力する比較器を含むことを特徴とする請求項 1 ~ 4 のいずれか 1 つに記載のスイッチング回路。30

**【請求項 6】**

前記監視手段は、前記比較器の入力端子に前記入力信号を導く監視用抵抗を含み、

前記ディレイ手段は、該監視用抵抗と該比較器の入力端子の入力容量とで形成される回路であることを特徴とする請求項 5 記載のスイッチング回路。

**【請求項 7】**

前記比較器の入力端子に接続され、該入力端子に対し、前記監視用抵抗のオープン時には前記出力の論理信号が前記駆動側スイッチング手段がオン状態に駆動されていることを表す側に固定されるように、予め設定される電圧を印加する論理固定用抵抗をさらに含むことを特徴とする請求項 6 記載のスイッチング回路。

**【請求項 8】**

前記ディレイ手段は、前記監視手段の監視結果を遅延させて、前記ディレイ時間を設定することを特徴とする請求項 1 ~ 5 のいずれか 1 つに記載のスイッチング回路。40

**【請求項 9】**

前記駆動用スイッチング手段と前記環流用スイッチング手段とのうち、電源のハイサイド側となるスイッチング手段は P チャネル M OS トランジスタを、電源のローサイド側となるスイッチング手段は N チャネル M OS トランジスタを、それぞれスイッチング素子として備えることを特徴とする請求項 1 ~ 8 のいずれか 1 つに記載のスイッチング回路。

**【請求項 10】**

前記駆動用スイッチング手段および前記環流用スイッチング手段は、いずれも N チャネル M OS トランジスタを、スイッチング素子として備えることを特徴とする請求項 1 ~ 8 のいずれか 1 つに記載のスイッチング回路。

**【請求項 11】**

10

20

30

40

50

前記駆動用スイッチング手段および前記環流用スイッチング手段の組合せは、複数設けられ、

前記負荷は該複数の接続端子を有し、各接続端子は各組合せの前記環流用スイッチング手段と前記駆動用スイッチング手段との接続部にそれぞれ接続され、

前記監視手段は、各組合せの駆動用スイッチング手段のスイッチング制御用の入力信号をそれぞれ監視することを特徴とする請求項1～10のいずれか1つに記載のスイッチング回路。

#### 【請求項12】

前記ディレイ手段には、前記各組合せの駆動用スイッチング手段のターンオフ時間に応じて、前記ディレイ時間が各駆動用スイッチング手段毎に設定されることを特徴とする請求項11記載のスイッチング回路。10

#### 【請求項13】

前記監視手段は、前記駆動側スイッチング手段のスイッチング制御用の入力信号を、チャタリング防止用のヒステリシスを付けて監視することを特徴とする請求項1～12のいずれか1つに記載のスイッチング回路。

#### 【請求項14】

前記駆動側スイッチング手段に印加する入力信号を、PWM制御を行うように発生する駆動ロジックと、

該駆動ロジックによるPWM制御でのデューティが0に近くなり、前記環流用スイッチング手段に対するスイッチング制御が逆相PWM制御となる領域では、逆相PWM制御を禁止する指定が可能な逆相PWM禁止手段とをさらに含むことを特徴とする請求項1～13のいずれか1つに記載のスイッチング回路。20

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、環流動作が可能なスイッチング回路、特に数A～数100Aの大電流をスイッチング制御して負荷を駆動することが可能なスイッチング回路に関する。

#### 【背景技術】

#### 【0002】

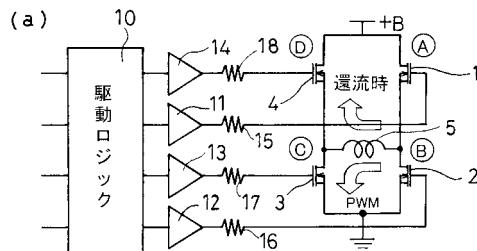

従来から、図16に示すようなスイッチング回路が各種アクチュエータなどを電気的に駆動するために用いられている。図16(a)はスイッチング回路としてHブリッジでの例を示し、図16(b)はPWM(Pulse Width Modulation)制御時の動作波形を示す。Hブリッジは、4つのNチャネルMOSトランジスタ1～4によって形成される。負荷5を、数A～数100Aの大電流で駆動するシステムでは、NチャネルMOSトランジスタ1～4には、DMOS(Double diffusion Metal Oxide Semiconductor)構造のものが好適に使用される。DMOS構造は、ゲートをフラット化し、チャネルを二重拡散によって形成し、高電流、高耐圧化を容易に図ることができる。各NチャネルMOSトランジスタ1～4は、負荷5を駆動する電流の方向に応じて、NチャネルMOSトランジスタ1, 3の組、またはNチャネルMOSトランジスタ2, 4の組のいずれか一方がオン状態になり、他方はオフ状態になるように、駆動ロジック10によってゲートへの駆動信号がそれぞれ発生される。駆動信号は、駆動ロジック10からドライバ11～14およびゲート抵抗15～18を介して、NチャネルMOSトランジスタ1～4のゲートにそれぞれ印加される。大電流駆動用のMOSトランジスタは、一般にゲート容量が大きいので、駆動段の損失低減、ノイズ発生抑制のために、直列にゲート抵抗を挿入することが多い。3040

#### 【0003】

図16(a)に示すようなシステムでは、負荷25に供給する負荷電流をPWM制御する。負荷25には一般に誘導成分が含まれたり、負荷25への導電線自体にも誘導成分が存在するので、負荷電流の一部は誘導成分に電磁エネルギーとして蓄えられ、PWM制御で負荷電流をオフにすると、負荷25に蓄えられている電磁エネルギーが電源側に戻ろうとする環流が生じる。システムの負荷電流が数A程度の場合、たとえば各NチャネルMOSト50

ランジスタ1～4のドレイン・ソース間に、カソードがドレイン側、アノードがソース側となるように、逆並列にダイオードを接続する。このダイオードは、フリーホイールダイオードと呼ばれ、PWM制御の負荷電流とは逆方向となる環流電流を流すことができる。ただし、フリーホイールダイオードは、PN接合の部分で、約0.7V程度の順方向電圧を発生し、この順方向電圧と環流電流との積の電力が損失となって発熱する。環流動作で、環流電流が数10A程度になると、フリーホイールダイオードでの発熱量が問題となるため、たとえばNチャネルMOSトランジスタ1，3の組がPWM制御を行って、NチャネルMOSトランジスタ2，4の組はオフになっていても、ハイサイド側のNチャネルMOSトランジスタ4を、下流のローサイド側NチャネルMOSトランジスタ3のPWM制御とは逆相で駆動し、環流動作時の損失を低減する方法が用いられる。オン抵抗が低いMOSトランジスタを用いると、大きな環流電流が流れても、電圧降下は小さくなり、電力損失に伴う発熱を小さくすることができる。

10

## 【0004】

ただし、逆相PWM制御時、ローサイド側のNチャネルMOSトランジスタ3とハイサイド側のNチャネルMOSトランジスタ4とが同時にオンとなると、電源の+Bと接地のGNDとの間が2つのスイッチング素子であるNチャネルMOSトランジスタ3，4によって短絡されることになり、電源とGNDとの間に貫通電流が流れる。貫通電流は、スイッチング素子のオン抵抗が小さいほど大きくなり、スイッチング素子であるNチャネルMOSトランジスタ3，4の破壊、ノイズの発生などの不具合を引き起すため、同時オンを禁止する動作が必要となる。

20

## 【0005】

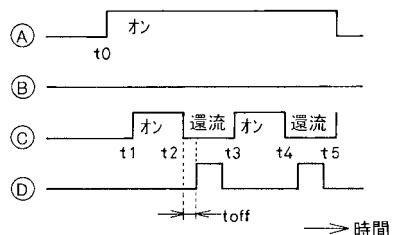

図16(b)に示すように、従来技術では、ハイサイド側のNチャネルMOSトランジスタ4とローサイド側のNチャネルMOSトランジスタ3との駆動時間に、数μ～数10μs程度、さらには100μs程度のノンオーバーラップ時間を設け、貫通電流の流れるおそれがある動作を禁止している。ノンオーバーラップ時間の主要部分は、MOSトランジスタのゲート信号がMOSトランジスタのオフ電圧になった後、実際にMOSトランジスタがオフになるまでの遅れ時間であるターンオフ時間 $t_{off}$ が占める。なお、図16(b)で、A～Dは、図16(a)のNチャネルMOSトランジスタ1～4の動作状態をそれぞれ示す。基本的に、NチャネルMOSトランジスタ1，3の組がオンとなり、NチャネルMOSトランジスタ2，4の組がオフとなる。A，Cとして示すように、NチャネルMOSトランジスタ1，3の組では、ハイサイド側のNチャネルMOSトランジスタ1を時刻 $t_0$ からオン状態に保ち、ローサイド側のNチャネルMOSトランジスタ3を時刻 $t_1$ から $t_2$ までオン、時刻 $t_2$ から $t_3$ までオフ、時刻 $t_3$ から $t_4$ までオン、時刻 $t_4$ から $t_5$ までオフとなるように、オンとオフとを繰返し、オンとオフとの時間的な比率で負荷電流を制御するPWM制御が行われる。

30

## 【0006】

ローサイド側のNチャネルMOSトランジスタ3がオフの間、Dに示すように、他の組のハイサイド側のNチャネルMOSトランジスタ4をオンにして環流動作が行われる。前述の貫通電流を禁止するために、時刻 $t_2$ でローサイド側のNチャネルMOSトランジスタ4がオフになってから、ノンオーバーラップ時間 $t_{off}$ 経過後に、ハイサイド側のNチャネルMOSトランジスタ3がオンになる。時刻 $t_4$ でも、同様に、ノンオーバーラップ時間が設けられる。なお、ハイサイド側のNチャネルMOSトランジスタ4は、ローサイド側のNチャネルMOSトランジスタ3が時刻 $t_3$ ， $t_5$ でオフからオンに遷移する前にオンからオフに遷移させて、貫通電流を禁止する。このような貫通電流の禁止は、駆動ロジック10で各NチャネルMOSトランジスタ1～4を駆動する信号を生成する際に、タイミング調整で実現される。

40

## 【0007】

Hブリッジなどのスイッチング回路の貫通電流対策は、種々提案されている（たとえば、特許文献1～3参照）。特許文献1では、ハイサイド側のMOSトランジスタがオンからオフになる立下がり時間を早くするために、シュミット回路の正帰還を利用している。

50

特許文献2では、電源とHブリッジとの間に電流制限抵抗を設けて貫通電流を制限している。特許文献3では、Hブリッジを構成するパワーMOSトランジスタのゲートに補助のMOSスイッチングトランジスタを接続し、ゲート信号の電位変動を抑制してパワーMOSトランジスタの破壊や誤動作を防止している。

#### 【0008】

なお、ハイサイド側にPチャネルMOSトランジスタ、ローサイド側にNチャネルMOSトランジスタを用い、同一の半導体チップ上に両方の導電形式のMOSトランジスタを形成する半導体集積回路は、CMOS(Complementary MOS)と呼ばれ、広く用いられている。CMOSの出力回路で貫通電流を抑圧するために、各MOSのゲートへの入力論理を監視し、出力論理の反転時には、一方が遮断状態となってから他方を導通状態となるように制御する構成が提案されている(たとえば、特許文献4、5参照)。

#### 【0009】

【特許文献1】特開平5-268038号公報

【特許文献2】特開平9-50078号公報

【特許文献3】特許第3324555号公報

【特許文献4】特開2000-49586号公報

【特許文献5】特開平6-237158号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

図16(a)に示すようなシステムでは、ターンオフ時間 $t_{off}$ を主とするノンオーバーラップ時間を設けて貫通を禁止している。この時間は、MOSトランジスタの応答速度も考慮しなければならない。特に、各NチャネルMOSトランジスタ1~4をゲート抵抗15~18を介して駆動する場合は、ゲート抵抗15~18と各NチャネルMOSトランジスタ1~4のゲートでの入力容量とで積分回路が形成され、この積分回路による遅延時間分だけ、実際にゲートに印加される制御信号にディレイが生じ、ドライバ11~14の応答速度自体もばらつく。したがって、図16(b)に示すノンオーバーラップ時間の主要部分であるターンオフ時間 $t_{off}$ は、ゲート抵抗15~18と入力容量とによる遅延と、ドライバ11~14の応答速度のばらつき幅とを考慮して最適化する必要がある。最適化したノンオーバーラップ時間には、マージンをとった値を用意する必要があるため、PWM制御の周波数が高くなると、Dとして示すハイサイド側のNチャネルMOSトランジスタ4をオンにする期間を設けることができなくなり、ハイサイド側をオンにして環流時の損失低減を図る手段すら実施することができなくなってしまう。

#### 【0011】

特許文献1~5に示されるような貫通電流の対策は、環流電流を流す必要がある場合について考慮されていない。特に特許文献4、5は、CMOSプロセスを前提としており、大電流MOSのスイッチング回路では次のような注意が必要となる。

1. 大電流駆動用のMOSトランジスタはゲートの入力容量が大きいため、駆動段の損失低減、ノイズ発生抑制のために、直列にゲート抵抗を挿入して駆動することが多い。このゲート抵抗と、ゲートの入力容量とにより、駆動段の駆動タイミングと、MOSトランジスタの動作タイミングにずれが発生するため、この遅延分を考慮する必要がある。

2. MOSトランジスタのターンオフ時間を考慮する必要がある。

#### 【0012】

本発明の目的は、環流動作が可能で、しかも確実に貫通電流を禁止することができるスイッチング回路を提供することである。

#### 【課題を解決するための手段】

#### 【0013】

本発明は、電源から供給される電流を負荷に供給する経路を断続するスイッチング制御が行われる駆動側スイッチング手段と、負荷からの環流電流を流す経路を断続するスイッチング制御が行われる環流側スイッチング手段とを、電源に対して直列に接続し、駆動側

10

20

30

40

50

スイッチング手段と環流側スイッチング手段との接続部に負荷が接続されるスイッチング回路であって、

駆動側スイッチング手段のスイッチング制御用の入力信号を監視する監視手段と、

監視手段が監視する駆動側スイッチング手段をオン状態からオフ状態に遷移させる入力信号の印加時を基準に、環流側スイッチング手段を、駆動側スイッチング手段のターンオフ時間を含む時間の経過後に、オン状態となるようにスイッチング駆動するためのディレイ時間を設定するディレイ手段とを含むことを特徴とするスイッチング回路である。

【0014】

また本発明で、前記監視手段は、前記入力信号を、前記負荷の接地位置の電位を基準とする前記駆動側スイッチング手段への入力電圧として監視することを特徴とする。 10

【0015】

また本発明で、前記駆動側スイッチング手段のスイッチング制御用の入力信号は、入力用抵抗を介して印加され、

前記監視手段は、該入力用抵抗を介して印加される入力信号を監視することを特徴とする。

【0016】

また本発明で、前記監視手段は、前記入力信号を、前記入力用抵抗の両端電圧として監視することを特徴とする。 20

【0017】

また本発明で、前記監視手段は、前記入力信号の電圧を弁別し、前記駆動用スイッチング手段がオン状態に駆動されているかオフ状態に駆動されているかを表す論理信号を出力する比較器を含むことを特徴とする。 20

【0018】

また本発明で、前記監視手段は、前記比較器の入力端子に前記入力信号を導く監視用抵抗を含み、

前記ディレイ手段は、該監視用抵抗と該比較器の入力端子の入力容量とで形成される回路であることを特徴とする。 30

【0019】

また本発明は、前記比較器の入力端子に接続され、該入力端子に対し、前記監視用抵抗のオープン時には前記出力の論理信号が前記駆動側スイッチング手段がオン状態に駆動されていることを表す側に固定されるように、予め設定される電圧を印加する論理固定用抵抗をさらに含むことを特徴とする。 30

【0020】

また本発明で、前記ディレイ手段は、前記監視手段の監視結果を遅延させて、前記ディレイ時間を設定することを特徴とする。 40

【0021】

また本発明は、前記駆動用スイッチング手段と前記環流用スイッチング手段とのうち、電源のハイサイド側となるスイッチング手段はPチャネルMOSトランジスタを、電源のローサイド側となるスイッチング手段はNチャネルMOSトランジスタを、それぞれスイッチング素子として備えることを特徴とする。 40

【0022】

また本発明で、前記駆動用スイッチング手段および前記環流用スイッチング手段は、いずれもNチャネルMOSトランジスタを、スイッチング素子として備えることを特徴とする。

【0023】

また本発明で、前記駆動用スイッチング手段および前記環流用スイッチング手段の組合せは、複数設けられ、

前記負荷は該複数の接続端子を有し、各接続端子は各組合せの前記環流用スイッチング手段と前記駆動用スイッチング手段との接続部にそれぞれ接続され、

前記監視手段は、各組合せの駆動用スイッチング手段のスイッチング制御用の入力信号 50

をそれぞれ監視することを特徴とする。

【0024】

また本発明で、前記ディレイ手段には、前記各組合せの駆動用スイッチング手段のターンオフ時間に応じて、前記ディレイ時間が各駆動用スイッチング手段毎に設定されることを特徴とする。

【0025】

また本発明で、前記監視手段は、前記駆動側スイッチング手段のスイッチング制御用の入力信号を、チャタリング防止用のヒステリシスを付けて監視することを特徴とする。

【0026】

また本発明は、前記駆動側スイッチング手段に印加する入力信号を、PWM制御を行うように発生する駆動ロジックと、

該駆動ロジックによるPWM制御でのデューティが0に近くなり、前記環流用スイッチング手段に対するスイッチング制御が逆相PWM制御となる領域では、逆相PWM制御を禁止する指定が可能な逆相PWM禁止手段とをさらに含むことを特徴とする。

【発明の効果】

【0027】

本発明によれば、駆動側スイッチング手段をオン状態からオフ状態に遷移させる入力信号の印加時を基準に、環流側スイッチング手段を、駆動側スイッチング手段のターンオフ時間を含む時間の経過後に、オン状態となるようにスイッチング駆動するので、貫通電流を確実に禁止することができ、環流電流は環流側スイッチング手段に低損失で流すことができる。

【0028】

また本発明によれば、監視手段は、入力信号を、負荷の接地位置の電位を基準とする駆動側スイッチング手段への入力電圧として監視するので、大電流の制御に伴って、接地位置で電圧レベルに差がある場合でも、駆動側スイッチング手段をオフにする入力電圧を確実に検出することができる。

【0029】

また本発明によれば、駆動側スイッチング手段のスイッチング制御用の入力信号は、入力用抵抗を介して印加され、監視手段は、入力用抵抗を介して印加される入力信号を監視するので、入力用抵抗と駆動側スイッチング手段の入力容量とで遅延する入力信号を確実に検出することができる。

【0030】

また本発明によれば、監視手段は、入力信号を、入力用抵抗の両端電圧として監視するので、入力用抵抗の両端電圧が低下すれば、駆動用スイッチング手段をオンからオフに遷移させる動作が完了したと判断することができる。

【0031】

また本発明によれば、監視手段は、入力信号の電圧を弁別し、駆動用スイッチング手段がオン状態に駆動されているかオフ状態に駆動されているかを表す論理信号を出力する比較器を含むので、比較器から出力される論理信号で駆動用スイッチング手段の駆動状態を容易に判別することができる。

【0032】

また本発明によれば、監視手段は、比較器の入力端子に入力信号を導く監視用抵抗を含み、ディレイ手段は、監視用抵抗と比較器の入力端子の入力容量とで形成される回路であるので、比較器からの論理出力にはディレイ時間が含まれ、論理出力を直接利用して環流側スイッチング手段の制御を行っても、貫通電流を確実に禁止することができる。

【0033】

また本発明によれば、比較器の入力端子に接続される論理固定用抵抗によって、監視用抵抗のオープン時には出力の論理信号が駆動側スイッチング手段がオン状態に駆動されていることを表す側に固定されるように、予め設定される電圧を入力端子に印加する。外付け部品である監視用抵抗のオープン故障等により、監視手段への入力信号が不定となる場

10

20

30

40

50

合には、駆動側スイッチング手段への入力信号がオフ状態を表す側に駆動されると判断しなくなるので、環流側スイッチング手段をオンに駆動しないようになり、駆動側スイッチング手段と環流側スイッチング手段との両方がオンになる貫通動作を避けることができる。

#### 【0034】

また本発明によれば、ディレイ手段は、監視手段の監視結果を遅延させてディレイ時間を設定するので、監視手段が監視結果を論理信号で出力すれば、デジタルプロセスで遅延を容易に実現することができ、システム動作中のディレイ時間の可変も可能となる。

#### 【0035】

また本発明によれば、駆動用スイッチング手段と環流用スイッチング手段とのうち、電源のハイサイド側となるスイッチング手段はPチャネルMOSトランジスタを、電源のローサイド側となるスイッチング手段はNチャネルMOSトランジスタを、それぞれスイッチング素子として備える。入力信号をハイレベルにすればハイサイド側のPチャネルMOSトランジスタはオフになり、ローサイド側のNチャネルMOSトランジスタはオンになります、入力信号をローレベルにすればハイサイド側のPチャネルMOSトランジスタはオンになります、ローサイド側のNチャネルMOSトランジスタはオフになるので、ハイサイド側とローサイド側とを対称的にスイッチング駆動することができる。

#### 【0036】

また本発明によれば、駆動用スイッチング手段および環流用スイッチング手段は、いずれもNチャネルMOSトランジスタを、スイッチング素子として備える。大電流を駆動可能なPチャネルMOSトランジスタは、製造が困難で高価であるけれども、その使用を避けて、大電流で負荷を駆動することができる。

#### 【0037】

また本発明によれば、駆動用スイッチング手段および環流用スイッチング手段の組合せは、複数設けられ、負荷はその複数の接続端子を有し、各接続端子は各組合せの環流用スイッチング手段と駆動用スイッチング手段との接続部にそれぞれ接続されるので、Hブリッジなどの2相や3相モータなどのような多相の駆動回路を容易に実現することができる。監視手段は、各組合せの駆動用スイッチング手段のスイッチング制御用の入力信号をそれぞれ監視するので、多相の各相で確実に貫通電流を禁止することができる。

#### 【0038】

また本発明によれば、ディレイ手段には、各組合せの駆動用スイッチング手段のターンオフ時間に応じて、ディレイ時間が各駆動用スイッチング手段毎に設定されるので、各駆動用スイッチング手段の動作遅れに応じて、最適な貫通対策を行うことができる。

#### 【0039】

また本発明によれば、監視手段は、駆動側スイッチング手段のスイッチング制御用の入力信号を、チャタリング防止用のヒステリシスを付けて監視するので、駆動用スイッチング手段のオンやオフのタイミングで発生するノイズによって誤認識することなく、貫通対策を行うことができる。

#### 【0040】

また本発明によれば、駆動側スイッチング手段に印加する入力信号を、PWM制御を行うように発生する駆動ロジックと、駆動ロジックによるPWM制御でのデューティが0に近くなり、環流用スイッチング手段に対するスイッチング制御が逆相PWM制御となる領域では、逆相PWM制御を禁止する指定が可能な逆相PWM禁止手段とをさらに含む。本発明では、従来のようにマージンを大きくとる必要がないので、ノンオーバーラップ時間としてのターンオフ時間の誤差を小さくすることができるけれども、0にすることはできない。PWM制御のデューティが小さくなつて0に近くなるときには、環流電流を流すための逆相PWM制御を禁止し、それによってターンオフ時間の発生を0にすることができます。すなわち、逆相PWM制御を禁止するだけで、ターンオフ時間を0とすることができます。

#### 【発明を実施するための最良の形態】

10

20

30

40

50

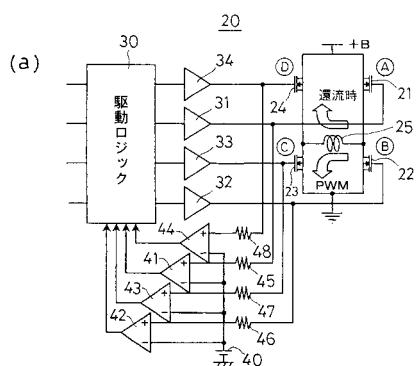

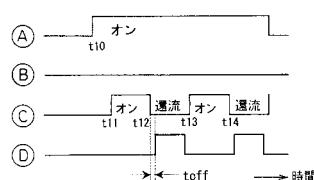

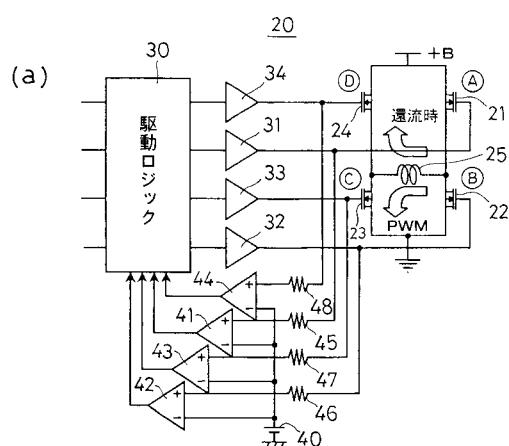

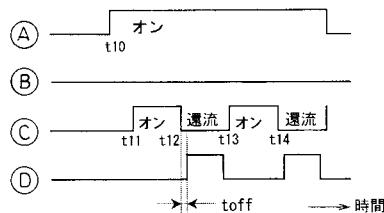

## 【0041】

図1は、(a)で本発明の実施の第1形態としてのスイッチング回路20の概略的な電気的構成を示し、(b)でスイッチング回路20の基本的な動作波形を示す。以下図1から図11に示す実施の各形態では、先行して説明する部分や要素に対応する部分や要素には同一の参照符を付して示し、重複する説明を省略する。

## 【0042】

図1(a)に示すように、スイッチング回路20は、スイッチング素子であるNチャネルMOSトランジスタ21～24でHブリッジを形成し、電源から供給される電流を負荷に供給する経路を断続するスイッチング制御を行う。このHブリッジでは、直列に接続されるNチャネルMOSトランジスタ21とNチャネルMOSトランジスタ22との接続部と、直列に接続されるNチャネルMOSトランジスタ23とNチャネルMOSトランジスタ24との接続部との間に負荷25が接続される。各NチャネルMOSトランジスタ21～24のゲートには、駆動ロジック30で生成される駆動信号がドライバ31～34を介してそれぞれ印加される。

## 【0043】

Hブリッジを構成するNチャネルMOSトランジスタ21とNチャネルMOSトランジスタ23とがオンになり、NチャネルMOSトランジスタ22とNチャネルMOSトランジスタ24とがオフになるように駆動されると、電源+Bからの負荷電流は、NチャネルMOSトランジスタ21のドレイン・ソース間を流れ、負荷を図の右から左の方向に流れ、NチャネルMOSトランジスタ23のドレイン・ソース間を流れて接地GNDに到る。Hブリッジを構成するNチャネルMOSトランジスタ24とNチャネルMOSトランジスタ22とがオンになり、NチャネルMOSトランジスタ21とNチャネルMOSトランジスタ23とがオフになるように駆動されると、電源+Bからの負荷電流は、NチャネルMOSトランジスタ24のドレイン・ソース間を流れ、負荷を図の左から右の方向に流れ、NチャネルMOSトランジスタ22のドレイン・ソース間を流れて接地GNDに到る。このように、Hブリッジでは、オンにするスイッチング素子の組合せで、負荷25に流す電流の方向を切換えることができる。

## 【0044】

負荷25に流す電流は、PWM方式で制御される。PWM制御の動作は、負荷25に流す電流の方向に応じてオンになるNチャネルMOSトランジスタ21, 23の組、またはNチャネルMOSトランジスタ24, 22の組のうち、それぞれローサイド側のNチャネルMOSトランジスタ23, 22によって行われる。PWM制御動作を行うNチャネルMOSトランジスタ23, 22に対して、直接電源の+B側との間に接続されるハイサイド側のNチャネルMOSトランジスタ24, 21は、PWM制御で負荷25への電流の供給が遮断されるときに発生する環流電流を流すために、ローサイド側のNチャネルMOSトランジスタ23, 22とそれぞれ逆相でPWM制御される。このように、オフになっているハイサイド側のスイッチング素子を利用して環流動作を行う点は、図16と同様である。ただし、スイッチング回路20では、PWM動作を行うNチャネルMOSトランジスタ23, 22がオフになってから逆相PWM動作を行うNチャネルMOSトランジスタ24, 21がオンになるまでのノンオーバーラップ時間を最短にして、確実に貫通対策ができる、しかも環流電流を低損失で流し得るようにしている。

## 【0045】

ノンオーバーラップ時間を最短にするためには、各NチャネルMOSトランジスタ21～24のゲート電圧を、基準電圧源40の電圧を基準に、比較器41～44でそれぞれ監視している。各比較器41～44の反転入力側には基準電圧源40からの基準となる電圧、たとえば接地GNDの電位を基準として電源+Bの電圧の中間の電圧が共通に印加される。各比較器41～44の非反転入力側には、監視用抵抗45～48を介して、NチャネルMOSトランジスタ21～24のゲート電圧がそれぞれ入力される。各比較器41～44は、反転入力側の基準電圧源40の電圧よりも非反転入力側に入力されるNチャネルMOSトランジスタ21～24のゲート電圧が高くなればハイレベルとなり、反転入力側の

基準電圧源 4 0 の電圧よりも非反転入力側に入力される N チャネル M O S トランジスタ 2 1 ~ 2 4 のゲート電圧が低くなればローレベルとなる論理信号をそれぞれ出力し、駆動ロジック 3 0 に入力させる。駆動ロジック 3 0 では、各比較器 4 1 ~ 4 4 から出力される論理信号に基づき、各 N チャネル M O S トランジスタ 2 1 ~ 2 4 をスイッチング制御するための駆動信号を生成する。

#### 【 0 0 4 6 】

図 1 ( b ) は、図 1 ( a ) の H ブリッジを構成する N チャネル M O S トランジスタ 2 1 ~ 2 4 のスイッチング制御動作を、ゲートへの駆動信号の論理レベルとして A ~ D でそれぞれ示す。N チャネル M O S トランジスタ 2 1 , 2 3 の組がオンになってローサイド側の N チャネル M O S トランジスタ 2 3 で P W M 制御を行い、環流電流に対してはオフになっている N チャネル M O S トランジスタ 2 4 , 2 2 のうちのハイサイド側の N チャネル M O S トランジスタ 2 4 を使用して逆相 P W M 制御を行う状態について示す。負荷 2 5 に流す電流の方向が逆になるときには、N チャネル M O S トランジスタ 2 4 , 2 2 の組がオンになってローサイド側の N チャネル M O S トランジスタ 2 2 で P W M 制御を行い、環流電流に対してはオフになっている N チャネル M O S トランジスタ 2 1 , 2 3 のうちのハイサイド側の N チャネル M O S トランジスタ 2 1 を使用して逆相 P W M 制御を行うことはもちろんである。

#### 【 0 0 4 7 】

A に示すように、時刻 t 1 0 でハイサイド側の N チャネル M O S トランジスタ 2 1 がオンになると、以下、負荷 2 5 に流す電流を遮断するまで、オンの状態を続ける。B に示すように、N チャネル M O S トランジスタ 2 1 と接地との間のローサイド側に直接接続される N チャネル M O S トランジスタ 2 2 はオフ状態を続ける。C に示すように、N チャネル M O S トランジスタ 2 1 と同一の組でローサイド側となる N チャネル M O S トランジスタ 2 3 は、時刻 t 1 1 から時刻 t 1 2 まではオン、時刻 t 1 2 から時刻 t 1 3 まではオフ、時刻 t 1 3 から時刻 t 1 4 まではオン、時刻 t 1 4 から時刻 t 1 5 まではオフと、オンとオフとを交互に繰返す。オンの時間とオフの時間との和に対してオンの時間の割合は、デューティと呼ばれる。D で示すように、P W M 制御を行うローサイド側の N チャネル M O S トランジスタ 2 3 と電源 + B との間に直接接続されるハイサイド側の N チャネル M O S トランジスタ 2 4 は、ローサイド側の N チャネル M O S トランジスタ 2 3 の P W M 動作でのオフの期間にオンになって環流電流を流す。C で示す時刻 t 1 2 にローサイド側がオンからオフに遷移すると、D に示すターンオフ時間 t o f f の経過後にハイサイド側の N チャネル M O S トランジスタ 2 4 がオンになるように制御する。

#### 【 0 0 4 8 】

このターンオフ時間 t o f f は、C で示すローサイド側の N チャネル M O S トランジスタ 2 3 のゲート電圧がオフになるスレッショルド電圧よりも低くなつてから実際に N チャネル M O S トランジスタ 2 3 がオフになるまでの遅れ時間である。大電流用の N チャネル M O S トランジスタ 2 3 では、ターンオフ時間 t o f f は数  $\mu$  s 程度である。N チャネル M O S トランジスタ 2 3 では、N チャネル M O S トランジスタ 2 3 のゲート電圧を監視し、ゲート電圧がオフになるスレッショルド電圧よりも高くなつてから実際に N チャネル M O S トランジスタ 2 3 がオフになるまでの遅れ時間はターンオフ時間であり、一般にターンオフ時間 t o f f よりも短い。ハイサイド側の N チャネル M O S トランジスタ 2 4 でもターンオフ時間は短い。したがって、ローサイド側の N チャネル M O S トランジスタ 2 3 のゲート電圧を監視し、ゲート電圧がオフに相当する電圧レベルになる時刻 t 1 2 から N チャネル M O S トランジスタ 2 4 がオフになるように駆動すれば、最短のターンオフ時間 t o f f が選択され、しかもノンオーバーラップ時間は確保されて貫通対策も可能となる。

#### 【 0 0 4 9 】

ターンオフ時間 t o f f は、比較器 4 1 ~ 4 4 の非反転入力側にシリーズで挿入される監視用抵抗 4 5 ~ 4 8 と比較器 4 1 ~ 4 4 の入力容量とで形成される積分回路によるディ

10

20

30

40

50

レイ時間に基づいて設定することができる。時刻  $t_{12}$  で N チャネル MOS トランジスタ 23 のゲート電圧がオフに相当する電圧レベルになると、ディレイ時間分だけ遅れて、比較器 43 から出力される論理信号が反転する。比較器 41 ~ 44、駆動ロジック 30 およびドライバ 31 ~ 34 の動作による遅延時間が N チャネル MOS トランジスタ 21 ~ 24 のターンオフ時間よりも充分に短ければ、時刻  $t_{12}$  からターンオフ時間  $t_{off}$  経過後に、N チャネル MOS トランジスタ 24 をオン状態に遷移させることができる。なお、ターンオフ時間  $t_{off}$  以外の遅延時間がターンオフ時間  $t_{off}$  に比較して無視することができない程度に大きいときは、ディレイ時間を短くし、全体として、時刻  $t_{12}$  からターンオフ時間  $t_{off}$  経過後に N チャネル MOS トランジスタ 24 をオンさせることができる。また、時刻  $t_{12} + t_{off}$  の逆相 PWM 制御でオンになる N チャネル MOS トランジスタ 24 は、PWM 制御で N チャネル MOS トランジスタ 23 を次にオンにする時刻  $t_{12}$  よりも、少なくとも N チャネル MOS トランジスタ 24 のターンオフ時間は先行してオフに制御する。

#### 【 0 0 5 0 】

すなわち、スイッチング回路 20 は、電源から供給される電流を負荷 25 に供給する経路を断続するスイッチング制御が行われる駆動側スイッチング手段としての N チャネル MOS トランジスタ 23, 22 と、負荷 25 からの環流電流を流す経路を断続するスイッチング制御が行われる環流側スイッチング手段としての N チャネル MOS トランジスタ 24, 21 を、電源 +B と接地 GND とに対して直列に接続して形成される。駆動側スイッチング手段であるローサイド側の N チャネル MOS トランジスタ 23, 22 と環流側スイッチング手段であるハイサイド側の N チャネル MOS トランジスタ 24, 21 との接続部には、負荷 25 が接続される。スイッチング回路 20 は、監視手段である比較器 43, 42 と、ディレイ手段である監視用抵抗 47, 46 を含む。監視手段である比較器 47, 46 は、駆動側スイッチング手段である N チャネル MOS トランジスタ 23, 22 のゲートでスイッチング制御用の入力信号を監視する。ディレイ手段である監視用抵抗 47, 46 は、監視手段である比較器 43, 42 が監視する駆動側スイッチング手段である N チャネル MOS トランジスタ 23, 22 をオン状態からオフ状態に遷移させる入力信号の印加時を基準に、環流側スイッチング手段である N チャネル MOS トランジスタ 24, 21 を、駆動側スイッチング手段である N チャネル MOS トランジスタ 23, 22 のターンオフ時間  $t_{off}$  を含む時間の経過後に、オン状態となるようにスイッチング駆動するためのディレイ時間を設定する。

#### 【 0 0 5 1 】

環流側スイッチング手段である N チャネル MOS トランジスタ 24, 21 は、駆動側スイッチング手段である N チャネル MOS トランジスタ 23, 22 のターンオフ時間  $t_{off}$  を含む時間の経過後に、オン状態となるようにスイッチング駆動されるので、駆動側スイッチング手段であるローサイド側の N チャネル MOS トランジスタ 23, 22 がオンの状態のまま環流側スイッチング手段であるハイサイド側の N チャネル MOS トランジスタ 24, 21 がオンになることはなく、貫通電流を確実に禁止することができる。駆動側スイッチング手段である N チャネル MOS トランジスタ 23, 22 がターンオフ時間  $t_{off}$  を経過してオフになると、環流側スイッチング手段である N チャネル MOS トランジスタ 24, 21 がオンになるので、環流電流を低損失で流すことができる。

#### 【 0 0 5 2 】

このように、駆動側スイッチング手段であるローサイド側の N チャネル MOS トランジスタ 23, 22 をオン状態からオフ状態に遷移させる入力信号の印加時を基準に、環流側スイッチング手段であるハイサイド側の N チャネル MOS トランジスタ 24, 21 を、駆動側スイッチング手段である N チャネル MOS トランジスタ 23, 22 のターンオフ時間  $t_{off}$  を含む時間の経過後に、オン状態となるようにスイッチング駆動するので、貫通電流を確実に禁止することができ、環流電流は環流側スイッチング手段である N チャネル MOS トランジスタ 24, 21 に低損失で流すことができる。

#### 【 0 0 5 3 】

10

20

30

40

50

監視手段は、入力信号の電圧を弁別し、駆動用スイッチング手段であるNチャネルMOSトランジスタ23, 22がオン状態に駆動されているかオフ状態に駆動されているかを表す論理信号を出力する比較器43, 42を含むので、比較器43, 42から出力される論理信号で駆動用スイッチング手段であるNチャネルMOSトランジスタ23, 22の駆動状態を容易に判別することができる。また、比較器43, 42の非反転側の入力端子に入力信号を導く監視用抵抗47, 46を含み、ディレイ手段は、監視用抵抗47, 46と比較器43, 42の入力端子の入力容量とで形成される回路であるので、比較器43, 42からの論理出力にはディレイ時間が含まれ、論理出力を直接利用して環流側スイッチング手段であるNチャネルMOSトランジスタ24, 21の制御を行っても、貫通電流を確実に禁止することができる。

10

## 【0054】

なお、スイッチング回路20では、駆動用スイッチング手段および環流用スイッチング手段は、いずれもNチャネルMOSトランジスタ23, 24を、スイッチング素子として備える。Nチャネルでは電子がキャリアとなり、Pチャネルでは電子に比べて重い正孔がキャリアとなるなどの理由で、大電流を駆動可能なPチャネルMOSトランジスタは、NチャネルMOSトランジスタに比較して、製造が困難で高価である。スイッチング回路20では、PチャネルMOSトランジスタの使用を避けて、NチャネルMOSトランジスタ21～24のみを用いて、大電流で負荷25を駆動することができる。

20

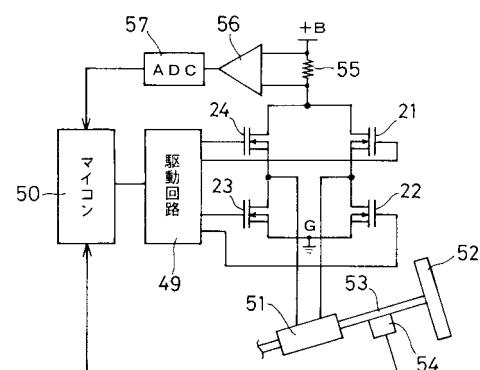

## 【0055】

図2は、図1に示すスイッチング回路20の応用例として、自動車の電動式パワーステアリング装置へ適用する構成を示す。実施の他の形態のスイッチング回路も、同様に適用することができる。各スイッチング回路は、このような電動式パワーステアリング装置に限らず、大電流のスイッチング制御で、環流電流が発生するような負荷を駆動する場合に、好適に利用することができる。

20

## 【0056】

電動式パワーステアリング装置は、自動車のエンジンが停止していてもパワーステアリング動作を行わせることができる。図1(a)の駆動ロジック30、ドライバ31～34、基準電圧源40、比較器41～44および監視用抵抗45～48を、駆動回路49として示す。パワーステアリングの動作は、マイコン50によって制御される。図1の負荷25としては、モータ51が用いられる。モータ51は、自動車の運転者などによるステアリングホイール52への角変位操作に対応してステアリング軸53を角変位させるトルクを発生する。ステアリングホイール52の操作に基づくステアリング軸53の角変位は角度センサ54によって検出され、マイコン50に入力される。電源+BとNチャネルMOSトランジスタ21～24によるHブリッジとの間には、抵抗55が設けられる。抵抗55には、電源+BからHブリッジを介してモータ51に供給する負荷電流が流れる。この負荷電流による抵抗55での電圧降下分の電圧は、差動増幅器56によって検出され、アナログデジタル変換器であるADC(Analog Digital Converter)57でデジタル信号に変換されて、マイコン50に入力される。マイコン50は、負荷電流に基づいてPWM制御のデューティを設定し、駆動ロジック30にデューティを指示する。

30

## 【0057】

自動車などでは、車体を接地に使用する。モータ51に大電流が流れる場合は、車体が電流の帰路となると、車体の電気抵抗分による電圧降下で、接地電位が場所によって変化してしまう。このように、GND間にレベル差が発生しやすいような場合は、監視手段である比較器41～44は、入力信号を、負荷25の接地位置、たとえば図2に示すGの位置などの電位を基準とする基準電圧源40の電圧に基づいて監視する。駆動側スイッチング手段への入力電圧として監視するので、大電流の制御に伴って、接地位置で電圧レベルに差がある場合でも、駆動側スイッチング手段をオフにする入力電圧を確実に検出することができる。

40

## 【0058】

なお、駆動回路49、マイコン50、差動増幅器56およびADC57などは、同一ま

50

たは複数の半導体チップ上に集積回路として形成することができる。スイッチング素子であるNチャネルMOSトランジスタ21～24および抵抗55は、一般に個別の素子を使用する。ただし、複数の素子を予めモジュールとして組合せているものを使用する場合もある。

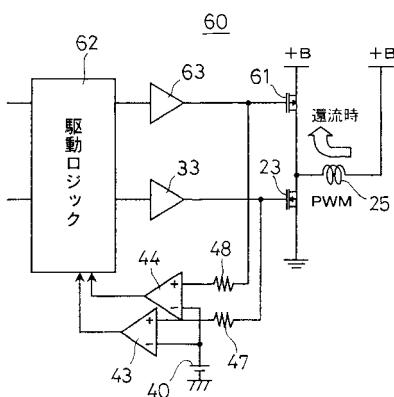

#### 【0059】

図3は、本発明の実施の第2形態としてのスイッチング回路60の概略的な電気的構成を示す。スイッチング出力は、電源+Bと接地GNDとの間に直列に接続されるハイサイド側のPチャネルMOSトランジスタ61とローサイド側のNチャネルMOSトランジスタ23との直列回路で、ハイサイド側とローサイド側との接続部分から負荷25の一端に与えられる。負荷25の他端は電源+Bに接続される。ハイサイド側のPチャネルMOSトランジスタは、ソースが電源+B側に接続され、ドレインがローサイド側のNチャネルMOSトランジスタ23のドレインに接続される。すなわち、PチャネルMOSトランジスタ61とNチャネルMOSトランジスタ23のドレインとは共通接続される。共通接続されるドレインには、負荷25の一端側も接続される。ハイサイド側のPチャネルMOSトランジスタ61がオフになって、ローサイド側のNチャネルMOSトランジスタ23がオンになれば、電源+Bから負荷電流が負荷25の他端側に供給され、負荷25の一端側からNチャネルMOSトランジスタ23のドレイン・ソース間を通って、接地GNDに到る経路を流れる。

#### 【0060】

PチャネルMOSトランジスタ61およびNチャネルMOSトランジスタ23のゲートへの駆動信号は、駆動ロジック62によって生成され、ドライバ33, 63をそれぞれ介して印加される。この駆動信号は、比較器43, 44によって監視される。ターンオフ時間などに対応するディレイ時間を設定する機能を、比較器43, 42の入力側に設けるので、比較器43, 44の入力容量を有効に利用し、部品点数などの削減を図ることができる。

#### 【0061】

図3に示すスイッチング素子の接続形態は、負荷25の他端側にも、ハイサイド側にPチャネルMOSトランジスタ、ローサイド側にNチャネルMOSトランジスタを設け、Hブリッジを構成し、ハイサイド側がオンでローサイド側がオフの状態と単純化して示す。負荷25に逆方向に電流を流す場合は、PチャネルMOSトランジスタ61をオンにし、NチャネルMOSトランジスタ23をオフにして、負荷25の他端側のハイサイド側を環流動作用、ローサイド側をPWM動作用とすればよい。負荷25に一方向のみ電流を流す場合は、図3に示すように、スイッチング素子を直列の1組のみしか用いなくてもよい。

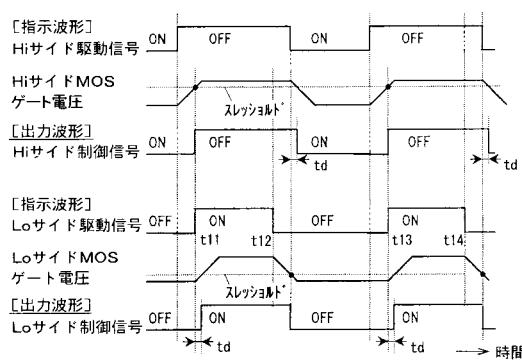

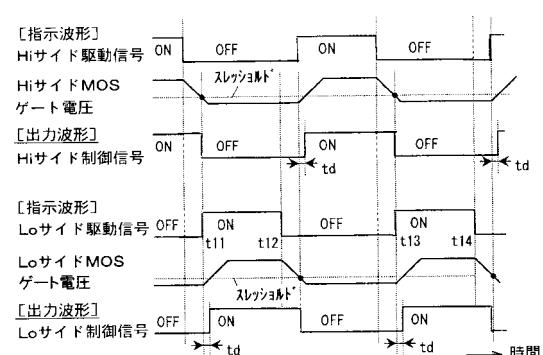

#### 【0062】

図4は、図3に示すスイッチング回路60の各部の動作波形を示す。PWM制御は、駆動用スイッチング手段であるローサイド側のNチャネルMOSトランジスタ23のゲートへのLoサイド駆動信号による指示波形が基準となる。すなわち、時刻t11でOFFに対応するローレベルからONに対応するハイレベルまでLoサイド駆動信号が遷移すると、NチャネルMOSトランジスタ23のゲート電圧であるLoサイドMOSゲート電圧は、NチャネルMOSトランジスタ23のゲートの入力容量を充電しながら上昇する。NチャネルMOSトランジスタ23が大電流制御用であれば、チャネルの幅も広く、ゲート電極の面積も大きくなり、入力容量も大きくなる。この大きな入力容量を充電するので、LoサイドMOSゲート電圧の上昇は、ドライバ33の出力インピーダンスとNチャネルMOSトランジスタ23のゲートの入力容量とで形成する積分回路による遅延を受ける。時刻t12でLoサイド駆動信号がハイレベルからローレベルに遷移する場合も、LoサイドMOSゲート電圧の下降は、入力容量に基づく遅延を受ける。NチャネルMOSトランジスタ23による負荷25の駆動の出力波形は、Loサイド制御信号として示すように、LoサイドMOSゲート電圧がスレッショルド電圧レベルよりも高くなるとオン状態となり、LoサイドMOSゲート電圧がスレッショルド電圧レベルよりも低くなるとオフ状態となる。

10

20

30

40

50

## 【0063】

ハイサイド側のPチャネルMOSトランジスタ61に対する環流時の逆相PWM制御は、PチャネルMOSトランジスタ61のゲートへのHiサイド駆動信号の指示波形が基準となる。すなわち、時刻t11に先行してONに対応するローレベルからOFFに対応するハイレベルまでHiサイド駆動信号が遷移すると、PチャネルMOSトランジスタ61のゲート電圧であるHiサイドMOSゲート電圧は、PチャネルMOSトランジスタ61のゲートの入力容量を充電しながら上昇する。PチャネルMOSトランジスタ61も大電流制御用であれば、チャネルの幅も広く、ゲート電極の面積も大きくなり、入力容量も大きくなる。この大きな入力容量を充電するので、HiサイドMOSゲート電圧の上昇は、ドライバ63の出力インピーダンスとPチャネルMOSトランジスタ61のゲートの入力容量とで形成する積分回路による遅延を受ける。時刻t12でLoサイド駆動信号がハイレベルからローレベルに遷移する場合は、遅れてHiサイド駆動信号がハイレベルからローレベルに遷移する。HiサイドMOSゲート電圧の下降も、入力容量に基づく遅延を受ける。PチャネルMOSトランジスタ63による負荷25からの環流電流を流すための出力波形は、Hiサイド制御信号として示すように、HiサイドMOSゲート電圧がスレッショルド電圧レベルよりも高くなるとオフ状態となり、HiサイドMOSゲート電圧がスレッショルド電圧レベルよりも低くなるとオン状態なる。

## 【0064】

すなわち、スイッチング回路60では、駆動用スイッチング手段と環流用スイッチング手段とのうち、電源のハイサイド+B側となるスイッチング手段はPチャネルMOSトランジスタ61を、電源のローサイドGND側となるスイッチング手段はNチャネルMOSトランジスタ23を、それぞれスイッチング素子として備える。入力信号をハイレベルにすればハイサイド側のPチャネルMOSトランジスタ61はオフになり、ローサイド側のNチャネルMOSトランジスタ23はオンになり、入力信号をローレベルにすればハイサイド側のPチャネルMOSトランジスタはオンになり、ローサイド側のNチャネルMOSトランジスタはオフになるので、ハイサイド側とローサイド側とを対称的にスイッチング駆動することができる。

## 【0065】

時刻t11でローサイド側のNチャネルMOSトランジスタ23をオフからオンに遷移させる時、駆動ロジック62は、比較器44から出力される論理信号でハイサイド側のPチャネルMOSトランジスタ61のHiサイドMOSゲート電圧の変化を監視し、監視用抵抗48によるディレイ時間を見込んで、Hiサイド制御信号がオンからオフへ遷移するタイミングでNチャネルMOSトランジスタ23のゲートに与えるLoサイド駆動信号がローレベルからハイレベルに遷移するように、Loサイド駆動信号を発生する。NチャネルMOSトランジスタ23のゲートには、LoサイドMOSゲート電圧として示すように、矩形のLoサイド駆動信号を積分した波形で入力信号が印加される。NチャネルMOSトランジスタ23は、LoサイドMOSゲート電圧がスレッショルドレベルよりも高くなるとオフからオンに遷移するので、実際にLoサイド制御信号がオフからオンに遷移するのは、時間tdだけ遅れる。この時間tdはノンオーバーラップ時間となり、PチャネルMOSトランジスタ61とNチャネルMOSトランジスタ23との同時オンによる貫通動作は禁止される。

## 【0066】

時刻t12でローサイド側のNチャネルMOSトランジスタ23をオンからオフに遷移させる時、駆動ロジック62は、比較器43から出力される論理信号でローサイド側のNチャネルMOSトランジスタ23のLoサイドMOSゲート電圧の変化を監視し、監視用抵抗47によるディレイ時間を見込んで、Loサイド制御信号がオンからオフへ遷移するタイミングでPチャネルMOSトランジスタ61のゲートに与えるHiサイド駆動信号がハイレベルからローレベルに遷移するように、Hiサイド駆動信号を発生する。PチャネルMOSトランジスタ61のゲートには、HiサイドMOSゲート電圧として示すように、矩形のHiサイド駆動信号を積分した波形で入力信号が印加される。PチャネルMOS

10

20

30

40

50

トランジスタ 6 1 は、 H i サイド M O S ゲート電圧がスレッショルドレベルよりも低くなるとオフからオンに遷移するので、実際に H i サイド制御信号がオフからオンに遷移するのは、時間  $t_d$  だけ遅れる。この時間  $t_d$  はノンオーバーラップ時間となり、 P チャネル M O S トランジスタ 6 1 と N チャネル M O S トランジスタ 2 3 との同時オンによる貫通動作は禁止される。

#### 【 0 0 6 7 】

なお、環流電流は、ハイサイド側の P チャネル M O S トランジスタ 6 1 がオフからオンに遷移する時点で多く流れるので、時刻  $t_{12}$  側での切換えのタイミングが重要である。時刻  $t_{11}$  側は、ハイサイド側のゲート電圧を監視しないで、充分な時間的マージンをとって切換えることもできる。このような切換えるタイミングについての考え方は、図 1 のスイッチング回路 2 0 についても同様である。10

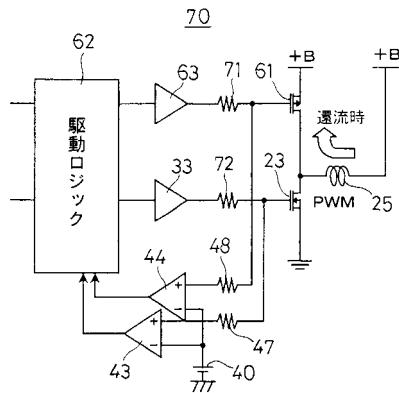

#### 【 0 0 6 8 】

図 5 は、本発明の実施の第 3 形態としてのスイッチング回路 7 0 の概略的な電気的構成を示す。スイッチング回路 7 0 では、 P チャネル M O S トランジスタ 6 1 および N チャネル M O S トランジスタ 2 3 とドライバ 6 3 およびドライバ 3 3 との間に、ゲート抵抗 7 1 , 7 2 をそれぞれシリーズに挿入している。従来技術に関しても説明しているように、大電流駆動用の M O S トランジスタはゲートの入力容量が大きいため、ドライバの損失低減やノイズ発生抑制のために、シリーズにゲート抵抗が挿入される。ゲート抵抗とゲートの入力容量とにより、 M O S トランジスタの動作タイミングにずれが発生するため、この遅延分を考慮する必要がある。比較器 4 4 , 4 3 によるゲート電圧の監視は、ゲート抵抗 7 1 , 7 2 のゲート側で行う。ノイズ低減のために挿入するゲート抵抗 7 1 , 7 2 と M O S トランジスタのゲート入力容量とによる遅延で遅れる M O S トランジスタのオン / オフタイミングを考慮して、貫通防止対策を行うことができる。20

#### 【 0 0 6 9 】

すなわち、駆動側スイッチング手段である N チャネル M O S トランジスタ 2 3 のスイッチング制御用の入力信号は、入力用抵抗であるゲート抵抗 7 2 を介して印加され、監視手段である比較器 4 3 は、ゲート抵抗 7 2 を介して印加される入力信号を監視するので、ゲート抵抗 7 2 と駆動側スイッチング手段の入力容量とで遅延する入力信号を確実に検出することができる。なお、ゲート抵抗 7 1 , 7 2 は、図 1 のスイッチング回路 2 0 に設けることもできる。30

#### 【 0 0 7 0 】

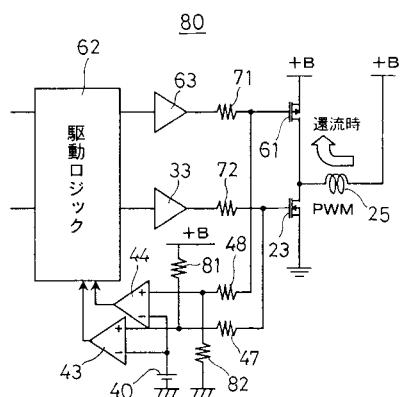

図 6 は、本発明の実施の第 4 形態としてのスイッチング回路 8 0 の概略的な電気的構成を示す。スイッチング回路 8 0 では、ドライバ 3 3 , 6 3 、比較器 4 3 , 4 4 および駆動ロジック 6 2 は、同一の半導体チップ上などに集積される。スイッチング素子である P チャネル M O S トランジスタ 6 1 および N チャネル M O S トランジスタ 2 3 は、外付けとなり、そのゲートに接続されるゲート抵抗 7 1 , 7 2 や監視用抵抗 4 8 , 4 7 も外付けとなる。このような外付け部品は、破損したり接続経路が切断されたりして、オープン故障等が生じる可能性がある。オープン故障等が生じると、比較器 4 4 , 4 3 への入力信号が浮いてしまい、不定になるおそれがある。スイッチング回路 8 0 では、比較器 4 4 , 4 3 への入力信号が不定となっても、貫通動作しないように、論理固定用抵抗 8 1 , 8 2 を追加している。なお、論理固定用抵抗 8 1 , 8 2 は、図 1 のスイッチング回路 2 0 に設けることもできる。40

#### 【 0 0 7 1 】

駆動用スイッチング手段となる N チャネル M O S トランジスタ 2 3 のゲート電圧を監視する比較器 4 3 の非反転入力側は、論理固定用抵抗 8 1 を介して電源の + B 側にプルアップされる。監視用抵抗 4 7 などのオープン故障時には、比較器 4 3 の非反転入力側は、反転入力側に与えられる基準電圧源 4 0 からの基準電圧よりも高い電圧が常に印加される。この状態は、図 4 の L o サイド M O S ゲート電圧が常にスレッショルド電圧よりも高くなっている状態に対応し、駆動ロジック 6 2 は、ローサイド側の N チャネル M O S トランジスタ 2 3 がオンからオフに遷移しないと判断するので、ハイサイド側の P チャネル M O S

10

20

30

40

50

トランジスタ 6 1 にオフ状態を続けさせる。駆動ロジック 6 2 は、ハイサイド側の P チャネルMOSトランジスタ 6 1 をオフからオンに遷移させないので、貫通動作を避けることができる。

#### 【 0 0 7 2 】

すなわち、比較器 4 3 の非反転側の入力端子に接続される論理固定用抵抗 8 1 によって、監視用抵抗 4 7 のオープン時には出力の論理信号が駆動側スイッチング手段である N チャネルMOSトランジスタ 2 3 がオン状態に駆動されていることを表す側に固定されるように、予め設定される電圧を入力端子に印加する。外付け部品である監視用抵抗 4 7 のオープン故障等により、監視手段である比較器 4 3 への入力信号が不定となる場合には、駆動側スイッチング手段である N チャネルMOSトランジスタ 2 3 への入力信号がオフ状態を表す側に駆動されると判断しなくなるので、環流側スイッチング手段である P チャネルMOSトランジスタをオンに駆動しないようになり、駆動側スイッチング手段と環流側スイッチング手段との両方がオンになる貫通動作を避けることができる。10

#### 【 0 0 7 3 】

環流用スイッチング手段となる P チャネルMOSトランジスタ 6 1 のゲート電圧を監視する比較器 4 4 の非反転入力側は、論理固定用抵抗 8 2 を介して接地 GND 側にプルダウンされる。監視用抵抗 4 8 などのオープン故障時には、比較器 4 4 の非反転入力側は、反転入力側に与えられる基準電圧源 4 0 からの基準電圧よりも低い電圧が常に印加される。この状態は、図 4 の Hi サイドMOSゲート電圧が常にスレッショルド電圧よりも低い状態に対応し、ハイサイド側の P チャネルMOSトランジスタ 6 1 がオンからオフに遷移しないので、駆動ロジック 6 2 は、ローサイド側の N チャネルMOSトランジスタ 2 3 にオフ状態を続けさせ、オフからオンに遷移させないので、貫通動作を避けることができる。20

#### 【 0 0 7 4 】

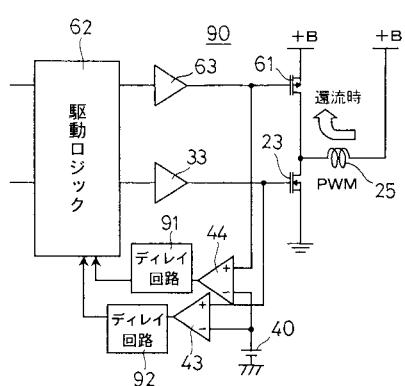

図 7 は、本発明の実施の第 5 形態としてのスイッチング回路 9 0 の概略的な電気的構成を示す。スイッチング回路 8 0 では、ディレイ回路 9 1 , 9 2 を比較器 4 4 , 4 3 の後段にそれぞれ設けるようにしている。ディレイ回路 9 1 , 9 2 は、比較器 4 4 , 4 3 から出力される論理信号にディレイ時間分だけの遅延を与えればよいので、デジタルプロセスでの実現が容易であり、システム動作中にディレイ時間を変化させることも可能となる。ディレイ回路 9 1 , 9 2 も駆動ロジック 6 2 、ドライバ 6 3 , 3 3 、基準電圧源 4 0 および比較器 4 4 , 4 3 とともに半導体集積回路として形成することができ、外付けの部品点数を削減することもできる。なお、ドライバ 6 3 , 3 3 は、ゲート抵抗を介して P チャネルMOSトランジスタ 6 1 および N チャネルMOSトランジスタ 2 3 をそれぞれ駆動するようにしてもよいことはもちろんである。30

#### 【 0 0 7 5 】

すなわち、スイッチング回路 9 0 で、ディレイ手段であるディレイ回路 9 1 , 9 2 は、監視手段である比較器 4 4 , 4 3 の監視結果を遅延させてディレイ時間を設定するので、監視手段が監視結果を論理信号で出力すれば、デジタルプロセスで遅延を容易に実現することができ、システム動作中のディレイ時間の可変も可能となる。

#### 【 0 0 7 6 】

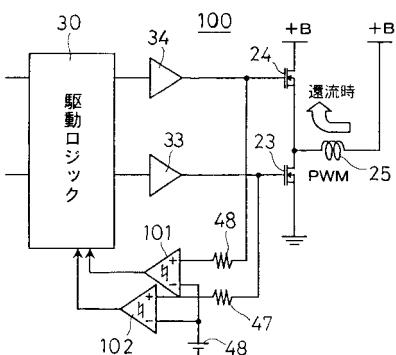

図 8 は、本発明の実施の第 6 形態としてのスイッチング回路 1 0 0 の概略的な電気的構成を示す。スイッチング回路 1 0 0 では、図 1 のスイッチング回路 2 0 と同様な比較器の代りに、ヒステリシスを持たせている比較器 1 0 1 , 1 0 2 をそれぞれ使用する。図 3 のスイッチング回路 3 0 のように、ハイサイド側に P チャネルMOSトランジスタ 6 1 を使用する場合や、ゲート抵抗 7 1 , 7 2 を用いたり、監視用抵抗 4 8 , 4 7 を用いたり、論理固定用抵抗 8 1 , 8 2 を用いる場合も同様である。40

#### 【 0 0 7 7 】

ヒステリシス付の比較器 1 0 2 を用いることによって、監視手段は、駆動側スイッチング手段である N チャネルMOSトランジスタ 2 3 のスイッチング制御用の入力信号を、チャタリング防止用のヒステリシスを付けて監視するので、駆動用スイッチング手段のオンやオフのタイミングで発生するノイズによって誤認識することなく、貫通対策を行うこと50

ができる。ヒステリシス付の監視は、他の実施形態でも同様に行うことができる。

#### 【0078】

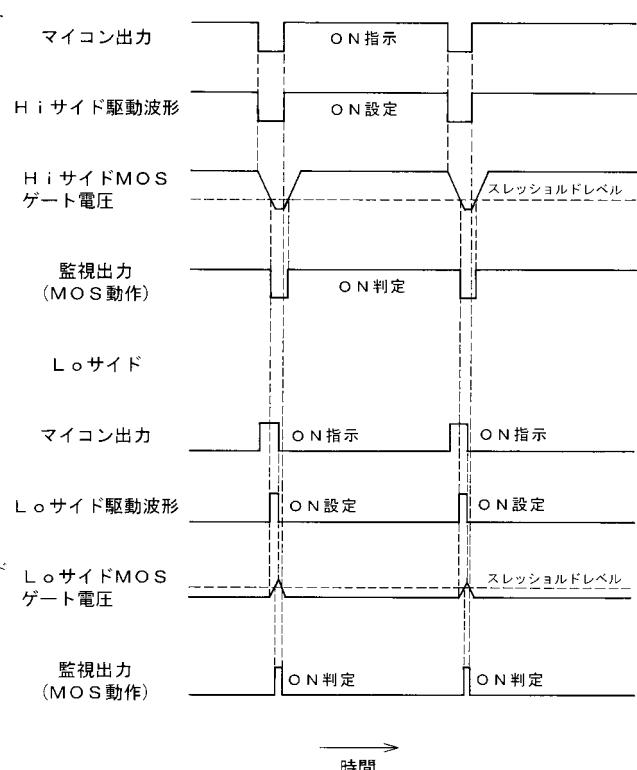

図9は、図8のスイッチング回路100での動作波形を示す。ハイサイド側にもNチャネルMOSトランジスタ24を使用するので、HiサイドMOSゲート電圧がスレッショルド電圧よりも高ければハイサイド側のNチャネルMOSトランジスタ24はオンになり、HiサイドMOSゲート電圧がスレッショルド電圧よりも低ければハイサイド側のNチャネルMOSトランジスタ24はオフになる。図1のスイッチング回路20でも同様である。HiサイドMOSゲート電圧とLoサイドMOSゲート電圧とを監視して、Loサイド駆動信号およびHiサイド駆動信号をそれぞれ生成し、遅れ時間 を最適化して貫通動作を避け、しかも低損失の環流動作を行わせることができる。 |

10

#### 【0079】

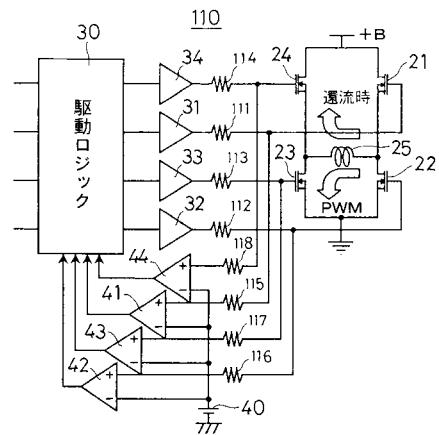

図10は、本発明の実施の第7形態としてのスイッチング回路110の概略的な電気的構成を示す。スイッチング回路110では、Hブリッジを構成するNチャネルMOSトランジスタ21～24をゲート抵抗111～114を介してそれぞれ駆動し、ゲートへの入力電圧を監視用抵抗115～118を介して比較器41～44でそれぞれ監視する。各NチャネルMOSトランジスタ21～24のターンオフ時間や比較器41～44の入力容量は異なる場合があるけれども、監視用抵抗115～118の抵抗値を調整して、各監視手段としてのディレイ時間を個別に設定し、各NチャネルMOSトランジスタ21～24のターンオフ時間に合わせて、最適な貫通対策を行うことができる。

20

#### 【0080】

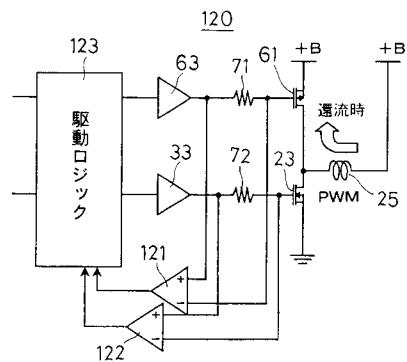

図11は、本発明の実施の第8形態としてのスイッチング回路120の概略的な電気的構成を示す。スイッチング回路120では、ゲート抵抗71, 72の両端の電圧を比較器121, 122でそれぞれ監視し、その電位差が規定値以下となることで、論理ロジック123はPチャネルMOSトランジスタ61およびNチャネルMOSトランジスタ23のオフ動作が完了したと判断する。図4および図9に示すHiサイドMOSゲート電圧およびLoサイドMOSゲート電圧が上昇または下降している期間は、ゲート抵抗71, 72をゲート容量を充電または放電するための電流が流れ、ゲート抵抗71, 72の両端の電位差は大きくなる。入力容量の充電または放電が終了することは、電位差が既定値以下となることで判断することができる。図1のスイッチング回路20のように、ハイサイド側がNチャネルMOSトランジスタ24であっても、同様に判断することができる。

30

#### 【0081】

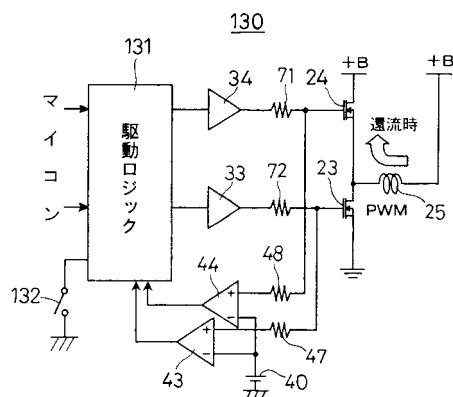

図12は、本発明の実施の第9形態としてのスイッチング回路130の概略的な電気的構成を示す。スイッチング回路130では、駆動ロジック131に、制御スイッチ132が接続され、逆相PWMを禁止するように指示を与えることができる。すなわち、スイッチング回路130は、駆動側スイッチング手段であるローサイド側のNチャネルMOSトランジスタ24に印加する入力信号を、PWM制御を行うように発生する駆動ロジック131と、駆動ロジック131によるPWM制御でのデューティが0に近くなり、環流用スイッチング手段であるハイサイド側のNチャネルMOSトランジスタ24に対するスイッチング制御が逆相PWM制御となる領域では、逆相PWM制御を禁止する指定が可能な逆相PWM禁止手段である制御スイッチ132とをさらに含む。このような制御スイッチ132は、たとえばオフで通常動作を指示し、オンで逆相PWM禁止動作を指示するものであり、他の実施形態でも使用することができる。

40

#### 【0082】

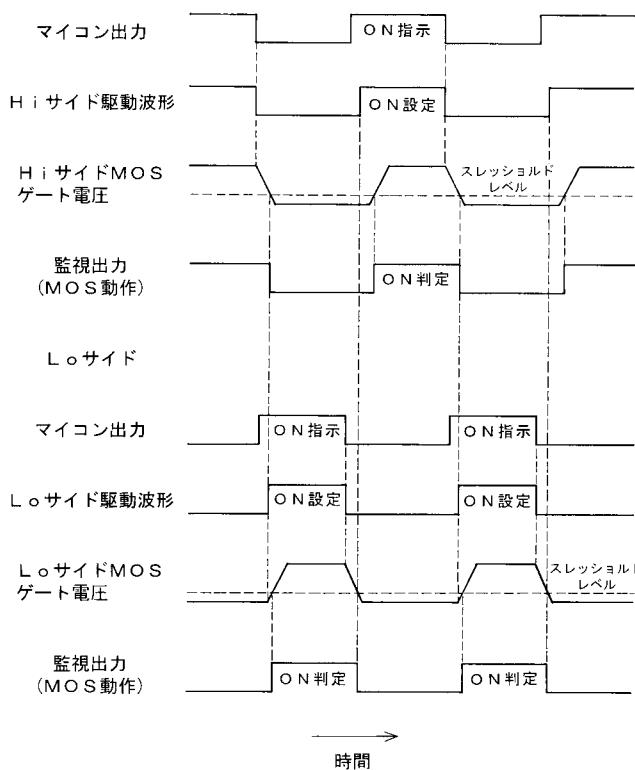

図13は、PWM制御のデューティが0よりも充分に大きい通常動作時のスイッチング回路130の動作波形を示す。駆動ロジック131には、Hiサイド側とLoサイド側とにマイコン出力として示すON指示が与えられる。マイコン出力は、Loサイド側でPWM制御のデューティに応じた時間割合でON指示となり、Hiサイド側では環流動作のための逆相PWM制御のデューティに応じたタイミングでのON指示となる。駆動ロジック131からハイサイド側およびローサイド側のNチャネルMOSトランジスタ24, 23のゲートにそれぞれ出力されるHiサイド駆動信号およびLoサイド駆動信号は、ON

50

指示の終了時にはマイコン出力に従ってON設定を終了するように遷移するけれども、ON指示の開始時には、監視出力の変化を待って遷移する。すなわち、ハイサイド側では、マイコン出力のON指示が開始されても、ローサイド側のNチャネルMOSトランジスタ23のゲート電圧の監視結果である比較器43の監視出力がMOS動作のON判定を続けている限り、Hiサイド駆動信号をON設定には遷移させない。この監視出力のON判定が終了すると、Hiサイド駆動信号はON設定に遷移する。Loサイド駆動信号も、マイコン出力によるON指示だけではON設定には遷移しないで、ハイサイド側の監視出力のON判定が終了すると、ON設定に遷移する。

#### 【0083】

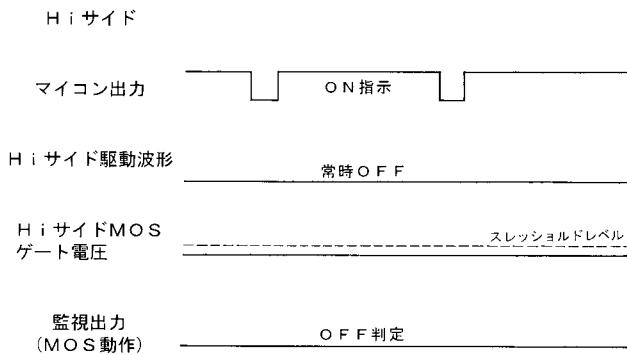

図14は、PWM制御のデューティが0に近い通常動作時でのスイッチング回路130の動作波形を示す。デューティが0に近くなってくると、Hiサイド側の監視出力のON判定が終了する遷移で駆動ロジック131はLoサイド駆動信号をON設定に遷移させるので、ドライバ33がローサイド側のNチャネルMOSトランジスタ23のゲートをオンにするように駆動するハイレベル出力の時間が短くなる。NチャネルMOSトランジスタ23のゲートに印加されるLoサイドMOSゲート電圧がスレッショルドの電圧レベルを越えて、比較器43でON判定される時間はさらに短くなるので、図14よりもマイコン出力でのON指示期間が短くなると、デューティは0にならなくても、NチャネルMOSトランジスタ23がオンになる期間がなくなってしまう。

#### 【0084】

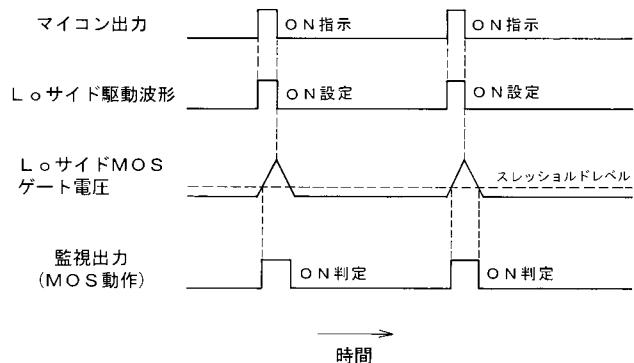

図15は、制御スイッチ132をオンにする逆相PWM動作禁止時でのスイッチング回路130の動作波形を示す。制御スイッチ132をオンにすると、駆動ロジック130は、逆相PWM制御の動作を行うハイサイド側のNチャネルMOSトランジスタ24のゲートを駆動するHiサイド駆動信号をON設定にはしないで常時OFFにする。NチャネルMOSトランジスタ24のゲートに与えられるHiサイドMOSゲート電圧は、スレッショルドの電圧レベルよりも低い状態を続け、比較器44によるMOS動作の監視出力もOFF判定を続ける。Loサイド側では、ハイサイド側の監視出力がOFF判定となっているので、マイコン出力がON指示への遷移を開始すると、直ちに駆動ロジック130からのLoサイド駆動信号もON設定への遷移を開始する。このような逆相PWM動作禁止で、ハイサイド側のNチャネルMOSトランジスタ24をオンさせずに、ローサイド側のNチャネルMOSトランジスタ23のオン時間を確保することができる。

#### 【0085】

ここで、逆相PWM動作を禁止すると、環流電流の処理が問題となる。デューティが0に近いことは、負荷25への負荷電流が少ないことを意味する。負荷電流が少なければ、負荷電流のエネルギーが蓄積されて発生する環流電流も少なくなる。MOSトランジスタには、構造的に、ドレインとバックゲートとの間にボディダイオードと呼ばれるダイオードが形成されている。このダイオードは、通常の使用状態では逆方向となり、無視することができる。逆相PWM動作の禁止でハイサイド側のNチャネルMOSトランジスタ24を常時OFFにすると、環流電流に対してはボディダイオードが順方向となる。スイッチング素子に通常は逆方向となるフリーホイールダイオードを接続することもできる。デューティが0付近では環流電流が少なくなるので、ダイオードに流し続けても、発熱の問題はなくなる。

#### 【0086】

各実施形態のスイッチング回路では、従来のようにマージンを大きくとる必要がないので、ノンオーバーラップ時間としてのターンオフ時間の誤差を小さくすることができるけれども、0にすることはできない。制御スイッチ132のような逆相PWM制御動作の禁止を指示する手段を設ければ、PWM制御のデューティが小さくなつて0に近くなるときには、環流電流を流すための逆相PWM制御を禁止し、それによって、逆相PWM制御によるONからOFFへの遷移を確認してからONになるまでのターンオフ時間の発生を0にすることができます。すなわち、逆相PWM制御を禁止するだけで、ターンオフ時間を0とすることができます。

10

20

30

40

50

## 【0087】

また各実施形態では、駆動用スイッチング手段および環流用スイッチング手段の組合せは、複数設けられ、負荷はその複数の接続端子を有し、各接続端子は各組合せの環流用スイッチング手段と駆動用スイッチング手段との接続部にそれぞれ接続されるので、Hブリッジなどの2相や3相モータなどのような多相の駆動回路を容易に実現することができる。スイッチング素子としてNチャネルMOSトランジスタまたはPチャネルMOSトランジスタを用いているけれども、バイポーラトランジスタやIGBT(Insulated Gate Bipolar Transistor)など、他のスイッチング素子を用いることもできる。また、スイッチング素子は、複数を並列に用いることもできる。

## 【0088】

監視手段は、各組合せの駆動用スイッチング手段のスイッチング制御用の入力信号をそれぞれ監視するので、多相の各相で確実に貫通電流を禁止することができる。監視手段では、比較器を用いて、アナログ電圧でスイッチング素子の入力電圧を監視しているけれども、アナログ電圧をADCでデジタル値に変換してから監視することもできる。

## 【0089】

なお、スイッチング素子のターンオフ時間などのスイッチング特性は、個別に実測することもできる。大電流の制御を行う際には、実際に使用するスイッチング素子の個別のスイッチング特性に合わせてディレイ時間などのタイミングを設定し、効率の向上を図ることができる。また、スイッチング素子の製造過程では、スイッチング特性の試験データが測定され、特定の製造ロットに対しては、少なくとも統計的な平均値やばらつきの範囲などの試験データが得られるはずである。このような試験データに基づいて、ディレイ時間などを設定することもできる。

## 【図面の簡単な説明】

## 【0090】

【図1】本発明の実施の第1形態としてのスイッチング回路20の概略的な電気的構成を示すブロック図、およびスイッチング回路20の基本的な動作波形図である。

【図2】図1に示すスイッチング回路20の応用例として、自動車の電動式パワーステアリング装置へ適用する構成を示すブロック図である。

【図3】本発明の実施の第2形態としてのスイッチング回路60の概略的な電気的構成を示すブロック図である。

【図4】図3に示すスイッチング回路60の各部の動作波形図である。

【図5】本発明の実施の第3形態としてのスイッチング回路70の概略的な電気的構成を示すブロック図である。

【図6】本発明の実施の第4形態としてのスイッチング回路80の概略的な電気的構成を示すブロック図である。

【図7】本発明の実施の第5形態としてのスイッチング回路90の概略的な電気的構成を示すブロック図である。

【図8】本発明の実施の第6形態としてのスイッチング回路100の概略的な電気的構成を示すブロック図である。

【図9】図8のスイッチング回路100での動作波形図である。

【図10】本発明の実施の第7形態としてのスイッチング回路110の概略的な電気的構成を示すブロック図である。

【図11】本発明の実施の第8形態としてのスイッチング回路120の概略的な電気的構成を示すブロック図である。

【図12】本発明の実施の第9形態としてのスイッチング回路130の概略的な電気的構成を示すブロック図である。

【図13】図12のスイッチング回路130で、通常動作時に、デューティが0よりも充分に大きいときの動作波形図である。

【図14】図12のスイッチング回路130で、通常動作時に、デューティが0に近いときの動作波形図である。

10

20

30

40

50

【図15】図12のスイッチング回路130で、逆相PWM動作禁止時に、デューティが0に近いときの動作波形図である。

【図16】従来からのスイッチング回路の概略的な電気的構成を示すブロック図、およびス基本的な動作波形図である。

【符号の説明】

【0091】

20, 60, 70, 80, 90, 100, 110, 120, 130 スイッチング回路

21, 22, 23, 24 NチャネルMOSトランジスタ

25 負荷

30, 62, 123, 131 駆動ロジック

31, 32, 33, 34, 63 ドライバ

40 基準電圧源

41, 42, 43, 44, 101, 102, 121, 122 比較器

45, 46, 47, 48 監視用抵抗

71, 72, 111, 112, 113, 114 ゲート抵抗

81, 82 論理固定用抵抗

91, 92 ディレイ回路

132 設定スイッチ

10

【図1】

(b)

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

【図9】

【図10】

【図12】

【図11】

【図13】

Hi サイド

【図14】

Hi サイド

【図15】

L*o* サイド

【図16】

(b)

---

フロントページの続き(51)Int.Cl.<sup>7</sup>H 03K 17/687

H 03K 19/0175

F I

H 03K 17/687

H 03K 19/00 101F

テーマコード(参考)

(72)発明者 木戸 啓介

兵庫県神戸市兵庫区御所通1丁目2番28号 富士通テン株式会社内

F ターム(参考) 5H740 AA04 BA12 BB05 BC01 BC02 KK01 MM11

5J055 AX24 AX27 AX32 BX16 CX28 DX22 DX56 DX60 DX72 DX73

DX83 EX02 EX07 EY01 EY05 EY21 EZ05 EZ10 EZ23 EZ24

EZ50 FX18 FX31 GX01 GX02 GX04 GX05

5J056 AA05 BB19 BB45 CC00 CC05 DD13 DD29 DD53 EE06 EE07

FF09 GG08 KK01

5J500 AA01 AA15 AA27 AA41 AC36 AF19 AH10 AH25 AH33 AH38

AK15 AK17 AK53 AM09 AT01 AT06 WU10