(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7158373号

(P7158373)

(45)発行日 令和4年10月21日(2022.10.21)

(24)登録日 令和4年10月13日(2022.10.13)

(51)国際特許分類

|        |                   |        |        |         |

|--------|-------------------|--------|--------|---------|

| H 01 L | 29/786 (2006.01)  | H 01 L | 29/78  | 6 1 6 T |

| H 01 L | 21/336 (2006.01)  | H 01 L | 29/78  | 6 1 8 C |

| H 01 L | 27/088 (2006.01)  | H 01 L | 29/78  | 6 2 7 D |

| H 01 L | 21/8234 (2006.01) | H 01 L | 27/088 | 3 3 1 E |

|        |                   | H 01 L | 27/088 | B       |

請求項の数 13 (全28頁) 最終頁に続く

(21)出願番号 特願2019-506348(P2019-506348)

(86)(22)出願日 平成29年7月12日(2017.7.12)

(65)公表番号 特表2019-525478(P2019-525478)

A)

(43)公表日 令和1年9月5日(2019.9.5)

(86)国際出願番号 PCT/US2017/041755

(87)国際公開番号 WO2018/031175

(87)国際公開日 平成30年2月15日(2018.2.15)

審査請求日 令和2年6月25日(2020.6.25)

(31)優先権主張番号 15/234,889

(32)優先日 平成28年8月11日(2016.8.11)

(33)優先権主張国・地域又は機関

米国(US)

前置審査

(73)特許権者 507364838

クアルコム, インコーポレイテッド

アメリカ合衆国 カリフォルニア 9 2 1

2 1 サン デイエゴ モアハウス ドライ

ブ 5 7 7 5

(74)代理人 100108453

弁理士 村山 靖彦

(74)代理人 100163522

弁理士 黒田 晋平

(72)発明者 シナン・ゴクテペリ

アメリカ合衆国・カリフォルニア・ 9 2

1 2 1 - 1 7 1 4 ・サン・ディエゴ・モ

アハウス・ドライヴ・ 5 7 7 5

リチャード・ハモンド

イギリス・S T 7 ・4 J Z ・スタッフ

最終頁に続く

(54)【発明の名称】 裏面半導体成長

## (57)【特許請求の範囲】

## 【請求項1】

半導体層内のトランジスタであって、酸化物層を覆い、前記半導体層内に第1のソース/ドレイン領域およびボディ領域を含む、トランジスタと、

前記トランジスタの前記第1のソース/ドレイン領域に結合された、隆起したソース/ドレイン領域であって、前記酸化物層を通して前記酸化物層を支持するように配置された誘電体層の方に延びる、隆起したソース/ドレイン領域と、

前記トランジスタの前記ボディ領域に結合された隆起したボディ領域であって、前記酸化物層を通して前記誘電体層の中に延び、前記隆起したボディ領域と前記隆起したソース/ドレイン領域とが、前記酸化物層を介して分離された、隆起したボディ領域と、

前記トランジスタの前記隆起したソース/ドレイン領域および/または前記隆起したボディ領域に結合された金属被覆とを備え、

前記隆起したボディ領域が、エピタキシャルに成長した半導体材料から構成され、

前記隆起したソース/ドレイン領域が、前記トランジスタの前記第1のソース/ドレイン領域と自己整合される、集積回路構造。

## 【請求項2】

前記隆起したソース/ドレイン領域が、エピタキシャルに成長した半導体材料から構成される、請求項1に記載の集積回路構造。

## 【請求項3】

前記トランジスタの第2のソース/ドレイン領域に結合された第2の金属被覆をさらに備

え、前記第2の金属被覆が前記隆起したソース/ドレイン領域に結合された前記金属被覆から遠位にある、請求項1に記載の集積回路構造。

**【請求項4】**

前記第2の金属被覆が、前記トランジスタの前記第2のソース/ドレイン領域上の接点に結合された配線工程(BEOL)相互接続を備え、前記BEOL相互接続が第2の誘電体層内部にある、請求項3に記載の集積回路構造。

**【請求項5】**

前記隆起したソース/ドレイン領域が、前記トランジスタの前記第1のソース/ドレイン領域のドーパントとは異なるドーパントでドープされる、請求項1に記載の集積回路構造。

**【請求項6】**

無線周波数(RF)フロントエンドモジュールに組み込まれ、前記RFフロントエンドモジュールが、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)、固定ロケーションデータユニット、モバイル電話、およびポータブルコンピュータのうちの少なくとも1つに組み込まれる、請求項1に記載の集積回路構造。

**【請求項7】**

集積回路構造を構築する方法であって、

絶縁層に接触する半導体層を使用してトランジスタを製作するステップであって、前記トランジスタがゲート、ソース/ドレイン領域、およびボディ領域を含む、ステップと、

マスクとして前記ゲートを使用して、少なくとも、前記絶縁層を支持し且つ前記絶縁層に接触する誘電体層内に、イオンを注入するステップであって、前記集積回路構造のトランジスタ側から実行される、ステップと、

前記誘電体層内の注入された欠陥に従って前記誘電体層をパターニングするステップであって、前記注入された欠陥が、前記トランジスタの前記ソース/ドレイン領域に近接する、ステップと、

前記ソース/ドレイン領域を前記誘電体層および前記絶縁層を通して露出させるステップと、

前記トランジスタの前記ソース/ドレイン領域に結合された隆起したソース/ドレイン領域を製作するステップであって、前記隆起したソース/ドレイン領域が、前記ソース/ドレイン領域から前記誘電体層の方に延びる、ステップと、

前記トランジスタの前記隆起したソース/ドレイン領域に結合された金属被覆を製作するステップとを含む、方法。

**【請求項8】**

前記隆起したソース/ドレイン領域を製作するステップが、前記トランジスタの前記ソース/ドレイン領域上に半導体層を選択的に成長させるステップを含む、請求項7に記載の方法。

**【請求項9】**

前記隆起したソース/ドレイン領域を形成するために前記半導体層をアニールするステップをさらに含む、請求項8に記載の方法。

**【請求項10】**

前記隆起したソース/ドレイン領域上にシリサイドを堆積させるステップと、

前記シリサイドおよび前記誘電体層の上に第2の誘電体層を堆積させるステップとをさらに含む、請求項7に記載の方法。

**【請求項11】**

前記隆起したソース/ドレイン領域を製作するステップが、前記ソース/ドレイン領域の露出部分の上に半導体層を堆積させるステップを含む、請求項7に記載の方法。

**【請求項12】**

前記集積回路構造を無線周波数(RF)フロントエンドモジュールに組み込まれるステップであって、前記RFフロントエンドモジュールが、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末(PDA)

10

20

30

40

50

、固定ロケーションデータユニット、モバイル電話、およびポータブルコンピュータのうちの少なくとも1つに組み込まれる、ステップをさらに含む、請求項1に記載の方法。

【請求項13】

請求項1に記載の前記集積回路構造と、

前記トランジスタの出力に結合されたアンテナとを備える、無線周波数(RF)フロントエンドモジュール。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、一般に、集積回路(IC)に関する。より詳細には、本開示は、裏面半導体成長のための方法および装置に関する。

10

【背景技術】

【0002】

高性能ダイプレクサを含むモバイル無線周波(RF)チップ構成(たとえば、モバイルRFトランシーバ)は、コストおよび電力消費量の問題に起因してディープサブミクロンプロセスノードに移行している。そのようなモバイルRFトランシーバの設計は、このディープサブミクロンプロセスノードにおいて複雑になる。これらのモバイルRFトランシーバの設計は、キャリアアグリゲーションなどの通信拡張機能をサポートするための追加の回路機能によってさらに複雑さが増している。モバイルRFトランシーバに関する設計上のさらなる問題には、不適合、ノイズ、および性能面のその他の問題を含むアナログ/RF性能面の問題が含まれる。このようなモバイルRFトランシーバの設計には、たとえば共振を抑制するため、および/またはフィルタ処理、バイパス、および結合を実行するために追加の受動デバイスを使用することが含まれる。

20

【0003】

これらのモバイルRFトランシーバの設計には、シリコンオンインシュレータ(SOI)技術の使用が含まれ得る。SOI技術は、寄生デバイスキャパシタンスを低減して性能を改善するために、従来のシリコン基板を層状シリコンオンインシュレータ基板と置き換える。シリコン接合は電気的絶縁体、典型的には埋込み酸化物(BOX)層の上にあるので、SOIベースのデバイスは、従来のシリコン製デバイスとは異なる。しかしながら、低減された厚さのBOX層は、シリコン層上の能動デバイスとBOX層を支持する基板との近接によって生じる寄生キャパシタンスを十分に低減しない場合がある。

30

【0004】

SOI層上の能動デバイスは、相補型金属酸化物半導体(CMOS)トランジスタを含み得る。残念ながら、SOI技術を使用して成功しているトランジスタの製作は、隆起したソース/ドレイン領域の使用を伴う場合がある。従来、隆起したソース/ドレインは、隆起したソース/ドレイン領域と後続の金属被覆層との間の接触を可能にするように指定される。加えて、隆起したソース/ドレイン領域は、キャリアが進むためのチャネルを提供する。その結果、隆起したソース/ドレイン領域を有する従来のトランジスタは、概して、隆起したソース/ドレイン領域の問題に遭遇する。ソース/ドレイン領域の問題は、トランジスタのゲートとソース/ドレイン領域との間のフリンジキャパシタンスおよびオーバーラップキャパシタンスの形態の不要な寄生キャパシタンスによって特徴づけられる。

40

【発明の概要】

【課題を解決するための手段】

【0005】

集積回路構造は、絶縁層によって支持される前面半導体層上のトランジスタを含み得る。トランジスタは、第1のソース/ドレイン/ボディ領域を含む。集積回路構造はまた、トランジスタの第1のソース/ドレイン/ボディ領域の裏面に結合された隆起したソース/ドレイン/ボディ領域を含み得る。隆起したソース/ドレイン/ボディ領域は、第1のソース/ドレイン/ボディ領域の裏面から絶縁層を支持する裏面誘電体層の方に延びてもよい。集積回路構造は、隆起したソース/ドレイン/ボディ領域に結合された裏面金属被覆をさらに含み

50

得る。

【 0 0 0 6 】

集積回路構造を構築する方法は、絶縁層によって支持される前面半導体層を使用してトランジスタを製作するステップを含み得る。トランジスタは、第1のソース/ドレイン/ボディ領域を含む。方法はまた、第1のソース/ドレイン/ボディ領域の裏面を露出させるステップを含み得る。方法は、トランジスタの第1のソース/ドレイン/ボディ領域の裏面に結合された隆起したソース/ドレイン/ボディ領域を製作するステップをさらに含み得る。隆起したソース/ドレイン/ボディ領域は、第1のソース/ドレイン/ボディ領域の裏面から絶縁層を支持する第1の裏面誘電体層の方に延びてもよい。方法はまた、隆起したソース/ドレイン/ボディ領域に結合された裏面金属被覆を製作するステップを含み得る。

10

【 0 0 0 7 】

集積回路構造は、絶縁層によって支持される前面半導体層上のトランジスタを含み得る。トランジスタは、第1のソース/ドレイン/ボディ領域を含む。集積回路構造はまた、トランジスタの第1のソース/ドレイン/ボディ領域の裏面を絶縁層から絶縁層を支持する裏面誘電体層の方に延ばすための手段を含み得る。集積回路構造は、延ばす手段を介して第1のソース/ドレイン/ボディ領域の裏面に結合された裏面金属被覆をさらに含み得る。

【 0 0 0 8 】

無線周波数(RF)フロントエンドモジュールは、集積RF回路構造を含み得る。集積RF回路構造は、絶縁層によって支持される前面半導体層上のスイッチトランジスタを含み得る。スイッチトランジスタは、スイッチトランジスタの第1のソース/ドレイン/ボディ領域の裏面に結合された、第1のソース/ドレイン/ボディ領域と隆起したソース/ドレイン/ボディ領域とを含む。隆起したソース/ドレイン/ボディ領域は、第1のソース/ドレイン/ボディ領域の裏面から絶縁層を支持する裏面誘電体層の方に延びる。スイッチトランジスタはまた、隆起したソース/ドレイン/ボディ領域に結合された裏面金属被覆を含む。REフロントエンドモジュールは、スイッチトランジスタの出力に結合されたアンテナをさらに含み得る。

20

【 0 0 0 9 】

上記では、後続の発明を実施するための形態がより良く理解できるように、本開示の特徴および技術的利点について、かなり大まかに概説してきた。本開示の追加の特徴および利点について以下において説明する。本開示が、本開示と同じ目的を果たすための他の構造を変更または設計するための基礎として容易に利用できることを、当業者には諒解されたい。そのような同等な構成が、添付の特許請求の範囲に記載されるような本開示の教示から逸脱しないことも、当業者には理解されたい。本開示の構成と動作方法の両方に関して本開示の特徴になると考えられる新規の特徴が、さらなる目的および利点とともに、以下の説明を添付の図と併せて検討することからより十分に理解されるであろう。しかしながら、図の各々が、例示および説明のために提供されるにすぎず、本開示の範囲を定めるものではないことは明確に理解されたい。

30

【 0 0 1 0 】

本開示をより完全に理解できるように、ここで、添付の図面と併せて以下の説明を参照する。

40

【図面の簡単な説明】

【 0 0 1 1 】

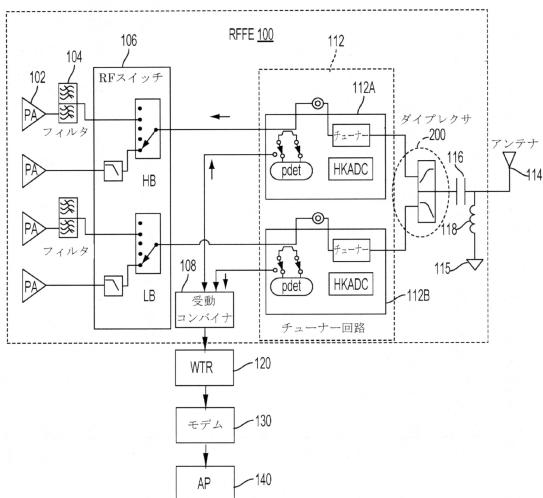

【図1 A】本開示の一態様による、ダイプレクサを使用する無線周波数(RF)フロントエンド(RFFE)モジュールの概略図である。

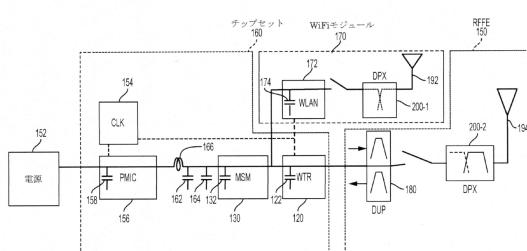

【図1 B】本開示の態様による、チップセット用のダイプレクサを使用してキャリアアグリゲーションを実現する無線周波数(RF)フロントエンド(RFFE)モジュールの概略図である。

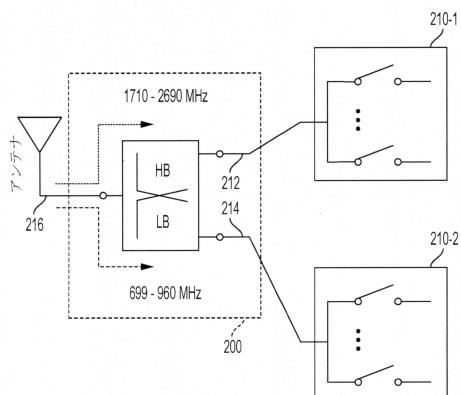

【図2 A】本開示の一態様によるダイプレクサ構成の図である。

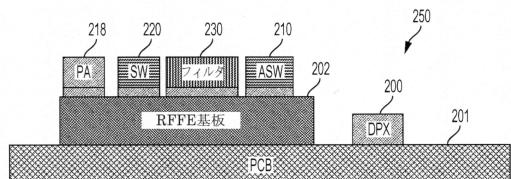

【図2 B】本開示の一態様による無線周波数(RF)フロントエンドモジュールの図である。

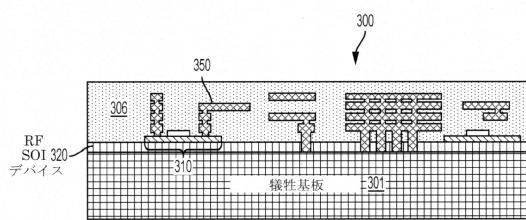

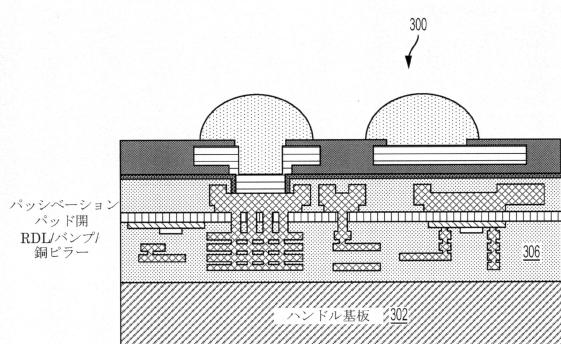

【図3 A】本開示の一態様による、層転写プロセスの間の集積無線周波数(RF)回路構造の

50

断面図である。

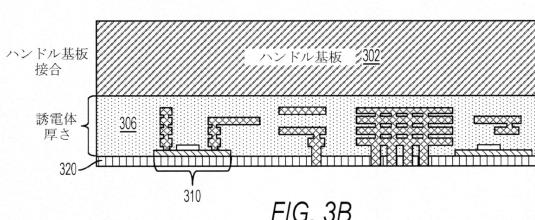

【図 3 B】本開示の一態様による、層転写プロセスの間の集積無線周波数(RF)回路構造の断面図である。

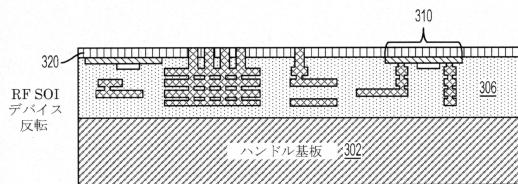

【図 3 C】本開示の一態様による、層転写プロセスの間の集積無線周波数(RF)回路構造の断面図である。

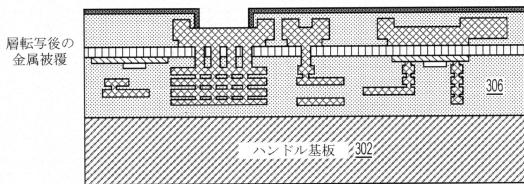

【図 3 D】本開示の一態様による、層転写プロセスの間の集積無線周波数(RF)回路構造の断面図である。

【図 3 E】本開示の一態様による、層転写プロセスの間の集積無線周波数(RF)回路構造の断面図である。

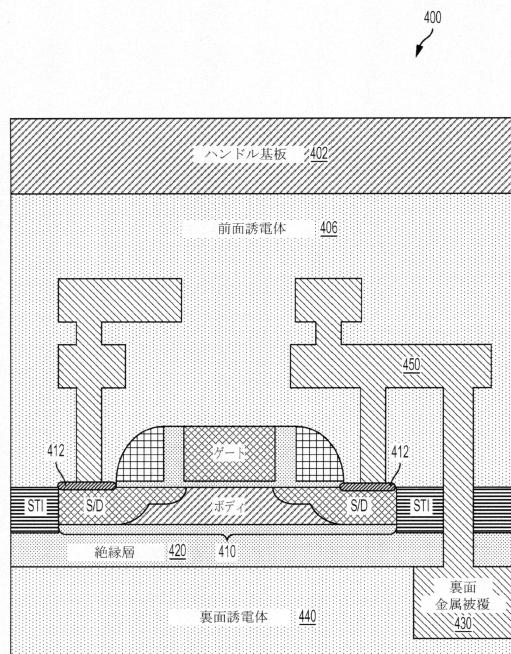

【図 4】本開示の態様による、層転写プロセスを使用して製作された集積無線周波数(RF)回路構造の断面図である。 10

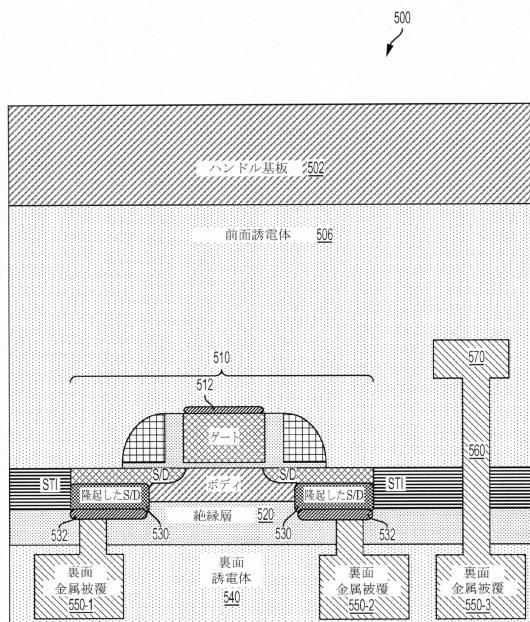

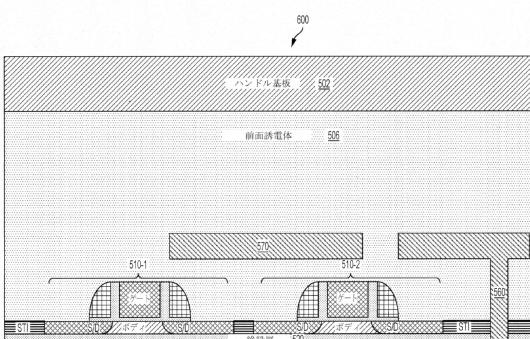

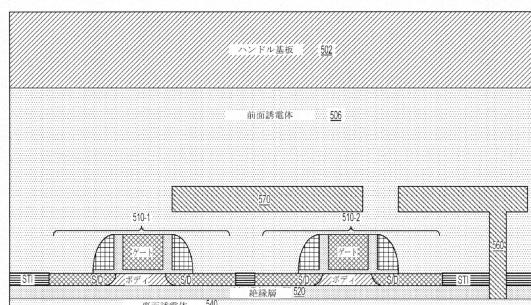

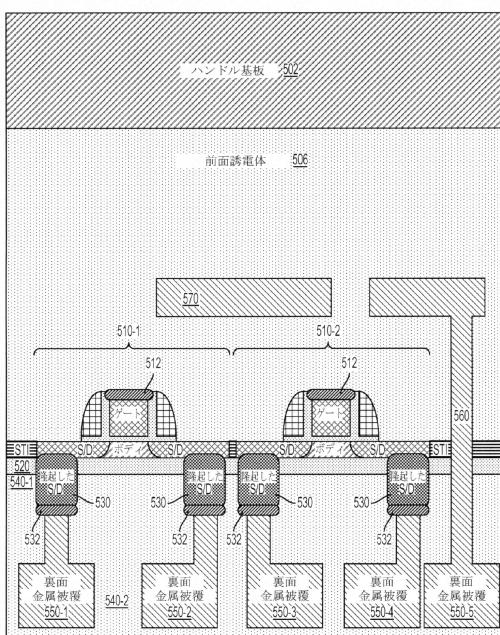

【図 5 A】本開示の一態様による、層転写後のプロセスが能動デバイスの裏面の隆起したソース/ドレイン領域を形成する集積回路構造を示す図である。

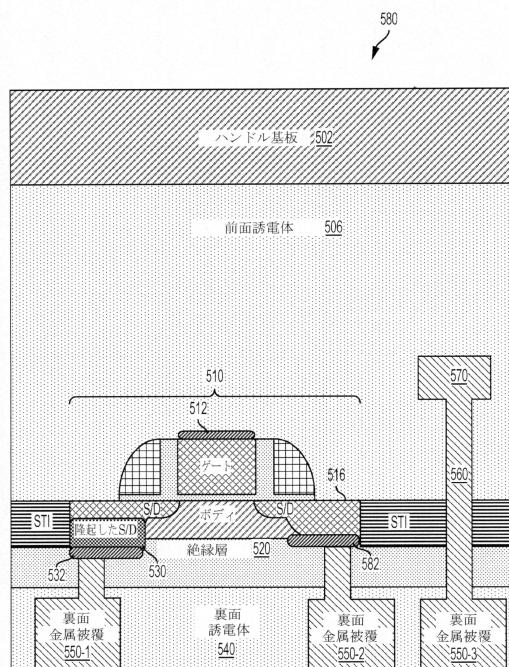

【図 5 B】本開示の一態様による、層転写後のプロセスが能動デバイスの裏面の隆起したソース/ドレイン領域を形成する集積回路構造を示す図である。

【図 6 A】本開示の一態様による、裏面の隆起したソース/ドレイン領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

【図 6 B】本開示の一態様による、裏面の隆起したソース/ドレイン領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

【図 6 C】本開示の一態様による、裏面の隆起したソース/ドレイン領域を含む集積回路構造を製作するためのプロセスを示す断面図である。 20

【図 6 D】本開示の一態様による、裏面の隆起したソース/ドレイン領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

【図 6 E】本開示の一態様による、裏面の隆起したソース/ドレイン領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

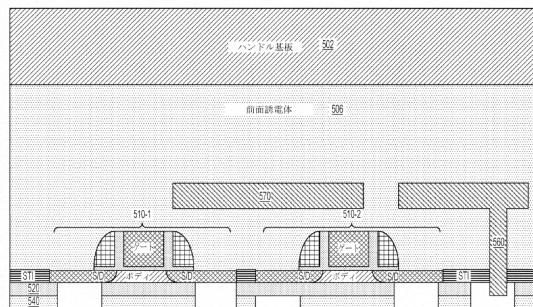

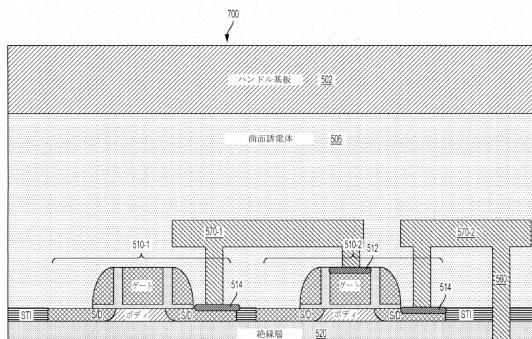

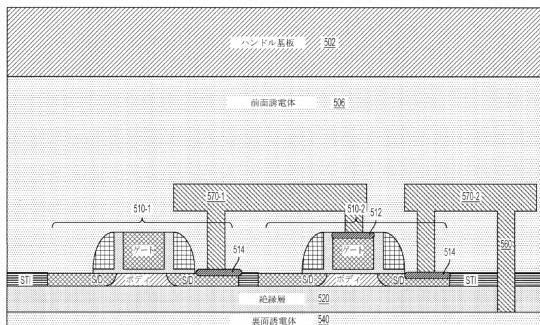

【図 7 A】本開示の一態様による、裏面の伸びたソース/ドレイン/ボディ領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

【図 7 B】本開示の一態様による、裏面の伸びたソース/ドレイン/ボディ領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

【図 7 C】本開示の一態様による、裏面の伸びたソース/ドレイン/ボディ領域を含む集積回路構造を製作するためのプロセスを示す断面図である。 30

【図 7 D】本開示の一態様による、裏面の伸びたソース/ドレイン/ボディ領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

【図 7 E】本開示の一態様による、裏面の伸びたソース/ドレイン/ボディ領域を含む集積回路構造を製作するためのプロセスを示す断面図である。

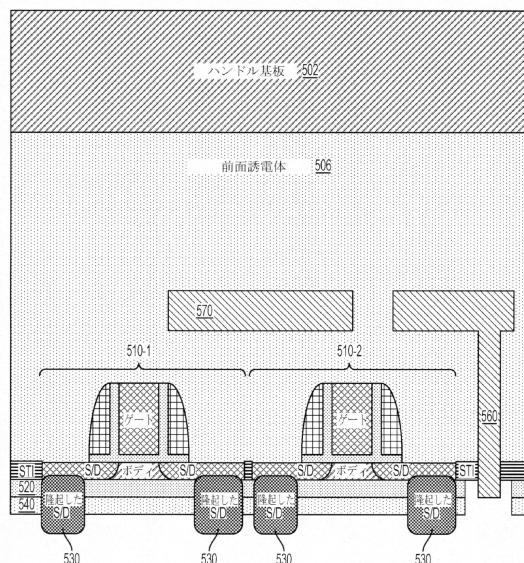

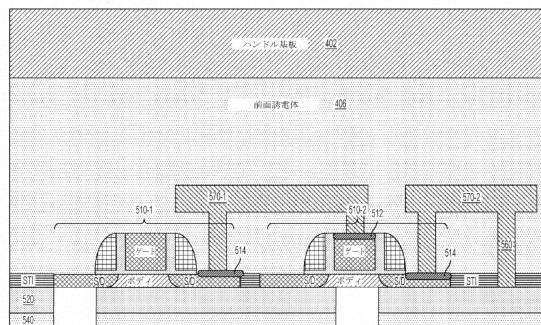

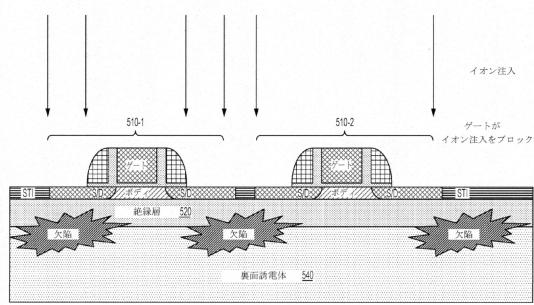

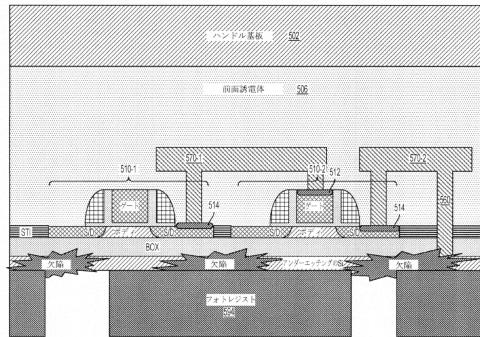

【図 8 A】本開示の一態様による、能動デバイスのソース/ドレイン/ボディ領域と能動デバイスの裏面の伸びたソース/ドレイン/ボディ領域との間の自己整合のためのプロセスを示す断面図である。

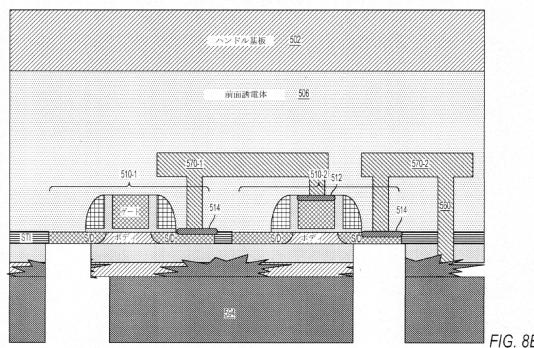

【図 8 B】本開示の一態様による、能動デバイスのソース/ドレイン/ボディ領域と能動デバイスの裏面の伸びたソース/ドレイン/ボディ領域との間の自己整合のためのプロセスを示す断面図である。 40

【図 8 C】本開示の一態様による、能動デバイスのソース/ドレイン/ボディ領域と能動デバイスの裏面の伸びたソース/ドレイン/ボディ領域との間の自己整合のためのプロセスを示す断面図である。

【図 8 D】本開示の一態様による、能動デバイスのソース/ドレイン/ボディ領域と能動デバイスの裏面の伸びたソース/ドレイン/ボディ領域との間の自己整合のためのプロセスを示す断面図である。

【図 8 E】本開示の一態様による、能動デバイスのソース/ドレイン/ボディ領域と能動デバイスの裏面の伸びたソース/ドレイン/ボディ領域との間の自己整合のためのプロセスを示す断面図である。 50

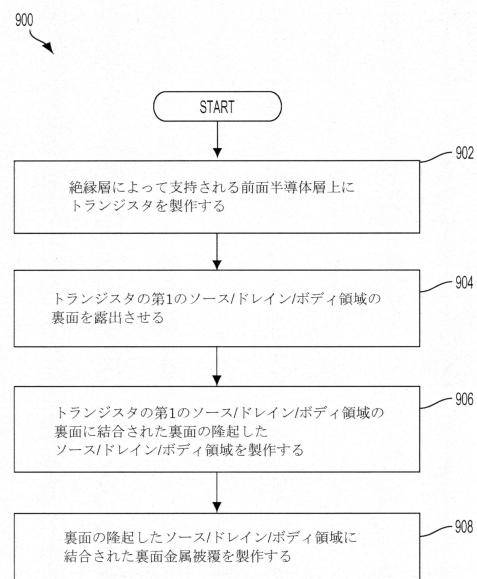

【図9】本開示の一態様による、裏面の伸びたソース/ドレイン/ボディ領域を有する能動デバイスを含む集積回路構造を構築する方法を示すプロセスフロー図である。

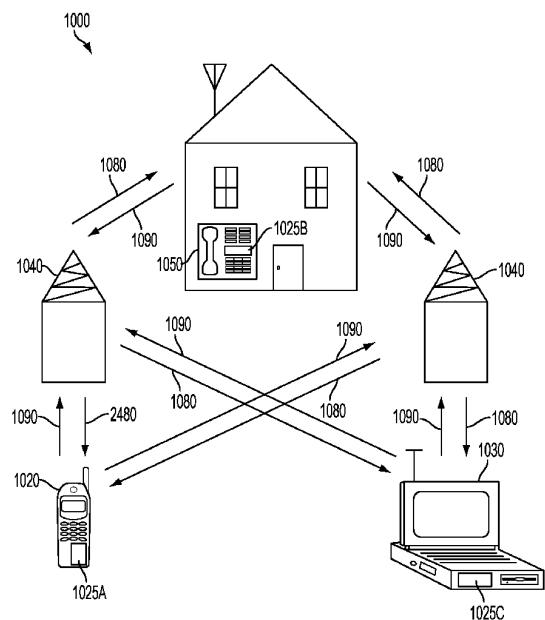

【図10】本開示の一構成が有利に利用される場合がある例示的なワイヤレス通信システムを示すブロック図である。

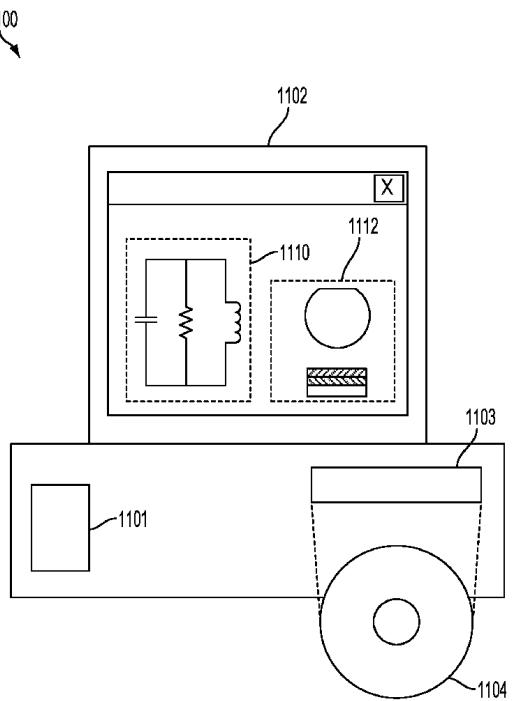

【図11】1つの構成による、半導体構成要素の回路設計、レイアウト設計、および論理設計のために使用される設計用ワークステーションを示すブロック図である。

【発明を実施するための形態】

【0012】

添付の図面に関して以下に記載される発明を実施するための形態は、様々な構成の説明として意図され、本明細書で説明される概念が実践され得る唯一の構成を表すことは意図されない。発明を実施するための形態は、様々な概念を完全に理解できるようにすることを目的とした具体的な詳細を含む。しかしながら、これらの概念がこれらの具体的な詳細なしに実践されてもよいことは、当業者には明らかであろう。場合によっては、そのような概念を曖昧にするのを回避するために、よく知られている構造および構成要素がブロック図の形態で示される。本明細書において説明されるときに、「および/または」という用語の使用は、「包含的論理和」を表すことが意図されており、「または」という用語の使用は、「排他的論理和」を表すことが意図されている。

10

【0013】

モバイル無線周波(RF)チップ構成(たとえば、モバイルRFトランシーバ)は、コストおよび電力消費量の問題に起因してディープサブミクロンプロセスノードに移行している。モバイルRFトランシーバの設計については、キャリアアグリゲーションなどの通信拡張機能をサポートするための追加の回路機能によってさらに複雑さが増している。モバイルRFトランシーバに関するさらなる設計課題には、不整合、ノイズ、および他の性能上の問題を含むアナログ/RF性能の問題が含まれる。このようなモバイルRFトランシーバの設計には、受動デバイスを使用して、たとえば、共振を抑制すること、および/またはフィルタ処理、バイパス、および結合を実行することが含まれる。

20

【0014】

現代の半導体チップ製品を首尾よく製作するには、採用される材料とプロセスとの間の相互作用が必要である。具体的には、配線工程(BEOL)プロセスにおける半導体製作のための導電材料めっきの形成は、プロセスフローにおいてますます困難になっている部分である。これは、小さなフィーチャサイズを維持するという観点において特に当てはまる。受動オンガラス(POG)技術でも、小さなフィーチャサイズを維持することに関する同じ問題があり、その技術では、モバイルRFトランシーバ設計をサポートするために、インダクタおよびキャパシタのような高性能構成要素が、同じく損失が非常に少ない場合がある絶縁性の高い基板上に構築される。

30

【0015】

これらのモバイルRFトランシーバの設計には、シリコンオンインシュレータ(SOI)技術の使用が含まれる。SOI技術は、寄生デバイスキャパシタンスを低減して性能を改善するために、従来のシリコン基板を層状シリコンオンインシュレータ基板と置き換える。シリコン接合は電気的絶縁体、典型的には埋込み酸化物(BOX)層の上にあるので、SOIベースのデバイスは、従来のシリコン製デバイスとは異なり、BOX層の厚さは低減され得る。しかしながら、低減された厚さのBOX層は、シリコン層およびBOX層を支持する基板上の能動デバイスに近接することによって生じる寄生キャパシタンスを十分に低減しない場合がある。加えて、SOI層上の能動デバイスは、相補型金属酸化物半導体(CMOS)トランジスタを含み得る。

40

【0016】

残念ながら、SOI技術を使用して成功しているトランジスタの製作は、隆起したソース/ドレイン領域の使用を伴う場合がある。従来、隆起したソース/ドレインは、隆起したソース/ドレイン領域と後続の金属被覆層との間の接触を可能にする。加えて、隆起したソース/ドレイン領域は、キャリアが進むためのチャネルを提供する。隆起したソース/ドレイン

50

領域を有する従来のトランジスタは、概して、隆起したソース/ドレイン領域の問題に遭遇する。隆起したソース/ドレイン領域の問題は、ゲートとソース/ドレイン領域との間のフリンジキャパシタンスおよびオーバーラップキャパシタンスの形態の不要な寄生キャパシタンスによって特徴づけられる。加えて、従来のCMOS技術は、能動デバイスの前面上のエピタキシャル成長に限定される。その結果、本開示の態様は、隆起したソース/ドレイン領域の問題を解消するために、裏面半導体の堆積/成長を可能にする層転写後のプロセスを含む。

#### 【 0 0 1 7 】

本開示の様々な態様は、裏面の伸びた(隆起した)ソース/ドレイン/ボディ領域を有するトランジスタを含む集積回路構造のための技法を提供する。集積回路構造の半導体製作のためのプロセスフローには、基板工程(FEOL)プロセス、中間工程(MOL)(中間工程(MEOL)とも呼ばれる)プロセス、および配線工程(BEOL)プロセスが含まれてもよい。基板工程プロセスは、トランジスタ、キャパシタ、ダイオードなどの能動デバイスを形成するプロセスステップのセットを含んでもよい。FEOLプロセスには、イオン注入、アニール、酸化、化学気相堆積(CVD)または原子層堆積(ALD)、エッチング、化学機械研磨(CMP)、エピタキシーが含まれる。中間工程プロセスには、トランジスタの接続がBEOL相互接続することを可能にするプロセスステップのセットが含まれてもよい。これらのステップには、シリサイド化および接点形成、ならびに応力導入が含まれる。配線工程プロセスは、個々のトランジスタを結んで回路を形成する相互接続を形成するプロセスステップのセットを含んでもよい。今回、銅およびアルミニウムが相互接続を実現しているが、技術のさらなる進展について、他の導電材料が使用されてもよい。

10

#### 【 0 0 1 8 】

「層」という用語は、膜を含み、別段述べられていない限り、垂直厚または水平厚を示すものと解釈されるべきではないことが理解されよう。本明細書において説明するよう、「基板」という用語は、ダイシングされたウエハの基板を指す場合があるか、または、ダイシングされていないウエハの基板を指す場合がある。同様に、チップおよびダイという用語は、入れ換えられると信じることが難しくない限り、互換的に使用することができる。

20

#### 【 0 0 1 9 】

本開示の態様は、クオリティ(Q)ファクタの高いRFアプリケーションに対する集積無線周波数(RF)回路構造内でアンテナスイッチトランジスタとして使用され得る裏面の隆起したソース/ドレイン/ボディ領域を有するトランジスタを含む集積回路構造を説明する。一構成では、層転写後のプロセスは、トランジスタの裏面の隆起したソース/ドレイン/ボディ領域を形成する。層転写後のプロセスは、トランジスタのソース/ドレイン領域の裏面上に裏面半導体層を形成し得る。裏面半導体層は、絶縁層の第1の表面から第2の表面まで延びてもよく、絶縁層の第1の表面はトランジスタを支持する。

30

#### 【 0 0 2 0 】

この構成では、層転写後のプロセスは、トランジスタのソース/ドレイン領域の裏面上に裏面半導体層を形成するための層堆積後のプロセスまたは層成長後のプロセスを含み得る。隆起したソース/ドレイン/ボディ領域は、エピタキシャルに成長した裏面半導体材料から構成される。代替的に、隆起したソース/ドレイン領域は、化学気相堆積(CVD)、原子層堆積(ALD)、または他の同様の基板工程製作プロセスを使用して形成され得る。この構成では、トランジスタの裏面の隆起したソース/ドレイン領域は、従来のCMOSプロセスを使用して製作された前面の隆起したソース/ドレイン領域に関連する寄生キャパシタンスを低減し得る。すなわち、ソース/ドレイン領域をトランジスタの裏面の中に延ばすことは、トランジスタのボディと従来の前面の隆起したソース/ドレイン領域との間ににおける寄生キャパシタンスの形成を防止するのを助ける。

40

#### 【 0 0 2 1 】

ワイヤレス通信産業を活発にする1つの目標は、増加した帯域幅を消費者に提供することである。現世代の通信においてキャリアアグリゲーションを使用することで、この目標

50

を達成するための1つの可能な解決策が提供される。キャリアアグリゲーションは、特定の地理的エリア内で2つの周波数帯域(たとえば、700MHzおよび2GHz)に対する認可を有する無線通信事業者が、単一の通信ストリームに対して両周波数を同時に使用することによって帯域幅を最大化することを可能にする。増加した量のデータがエンドユーザに供給されるが、キャリアアグリゲーションの実施は、データ送信のために使用される周波数による高調波周波数において生じるノイズによって複雑になる。たとえば、700MHzの送信は2.1GHzにおいて高調波を生じる場合があり、この高調波は、2GHzの周波数においてブロードキャストされるデータと干渉する。

#### 【0022】

ワイヤレス通信に対して、受動デバイスが、キャリアアグリゲーションシステム内で信号を処理するために使用される。キャリアアグリゲーションシステムでは、信号はハイバンド周波数とローバンド周波数の両方によって伝達される。チップセットでは、受動デバイス(たとえば、ダイプレクサ)は通常、アンテナとチューナー(または無線周波数(RF)スイッチ)との間に挿入され、高い性能を確保する。通常、ダイプレクサ構成はインダクタとキャパシタとを含む。ダイプレクサは、クオリティ(Q)ファクタの高いインダクタおよびキャパシタを使用することによって、高性能を達成できる。各構成要素の形状および方向を調整することによって実現することができる各構成要素間の電磁結合の低減によって、高性能ダイプレクサを実現することもできる。

#### 【0023】

図1Aは、本開示の一態様による、ダイプレクサ200を使用する無線周波数(RF)フロントエンド(RFFE)モジュール100の概略図である。RFフロントエンドモジュール100は、電力増幅器102と、デュプレクサ/フィルタ104と、無線周波数(RF)スイッチモジュール106とを含む。電力増幅器102は、信号を送信のための特定の電力レベルに増幅する。デュプレクサ/フィルタ104は、周波数、挿入損失、拒絶、または他の同様のパラメータを含む様々な異なるパラメータに応じて入出力信号をフィルタ処理する。さらに、RFスイッチモジュール106は、RFフロントエンドモジュール100の残りの部分に渡す入力信号の特定の部分を選択してもよい。

#### 【0024】

RFフロントエンドモジュール100はまた、チューナー回路112(たとえば、第1のチューナー回路112Aおよび第2のチューナー回路112B)と、ダイプレクサ200と、キャパシタ116と、インダクタ118と、接地端子115と、アンテナ114とを含む。チューナー回路112(たとえば、第1のチューナー回路112Aおよび第2のチューナー回路112B)は、チューナー、ポータブルデータ入力端末(PDET)、およびハウスキーピングアナログデジタル変換器(HKADC)などの構成要素を含む。チューナー回路112は、アンテナ114のインピーダンス同調(たとえば、電圧定在波比(VSWR)最適化)を実行してもよい。RFフロントエンドモジュール100は、ワイヤレストランシーバ(WTR)120に結合された受動コンバイナ108も含む。受動コンバイナ108は、第1のチューナー回路112Aおよび第2のチューナー回路112Bからの検出された電力を組み合わせる。ワイヤレストランシーバ120は、受動コンバイナ108からの情報を処理し、この情報をモデル130(たとえば、移動局モデル(MSM))に提供する。モデル130は、デジタル信号をアプリケーションプロセッサ(AP)140に与える。

#### 【0025】

図1Aに示すように、ダイプレクサ200は、チューナー回路112のチューナー構成要素とキャパシタ116、インダクタ118、およびアンテナ114との間に位置する。ダイプレクサ200は、アンテナ114とチューナー回路112との間に配置され、RFフロントエンドモジュール100から、ワイヤレストランシーバ120と、モデル130と、アプリケーションプロセッサ140とを含むチップセットへ高システム性能を提供することができる。ダイプレクサ200は、ハイバンド周波数とローバンド周波数の両方に対して周波数ドメイン多重化も実行する。ダイプレクサ200が入力信号に対してダイプレクサ200の周波数多重化機能を実行した後、ダイプレクサ200の出力が、キャパシタ116とインダクタ118とを含む任意のLC(インダクタ/キャパシタ)ネットワークに送られる。LCネットワークは、必要に応じて

10

20

30

40

50

、アンテナ114の追加のインピーダンス整合構成要素を構成してもよい。その場合、特定の周波数を有する信号がアンテナ114によって送信または受信される。単一のキャパシタおよびインダクタが示されているが、複数の構成要素も企図される。

#### 【0026】

図1Bは、本開示の一態様による、キャリアアグリゲーションを実現するためのチップセット160用の、第1のダイプレクサ200-1を含むワイヤレスローカルエリアネットワーク(WLAN)(たとえば、WiFi)モジュール170および第2のダイプレクサ200-2を含むRFフロントエンドモジュール150の概略図である。WiFiモジュール170は、アンテナ192をワイヤレスローカルエリアネットワークモジュール(たとえば、WLANモジュール172)に通信可能に結合する第1のダイプレクサ200-1を含む。RFフロントエンドモジュール150は、アンテナ194をデュプレクサ180を介してワイヤレストランシーバ(WTR)120に通信可能に結合する第2のダイプレクサ200-2を含む。ワイヤレストランシーバ120およびWiFiモジュール170のWLANモジュール172は、電力管理集積回路(PMIC)156を介して電源152によって電力を供給されるモデム(MSM、たとえばベースバンドモデム)130に結合される。チップセット160は、信号完全性を実現するためにキャパシタ162および164ならびにインダクタ166も含む。PMIC156、モデム130、ワイヤレストランシーバ120、およびWLANモジュール172の各々は、キャパシタ(たとえば、158、132、122、および174)を含み、クロック154に従って動作する。チップセット160における様々なインダクタ構成要素およびキャパシタ構成要素の形状および配置によって、各構成要素間の電磁結合が低減し得る。

10

#### 【0027】

図2Aは、本開示の一態様によるダイプレクサ200の図である。ダイプレクサ200は、ハイバンド(HB)入力ポート212と、ローバンド(LB)入力ポート214と、アンテナ216とを含む。ダイプレクサ200のハイバンドパスはハイバンドアンテナスイッチ210-1を含む。ダイプレクサ200のローバンドパスはローバンドアンテナスイッチ210-2を含む。RFフロントエンドモジュールを含むワイヤレスデバイスは、アンテナスイッチ210およびダイプレクサ200を使用してワイヤレスデバイスのRF入力およびRF出力用の広範囲のバンドを使用可能にし得る。さらに、アンテナ216は多入力多出力(MIMO)アンテナであってもよい。多入力多出力アンテナは、キャリアアグリゲーションなどの機能をサポートするためにワイヤレスデバイスのRFフロントエンドに広く使用される。

20

#### 【0028】

図2Bは、本開示の一態様によるRFフロントエンドモジュール250の図である。RFフロントエンドモジュール250は、図2Aに示されている広範囲の帯域を使用可能にするためにアンテナスイッチ(ASW)210とダイプレクサ200(またはトリプレクサ)とを含む。さらに、RFフロントエンドモジュール250は、基板202によって支持されるフィルタ230と、RFスイッチ220と、電力増幅器218とを含む。フィルタ230は、RFフロントエンドモジュール250における高次高調波を防止するためにダイプレクサ、トリプレクサ、ローパスフィルタ、バランフィルタ、および/またはノッチフィルタを形成するように基板202に沿って配置されたインダクタ(L)とキャパシタ(C)とを有する様々なLCフィルタを含んでもよい。ダイプレクサ200は、システムボード201(たとえば、プリント回路板(PCB)またはパッケージ基板)上の表面実装型デバイス(SMD)として実装されてもよい。代替的に、ダイプレクサ200は、基板202上に実装されてもよい。

30

#### 【0029】

この構成では、RFフロントエンドモジュール250は、シリコンオンインシュレータ(SOI)技術を使用して実装され、SOI技術は、RFフロントエンドモジュール250内の高次高調波の低減を助ける。SOI技術は、寄生デバイスキャパシタンスを低減して性能を改善するために、従来のシリコン基板を層状シリコンオンインシュレータ基板に置き換える。シリコン接合は電気的絶縁体、典型的には埋込み酸化物(BOX)層の上にあるので、SOIベースのデバイスは、従来のシリコン製デバイスとは異なる。しかしながら、低減された厚さのBOX層は、(シリコン層上の)能動デバイスとBOX層を支持する基板との間が近接することに

40

50

よって生じる寄生キャパシタンスを十分に低減しない場合がある。その結果、本開示の態様は、図3A～図3Eに示すように、能動デバイスを基板からさらに分離するための層転写プロセスを含む。

#### 【0030】

図3A～図3Eは、本開示の態様による、層転写プロセスの間の集積無線周波数(RF)回路構造300の断面図を示す。図3Aに示すように、RFシリコンオンインシュレータ(SOI)デバイスは、犠牲基板301(たとえば、バルクウエハ)によって支持される埋込み酸化物(BOX)層320上に能動デバイス310を含む。RF SOIデバイスはまた、第1の誘電体層306内部で能動デバイス310に結合される相互接続350を含む。図3Bに示すように、ハンドル基板302が、RF SOIデバイスの第1の誘電体層306に接合される。加えて、犠牲基板301が除去される。層転写プロセスを使用して犠牲基板301を除去することで、誘電体の厚さが増加することによって、高性能で低寄生のRFデバイスが可能になる。すなわち、RF SOIデバイスの寄生キャパシタンスは、能動デバイス310とハンドル基板302との間の距離を決定する誘電体厚さに比例する。

10

#### 【0031】

図3Cに示すように、RF SOIデバイスは、ハンドル基板302が固定されて犠牲基板301が除去された時点で反転される。図3Dに示すように、層転写後の金属被覆プロセスは、たとえば、通常の相補型金属酸化物半導体(CMOS)プロセスを使用して実行される。図3Eに示すように、集積RF回路構造300は、パッシベーション層を堆積させることと、ボンドパッドを開くことと、再配線層(redistribution layer)を堆積させることと、集積RF回路構造300をシステムボード(たとえば、プリント回路板(PCB))に接合することを可能にするために導電バンプ/ピラーを形成することによって達成される。

20

#### 【0032】

再び図3Aを参照すると、RF SOIデバイスは、犠牲基板301とBOX層320との間にトラップリッチ層を含んでもよい。加えて、犠牲基板301はハンドル基板と置き換えられてもよく、BOX層320の厚さは高調波を改善するために増加されてもよい。RF SOIデバイスのこの配置は、純シリコンまたはSOI実装に対して改善された高調波をもたらし得るが、RF SOIデバイスは、特にシリコンハンドル基板が使用されるときに、ハンドル基板からの非線型応答によって制限される。すなわち、図3Aでは、図3B～図3Eに示す構成に対して、増加された厚さのBOX層320は、能動デバイス310と犠牲基板301との間に十分な距離をもたらさない。その上、RF SOIデバイス内の能動デバイス310のボディは結ばれ(tied)ない。

30

#### 【0033】

図4は、本開示の態様による、層転写プロセスを使用して製作された集積RF回路構造400の断面図である。代表的に、集積RF回路構造400は、絶縁層420上に形成されたゲート、ボディ、およびソース/ドレイン領域を有する能動デバイス410を含む。シリコンオンインシュレータ(SOI)実装形態では、絶縁層420は埋込み酸化物(BOX)層であり、ボディおよびソース/ドレイン領域は、BOX層によって支持されるシャロートレンチ分離(STI:shallow trench isolation)領域を含むSOI層から形成される。

40

#### 【0034】

集積RF回路構造400はまた、能動デバイス410のソース/ドレイン領域に結合された中間工程(MEOL)/配線工程(BEOL)相互接続を含む。本明細書で説明するように、MEOL/BEOL層は、前面層と呼ばれる。対照的に、絶縁層420を支持する層は、本明細書では裏面層と呼ばれることがある。この用語に従って、前面相互接続450は、前面接点412を介して能動デバイス410のソース/ドレイン領域に結合され、前面誘電体層406内に配置される。加えて、ハンドル基板402は、前面誘電体層406に直接結合される。この構成では、裏面誘電体440は絶縁層420に隣接し、場合によっては絶縁層420を支持する。加えて、裏面金属被覆430は、前面相互接続450に結合される。

#### 【0035】

図4に示すように、層転写プロセスは、集積RF回路構造400の高調波を改善するために

50

、能動デバイス410とハンドル基板402との間に増加した分離をもたらす。層転写プロセスは、高性能、低寄生のRFのデバイスを可能にするが、集積RF回路構造400は、フローティングボディ効果の欠点がある。したがって、集積RF回路構造400の性能は、能動デバイス410のボディ領域を結ぶために、転写後の金属被覆を使用して能動デバイス410の裏へのアクセスを設けることによってさらに改善され得る。

#### 【0036】

本開示の様々な態様は、集積無線周波数(RF)回路構造の能動デバイスの裏面上の層転写後の堆積/成長プロセスのための技法を提供する。対照的に、基板工程(FEOL)プロセスの間に形成された能動デバイスへのアクセスは、従来では、能動デバイスのゲートおよびソース/ドレイン領域と配線工程(BEOL)相互接続層(たとえば、M1、M2など)との間に接点を設ける中間工程(MEOL)処理の間に設けられる。本開示の態様は、クオリティ(Q)ファクタの高いRFアプリケーションに対する集積無線周波数(RF)回路構造内でアンテナスイッチトランジスタとして使用され得るトランジスタの裏面の伸びた(隆起した)ソース/ドレイン/ボディ領域を形成するための層転写後の成長/堆積プロセスを伴う。他のアプリケーションは、低電力増幅器モジュール、低ノイズ増幅器、およびアンテナダイバーシティスイッチ内の能動デバイスを含む。

10

#### 【0037】

図5Aは、本開示の態様による、層転写後のプロセスが能動デバイス(たとえば、トランジスタ)のソース/ドレイン(S/D)領域の裏面上で実行される、集積回路構造500の断面図である。代表的に、集積回路構造500は、絶縁層520上に形成されたゲート、ボディ、およびソース/ドレイン(S/D)領域を有する能動デバイス510を含む。絶縁層520は、シリコンオンインシュレータ(SOI)実装に対する埋込み酸化物(BOX)層であってもよく、ボディおよびソース/ドレイン領域はSOI層から形成される。この構成では、シャロートレンチ分離(STI)領域はまた、BOX層によって支持される。

20

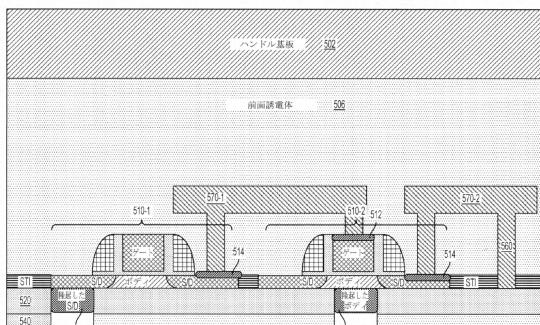

#### 【0038】

集積RF回路構造500は、前面誘電体層506内に配置された前面金属被覆570(たとえば、第1のBEOL相互接続(M1))を含む。前面金属被覆は、ビア560を通して裏面金属被覆550の第3の部分550-3に結合され、裏面金属被覆550は裏面誘電体層540内に配置される。加えて、能動デバイス510のゲートは、前面シリサイド層から構成され得るゲート接点512を含む。加えて、ハンドル基板502は、前面誘電体層506に結合される。裏面誘電体層540は、絶縁層520に隣接し、場合によっては絶縁層520を支持する。この構成では、層転写後の金属被覆プロセスは、裏面金属被覆550を形成する。

30

#### 【0039】

本開示の態様では、層転写後のプロセスは、能動デバイス510のソース/ドレイン領域の裏面上に裏面半導体層を設けるために使用される。本開示の態様では、裏面半導体層は、アモルファス半導体層として堆積され得る。代替的に、裏面半導体層は、層転写後の成長プロセスの一部としてエピタキシャルに成長され得る。形成されると、裏面半導体層は、随意に、隆起したソース/ドレイン(S/D)領域530を形成するために堆積後のアニールプロセス(たとえば、低温度または短い局所的レーザーアニール)にかけられる場合がある。この構成では、裏面の隆起したソース/ドレイン領域530は、能動デバイス510のソース/ドレイン領域の裏面から絶縁層520の中に伸びる。形成されると、裏面接点532(たとえば、裏面シリサイド層)は、ソース/ドレイン領域の前面から遠位にある裏面の隆起したソース/ドレイン領域530上に堆積され得る。次いで、層転写後の金属被覆プロセスが、裏面金属被覆550の第1の部分550-1および第2の部分550-2を能動デバイス510の裏面隆起したソース/ドレイン領域530の裏面接点532に結合するために実行される。図5Aに示すように、前面金属被覆570は、裏面金属被覆550から遠位に配置される。

40

#### 【0040】

図5Bは、本開示の態様による、層転写後のプロセスもまた、能動デバイス510(たとえば、トランジスタ)のソース/ドレイン(S/D)領域516の裏面上で実行される、集積回路構造580の断面図である。理解されるように、集積回路構造580の構成は、図5Aの集積回路

50

構造500の構成と同様である。しかしながら、図5Bに示す構成では、能動デバイス510は、裏面の隆起したソース/ドレイン領域530のうちの1つだけを含む。代わりに、裏面接点582は、直接、能動デバイス510のソース/ドレイン領域516の裏面上にある。加えて、裏面金属被覆550の第2の部分550-2は、能動デバイス510のソース/ドレイン領域516の裏面接点582に結合される。

#### 【0041】

再び図5Aを参照すると、裏面の隆起したソース/ドレイン領域530は、絶縁層520内に設けられ、裏面金属被覆550との接触を可能にするように配置される。能動デバイス510のソース/ドレイン領域を延ばすことは、能動デバイス510のボディと従来の前面の隆起したソース/ドレイン領域との間ににおける寄生キャパシタンスの形成を防止するのを助ける。この構成では、層転写後のプロセスは、裏面の隆起したソース/ドレイン領域530を形成するための層堆積後のプロセスまたは層成長後のプロセスを含み得る。この構成では、裏面の隆起したソース/ドレイン領域530は、従来のCMOSプロセスを使用して製作された隆起したソース/ドレイン領域に関連する寄生キャパシタンスを低減し得る。

10

#### 【0042】

本開示の態様によれば、ハンドル基板502は、シリコンなどの半導体材料から構成され得る。この構成では、ハンドル基板502は、少なくとも1つの他の能動デバイスを含み得る。代替的に、ハンドル基板502は、寄生キャパシタンスを低減することによって高調波をさらに改善するために受動基板であり得る。この構成では、ハンドル基板502は、少なくとも1つの他の受動デバイスを含み得る。本明細書における説明では、「受動基板」という用語は、ダイシングされたウエハまたはパネルの基板を指す場合があるか、または、ダイシングされていないウエハ/パネルの基板を指す場合がある。一構成では、受動基板は、ガラス、空気、石英、サファイア、高抵抗シリコン、または他の同様の受動材料で構成される。受動基板はまた、コアレス基板であってもよい。

20

#### 【0043】

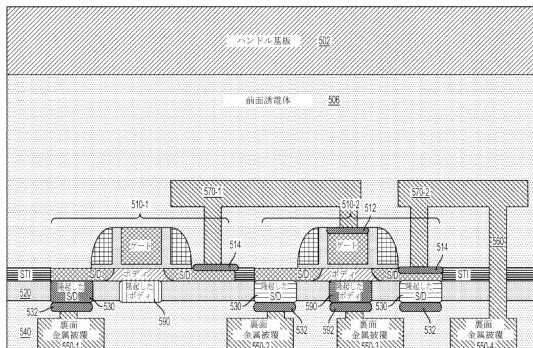

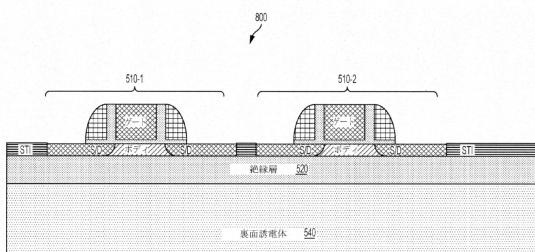

図6A～図6Eは、本開示の態様による、裏面の延びたソース/ドレイン領域を含む集積回路構造を製作するためのプロセスを示す断面図である。図6Aに示すように、集積回路構造600は、図5Aに示す集積回路構造500の構成と同様の構成において示される。しかしながら、図6Aに示す構成では、層転写プロセスは、能動デバイス510(510-1および510-2)の形成に続いて、ハンドル基板502を前面誘電体層506に接合するために実行される。図6Bに示すように、層転写後のプロセスは、裏面誘電体層540の堆積で始まる。単一の層が示されているが、複数の誘電体層が堆積されてもよいことを認識されたい。

30

#### 【0044】

図6Cに示すように、層転写後のプロセスは、能動デバイス510のソース/ドレイン領域の裏面を露出させるために裏面誘電体層540および絶縁層520をパターニングおよびエッチングすることで継続する。図6Dにおいて、層転写後の堆積/成長プロセスが、裏面の隆起したソース/ドレイン領域530を製作するために実行される。図6Eにおいて、層転写後の金属被覆プロセスが、裏面金属被覆550を裏面接点532を介して裏面の隆起したソース/ドレイン領域530に結合するために実行される。加えて、裏面金属被覆550の第5の部分550-5が、ビア560を通して前面金属被覆570に結合される。この構成では、裏面金属被覆550の第3の部分550-3が、裏面の隆起したソース/ドレイン領域530のうちの1つの裏面接点532に結合され、裏面金属被覆550の第4の部分550-4が、第2の能動デバイス510-2の裏面の隆起したソース/ドレイン領域530のうちの1つの裏面接点532に結合される。

40

#### 【0045】

異なる材料が、能動デバイスに応力を加えるために成長プロセスの中で使用され得る。たとえば、一構成では、PFETデバイスは、ゲルマニウム成長によって40%まで応力を加えられ得る。NMOSデバイスは、たとえば、炭素の割合がわずか3%から4%である炭素ドープシリコンを使用して応力を加えられ得る。炭素のこの割合は、シリコン内の転位を防止する。隆起したボディ領域もまたストレッサを含み得ることを認識されたい。

#### 【0046】

50

図7A～図7Eは、本開示の態様による、裏面の延びたソース/ドレイン/ボディ領域を含む集積回路構造を製作するためのプロセスを示す断面図である。図7Aに示すように、集積回路構造700は、図5Aに示す集積回路構造500の構成と同様の構成において示される。しかしながら、図7Aに示す構成では、層転写プロセスは、能動デバイス510(510-1および510-2)の形成に続いて、ハンドル基板502を前面誘電体層506に接合するために実行される。加えて、前面金属被覆570の第1の部分570-1は、第1の能動デバイス510-1のソース/ドレイン領域の前面接点514を第2の能動デバイス510-2のゲート接点512に結合する。同じく、前面金属被覆570の第2の部分570-2は、第2の能動デバイス510-2のソース/ドレイン領域の前面接点514をビア560に結合する。

【0047】

10

図7Bに示すように、層転写後のプロセスはまた、裏面誘電体層540の堆積で始まる。図7Cに示すように、層転写後のプロセスはまた、第1の能動デバイス510-1のソース/ドレイン領域の裏面を露出させるために裏面誘電体層540および絶縁層520をパターニングおよびエッチングすることで継続する。本開示のこの態様では、層転写後のプロセスは、第2の能動デバイス510-2のボディを露出させる。図7Dにおいて、層転写後の堆積/成長プロセスが、裏面の隆起したソース/ドレイン領域530および裏面の隆起したボディ領域590を製作するために実行される。

【0048】

20

図7Eにおいて、層転写後の金属被覆プロセスが、裏面金属被覆550を裏面接点532を介して裏面の隆起したソース/ドレイン領域530に結合するために実行される。加えて、裏面金属被覆550の第4の部分550-4は、ビア560を通して前面金属被覆570の第2の部分に結合される。この構成では、裏面金属被覆550の第3の部分550-3は、裏面の隆起したボディ領域590の裏面接点592に結合される。本開示のこの態様では、裏面の隆起したボディ領域590は、裏面の隆起したソース/ドレイン領域530のドーパントとは異なるドーパントでドープされる。加えて、第1の能動デバイス510-1の裏面の隆起したボディ領域590は、第2の能動デバイス510-2の裏面の隆起したボディ領域590のドーパントとは異なるドーパントでドープされる。

【0049】

30

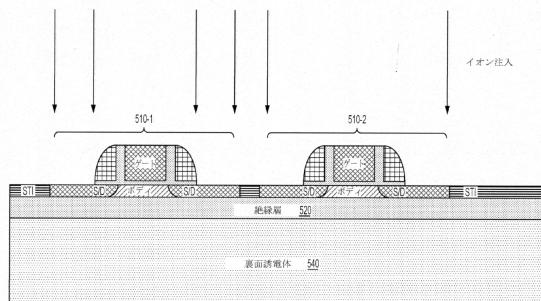

図8A～図8Eは、本開示の態様による、能動デバイスのソース/ドレイン/ボディ領域と能動デバイスの裏面の延びたソース/ドレイン/ボディ領域との間の自己整合のためのプロセスを示す断面図である。図8Aに示すように、集積回路構造800は、図7Aに示す集積回路構造700の構成と同様の構成において示される。しかしながら、図8Aに示す構成では、能動デバイス510(510-1および510-2)の形成に続いて、ハンドル基板502を前面誘電体層506に接合するための層転写プロセスは示されない。加えて、図8Dに示す集積回路構造の構成はまた、第1の能動デバイス510-1のソース/ドレイン領域の前面接点514を第2の能動デバイス510-2のゲート接点512に結合する、前面金属被覆570の第1の部分570-1を含む。同じく、前面金属被覆570の第2の部分570-2は、第2の能動デバイス510-2のソース/ドレイン領域の前面接点514をビア560に結合する。

【0050】

40

図8Bに示すように、イオン注入プロセスが、裏面誘電体層540および絶縁層520にイオンを注入することによって、不純物を裏面誘電体層540に注入するために実行される。注入は、集積回路構造800の前面から実行される。特定のドーパント、たとえば高用量ホウ素が、埋込み酸化物層に損傷を与える(欠陥を生じさせる)ために使用され得る。図8Cに示すように、イオン注入プロセスは、能動デバイス510のゲートによってロックされる。その結果、注入された欠陥は、概して、能動デバイス510のソース/ドレイン領域に近接した裏面誘電体層540および絶縁層内部のエリアに限定される。

【0051】

図8Dに示すように、層転写後のマスクプロセスは、フォトレジスト594を堆積させることおよび、たとえばアンダーエッチングの半導体(たとえば、シリコン(Si))層内部の注入された欠陥を露出させることによって実行される。図8Eに示すように、プロセスは、第1

50

の能動デバイス510-1のソース/ドレイン領域の裏面および第2の能動デバイス510-2のソース/ドレイン領域の裏面を露出させるために、裏面誘電体層540および絶縁層520をエッチングすることで継続する。本開示のこの態様では、注入された欠陥は、能動デバイス510のソース/ドレイン/ボディ領域と裏面の伸びたソース/ドレイン/ボディ領域との間の自己整合を可能にする。すなわち、裏面エッチングは、ゲートに到達しない。代替的に、注入された欠陥はエッチストップ層をもたらし、裏面の隆起したソース/ドレイン/ボディ領域を支持するためにエッチ速度を引き下げる場合がある。

#### 【 0 0 5 2 】

図9は、本開示の一態様による、裏面の伸びたソース/ドレイン/ボディ領域を有する能動デバイスを含む集積回路構造を構築する方法900を示すプロセスフロー図である。ブロック902において、トランジスタが、絶縁層によって支持される前面半導体層を使用して製作される。たとえば、図6Aに示すように、能動デバイス310は、絶縁層(たとえば、埋込み酸化物(BOX)層)によって支持される前面半導体層(たとえば、シリコンオンインシユレータ(SOI)層)を使用して製作される。図6A～図6Eに示す構成では、前面金属被覆は、能動デバイス上の前面誘電体層内に製作される。たとえば、図6Aに示すように、前面金属被覆570は、シャロートレンチ分離(STI)領域および絶縁層520を通して伸びる前面ビア560に結合される。トランジスタを製作するためのプロセスのこの部分は、層転写プロセスの前に実行される。

#### 【 0 0 5 3 】

たとえば、図6Aに示すように、層転写プロセスが実行され、ハンドル基板502が前面誘電体層506に接合される。層転写プロセスはまた、犠牲基板の除去を含む。図3Bに示すように、層転写プロセスは、犠牲基板301の除去を含む。本開示のこの態様では、隆起した裏面のソース/ドレイン/ボディ領域の製作が、層転写後のプロセスの一部として実行される。

#### 【 0 0 5 4 】

再び図9を参照すると、ブロック904において、トランジスタの第1のソース/ドレイン/ボディ領域の裏面が露出される。たとえば、図6Bに示すように、層転写後の隆起したソース/ドレイン/ボディ形成プロセスが、絶縁層520上の裏面誘電体層540の堆積で開始し得る。図6Cに示すように、能動デバイス510のソース/ドレイン領域の裏面が露出される。ブロック906において、隆起したソース/ドレイン/ボディ領域が製作される。たとえば、図6Dに示すように、隆起したソース/ドレイン(S/D)領域が、能動デバイス510のソース/ドレイン領域の裏面に結合される。隆起したソース/ドレイン領域は、ソース/ドレイン領域の裏面から絶縁層520を支持する裏面誘電体層540の方に伸びてもよい。代替的に、第2のソース/ドレイン/ボディ領域の裏面は、別の隆起したソース/ドレイン/ボディ領域の形成を可能にするために露出され得る。

#### 【 0 0 5 5 】

本開示の態様によれば、隆起したソース/ドレイン/ボディ領域は、アモルファス堆積プロセスの一部としてエピタキシャルに成長または製作され得る。たとえば、図6Dに示すように、エピタキシャル成長プロセスは、能動デバイス510の隆起したソース/ドレイン領域の露出された裏面上で裏面半導体層を選択的に成長させることを含み得る。このエピタキシャル成長はまた、隆起したソース/ドレイン領域を形成するために、裏面半導体層をアニールプロセスにかけることを含む。隆起したソース/ドレイン領域が形成されると、能動デバイス510の裏面誘電体層540および/または隆起したソース/ドレイン領域の表面のエッチングが実行される。集積回路構造500の前面から離れて伸びる裏面の隆起したソース/ドレイン領域を設けることによって、トランジスタゲートと従来の隆起したソース/ドレイン領域との間の寄生キャパシタンスが回避される。

#### 【 0 0 5 6 】

本開示の態様によれば、層転写後の成長/堆積プロセスが、裏面の隆起したソース/ドレイン/ボディ領域を形成するために説明される。層転写後の成長プロセスは、ブリクリーン部分、成長部分、および堆積後のアニールを伴う場合がある。堆積後のアニールは、低温

10

20

30

40

50

度アニール(たとえば、350 °未満)または短い局所的レーザーアニールであり得る。加えて、裏面の隆起したソース/ドレイン/ボディ領域は、単一の結晶構造であってもよく、またはなくてもよい。たとえば、裏面の隆起したソース/ドレイン/ボディ領域は、単一の結晶構造を形成するための固相エピタキシーアニールが後続する、完全アモルファス堆積によって形成され得る。代替的に、単一の結晶材料が望ましくない場合、ポリシリコン、シリコン合金、または他の同様の半導体化合物が、裏面半導体層を設けるために堆積され得る。

#### 【 0 0 5 7 】

裏面半導体層を形成するためにエピタキシャル成長プロセスが使用されるとき、低温度エピタキシャル成長が、トリシランを使用して実行され得る。トリシランは、H(水素)堆積を強化するための特定の成長メカニズムによって、350 °未満の低温度において裏面半導体層(たとえば、シリコン)の成長を可能にし得る。対照的に、500 °より低い温度で成長する従来の半導体層は、使用されるキャリアガス、圧力、および先駆フロー(precursor flow)にかかわらず欠陥がある。加えて、エピタキシャルに成長した裏面半導体層の厚さは、層が成長するウエハの表面より高くてもよく、または低くてもよい。

10

#### 【 0 0 5 8 】

図9のブロック908では、裏面金属被覆が、隆起したソース/ドレイン領域に結合されるように製作される。図6Eに示すように、裏面接点532が、裏面の隆起したソース/ドレイン領域530上に堆積される。加えて、第2の裏面誘電体層540-2が、裏面接点532および第1の裏面誘電体層540-1上に堆積される。堆積されると、第2の裏面誘電体層540-2は、裏面接点532に従ってパターンングされる。第2の裏面誘電体層540-2は、次に、裏面接点532の一部を露出させるためにエッチング(たとえば、ドライプラズマエッチングおよびクリーンプロセス)される。次いで、裏面金属被覆550が、能動デバイス510のソース/ドレイン領域に接触するために裏面接点532の露出部分の上に堆積される。

20

#### 【 0 0 5 9 】

本開示のさらなる態様によれば、絶縁層によって支持される前面半導体層上にトランジスタを含む集積回路構造が説明される。トランジスタは、第1のソース/ドレイン/ボディ領域を含む。集積回路構造はまた、トランジスタの第1のソース/ドレイン/ボディ領域の裏面を絶縁層から絶縁層を支持する裏面誘電体層の方に延ばすための手段を含み得る。集積回路構造は、延ばす手段を介して第1のソース/ドレイン/ボディ領域の裏面に結合された裏面金属被覆をさらに含み得る。延ばす手段は、図5Aおよび図5Bに示す隆起したソース/ドレイン領域であり得る。延ばす手段はまた、図7Dおよび図7Eに示す隆起したボディ領域であり得る。別の態様では、前述の手段は、前述の手段によって列挙された機能を実行するように構成される任意のモジュールまたは任意の装置であってもよい。

30

#### 【 0 0 6 0 】

残念ながら、シリコンオンインシュレータ(SOI)技術を使用して成功しているトランジスタの製作は、隆起したソース/ドレイン領域の使用を伴う場合がある。従来、隆起したソース/ドレインは、隆起したソース/ドレイン領域と後続の金属被覆層との間の接触を可能にする。加えて、隆起したソース/ドレイン領域は、キャリアが進むためのチャネルを提供する。残念ながら、隆起したソース/ドレイン領域を有する従来のトランジスタは、概して、隆起したソース/ドレイン領域の問題に遭遇する。加えて、従来のCMOS技術は、能動デバイスの前面のエピタキシャル成長に限定される。その結果、本開示の態様は、隆起したソース/ドレイン領域の問題を解消するために、裏面半導体の堆積/成長を可能にする層転写後のプロセスを含む。

40

#### 【 0 0 6 1 】

本開示の態様は、クオリティ(Q)ファクタの高いRFアプリケーションに対する集積無線周波数(RF)回路構造内でアンテナスイッチトランジスタとして使用され得る裏面の隆起したソース/ドレイン/ボディ領域を有するトランジスタを含む集積回路構造を説明する。一構成では、層転写後の金属被覆は、トランジスタの裏面の隆起したソース/ドレイン/ボディ領域を形成するために使用される。層転写後のプロセスは、トランジスタのソース/ドレ

50

イン領域の裏面上に裏面半導体層を形成し得る。裏面半導体層は、絶縁層の第1の表面から第2の表面まで延びてもよく、絶縁層の第1の表面はトランジスタを支持する。

#### 【 0 0 6 2 】

この構成では、層転写後のプロセスは、トランジスタのソース/ドレイン領域の裏面上に裏面半導体層を形成するための層堆積後のプロセスまたは層成長後のプロセスを含み得る。後続のアニールプロセスが、トランジスタの裏面の隆起したソース/ドレイン領域を形成するために半導体層に適用される。この構成では、トランジスタの裏面の隆起したソース/ドレイン領域は、従来のCMOSプロセスを使用して製作された前面の隆起したソース/ドレイン領域に関連する寄生キャパシタンスを低減し得る。すなわち、ソース/ドレイン領域をトランジスタの裏面の中に延ばすことは、トランジスタのボディと従来の前面の隆起したソース/ドレイン領域との間における寄生キャパシタンスの形成を防止するのを助ける。

10

#### 【 0 0 6 3 】

図10は、本開示の一態様が有利に利用される場合がある、例示的なワイヤレス通信システム1000を示すブロック図である。説明のために、図10は、3つのリモートユニット1020、1030、および1050、ならびに2つの基地局1040を示す。ワイヤレス通信システムがこれよりも多くのリモートユニットおよび基地局を有してもよいことが認識されよう。遠隔ユニット1020、1030および1050は、開示された裏面半導体成長を含むICデバイス1025A、1025C、および1025Bを含む。他のデバイスがまた、基地局、スイッチングデバイス、およびネットワーク機器などの、開示された裏面半導体成長を含んでもよいことが認識されよう。図10は、基地局1040からリモートユニット1020、1030、および1050への順方向リンク信号1080、ならびに、リモートユニット1020、1030、および1050から基地局1040への逆方向リンク信号1090を示す。

20

#### 【 0 0 6 4 】

図10では、リモートユニット1020はモバイル電話として示され、リモートユニット1030はポータブルコンピュータとして示され、リモートユニット1050はワイヤレスローカルループシステム内の固定ロケーションリモートユニットとして示される。たとえば、リモートユニットは、モバイル電話、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末(PDA)などのポータブルデータユニット、GPS対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、メーター読み取り機器などの固定ロケーションデータユニット、またはデータもしくはコンピュータ命令を記憶するかもしくは取り出す他の通信デバイス、あるいはそれらの組合せであってもよい。図10は本開示の態様によるリモートユニットを示すが、本開示はこれらの例示的に示されるユニットに限定されない。本開示の態様は、開示されたRFデバイスを含む、多くのデバイスにおいて適切に採用され得る。

30

#### 【 0 0 6 5 】

図11は、上で開示されたRFデバイスのような、半導体構成要素の回路設計、レイアウト設計、および論理設計のために使用される、設計用ワークステーションを示すブロック図である。設計用ワークステーション1100は、オペレーティングシステムソフトウェアと、サポートファイルと、CadenceまたはOrCADなどの設計ソフトウェアが入っているハードディスク1101を含む。設計用ワークステーション1100はまた、回路1110、またはRFデバイスなどの半導体構成要素1112の設計を容易にするためにディスプレイ1102を含む。回路設計1110または半導体構成要素1112を有形に記憶するために記憶媒体1104が設けられる。回路設計1110または半導体構成要素1112は、GDSIIやGERBERなどのファイルフォーマットで記憶媒体1104上に格納されてもよい。記憶媒体1104は、CD-ROM、DVD、ハードディスク、フラッシュメモリ、または他の適切なデバイスであってもよい。さらに、設計用ワークステーション1100は、記憶媒体1104から入力を受け取るか、または記憶媒体1104に出力を書き込むためのドライブ装置1103を含む。

40

#### 【 0 0 6 6 】

記憶媒体1104上に記録されたデータは、論理回路構成、フォトリソグラフィマスクのためのパターンデータ、または電子ビームリソグラフィなどのシリアル書き込みツールのた

50

めのマスクパターンデータを指定してもよい。データはさらに、論理シミュレーションに関連したタイミング図やネット回路などの論理検証データを含んでもよい。記憶媒体1104上にデータを用意すると、半導体ウエハを設計するためのプロセスの数が減少することによって、回路設計1110または半導体構成要素1112の設計が容易になる。

#### 【0067】

ファームウェアおよび/またはソフトウェアの実装形態の場合、この方法は、本明細書で説明した機能を実行するモジュール(たとえば、プロシージャ、関数など)を用いて実装されてもよい。本明細書で説明する方法を実施する際に、命令を有形に具現する機械可読媒体が使用されてもよい。たとえば、ソフトウェアコードは、メモリに記憶され、プロセッサユニットによって実行されてもよい。メモリは、プロセッサユニット内に実装されてもよくあるいはプロセッサユニットの外部に実装されてもよい。本明細書において使用される「メモリ」という用語は、長期メモリ、短期メモリ、揮発性メモリ、不揮発性メモリ、または他のメモリのタイプを指し、特定のタイプのメモリもしくは特定の数のメモリ、またはメモリが格納される媒体のタイプに限定すべきではない。

#### 【0068】

各機能は、ファームウェアおよび/またはソフトウェアにおいて実装される場合、コンピュータ可読媒体上の1つまたは複数の命令またはコードとして記憶されてもよい。例には、データ構造を用いて符号化されたコンピュータ可読媒体、およびコンピュータプログラムを用いて符号化されたコンピュータ可読媒体が含まれる。コンピュータ可読媒体は、物理的なコンピュータ記憶媒体を含む。記憶媒体は、コンピュータによってアクセスできる入手可能な媒体であってもよい。限定ではなく例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROMもしくは他の光ディスクストレージ、磁気ディスクストレージもしくは他の磁気記憶デバイス、または、所望のプログラムコードを命令もしくはデータ構造の形で記憶するために使用することができるとともに、コンピュータによってアクセスすることができる他の媒体を含むことができ、本明細書において使用されるディスク(disk)およびディスク(disc)は、コンパクトディスク(disc)(CD)、レーザーディスク(登録商標)(disc)、光ディスク(disc)、デジタル多用途ディスク(disc)(DVD)、フロッピーディスク(disk)、およびブルーレイディスク(disc)を含み、ディスク(disk)は通常、データを磁気的に再生し、ディスク(disc)はデータをレーザーを用いて光学的に再生する。上記の組合せもコンピュータ可読媒体の範囲に含まれるべきである。

#### 【0069】

コンピュータ可読媒体上のストレージに加えて、命令および/またはデータは、通信装置に含まれる伝送媒体上の信号として備えられてもよい。たとえば、通信装置は、命令およびデータを示す信号を有するトランシーバを含んでもよい。命令およびデータは、1つまたは複数のプロセッサに、請求項に概説される機能を実施させるように構成される。

#### 【0070】

本開示およびその利点について詳細に説明したが、添付の特許請求の範囲によって定義される本開示の技術から逸脱することなく、明細書において様々な変更、置換、および改変を施すことができることを理解されたい。たとえば、「上」および「下」などの関係語が、基板または電子デバイスについて使用される。当然、基板または電子デバイスが反転される場合、上は下に、下は上になる。加えて、横向きの場合、上および下は、基板または電子デバイスの側面を指すことがある。さらに、本出願の範囲は、本明細書で説明したプロセス、機械、製造、ならびに組成物、手段、方法、およびステップの特定の構成に限定されることを意図していない。本開示から当業者が容易に諒解するように、本明細書で説明する対応する構成と実質的に同じ機能を実行するかまたは実質的にそれと同じ結果を達成する、現存するかまたは今後開発されるプロセス、機械、製造、組成物、手段、方法、またはステップが、本開示に従って利用されてもよい。したがって、添付の特許請求の範囲は、そのようなプロセス、機械、製造、組成物、手段、方法、またはステップをそれらの範囲内に含むことを意図する。

#### 【符号の説明】

10

20

30

40

50

## 【0071】

|       |                             |    |

|-------|-----------------------------|----|

| 100   | 無線周波数(RF)フロントエンド(RFFE)モジュール |    |

| 102   | 電力増幅器                       |    |

| 104   | デュプレクサ/フィルタ                 |    |

| 106   | RFスイッチモジュール                 |    |

| 108   | 受動コンバイナ                     |    |

| 112   | チューナー回路                     |    |

| 112A  | 第1のチューナー回路                  | 10 |

| 112B  | 第2のチューナー回路                  |    |

| 114   | アンテナ                        |    |

| 115   | 接地端子                        |    |

| 116   | キャパシタ                       |    |

| 118   | インダクタ                       |    |

| 120   | ワイヤレストラシーバ(WTR)             |    |

| 122   | キャパシタ                       |    |

| 130   | モデム                         |    |

| 132   | キャパシタ                       |    |

| 140   | アプリケーションプロセッサ               |    |

| 150   | RFフロントエンドモジュール              |    |

| 152   | 電源                          | 20 |

| 154   | クロック                        |    |

| 156   | 電力管理集積回路(PMIC)              |    |

| 158   | キャパシタ                       |    |

| 160   | チップセット                      |    |

| 162   | キャパシタ                       |    |

| 164   | キャパシタ                       |    |

| 166   | インダクタ                       |    |

| 170   | WiFiモジュール                   |    |

| 172   | WLANモジュール                   |    |

| 174   | キャパシタ                       | 30 |

| 180   | デュプレクサ                      |    |

| 192   | アンテナ                        |    |

| 194   | アンテナ                        |    |

| 200   | ダイプレクサ                      |    |

| 200-1 | 第1のダイプレクサ                   |    |

| 200-2 | 第2のダイプレクサ                   |    |

| 201   | システムボード                     |    |

| 202   | 基板                          |    |

| 210   | アンテナスイッチ(ASW)               |    |

| 210-1 | ハイバンドアンテナスイッチ               | 40 |

| 210-2 | ローバンドアンテナスイッチ               |    |

| 212   | ハイバンド(HB)入力ポート              |    |

| 214   | ローバンド(LB)入力ポート              |    |

| 216   | アンテナ                        |    |

| 218   | 電力増幅器                       |    |

| 220   | RFスイッチ                      |    |

| 230   | フィルタ                        |    |

| 250   | RFフロントエンドモジュール              |    |

| 300   | RF回路構造                      |    |

| 301   | 犠牲基板                        | 50 |

|                         |    |

|-------------------------|----|

| 302 ハンドル基板              |    |

| 306 第1の誘電体層             |    |

| 310 能動デバイス              |    |

| 320 埋込み酸化物(BOX)層        |    |

| 350 相互接続                |    |

| 400 集積RF回路構造            |    |

| 402 ハンドル基板              |    |

| 406 前面誘電体層              |    |

| 410 能動デバイス              |    |

| 412 前面接点                | 10 |

| 420 絶縁層                 |    |

| 430 裏面金属被覆              |    |

| 440 裏面誘電体               |    |

| 450 前面相互接続              |    |

| 500 集積回路構造              |    |

| 502 ハンドル基板              |    |

| 506 前面誘電体層              |    |

| 510 能動デバイス              |    |

| 510-1 第1の能動デバイス         |    |

| 510-2 第2の能動デバイス         | 20 |

| 512 ゲート接点               |    |

| 514 前面接点                |    |

| 516 ソース/ドレイン(S/D)領域     |    |

| 520 絶縁層                 |    |

| 530 隆起したソース/ドレイン(S/D)領域 |    |

| 532 裏面接点                |    |

| 540 裏面誘電体層              |    |

| 540-1 第1の裏面誘電体層         |    |

| 540-2 第2の裏面誘電体層         |    |

| 550 裏面金属被覆              | 30 |

| 550-1 裏面金属被覆の第1の部分      |    |

| 550-2 裏面金属被覆の第2の部分      |    |

| 550-3 裏面金属被覆の第3の部分      |    |

| 550-4 裏面金属被覆の第4の部分      |    |

| 550-5 裏面金属被覆の第5の部分      |    |

| 560 ピア                  |    |

| 570 前面金属被覆              |    |

| 570-1 前面金属被覆の第1の部分      |    |

| 570-2 前面金属被覆の第2の部分      |    |

| 580 集積回路構造              | 40 |

| 582 裏面接点                |    |

| 590 裏面の隆起したボディ領域        |    |

| 592 裏面接点                |    |

| 594 フォトレジスト             |    |

| 600 集積回路構造              |    |

| 700 集積回路構造              |    |

| 800 集積回路構造              |    |

| 1000 ワイヤレス通信システム        |    |

| 1020 リモートユニット           |    |

| 1025A ICデバイス            | 50 |

1025B ICデバイス

1025C ICデバイス

1030 リモートユニット

1040 基地局

1050 リモートユニット

1080 順方向リンク信号

1090 逆方向リンク信号

1100 設計用ワークステーション

1101 ハードディスク

1102 ディスプレイ

1103 ドライブ装置

1104 記憶媒体

1110 回路設計

1112 半導体構成要素

10

【図面】

【図1A】

FIG. 1A

【図1B】

FIG. 1B

20

30

40

50

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

10

【図 3 A】

FIG. 3A

【図 3 B】

FIG. 3B

20

30

40

50

【図 3 C】

FIG. 3C

【図 3 D】

FIG. 3D

10

【図 3 E】

FIG. 3E

【図 4】

FIG. 4

20

30

40

50

【図 5 A】

FIG. 5A

【図 5 B】

FIG. 5B

10

20

【図 6 A】

FIG. 6A

【図 6 B】

FIG. 6B

30

40

50

【図 6 C】

FIG. 6C

【図 6 D】

FIG. 6D

10

20

【図 6 E】

FIG. 6E

30

40

【図 7 A】

FIG. 7A

50

【図 7 B】

FIG. 7B

【図 7 C】

FIG. 7C

10

【図 7 D】

FIG. 7D

【図 7 E】

FIG. 7E

20

【図 8 A】

FIG. 8A

【図 8 B】

FIG. 8B

30

40

50

【図 8 C】

FIG. 8C

【図 8 D】

FIG. 8D

10

【図 8 E】

FIG. 8E

【図 9】

20

30

FIG. 9

40

50

【図 10】

FIG. 10

【図 11】

FIG. 11

10

20

30

40

50

## フロントページの続き

(51)国際特許分類

|        |        |   |

|--------|--------|---|

| F I    |        |   |

| H 01 L | 27/088 | C |

| H 01 L | 27/088 | D |

ードシャー・ストーク - オン - トレント・サンズ・ロード・55

審査官 恩田 和彦

(56)参考文献 米国特許出願公開第2008/0206977(US, A1)

特開2001-230423(JP, A)

特開平05-257171(JP, A)

特開2008-252068(JP, A)

(58)調査した分野 (Int.Cl., DB名)

|        |         |

|--------|---------|

| H 01 L | 29/786  |

| H 01 L | 21/336  |

| H 01 L | 27/088  |

| H 01 L | 21/8234 |