(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6112972号

(P6112972)

(45) 発行日 平成29年4月12日(2017.4.12)

(24) 登録日 平成29年3月24日(2017.3.24)

(51) Int.Cl.

F 1

H04N 5/225 (2006.01)

H04N 5/91 (2006.01)H04N 5/225

H04N 5/91F

J

請求項の数 7 (全 14 頁)

(21) 出願番号 特願2013-112376 (P2013-112376)

(22) 出願日 平成25年5月28日 (2013.5.28)

(65) 公開番号 特開2014-232955 (P2014-232955A)

(43) 公開日 平成26年12月11日 (2014.12.11)

審査請求日 平成28年5月25日 (2016.5.25)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

撮像手段と、

第1のCPUと第1の通信手段とを有する第1の処理回路であって、撮影指示に応じて前記撮像手段から取得した画像データを記録媒体に記録すると共に、取得した画像データを第1のメモリに記憶する第1の処理回路と、

第2のCPUと第2の通信手段とを有する第2の処理回路であって、撮影指示に応じて前記撮像手段から取得した画像データを前記記録媒体に記録すると共に、取得した画像データを第2のメモリに記憶し、インデックス画面の表示指示に応じて前記第2のメモリに記憶された画像データを用いて前記記録媒体に記録された画像データのインデックス画面を表示する第2の処理回路とを備え、

前記第1のCPUは、撮影指示に応じた1画面の画像データの記録処理に応じて前記第2の処理回路に前記1画面の画像データを送信し、前記第2のCPUは、前記第2の通信手段を介して前記第1の処理回路から受信した画像データを前記第2のメモリに記憶することを特徴とする撮像装置。

## 【請求項 2】

前記第1のCPUは、前記1画面の画像データの記録処理が完了したことに応じて、前記第2のCPUにより画像データの送信が指示されているか否かを判別し、前記第2のCPUにより画像データの送信が指示されていると判別した場合に、前記1画面の画像データを前記第2の処理回路に送信することを特徴とする請求項1に記載の撮像装置。

## 【請求項 3】

前記第2のC P Uは、前記第2の処理回路の処理負荷に応じて、前記第1の処理回路に對して画像データの送信指示を発行し、

前記第1のC P Uは、前記送信指示に応答して、前記1画面の画像データを送信することを特徴とする請求項2に記載の撮像装置。

## 【請求項 4】

前記第2のC P Uは、前記処理負荷を前記撮像手段による連写速度で判定することを特徴とする請求項3に記載の撮像装置。

## 【請求項 5】

前記第1のC P Uは、前記第2のC P Uにより画像データの送信が指示されていると判別しない場合、前記1画面の画像データを前記第2の処理回路に送信しないようにすることを特徴とする請求項2に記載の撮像装置。 10

## 【請求項 6】

前記第2のC P Uは、前記表示指示に係る画像データが前記第2のメモリに記憶されていない場合、前記第1のC P Uに対して前記表示指示に係る画像データを送信するように指示し、前記表示指示に係る画像データの送信の指示に応じて前記第1の処理回路から送信された画像データを前記第2のメモリに記憶することを特徴とする請求項2に記載の撮像装置。

## 【請求項 7】

前記第2のC P Uは、前記表示指示に係る画像データを前記第1の処理回路から取得できない場合、前記表示指示に係る画像データを前記記録媒体から取得することを特徴とする請求項6に記載の撮像装置。 20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は撮像装置に関し、特に動画の記録を行う撮像装置に関する。

## 【背景技術】

## 【0002】

従来、動画を撮影してメモリカードなどの記録媒体に記録するデジタルカメラなどの撮像装置が知られている（例えば特許文献1）。民生用のデジタルカメラにおいても、近年では、画素数の多い画像を撮影することができるものも登場している。 30

## 【0003】

撮影する画像の画素数が多くなった場合、処理すべきデータ量が増加する。特に静止画の連写時においては、今までよりも高速に画像データを処理する必要がある。画像データの処理能力を上げるためには、記憶容量が大きく高速にアクセスが可能なメモリや、より高速に画像データを処理可能なマイクロコンピュータなどの処理回路が必要になる。

## 【0004】

しかしながら、このような高性能なメモリやマイコンを使うことは、回路規模の大型化や消費電力の増加につながる。民生用のデジタルカメラにおいては、サイズやコスト面での制約から、或いは、消費電力を極力抑えることの要請から、高性能なメモリやマイコンを使うことができない場合がある。 40

## 【0005】

そこで、複数の処理回路を備え、撮影した画像をこれら複数の処理回路により並列に処理して記録することが考えられる。また、記録された画像を再生する際、記録された画像の縮小画像（サムネイル）画像の一覧を含むインデックス画面を表示し、インデックス画面に表示されたサムネイル画像からユーザが選択した画像を再生する構成が一般的である。

## 【先行技術文献】

## 【特許文献】

## 【0006】

【特許文献1】特開2005-101835号公報 50

**【発明の概要】****【発明が解決しようとする課題】****【0007】**

インデックス画面を表示する際、記録媒体から画像データを再生して復号した後、画面サイズを縮小する必要がある。そのため、インデックス画面を表示するまでに時間がかかってしまうという問題がある。そこで、撮影された画像をメモリに記憶しておき、インデックス画面を表示する際には、メモリに記憶された画像データを縮小して表示することで、撮影後に迅速にインデックス画面を表示することが考えられる。

**【0008】**

しかしながら、前述のように、複数の処理回路によりそれぞれ記録された画像をメモリに記憶していた場合、各処理回路がメモリから画像データを読み出してインデックス画面を生成する必要がある。そのため、表示までに時間がかかってしまうことが考えられる。

10

**【0009】**

本発明はこのような問題を解決し、迅速にインデックス画面を表示することが可能な撮像装置を提供することを目的とする。

**【課題を解決するための手段】****【0010】**

本発明の一側面によれば、撮像手段と、第1のCPUと第1の通信手段とを有する第1の処理回路であって、撮影指示に応じて前記撮像手段から取得した画像データを記録媒体に記録すると共に、取得した画像データを第1のメモリに記憶する第1の処理回路と、第2のCPUと第2の通信手段とを有する第2の処理回路であって、撮影指示に応じて前記撮像手段から取得した画像データを前記記録媒体に記録すると共に、取得した画像データを第2のメモリに記憶し、インデックス画面の表示指示に応じて前記第2のメモリに記憶された画像データを用いて前記記録媒体に記録された画像データのインデックス画面を表示する第2の処理回路とを備え、前記第1のCPUは、撮影指示に応じた1画面の画像データの記録処理に応じて前記第2の処理回路に前記1画面の画像データを送信し、前記第2のCPUは、前記第2の通信手段を介して前記第1の処理回路から受信した画像データを前記第2のメモリに記憶することを特徴とする撮像装置が提供される。

20

**【発明の効果】****【0011】**

30

本発明によれば、迅速にインデックス画面を表示することが可能となる。

**【図面の簡単な説明】****【0012】**

【図1】実施形態における撮像装置の構成を示すブロック図。

【図2】処理回路200による記録時の処理を示すフローチャート。

【図3】処理回路100による記録時の処理を示すフローチャート。

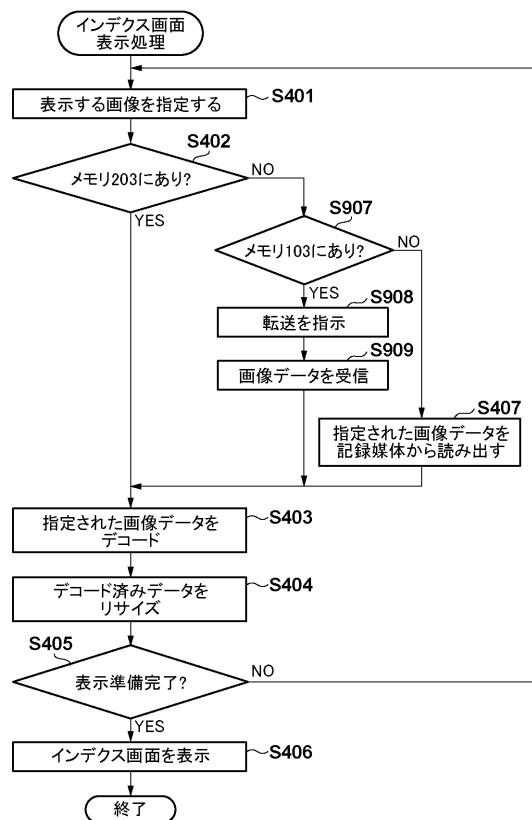

【図4】インデックス画面の表示処理を示すフローチャート。

【図5】処理回路200による記録時の処理を示すフローチャート。

【図6】処理回路100による記録時の処理を示すフローチャート。

【図7】撮影待機状態で実行される連写速度の判定処理を示すフローチャート。

40

【図8】撮影処理中に実行される連写速度の判定処理を示すフローチャート。

【図9】インデックス画面の表示処理を示すフローチャート。

**【発明を実施するための形態】****【0013】**

以下、図面を参照して本発明の好適な実施形態について詳細に説明する。なお、本発明は以下の実施形態に限定されるものではなく、本発明の実施に有利な具体例を示すにすぎない。また、以下の実施形態の中で説明されている特徴の組み合わせの全てが本発明の課題解決のために必須のものであるとは限らない。

**【0014】**

(第1の実施形態)

50

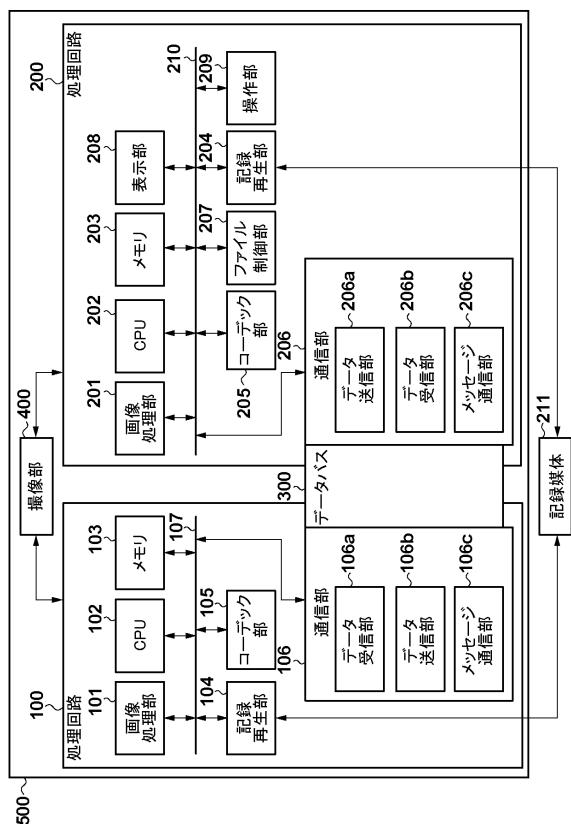

図1は、本発明の実施形態に係る撮像装置500の構成の一例を示すブロック図である。撮像装置500は、二つの処理回路100（第1の処理回路）と処理回路200（第2の処理回路）を備えている。本実施形態では、これら二つの処理回路100、200はそれぞれが一つの集積回路（IC）として構成される。

【0015】

また、二つの処理回路100と処理回路200の間で通信を行うためのデータバス300が設けられている。処理回路100、200はそれぞれ独立に撮像部400から動画データを取得することが可能である。処理回路100、200はそれぞれ、撮像部400から取得した動画データを処理することが可能である。

【0016】

次に、処理回路100と処理回路200の構成について説明する。処理回路100は、画像処理部101、CPU102（Central Processing Unit）（第1のCPU）、メモリ103、記録再生部104、コーデック部105、通信部106、バス107を有する。本実施形態では、メモリ103としてSDRAMを使用する。また、メモリ103は処理回路100に内蔵されているが、処理回路100の外部に設けられてもよい。

10

【0017】

CPU102は、メモリ103に格納されているコンピュータプログラム（ソフトウェア）に従って、撮像装置500全体の動作を制御する。メモリ103は、CPU102のワークエリアとして機能する。なお、CPU102のワークエリアは、メモリ103に限られるものではなく、ハードディスクドライブ等の外部記録装置等であってもよい。画像処理部101は、撮像部400から取得した静止画データに対して画素補間処理や色変換処理等の画像処理を行う。画像処理部101は、撮像部400から取得したRGB色空間の動画データをYUV色空間のデータフォーマットに変換する。また、画像処理部101は、撮像部400が取得した画像の画素数（画面サイズ）を縮小、或いは拡大（リサイズ）する。

20

【0018】

撮像部400及び画像処理部101は、CPU102によって、オートフォーカス（AF）処理及び自動露出制御（AE）処理を行うように制御される。CPU102から撮影を行うように指示された場合、撮像部400及び画像処理部101は露光処理や現像処理等の処理を含む撮影処理を実行する。撮像部400は、CCDやCMOS等の撮像素子やA/D変換器等を備える。撮像部400は、撮像素子により得られたアナログ信号をデジタルデータに変換して出力する。撮像部400から取得された静止画データは、YUV形式の静止画データとしてメモリ103に記憶される。メモリ103に記憶された静止画データに対して、コーデック部105（第1の符号化部、第1の復号部）により符号化処理が行われ、静止画データのデータ量が圧縮される。

30

【0019】

記録再生部104は、記録時においては、符号化された静止画データを記録媒体211に書き込む。コーデック部105は、撮影時においては、撮像部400より取得した静止画データをJPEG等の公知の符号化方式により符号化する。

40

【0020】

通信部106（第1の通信部）は、処理回路200との間で動画データやその他必要なコマンドを送受信する。通信部106は、動画データを受信するためのデータ受信部106a、画像データを送信するためのデータ送信部106b、制御コマンドなどのメッセージを送るためのメッセージ通信部106cを有する。通信部106での通信はデータバス300を介して行われる。それぞれの通信は独立して行うことが可能である。

【0021】

本実施形態においては、後述のように、連写後、処理回路100により処理されたインデクス用の画像データが通信部106により処理回路200に送信される。

【0022】

処理回路200は、画像処理部201、CPU202（第2のCPU）、メモリ203

50

、記録再生部 204、コーデック部 205、通信部 206、ファイル制御部 207、表示部 208、操作部 209、バス 210 を有する。本実施形態では、メモリ 203 として SDRAM を使用する。また、メモリ 203 は処理回路 100 に内蔵されているが、処理回路 200 の外部にメモリ 203 を設けることも可能である。画像処理部 201、CPU 202、メモリ 203、コーデック部 205、通信部 206（第 2 の通信部）の各ブロックは処理回路 100 における各ブロックと同様の機能を持つ。

#### 【0023】

処理回路 200 は、撮影時には、撮像部 400 から動画データを取得して、コーデック部 205（第 2 の符号化部、第 2 の復号部）により符号化処理を行う。記録再生部 204 は、記録時においては、コーデック部 205 により符号化された静止画データを記録媒体 212 に記録する。記録媒体 211 は、メモリカードなどのランダムアクセス媒体である。また、本実施形態では、不図示の装着、排出機構により、容易に装着、排出が可能となっている。また、記録媒体 211 を撮像装置 500 に内蔵する構成としてもよい。CPU 202 は、操作部 209 により指定された画素数や画質の設定に従って静止画データの記録を制御する。また、記録再生部 204 は、再生時においては、後述のようにユーザによって選択された静止画データを記録媒体 211 から読み出す。コーデック部 205 は、再生時においては、記録媒体 211 から読み出された静止画データを復号する。

#### 【0024】

画像処理部 201（第 2 のリサイズ部）は、撮影時においては、撮像部 400 から取得した動画データの画像サイズを表示部 208 のサイズに合わせて変更してメモリ 203 に記憶する。そして、リサイズされたデータが表示部 208 に供給されて表示される。また、再生時においては、画像処理部 201 は、再生された静止画データのサイズを表示部 208 のサイズに合わせて変更してメモリ 203 に記憶する。そして、リサイズされたデータが表示部 208 に供給されて表示される。表示部 208 は、撮影された画像や再生された画像の他、各種の必要な情報を表示する。CPU 202 は、表示部 208 に表示する情報を生成して表示部 208 に送る。

#### 【0025】

ファイル制御部 207 は、所定のファイルシステムに従い、記録媒体 211 に記録された静止画をファイルとして管理する。本実施形態では、FAT ファイルシステムに従い、記録媒体 211 に記録された画像ファイルを管理する。なお、本実施形態では、ファイル制御部 207 は処理回路 200 に設けている。ファイル制御部 207 は、電源投入時、或いは、記録媒体が装着された場合に、記録媒体 211 からファイルシステムに係る管理情報（FAT やディレクトリエントリなど）を読み出し、メモリ 203 に記憶する。そして、記録媒体 211 に対する記録処理に伴い、メモリ 203 に記憶された管理情報を変更（更新）する。そして、静止画記録時などの所定のタイミングで、メモリ 203 より管理情報を読み出し、記録再生部 204 により記録媒体 211 に記録することにより、記録媒体 212 の管理情報を更新する。

#### 【0026】

操作部 209 は、撮像装置 500 を操作するためのユーザインターフェースとして機能する。操作部 209 は、撮像装置 500 を操作するための電源ボタン、モード変更ボタン、シャッターボタン、十字ボタン、メニューボタン等を有し、各ボタンはスイッチ、タッチパネル等により構成される。CPU 202 は、操作部 209 を介して入力されたユーザの指示に従って撮像装置 500 を制御する。ユーザによって操作部 209 のボタンが操作された場合、操作部 209 から各ボタンに応じた操作信号が CPU 202 に入力される。CPU 202 は操作部 209 から入力された操作信号を解析し、解析結果に応じて操作信号に対応した処理を判定する。CPU 202 は、操作部 209 から入力された操作信号に対応した処理を実行するように撮像装置 500 の各部を制御する。

#### 【0027】

ユーザは操作部 209 を操作することにより、撮影する画像の露光時間（シャッタ速度）や記録する画像のサイズ（画素数）と画質（圧縮率）などを設定することができる。ま

10

20

30

40

50

た、ユーザは、操作部 209 を操作することにより、撮影された画像に対し、ノイズ低減処理などの特殊な処理を施すか否かを設定することができる。CPU202 は、ユーザによるこれらの設定に基づいて、撮像部 400 により撮影される画像データの露光時間や、撮影された画像に対する処理を制御する。また、CPU202 は、操作部 209 のシャッター ボタンがユーザにより連続して操作されている場合に、所定のタイミングで連続的に撮影指示を発行することにより、静止画の連写を行う。また、CPU202 は、撮影される画像データの露光時間、撮影された画像に対する処理、画像データを一時記憶するメモリ 203 の空き容量や記録再生部 204 によるデータの書き込み速度などにより、連写中に発行する撮影指示の間隔を変更することができる。

## 【0028】

10

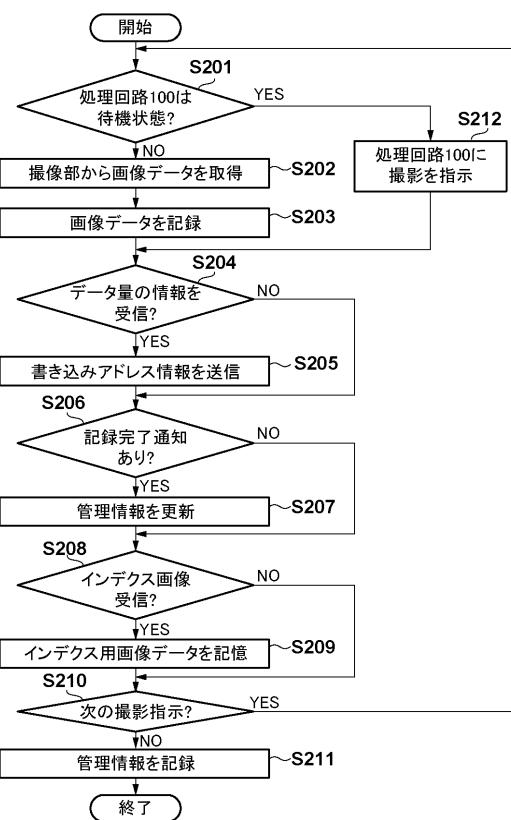

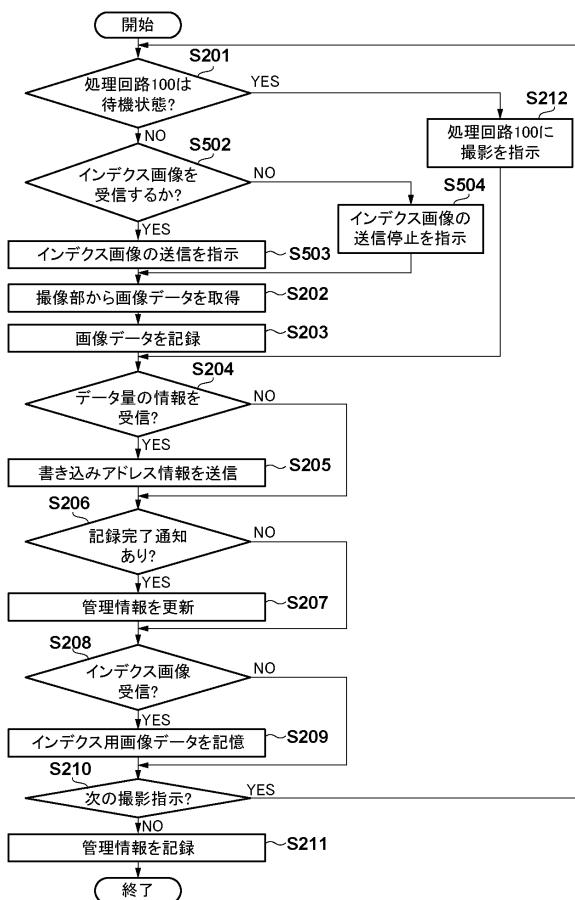

次に、撮像装置 500 における記録時の処理について説明する。図 2 は処理回路 200 における記録時の処理を示すフローチャートである。図 2 の処理は CPU202 が各部を制御することにより実行される。まず、記録に先立ち、ファイル制御部 207 は、記録媒体 211 から読み出した管理情報 (FAT) に基づいて、記録媒体 211 における空き領域を判別する。ファイル制御部 207 は、この空き領域に基づいて、記録媒体 211 に対してデータを書き込むための書き込みアドレスを決める。

## 【0029】

操作部 209 より静止画撮影の指示があった場合、CPU202 は、通信部 206 により通信を行うことにより、処理回路 100 が撮影待機状態、即ち、撮像部 400 により撮影された静止画を処理しているか否かを判別する (S201)。処理回路 100 が待機状態である場合、CPU202 は、通信部 206 により、処理回路 100 に対し撮影指示を出力する (S212)。処理回路 100 が待機状態ではない場合、CPU202 は、撮像部 400 から 1 フレームの静止画データを取得し、画像処理部 201 にて YUV 色空間データに変換した後、メモリ 203 に記憶する (S202)。次に、CPU202 は、コードック部 205 により、メモリ 203 に記憶された静止画データを符号化し、メモリ 203 に記憶する。ここでメモリ 203 に記憶された静止画データは、インデックス画像として使用するため、電源がオフされるか、或いは、メモリ 203 の空き領域が無くなつて削除されるまで、メモリ 203 に保持される。

20

## 【0030】

1 画面の静止画データの処理が完了した場合、CPU202 は、ファイル制御部 207 に対し、この符号化データの書き込みを指示する。ファイル制御部 207 は、記録媒体 212 の空き領域から書き込みアドレスを決定し、記録再生部 204 に対しデータの書き込みを指示する。記録再生部 204 はメモリ 203 より符号化データを読み出し、記録媒体 211 の指定されたアドレスに書き込む (S203)。データの書き込みが完了した場合、ファイル制御部 207 は、メモリ 203 に記憶された管理情報の内容を更新すると共に、空き領域も更新する。

30

## 【0031】

次に、CPU202 は、処理回路 100 から、符号化された静止画データのデータ量の情報が通知されたか否かを判別する (S204)。データ量の情報が通知された場合、CPU202 は、記録再生部 204 により記録媒体 211 に直前に書き込まれた静止画データの書き込みアドレスと、通知されたデータ量とに基づいて、処理回路 100 による符号化データの書き込みアドレスを決定する。そして、決定した書き込みアドレスをデータ送信部 206a により処理回路 100 に送信する (S205)。即ち、CPU202 は、連写時において、直前に書き込まれた静止画データの最終書き込みアドレスを含むクラスタの次のクラスタの先頭から処理回路 100 が符号化データを書き込むように、書き込みアドレスを決定する。

40

## 【0032】

このように書き込みアドレスの情報を送信した後、CPU202 は、処理回路 100 から符号化データの書き込み完了の通知が送信されたか否かを判別する (S206)。書き込み完了の通知がデータ受信部 206b により受信された場合、CPU202 は、ファイ

50

ル制御部 207 に対し、FAT を更新するように指示する。ファイル制御部 207 は、処理回路 100 による書き込みに応じて、メモリ 203 に記憶された FAT の内容を更新する (S207)。

#### 【0033】

次に、CPU 202 は、後述のように、データ受信部 206b が処理回路 100 からのインデックス画像を受信したか否かを判別する (S208)。ここで、データ受信部 206b がインデックス画像データを受信した場合、これをメモリ 203 に記憶する (S209)。このとき、メモリ 203 におけるインデックス画像データのための記憶領域に空きが無い場合、CPU 202 は、メモリ 203 から最も古い画像データを削除することができる。こうしてメモリ 203 の空き領域が確保され、受信した画像データがメモリ 203 に記憶される。

#### 【0034】

次に、CPU 202 は、操作部 209 により撮影指示の操作が行われているか否かを判別する (S210)。撮影指示の操作が行われている場合、CPU 202 は、S201 に戻って処理を続ける。また、撮影指示の操作が行われていない場合、CPU 202 は、メモリ 203 に記憶された管理情報を記録媒体 211 に書き込むように記録再生部 204 に指示する。記録再生部 204 は、メモリ 203 から管理情報を読み出し、記録媒体 211 に記録する (S211)。

#### 【0035】

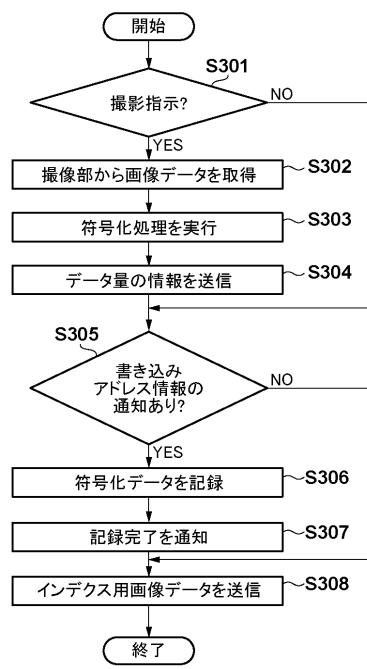

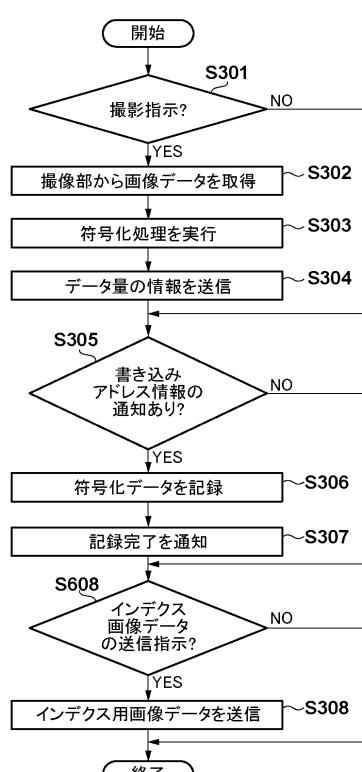

図 3 は、処理回路 100 における記録時の処理を示すフローチャートである。図 3 の処理は CPU 102 が各部を制御することにより実行される。CPU 102 は、通信部 106 により、処理回路 200 から撮影指示 (図 2 の S212 参照。) を受けたか否かを判別する (S301)。撮影指示を受けていない場合は S307 に進む。撮影指示を受けた場合、CPU 102 は、撮像部 400 から 1 フレームの画像データを取得し、画像処理部 101 にて YUV 色空間データに変換した後、メモリ 103 に記憶する (S302)。ここでメモリ 103 に記憶された静止画データは、静止画の記録終了後に、インデックス画像として処理回路 100 に転送される。そのため、電源がオフされるか、メモリ 103 の空き領域が無くなつて削除されるまで、或いは、処理回路 200 への転送が完了するまで、メモリ 103 に保持される。次に、CPU 102 は、符号化された静止画データのサイズの情報をメッセージ通信部 106c により処理回路 200 に送信する (S304)。

#### 【0036】

次に、CPU 102 は、処理回路 200 から、記録媒体 211 における書き込みアドレスの情報 (図 2 の S205 参照。) が受信されたか否かを判別する (S305)。書き込みアドレスの情報が受信されていた場合、CPU 102 は、記録媒体 211 における指定された書き込みアドレスに、メモリ 103 に記憶された静止画データを書き込むように記録再生部 104 に指示する。記録再生部 104 は、メモリ 103 より符号化された静止画データを読み出し、記録媒体 211 の指定された書き込みアドレスに書き込む (S306)。符号化データの書き込みが完了すると、CPU 102 は、メッセージ通信部 106c により、書き込み完了の通知を処理回路 200 に送信する (S307)。次に、CPU 102 は、メモリ 103 よりインデックス用の画像データを読み出し、データ送信部 106b より処理回路 200 に送信する (S308)。 (図 2 の S208 参照。)

#### 【0037】

このように、処理回路 100 による画像データの記録が終了した後、インデックス画像のための画像データが処理回路 100 から処理回路 200 に送信され、メモリ 203 に記憶される。

#### 【0038】

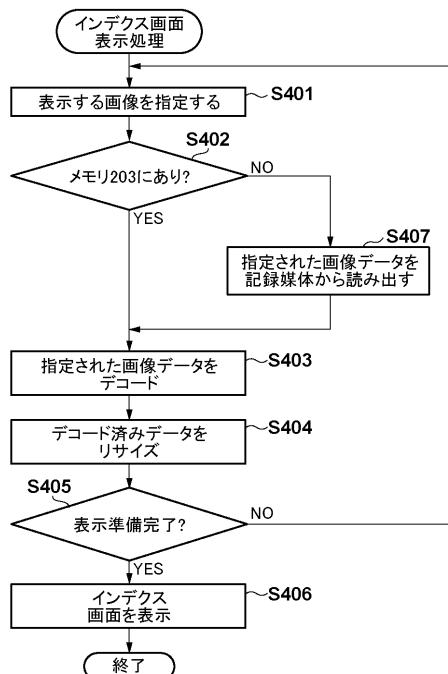

次に、再生時におけるインデックス画面の生成処理を説明する。操作部 209 よりインデックス表示の指示があった場合、CPU 202 は、インデックス画面を生成する。本実施形態では、インデックス画面の表示の指示があった場合、撮影の順に、最新の画像から n 画面分のサムネイル画像を生成し、これら n 画面のサムネイル画像を含むインデックス画面が表示

10

20

30

40

50

される。なお、1画面に表示するサムネイル画像の画面数nを、ユーザが操作部209を操作することにより決める構成としてもよい。この場合、CPU102は、設定されている画面数nに基づいて、表示すべきサムネイル画像を決める。

#### 【0039】

図4は処理回路200によるインデクス画面の表示処理を示すフローチャートである。図4の処理はCPU202が各部を制御することにより実行される。まず、CPU202は、前述のように決定したサムネイル画像の一つを指定する(S401)。そして、CPU202は、指定された画像データがメモリ203に記憶されているか否かを判別する(S402)。メモリ203に指定された画像データが記憶されていた場合、CPU202は、コーデック部205により指定された画像データを復号する(S403)。CPU202は、画像処理部201により復号された画像データのサイズを縮小し、メモリ203のインデクス画面用の記憶領域に記憶する(S404)。次に、CPU202は、表示すべき全てのサムネイル画像がメモリ203に記憶され、表示準備が完了したか否かを判別する(S405)。全てのサムネイル画像がメモリ203に記憶され、表示準備が完了した場合、CPU202は、各サムネイル画像データをメモリ103より読み出し、インデクス画面を生成して表示部208に表示する(S406)。

#### 【0040】

S402において、メモリ203に指定された画像データが記憶されていない場合、CPU202は、記録再生部204により、指定された画像データを記録媒体211から読み出す(S407)。そして、読み出した画像データをコーデック部205により復号する。

#### 【0041】

このようにインデクス画面が表示部208に表示された後、ユーザが操作部209を操作して再生する画像を指定し、再生を指示することができる。再生が指示された場合、CPU202は、記録再生部204により、指定された画像データを記録媒体211より読み出し、コーデック部205によりデコードする。そして、デコードされた静止画データを画像処理部201により縮小し、表示部208により表示する。

#### 【0042】

このように、本実施形態では、二つの処理回路100、200により静止画を撮影し記録する構成において、処理回路100による1画面の画像データの記録終了後、画像データを処理回路200に転送する。そして、転送された画像データを処理回路200におけるメモリ203に記憶しておく。そのため、インデクス画面の表示の指示があった場合、このメモリ203に記憶された画像データからサムネイル画像を生成し、インデクス画面を表示することにより、迅速にインデクス画面を表示することができる。また、1画面の静止画の記録が完了する度に、処理回路100に画像データが転送され、メモリ203に記憶される。そのため、連写後のインデクス表示があった場合にも迅速にインデクス画面を表示することができる。

#### 【0043】

なお、本実施形態では、処理回路100により記録される画像データをインデクス用の画像データとして処理回路200に送信したが、処理回路100によりサムネイル画像のサイズに縮小した状態で処理回路200に送信する構成としてもよい。こうすることで、処理回路200への画像データの送信に要する時間が短くなり、CPU202の処理負荷が軽減され、また、バス210の占有時間も短くなる。更に、メモリ203に対して記憶できるインデクス画像の数も増やすことができる。

#### 【0044】

##### (第2の実施形態)

次に、第2の実施形態を説明する。本実施形態においても、撮像装置の構成は図1の構成と同様である。第1の実施形態では、処理回路100は、1画面の画像データの記録処理が終了した後に、インデクス画像データを処理回路200に送信していた。これに対し第2の実施形態では、処理回路200のCPU202が、処理回路100に対しインデク

ス画像データの送信を指示し、処理回路100はこの送信指示に応答してインデクス画像データを処理回路200に送信する。そして、CPU202は、処理回路200における連写速度に基づいて、連写速度が遅く、CPU202の能力やバス210の処理帯域に余裕がある状態であるか否かを判定する。そして、この判定結果により、CPU202が、処理回路100に対してインデクス画像データの送信を指示する。

#### 【0045】

図5は、本実施形態における処理回路200による記録処理を示すフローチャートである。第1の実施形態に係る図2における処理ステップと同一の処理ステップには同一の参考番号を付しその説明を省略する。図5においては、S201とS202の間に、S502, S503, S504の処理ステップが介在する。S201において処理回路100が待機状態でない場合、CPU202は、処理回路200における連写速度が低く、処理回路100からのインデクス画像データを受信する状態であるか否かを判定する(S502)。インデクス画像データを受信すると判定した場合、CPU202は、メッセージ通信部206cにより、処理回路100に対してインデクス画像データの送信を指示する(S503)。一方、インデクス画像データを受信しないと判定した場合、CPU202は、処理回路100に対してインデクス画像データの送信停止を指示する(S504)。処理回路100では、メッセージ通信部106cがインデクス画像の送信指示、或いは、送信停止指示を受信すると、受信した指示をメモリ103に記憶する。

#### 【0046】

次に、S502における判定処理について説明する。CPU202は、操作部209からの撮影指示が出力されていない状態と、連写中の処理回路200の状態に基づいて、連写速度が低い状態であるか否かを判別する。そして、連写速度が低く、処理回路200によるCPU202の処理に余裕があり、また、バス210の処理帯域に余裕があると判断した場合に、処理回路100からのインデクス画像を受信すると判定する。

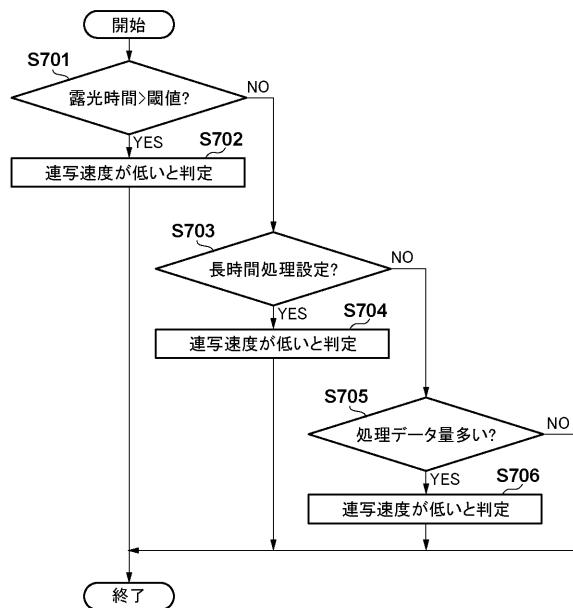

#### 【0047】

図7は、撮影指示が出力されていない状態においてCPU202によって実行される連写速度の判定処理を示すフローチャートである。図7の処理は、撮影待機状態において、CPU202により繰り返し実行される。CPU202は、ユーザにより設定されたシャッタ速度に基づく露光時間が閾値よりも長いか否かを判別する(S701)。露光時間が閾値よりも長い場合、CPU202は、連写速度が低いと判定する(S702)。また、S701で露光時間が閾値以下であった場合、CPU202は、ノイズ低減処理など、処理に時間がかかる所定の長時間処理がユーザにより設定されているか否かを判別する(S703)。長時間処理が設定されていた場合、CPU202は、連写速度が低いと判定する(S704)。また、長時間処理が設定されていない場合、CPU202は、ユーザにより設定された画像のサイズや画質に基づき、処理される画像のデータ量が多いか否かを判別する(S705)。処理データ量が多い設定、例えば、複数種類のサイズのうち、画像のサイズが最も大きいものに設定され、かつ、複数種類の画質のうち、最も高い画質であり、圧縮後のデータ量が多い場合、CPU202は、連写速度が低いと判定する(S706)。このように、連写速度が低いと判定した場合、CPU202は、判定結果をメモリ203に記憶しておく。

#### 【0048】

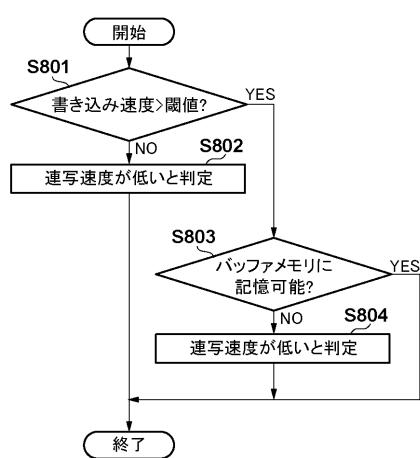

図8は、撮影(連写)開始後においてCPU202により実行される判断処理を示すフローチャートである。図8の処理は、撮影処理の実行中、CPU202により繰り返し実行される。CPU202は、記録媒体211に対するデータの書き込み可能速度が閾値よりも高いか否かを判別する(S801)。データの書き込み速度が閾値よりも高くない場合、連写速度が低いと判定する(S802)。また、データの書き込み速度が閾値よりも高い場合、CPU202は、メモリ203における、記録する画像データを一時記憶するためのバッファメモリ領域に空きがあり、データの記憶が可能であるか否かを判別する(S803)。バッファメモリ領域に空きがなくなると、CPU202は、撮像部400から画像データを取得する間隔を長くするように変更する。そのため、CPU202は、バ

ツファメモリ領域に空きが無い場合は連写速度が低いと判断する(S 8 0 4)。このように、連写速度が低いと判断した場合、CPU202は、判定結果をメモリ203に記憶する。

#### 【0049】

S 5 0 2においては、CPU202は、図7、図8の処理によってメモリ203に記憶された判定結果に基づいて連写速度が低いと判断した場合に、インデクス画像を受信すると判断する。

#### 【0050】

図6は、第2の実施形態における処理回路100の記録時の処理を示すフローチャートである。第1の実施形態に係る図3における処理ステップと同一の処理ステップには同一の参照番号を付しその説明を省略する。図6において、CPU102は、S 3 0 7で処理回路200に対して書き込み完了を通知した後、インデクス画像の送信指示を処理回路200から受信したか否かを判別する(S 6 0 8)。インデクス画像の送信指示を受信していた場合、CPU102は、メモリ103に記憶された未送信の画像データのうち最も新しい画像データをデータ送信部106bより処理回路200に送信する(S 3 0 8)。ここでは、CPU102は、1画面の画像データを送信する度に、処理回路200からの指示を確認し、処理回路200からインデクス画像の送信停止指示を受けるまでは、未送信の画像データの送信を続ける。そして、未送信の画像データを全て送信した場合、CPU102は、処理回路200への画像データの送信を停止する。

#### 【0051】

一方、未送信の画像データがメモリ103に記憶されている場合であっても、処理回路200よりインデクス画像の送信停止指示が発行された場合、CPU102は、処理回路200に画像データを送信せず、メモリ103に保持する。また、メモリ103の空き領域がなく、新たに生成されたインデクス画像データを記憶することができない場合、CPU102は、送信済みの画像データを削除して、新たに生成された画像データをメモリ103に記憶する。

#### 【0052】

次に、再生時におけるインデクス画面の生成処理を説明する。図9は処理回路200によるインデクス画面の表示処理を示すフローチャートである。図9の処理はCPU202が各部を制御することにより実行される。第1の実施形態に係る図4における処理ステップと同一の処理ステップには同一の参照番号を付しその説明を省略する。S 4 0 2において、メモリ203に指定された画像データが記憶されていない場合、CPU202は、メッセージ通信部206cにより、指定された画像データが処理回路100のメモリ103に記憶されているかを処理回路100に問い合わせる(S 9 0 7)。この結果、処理回路100より、指定された画像データがメモリ103に記憶されている旨の応答をメッセージ通信部206cにより受信した場合、CPU202は、指定した画像データの転送を処理回路100に指示する(S 9 0 8)。そして、CPU202は、データ受信部206bにより画像データを受信し(S 9 0 9)、指定された画像データをコーデック部205によりデコードする(S 4 0 3)。このように、CPU202は、表示指示に係る画像データがメモリ203に記憶されていない場合、処理回路100のメモリ103に対して当該表示指示に係る画像データの取得を試行する。

#### 【0053】

また、S 9 0 7で、メモリ103に指定された画像データが記憶されていない旨の応答を受信した場合、CPU202は、記録再生部204により、指定された画像データを記録媒体211から読み出す(S 4 0 7)。こうして、CPU202は、S 9 0 7～S 9 0 9の試行による上記表示指示に係る画像データの取得に失敗した場合には、当該表示指示に係る画像データを記録媒体211から取得することができる。そして、読み出した画像データをコーデック部205により復号する(S 4 0 3)。

#### 【0054】

このようにインデクス画面が表示部208に表示された後、ユーザが操作部209を操

10

20

30

40

50

作して再生する画像を指定し、再生を指示することができる。再生が指示された場合、CPU202は、記録再生部204により、指定された画像データを記録媒体211より読み出し、コードック部205によりデコードする。そして、デコードされた静止画データを画像処理部201により縮小し、表示部208により表示する。

#### 【0055】

このように、第2の実施形態では、CPU202は、処理回路200の処理負荷に応じて、処理回路100に対して画像データの送信指示又は送信停止指示を発行する。処理負荷は例えば連写速度で判定することができる。処理回路200による連写速度が低く、処理回路200が処理回路100により生成されたインデックス用の画像データを受信して記憶できる場合に、処理回路100から処理回路200に画像データが送信される。そのため、連写中に処理回路100から処理回路200に対して画像データを送信することでCPU202の負荷が大きくなり、更に、バス210の処理帯域が圧迫されることにより、撮影処理が中断することが無い。

#### 【0056】

##### (他の実施形態)

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。この場合、そのプログラム、及び該プログラムを記憶した記憶媒体は本発明を構成することになる。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 有福 浩信

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 徳 田 賢二

(56)参考文献 特開2008-219319 (JP, A)

特開2006-148731 (JP, A)

特開2008-124826 (JP, A)

特開2012-209798 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225

H04N 5/91