(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-56266

(P2010-56266A)

(43) 公開日 平成22年3月11日(2010.3.11)

(51) Int.Cl.

|      |         |           |

|------|---------|-----------|

| HO1L | 23/12   | (2006.01) |

| HO1L | 21/3205 | (2006.01) |

| HO1L | 23/52   | (2006.01) |

F 1

|      |       |

|------|-------|

| HO1L | 23/12 |

| HO1L | 21/88 |

| HO1L | 21/88 |

| HO1L | 21/88 |

|         |

|---------|

| 5 O 1 P |

| B       |

| T       |

| R       |

テーマコード(参考)

5 F O 3 3

審査請求 未請求 請求項の数 8 O L (全 10 頁)

(21) 出願番号

特願2008-219183 (P2008-219183)

(22) 出願日

平成20年8月28日 (2008.8.28)

(71) 出願人 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

(74) 代理人 100096699

弁理士 鹿嶋 英實

(72) 発明者 小谷 昭一

東京都青梅市藤橋3丁目3番地の2

カシオ計算機株式会社青

梅事業所第二工場内

F ターム(参考) 5F033 HH11 HH18 JJ11 JJ18 KK08

KK09 KK11 KK18 MM05 NN06

PP15 PP27 RR04 RR21 RR22

VV00 VV07 WW02 XX01 XX31

XX33

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】 C S P と呼ばれる半導体装置において、柱状電極形成用メッキレジスト膜を剥離した際にレジスト残渣が発生しにくいようにし、且つ、工程数を少なくする。

【解決手段】 保護膜 5 の上面全体に、スパッタにより形成されたチタン膜および銅膜からなる 2 層構造の配線形成用金属膜 7 a を形成する。次に、配線形成用金属膜 7 a の上面にネガ型のドライフィルムレジストからなる柱状電極形成用メッキレジスト膜 2 3 をパターン形成する。次に、配線形成用金属膜 7 a をメッキ電流路とした銅の電解メッキを行うことにより、柱状電極形成用メッキレジスト膜 2 3 の開口部 2 4 内の配線形成用金属膜 7 a の上面に柱状電極 8 を形成する。次に、柱状電極形成用メッキレジスト膜 2 3 を剥離する。この場合、柱状電極形成用メッキレジスト膜 2 3 は平坦性の極めて高い配線形成用金属膜 7 a の上面に形成されているため、柱状電極形成用メッキレジスト膜 2 3 のレジスト残渣が発生しにくくすることができる。

**【特許請求の範囲】****【請求項 1】**

半導体基板上の全面に配線形成用金属膜を形成する工程と、

前記配線形成用金属膜上に、柱状電極形成領域に対応する部分に開口部を有する柱状電極形成用メッキレジスト膜を形成する工程と、

前記配線形成用金属膜をメッキ電流路とした電解メッキを行なうことにより、前記柱状電極形成用メッキレジスト膜の開口部内の前記配線形成用金属膜上に柱状電極を形成する工程と、

前記柱状電極形成用メッキレジスト膜を剥離する工程と、

前記柱状電極を含む前記配線形成用金属膜上の配線形成領域にエッチングレジスト膜を形成する工程と、

前記配線形成用レジスト膜をマスクとして前記エッチングレジスト膜下以外の領域における前記配線形成用金属膜をエッチングして除去することにより、前記柱状電極を含む前記エッチングレジスト膜下に配線を形成する工程と、

前記エッチングレジスト膜を剥離する工程と、

を有することを特徴とする半導体装置の製造方法。

**【請求項 2】**

請求項 1 に記載の発明において、前記配線形成用金属膜を形成する工程は、スパッタにより形成されたチタン膜上にスパッタにより銅膜を形成する工程であることを特徴とする半導体装置の製造方法。

20

**【請求項 3】**

請求項 2 に記載の発明において、前記銅膜の厚さは前記チタン膜の厚さよりも厚くすることを特徴とする半導体装置の製造方法。

**【請求項 4】**

請求項 3 に記載の発明において、前記配線形成用金属膜の厚さは  $2 \sim 5 \mu\text{m}$  とすることを特徴とする半導体装置の製造方法。

**【請求項 5】**

請求項 1 に記載の発明において、前記柱状電極形成用メッキレジスト膜はドライフィルムレジストで形成することを特徴とする半導体装置の製造方法。

30

**【請求項 6】**

請求項 1 に記載の発明において、前記エッチング用レジスト膜は液状レジストで形成することを特徴とする半導体装置の製造方法。

**【請求項 7】**

請求項 6 に記載の発明において、前記エッチングレジスト膜は、スピンドル法により形成されたレジスト膜をフォトリソグラフィ法によりパターニングすることにより形成することを特徴とする半導体装置の製造方法。

**【請求項 8】**

請求項 6 に記載の発明において、前記エッチングレジスト膜はインクジェットプリント法により形成することを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】**

40

**【技術分野】****【0001】**

この発明は半導体装置の製造方法に関する。

**【背景技術】****【0002】**

従来の C S P (chip size package) と呼ばれる半導体装置には、半導体基板上に形成された配線の接続パッド部上面に柱状電極を形成したものがある（例えば、特許文献 1 参照）。この場合、配線は、半導体基板上に形成された銅を含む金属からなる下地金属層と、下地金属層の上面に形成された銅からなる上部金属層との 2 層構造となっている。

**【0003】**

50

【特許文献 1】特開 2008 - 84919 号公報

【0004】

上記従来の半導体装置の製造方法では、まず、半導体基板上の全面に形成された下地金属層の上面に形成された上部金属層を含む下地金属層の上面に、感光剤を含まない液状樹脂からなる被覆膜を形成する。この場合、被覆膜によって上部金属層を完全に覆い、上部金属層間に上部金属層の厚さよりも厚い被覆膜が形成されるようにする。被覆膜は、後述する柱状電極形成用メッキレジスト膜を剥離する際に、レジスト残渣が発生しにくくするためにするためのものである。

【0005】

次に、被覆膜の上面にネガ型のドライフィルムレジストをラミネートし、未露光の柱状電極形成用メッキレジスト膜を形成する。次に、露光、現像を行うことにより、上部金属層の接続パッド部つまり柱状電極形成領域に対応する部分における柱状電極形成用メッキレジスト膜および被覆膜に開口部を形成する。次に、下地金属層をメッキ電流路とした銅の電解メッキを行なうことにより、柱状電極形成用メッキレジスト膜および被覆膜の開口部内の上部金属層の接続パッド部上面に柱状電極を形成する。

【0006】

次に、柱状電極形成用メッキレジスト膜およびその下に形成された被覆膜を同時に剥離する。これにより、柱状電極形成用メッキレジスト膜のレジスト残渣が発生しにくくすることができる。次に、上部金属層をマスクとして下地金属層の不要な部分をエッチングして除去すると、上部金属層下にのみ下地金属層が残存される。この状態では、上部金属層およびその下に残存された下地金属層により、2層構造の配線が形成されている。

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、上記従来の半導体装置の製造方法では、半導体基板上の全面に形成された下地金属層の上面に形成された上部金属層間に、柱状電極形成用メッキレジスト膜が入り込まないようにするために、予め、上部金属層の厚さよりも厚い被覆膜を形成しているので、被覆膜を形成する工程が必要となり、工程数が増加するという問題があった。

【0008】

そこで、この発明は、柱状電極形成用メッキレジスト膜のレジスト残渣が発生しにくくすることができ、且つ、工程数を少なくすることができる半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

請求項 1 に記載の発明は、半導体基板上の全面に配線形成用金属膜を形成する工程と、前記配線形成用金属膜上に、柱状電極形成領域に対応する部分に開口部を有する柱状電極形成用メッキレジスト膜を形成する工程と、前記エッチング金属膜をメッキ電流路とした電解メッキを行なうことにより、前記柱状電極形成用メッキレジスト膜の開口部内の前記配線形成用金属膜上に柱状電極を形成する工程と、前記柱状電極形成用メッキレジスト膜を剥離する工程と、前記柱状電極を含む前記配線形成用金属膜上の配線形成領域にエッチングレジスト膜を形成する工程と、前記エッティングレジスト膜をマスクとして前記エッティングレジスト膜下以外の領域における前記配線形成用金属膜をエッティングして除去することにより、前記柱状電極を含む前記エッティングレジスト膜下に配線を形成する工程と、前記エッティングレジスト膜を剥離する工程と、を有することを特徴とするものである。

請求項 2 に記載の発明は、請求項 1 に記載の発明において、前記配線形成用金属膜を形成する工程は、スパッタにより形成されたチタン膜上にスパッタにより銅膜を形成する工程であることを特徴とするものである。

請求項 3 に記載の発明は、請求項 2 に記載の発明において、前記銅膜の厚さは前記チタン膜の厚さよりも厚くすることを特徴とするものである。

請求項 4 に記載の発明は、請求項 3 に記載の発明において、前記配線形成用金属膜の厚

10

20

30

40

50

さは2～5μmとすることを特徴とするものである。

請求項5に記載の発明は、請求項1に記載の発明において、前記柱状電極形成用メッキレジスト膜はドライフィルムレジストで形成することを特徴とするものである。

請求項6に記載の発明は、請求項1に記載の発明において、前記エッチングレジスト膜は液状レジストで形成することを特徴とするものである。

請求項7に記載の発明は、請求項6に記載の発明において、前記エッティングレジスト膜は、スピンドルコート法により形成されたレジスト膜をフォトリソグラフィ法によりパターニングすることにより形成することを特徴とするものである。

請求項8に記載の発明は、請求項6に記載の発明において、前記エッティングレジスト膜はインクジェットプリント法により形成することを特徴とするものである。 10

#### 【発明の効果】

#### 【0010】

この発明によれば、半導体基板上の全面に形成された配線形成用金属膜上に柱状電極形成用メッキレジスト膜を形成しているので、柱状電極形成用メッキレジスト膜の形成面となる配線形成用金属膜の上面の平坦性を極めて高くすることができ、ひいては柱状電極形成用メッキレジスト膜を剥離した際にレジスト残渣が発生しにくくすることができる。また、平坦性が極めて高い配線形成用金属膜の上面に柱状電極形成用メッキレジスト膜を形成しているので、従来のような被覆膜を形成する必要がなく、その分、工程数を少なくすることができます。

#### 【発明を実施するための最良の形態】 20

#### 【0011】

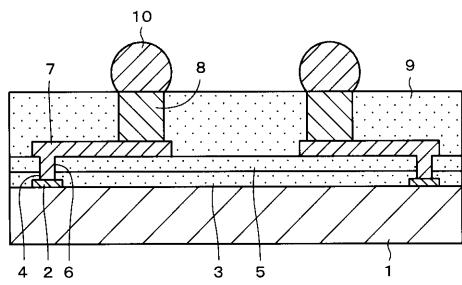

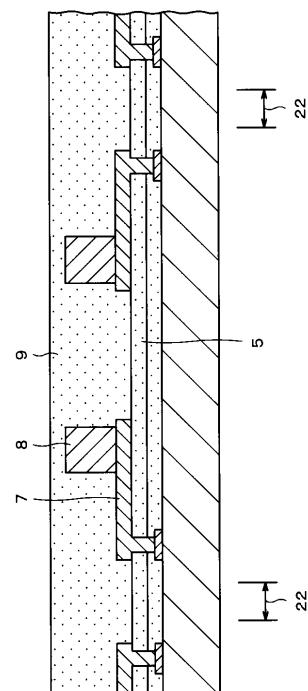

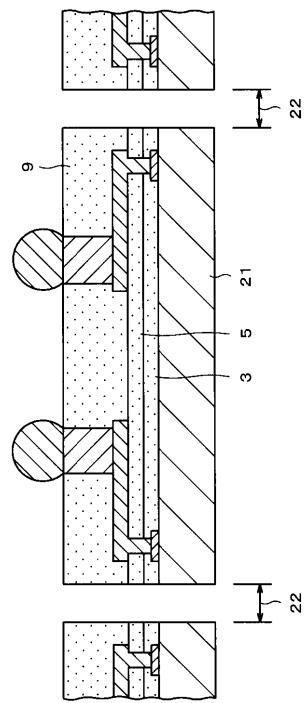

図1はこの発明の製造方法により製造された半導体装置の一例の断面図を示す。この半導体装置は、一般的にはCSPと呼ばれるものであり、シリコン基板（半導体基板）1を備えている。シリコン基板1の上面には集積回路、特に、トランジスタ、ダイオード、抵抗、コンデンサ等の素子（図示せず）が設けられ、上面周辺部には、上記集積回路に接続されたアルミニウム系金属等からなる接続パッド2が設けられている。接続パッド2は2個のみを図示するが実際にはシリコン基板1の上面周辺部に多数配列されている。

#### 【0012】

接続パッド2の中央部を除くシリコン基板1の上面には酸化シリコン等からなる絶縁膜3が設けられ、接続パッド2の中央部は絶縁膜3に設けられた開口部4を介して露出されている。絶縁膜3の上面にはポリイミド系樹脂等からなる保護膜5が設けられている。絶縁膜3の開口部4に対応する部分における保護膜5には開口部6が設けられている。 30

#### 【0013】

保護膜5の上面には配線7が設けられている。配線7は、詳細には図示していないが、保護膜5の上面に設けられたチタン膜と、チタン膜の上面に設けられた銅膜との2層構造となっている。配線7の一端部は、絶縁膜3および保護膜5の開口部4、6を介して接続パッド2に接続されている。

#### 【0014】

配線7の接続パッド部上面には銅からなる柱状電極8が設けられている。配線7を含む保護膜5の上面にはエポキシ系樹脂等からなる封止膜9がその上面が柱状電極8の上面と面一となるように設けられている。柱状電極8の上面には半田ボール10が設けられている。 40

#### 【0015】

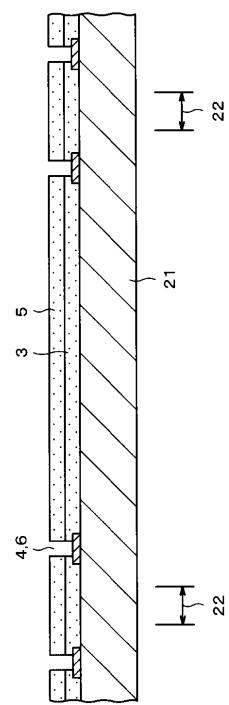

次に、この半導体装置の製造方法の一実施形態について説明する。まず、図2に示すように、ウエハ状態のシリコン基板（以下、半導体ウエハ21という）の上面にアルミニウム系金属等からなる接続パッド2、酸化シリコン等からなる絶縁膜3およびポリイミド系樹脂等からなる保護膜5が形成され、接続パッド2の中央部が絶縁膜3および保護膜5に形成された開口部4、6を介して露出されたものを準備する。なお、図2において、符号22で示す領域はダイシングストリートに対応する領域である。

#### 【0016】 50

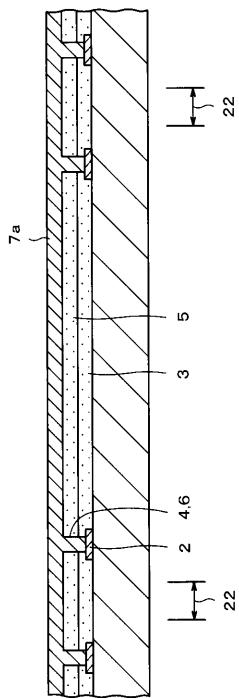

次に、図3に示すように、絶縁膜3および保護膜5の開口部4、6を介して露出された接続パッド2の上面を含む保護膜5の上面全体に配線形成用金属膜7aを形成する。この場合、配線形成用金属膜7aは、詳細には図示していないが、スパッタにより形成されたチタン膜とその上にスパッタにより形成された銅膜との2層構造となっている。また、銅膜はチタン膜よりも厚く形成され、全体としての配線形成用金属膜7aの厚さは2~5μmと比較的厚くなっている。ちなみに、上記特許文献1に記載の下地金属層の場合には、スパッタにより形成されたチタン膜とその上にスパッタにより形成された銅膜との2層構造であっても、その厚さは一般的に1μm以下である。

#### 【0017】

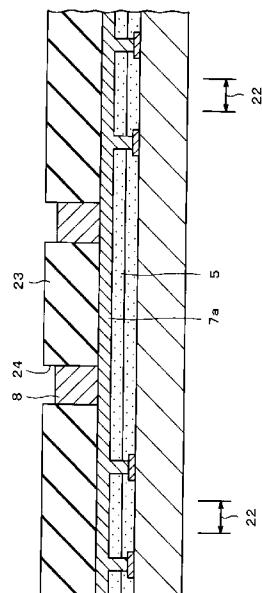

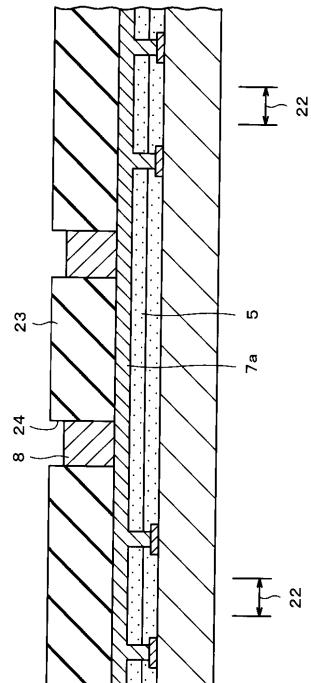

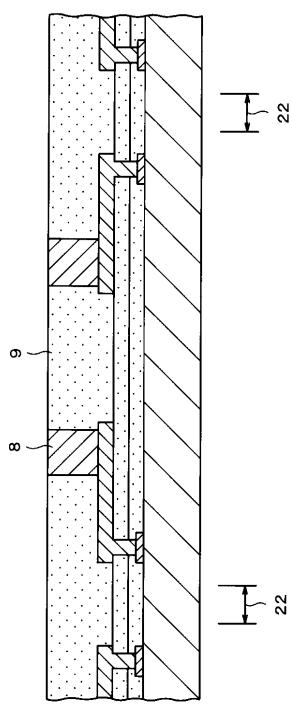

次に、図4に示すように、配線形成用金属膜7aの上面にネガ型のドライフィルムレジストからなる柱状電極形成用メッキレジスト膜23を形成する。この場合、柱状電極8形成領域に対応する部分における柱状電極形成用メッキレジスト膜23には、フォトリソグラフィ法により、開口部24が形成されている。

#### 【0018】

ここで、保護膜5の上面全体に形成された配線形成用金属膜7aの上面の平坦性は極めて高い。このため、配線形成用金属膜7aと柱状電極形成用メッキレジスト膜23との間に空気(気泡)が残存しないようにすることができ、ひいてはこの気泡に起因する柱状電極形成用メッキレジスト膜23の不要な剥離が生じないようにすることができる。

#### 【0019】

次に、配線形成用金属膜7aをメッキ電流路とした銅の電解メッキを行なうことにより、柱状電極形成用メッキレジスト膜23の開口部24内の配線形成用金属膜7aの上面に柱状電極8を形成する。次に、柱状電極形成用メッキレジスト膜23を剥離する。この場合、柱状電極形成用メッキレジスト膜23は平坦性の極めて高い配線形成用金属膜7aの上面に形成されているため、図1に示す配線7間の間隔が狭くなった場合であっても、配線7間に柱状電極形成用メッキレジスト膜23のレジスト残渣が発生することなく、柱状電極形成用メッキレジスト膜23のレジスト残渣に起因する配線7間でのショートの発生を確実に防止することができる。

#### 【0020】

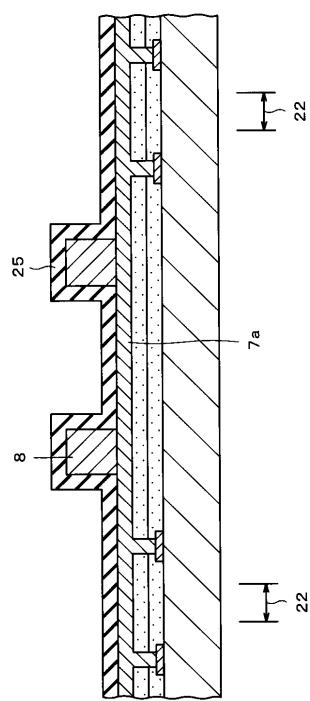

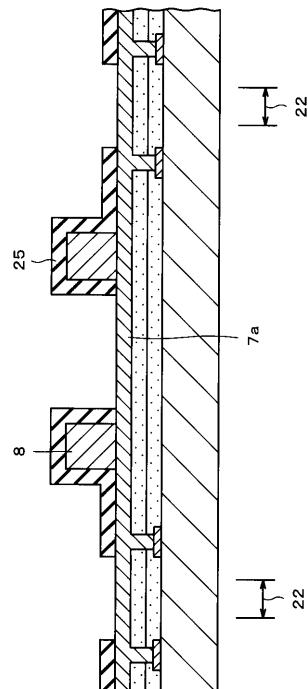

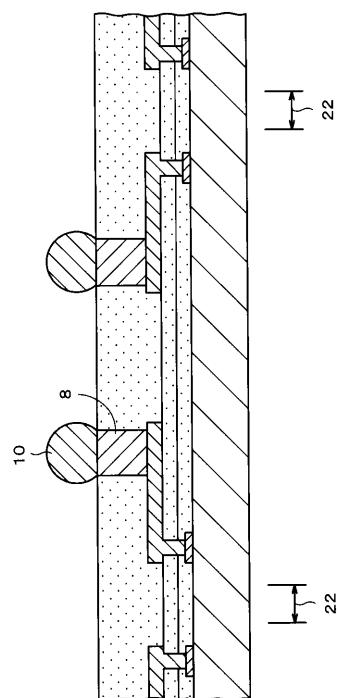

次に、図5に示すように、柱状電極8を含む配線形成用金属膜7aの上面に、スピニコート法等により、液状レジストからなるエッチングレジスト膜25を形成する。次に、図6に示すように、エッチングレジスト膜25をフォトリソグラフィ法によりパターニングすることにより、柱状電極8を含む配線形成用金属膜7aの上面の配線形成領域にエッチングレジスト膜25を残存させる。

#### 【0021】

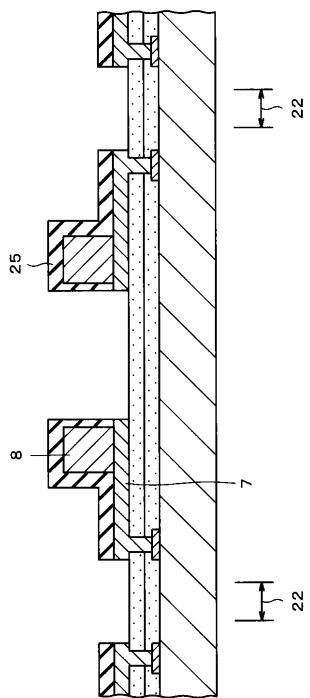

次に、エッチングレジスト膜25をマスクとしてレジスト膜25下以外の領域における配線形成用金属膜7aをエッチングして除去すると、図7に示すように、エッチングレジスト膜25下に配線が形成される。この状態では、配線7の接続パッド部上面には柱状電極8が形成されている。次に、エッチングレジスト膜25を剥離する。

#### 【0022】

ここで、エッチングレジスト膜25は配線形成用金属膜7aをエッチングして配線7を形成するためのものであるので、上記特許文献1に記載の配線用の上部金属層を電解メッキにより形成するためのメッキレジスト膜のような厚さ精度を要求されることはなく、したがって柱状電極8を形成した後であっても、良好に形成することができる。

#### 【0023】

次に、図8に示すように、配線7および柱状電極8を含む保護膜5の上面に、スクリーン印刷法、スピニコート法等により、エポキシ系樹脂等からなる封止膜9をその厚さが柱状電極8の高さよりもやや厚くなるように形成する。したがって、この状態では、柱状電極8の上面は封止膜9によって覆われている。

#### 【0024】

次に、封止膜9の上面側を適宜に研削し、図9に示すように、柱状電極8の上面を露出

10

20

30

40

50

させ、且つ、この露出された柱状電極8の上面を含む封止膜9の上面を平坦化する。次に、図10に示すように、柱状電極8の上面に半田ボール10を形成する。次に、図11に示すように、封止膜9、保護膜5、絶縁膜3および半導体ウエハ21をダイシングストリート22に沿って切断すると、図1に示す半導体装置が複数個得られる。

#### 【0025】

以上のように、この半導体装置の製造方法では、平坦性が極めて高い配線形成用金属膜7aの上面に柱状電極形成用メッキレジスト膜23を形成しているので、従来のような被覆膜を形成する必要がなく、その分、工程数を少なくすることができる。また、配線用の上部金属層を電解メッキにより形成する必要もなく、工程数をより一層少なくすることができる。

10

#### 【0026】

なお、上記実施形態では、エッチングのレジスト膜25を、スピンコート法により形成されたレジスト膜をフォトリソグラフィ法によりパターニングすることにより形成しているが、これに限らず、パターンを直接描画することができるインクジェットプリント法により形成するようにしてもよい。このようにした場合には、フォトリソグラフィ工程が不要となり、工程数をより一層少なくすることができる。

#### 【図面の簡単な説明】

#### 【0027】

【図1】この発明の製造方法により製造された半導体装置の一例の断面図。

【図2】図1に示す半導体装置の製造方法の一実施形態において、当初準備したものとの断面図。

20

【図3】図2に続く工程の断面図。

【図4】図3に続く工程の断面図。

【図5】図4に続く工程の断面図。

【図6】図5に続く工程の断面図。

【図7】図6に続く工程の断面図。

【図8】図7に続く工程の断面図。

【図9】図8に続く工程の断面図。

【図10】図9に続く工程の断面図。

【図11】図10に続く工程の断面図。

30

#### 【符号の説明】

#### 【0028】

1 シリコン基板

2 接続パッド

3 絶縁膜

5 保護膜

7 配線

8 柱状電極

9 封止膜

10 半田ボール

40

21 半導体ウエハ

22 ダイシングストリート

23 柱状電極形成用メッキレジスト膜

25 エッチングレジスト膜

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

フロントページの続き

【要約の続き】

【選択図】 図4