(12)发明专利申请

(10)申请公布号 CN 110277414 A

(43)申请公布日 2019.09.24

(21)申请号 201811274379.X

(22)申请日 2018.10.30

(30)优先权数据

2018-046725 2018.03.14 JP

(71)申请人 株式会社 东芝

地址 日本东京都

申请人 东芝电子元件及存储装置株式会社

(72)发明人 国分弘一

(74)专利代理机构 北京市中咨律师事务所

11247

代理人 张轶楠 段承恩

(51)Int.Cl.

H01L 27/144(2006.01)

H01L 31/107(2006.01)

H01L 31/18(2006.01)

权利要求书2页 说明书5页 附图7页

(54)发明名称

受光装置及受光装置的制造方法

(57)摘要

本公开提供能够不使相邻的受光元件间的串扰劣化地提高受光灵敏度的受光元件。根据实施方式，受光装置具备：设置在半导体基板的第一主面上且以第一浓度被导入第一导电型杂质的第一半导体层；设置于第一主面上的第一半导体层间的绝缘膜；设置于第一半导体层的光电变换元件；设置在第一主面侧的绝缘膜上的第一电极；以及设置在半导体基板的与第一主面相对的第二主面上的第二电极。光电变换元件具有：设置于距离第一半导体层的配置第一电极侧的上表面为预定深度处且以第二浓度被导入第二导电型杂质的第二半导体层；和设置成在第一半导体层内包围第二半导体层的侧面及下表面且以比第一浓度高的第三浓度被导入第一导电型杂质的第三半导体层。

1.一种受光装置,具备:

第一半导体层,其设置在半导体基板的第一主面上,以第一浓度被导入第一导电型杂质;

绝缘膜,其设置于所述第一主面上的所述第一半导体层之间;

光电变换元件,其设置于所述第一半导体层;

第一电极,其设置在所述第一主面侧的所述绝缘膜上;以及

第二电极,其设置在所述半导体基板的与所述第一主面相对的第二主面上,

所述光电变换元件具有:

第二半导体层,其设置于距离所述第一半导体层的配置所述第一电极的一侧的上表面为预定深度处,以第二浓度被导入第二导电型杂质;和

第三半导体层,其设置成在所述第一半导体层内包围所述第二半导体层的侧面以及下表面,以比所述第一浓度高的第三浓度被导入所述第一导电型杂质。

2.根据权利要求1所述的受光装置,

在俯视时所述第一半导体层、所述第二半导体层以及所述第三半导体层呈矩形形状。

3.根据权利要求1所述的受光装置,

在俯视时所述第一半导体层、所述第二半导体层以及所述第三半导体层呈具有带圆弧的角部的矩形形状。

4.根据权利要求1所述的受光装置,

在俯视时所述第一半导体层、所述第二半导体层以及所述第三半导体层呈圆形形状。

5.根据权利要求1所述的受光装置,

在俯视时所述第一半导体层、所述第二半导体层以及所述第三半导体层呈椭圆形形状。

6.根据权利要求1所述的受光装置,

所述第一导电型是P型,

所述第二导电型是N型。

7.根据权利要求1所述的受光装置,

所述第一导电型是N型,

所述第二导电型是P型。

8.根据权利要求1所述的受光装置,

所述第一半导体层、所述第二半导体层以及所述第三半导体层由外延膜构成。

9.根据权利要求1所述的受光装置,

所述光电变换元件是以盖革模式工作的雪崩光电二极管。

10.根据权利要求1所述的受光装置,

所述光电变换元件的阴极经由淬灭电阻与电极膜电连接。

11.根据权利要求4所述的受光装置,

所述半导体基板是单晶硅基板,

所述第一半导体层、所述第二半导体层以及所述第三半导体层是硅的外延膜。

12.一种受光装置,具备:

第一半导体层,其设置在半导体基板的第一主面上,以第一浓度被导入第一导电型杂质;

绝缘膜，其设置于所述第一主面上的所述第一半导体层之间；

光电变换元件，其设置于所述第一半导体层；

第一电极，其设置在所述第一主面侧的所述绝缘膜上；以及

第二电极，其设置在所述半导体基板的与所述第一主面相对的第二主面上，

所述光电变换元件具有：

第二半导体层，其从所述第一半导体层的顶部高度延伸至俯视时比所述第一半导体层的形成范围窄的第一深度，具有比所述第一浓度高的第二浓度的所述第一导电型杂质；和

第三半导体层，其从所述第二半导体层的高度延伸至比所述第一深度浅且俯视时比所述第二半导体层的形成范围窄的第二深度，侧面和底面被所述第二半导体层包围，具有第三浓度的第二导电型杂质。

13.一种受光装置的制造方法，包括：

在半导体基板上形成绝缘膜的工序；

在所述绝缘膜形成到达至所述半导体基板为止的开口部的工序；

在所述开口部内形成以第一浓度包含第一导电型杂质的第一半导体层的工序；

在从所述第一半导体层的上表面到第一深度为止的范围内，向俯视时比所述第一半导体层的形成范围窄的范围，以比所述第一浓度高的第二浓度导入所述第一导电型杂质而形成第二半导体层的工序；以及

在从所述第二半导体层的上表面到比所述第一深度浅的第二深度为止的范围内，向俯视时比所述第二半导体层的形成范围窄的范围，以第三浓度导入第二导电型杂质而形成第三半导体层的工序。

## 受光装置及受光装置的制造方法

[0001] 本申请享有以日本专利申请2018-046725号(申请日:2018年3月14日)为在先申请的优先权。本申请通过参照该在先申请而包括该在先申请的全部内容。

### 技术领域

[0002] 本发明的实施方式涉及受光装置以及受光装置的制造方法。

### 背景技术

[0003] 以往公开了一种将淬灭电阻(quenching resistor)以及雪崩光电二极管(以下称作APD)的串联连接进行并联连接来计测所入射的光子的个数的受光装置。由于APD由硅(Si)构成,所以被称作SiPM(Silicon Photomultipliers:硅光电倍增管)。在这样的受光装置中,期望在不使相邻的APD间的串扰(crosstalk)劣化的同时提高受光灵敏度。

### 发明内容

[0004] 本发明的一个实施方式的目的在于提供,能够不使相邻的受光元件间的串扰劣化地提高受光灵敏度的受光元件以及受光装置的制造方法。

[0005] 根据本发明的一个实施方式,提供一种受光装置,该受光装置具备:第一半导体层,其设置在半导体基板的第一主面上,以第一浓度被导入第一导电型杂质;绝缘膜,其设置于所述第一主面上的所述第一半导体层之间;光电变换元件,其设置于所述第一半导体层;第一电极,其设置在所述第一主面侧的所述绝缘膜上;以及第二电极,其设置在所述半导体基板的与所述第一主面相对的第二主面上。所述光电变换元件具有:第二半导体层,其设置于距离所述第一半导体层的配置所述第一电极的一侧的上表面为预定深度处,以第二浓度被导入第二导电型杂质;和第三半导体层,其设置成在所述第一半导体层内包围所述第二半导体层的侧面以及下表面,以比所述第一浓度高的第三浓度被导入所述第一导电型杂质。

[0006] 根据上述结构的受光装置,能够增加有效的PN结的面积,提高受光灵敏度。

### 附图说明

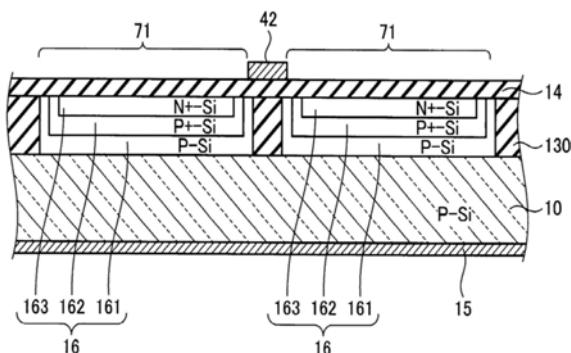

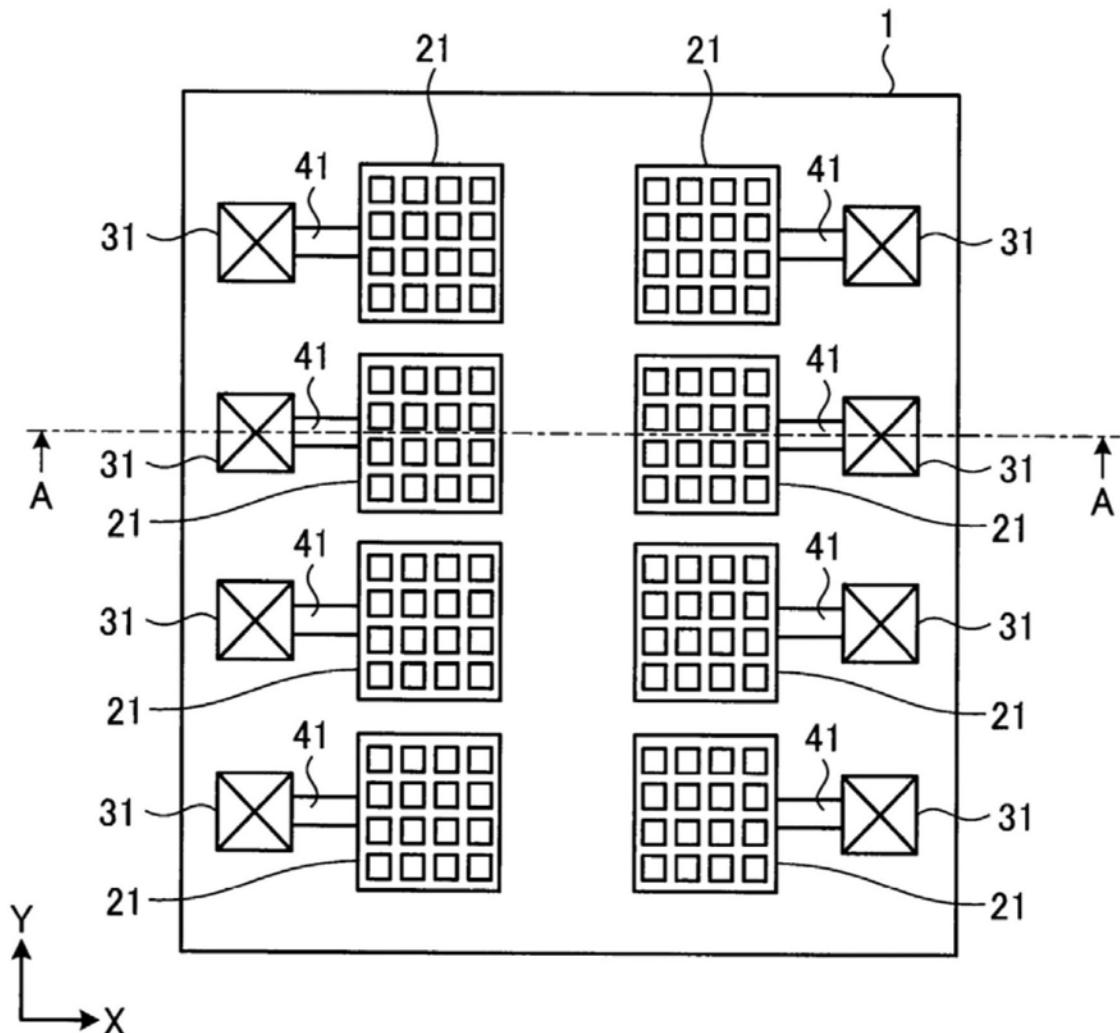

[0007] 图1是示意性地示出第一实施方式的受光装置的结构的一例的俯视图。

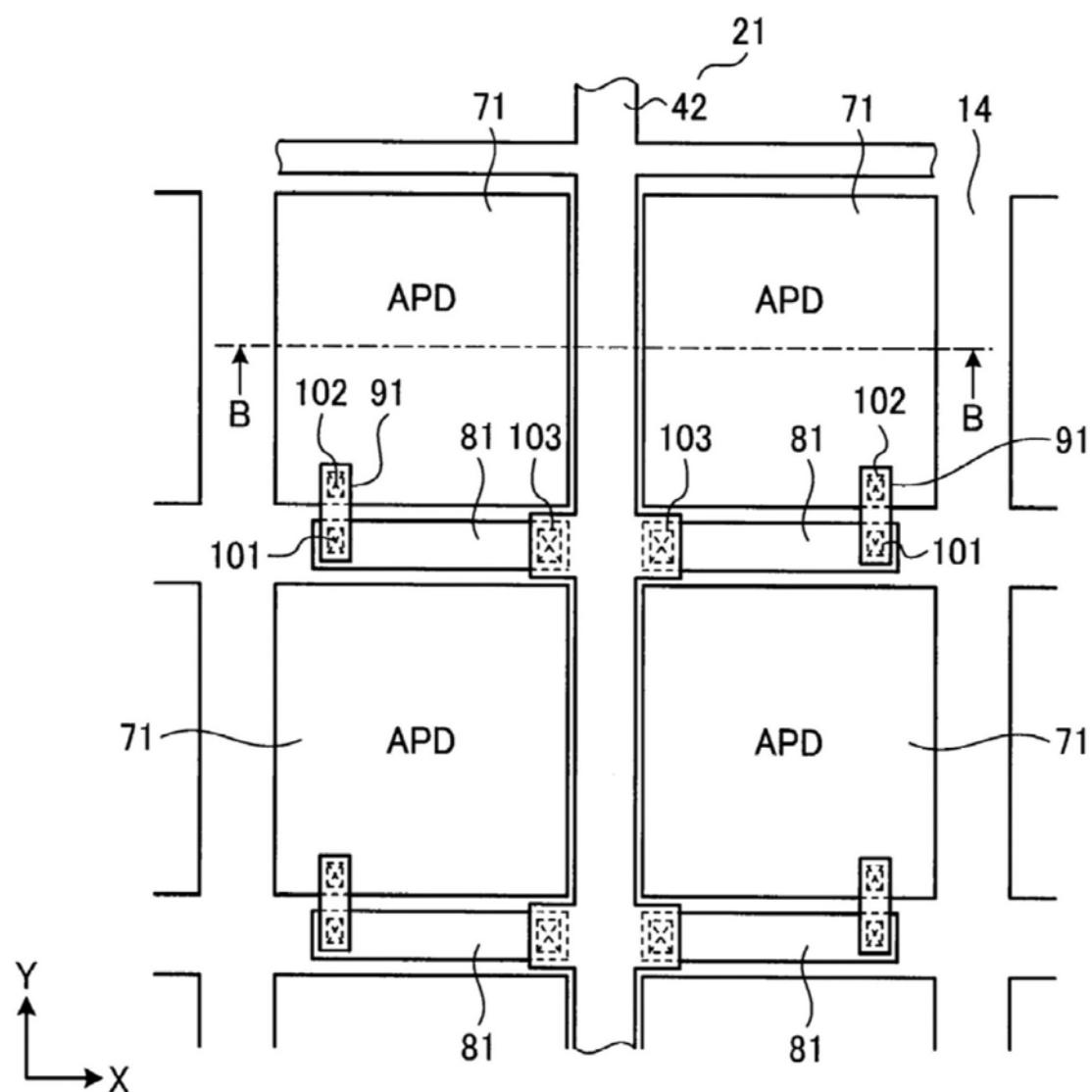

[0008] 图2是示意性地示出第一实施方式的受光装置的结构的一例的截面图,且是图1的A-A截面图。

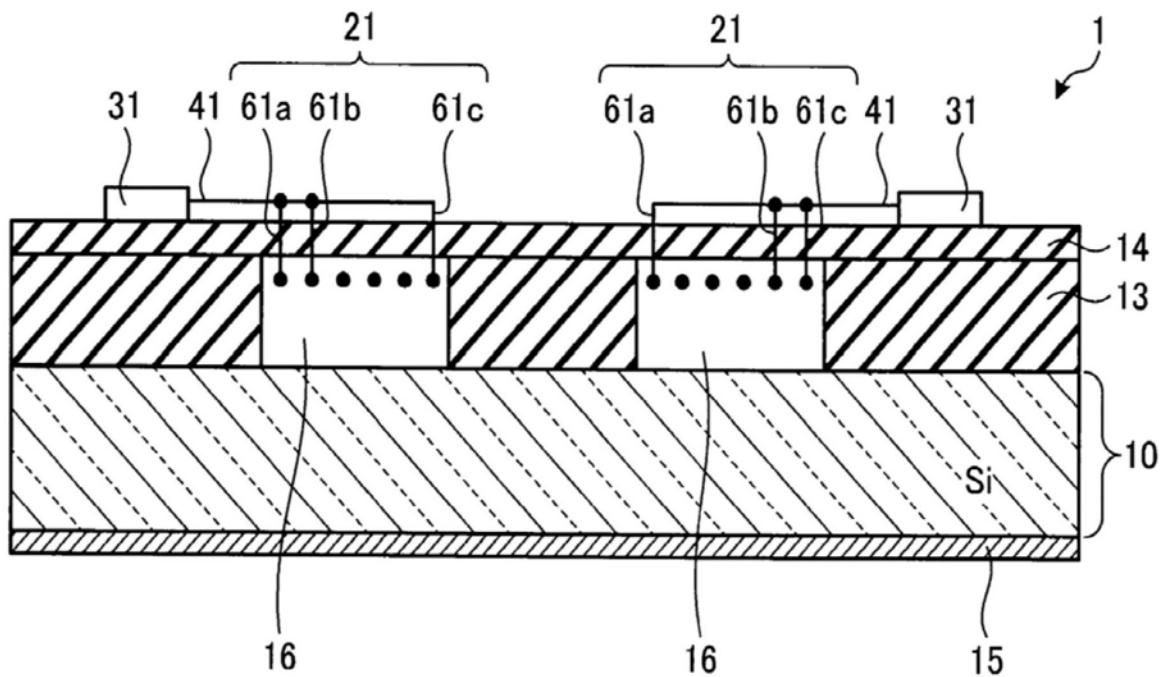

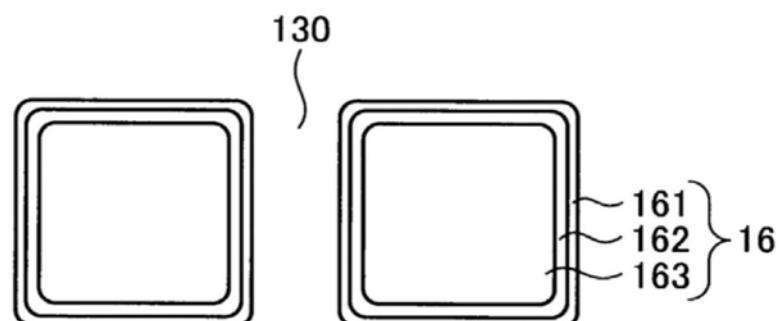

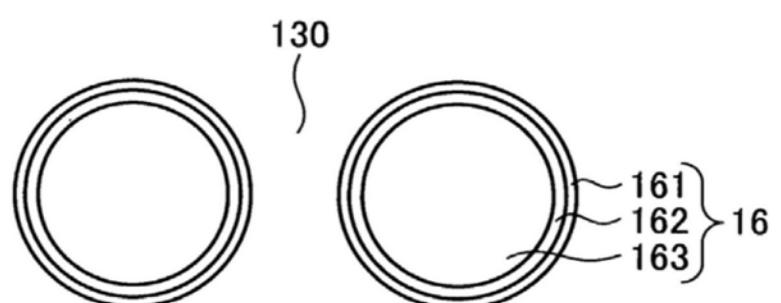

[0009] 图3是示意性地示出第一实施方式的受光装置的像素区域的一部分的俯视图。

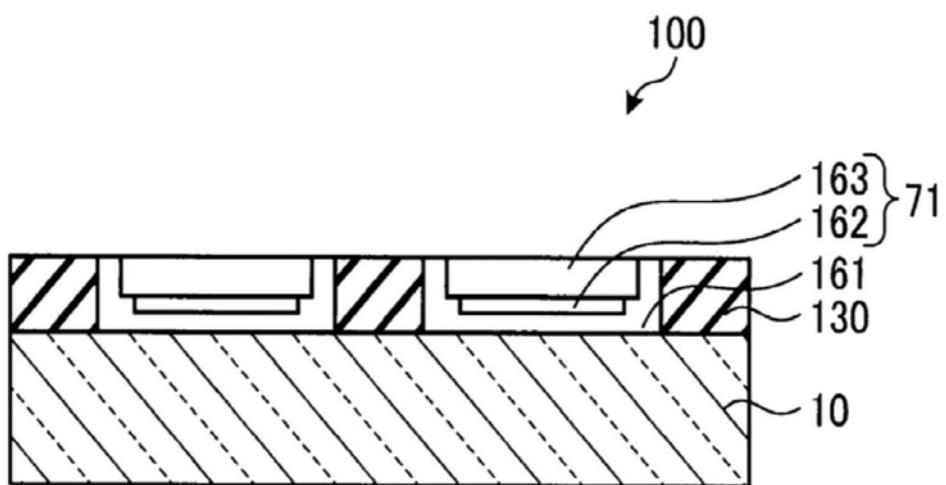

[0010] 图4是示意性地示出第一实施方式的受光装置的截面构造的图,且是图3的B-B截面图。

[0011] 图5是示出第一实施方式的受光装置的一部分的等效电路的图。

[0012] 图6是示意性地示出第一实施方式的受光装置的制造方法的一例的截面图。

[0013] 图7是示意性地示出比较例的受光装置的像素区域的一部分的俯视图。

- [0014] 图8是示意性地示出比较例的受光装置的截面构造的图，且是图7的C-C截面图。

- [0015] 图9是示意性地示出第二实施方式的受光装置的像素区域的一部分的俯视图。

- [0016] 附图标记的说明

- [0017] 1受光装置；10硅基板；13、130分离膜；14保护膜；15金属膜；16Si外延层；21像素区域；31电极焊盘；41布线；42电极膜；61a～61c布线；81淬灭电阻；91布线；101～103连接部；131绝缘膜；141抗蚀剂图案；150阳极电极；151阳极布线；161P型Si外延层；162P+型Si外延层；163N+型Si外延层；300开口。

## 具体实施方式

[0018] 以下，参照附图对实施方式涉及的受光元件以及受光装置的制造方法进行详细说明。此外，本发明不受这些实施方式限定。另外，在以下的实施方式中使用的受光装置的截面图是示意图，层的厚度与宽度的关系和/或各层的厚度的比率等有时与实际情况不同。

[0019] (第一实施方式)

[0020] 图1是示意性地示出第一实施方式的受光装置的结构的一例的俯视图。图2是示意性地示出第一实施方式的受光装置的结构的一例的截面图，且是图1的A-A截面图。受光装置1具有在硅基板10上形成有多个光电变换元件的多个像素区域21。例如，像素区域21二维地配置在硅基板10的主表面内。硅基板10例如能够使用单晶基板。

[0021] 各像素区域21具有被供给来自光电变换元件的输出信号的电极焊盘31。像素区域21以及电极焊盘31分别通过布线41连接。电极焊盘31例如是通过接合线(bonding wire) (未图示)与外部电极连接的接合焊盘(bonding pad)。

[0022] 像素区域21形成于在硅基板10的表面(以下也称作受光面)上设置的Si外延层16。在各像素区域21之间设置分离膜13。作为分离膜13，例如可以使用硅氧化膜。在各像素区域21的表面设置保护膜14。作为保护膜14，例如可以使用硅氧化膜。在各像素区域21设置多个光电变换元件。各光电变换元件经由布线61a～61c与各自的布线41连接。

[0023] 在硅基板10的背面形成金属膜15。金属膜15具有作为将所入射的光向像素区域21侧反射的反射膜的功能。由金属膜15反射后的光到达像素区域21，由此能够提高光电变换元件的灵敏度。另外，金属膜15具有作为各光电变换元件的共同电极、此处为阳极电极的功能。作为金属膜15，例如可以使用铝、铜、金等。

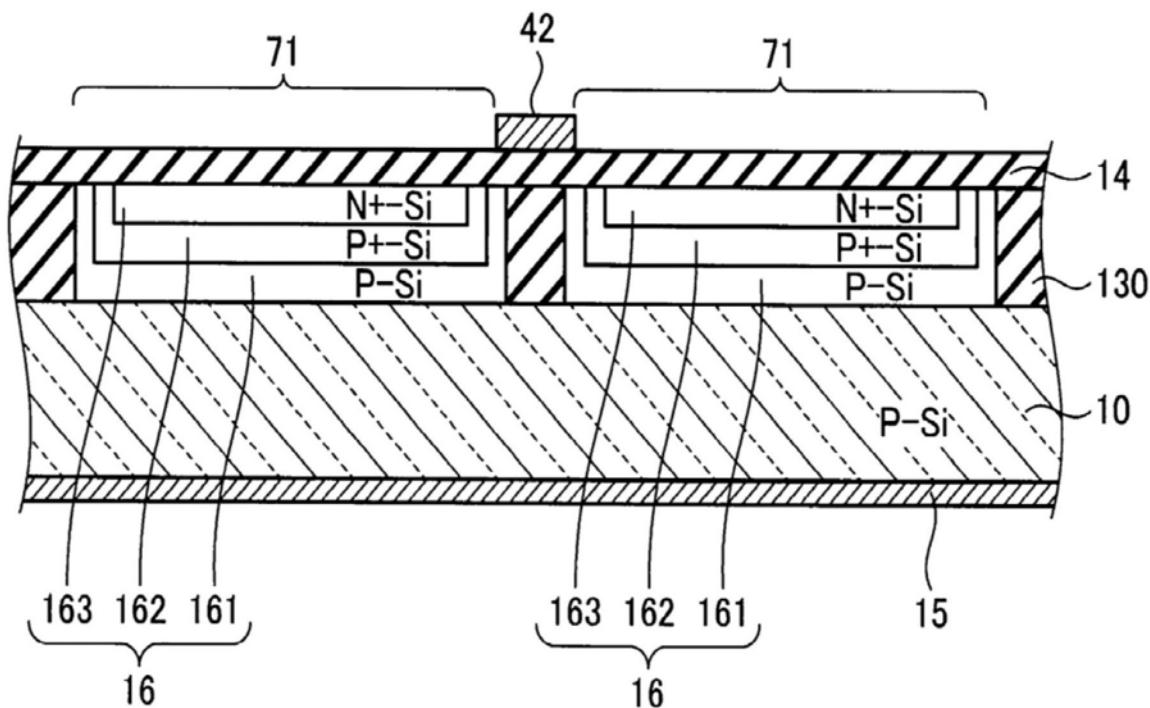

[0024] 图3是示意性地示出第一实施方式的受光装置的像素区域的一部分的俯视图。图4是示意性地示出第一实施方式的受光装置的截面构造的图，且是图3的B-B截面图。在像素区域21的P型硅基板10上设置P型Si外延层161，在P型Si外延层161内设置光电变换元件71。光电变换元件71是以盖革模式工作的APD。在盖革模式下向各APD的阳极与阴极间施加比击穿电压高的反向偏置电压。

[0025] 光电变换元件71具有设置在P型Si外延层161内的P+型Si外延层162和设置在P+型Si外延层162内的N+型Si外延层163。P+型Si外延层162以及N+型Si外延层163构成光电变换元件71的PN结。P+型Si外延层162的P型杂质浓度比P型Si外延层161的P型杂质浓度高。P型Si外延层161的P型杂质浓度为例如 $1 \times 10^{15}/\text{cm}^3$ ，P+型Si外延层162的P型杂质浓度的峰值浓度为 $7 \times 10^{16}/\text{cm}^3$ ，N+型Si外延层163的N型杂质浓度的峰值浓度为 $1 \times 10^{19}/\text{cm}^3$ 。P型Si外延层161、P+型Si外延层162以及N+型Si外延层163构成Si外延层16。

[0026] 如图3所示,光电变换元件71在俯视时具有矩形形状,二维地配置在硅基板10上。由于是矩形形状的相同图案,所以能够在预定面积内配置更多的光电变换元件71。如图4所示,在硅基板10上的相邻的光电变换元件71间设置分离膜130。分离膜130也可以由与像素区域21间分离的分离膜13相同的材料构成,例如由硅氧化膜构成。相邻的光电变换元件71间的距离、即分离膜130的宽度能够设为在相邻的光电变换元件71产生的次级光子(日语:2次光子)衰减而不会到达的程度的距离。在光电变换元件71上以及分离膜130上设置保护膜14。

[0027] 如图4所示,N+型Si外延层163的上表面与保护膜14接触,另一表面与P+型Si外延层162接触。这样,通过增加PN结面积,能够提高受光灵敏度。

[0028] 在图3的例子中,在沿X方向延伸的保护膜14上的一部分设置淬灭电阻81。淬灭电阻81具有在光子入射至APD而产生了电子雪崩的情况下利用其电压下降来使APD的增倍作用终止的作用。淬灭电阻81的电阻值例如设定为几百k $\Omega$ 左右。淬灭电阻81例如由多晶硅构成。

[0029] 另外,在沿Y方向延伸的保护膜14上的一部分设置电极膜42。电极膜42经由各淬灭电阻81与各光电变换元件71的N+型Si外延层163连接。具体而言,设置从各淬灭电阻81的一端延伸至光电变换元件71上的保护膜14的布线91。布线91的一方的端部经由连接部101与各淬灭电阻81的一端连接。布线91的另一方的端部与设置于光电变换元件71上的保护膜14的、到达N+型Si外延层163的过孔等连接部102连接。过孔例如由金属材料构成。电极膜42经由连接部103与各淬灭电阻81的另一端连接。电极膜42具有作为光电变换元件71的阴极电极的功能。此外,如上所述,在硅基板10的背面侧形成作为阳极电极的金属膜15。

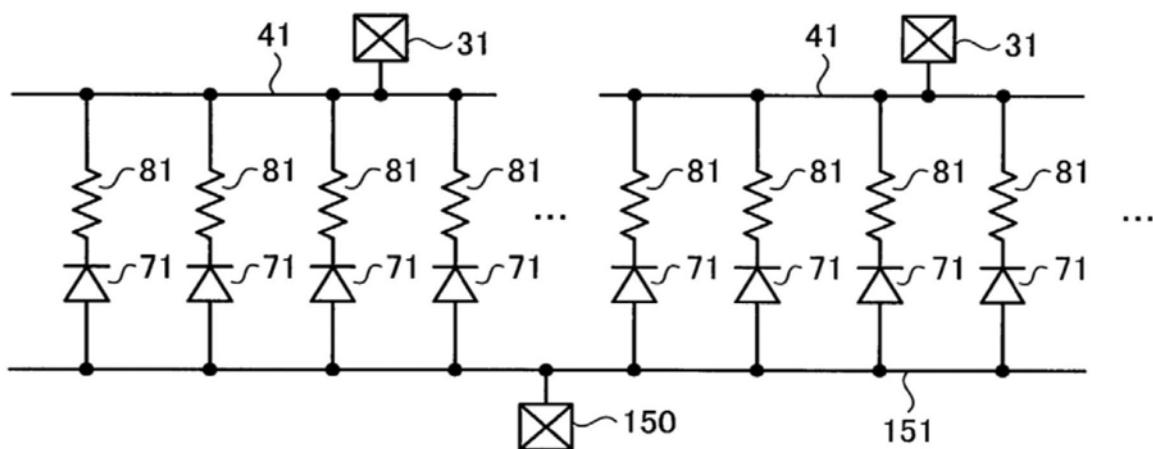

[0030] 图5是示出第一实施方式的受光装置的一部分的等效电路的图。各光电变换元件71的阳极经由阳极布线151与阳极电极150连接。图2以及图4所示的金属膜15作为阳极布线151使用。此外,阳极布线151在各像素区域21是共同的。

[0031] 各个像素区域21内的光电变换元件71的阴极经由各淬灭电阻81与按各像素区域21设置的布线41连接。布线41与电极焊盘31电连接。

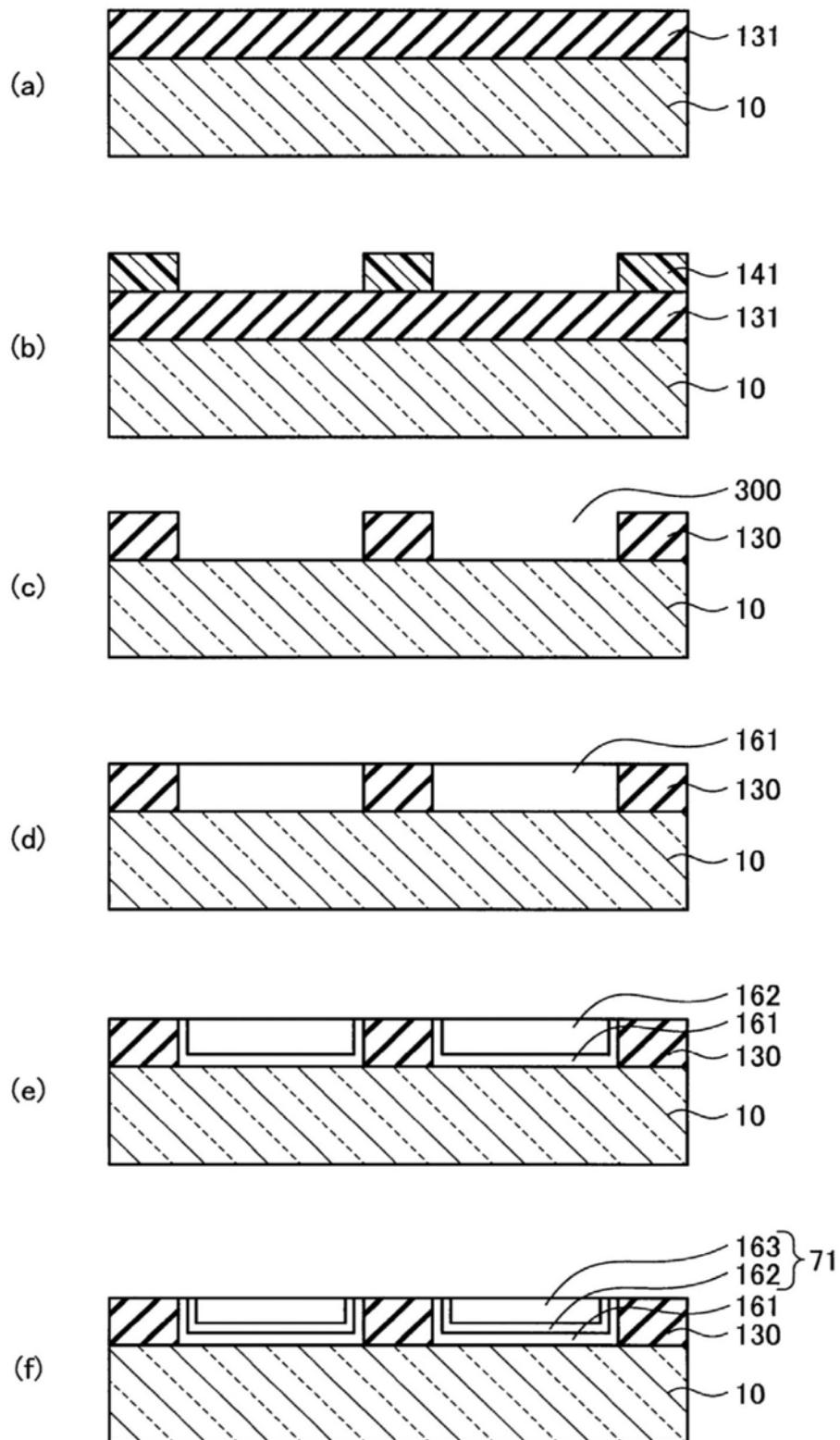

[0032] 接着,对这样的结构的受光装置1的制造方法进行说明。图6是示意性地示出第一实施方式的受光装置的制造方法的一例的截面图。首先,如图6的(a)所示,在硅基板10的主要表面,例如通过化学气相沉积(CVD, Chemical Vapor Deposition)法等成膜法形成绝缘膜131。作为绝缘膜131,能够使用硅氧化膜等。

[0033] 接下来,在绝缘膜131上涂覆抗蚀剂。之后,如图6的(b)所示,通过光刻技术在抗蚀剂中对使光电变换元件71的形成区域开了口的图案进行曝光、显影,形成抗蚀剂图案141。

[0034] 接下来,如图6的(c)所示,将抗蚀剂图案141作为掩模,并通过反应离子蚀刻(RIE, Reactive Ion Etching)法等各向异性蚀刻对绝缘膜131进行蚀刻。由此,形成在俯视时具有矩形形状的开口300。如上所述,开口300成为形成光电变换元件71的区域。此外,在像素区域21内,绝缘膜131成为分离膜130,在像素区域21间,绝缘膜131成为分离膜13。

[0035] 在除去抗蚀剂图案141后,如图6的(d)所示,在通过开口300露出的硅基板10的主要表面上,例如通过CVD法来选择性地形成P型Si外延层161。作为载气能够使用氢气(H<sub>2</sub>),作为气体种类,例如能够使用二氯硅烷(SiH<sub>2</sub>Cl<sub>2</sub>)、氯化氢(HCl),作为P型掺杂气体,能够使用乙硼烷(B<sub>2</sub>H<sub>6</sub>)。P型Si外延层161的P型杂质浓度例如为1×10<sup>15</sup>/cm<sup>3</sup>。

[0036] 接下来,如图6的(e)所示,通过离子注入法,进一步向P型Si外延层161导入P型杂质,形成P+型Si外延层162。例如,以使P型杂质浓度的峰值浓度成为 $7 \times 10^{16}/\text{cm}^3$ 的方式将P等P型杂质进行离子注入。P+型Si外延层162形成于比P型Si外延层161浅的区域并且形成为与P型Si外延层161相同或比P型Si外延层161窄的区域。

[0037] 进而,如图6的(f)所示,通过离子注入法,向P+型Si外延层162内导入N型杂质,形成N+型Si外延层163。例如,以使N型杂质浓度的峰值浓度为 $1 \times 10^{19}/\text{cm}^3$ 的方式将P、As等N型杂质进行离子注入。另外,N+型Si外延层163形成于比P+型Si外延层162浅的区域并且形成为比P+型Si外延层162窄的区域。

[0038] 之后,通过对硅基板10进行热处理,使导入至P型Si外延层161、P+型Si外延层162以及N+型Si外延层163的P型杂质以及N型杂质活性化。由此,在各开口300形成具有PN结的光电变换元件71。

[0039] 接下来,在形成有光电变换元件71的硅基板10上形成保护膜14。作为保护膜14,例如可以使用硅氧化膜等。之后,在分离膜130上的预定位置,经由保护膜14形成成为淬灭电阻81的多晶硅膜。另外,当在形成有N+型Si外延层163的区域内的保护膜14形成到达至N+型Si外延层163的接触孔后,在保护膜14上的整面形成导电层。之后,以在分离膜130上的预定位置以及将接触孔和淬灭电阻81连接的预定位置残留导电膜的方式进行图案化。由此,形成电极膜42和布线91。而且,通过在硅基板10的背面的整面形成成为阳极布线的金属膜15,能够得到图1~图3所示的受光装置1。

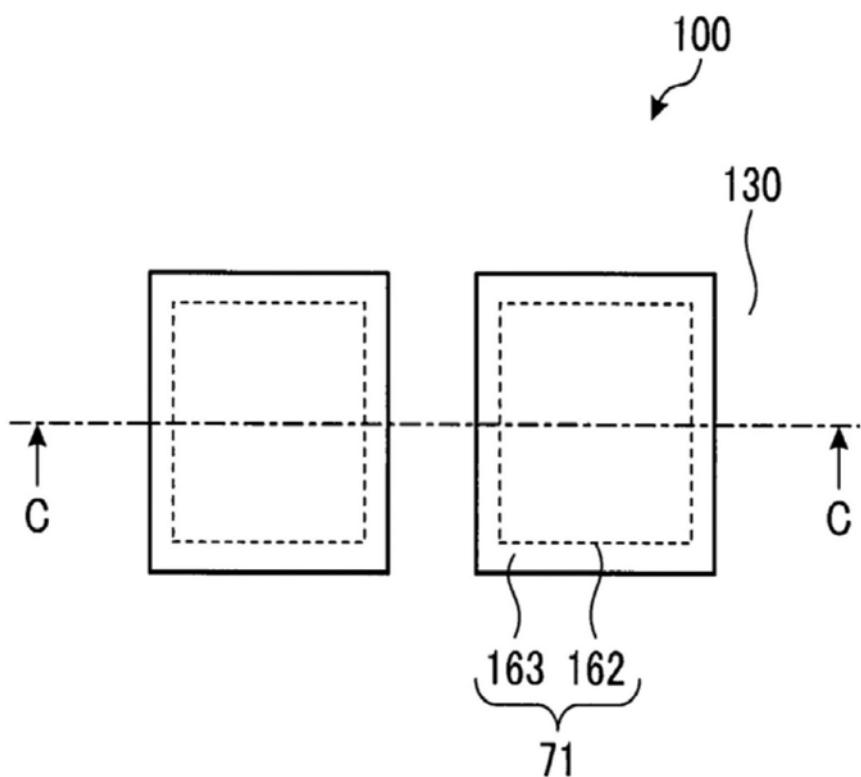

[0040] 图7是示意性地示出比较例的受光装置的像素区域的一部分的俯视图。图8是示意性地示出比较例的受光装置的截面构造的图,且是图7的C-C截面图。此外,此处省略了形成于比光电变换元件靠上的保护膜和阴极布线等布线层。

[0041] 在比较例中,在P型硅基板10上配置P型Si外延层161,在P型Si外延层161形成光电变换元件71。与第一实施方式同样地,在光电变换元件71间设置有由硅氧化膜等构成的分离膜130。光电变换元件71具有设置于距离P型Si外延层161的上表面预定深度处的P+型Si外延层162、和与P+型Si外延层162的上表面接触且设置于比P+型Si外延层162靠上的N+型Si外延层163。P+型Si外延层162与N+型Si外延层163相比,基板面内方向的尺寸较小。另外,P+型Si外延层162与N+型Si外延层163仅在上表面接触。

[0042] 在受光装置1中,期望尽量提高SN比。于是,在比较例的受光装置100中,为了提高灵敏度,考虑提高开口率来增加受光面积。为增加受光面积,要增加P+型Si外延层162的基板面内方向的尺寸。但是,这样一来,相邻的光电变换元件71间的距离、即配置于光电变换元件71间的分离膜130的宽度变小。若分离膜130的宽度变小,则当在某光电变换元件71产生次级光子时,次级光子会向相邻的其它光电变换元件71入射。也就是说,在与产生了次级光子的光电变换元件71相邻的其它光电变换元件71中,检测次级光子的串扰会劣化,噪声变高。结果,仅提高开口率,无法提高SN比。这样,在比较例的受光装置100中,难以减少噪声。

[0043] 与此相对,在第一实施方式中,设为以包围N+型Si外延层163的侧面以及下表面的方式配置有P+型Si外延层162的光电变换元件71。这样,比较例中的有效的PN结是面积较小的P+型Si外延层162的上表面与N+型Si外延层163的下表面接触的部分,与此相对,第一实施方式的有效的PN结的面积增加。结果,与比较例相比,能够提高受光灵敏度。另外,通过提

高受光灵敏度，也可以不减小相邻的光电变换元件71间的距离，因此也能够不使串扰劣化。

[0044] 此外，由于以包围N+型Si外延层163的侧面以及下表面的方式配置有P+型Si外延层162，所以与不以包围P+型Si外延层162的侧面以及下表面的方式配置N+型Si外延层163的情况相比，能够提高受光灵敏度。尤其是，若增加N+型Si外延层163的膜厚，则受光面增加，因此能够进一步提高受光灵敏度。

[0045] (第二实施方式)

[0046] 在第一实施方式中，举出了光电变换元件的俯视时的形状为矩形形状的情况为例，但光电变换元件的俯视时的形状不限定于上述例子的情况。在第二实施方式中，举出光电变换元件的俯视时的形态为其它形状的情况为例。

[0047] 图9是示意性地示出第二实施方式的受光装置的像素区域的一部分的俯视图。图9的(a)中，P型Si外延层161、P+型Si外延层162以及N+型Si外延层163均呈角部带圆弧的矩形形状。另外，在图9的(b)中，P型Si外延层161、P+型Si外延层162以及N+型Si外延层163均呈圆形形状。此外，除此处所示的形状以外，P型Si外延层161、P+型Si外延层162以及N+型Si外延层163还可以呈椭圆形状。此外，其它结构与第一实施方式相同，从而省略其说明。

[0048] 如第一实施方式所示，在光电变换元件71的俯视时的形状呈矩形形状的情况下，在角部会产生电场集中。但是，在第二实施方式中，在Si外延层16的形状中，形成为角部带圆弧的矩形形状或者圆形形状、椭圆形状，所以能够在第一实施方式的效果的基础上还获得与第一实施方式相比能够抑制电场集中这一效果。

[0049] 此外，在上述的说明中，以包围N+型Si外延层163的侧面以及下表面的方式配置有P+型Si外延层162，但也可以以包围P+型Si外延层162的侧面以及下表面的方式配置N+型Si外延层163。

[0050] 对几个实施方式进行了说明，但是这些实施方式仅作为示例提出，并非用于限定发明范围。这些新的实施方式可以通过其他各种形态实施，在不脱离发明要旨的范围内能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明范围、要旨内，并且包含在权利要求范围所记载的发明及其等同的范围内。

图1

图2

图3

图4

图5

图6

图7

图8

(a)

(b)

图9