(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6478621号

(P6478621)

(45) 発行日 平成31年3月6日(2019.3.6)

(24) 登録日 平成31年2月15日(2019.2.15)

|              |           |           |      |

|--------------|-----------|-----------|------|

| (51) Int.Cl. | F 1       |           |      |

| G09G 5/00    | (2006.01) | G09G 5/00 | 520V |

| G09G 5/391   | (2006.01) | H04N 5/66 | A    |

| H04N 5/66    | (2006.01) | G09G 5/00 | 555W |

| G09G 5/397   | (2006.01) | G09G 5/36 | 520L |

| G09G 5/399   | (2006.01) | G09G 5/18 |      |

請求項の数 6 (全 11 頁) 最終頁に続く

(21) 出願番号 特願2014-258251 (P2014-258251)

(22) 出願日 平成26年12月22日 (2014.12.22)

(65) 公開番号 特開2016-118660 (P2016-118660A)

(43) 公開日 平成28年6月30日 (2016.6.30)

審査請求日 平成29年12月15日 (2017.12.15)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 伊藤 靖

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

審査官 橋本 直明

最終頁に続く

(54) 【発明の名称】 画像処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

入力画像データを水平方向に 2つに分割して得られる2つの画像データのうち第1画像データを記憶する第1記憶手段と、

前記2つの画像データのうち前記第1画像データと異なる第2画像データを記憶する第2記憶手段と、

前記第1記憶手段及び前記第2記憶手段から前記第1画像データの水平ラインと前記第2画像データの水平ラインを交互に読み出し、読み出した水平ラインを垂直方向に合成した合成画像データを生成する合成手段と、

前記合成画像データを前記入力画像データの形式の出力画像データに変換する変換手段であって、前記合成画像データのうち、前記入力画像データにおいて同じ水平ラインに対応する複数の水平ラインが前記出力画像データの1つの水平ラインに変換されるように前記合成画像データを変換する変換手段と、

を備えることを特徴とする画像処理装置。

## 【請求項 2】

入力画像データを水平方向に 2つに分割して得られる2つの画像データのうち第1画像データを記憶する第1記憶手段と、

前記2つの画像データのうち前記第1画像データと異なる第2画像データを記憶する第2記憶手段と、

前記第1記憶手段及び前記第2記憶手段から前記第1画像データの水平ラインの半分と

10

20

前記第2画像データの水平ラインの半分を交互に読み出し、読み出した前記第1画像データ及び前記第2画像データの水平ラインの半分を水平方向に合成した複数の合成水平ラインを、垂直方向に合成した合成画像データを生成する合成手段と、

前記合成画像データを前記入力画像データの形式の出力画像データに変換する変換手段であって、前記合成画像データのうち、前記入力画像データにおいて同じ水平ラインに対応する複数の前記合成水平ラインが前記出力画像データの1つの水平ラインに変換されるように前記合成画像データを変換する変換手段と、

を備えることを特徴とする画像処理装置。

### 【請求項3】

前記第1画像データの水平画素数、前記第2画像データの水平画素数、および前記合成画像データの水平画素数は、前記入力画像データの水平画素数の半分の画素数であることを特徴とする請求項1または2に記載の画像処理装置。 10

### 【請求項4】

前記合成手段は、前記合成画像データに第1の同期信号を付加して出力し、

前記変換手段は、前記出力画像データに第2の同期信号を付加して出力することを特徴とする請求項1乃至3のいずれか1項に記載の画像処理装置。

### 【請求項5】

前記入力画像データは、4K画像データであり、

前記合成手段は、2K画像データに対応した前記第1の同期信号を前記合成画像データに付加して出力し、 20

前記変換手段は、前記出力画像データに前記4K画像データに対応した前記第2の同期信号を付加して出力する

ことを特徴とする請求項4に記載の画像処理装置。

### 【請求項6】

前記入力画像データおよび前記出力画像データは、デジタル映像信号形式のデータであることを特徴とする請求項1乃至5のいずれか1項に記載の画像処理装置。 30

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、画像処理装置に関する。

#### 【背景技術】

#### 【0002】

従来、デジタルテレビやビデオカメラ等、1画面の有効画素数が水平1920画素×垂直1080画素の画像（以下、「2K画像」という。）からなる動画像信号（以下、「2K画像信号」という。）を処理する装置が知られている。近年では、更に画素数が多くなり、1画面が水平3840画素×垂直2160画素の画像（以下、「4K画像」という。）からなる動画像信号（以下、「4K画像信号」という。）を表示できる表示装置も登場している。

#### 【0003】

特許文献1には、4K画像信号を出力する装置が記載されている。 40

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

#### 【特許文献1】特開2008-191586号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

4K画像は2K画像に比べ、4倍の画素数を持つ。そのため、4K画像を表示装置に出力するための画像処理装置においては、メモリのサイズ、バス幅など、様々な回路が4K画像信号に対応した設計が必要である。つまり、従来の2K画像を処理する装置ではその 50

まま 4 K 画像を扱うことができず、再度、装置を設計する必要がある。この課題は、4 K 画像を処理する装置により、8 K 画像を出力する場合も同様である。

#### 【0006】

本発明は、このような問題を解決する構成の画像処理装置を提示することを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

上記目的を達成するために、本発明に係る画像処理装置は、入力画像データを水平方向に 2 つに分割して得られる 2 つの画像データのうち第 1 画像データを記憶する第 1 記憶手段と、前記 2 つの画像データのうち前記第 1 画像データと異なる第 2 画像データを記憶する第 2 記憶手段と、前記第 1 記憶手段及び前記第 2 記憶手段から前記第 1 画像データの水平ラインと前記第 2 画像データの水平ラインを交互に読み出し、読み出した水平ラインを垂直方向に合成した合成画像データを生成する合成手段と、前記合成画像データを前記入力画像データの形式の出力画像データに変換する変換手段であって、前記合成画像データのうち、前記入力画像データにおいて同じ水平ラインに対応する複数の水平ラインが前記出力画像データの 1 つの水平ラインに変換されるように前記合成画像データを変換する変換手段と、を備えることを特徴とする。

10

#### 【発明の効果】

#### 【0008】

本発明によれば、例えば、2 K 画像を扱う回路を使って 4 K 画像を出力するというよう 20 に、画素数の多い画像を処理する回路構成をより迅速に実現し提供することができるようになる。

#### 【図面の簡単な説明】

#### 【0009】

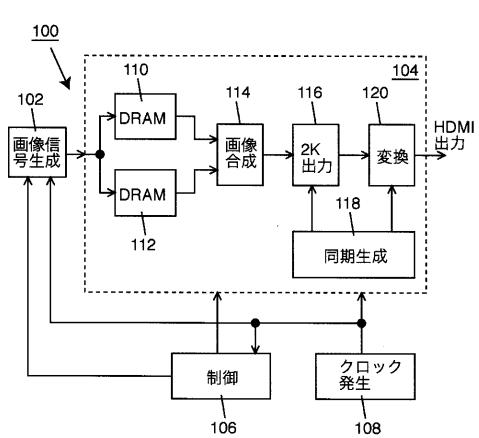

【図 1】本発明の実施例 1 の概略構成ブロック図である。実施例 1 の映像信号伝送装置ブロッ 25 ク図である。

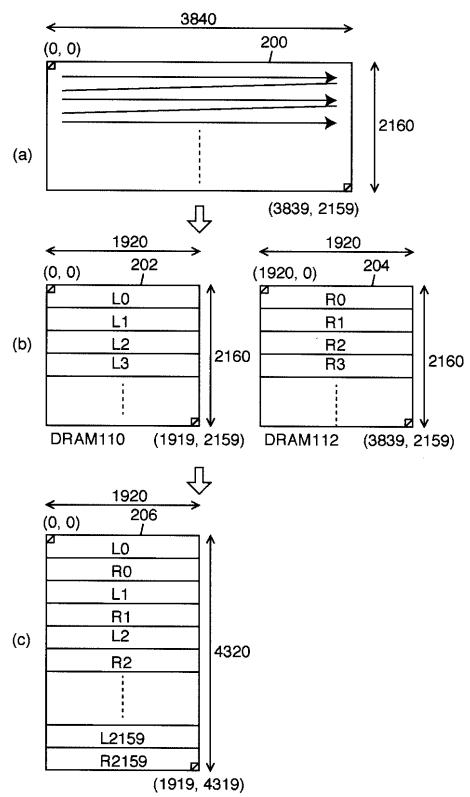

【図 2】実施例 1 における画像分割記憶と合成の説明図である。

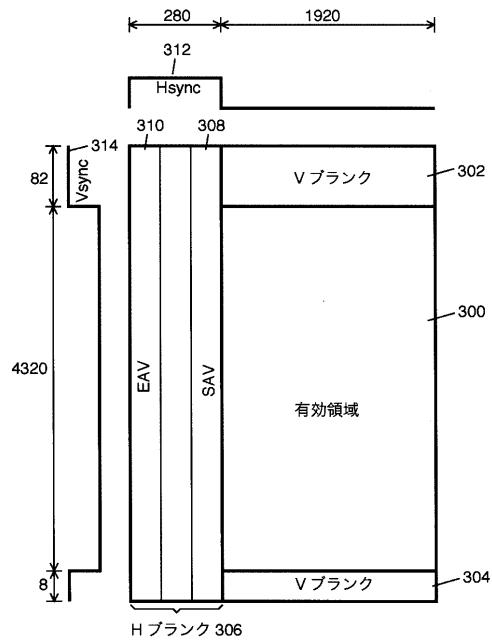

【図 3】合成画像のフォーマットの説明図である。

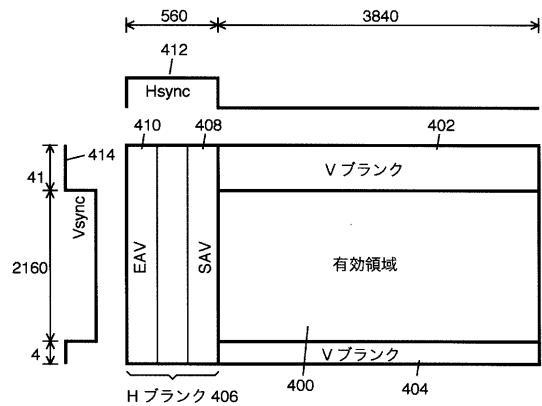

【図 4】出力画像のフォーマットの説明図である。

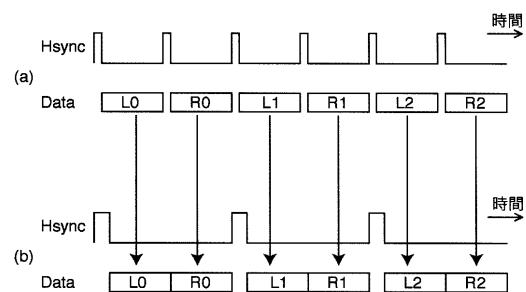

【図 5】実施例 1 における水平ライン復元のタイミング図である。

30

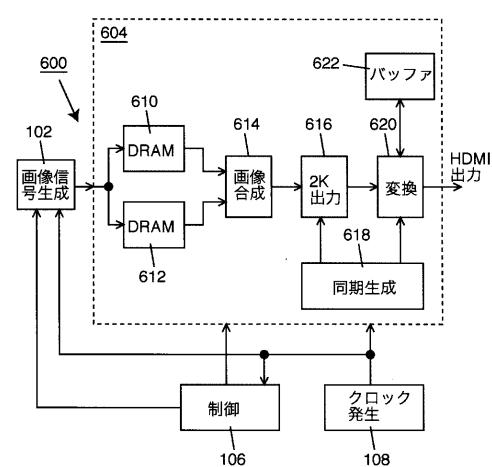

【図 6】本発明の実施例 2 の概略構成ブロック図である。

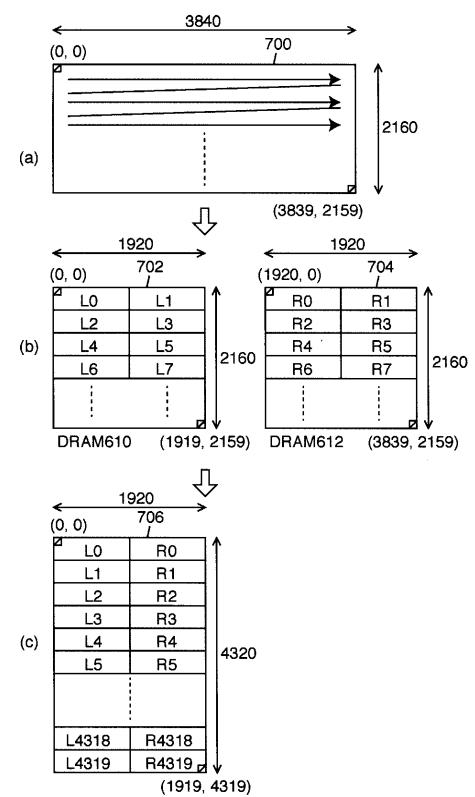

【図 7】実施例 2 における画像分割記憶と合成の説明図である。

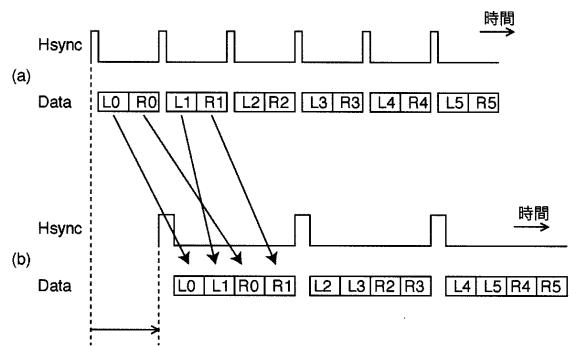

【図 8】実施例 2 における水平ライン復元のタイミング図である。

#### 【発明を実施するための形態】

#### 【0010】

以下、図面を参照して、本発明の実施例を詳細に説明する。

#### 【実施例 1】

#### 【0011】

図 1 は、本発明の一実施例の概略構成ブロック図を示す。図 1 に示す画像処理装置 100 は、画像信号生成装置 102、出力装置 104、制御装置 106 及びクロック発生装置 108 からなる。画像処理装置 100 は、例えば、ビデオカメラ、または、DVD (登録商標) 及び BD (登録商標) などの光ディスクから上述の動画像を再生する再生装置に実装される。

40

#### 【0012】

画像信号生成装置 102 は、制御装置 106 の制御下で、4 K 画像の 30 フレーム / 秒 (fps) の動画像信号と、2 K 画像の 30 フレーム / 秒 (fps) の動画像信号を選択的に出力する。出力装置 104 は、画像信号生成装置 102 からの動画像を HDMI (登録商標) に対応するデジタル映像信号形式に変換して出力する。制御装置 106 は、HDMI 出力として 4 K 画像出力モードと 2 K 画像出力モードを選択可能である。制御装置 106 は、画像信号生成装置 102 と出力装置 104 が 2 K 画像出力 / 4 K 画像出力のため

50

に協調して動作するように、画像信号生成装置 102 と出力装置 104 を制御する。

【0013】

クロック発生装置 108 は、SMPTE で規定されている 4K 画像信号（フレームレート 30Hz）のクロック（297MHz）を、画像信号生成装置 102、出力装置 104 及び制御装置 106 に供給する。画像信号生成装置 102、出力装置 104 及び制御装置 106 は、クロック発生装置 108 からのクロックに従い同期動作する。

【0014】

出力装置 104 は、画像信号生成装置 102 からの入力画像を HDMI 形式のデジタル映像信号として出力する。出力装置 104 は、画像信号生成装置 102 からの動画像信号の各画像データを一時記憶する DRAM110, 112 を具備する。DRAM110, 112 はそれぞれ、水平 1920 画素 × 垂直 2160 画素の 2 画面分の画像データ、すなわち、2K 画像の水平画素数で 4K 画像の水平ライン数に等しい水平ライン数の画像データを記憶できる。詳細は後述するが、制御装置 106 による制御の下で、画像信号生成装置 102 からの 1 画面の 4K 画像信号は、1 ラインの左半分が一方の DRAM110 に、残る右半分が他方の DRAM112 にそれぞれ一時記憶される。また、画像信号生成装置 102 からの 1 画面の 2K 画像信号は、一方の DRAM110 に一時記憶される。

【0015】

画像合成部 114 は、4K 画像出力モードでは、DRAM110, 112 に一時記憶される画像データをその水平ラインのライン順次で合成または多重し、得られた合成画像信号を 2K 出力部 116 に出力する。2K 画像出力モードでは、DRAM110, 112 に一時記憶される画像データをその水平ラインを単位にライン順次で読み出し、2K 出力部 116 に出力する。

【0016】

同期生成部 118 は、2K 出力部 116 に入力する画像信号の水平ラインと画面の構成を規定するタイミングデータ（TRS : Timing Reference Signal）を 2K 出力部 116 に供給する。そのようなタイミングデータには、水平ラインの始端を示す SAV (Start of Active Video) 及び水平ラインの終端を示す EAV (End of Active Video) がある。2K 出力部 116 は、画像合成部 114 からの画像信号に同期生成部 118 からのタイミングデータを合成すると共に所定の垂直ブランクコードを追加して、所定形式のデジタル映像信号を生成する。詳細は後述するが、2K 出力部 116 が出力するデジタル映像信号の画像領域の水平画素数は、2K 画像出力モードと 4K 画像出力モードのいずれの場合も、2K 画像の水平画素数（1902 画素）に一致する。2K 出力部 116 は、生成したデジタル映像信号を変換部 120 に供給する。

【0017】

変換部 120 は、2K 画像出力モードでは、2K 出力部 116 からの映像信号をスルー出力し、4K 画像出力モードでは、2K 出力部 116 からの映像信号を 4K 画像構成に再構成し、同期生成部 118 からのタイミングデータを合成して、出力する。

【0018】

図 2 ないし図 5 を参照して、4K 画像出力モードでの本実施例の動作を説明する。

【0019】

4K 画像出力モードでは、画像信号生成装置 102 は、図 2 (a) に示すように、水平 3840 画素、垂直 2160 画素の 4K 画像信号を出力する。出力装置 104 は、制御装置 106 による制御の下で、画像信号生成装置 102 からの 1 画面の 4K 画像信号の 1 水平ラインの左半分を一方の DRAM110 に、残る右半分を DRAM112 にそれぞれ一時記憶する。図 2 (b) は、DRAM110, 112 に一時記憶される画像データ配置を示す。Ln は n 番目の水平ラインの左半分のライン画像データを示し、Rn は、残る右半分のライン画像データを示す。一般的には、DRAM110, 112 は、出力装置 104 への入力画像の水平画素数の半分以下の水平画素数で、入力画像の互いに異なる水平ライン部分を記憶する記憶手段である。

【0020】

10

20

30

40

50

4 K 画像 200において、1フレームの左上の画素（の座標）を（0, 0）、右下の画素を（3839, 2159）とする。この画像 200に対し、（0, n）～（1919, n）と（1920, n）～（3839, n）というように、水平方向を  $3840 / 2 = 1920$  を中心に左右同じ画素数で分割し、それぞれをDRAM110、112に格納する。これにより、DRAM110には、4 K 画像 200 の左半分に相当する水平 1920 画素、垂直 2160 画素の画像 202 が格納される。また、DRAM112には、4 K 画像 200 の右半分に相当する水平 1920 画素、垂直 2160 画素の画像 204 が格納される。

#### 【0021】

画像合成部 114 は、DRAM110、112 に一時記憶される画像 202、204 をその水平ライン単位で交互に読み出し、ライン順次で合成または多重する。図 2 (c) に示すように、画像 202 のライン  $L_0 \sim L_n$  及び画像 204 のライン  $R_0 \sim R_n$  を交互に  $L_0, R_0, L_1, R_1, L_2, R_2, \dots, L_n, R_n$  というように配置する。この合成で得られる合成画像 206 は、図 2 (c) に示すように、水平 1920 画素、垂直 4320 画素の構成からなり、データ量としては 2 K 画像の 4 画面分に相当する。画像合成部 114 は、この合成で得られた合成画像信号を 2 K 出力部 116 に出力する。

#### 【0022】

同期生成部 118 は、図 3 に示すような、水平 1920 画素、垂直 4320 画素の水平垂直同期を規定するタイミングデータを 2 K 出力部 116 に供給する。図 3 では、理解を容易にするため、アナログ映像信号における水平同期信号 H sync と垂直同期信号 V sync を付記してある。

#### 【0023】

2 K 出力部 116 は、画像合成部 114 からの図 2 (c) に示す構成の画像信号を、図 3 に示す画像構成の有効領域に配置し、同期生成部 118 からのタイミングデータを図 3 に示す位置に配置する。2 K 出力部 116 は、水平ブランク及び垂直ブランクを示すコードも、図 3 に示す位置に配置する。

#### 【0024】

2 K 出力部 116 が出力する画像信号の 1 フレームは、図 3 に示すように、有効領域 300、V(垂直)ブランク 302, 304、及び H(水平)ブランク 306 からなる。H ブランク 306 には、水平ラインの始端を示す SAV (Start of Active Video) 308 と、終端を示す EAV (End of Active Video) 310 が配置される。理解を容易にするために、アナログ映像信号の水平同期信号 (H sync) 312 と垂直同期信号 (V sync) 314 を付記してある。

#### 【0025】

水平同期信号 (H sync) 312 は、2 K 画像の水平画素数 (1920 画素) に対応しており、SMPTE で規定されている 2 K 画像のデジタル映像信号形式に準拠している。すなわち、1920 画素幅の有効領域 300 に対して、H ブランク 306 を 280 画素相当としている。

#### 【0026】

垂直方向については、4 K 画像の 2 倍である 4320 ラインとなっている。そこで、有効領域 300 の 4320 ラインの上側には、4 K 画像の規格値である 41 ラインの 2 倍となる 82 ライン相当の V ブランク 302 を配置する。同様に、有効領域 300 の下側には、4 K 画像の規格値である 4 ラインの 2 倍となる 8 ライン相当の V ブランク 304 を配置する。 $4320 + 90 = 4410$  ラインで 1 フレームが完結する。

#### 【0027】

2 K 出力部 116 は、図 3 に示すように各データ及びコードを配置して生成したデジタル映像信号を変換部 120 に出力する。水平方向のサイズで見ると、2 K 画像と同じであるので、画像合成部 114 と 2 K 出力部 116 については、2 K 画像を処理するための同様の目的の回路構成を垂直方向に拡張するだけで済むことが分かる。

#### 【0028】

10

20

30

40

50

変換部 120 は、2K出力部 116 からのデジタル映像信号（図3）を、図4に示す4K画像のデジタル映像信号形式に変換し、同期生成部 118 からの4K画像の水平垂直同期のタイミング信号を合成または多重して、出力する。

【0029】

変換部 120 が出力する4K画像のデジタル映像信号の1フレームは、図4に示すように、有効領域 400、V ブランク 402, 404、及び H ブランク 406 からなる。H ブランク 406 には、水平ラインの始端を示す SAV 408 と、終端を示す EAV 410 が配置される。有効領域 400 に画像 206 の画像データが再配置されて収容される。有効領域 400 に先行する V ブランク 402 の幅は 41 ライン相当で、後行する V ブランク 404 の幅は 4 ライン相当である。H ブランク 406 の幅は 560 画素相当である。理解を容易にするために、アナログ映像信号の水平同期信号（H sync）412 と垂直同期信号（V sync）414 を付記してある。有効領域 400 に画像データが配置される。

【0030】

変換部 120 は、4K画像の各水平ラインを復元するために、図3に示す画像構成（または画像 206）でライン順次になっているライン画像データ L<sub>n</sub>、R<sub>n</sub> を、図5に示すように 1 水平ラインに再配置する。図5（a）は、図3に示す画像構成からの読み出し順序例を示し、図5（b）は、読み出したライン画像データ L<sub>n</sub>、R<sub>n</sub> を再配置した後のライン画像データ構成を示す。すなわち、ライン画像データ L<sub>n</sub> を時間的に先に配置し、これに続けてライン画像データ R<sub>n</sub> を配置して 1 水平ラインとする。

【0031】

2K画像出力モードでの本実施例の動作を説明する。2K画像出力モードでは、画像信号生成装置 102 は、制御装置 106 からの指示に従い、水平 1920 画素、垂直 1080 画素の 2K 画像信号を出力する。出力装置 104 は、制御装置 106 による制御の下で、画像信号生成装置 102 からの 1 画面の 2K 画像信号を DRAM110（または DRAM112）に一時記憶する。

【0032】

画像合成部 114 は、DRAM110 から 2K 画像信号を読み出し、そのまま 2K 出力部 116 に供給する。2K 出力部 116 は、画像合成部 114 からの 2K 画像信号の各フレームに対し、図3と同様の構成で水平垂直同期のタイミングデータを合成または多重する。ただし、2K 画像のライン数が 1080 本なので、これに応じて V ブランクの幅は調整される。2K 出力部 116 はこのようにタイミングデータを付加した 2K 画像のデジタル映像信号を変換部 120 に供給する。変換部 120 は、2K 出力部 116 からの 2K 画像のデジタル映像信号をそのまま外部に出力する。

【0033】

2K 画像出力モード時には、画像合成部 114 及び変換部 120 はそれぞれの入力データをスルー出力するのみである。従って、画像合成部 114 及び変換部 120 のそれぞれに対して 2K 画像出力モード時に迂回する迂回路を設けても良いことは明らかである。

【0034】

本実施例では、2K 画像の水平画素数になるように 4K 画像の各画面を水平方向に 2 分割して DRAM110、112 に一時格納するので、2K 画像用の回路構成をわずかな修整で 4K 画像出力に対応させることができる。

【実施例 2】

【0035】

図6は、本発明の実施例2の概略構成ブロック図を示す。図1と同じ構成要素には同じ符号を付してある。

【0036】

図6に示す画像処理装置 600 の 4K 画像出力モードでの動作を、図7 及び図8 を参照して説明する。図7は、出力装置 604 の DRAM610、612 及び画像合成部 614 での画像データの扱いを説明する模式図であり、図2に対応する。図8は、変換部 620 における変換動作を説明する模式図である。

10

20

30

40

50

## 【0037】

4K画像出力モードでは、画像信号生成装置102は、図7(a)に示すように、水平3840画素、垂直2160画素の4K画像信号(画像700)を出力する。出力装置604は、制御装置106による制御の下で、画像信号生成装置102からの1画面の4K画像信号の1ラインの左半分(画像702)を一方のDRAM610に、残る右半分(画像704)をDRAM612にそれぞれ一時記憶する。図7(b)は、DRAM610, 612に一時記憶される画像データ配置を示す。

## 【0038】

本実施例2では、実施例1とは異なり、原画像700の左半分をさらに2等分し、右半分もさらに2等分する。これにより、DRAM610, 612へのアクセスを960画素単位とすることができます。図7では、水平ライン番号をnとしたとき、DRAM610の画像702の左半分をLに(2n)を付加した記号で表記し、右半分をLに(2n+1)を付加した記号で表記する。例えば、L2は、(0, 1)～(959, 1)の画像部分を示し、L3は(960, 1)～(1919, 1)の画像部分を示す。同様に、DRAM612の画像704の左半分をRに(2n)を付加した記号で表記し、右半分をRに(2n+1)を付加した記号で表記する。例えば、R2は、(1920, 1)～(2879, 1)の画像部分を示し、R3は(2880, 1)～(3839, 1)の画像部分を示す。

## 【0039】

画像合成部614は、DRAM610, 612に一時記憶される画像702、704をラインの半分単位、すなわち960画素単位で交互に読み出し、1920画素単位のラインとして合成または多重する。図7(c)は、画像合成部614による合成結果の画像706を示す。図7(c)に示すように、画像702の左半画像L0と画像704の左半画像R0をそれぞれDRAM610, 612から読み出して1ラインに配置する。次に、画像702の右半画像L1と画像704の右半画像R1をそれぞれDRAM610, 612から読み出して1ラインに配置する。以下、この合成を繰り返す。この合成で得られる合成画像706は、図7(c)に示すように、水平1920画素、垂直4320画素の構成からなり、データ量としては2K画像の4画面分に相当する。画像合成部614は、この合成で得られた合成画像信号を2K出力部616に出力する。

## 【0040】

2K出力部616及び同期生成部618はそれぞれ、2K出力部116及び同期生成部118と同様に動作する。すなわち、2K出力部616は、画像合成部614からの画像信号に同期生成部618からの実施例1と同様のタイミングデータを付加し、SMPTE規格に準拠する形式のデジタル映像信号を出力する。

## 【0041】

変換部620は、2K出力部616からのデジタル映像信号の有効領域を抜き出し、バッファ622を使って4K画像を復元する。具体的に説明すると、変換部620は、2K出力部616からの画像信号の2水平ライン分を、図8に示すシーケンスで1水平ラインに再構成する。例えば、図7(c)に示す画像706の最初の水平ラインに含まれるライン画像データL0, R0と2本目の水平ラインに含まれるライン画像データL1, R1を、図8に示すように、L0, L1, R0, R1の順に再配置して1本の水平ラインとする。以下、同様に、変換部620は、2K出力部616からの画像信号の2ラインを合成して4K画像の1ラインに変換する。

## 【0042】

変換部620は、このように再構成された4K画像信号に対して、実施例1と同様に、同期生成部618からの水平垂直同期のタイミングデータを重畠する。変換部620は、このようにして生成されたデジタル映像信号をSMPTE規格準拠形式で出力する。

## 【0043】

このように、4K画像を水平方向に2分割して2個のDRAMに書き込み、各DRAMからのデータ読出し時には半分を単位に読出しを交互に行うことで、各DRAMの1回あたりアクセス占有時間を短くできる。これにより、画像信号生成装置102における複数

10

20

30

40

50

の処理ブロックからのアクセスを許容し易くなる。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

G 09 G 5/377 (2006.01)

G 09 G 5/18 (2006.01)

(56)参考文献 特開2015-219279 (JP, A)

特開2006-053527 (JP, A)

特開2010-124309 (JP, A)

特開2009-229480 (JP, A)

特開2013-098966 (JP, A)

特開2014-135667 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 5 / 0 0

G 09 G 5 / 1 8

G 09 G 5 / 3 7 7

G 09 G 5 / 3 9 1

G 09 G 5 / 3 9 7

G 09 G 5 / 3 9 9

H 04 N 5 / 6 6