(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-323323

(P2005-323323A)

(43) 公開日 平成17年11月17日(2005.11.17)

(51) Int.Cl.<sup>7</sup>

H03L 7/095

G11C 11/407

H03L 7/081

F 1

H03L 7/08

H03L 7/08

G11C 11/34

G11C 11/34

テーマコード(参考)

5J106

5MO24

審査請求 未請求 請求項の数 11 O L (全 12 頁)

(21) 出願番号 特願2004-190213 (P2004-190213)

(22) 出願日 平成16年6月28日 (2004.6.28)

(31) 優先権主張番号 2004-031983

(32) 優先日 平成16年5月6日 (2004.5.6)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 591024111

株式会社ハイニックスセミコンダクター

大韓民国京畿道利川市夫鉢邑牙美里山13

6-1

(74) 代理人 100064724

弁理士 長谷 照一

(74) 代理人 100073302

弁理士 神谷 牧

(72) 発明者 郭 鍾太

大韓民国京畿道利川市夫鉢邑牙美里山13

6-1 株式会社ハイニックスセミコンダ

クター内

F ターム(参考) 5J106 AA03 BB00 CC30 CC59 DD24

DD33 DD43 DD48 EE10 JJ09

LL07

最終頁に続く

(54) 【発明の名称】ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

## (57) 【要約】

## 【課題】

階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

## 【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループプロックと、ディレイロックループプロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

## 【選択図】図1

**【特許請求の範囲】****【請求項 1】**

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、

前記ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答して、コース遅延調整終了時点での比較対象クロックの位相状態を記憶するための位相状態記憶手段と、

前記位相比較信号、前記コース遅延調整終了信号及び前記位相状態の記憶手段から出力された位相状態信号に応答して、ファイン遅延調整によって前記位相比較信号の遷移時点を検出し、その時点にアサートされるディレイロック信号を生成するためのディレイロック状態検出手段と、

を備えてなる半導体素子。

**【請求項 2】**

請求項 1 に記載の半導体素子において、

前記位相状態記憶手段は、

前記コース遅延調整終了信号に応答して、前記位相比較信号をスイッチングするためのスイッチング部と、

前記スイッチング部の出力信号をラッチするためのラッチ部とを含んでなることを特徴とする半導体素子。

**【請求項 3】**

請求項 1 又は 2 に記載の半導体素子において、

前記ディレイロック状態検出手段は、

ファイン遅延調整過程で前記位相比較信号が論理レベルハイからローに遷移される時点を検出するための第 1 遷移検出部と、

ファイン遅延調整過程で前記位相比較信号が論理レベルローからハイに遷移される時点を検出するための第 2 遷移検出部と、

前記第 1 遷移検出部及び第 2 遷移検出部の共通出力ノードに接続されて、前記ディレイロック信号を出力する出力部とを含んでなることを特徴とする半導体素子。

**【請求項 4】**

請求項 3 に記載の半導体素子において、

前記出力部は、

前記第 1 遷移検出部及び第 2 遷移検出部の共通出力ノードに係る信号をラッチするラッチ部と、

リセット信号に応答して、前記共通出力ノードを初期化するリセット部とを含んでなることを特徴とする半導体素子。

**【請求項 5】**

請求項 4 に記載の半導体素子において、

前記第 1 遷移検出部及び第 2 遷移検出部は、それぞれ、

前記コース遅延調整終了信号及び前記位相状態信号により制御される第 1 スイッチング素子と、

現在の前記位相比較信号により制御される第 2 スイッチング素子と、

ラッチされる以前の前記位相比較信号により制御される第 3 スイッチング素子とを含んでなり、

前記第 1 スイッチング素子、第 2 スイッチング素子及び第 3 スイッチング素子は、前記第 1 遷移検出部及び第 2 遷移検出部の共通出力ノードと接地電圧端との間に直列に接続されている

ことを特徴とする半導体素子。

**【請求項 6】**

請求項 4 に記載の半導体素子において、

10

20

30

40

50

前記第1遷移検出部は、

前記位相状態信号を入力とする第1インバータと、

前記インバータの出力信号及び前記コース遅延調整終了信号を入力とする第1NANDゲートと、

前記第1NANDゲートの出力信号を入力とする第2インバータと、

前記位相比較信号を入力とする第3インバータと、

前記ディレイロックループロックの比較動作周期ごとに前記位相比較信号をラッチするためのフリップフロップと、

前記共通出力ノードと接地電圧端との間に直列に接続され、それぞれ、前記第2インバータの出力信号、前記第3インバータの出力信号、前記フリップフロップの出力信号をゲート入力とする第1NMOSトランジスタ、第2NMOSトランジスタ及び第3NMOSトランジスタとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項7】

請求項6に記載の半導体素子において、

前記第2遷移検出部は、

前記位相状態信号及び前記コース遅延調整終了信号を入力とする第2NANDゲートと、

前記第2NANDゲートの出力信号を入力とする第4インバータと、

前記フリップフロップの出力信号を入力とする第5インバータと、

前記共通出力ノードと前記接地電圧端との間に直列に接続され、それぞれ、前記第4インバータの出力信号、前記位相比較信号、前記第5インバータの出力信号をゲート入力とする第4NMOSトランジスタ、第5NMOSトランジスタ及び第6NMOSトランジスタとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項8】

請求項2に記載の半導体素子において、

前記位相状態記憶手段の前記スイッチング部は、

前記位相比較信号を入力とする第1インバータと、

前記コース遅延調整終了信号を入力とする第2インバータと、

前記コース遅延調整終了信号及び前記第2インバータの出力信号により制御されて、前記第1インバータの出力信号を選択的に前記ラッチ部に伝達するトランスマッピングゲートとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項9】

請求項8に記載の半導体素子において、

前記位相状態記憶手段の前記ラッチ部は、

前記スイッチング部の出力信号を入力とするインバタラッチと、

前記インバタラッチの出力信号を入力として前記位相状態信号を出力する第3インバータとを含んでなる

ことを特徴とする半導体素子。

#### 【請求項10】

請求項4に記載の半導体素子において、

前記出力部の前記ラッチ部は、

前記第1遷移検出部及び第2遷移検出部の共通出力ノードに接続されたインバタラッチを含んでなる

ことを特徴とする半導体素子。

#### 【請求項11】

請求項4に記載の半導体素子において、

前記出力部の前記リセット部は、

10

20

30

40

50

前記リセット信号をゲート入力とし、電源電圧端と前記第1遷移検出部及び第2遷移検出部の共通出力ノードとの間に接続されたPMOSトランジスタを含んでなることを特徴とする半導体素子。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体回路技術に関し、特にディレイロックループ(delay locked loop)(以下、「DLL」と称する)回路に関し、さらに詳細には、階層的遅延ライン構造のDLL回路のディレイロック状態を検出する技術に関する。

【背景技術】

【0002】

一般に、システムや回路において、クロック信号は、動作タイミングを合せるためのレフアレンスとして用いられており、エラー無しでより速い動作を保障するために使用されることもある。外部から入力されるクロック信号が内部で使用される際に、内部回路によるクロック信号の時間遅延(これをクロックスキューという)が生じるが、このような時間遅延を補償し、内部クロックが外部クロックと同じ位相を有するようにするために、DLL回路が使用されている。

【0003】

一方、DLL回路は、従来広く使用されていたフェーズロックループ(PLL)回路に比べて、雑音の影響をより少なく受けるという長所を有しているため、SDRAM(Synchronous DRAM)、DDR-SDRAM(Double Data Rate Synchronous DRAM)を始めとする同期式半導体メモリに広く使用されている。同期式半導体メモリ素子において、レジスタ制御DLLは、基本的に外部クロックを受け取ってクロック経路及びデータ経路の遅延成分を補償し、予めネガティブ遅延を反映することによって、データの出力が外部クロックと同期されるようにする機能を行う。

【0004】

一方、最近では、このようなDLLにおいて、最小可変遅延時間(minimum variable delay time) $t_{\text{VD}}$ を縮め、ジッタ(jitter)を最小化する方向に研究が持続されており、その一環としてコース遅延ライン(coarse delay line)(粗遅延ライン)とファイン遅延ライン(fine delay line)(微細遅延ライン)とを含んでなる階層的遅延ライン構造を使用したDLLが提案された。

【0005】

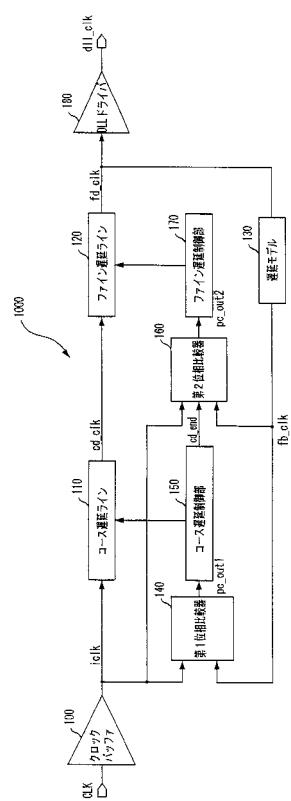

図5は、従来技術に係る階層的遅延ラインを備えたDLLのブロック図である。

【0006】

図5を参照して説明すれば、従来技術に係るDLL回路1000は、外部クロックCLKをバッファリングして外部クロックCLKの立上りエッジ(又は、立下りエッジ)に同期したソースクロックiclkを生成するクロックバッファ100と、ソースクロックiclkを入力としてプログラム可能な多数の単位コース遅延(粗遅延)セルを含むコース遅延ライン110と、コース遅延ライン110から出力されたコース遅延クロックcd\_clkを入力としてプログラム可能な多数の単位ファイン遅延(微細遅延)セルを含むファイン遅延ライン120と、ファイン遅延ライン120から出力されたファイン遅延クロックfd\_clkを入力として実際のクロック信号経路の遅延分量をモデリングした遅延モデル130と、ソースクロックiclkと遅延モデル130から出力されたフィードバッククロックfb\_clkとの位相を比較するための第1位相比較器140と、第1位相比較器140から出力された位相比較信号pc\_out1によって、コース遅延ライン110の遅延量を制御するためのコース遅延制御部150と、コース遅延制御部150から出力されたコース遅延調整終了信号cd\_endに応答して、ソースクロックiclkとフィードバッククロックfb\_clkとの位相を比較するための第2位相比較器160と、第2位相比較器160から出力された位相比較信号pc\_out2によって、ファイン遅延ライン120の遅延量を制御するためのファイン遅延制御部170と、ファイン遅延ライン120から出力されたファイン遅延クロックfd\_clkを入

10

20

30

40

50

力として D L L クロック dI1\_clk を生成する D L L ドライバ 180 とを備えて構成されている。

【 0 0 0 7 】

ここで、遅延モデル 130 は、実際のクロックバッファ 100、データ出力バッファ（図示せず）、クロック信号ライン（図示せず）などの遅延時間または経路と同じ遅延条件を有し、しばしば「レプリカ遅延」と呼ばれる。

【 0 0 0 8 】

上述したように構成された従来技術に係る D L L 回路 1000 は、まず、第 1 位相比較器 140 及びコース遅延制御部 150 によりコース遅延ライン 110 の遅延量を調節する動作を行い、粗いけれども早くディレイロック状態に近接させたコース遅延クロック cd\_clk を確保し、次いで、第 2 位相比較器 160 及びファイン遅延制御部 170 によりファイン遅延ライン 120 の遅延量を調節する動作を行なうことによって、微細にその位相を合せて行く。

【 0 0 0 9 】

ところが、従来技術に係る D L L 回路 1000 は、外部クロック CLK と内部クロック fb\_clk の位相が互いに一致する瞬間、すなわちディレイロック状態になる瞬間を判断する構造を有していない。したがって、D L L ブロック内で、又は半導体素子内の他のブロックで D L L のディレイロック状態の情報を使用し、他のいろいろな動作を行わせる余地がなかった。

【 0 0 1 0 】

一方、従来の階層的遅延ラインを備えた D L L 回路の中には、前記図 5 に示されたブロック構成と異なるブロック構成を有する D L L 回路も存在するが、そのように一部構成上に相違点があつても、階層的遅延ラインを備えた D L L の場合、前記のような問題点を伴わざるを得なかった。

【 特許文献 1 】米国特許第 6, 499, 111 号明細書

【 発明の開示 】

【 発明が解決しようとする課題 】

【 0 0 1 1 】

この発明は、上述した従来技術の問題点に鑑みてなされたものであつて、その目的とするところは、階層的遅延ラインを備えたディレイロックループ（D L L）回路のディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供することにある。

【 課題を解決するための手段 】

【 0 0 1 2 】

上記目的を達成するため、この発明によれば、コース遅延ライン及びファイン遅延ラインを備えた階層的遅延ライン構造のディレイロックループブロックと、前記ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答して、コース遅延調整終了時点での比較対象クロックの位相状態を記憶するための位相状態記憶手段と、前記位相比較信号、前記コース遅延調整終了信号及び前記位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整によって前記位相比較信号の遷移時点を検出し、その時点にアサートされるディレイロック信号を生成するためのディレイロック状態検出手段とを備えてなる半導体素子を提供する。

【 0 0 1 3 】

この発明は、階層的遅延ラインを備えた D L L において、コース遅延調節動作を終了する時点での内部クロックと、外部クロックとの位相がどのような関係にあるかを予め記憶しておき、ファイン遅延調節動作を行つて内部クロックと外部クロックとの位相が既に記憶された以前の位相状態とは異なり、位相が同じ J Y なる時点を検出し、この時点に D L L がディレイロック状態になったことを示す内部信号をアサートするようとする。

【 発明の効果 】

【 0 0 1 4 】

10

20

30

40

50

この発明によれば、ディレイロック時点を簡単に明確に検出でき、これによってD L L ブロック内において、又は半導体素子内の他のブロックにおいて、D L L のディレイロック状態の情報を使用して他のいろいろな動作を行わせることのできる根拠を設けた。また、ディレイロック状態の情報を使用すれば、半導体素子の不必要的動作を防止して、電力消耗を大幅に減らすことができるという効果を奏する。

【発明を実施するための最良の形態】

【0015】

以下、この発明の最も好ましい実施形態を、添付の図面を参照しながら説明する。

【0016】

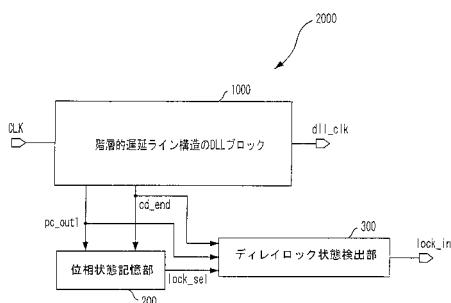

図1は、この発明の実施形態に係る半導体素子のブロック図である。

10

【0017】

図1を参照すれば、この実施形態に係る半導体素子2000は、コース遅延ライン及びファイン遅延ラインを含む階層的遅延ライン構造のD L L ブロック1000と、階層的遅延ライン構造のD L L ブロック1000から出力された位相比較信号pc\_out1及びコース遅延調整終了信号cd\_endに応答して、コース遅延調整終了時点でのソースクロックiclkに対するフィードバッククロックfb\_clkの位相状態を記憶するための位相状態記憶部200と、位相比較信号pc\_out1、コース遅延調整終了信号cd\_end及び位相状態格納部200から出力された位相状態信号lock\_selに応答して、ファイン遅延調整による前記位相比較信号pc\_out1の遷移時点を検出して、その時点にアサートされるディレイロック信号lock\_inを生成するためのディレイロック状態検出部300とを備えて構成される。

20

【0018】

すなわち、この実施形態に係る半導体素子は、コース遅延ライン及びファイン遅延ラインを備えた階層的遅延ライン構造のD L L ブロック1000に対して、ディレイロック状態を示すことのできるディレイロック信号lock\_inを生成するための位相状態記憶部200とディレイロック状態検出部300とを追加した。

【0019】

位相状態記憶部200とディレイロック状態検出部300は、階層的遅延ライン構造のD L L ブロック1000から出力された位相比較信号pc\_out1と、コース遅延調整終了信号cd\_endとを用いる。

30

【0020】

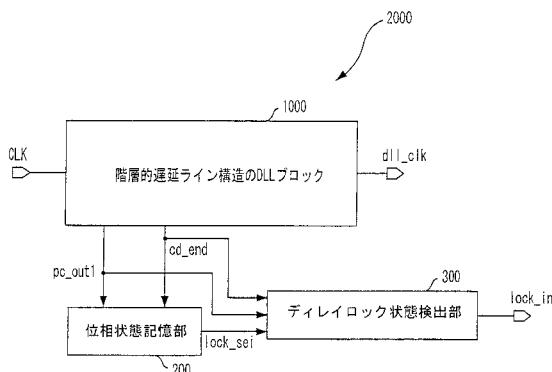

図2は、図1の位相状態記憶部200の構成を示す回路図である。

【0021】

図2を参照すれば、位相状態格納部200は、コース遅延調整終了信号cd\_endに応答して位相比較信号pc\_out1をスイッチングするスイッチング部210と、スイッチング部210の出力信号をラッチするラッチ部220と含んで構成されている。

【0022】

ここで、スイッチング部210は、位相比較信号pc\_out1を入力とするインバータIN V1と、コース遅延調整終了信号cd\_endを入力とするインバータIN V2と、コース遅延調整終了信号cd\_end及びインバータIN V2の出力信号に制御されて、インバータIN V1の出力信号を選択的にラッチ部220に伝達するためのトランസファーゲートTGとを含む。

40

【0023】

また、ラッチ部220は、スイッチング部210の出力信号を入力とするインバタラッチIN V3及びIN V4と、インバタラッチIN V3及びIN V4の出力信号を入力として位相状態信号lock\_selを出力するインバタIN V5とを備える。

【0024】

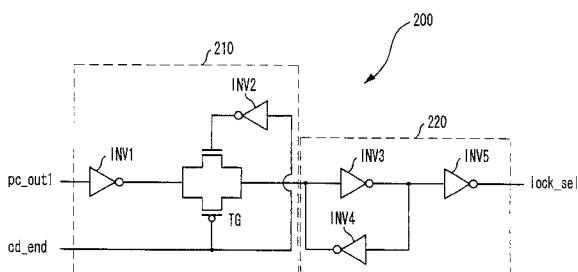

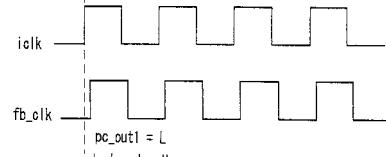

図3a及び図3bは、階層的遅延ライン構造のD L L ブロック1000内の位相比較対象クロックであるソースクロックiclkとフィードバッククロックfb\_clkとのコース遅延調整終了時点における位相状態に応じて、位相比較信号pc\_out1及び位相状態信号lock\_selがいかなる論理レベルを呈するかを説明するための図である。

50

## 【0025】

図3aを参照すれば、コース遅延調整終了信号cd\_endが論理レベルハイにアサートされた時点、すなわち、コース遅延調整が完了した時点において、フィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより先行する位相を有する場合には、位相比較信号pc\_out1は論理レベルハイHを呈し、この時位相状態信号lock\_selは論理レベルローLを呈する。

## 【0026】

他方、図3bを参照すれば、コース遅延調整が完了した時点でフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより遅れた位相を有する場合には、位相比較信号pc\_out1は論理レベルローLを呈し、この時位相状態信号lock\_selは論理レベルハイHを呈する。

## 【0027】

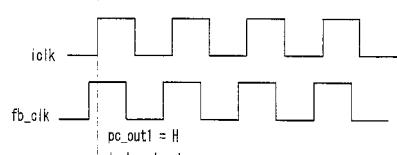

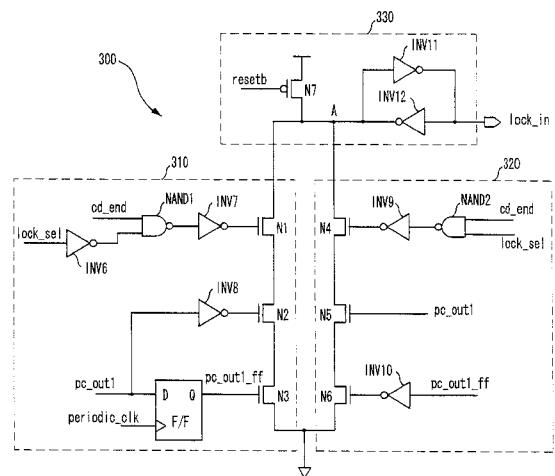

図4は、図1のディレイロック状態検出部300の回路構成を示す回路図である。

## 【0028】

図4を参照すれば、ディレイロック状態検出部300は、ファイン遅延調整過程でフィードバッククロックfb\_clkの位相がソースクロックiclkの位相に比べ、初めて遅れる時点を検出するための第1遷移検出部310と、ファイン遅延調整過程でフィードバッククロックfb\_clkの位相がソースクロックiclkの位相に比べ、初めて先行する時点を検出するための第2遷移検出部320と、第1遷移検出部310及び第2遷移検出部320の共通出力ノードAに接続されて、ディレイロック信号lock\_inを出力する出力部330とを含んで構成されている。

## 【0029】

ここで、出力部330は、第1遷移検出部310及び第2遷移検出部320の共通出力ノードAに現れる信号をラッチするラッチ部と、リセット信号に応答して共通出力ノードAを初期化するためのリセット部とを有している。ラッチ部は、共通出力ノードAに接続されたインバータラッチINV11及びINV12で実現でき、リセット部は、リセット信号をゲート入力とし電源電圧端と共に接続されたPMOSトランジスタN7で実現できる。

## 【0030】

一方、第1遷移検出部310は、位相状態信号lock\_selを入力とするインバータINV6と、インバータINV6の出力信号及びコース遅延調整終了信号cd\_endを入力とするNANDゲートNAND1と、NANDゲートNAND1の出力信号を入力とするインバータINV7と、位相比較信号pc\_out1を入力とするインバータINV8と、周期クロックperiodic\_clkをクロック入力とし、位相比較信号pc\_out1をデータ入力とするフリップフロップF/Fと、共通出力ノードAと接地電圧端との間に直列に接続され、それぞれ、インバータINV7の出力信号、インバータINV8の出力信号、フリップフロップF/Fの出力信号pc\_out1\_ffをゲート入力とするNMOSトランジスタN1、N2、N3とを含んで構成されている。

## 【0031】

また、第2遷移検出部320は、位相状態信号lock\_sel及びコース遅延調整終了信号cd\_endを入力とするNANDゲートNAND2と、NANDゲートNAND2の出力信号を入力とするインバータINV9と、フリップフロップF/Fの出力信号pc\_out1\_ffを入力とするインバータINV10と、共通出力ノードAと接地電圧端との間に直列に接続され、それぞれ、インバータINV9の出力信号、位相比較信号pc\_out1、インバータINV10の出力信号をゲート入力とするNMOSトランジスタN4、N5、N6とを含んで構成されている。

## 【0032】

以下、図1～図4を参照して、この実施形態に係る半導体素子の動作を説明する。

## 【0033】

まず、階層的遅延ライン構造のDLLブロック1000において、コース遅延調整終了

信号cd\_endがアサートされる時までコース遅延調整過程を行う。コース遅延調整終了信号cd\_endは、初期状態から論理レベルローを呈するが、フィードバッククロックfb-clkの位相がソースクロックiclkの位相に一定程度以内に近接するようになると、論理レベルハイにアサートされる。

【0034】

次いで、コース遅延調整終了信号cd\_endがアサートされることよって、コース遅延調整過程が終了され、ファイン遅延調整が開始される。ところが、コース遅延調整過程が終了される時点におけるフィードバッククロックfb-clkとソースクロックiclkとの位相関係は、図3a及び図3bに示すように、2つの場合が存在する。

【0035】

コース遅延調整終了信号cd\_endが論理レベルハイにアサートされる前に、図2に示す位相状態記憶部200のトランスマルチплексор T Gが開かれていると、位相比較信号pc\_out1が反転され位相状態信号lock\_selとして出力されたが、コース遅延調整終了信号cd\_endが論理レベルハイにアサートされると、トランスマルチплексор T Gが閉められ、位相比較信号pc\_out1を遮断して、最終的な出力値がラッチ部220に記憶される。コース遅延調整が完了した時点でフィードバッククロックfb-clkの立上りエッジがソースクロックiclkの立ち上がりエッジより先行する位相を有する場合は、図3aのように、位相比較信号pc\_out1は、論理レベルハイHを呈し、位相状態信号lock\_selは論理レベルローLを呈するようになる。他方、コース遅延調整が完了した時点でフィードバッククロックfb-clkの立上りエッジがソースクロックiclkの立上りエッジより遅れた位相を有する場合は、図3bに示すように、位相比較信号pc\_out1は、論理レベルローLを呈し、位相状態信号lock\_selは、論理レベルハイHを呈する。すなわち、位相状態信号lock\_selは、コース遅延調整が完了した時点におけるフィードバッククロックfb-clkとソースクロックiclkとの位相状態に関する情報を有していることになる。

【0036】

コース遅延調整終了信号cd\_endが論理レベルハイにアサートされた後には、階層的遅延ライン構造のDLLブロック1000で、ファイン遅延調整過程を行うことになる。コース遅延調整が完了した時点でフィードバッククロックfb-clkの立上りエッジがソースクロックiclkの立上りエッジより先行した位相を有する場合は、図3aに示すように、ファイン遅延ラインに対する遅延調整によって、フィードバッククロックfb-clkの位相を少しづつ後に押す過程を行うようになり、このような過程を繰り返して行っていけば、ある瞬間にはフィードバッククロックfb-clkの立上りエッジがソースクロックiclkの立上りエッジより遅れる状態が生じるようになる。この時、位相比較信号pc\_out1が論理レベルハイから論理レベルローに遷移される。一方、コース遅延調整が完了した時点でフィードバッククロックfb-clkの立上りエッジがソースクロックiclkの立上りエッジより遅れた位相を有する場合は、図3bに示すように、ファイン遅延ラインに対する遅延調整によって、フィードバッククロックfb-clkの位相を少しづつ前に引く過程を行うようになり、このような過程を繰り返して行っていけば、ある瞬間にはフィードバッククロックfb-clkの立上りエッジがソースクロックiclkの立上りエッジより先行する状態が生じるようになる。この時、位相比較信号pc\_out1が論理レベルローからハイに遷移される。

【0037】

この発明では、このようにファイン遅延調整過程で生じる位相比較信号pc\_out1の遷移時点を検出し、その時点をディレイロック状態として認識するようにする。

【0038】

前記図4に示されたディレイロック状態検出部300は、コース遅延調整過程が完了した時点に記憶された位相状態信号lock\_selを基準として、ファイン遅延調整過程で位相比較信号pc\_out1が遷移される時点を検出して、ディレイロック信号lock\_inを生成する回路である。

【0039】

以下、ディレイロック状態検出部300の動作を説明する。

10

20

30

40

50

## 【0040】

まず、初期動作時リセット信号が論理レベルローにパルス化してアサートされれば、PMOSトランジスタN7がターンオンされ共通出力ノードAを論理レベルハイに初期化する。したがって、ディレイロック信号lock\_inは、論理レベルロー状態を呈するようになる。この時、コース遅延調整終了信号cd\_endは、論理レベルロー状態であるので、位相比較信号pc\_out1の論理値に関係なく、第1遷移検出部310及び第2遷移検出部320で接地電圧端と共に出力ノードAとの間がオープンされて、共通出力ノードAが放電されない。

## 【0041】

次いで、階層的遅延ライン構造のDLLブロック1000において、コース遅延調整過程を行うことになる。このとき、上述したようにコース遅延調整終了信号cd\_endが論理レベルハイにアサートされるまでは、位相状態信号lock\_sel及び位相比較信号pc\_out1の論理値と関係なく、共通出力ノードAの論理値が変化しない。

## 【0042】

次いで、コース遅延調整終了信号cd\_endが論理レベルハイにアサートされれば、階層的遅延ライン構造のDLLブロック1000では、コース遅延調整過程を終了し、ファイン遅延調整過程を行うことになる。

## 【0043】

ここで、コース遅延調整過程が完了した時点で、フィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより先行する位相を有する場合は、図3aに示すように、位相比較信号pc\_out1が論理レベルハイHであり、位相状態信号lock\_selが論理レベルローLであるので、第1遷移検出部310のNMOSトランジスタN1がターンオンされる。また、周期クロックperiodic\_clk(例えば、8t<sub>ck</sub>ごとに論理レベルハイにアサートされるクロック)の立上りエッジが発生する時点ごとに、位相比較信号pc\_out1をラッチするフリップフロップF/Fの出力信号pc-out1\_ffも論理レベルハイ状態になって、NMOSトランジスタN3もまたターンオン状態となる。このような状態でファイン遅延調整過程を繰り返しながら、位相比較信号pc\_out1が論理レベルローに遷移すれば、NMOSトランジスタN2もターンオンされ、共通出力ノードAを放電させて、最終的な出力であるディレイロック信号lock\_inは、論理レベルハイにアサートされる。一方、このように第1遷移検出部310が動作する間、第2遷移検出部320のNMOSトランジスタN4はターンオフ状態を維持するので、共通出力ノードAに影響を与えない。

## 【0044】

他方、コース遅延調整過程が完了した時点でフィードバッククロックfb\_clkの立上りエッジがソースクロックiclkの立上りエッジより遅い位相を有する場合は、図3bに示すように、位相比較信号pc\_out1が論理レベルローであり、位相状態信号lock\_selが論理レベルハイであるので、第1遷移検出部310のNMOSトランジスタN4がターンオンされ、フリップフロップF/Fの出力信号pc-out1\_ffも論理レベルロー状態になってNMOSトランジスタN6もまたターンオン状態となる。このような状態でファイン遅延調整過程を繰り返しながら、位相比較信号pc\_out1が論理レベルハイに遷移すれば、NMOSトランジスタN5もターンオンされ、共通出力ノードAを放電させて、最終的な出力であるディレイロック信号lock\_inは、論理レベルハイにアサートされる。一方、このように第2遷移検出部320が動作する間、第1遷移検出部310のNMOSトランジスタN1は、ターンオフ状態を維持するので、共通出力ノードAに影響を与えない。

## 【0045】

すなわち、第1遷移検出部310と第2遷移検出部320とは、コース遅延調整が完了した時点でのフィードバッククロックfb\_clkとソースクロックiclkとの位相関係に応じて、排他的に動作し、ファイン遅延調整過程で発生する位相比較信号pc\_out1の遷移時点を検出する。

## 【0046】

なお、この発明は、上記した実施形態に限られるものではなく、この発明の技術的思想

10

20

30

40

50

から逸脱しない範囲内で、多様に変更して実施することが可能である。例えば、上述した実施形態では図5に示された従来技術同様のブロック構成を有する階層的遅延ライン構造のD L L回路を例として説明したが、この発明はそれに対して一部構成上に相違点があつても、階層的遅延ラインを有する構造の場合であれば、採用が可能である。このような趣旨で、位相比較器を一つだけ使用する場合にも、この発明を採用することができる。また、上述した実施形態で用いられたトランスマジゲート及びN M O Sトランジスタは、他のスイッチング素子でもって代替することができる。

【図面の簡単な説明】

【0047】

【図1】この発明の一実施形態に係る半導体素子のブロック図である。

10

【図2】図2の位相状態記憶部の構成を例示する回路図である。

【図3a】階層的遅延ライン構造のD L Lブロック内の位相比較対象クロックのコース遅延調整終了時点での位相状態に係る位相比較信号及び位相状態信号の論理レベルを説明するための図である。

【図3b】階層的遅延ライン構造のD L Lブロック内の位相比較対象クロックのコース遅延調整終了時点での位相状態に係る位相比較信号及び位相状態信号の論理レベルを説明するための図である。

【図4】図2のディレイロック状態検出部の回路構成を例示する図である。

【図5】従来技術に係る階層的遅延ラインを備えたD L Lのブロック図である。

【符号の説明】

【0048】

1 0 0 0 ... 階層的遅延ライン構造のD L Lブロック

20

2 0 0 ... 位相状態記憶部

3 0 0 ... ディレイロック状態検出部

【図1】

【図2】

【図3a】

【図3b】

【 図 4 】

【 図 5 】

---

フロントページの続き

F ターム(参考) 5M024 AA87 BB27 DD83 JJ02 JJ38 PP01 PP02 PP03 PP07