(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-521489

(P2004-521489A)

(43) 公表日 平成16年7月15日(2004.7.15)

(51) Int.Cl.<sup>7</sup>

H01L 31/10

F 1

H01L 31/10

テーマコード(参考)

A

審査請求 未請求 予備審査請求 有 (全 65 頁)

(21) 出願番号 特願2002-558345 (P2002-558345)

(86) (22) 出願日 平成14年1月22日 (2002.1.22)

(85) 翻訳文提出日 平成15年7月22日 (2003.7.22)

(86) 國際出願番号 PCT/US2002/001969

(87) 國際公開番号 WO2002/058162

(87) 國際公開日 平成14年7月25日 (2002.7.25)

(31) 優先権主張番号 09/766,797

(32) 優先日 平成13年1月22日 (2001.1.22)

(33) 優先権主張国 米国(US)

(71) 出願人 500575824

ハネウェル・インターナショナル・インコ

ーポレーテッド

アメリカ合衆国ニュージャージー州O 7 9

6 2, モーリスタウン, コロンビア・ロー

ド 1 O 1

(74) 代理人 100089705

弁理士 松本 一夫

(74) 代理人 100076691

弁理士 増井 忠式

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】変性長波長高速フォトダイオード

## (57) 【要約】

変性長波長高速フォトダイオードを製造する方法および装置であって、基板の格子定数に整合するバッファー層が通常の成長温度で形成され、所望の格子定数を超えて勾配を付ける薄い勾配領域が低温で構成される。所望の格子定数に整合するために逆勾配付けが行われる。その後、所望の格子定数に基づく厚い層がその上に形成される。次いでアニーリングを行い、勾配層および逆勾配層中の転位材料を絶縁することができる。その上に歪んだ超格子層を作り、その上に高速のフォトダイオードを形成することができる。ドーパント中の注入層または拡散層がB e、M g、C、Y e、S i、S e、Z nまたはその他の材料に基づいて形成することができる。N -活性領域上に直接位置するP +領域の上のキャップの上に金属層を形成することができる。また、活性領域はp -ドーピングした領域を含む。高速フォトダイオードはこのようにして、G a A s、またはゲルマニウムおよびシリコンなど他の基板材料を用いて形成することができる。

**【特許請求の範囲】****【請求項 1】**

その上に勾配層を有する基板上に半導体装置を製造する方法であって、方法が、中間層を形成し、前記中間層が前記半導体装置に使用される格子定数よりも大きな格子定数を有するステップと、

前記中間層の前記格子定数から前記半導体に使用される前記格子定数へ勾配を付ける逆勾配層を形成するステップと、

前記勾配層をアニーリングして、前記勾配層を形成する結果作られる転位材料を絶縁するステップと、

歪んだ超格子層を作り、その上に形成される前記半導体装置からさらに転位を絶縁するステップとを含む方法。 10

**【請求項 2】**

前記基板上に前記勾配層を形成し、前記勾配層が、前記半導体装置に使用される前記格子定数を超えて基板の格子定数に勾配を付けるステップをさらに含む、請求項 1 に記載の方法。 10

**【請求項 3】**

前記半導体装置がフォトダイオードを含む請求項 2 に記載の方法。

**【請求項 4】**

公称の(100)配向基板を用いて前記勾配層を形成するステップをさらに含む請求項 2 に記載の方法。 20

**【請求項 5】**

MOCVD を用いて前記勾配層を形成するステップをさらに含む請求項 4 に記載の方法。

**【請求項 6】**

前記基板が GaAs 基板を含む請求項 2 に記載の方法。

**【請求項 7】**

前記基板がゲルマニウム基板を含む請求項 2 に記載の方法。

**【請求項 8】**

前記基板がシリコン基板を含む請求項 2 に記載の方法。

**【請求項 9】**

前記基板上に逆勾配に基づく少なくとも 1 つの勾配層を形成し、

前記少なくとも 1 つの勾配層が大量の n - 型ドーピングを用いて形成され、大きく転位した領域を通る勾配材料の導電性が、勾配材料として InGaAs を用いて維持されるステップをさらに含む請求項 2 に記載の方法。 30

**【請求項 10】**

所望の格子定数と整合するバッファー層を形成するステップをさらに含む請求項 2 に記載の方法。

**【請求項 11】**

カーボンを用いて活性領域の p - 型ドーピング部を成長させるステップをさらに含む請求項 3 に記載の方法。

**【請求項 12】**

デバイ長ドーピングを用いて前記基板上に少なくとも 1 つの層を形成するステップをさらに含む請求項 2 に記載の方法。 40

**【請求項 13】**

前記歪んだ超格子層が、

小さな歪みと、

中間の歪みと、

大きな歪みとを、前記歪んだ超格子層の個々の層が転位を起こすほど厚くないように含む請求項 2 に記載の方法。

**【請求項 14】**

MOCVD を用いて前記歪んだ超格子層を作るステップをさらに含む請求項 13 に記載の 50

方法。

【請求項 1 5】

活性領域の n - 型部を成長させるステップをさらに含む請求項 3 に記載の方法。

【請求項 1 6】

前記基板上に少なくとも 1 つの勾配材料を形成する結果作られた転位材料を絶縁する、少なくとも 1 つのアニーリングした勾配層と、

半導体装置を成長するために前記少なくとも 1 つの勾配層の上に構成した、歪んだ超格子層と、

を含む基板上に形成した半導体装置。

【請求項 1 7】

前記少なくとも 1 つの勾配層が、(100) 配向基板上に逆勾配を用いて形成される請求項 1 6 に記載の半導体装置。

【請求項 1 8】

前記少なくとも 1 つの勾配層を、MOCVD を用いて成長させる請求項 1 7 に記載の半導体装置。

【請求項 1 9】

前記基板が GaAs 基板を含む請求項 1 7 に記載の半導体装置。

【請求項 2 0】

前記基板がゲルマニウム基板を含む請求項 1 7 に記載の半導体装置。

【請求項 2 1】

前記基板がシリコン基板を含む請求項 1 7 に記載の半導体装置。

【請求項 2 2】

前記半導体装置がフォトダイオードを含む請求項 1 8 に記載の半導体装置。

【請求項 2 3】

前記少なくとも 1 つの勾配層が、大量の n - 型ドーピングを用いて形成され、勾配材料の導電性が、前記勾配材料として InGaAs を用いて、大きく転位した領域を通して維持される請求項 1 8 に記載の半導体装置。

【請求項 2 4】

所望の格子定数に整合するように前記基板から形成したバッファー層をさらに含む請求項 1 7 に記載の半導体装置。

【請求項 2 5】

前記歪んだ超格子層から形成した下部境界領域と、

前記下部境界領域上の前記歪んだ超格子層から形成した活性領域と、

前記活性領域から形成した上部境界領域と、

前記上部境界領域上に形成したキャップと、

前記キャップおよび上部境界領域中に形成した拡散領域と、

前記基板からその上に構成され、その上に高速のフォトダイオードを形成することのできる金属層とをさらに含む請求項 1 9 に記載の半導体装置。

【請求項 2 6】

前記拡散領域が P + 拡散領域を含む請求項 2 5 に記載の半導体装置。

【請求項 2 7】

前記活性領域が、

部分的に n - 活性領域と、

部分的に p - ドーピングした活性領域とを含む請求項 2 5 に記載の半導体装置。

【請求項 2 8】

前記下部境界領域が N 下部境界領域を含む請求項 2 5 に記載の半導体装置。

【請求項 2 9】

前記歪んだ超格子層が、

小さく歪んだ領域と、

中間に歪んだ領域と、

10

20

30

40

50

大きく歪んだ領域とを、前記歪んだ超格子層の個々の層が転位を起こすほど厚くないよう

に含む請求項 16 に記載の半導体装置。

【請求項 30】

前記勾配層を MOCVD を用いて成長させる請求項 18 に記載の半導体装置。

【請求項 31】

前記勾配層が公称 (100) の配向基板上に形成される請求項 16 に記載の半導体装置。

【請求項 32】

前記キャップが前記半導体装置の上から除去される請求項 25 に記載の半導体装置。

【請求項 33】

基板上に半導体装置を製造する方法であって、前記方法が、

勾配層を公称 (100) の配向基板上に形成し、前記勾配層が、前記半導体装置のために用いられる格子定数を超えて基板の格子定数に勾配を付けるステップと、

中間層を形成するステップであって、前記中間層が、前記半導体装置のために用いられる前記格子定数よりも大きい格子定数を有する、ステップと、

前記中間層の前記格子定数から前記半導体装置のために用いられる前記格子定数へ勾配を付ける逆勾配層を形成するステップと、

前記勾配層をアニーリングして、前記基板から前記勾配層を形成する結果作られた転位材料を絶縁するステップと、

歪んだ超格子層を作り、その上に形成された前記半導体装置からさらに転位を絶縁するステップとを含む方法。

【請求項 34】

基板上に半導体装置を製造する方法であって、前記方法が、

MOCVD を用いて前記基板上に勾配層を形成し、前記勾配層が、前記半導体装置のために用いられる前記格子定数を超えて基板の格子定数に勾配を付けるステップと、

中間層を形成し、前記中間層が前記半導体装置に使用される格子定数よりも大きな格子定数を有するステップと、

前記中間層の前記格子定数から前記半導体に使用される前記格子定数へ勾配を付ける逆勾配層を形成するステップと、

前記勾配層をアニーリングして、前記基板から前記勾配層を形成する結果作られる転位材料を絶縁するステップと、

歪んだ超格子層を作り、その上に形成される前記半導体装置からさらに転位を絶縁するステップとを含む方法。

【請求項 35】

GaAs 基板上に半導体装置を製造する方法であって、前記方法が、

前記 GaAs 基板上に勾配層を形成し、前記勾配層が、前記半導体装置のために用いられる前記格子定数を超えて基板の格子定数に勾配を付けるステップと、

中間層を形成するステップであって、前記中間層が前記半導体装置に使用される格子定数よりも大きな格子定数を有する、ステップと、

前記中間層の前記格子定数から前記半導体に使用される前記格子定数へ勾配を付ける逆勾配層を形成するステップと、

前記勾配層をアニーリングして、前記 GaAs 基板から前記勾配層を形成する結果作られる転位材料を絶縁するステップと、

歪んだ超格子層を作り、その上に形成される前記半導体装置からさらに転位を絶縁するステップとを含む方法。

【請求項 36】

基板上に半導体装置を製造する方法であって、前記方法が、前記半導体装置を製造するためにデバイスドーピングを用いて前記基板上に少なくとも 1 つの層を形成するステップを含む方法。

【請求項 37】

GaAs 基板上に半導体装置を製造する方法であって、前記方法が、

10

20

30

40

50

MOCVDを用いて前記GaaS基板上に勾配層を形成し、前記勾配層が、前記半導体装置のために用いられる前記格子定数を超えて基板の格子定数に勾配を付けるステップと、中間層を形成するステップであって、前記中間層が前記半導体装置に使用される格子定数よりも大きな格子定数を有する、ステップと、

前記中間層の前記格子定数から前記半導体に使用される前記格子定数へ勾配を付ける逆勾配層を形成するステップと、

前記勾配層をアニーリングして、前記GaaS基板から前記勾配層を形成する結果作られる転位材料を絶縁するステップと、

歪んだ超格子層を作り、その上に形成される前記半導体装置からさらに転位を絶縁するステップとを含む方法。

10

【請求項38】

GaaS基板上に半導体装置を製造する方法であって、前記方法が、

MOCVDを用いて前記GaaS基板上に勾配層を形成し、前記勾配層が、前記半導体装置のために用いられる前記格子定数を超えて基板の格子定数に勾配を付けるステップと、中間層を形成するステップであって、前記中間層が前記半導体装置に使用される格子定数よりも大きな格子定数を有する、ステップと、

前記中間層の前記格子定数から前記半導体に使用される前記格子定数へ勾配を付ける逆勾配層を形成するステップと、

前記勾配層をアニーリングして、前記GaaS基板から前記勾配層を形成する結果作られる転位材料を絶縁するステップと、

20

歪んだ超格子層を作り、その上に形成される前記半導体装置からさらに転位を絶縁するステップとを含む方法。

【請求項39】

GaaS基板上に半導体装置を製造する方法であって、前記方法が、

MOCVDを用いて前記GaaS基板上に勾配層を形成し、前記勾配層が、前記半導体装置のために用いられる前記格子定数を超えて基板の格子定数に勾配を付けるステップと、中間層を形成し、前記中間層が前記半導体装置に使用される格子定数よりも大きな格子定数を有するステップと、

前記中間層の前記格子定数から前記半導体に使用される前記格子定数へ勾配を付ける逆勾配層を形成するステップと、

30

前記勾配層をアニーリングして、前記GaaS基板から前記勾配層を形成する結果作られる転位材料を絶縁するステップと、

歪んだ超格子層を作り、その上に形成される前記半導体装置からさらに転位を絶縁し、前記GaaS基板が、公称(100)配向の基板を含むステップとを含み、

前記層の各々が前記GaaS基板上にデバイ長ドーピングを用いて形成される方法。

【請求項40】

基板上に成長する半導体装置であって、前記半導体装置が長波長変性フォトダイオードを含む装置。

40

【請求項41】

前記長波長変性フォトダイオードをMOCVDによって前記基板上に成長させる請求項40に記載の半導体装置。

【請求項42】

前記基板が、公称(100)配向の基板を含む請求項40に記載の半導体装置。

【請求項43】

前記基板が、GaaS基板を含む請求項40に記載の半導体装置。

【請求項44】

前記長波長変性フォトダイオードを、前記基板の少なくとも1つの層にデバイ長ドーピングを用いて前記基板上に成長させる請求項40に記載の半導体装置。

50

【請求項45】

前記基板が GaAs 基板を含む請求項 4 1 に記載の半導体装置。

【請求項 4 6】

前記基板が、公称 (100) 配向の基板である請求項 4 5 に記載の半導体装置。

【請求項 4 7】

前記長波長変性フォトダイオードを、前記基板の少なくとも 1 つの層にデバイ長ドーピングを用いて前記基板上に成長させる請求項 4 6 に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置および同品を製造する方法に関する。また、本発明はフォトダイオード装置および同品を製造する方法に関する。加えて本発明は高速の、長波長フォトダイオード、および同品を製造する改善された方法に関する。さらに、本発明は基板上に半導体フォトダイオードを成長する技術に関する。

10

【0002】

急速な光波通信の開発に伴い、低コストで高性能の光フォトダイオードが多くのシステム用途のために必要とされている。フォトダイオードは光を照射すると大きな光電流を発生する p - n 接合半導体装置である。フォトダイオードは、電磁照射を吸収することによって p - n 接合半導体の導電性が高くなる光導電性の原理に基づいている。光導電性はある材料の可視スペクトルの照射作用によってもたらすことができる。

20

【背景技術】

【0003】

現在使用されているフォトダイオードには 2 つの主要なクラスがある。これらは空乏層ダイオードおよびアバランシェダイオードである。空乏層フォトダイオードは特定の降伏電圧未満で動作する逆バイアスされた p - n 接合形態に基づく。所望の波長の電磁照射に露出すると、吸収の結果、過剰の電荷キャリアを発生させることができる。その電荷は電子 - 正孔対として形成することができる。これらの電子 - 正孔対は接合の空乏層中または近傍に接合をまたいで生成し、光電流を発生する。アバランシェダイオードは特定の降伏電圧以上で動作する逆方向にバイアスされた p - n 接合形態に基づく。入射された照射によって発生した電子 - 正孔対の電流増倍は、フォトダイオード技術で良く知られた“アバランシェプロセス”によって起きる。

30

【0004】

半導体フォトダイオードは任意の半導体から作ることができ、一般に集積回路の製造に用いられるものと同じ単結晶シリコンウェーハから作られる。長波長（例えば、1310 nm および 1550 nm）フォトダイオードは、一般にリン化インジウム（InP）と同じ公称格子定数を有する InGaAs から作られる。

【0005】

現在、長波長（約 1200 nm ~ 1650 nm）の高速フォトダイオードは全て、リン化インジウム（InP）基板上に成長させる。長波長域で動作するフォトダイオード受光素子の集積化にはヒ化インジウムガリウム（InGaAs）の p - i - n 光検出素子を必要とし、したがって層の歪みを避けるために InP 基板に基づく技術を必要とし、これは格子の不整合によって合致しない転位を招く。しかし、シリコン（Si）およびヒ化ガリウム（GaAs）とは異なり、InP は十分確立されていないし非常に脆い。加えて、InP 基板は高価であり、GaAs または Si と同じ大きさのサイズでは入手できない。最後に、InP 上の気相エピタキシャル成長はホスフィンを使用することが必要であるが、これは多くの場合特別なエピタキシャルシステムには入手できず、いくつかの技術的な問題を招く。

40

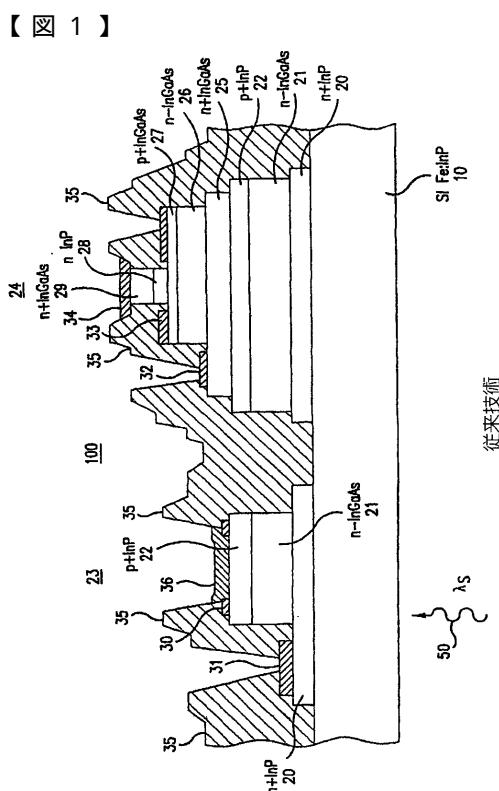

【0006】

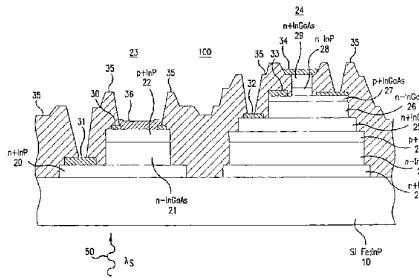

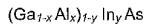

図 1 は従来技術のモノリシック集積受光素子の断面を示し、従来技術の受光素子の製造技術を示している。図 1 に示すように、受光素子 100 は p - i - p フォトダイオードに波長  $\lambda$  で衝突する光ビーム 50 を検出して増幅することができ、波長は、他の理由の中で

50

もInP半導体がこれらの波長に透明であることから、1.0 μmよりも大きく選択することができる。その集積受光素子は材料の適合性があり、各装置が他と物理的に分離されると同時に電気的に絶縁されているので、光子と電子の機能を分離して最適な制御を行うことができる。しかし、材料の適合性、分離された最適化制御にもかかわらず、その装置は比較的高価であり、脆弱で加工が困難であり、複雑な素子への集積化を必要とするに注目することが重要である。HBTの下地となる半導体層は、構造的にフォトダイオードを形成するようになっているが、電気的にまたは光的に活性ではないことに注目すべきである。

## 【0007】

図1に示す従来技術の受光素子構造では、フォトダイオードおよびヘテロ構造のバイポーラトランジスタはInP/InGaAs材料システムから選択された半導体層を有し、パターニングしない、FeをドープしたInP基板上に成長させる。

## 【0008】

有機金属気相エピタキシャル成長(MOVPE)、湿式選択化学エッチング、反応性イオンエッチング、および接触金属化を含んで、標準の製造技術が図1に示す従来技術の製造に用いることができる。これらの製造技術は当技術の通常の技術者に良く知られていることであり、したがって、ここでは詳細は論じない。

## 【0009】

図1に示す従来技術の装置は、平坦なFeをドープした<001>配向のInP基板10上にエピタキシャル成長することができる。p-i-nエピ層は4000厚さのInP層20、1.0 μm厚さのInGaAs層21、および4000厚さのInP層22を含み、これはMOVPEによって半絶縁基板10上に成長することができる。半導体層20、21、22はしたがってp-i-nフォトダイオード23を形成することができる。

## 【0010】

ヘテロ構造のバイポーラトランジスタ(HBT)24のエピタキシャル層は、各エピ層の被着の間に間入するプロセスがないように、構造全体の上に成長することができる。即ち、成長を連続的に中断しないで運転することができる。HBT24はサブコレクタ層25、コレクタ層26、ベース層27、エミッタ層28、およびエミッタキャップ層29を含むことができる。HBT24は単一のヘテロ構造の装置として構成され、一方、光検出素子23は光吸収層21を有することに注目すべきである。

## 【0011】

フォトダイオードおよびヘテロ構造のバイポーラトランジスタエピタキシャル層を成長した後、湿式化学エッチングを行ってそのメサ構造を実現することができる。湿式化学エッチングに関しては、メサ構造の幾何学的形状を保つように、フォトレジストのパターニングを[001]および[001]結晶方向の平面に対して45度に配向することができる。言い換えれば、装置、即ちフォトダイオード23およびHBT24の線の構造が[001]および[001]方向の平面に対して45度になるように配線することができる。

## 【0012】

AuGe/AuおよびAuZn/Auなど、従来のオーミックコンタクトをメサの横方向の端部に被着させ、層20、サブコレクタ25、ベース層27、およびエミッタキャップ層29に、それぞれオーミックコンタクト31、32、33および34を提供することができる。オーミックコンタクトの製造には標準の金属被着技術を用いることにして注目すべきである。加えて、光検出素子23では、輪状の合金オーミックコンタクト30が層22へのコンタクトを提供することができる。輪状のオーミックコンタクト30は、当技術で良く知られた蒸発およびリフトオフ技術を含んで標準のフォトリソグラフィ技術で形成することができる。

## 【0013】

吸収されなかった光ビーム50を光吸収領域21に反射し、したがって量子効果を高めるには、非合金のCr/Au金属コンタクト36をコンタクト30の輪状開口中に被着させることができる。スピノコートしたポリイミドなど、平坦化およびパッシベーションの後

10

20

30

40

50

、オーミックコンタクトにリード（示していない）を取り付け易くするために、ポリイミドを酸素プラズマ中の反応性イオンエッティングを用いてその中に窓を開けることができる。製造の後、バックサイド照明が可能となるように基板10を薄く研磨することができる。

#### 【0014】

前述に基づいて、当業者であれば、InP基板上にフォトダイオードを成長するような、従来技術の半導体装置を製造する方法は高価で脆弱であり、加工が困難であり、さらに素子に組み上げるのが難しいことを認識することができよう。その加工の複雑さはまた非効率性と製造費用の増加を招く。したがって、加工の複雑さの観点から、受光素子などの高速フォトダイオードに基づく高速のフォトダイオードおよび装置を形成する代替の技術を開発することが望まれている。本発明者は本明細書に開示したその技術および装置を開発し、従来技術の半導体装置の製造に内在する非効率性を克服した。

#### 【0015】

本発明の以下の概要は、本発明に独特の発明的な特徴のいくつかを理解するのが容易なように提供するものであって、全てを記述しようとするものではない。本発明の様々な態様の完全な認識は、全明細書、請求項、図面および要約を一体として把握することによって得ることができる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0016】

本発明の一態様は基板上に成長した高速フォトダイオードを提供することである。

本発明の他の態様は高速フォトダイオードを基板上に成長する方法を提供することである。

#### 【0017】

本発明のさらに他の態様は、GaAs基板上に成長した長波長のフォトダイオードを提供することである。

本発明のさらに他の態様は、超格子含有基板および変性エピタキシャル成長技術を用いて形成した、変性長波長高速フォトダイオードを提供することである。

#### 【課題を解決するための手段】

#### 【0018】

上述の、および他の態様はこれからの説明のように達成される。即ち、変性長波長高速フォトダイオードを製造する方法および装置が開示され、基板の格子定数に整合するバッファー層が通常の成長温度で形成することができ、所望の格子定数を越える薄い勾配をつけた領域が低い温度で構成される。この勾配をつけた領域の上に、その格子定数が勾配の最終格子定数であり所望の格子定数を超える、薄い層を低い温度で再び構成することができる。

#### 【0019】

次いで、所望の格子定数と整合させるために、逆方向の勾配を実施することができる。その後、その上に所望の格子定数に基づく厚い層が形成される。次いで、勾配層中、逆勾配層中、およびその間の層中の転位した材料を絶縁するためにアニールを行うことができる。次いで、歪んだ超格子層をその上に形成することができ、その上に高速フォトダイオードを形成することができる。歪んだ超格子層はさらに変性転移によって生じた合致しない転位からフォトダイオードを絶縁する。用語「勾配をつけた層」と「勾配をもつ層」は一般に同意語であり本明細書では互換性をもって使用される。

#### 【0020】

歪んだ超格子層の上にフォトダイオードの構造を作ることができる。注入層または拡散層をBe、Mg、C、Si、Se、Te、SまたはZnなどの材料をベースにして形成することができる。N-活性領域の上に直接位置するP+領域上のキャップエッチの上に金属層を形成することができる。高速フォトダイオードはこのようにしてGaAs上に形成することができ、はるかに安価で脆弱ではなく、素子に構成するのが容易である。フォトダ

10

20

30

40

50

イオードの形成はエピタキシャル成長技術としてMOCVDを用いて達成することができるが、当業者であれば、MBEなどの他の成長技術も本明細書に記載された方法および装置に従って用いることができることを認識することができよう。好ましい基板の配向は公称配向で(100)である。当業者であれば、本明細書に使用されている用語(100)が(100)、<100>、または[100]として表すことができ、あるいは音声的に“1-0-0”と発音され、図1に関して使用されている参照番号100と混同されることを認識するであろう。

#### 【0021】

さらに付随する図面は、同じ参照番号が異なる図面を通して同一のまたは機能的に同一の要素を表し、明細書に組み込まれて明細書の部分を形成しており、本発明を図解し、発明の詳細な説明とともに、本発明の原理の説明に役立てるものである。

10

#### 【発明を実施するための最良の形態】

#### 【0022】

これらの非制限的な例で論じられる特定の値および形態は変更を加えることができ、主として本発明の実施形態を説明するために引用しているものであって、発明の範囲を制限しようとするものではない。

#### 【0023】

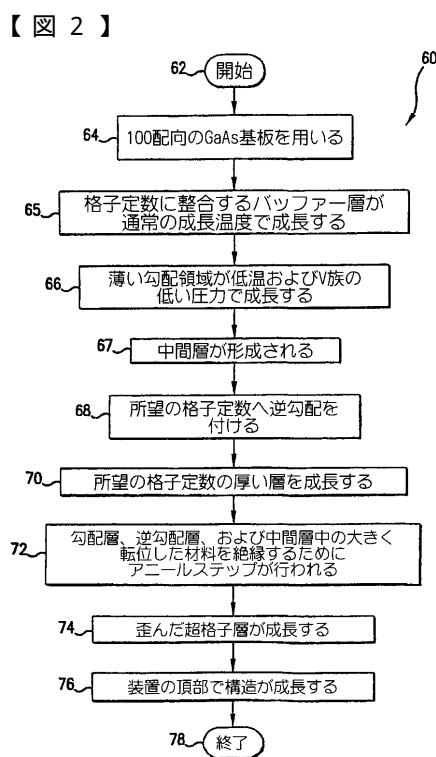

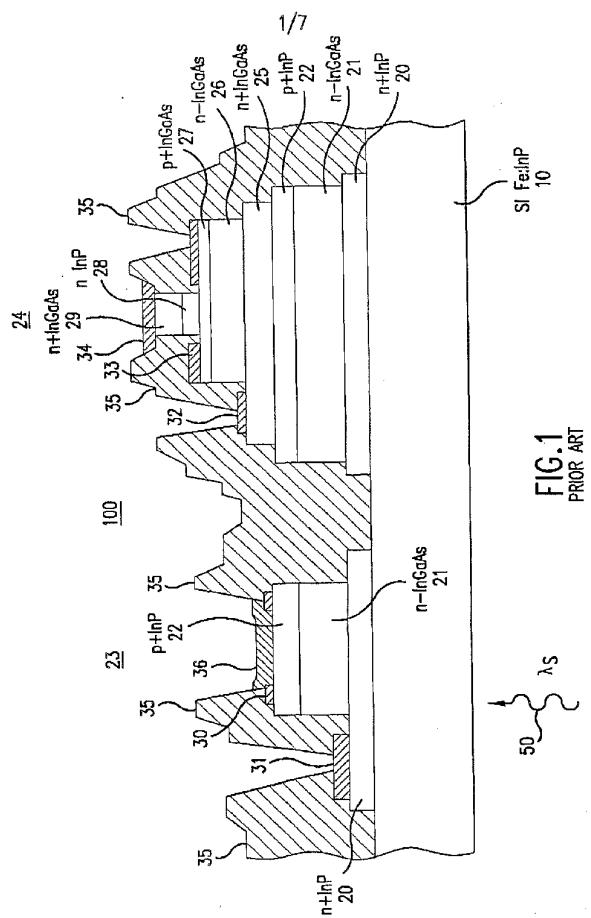

図2は本発明の好ましい実施形態によって半導体装置を製造する作業ステップを示すフロー図である。フォトダイオードは本明細書に開示されているステップおよびプロセスによって製造することのできる半導体装置の1つの種類である。したがって、フォトダイオード装置は図2に示す作業に従って作ることができる。勾配付け、中間層、逆勾配付け、公称(100)配向のGaAs基板、インシトゥーのアニーリング、および歪んだ超格子層を用いることによって、人工基板を作ることができ、その上に長波長フォトダイオードなどの半導体装置が製造される。

20

#### 【0024】

歪んだ超格子層は個々の層のいずれも転位を生成するほどには厚くなく、しかしこの厚さが高い歪み領域に近づくように、低い歪み、中間の歪み、および高い歪みから構成することができる。本明細書に記載した方法によるフォトダイオードの成長は、それらが広い範囲の波長で動作するように設計することができるので、“長波長”フォトダイオードと呼ぶことができる。好ましい実施形態では波長の範囲は、通常通信に使用されている、公称1550ナノメートルおよび1310ナノメートルの波長である。

30

#### 【0025】

勾配をもつ領域に多量のn-ドープを用い、勾配を付ける材料としてInGaAsを用いることによって、大きく転位した勾配領域に導電性を保つことができる。当業者であれば、“ドーピング”が、所望のn-導電性またはp-導電性(すなわち、p-型ドーピングの場合)を得るために、特定の種類の不純物を添加することを認識するであろう。ドナー不純物はn-型半導体を形成するために加えられる。アクセプター不純物は一般にp-型半導体を形成する。

#### 【0026】

比較的薄い勾配の、および(100)配向の基板を使用することによって、表面の形態は十分な装置の加工性を備えるであろう。加工はエピタキシャル成長技術としてMOCVDを用いて達成できる。当業者ならば、本発明に従って、当技術分野で良く知られているMBEを含んで、他の成長技術を用いることもできることを認識できよう。

40

#### 【0027】

すなわち、図2に示すようにプロック62でプロセスが開始する。本明細書に記載された方法によるフォトダイオード装置を構成するために、プロック64に示されている(100)に配向しているGaAs基板を使用することができる。基板として、それが他の基板材料よりも脆弱でなく高価でないことから、GaAsを用いることが好ましい。加えて、GaAsの使用はリンの供給源を必要としない。しかし、当業者であれば、本発明に従って、ゲルマニウムまたはシリコンなどの基板を含んで他の基板を使用できることが認識で

50

きよう。

【0028】

ブロック65に示すように、最初に、格子定数に整合するバッファー層を常温で成長させることができる。その後、ブロック66で説明したように、所望の格子定数を越える勾配をもつ薄い勾配領域を、低温およびV族の低い圧力で成長させることができる。次に、ブロック67に示すように、勾配をつけた層の最終端組成物の格子定数をもつ薄い中間層を成長させることができる。中間層は、中間層が所望の格子定数よりもわずかに大きな格子定数を有するように形成される。

【0029】

次に、ブロック68に示すように、所望の格子定数への逆勾配付けを行うことができる。10 このような勾配付けは三次元成長を防止し、これらの層への転位を絶縁するのに有用である。勾配の代わりに段差を用いると、三次元に島の成長が起こり、材料の品質を劣化させる。

【0030】

その後、ブロック70に示すように、低温で開始し温度を上昇させることによって、所望の格子定数をもつ厚い(約0.5ミクロン)層が形成される。

ブロック72に示すように、次いでアニーリングステップを実施し、勾配を付けた層、逆勾配を付けた層、およびその間の一定組成物層中の大きく転位した材料を絶縁することができる。次いで、ブロック74に示すように、歪んだ超格子層を、個々の厚さが臨界の厚さに近く、しかしそれを超えない厚さに成長させることができる。これは転位ループを排除し、後続の成長材料の品質を向上させる。

【0031】

最後に、ブロック76に示すように、装置の構造をこれらの層の上に成長させることができる。光検出素子(すなわちフォトダイオード)用の装置構造は、下部境界層へA1組成物の傾斜(ramp)が続く、バッファー層とすることができる。下部の境界層は遅いテール応答を防止する。下部境界層にA1の傾斜層(ramp down layer)を備える他の層を成長させ、活性領域の組成物へ勾配を付けることができる。勾配は装置の良好な導電性を確実にするために用いることができる。これらの傾斜はガリウム対アルミニウム比の勾配であり、意図的に格子定数を変更せずにエネルギー・バンドギャップを変化させる。

【0032】

活性領域は下部が公称3ミクロン厚さの、 $5 \times 10^{15}$ 未満ドーピングしたn-型とすることができ、上部に公称1ミクロンのp-型部を有することができる。活性領域が速度のために少なくとも部分的にn-型活性領域であるように構成され、加えて、活性領域のn部がキャパシタンスのために $5 \times 10^{15}$ 未満のn-ドーピング値を有することが重要である。この材料では、背景のn-ドーピングは公称n-型とすることができ、または下部層からのn-拡散テールが存在する所以で、実効ドーピングを $5 \times 10^{15}$ 未満に減少させるために、そのドーピング効率の低さからカーボンを使用して、逆ドーピングを行うことができる。

【0033】

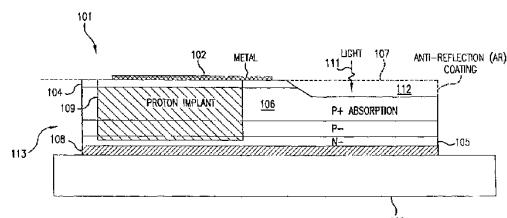

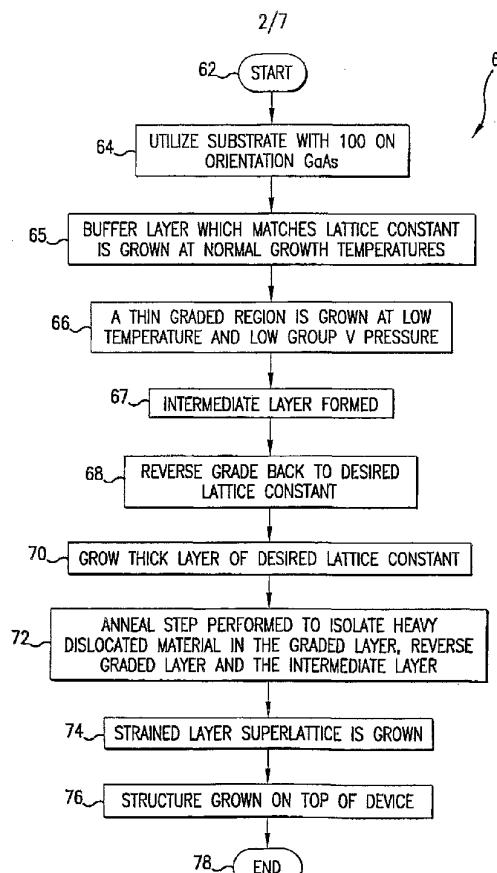

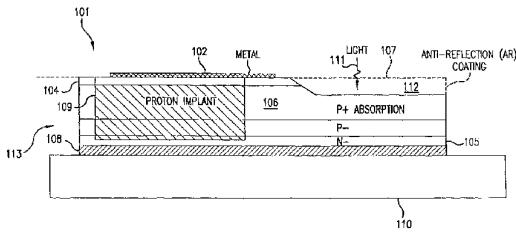

図3は本発明の好ましい実施形態による、フォトダイオード装置用の構造を示すブロック図101を示す。図3に示すブロック図では、変性層110を成長させ、その上に半導体フォトダイオード装置を構成することのできる基板構造を作ることができる。下部の境界層108は変性層110の上に重ねることができる。活性層105は下部の境界層108の上に成長させることができる。導電層106はキャップ104および金属層102の下に位置することができる。領域109はプロトン注入域を表す。キャップ104および導電層106の一部は光が活性領域へ伝達されるようにエッチングされる。

【0034】

反射防止(AR)コーティング112は、図3中に導電層106の上の破線で囲まれて示されている。ARコーティング112は窒化シリコンまたは当業者には明らかな他の材料

10

20

30

40

50

から構成することができる。光 111 は矢で示され、反射防止 (A R) コーティング 112 に入射されている。光 111 の吸収は、導電層 106 と活性層 105 を通して起きる。溝 113 は溝エッティングに基づくことができ、プロトン注入域に沿って絶縁を提供し、キャパシタンスを低下させる。溝 113 は下部境界層 108 中に展延しなければならない。当業者であれば、本明細書に記載された方法に従ってフォトダイオードを加工するのに使用できる、多くの変更が存在することを認識するであろう。

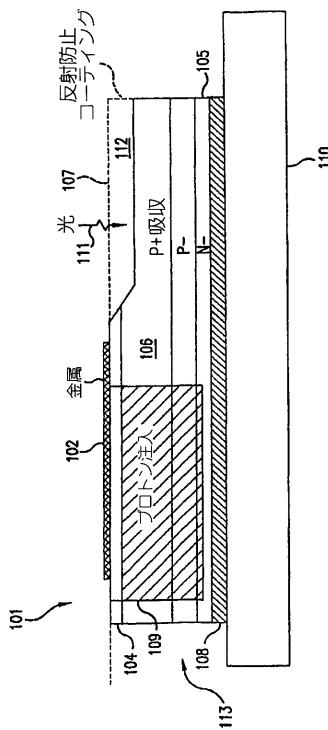

#### 【0035】

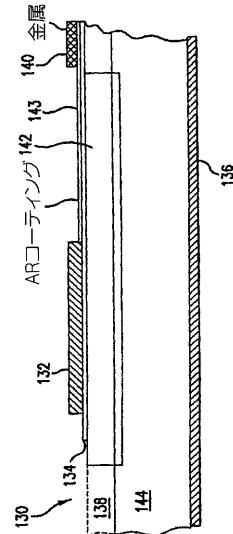

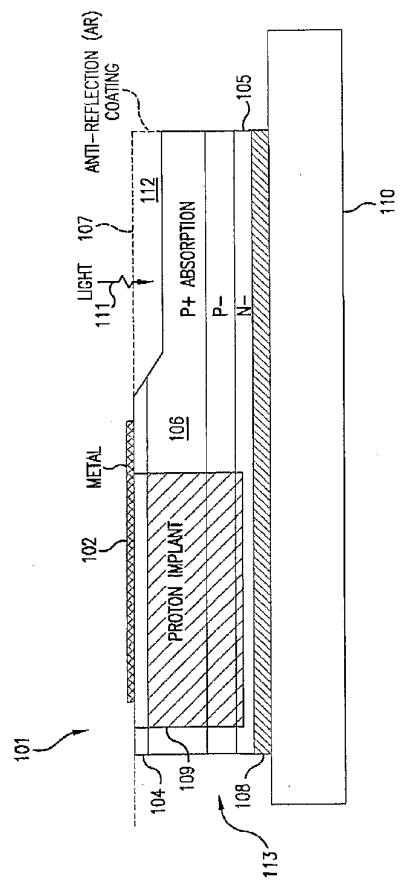

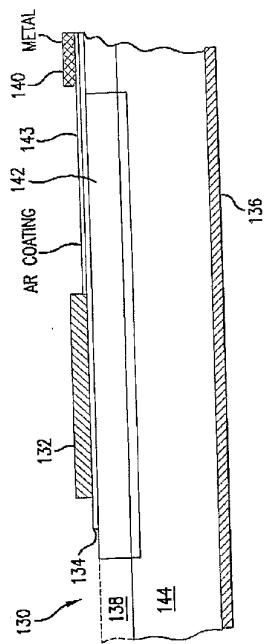

図 4 は本発明の好ましい実施形態による、フォトダイオード装置用の別法のエピタキシャル成長構造を示すブロック図 130 である。図 4 に示すように、金属層 132 はオーミックコンタクトのためにキャップ 134 の上に位置することができる。キャップ 134 は任意選択的なキャップエッティングの一部として、少なくとも活性層の上を部分的に除去できることに注目すべきである。P+拡散領域 142 は N-キャップ 134、上部の N-境界層 138 を通って活性領域 144 の上部に展延することができる。

#### 【0036】

n-上部境界層 138 はバンドギャップを増加させるのに十分な A1 を含むことができ、それによって吸収が少ないので、特有の波長の窓として働くことができる。また、この上部境界層は、それが p-拡散領域中に R-C 定数を低くする多量の p-ドーピングを有するので、導電性を提供するためにも使用することができる。フォトダイオードの応答時間が、電荷収集時間、および直列のプラスの付加抵抗および接合および歪みキャパシタンスから生じる R-C 時定数の和の平均二乗根であるので、このことは重要である。キャップ 134 はオーミックコンタクトに使用される、多量にドーピングした材料に基づく狭バンドギャップとして構成することができる。

#### 【0037】

また、横方向の p-n 接合の上の、光がこの領域に入って応答を遅くすることを防止する金属層 140 が図 4 に示されている。金属層 140 は A R コーティング 143 によって半導体から絶縁することができる。P+拡散層 142 は、Be、Mg、またはZn の注入または拡散から形成することができる。ある場合には、Be 注入および拡散技術が好ましい。しかし、当業者であれば、本発明の好ましい実施形態に従って他の注入および拡散技術が使用できることが認識できよう。N-活性領域 144 は P+拡散層 142 の下に位置している。N 下部境界層 136 は N-活性領域 144 の下に位置している。

#### 【0038】

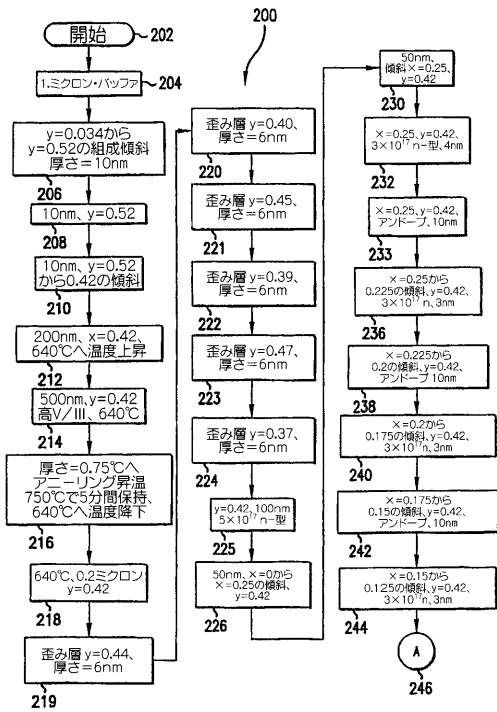

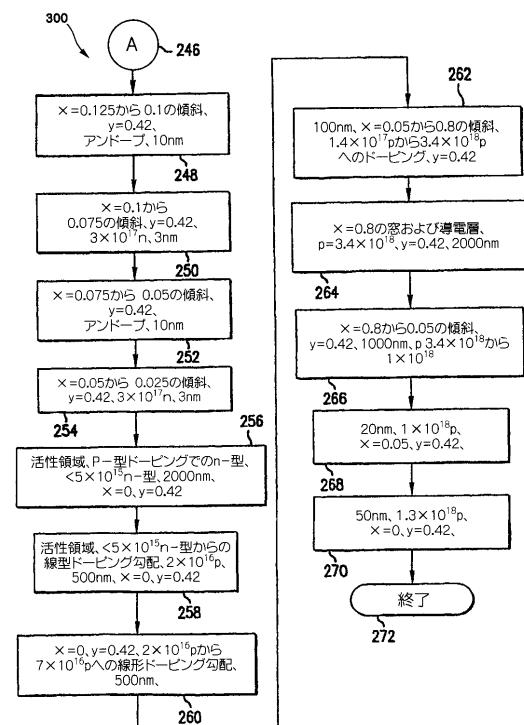

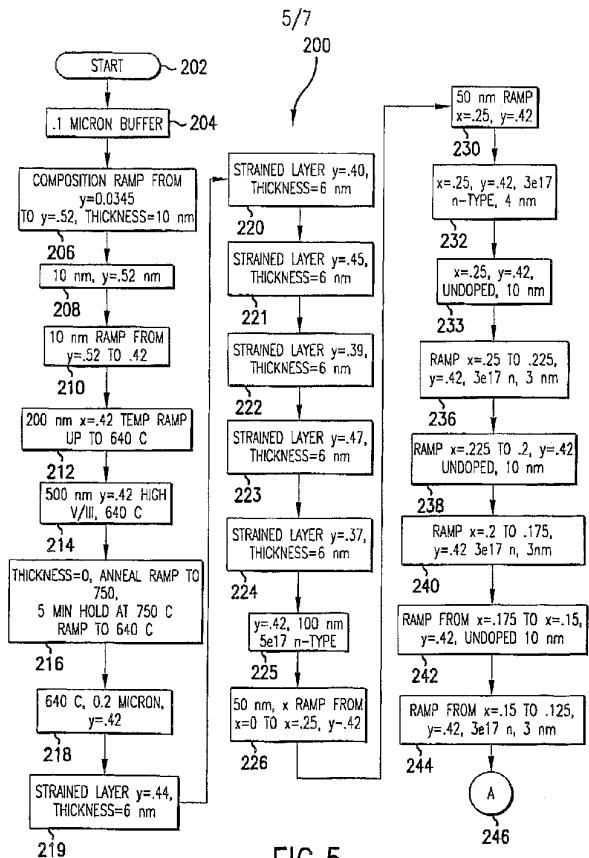

図 5 は、本発明の好ましい実施形態による、高速フォトダイオードを形成するエピタキシャル成長プロセスを示す作業のフロー図 200 を示している。フロー図 200 は図 6 に示すフロー図 300 に続くことに注意されたい。図 6 のフロー図 300 は図 5 のフロー図 200 の後続である。プロセスはブロック 202 で示すところで開始する。図 5 に関して本明細書で述べる x および y の値は一般に次の式に基づいている。

#### 【0039】

$$(G a_{1-x} A_{1-x})_{1-y} I_{n_y} A_s$$

最初に、ブロック 204 に示すように、基板の格子定数に整合する 0.1 ミクロンのバッファー層を通常の成長温度で成長させることができる。その後のブロック 206 で示すように、y = 0.0345 から y = 0.52 の傾斜組成物 (1300 nm の検出素子用) を 10 nm の厚さに作ることができる。次にブロック 208 で示すように、y = 0.52 で 10 nm の層を成長させることができる。

#### 【0040】

ブロック 210 に示すように、y = 0.52 から 0.42 の 10 nm の傾斜層を成長させることができる。後で示すように、ブロック 212 では、200 nm の層を形成することができ、温度上昇 640 で y = 0.42 である。次にブロック 214 で示すように、y = 0.42、高 V/I II、温度 640 で 500 nm 層が形成される。次いでブロック 216 で述べるように、アニーリング、温度上昇 750、750 で 5 分間の保持、640 への温度降下に基づいて、厚さが 0 に等しい層を形成することができる。ブロック

10

20

30

40

50

218で示すように、形成される次の層は、640、0.2ミクロン、 $y = 0.42$ に基づいている。

【0041】

その後、ブロック219に示すように、 $y = 0.44$ の歪んだ層が形成される。この層は約6nmの厚さである。ブロック220に示すように、厚さ約6nmの $y = 0.40$ の歪んだ層が形成される。ブロック219から220に関して示す、歪んだ層の形成は、約100周期にわたって起きることに注目されたい。 $y = 0.45$ 、厚さ6nmの歪んだ層がブロック221に示すように形成される。ブロック222に示すように、厚さ6nm以上の $y = 0.39$ の歪んだ層が形成される。ブロック221から222に関して示す、歪んだ層の形成は、約100周期にわたって起きることに注目されたい。その後、ブロック223に示すように、 $y = 0.47$ および厚さ6nmの歪んだ層が形成される。次いで、ブロック224に示すように、 $y = 0.37$ および厚さ6nmの歪んだ層が形成される。ブロック223から224に関して示す、歪んだ層の形成は、約100周期にわたって起きることに注目されたい。その後、ブロック225に示すように、 $y = 0.42$ 、厚さ100nmの層が形成される。ブロック226に示すように、50nmの層を、 $x = 0$ から $x = 0.25$ のx傾斜値、およびy値0.42で形成することができる。

【0042】

プロセスの次のステップは、ブロック230に示すように、 $x = 0.25$ および $y = 0.42$ の組成物を有する50nmの層を形成することを含む。この層はその後に形成される層よりも導電性を高めるために多くドーピング( $5 \times 10^{17}$ )されている。この層の形成に続いて、ブロック232に示すように、 $x = 0.25$ 、 $y = 0.42$ の層を形成することができる。この層は $3 \times 10^{17}$ で約4nmの厚さのn-型であることに注目されたい。次にブロック233に示すように、 $x = 0.25$ 、 $y = 0.42$ の層を、ドーピングしない10nmの厚さで形成することができる。デバイ(Deby e)長ドーピングがブロック232および233に示されたステップを通じて80周期にわたって起きることに注目されたい。デバイ長ドーピングは、実際に意図的にドーピングするには低すぎる、低ドーピングを制御する方法である。デバイ長ドーピングでは、ドーピングはほんの短時間に低レベルで周期的に起動される。これらのドーピングした領域間の距離がデバイ長またはドープ剤の拡散長よりも短い場合には、それは平均したドーピングで全領域にわたって効率的にドーピングされている。そのステップは活性領域に隣接するシリコンの拡散を最小に保つために必要であろう。このようにして、デバイ長ドーピングを用いて基板上に特別の領域を成長させることができる。

【0043】

その後のブロック236に示すように、 $x = 0.25$ から $x = 0.225$ の傾斜層が形成される。また、このステップで $y = 0.42$ である。ブロック236に述べたステップの結果として形成される層は約3nmの厚さの層を有し、 $3 \times 10^{17}$ nmのn-型ドーピングに基づく。その後のブロック238に示すように、 $x = 0.225$ から0.2、 $y = 0.42$ 、ドーピングしない10nmの厚さの傾斜が起きる。ブロック240に示すように、 $y = 0.42$ で $x = 0.2$ から $x = 0.175$ の傾斜が起きる。形成された、得られる層は3nmの厚さを有し、 $3 \times 10^{17}$ nmのn-ドーピングに基づく。その後ブロック242に示すように、次の層の形成では $y = 0.42$ で $x = 0.175$ から $x = 0.15$ の傾斜が起きる。ブロック242に述べた作業の結果形成された層は、ドーピングしない10nmの厚さを有する。次いで、ブロック244に示すように、 $x = 0.15$ から $x = 0.125$ 、および $y = 0.42$ の傾斜が起き、3nmの厚さを有し、および $3 \times 10^{17}$ nmのn-型ドーピングに基づく層が形成される。プロセスはコネクタブロック246に示すように、継続する。

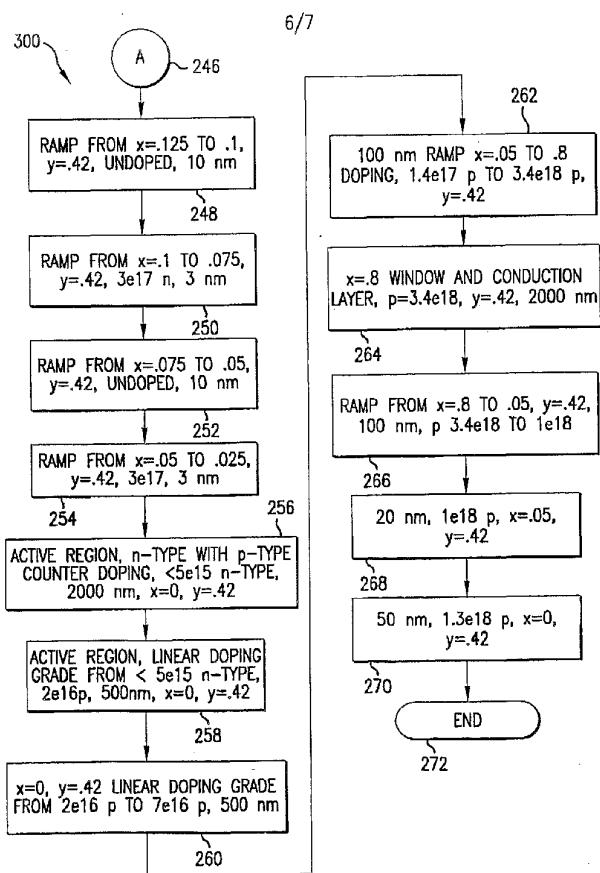

【0044】

図6は本発明の好ましい実施形態による、高速フォトダイオードを形成するエピタキシャル成長を示す作業の継続フロー図300である。ブロック248に示すように、 $y = 0.42$ で、 $x = 0.125$ から $x = 0.1$ の傾斜に基づき、層が形成される。ブロック24

10

20

30

40

50

8に示す作業の結果形成された層は10nmの厚さのドーピングしない層を含む。次にブロック250に示すように、 $y = 0.42$ で $x = 0.1$ から $x = 0.075$ の傾斜が起り、 $3 \times 10^{17} n$ のn-型ドーピングに基づく、得られる厚さが3nmの層が形成される。次に、ブロック252に示すように、 $y = 0.42$ で $0.075$ から $x = 0.05$ の傾斜が起り、10nmの厚さのドーピングしない層が形成される。その後のブロック254に示すように $y = 0.42$ で $x = 0.05$ から $= 0.025$ の傾斜に基づいて層が形成される。ブロック254に示す作業の結果形成される層は約3nmの厚さをもち、 $3 \times 10^{17}$ のドーピングに基づく。ブロック236～254は組成物が傾斜したデバイ長ドーピング領域を表している。

## 【0045】

10

次いでブロック256に示すように、 $5 \times 10^{15} n$ -型未満の活性領域がn-型ドーピングおよびp-型逆ドーピングで形成される。先に示すように、活性領域の下部は速度のためにn-型であることが重要である。しかし前に述べたように、p-型ドーピングも存在することができる。ブロック256に示すステップの間に形成される他の特性は、2000nmの厚さ、p-型逆ドーピングでの $5 \times 10^{15} n$ のn-型、 $x = 0$ 、 $y = 0.42$ を含む。その後のブロック258に示すように、次の活性領域層は $5 \times 10^{15}$ 未満のn-型から $2 \times 10^{16} p$ -型に線形ドーピングされ、得られる厚さは500nm、また再度 $x = 0$ 、 $y = 0.42$ である。次いでブロック260に示すように、 $x = 0$ 、 $y = 0.42$ で、 $2 \times 10^{16} p$ から $7 \times 10^{16} p$ に線形のp-ドーピング勾配が起り、500nmの厚さが得られる。次にブロック262に示すように、 $1.4 \times 10^{17} p$ から $3.4 \times 10^{18} p$ に傾斜ドーピングした、 $x = 0.05$ から $x = 0.8$ のpドーピング傾斜組成物、および $y = 0.42$ で100nmの層が形成される。

## 【0046】

20

その後のブロック264に示すように、窓および導電層に $x = 0.8$ の層が形成される。また、このステップでは、 $p = 3.4 \times 10^{18}$ 、 $y = 0.42$ 、および層の厚さが2000nmである。その後、ブロック266に示すように、 $x = 0.8$ から $0.05$ 、 $y = 0.42$ であり、厚さ100nmのA1組成物の傾斜層が形成され、p-ドーピングは $3.4 \times 10^{18}$ から $1 \times 10^{18}$ に傾斜する。最後に、ブロック268から272に示すようにキャップ層が形成される。ブロック268に示すように、 $x = 0.05$ 、 $y = 0.42$ および $1 \times 10^{18}$ のp-ドーピングに基づいて20nmの層が形成される。ブロック270に示すように、 $x = 0$ 、 $y = 0.42$ および $1.3 \times 10^{18}$ のp-ドーピングに基づいて50nmの層が形成される。次にプロセスはブロック272に示すように終了する。

30

## 【0047】

40

図7は本発明の好ましい実施形態による高速フォトダイオードを形成するためのエピタキシャル成長プロセスを示す例示的構造図320である。本明細書に述べる方法によって、高速ダイオードなどの半導体装置を形成するための構造は、基板322から始まる。前に述べたように、GaAsは、それが他の基板材料よりも脆弱ではなく、安価であり、加えてGaAsを使用するのにリンの供給源を必要としないことから、基板材料として好適に用いることができる。ゲルマニウムまたはシリコンなど他の基板も本発明に従って用いることができる。

## 【0048】

40

図7の層324で示すように、0.1ミクロンのバッファーは $1 \times 10^{18} n$ を用いて成長することができ、一方、層326では、層は一般に $y = 0.0345$ から $y = 0.52$ の組成物傾斜、厚さ10nm、 $2.5 \times 10^{18} n$ のドーピングに基づいて形成される。層328の厚さは約10nmとすることができます、 $y = 0.52$ nm、および $2.5 \times 10^{18} n$ のドーピングである。層328の上に位置している層330もまた、厚さ10nmとすることができます、 $y = 0.52$ から $0.42$ の傾斜に基づいている。さらに、層330は $2.5 \times 10^{18}$ のドーピングに基づくことができる。本明細書で言及しているドーピングの単位は一般に $cm^3$ 当たりであることに注目されたい。層332は層330の上に形成され、 $y = 0.42$ および温度上昇640、ドーピング値 $2.5 \times 10^{18}$ に基づいて、厚さ

50

が約 200 nm である。層 332 の上に位置する層 334 は、厚さが約 500 nm であり、 $y = 0.42$ 、高い V / I III 比をもち、形成温度は 640 である。

【0049】

層 336 は 0 に等しい層の厚さを有し、750 へのアニーリング昇温、および 750 で 5 分間の保持、および 640 への温度降下によって形成される。次に形成される層 338 は、640、0.2 ミクロン、 $y = 0.42$  の層に基づく。層 340 は、 $y = 0.44$  の歪んだ層を含む。層 340 もまた厚さ 6 nm である。層 342 もまた厚さ 6 nm の  $y = 0.40$  に基づく、歪んだ層として形成することができる。歪んだ層 340 から 342 は約 100 周期にわたって形成することができ、転位を排除するように設計されていることに注目されたい。層 344 は  $y = 0.45$  の厚さ 6 nm の歪んだ層として形成される。同様に、層 346 は  $y = 0.39$  の厚さ 6 nm の歪んだ層として形成することができる。歪んだ層 344 から 346 は約 100 周期にわたって形成することができることに注目されたい。さらに、層 348 が  $y = 0.47$  の厚さ 6 nm の歪んだ層として作られる。最後に、層 350 が  $y = 0.37$  の厚さ 6 nm の歪んだ層として形成される。歪んだ層 340 から 342 は約 100 周期にわたって形成することができる。

10

【0050】

その後、層 352 は  $y = 0.42$ 、および厚さ 100 nm に基づいて形成することができる。追加の層 352 は一般に  $5 \times 10^{17}$  n - 型ドーピングに基づく。層 354 は層 352 の上に、 $x$  傾斜値  $x = 0$  から  $x = 0.25$ 、および  $y$  値  $0.42$  に基づく 50 nm の厚さの層として形成される。さらに層 354 が  $5 \times 10^{17}$  n - 型ドーピングに基づいて形成される。層 354 の上に形成される層 356 は、 $x = 0.25$  の傾斜および  $y = 0.42$  に基づく 50 nm の厚さの層を含む。層 356 は  $x = 0.25$ 、および  $y = 0.42$  および  $5 \times 10^{17}$  の n - 型ドーピングに基づく厚さ 50 nm の層を含む。層 358 は層 356 の上に形成され、約 4 nm の厚さで  $3 \times 10^{17}$  n - 型ドーピングに基づく。加えて、層 358 が  $x = 0.25$  および  $y = 0.42$  に基づいて形成される。

20

【0051】

層 360 は  $x = 0.25$ 、および  $y = 0.42$  に基づくドーピングしない厚さ 10 nm の層を含む。デバイ長ドーピングは層 358 および 360 では 80 周期にわたって起きることに注目されたい。先に説明したように、デバイ長ドーピングは、実際に意図的にドーピングするには低すぎる、低ドーピングを制御する技術的方法である。デバイドーピングでは、ドーピングはほんの短時間に低レベルで周期的に起動される。これらのドーピングした領域間の距離がデバイ長またはドープ剤の拡散長よりも短い場合には、それは平均したドーピングで全領域にわたって効率的にドーピングされている。

30

【0052】

層 362 が  $x = 0.25$  から  $x = 0.225$  の傾斜に基づいて形成することができる。層 352 も層厚さ 3 nm、 $3 \times 10^{17}$  n のドーピングで形成することができる。層 364 は  $x = 0.225$  から  $x = 0.2$  の傾斜および  $y = 0.42$  に基づいて形成され、ドーピングしない厚さ 10 nm である。層 366 は  $x = 0.2$  から  $x = 0.175$  の傾斜および  $y = 0.42$  に基づいて形成される。形成された、得られる層は、 $3 \times 10^{17}$  n の n - 型ドーピングに基づく 3 nm の厚さである。層 368 では、 $x = 0.175$  から  $x = 0.15$  および  $y = 0.42$  の傾斜が起こり、ドーピングしない 10 nm 厚さの層を形成する。層 370 では  $x = 0.15$  から  $x = 0.125$  および  $y = 0.42$  の傾斜が起こり、厚さ 3 nm で  $3 \times 10^{17}$  n の n 型ドーピングに基づく層を形成する。同様に、層 372 では  $x = 0.125$  から  $x = 0.1$  および  $y = 0.42$  の傾斜が起こり、厚さ 10 nm のドーピングしない層を形成する。層 374 は  $x = 0.1$  から  $x = 0.075$  および  $y = 0.42$  の傾斜に基づいて形成される。形成される層 374 も  $3 \times 10^{17}$  の n - 型ドーピングに基づく 3 nm の厚さをもつ。層 376 は  $x = 0.075$  から  $x = 0.05$  および  $y = 0.42$  の傾斜に基づいて形成される。層 376 はドーピングしない 10 nm 厚さの層である。層 378 は  $x = 0.05$  から  $x = 0.025$  および  $y = 0.42$  の傾斜に基づいて形成することができる。形成された、得られる層（すなわち層 378）は  $3 \times 10^{17}$  のドーピング

40

50

に基づく約3nmの厚さである。

【0053】

次いで活性領域が、最終的に $5 \times 10^{15}$ n-型未満になる、n-型ドーピングおよびp-型逆ドーピングで形成することができる。層380はこの活性領域部分を含む。前に示したように、活性領域の下部は速度のためにn-型であることが重要である。しかし前に説明したように、p-型ドーピングも存在することができる。層380の他の特性はx=0およびy=0.42に基づく厚さ2000nmを含む。層382は $5 \times 10^{15}$ 未満のN-型から $2 \times 10^{16}$ pへ線形の傾斜ドーピングを行い、x=0およびy=0.42で500nmの厚さが得られる。層382は活性領域の追加の部分を形成する。層384は、x=0およびy=0.42で $2 \times 10^{16}$ pから $7 \times 10^{16}$ pの線形p-ドーピング勾配に基づく活性領域の部分を含む。層384は500nmの厚さが得られる。活性領域の上に形成される層386は、y=0.42でx=0.05からx=0.8、およびp-ドーピングの勾配が $1.4 \times 10^{17}$ pから $3.4 \times 10^{18}$ pに基づき、厚さ100nmである。

【0054】

層388は、x=0.8およびy=0.42に基づき窓および導電層として形成することができる。層388もまた、 $3.4 \times 10^{18}$ のp-型ドーピング、y=0.42に基づいて形成することができる。形成された、得られる層(すなわち層388)は、厚さ約2000nmである。その後、層390がx=0.8からx=0.05およびy=0.42の傾斜に基づいて形成される。層390は約100nmの厚さ、および $3.4 \times 10^{18}$ から $1 \times 10^{18}$ の傾斜のp-ドーピングを有する。最後に、図7中に層392および394で表されるキャップ層が形成される。層392はx=0.05、y=0.042、および $1 \times 10^{18}$ のp-ドーピングに基づく20nmの層を含む。層392の上に形成される層394は、約50nmの厚さを有し、x=0、y=0.42および $1.3 \times 10^{18}$ のp-ドーピングに基づいて形成される。図7の勾配層326および330は、段差またはMBEを用いて通常行われるデジタル合金によって隣接することができる。

【0055】

本明細書に記載した実施形態および実施例は、それによって当業者が本発明を製造し使用することができるよう、本発明とその実際の応用を最良に説明するために提示するものである。しかし、当業者であれば、前の説明および実施例が説明と例のためにのみ提示されたことを理解するであろう。本発明の他の変更および修正は当業者には明らかであろうし、その変更と修正を包含することは付随する請求項の意図するところである。提示した説明は本発明の範囲を網羅し、制限することを意図するものではない。上述の教示に基づき、多くの修正および変更が以下の請求項の精神と範囲から逸脱することなく可能である。本発明の使用には異なる特性を有する要素を含むことができることを意図している。本発明の範囲は本明細書に付随する請求項によって明確にされ、すべての点で等値のものを認識範囲とするものである。

【図面の簡単な説明】

【0056】

【図1】従来技術のフォトダイオード製造技術を説明するために、従来技術のモノリシック集積受光素子の断面を示す図である。

【図2】本発明の好ましい実施形態によって半導体装置を製造する作業ステップを示すフロー図である。

【図3】本発明の好ましい実施形態による、フォトダイオード装置のためのエピタキシャル構造を示すブロック図である。

【図4】本発明の好ましい実施形態による、フォトダイオード装置のための別法のエピタキシャル構造を示すブロック図である。

【図5】本発明の好ましい実施形態による、高速フォトダイオードを形成するエピタキシャルプロセスを示す作業フロー図である。

【図6】本発明の好ましい実施形態による、高速フォトダイオードを形成するエピタキシャルプロセスを示す作業の継続フロー図である。

10

20

30

40

50

【図7】本発明の好ましい実施形態による、高速フォトダイオードを形成するエピタキシャルプロセスを示す構造図である。

【図3】

【図4】

【図5】

【図6】

【図7】

|     |                                                                                              |      |     |

|-----|----------------------------------------------------------------------------------------------|------|-----|

| 394 | 50nm, 1, $3 \times 10^{18}$ p, $x=0, y=0.42$                                                 | キヤップ | 320 |

| 392 | 20nm, 1, $1 \times 10^{18}$ p, $x=0.05, y=0.42$                                              |      |     |

| 390 | $x=0.8$ から $0.95$ の傾斜, $y=0.42, 100nm, p=3.4 \times 10^{18}$ から $1 \times 10^{19}$           |      |     |

| 388 | $x=0.8$ の窓および導電層, $p=3.4 \times 10^{18}, y=0.42, 2000nm$                                     |      |     |

| 386 | 100nm, 傾斜 $x=0.95$ から $0.8, 1.4 \times 10^{18}$ pから, $3.4 \times 10^{18}$ pへのドーピング, $y=0.42$ |      |     |

| 384 | $x=0, y=0.42, 2 \times 10^{18}$ pから $7 \times 10^{18}$ pへの線形ドーピング勾配, 500nm                   |      |     |

| 382 | 活性領域< $5 \times 10^{18}$ nから約 $2 \times 10^{18}$ pへの線形ドーピング勾配, $y=0.42, x=0, 500nm$          | 活性領域 |     |

| 380 | 活性領域, p-型逆ドーピングでのn-型, 従ってこれは< $5 \times 10^{18}$ n-型, $2000nm, x=0, y=0.42$                  |      |     |

| 378 | 傾斜 $x=0.05$ から $0.25, y=0.42, 3 \times 10^{17}, 3nm$                                         |      |     |

| 376 | 傾斜 $x=-0.075$ から $0.05, y=0.42, アンドープ 10nm$                                                  |      |     |

| 374 | 傾斜 $x=0.1$ から $0.075, y=0.42, 3 \times 10^{17}, 3nm$                                         |      |     |

| 372 | 傾斜 $x=0.125$ から $0.1, y=0, アンドープ 10nm$                                                       |      |     |

| 370 | 傾斜 $x=0.5$ から $0.125, y=0.42, 3 \times 10^{17}, 3nm$                                         |      |     |

| 368 | 傾斜 $x=0.175$ から $0.15, y=0.42, 3 \times 10^{17}, 3nm$                                        |      |     |

| 366 | 傾斜 $x=0.2$ から $0.175, y=0.42, 3 \times 10^{17}, 3nm$                                         |      |     |

| 364 | 傾斜 $x=0.225$ から $0.2, y=0.42, アンドープ, 10nm$                                                   |      |     |

| 362 | 傾斜 $x=0.225$ から $0.225, y=0.42, 3 \times 10^{17}, 3nm$                                       |      |     |

| 360 | $x=0.25, y=0.42, アンドープ, 10nm$                                                                |      |     |

| 358 | $x=0.25, y=0.42, 3 \times 10^{17}, n$ -型, 4nm                                                |      |     |

| 356 | 50nm, $x=0.25, y=0.42, 5 \times 10^{17}, n$ -型                                               |      |     |

| 354 | 50nm, $x$ の傾斜 $x=0.25, y=0.42, 5 \times 10^{17}, n$ -型                                       |      |     |

|     | $y=0.42, 100nm, 5 \times 10^{17}, n$ -型                                                      |      |     |

|     |                                                                                              | 352  |     |

| 100 | 歪み層, $y=0.37$ , 厚さ=6nm                                                                       |      |     |

| 周期  | 歪み層, $y=0.47$ , 厚さ=6nm                                                                       |      | 350 |

| 100 | 歪み層, $y=0.39$ , 厚さ=6nm                                                                       |      | 348 |

| 周期  | 歪み層, $y=0.45$ , 厚さ=6nm                                                                       |      | 346 |

| 100 | 歪み層, $y=0.40$ , 厚さ=6nm                                                                       |      | 344 |

| 周期  | 歪み層, $y=0.44$ , 厚さ=6nm                                                                       |      | 342 |

|     | 640°C, 0.2ミクロノ, $y=0.42$                                                                     |      | 340 |

|     | 厚さ0.750°Cにアニーリング昇温, 750°Cで5分間保持,                                                             |      | 338 |

|     | 640°Cに温度降下                                                                                   |      | 336 |

|     | 500nm, $y=0.42$ 高V/III, 640°C, $5 \times 10^{17}$ nm                                         |      | 334 |

|     | 200nm, 640°CCL昇温, $2.5 \times 10^{18}$                                                       |      | 332 |

| 330 | 10nm, $y=0.52$ から $0.42$ の傾斜, $2.5 \times 10^{18}$ n                                         |      |     |

| 328 | 10nm, $y=0.52, 2.5 \times 10^{18}$                                                           |      |     |

| 326 | $y=0.0345$ から $y=0.52$ の組成物傾斜, 厚さ10nm, $2.5 \times 10^{18}$ n                                |      |     |

| 324 | 0.1ミクロン/ツワツワ, $1 \times 10^{18}$ n                                                           |      |     |

| 322 | 基板                                                                                           |      |     |

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 02/058162 A2

(51) International Patent Classification: H01L 31/00 (74) Agents: CRISS, Roger, H. et al.; Honeywell International Inc., 101 Columbia Avenue, P.O. Box 2245, Morristown, NJ 07960 (US)

(21) International Application Number: PCT/US02/01969

(22) International Filing Date: 22 January 2002 (22.01.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/766,797 22 January 2001 (22.01.2001) US

(71) Applicant: HONEYWELL INTERNATIONAL INC. [US/US]; 101 Columbia Road, P.O. Box 2245, Morristown, NJ 07960 (US).

(72) Inventors: JOHNSON, Ralph, H.; 211 Ridgeview, Murphy, TX 75094 (US); BIARD, James, R.; 207 Marsha Manor, Richardson, TX 75081 (US); GUENTER, James, K.; 214 Coral Ridge Road, Garland, TX 75044 (US).

(81) Designated States (national): AF, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, CA, CL, CN, CR, CU, CZ, DE, DK, DM, EE, ES, FI, GB, GD, GE, GL, GM, IIR, IU, ID, IL, IN, IS, JP, KU, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, NO, NZ, PI, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NL, SN, TD, TG).

Published:

without international search report and to be republished upon receipt of that report

[Continued on next page]

(54) Title: METAMORPHIC LONG WAVELENGTH HIGH-SPEED PHOTODIODE

WO 02/058162 A2

(57) Abstract: A method and apparatus for fabricating a metamorphic long-wavelength, high-speed photodiode, wherein a buffer layer matching a substrate lattice constant is formed at normal growth temperatures and a thin grading region which grades past the desired lattice constant is configured at a low temperature. A reverse grade back is performed to match a desired lattice constant. Thereafter, a thick layer is formed thereon, based on the desired lattice constant. Annealing can then occur to isolate dislocated material in a grading layer and a reverse grading layer. Thereon a strained layer superlattice substrate is created upon which a high-speed photodiode can be formed. Implant or diffusion layers grown in dopants can be formed based on materials, such as Be, Mg, C, Te, Si, Se, Zn, or others a metal layer can be formed over a cap above a P+ region situated directly over an N-active region. The active region also includes a p-doped region. The high-speed photodiode can thus be formed utilizing GaAs, or other substrate material, such as germanium and silicon.

---

**WO 02/058162 A2**

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**METAMORPHIC LONG WAVELENGTH HIGH-SPEED PHOTODIODE****BACKGROUND OF THE INVENTION**

5 The present invention relates to semiconductor devices and methods for manufacturing the same. The present invention also relates to photodiode devices and methods for manufacturing the same. The present invention additionally relates to high-speed, long-wavelength photodiode devices and improved methods for manufacturing the same. The present invention further relates to techniques for

10 growing semiconductor photodiode devices on substrates.

With the rapid development of lightwave communications, low-cost, high-performance optical photodiodes are required for a variety of system applications. Photodiodes are p-n junction semiconductor devices that produce a significant

15 photocurrent when illuminated. Photodiodes operate based on principals of photoconductivity, which is an enhancement of the conductivity of p-n semiconductor junctions due to the absorption of electromagnetic radiation. Photoconductivity may result from the action of radiation in the visible portion of the spectrum in some materials.

20 There are two main classes of photodiodes currently in use today. These are depletion-layer diodes and avalanche diodes. Depletion-layer photodiodes are based on a reverse-biased p-n junction configuration operated below a particular breakdown voltage. When exposed to electromagnetic radiation of a desired wavelength, excess

25 charge carriers may be produced as a result of absorption. Such carriers may be formed as electron-hole pairs. Those electron-hole pairs generated in or near to a depletion layer at a junction, cross the junction and produce a photocurrent. Avalanche diodes are based on reverse-biased p-n junction diodes operated at voltages above the breakdown voltage. Current multiplication of electron-hole pairs, generated by incident

30 electromagnetic radiation, occurs due to the "avalanche process," well known in the

photodiode arts.

5 Semiconductor photodiodes can be constructed from any semiconductor and are typically constructed from single crystal silicon wafers similar to those utilized in the manufacture of integrated circuits. Long-wavelength (e.g., 1310 nm and 1550 nm) photodiodes are typically made from InGaAs with nominally the same lattice constant as Indium Phosphide (InP).

10 Currently, long-wavelength (about 1200 nm – 1650 nm), high-speed photodiodes are all grown on Indium Phosphide (InP) substrates. The integration of receiver photodiode components operating in the long-wavelength range necessitates the utilization of Indium Gallium Arsenide (InGaAs) p-i-n photodetectors and, hence, a technology based on InP substrates in order to avoid strained layers, which cause misfit 15 dislocations due to the lattice mismatch. Unlike Silicon (Si) and Gallium Arsenide (GaAs), however, InP is not as well established and is very fragile. In addition, InP substrates are expensive and not available in sizes as large as GaAs or Si. Finally, gas phase epitaxial growth on InP requires the use of phosphine, which is often not available on particular epitaxial systems and causes several technical problems.

20 FIG. 1 depicts a cross-sectional view of a prior art monolithic integrated photoreceiver to illustrate prior art photodiode fabrication techniques. As shown in FIG. 1, a photoreceiver 100 may detect and amplify optical beam 50, which impinges on p-i-n photodiode 23 at a wavelength  $\lambda_s$ , which can be chosen to be greater than 1.0  $\mu\text{m}$  because, among other reasons, the InP semiconductor may be transparent for 25 those wavelengths. Such an integrated photoreceiver may afford materials compatibility and separate optimization control over the photonics and electronics functions because each device is electrically isolated as well as physically separated from the others. It is important to note, however, that despite materials compatibility and separate optimization control, such a device is relatively expensive, fragile, and 30 difficult to process, requiring complicated integration into components. It should be

WO 02/058162

PCT/US02/01969

noted that the semiconductor layers underlying the HBT, while structurally adapted for forming a photodiode, are not electrically or optically active.

5 In the prior art photoreceiver structure illustrated in FIG. 1, the photodiode and heterostructure bipolar transistor have semiconductor layers selected from the InP/InGaAs material system and grown over a non-patterned Fe doped InP substrate.

10 Standard fabrication techniques, including metalorganic vapor phase epitaxy (MOVPE), selective wet chemical etching, reactive ion etching and contact metallization, may be utilized to fabricate the prior art illustrated in FIG. 1. These fabrication techniques are well known to those persons of ordinary skill in the art and, thus, are not discussed in detail here.

15 The prior art device illustrated in FIG. 1 may be epitaxially grown on a planar Fe doped <001> oriented InP substrate 10. The p-i-n epilayers comprise a 4000 Å thick InP layer 20, a 1.0 µm thick InGaAs layer 21, and a 4000 Å thick InP layer 22, which may be grown on semi-insulating substrate 10 by MOVPE. Semiconductor layers 20, 21, and 22 thus may form p-i-n photodiode 23.

20 The epitaxial layers of heterostructure bipolar transistor (HBT) 24 can be grown over the entire structure, such that no intervening processing exists between the deposition of each epilayer. That is, the growth run may be continuous and uninterrupted. HBT 24 may comprise a sub-collector layer 25, collector layer 26, base layer 27, emitter layer 28, and an emitter cap layer 29. It should be noted that HBT 24

25 may be configured as a single heterostructure device, while photodetector 23 may possess a photoabsorbing layer 21.

30 After the growth of the photodiode and heterostructure bipolar transistor epitaxial layers, wet chemical etching can be performed to realize the mesa structures thereof. In association with the wet chemical etch, photoresist patterning can be oriented 45

degrees to the [001] and [001] crystallographic direction planes in order to maintain the geometrical shape of the mesa structure. Alternatively stated, the line features of the devices, that is, photodiode 23 and HBT 24, can be delineated so that they are 45 degrees to the [001] and [001] direction planes.

5

Conventional ohmic contacts, such as AuGe/Au and AuZn/Au, may be deposited on the lateral edges of the mesa in order to provide ohmic contacts 31, 32, 33, and 34 to layer 20, subcollector layer 25, base layer 27, and emitter cap layer 29, respectively. It should be noted that standard metallic deposition techniques can be employed in fabricating the ohmic contact. Additionally, for photodetector 23, an annular alloyed ohmic contact 30 may provide contact to layer 22. Annular ohmic contact 30 may be formed by standard photolithographic, including evaporation and lift-off techniques well known in the art.

10

To reflect any unabsoed optical beam 50 back into photoabsorbing region 21 and, thus, increase the quantum efficiency, a non-alloyed Cr/Au metal contact 36 can be deposited in the annular opening of contact 30. After planarization and passivation, such as by using a spun-on polyimide 35, reactive ion etching of the polyimide in an oxygen plasma may be employed to open windows therein in order to facilitate attaching leads, not shown, to the ohmic contacts. After fabrication, substrate 10 may be thinned and polished in order to permit backside illumination.

15

Based on the foregoing, those skilled in the art can appreciate that prior art manufacturing methods for semiconductor devices, such as photodiodes grown on InP substrates, are expensive, fragile, difficult to process, and additionally difficult to build into components. Such processing complexity also results in inefficiencies and increased manufacturing expenses. In view of reducing the processing complexity, it is, therefore, desirable to develop an alternative technique for forming high-speed photodiodes and devices based on high-speed photodiodes, such as photoreceivers.

20

The present inventors have developed a technique and devices thereof, disclosed

WO 02/058162

PCT/US02/01969

herein, which overcome the inefficiencies inherent in the manufacturing of prior art semiconductor devices.

**BRIEF SUMMARY OF THE INVENTION**

The following summary of the invention is provided to facilitate an understanding of some of the innovative features unique to the present invention and is not intended to be a full description. A full appreciation of the various aspects of the invention can be gained by taking the entire specification, claims, drawings, and abstract as a whole.

5 It is an aspect of the present invention to provide a high-speed photodiode grown on a substrate.

10 It is another aspect of the present invention to provide methods for growing aspect of high-speed photodiode on a substrate.

15 It is yet another aspect of the present invention to provide a long wavelength high-speed photodiode grown on GaAs.

20 It is still another aspect of the present invention to provide a metamorphic long-wavelength, high-speed photodiode formed utilizing a superlattice containing substrate and metamorphic epitaxial growth techniques.

25 The above and other aspects are achieved as is now described. A method and apparatus for fabricating a metamorphic long-wavelength, high-speed photodiode is thus disclosed, wherein a buffer layer matching the substrate lattice constant can be formed at normal growth temperatures and a thin graded region which grades past the desired lattice constant is configured at a low temperature. Upon this graded region, a thin layer can be configured again at low temperatures whose lattice constant is the end lattice constant of the grade and is past the desired lattice constant.

30 A reverse grade back can then be performed to match the desired lattice constant. Thereafter, a thick layer is formed thereon, based on the desired lattice constant. Annealing can then occur to isolate dislocated material in the graded layer, the reverse

WO 02/058162

PCT/US02/01969

graded layer and the layer therebetween. A strained layer superlattice can be then formed thereon, on which a high-speed photodiode can be formed. The strained layer superlattice further isolates the photodiode from the misfit dislocations caused by the metamorphic transition. Note that the terms "graded layer" and "grading layer" are 5 generally synonymous and may be utilized herein interchangeably.

Upon the strained layer superlattice, the photodiode structure can be created. Implant or diffusion layers can be formed based on materials, such as Be, Mg, C, Si, Se, Te, S or Zn. A metal layer can be formed over a cap etch above a P+ region situated 10 directly over an N+ active region. The high-speed photodiode can thus be formed on a GaAs, which is much cheaper, less fragile and readily configurable into components. Formation of the photodiode can be accomplished utilizing MOCVD as the epitaxial growth technique, although those skilled in the art can appreciate that other growth techniques, such as MBE, can also be utilized in accordance with the methods and 15 apparatus described herein. The preferred substrate orientation is (100) nominally on the orientation. Those skilled in the art will appreciate that the term (100) as utilized herein can be expressed as (100), <100>, or [100] or pronounced phonetically as "1-0-0", and 20 is not to be confused with the reference numeral 100 utilized with regard to FIG. 1(a).

**BRIEF DESCRIPTION OF THE DRAWINGS**

The accompanying figures, in which like reference numerals refer to identical or functionally-similar elements throughout the separate views and which are incorporated in and form part of the specification, further illustrate the present invention and, together with the detailed description of the invention, serve to explain the principles of the present invention.

FIG. 1 depicts a cross-sectional view of a prior art monolithic integrated photoreceiver to illustrate prior art photodiode fabrication techniques;

FIG. 2 is a flow chart illustrating operational steps for fabricating a semiconductor device in accordance with preferred embodiments of the present invention;

FIG. 3 depicts a block diagram illustrating an epitaxial structure for a photodiode device, in accordance with preferred embodiments of the present invention;

FIG. 4 is a block diagram illustrating an alternative epitaxial structure for a photodiode device, in accordance with preferred embodiments of the present invention;

FIG. 5 depicts a flow chart of operations illustrating the epitaxial process for forming a high-speed photodiode, in accordance with preferred embodiments of the present invention;

FIG. 6 illustrates a continued flow chart of operations illustrating the epitaxial process for forming a high-speed photodiode, in accordance with preferred embodiments of the present invention; and

FIG. 7 depicts a structural diagram illustrating the epitaxial process for forming a high-speed photodiode, in accordance with preferred embodiments of the present invention.

DETAILED DESCRIPTION OF THE INVENTION

The particular values and configurations discussed in these non-limiting examples can be varied and are cited merely to illustrate an embodiment of the present invention and are not intended to limit the scope of the invention.

5

FIG. 2 is a flow chart illustrating operational steps for fabricating a semiconductor device in accordance with preferred embodiments of the present invention. A photodiode is one type of semiconductor device that can be fabricated according to the steps and processes disclosed herein. Thus, a photodiode device can be constructed according to the operations illustrated in FIG. 2. Using grading, an intermediate layer, an inverse grade, (100) nominally on orientation GaAs substrates, in-situ annealing, and a strained layer superlattice, artificial substrates can be created on which semiconductor devices, such as long-wavelength photodiodes, are fabricated.

10

The strained layer superlattice can be composed of a lower strain, a medium strain, and a high strain, such that none of the individual layers are so thick so as to produce dislocations, but approach this thickness in the high-strain region. The photodiodes grown according to the method described herein may be referred to as "long wavelength" photodiodes because they can be designed to operate in a broad range of wavelengths. In a preferred embodiment the range of wavelengths is in the nominally 1550 nanometer and 1310 nanometer wavelength range which are commonly used in communications.

15

Using heavy n-type doping through the grading regions and InGaAs as the grading material, conduction through the heavily dislocated grading region can be maintained. Those skilled in the art will appreciate that "doping" involves the addition of a particular type of impurity in order to achieve a desired n-conductivity or p-conductivity (i.e., in the case of p-type doping). The donor impurities are added to form an n-type semiconductor. Acceptor impurities typically form p-type semiconductors.

20

25

WO 02/058162

PCT/US02/01969

By utilizing relatively thin grades, and (100) orientation substrates, the surface morphology will provide for adequate device processing. Processing can be achieved utilizing MOCVD as the epitaxial growth technique. Those skilled in the art can appreciate that other growth techniques can also be utilized in accordance with the 5 present invention, including MBE, which is well known in the art.

Thus, as indicated in FIG. 2 at block 62, the process is initiated. To configure a photodiode device according to the method described herein, a substrate, which is (100) on orientation GaAs can be utilized, as illustrated at block 64. Preferably, GaAs is 10 utilized as the substrate material because it is less fragile and less expensive than other substrate materials. In addition, the use of GaAs does not require a phosphorous source. Those skilled in the art can appreciate, however, that other substrates can be utilized in accordance with the present invention, including substrates such as germanium or silicon.

15

A buffer layer which matches the lattice constant can be grown first at normal growth temperatures, as depicted at block 65. Thereafter, as described at block 66, a thin grading region which grades past the desired lattice constant can be grown at a low temperature and a low group V pressure. Next, a thin intermediate layer of the 20 lattice constant, which is at the end point composition of the grading layer, is grown, as depicted at block 67. The intermediate layer is formed, such that the intermediate layer comprises a lattice constant slightly greater than a desired lattice constant.

Next, as illustrated at block 68, a reverse grade back to the desired lattice 25 constant can be performed. Grading in this manner is useful to prevent three-dimensional growth and to isolate dislocations to these layers. If a step is used instead of a grade, island growth in three dimensions occurs, which degrades the material quality.

30 Thereafter, as depicted at block 70, beginning at a low temperature and

WO 02/058162

PCT/US02/01969

ramping the temperature up, a thick (approximately .5 micron) layer of the desired lattice constant can be formed.

An anneal step can then be performed, as indicated at block 72, which tends 5 to isolate the heavily dislocated material in the graded, reverse graded and constant composition layer therebetween. Then, as depicted at block 74, a strained layer superlattice can be grown with individual thickness approaching a critical thickness, but not exceeding such a thickness. This will tend to exclude dislocation loops and further improves the quality of the subsequently grown material.

10

Finally, as illustrated at block 76, the device structure can be grown on top of these layers. The device structure for the photodetector (i.e., photodiode) can be a buffer layer followed by a ramp in Al composition to the lower confining layer. The lower confining layer prevents a slow tail response. On the lower confining layer, 15 another layer with an Al ramp down layer can be grown to grade to the active region composition. Grades can be utilized to ensure good electrical conduction in the device. These ramps are grades of the aluminum-to-gallium ratio and cause a change in energy band gap without an intentional change in lattice constant.

20

The active region can be nominally 3 microns thick and doped n-type at less than 5e15 in the lower portion and can have a p-type upper portion of nominally 1 micron thick. It is important that the active region be configured at least partially as an n-type active region for speed and that, additionally, the n portion of the active region have less than a value of 5e15 n-doping for capacitance. In this material, the background 25 doping can be nominally n-type, or there can be an n-diffusion tail from lower layers so counter doping can be used to reduce the effective doping to less than 5e15 using carbon because of its low doping efficiency.

30

FIG. 3 depicts a block diagram 101 illustrating a structure for a photodiode device, in accordance with preferred embodiments of the present invention. In the

block diagram illustrated in FIG. 3, metamorphic layers 110 can be grown to create a substrate structure upon which a semiconductor photodiode device can be configured. A lower confining layer 108 can be superimposed upon metamorphic layers 110. An active layer 105 can be grown above lower confining layer 108. A conduction layer 106 can be situated below cap 104 and a metal layer 102. Region 109 represents a proton implant. A portion of the cap 104 and conduction layer 106 is etched to allow transmission of light to the active region.

The antireflection (AR) coating 112 is indicated in FIG. 3 bordered by dashed lines above conduction layer 106. AR coating 112 can be composed of Silicon Nitride or other material as will become apparent to those skilled in the art. Light 111 is indicated by an arrow and is incident on antireflection (AR) coating 112. Absorption of light 111 occurs through conduction layer 106 and active layer 105. Trench 113 can be based on a trench etch, along with a proton implant to provide isolation and to reduce capacitance. Trench 113 should extend into lower confining layer 108. Those skilled in the art can appreciate that there are a number of possible variations that can be utilized to process a photodiode according to the methods described herein.

FIG. 4 is a block diagram 130 illustrating an alternative epitaxial structure for a photodiode device, in accordance with preferred embodiments of the present invention. As indicated in FIG. 4, a metal layer 132 can be positioned above a cap 134 for ohmic contact. Note that cap 134 can be partially removed as part of an optional cap etch, at least over the active area. A P+ diffusion region 142 can extend through the N- cap 134, the upper N- confining layer 138 and into the top of the active region 144.

The n-upper confining layer 138 can act as a window for appropriate wavelengths because it can contain enough Al to increase the band gap, thereby causing little absorption. This upper confining layer can also be utilized to provide conduction, because it possesses heavy p-doping in the p-diffused region to reduce the R-C constant. This is important because photodiode response time is the root mean

square sum of the charge collection time and the RC time constant arising from series plus load resistances and junction and stray capacitances. Cap 134 can be configured as a narrow band gap based on heavily doped material utilized for ohmic contact.

5 A metal layer 140 is also indicated in FIG. 4 above the lateral p-n junction to prevent light from entering this area and causing a slow response. Metal layer 140 can be insulated from the semiconductor by AR coating 143. P+ diffusion layer 142 can be formed by Be, Mg, or Zn implant or diffusion. Be implant and diffusion techniques are preferred in some instances. Those skilled in the art, however, can appreciate that

10 other implant and diffusion techniques can be utilized in accordance with preferred embodiments of the present invention. An N- active region 144 is positioned below P+ diffusion layer 142. An N lower confining layer 136 is located below N- active region 144.

15 FIG. 5 depicts a flow chart 200 of operations illustrating the epitaxial process for forming a high-speed photodiode, in accordance with preferred embodiments of the present invention. Note that the flow chart 200 continues with flow chart 300 illustrated in FIG. 6. Flow chart 300 of FIG. 6 is a continuation of flow chart 200 of FIG. 5. The process is initiated, as illustrated at block 202. The values x and y described herein

20 with respect to FIG. 5 are generally based on the following formulation:

Initially, as indicated at block 204, a 0.1 micron buffer layer which matches the substrate lattice constant can be grown at normal growth temperatures. As depicted

25 thereafter at block 206, a composition ramp can be created from  $y = 0.0345$  to  $y = 0.52$ , (for a 1300 nm detector) with a thickness of 10 nm. As described next at block 208, a 10 nm layer with  $y = 0.52$  can be grown.

As illustrated at block 210, a 10 nm ramp from  $y = 0.52$  to 0.42 can be grown.

30 As indicated thereafter at block 212, a 200 nm layer can be formed, wherein  $y = 0.42$

with a temperature ramp up to 640 C. As depicted next at block 214, a layer 500 nm, with  $y = 0.42$ , high V/III and 640 C temperature is formed. Then, as described at block 216, a layer with a thickness equivalent to 0 can be formed, based on an anneal, ramp up to 750 C, and a 5 minute hold at 750 C, and a temperature ramp back down to 640 C. The next layer formed, as illustrated at block 218, is based on a 640 C, 0.2 micron,  $y = 0.42$  layer.

Thereafter, as illustrated at block 219, a strained layer wherein  $y = 0.44$  is formed. This layer is about 6 nm thick. As indicated at block 220, a strained layer of  $y = 0.40$  is formed having a thickness of about 6 nm. Note that the strained layer formations illustrated with respect to blocks 219 to 220 occurs over approximately one hundred periods. A strained layer of  $y = 0.45$  with a thickness of 6 nm is formed, as illustrated at block 221. As indicated at block 222, a strained layer of  $y = 0.39$  with a thickness of above 6 nm is formed. Note that the strained layer formations illustrated with respect to blocks 221 to 222 occurs over approximately one hundred periods. Thereafter, as depicted at block 223, a strained layer of  $y = 0.47$  and a thickness of 6 nm is formed. Then, as described at block 224, a strained layer of  $y = 0.37$  and a thickness of 6 nm is formed. Note that the strained layer formations illustrated with respect to blocks 223 to 224 occur over approximately one hundred periods. Thereafter, as illustrated at block 225, a layer is formed in which  $y = 0.42$  with a thickness of 100 nm. As depicted at block 226, a layer of 50 nm can be formed from an x ramp value of  $x = 0$  to  $x = 0.25$  and a y value of 0.42.

The next step in the process, as depicted at block 230, involves the formation of a 50 nm layer with a composition of  $x \approx 0.25$  and  $y = 0.42$ . This layer is more heavily doped ( $5e17$ ) than layers formed thereafter so as to promote electrical conduction. Following the formation of this layer, as indicated at block 232, a layer can be formed in which  $x = 0.25$ , and  $y = 0.42$ . Note that this layer is approximately 4 nm thick with  $3e17$  n-type. As described next at block 233, a layer of  $x = 0.25$  and  $y = 0.42$  can be formed with an undoped thickness of 10 nm. Note that Debye length doping occurs over 80

periods through the steps indicated at blocks 232 and 233. Debye length doping is a method of controlling low doping which would be too low to actually intentionally dope otherwise. In Debye length doping, the doping is turned on periodically at a low level for only a short period of time. If the distance between these doped regions is less than 5 the Debye length or the dopant diffusion length, then it is effectively doped over the whole region with the average doping. Such a step may be necessary to keep the diffusion of silicon to a minimum next to an active region. Thus, particular regions can be grown on the substrate utilizing Debye length doping.

10 As indicated thereafter at block 236, a ramp of  $x = 0.25$  to  $x = 0.225$  is formed. Also, in this step,  $y = 0.42$ . The layer formed as a result of the step described at block 236 has a layer thickness of approximately 3 nm and is based on n-type doping  $3e17$  n. As indicated thereafter at block 238, ramping occurs from  $x = 0.225$  to 0.2 and  $y = 0.42$  15 undoped with thickness of 10 nm. As illustrated at block 240, ramping occurs from  $x = 0.2$  to  $x = 0.175$ , while  $y = 0.42$ . The resulting layer formed possesses a thickness of 3 nm and is based on n-doping of  $3e17$  n. As illustrated thereafter at block 242, ramping occurs in the formation of the next layer from  $x = 0.175$  to  $x = 0.15$  with  $y = 0.42$ . The 20 layer formed as a result of the operation described at block 242 has an undoped thickness of 10 nm. Then, as indicated at block 244, ramping occurs from  $x = 0.15$  to  $x = 0.125$  and  $y = 0.42$  to form a layer that is 3 nm thick and based on n-type doping of  $3e17$  n. The process continues, as indicated at connector block 246.

FIG. 6 is a continued flow chart 300 of operations illustrating the epitaxial process for forming a high-speed photodiode, in accordance with preferred 25 embodiments of the present invention. As illustrated at block 248, a layer is formed based on ramping from  $x = 0.125$  to  $x = 0.1$  and  $y = 0.42$ . The layer formed as a result of the operation depicted at block 248 comprises an undoped layer that is 10 nm thick. As indicated next at block 250, ramping occurs from  $x = 0.1$  to  $x = 0.075$  and  $y = 0.42$  to 30 form a layer based on n-type doping of  $3e17$  n, with a resulting thickness of 3 nm. Next, as illustrated at block 252, ramping occurs from 0.075 to  $x = 0.05$  and  $y = 0.42$  to

form an undoped layer of 10 nm thickness. As depicted thereafter at block 254, a layer is formed based on ramping from  $x = 0.05$  to  $x = 0.025$ , and  $y = 0.42$ . The layer formed as a result of the operation illustrated at block 254 is approximately 3 nm thick and based on doping of  $3e17$ . The blocks 236-254 represent a Debye length doped region 5 with a ramp of composition.

The active region is then formed with n-type doping and p-type counter doping, with less than  $5e15$  n-type, as illustrated at block 256. As indicated previously, it is important that the lower portion of the active region be n-type for speed. P-type doping 10 may also be present, however, as explained previously. Other characteristics formed during the step indicated at block 256 include a thickness of 2000 nm, n-type with p-type counter doping of  $5e15$  n and  $x = 0$  and  $y = 0.42$ . As illustrated thereafter at block 258, the next active region layer undergoes linear doping from less than  $5e15$  n-type to  $2e16$  p-type, with a resulting thickness of 500 nm, again with  $x = 0$  and  $y = 0.42$ . As 15 indicated then at block 260, a linear p-doping grade from  $2e16$  p to  $7e16$  p occurs wherein  $x = 0$  and  $y = 0.42$ , which results in a thickness of 500 nm. As described next at block 262, a 100 nm layer is formed with a composition ramp of  $x = 0.05$  to  $x = 0.8$  p-doping with a doping ramp of  $1.4e17$  p to  $3.4e18$  p and  $y = 0.42$ .

20 As illustrated thereafter at block 264, a layer is formed wherein  $x = 0.8$  in a window and conduction layer. Also, in this step,  $p = 3.4e18$ ,  $y = 0.42$ , and the thickness of the layer is 2000 nm. Thereafter, as illustrated in block 266, a layer with an Al composition ramp is formed wherein  $x = 0.8$  to  $0.05$ ,  $y = 0.42$ , with a 100 nm thickness, and p-doping ramps from  $3.4e18$  to  $1e18$ . Finally, a cap layer is formed, as illustrated 25 at blocks 268 to 272. As illustrated at block 268, a 20 nm layer is formed based on  $x = 0.05$ ,  $y = 0.42$  and p-doping of  $1e18$ . As illustrated at block 270, a 50 nm layer is formed based on  $x = 0$ ,  $y = 0.42$  and p-doping of  $1.3e18$ . The process then terminates, as indicated at block 272.

30 FIG. 7 depicts an exemplary structural diagram 320 illustrating the epitaxial

WO 02/058162

PCT/US02/01969

process for forming a high-speed photodiode, in accordance with preferred embodiments of the present invention. The structure for forming a semiconductor device, such as a high-speed diode, according to the methods described herein, begins with a substrate 322. As explained previously, GaAs can preferably be utilized as the 5 substrate material because it is less fragile and less expensive than other substrate materials, and additionally the use of GaAs does not require a phosphorous source. Other substrates can also be utilized in accordance with the present invention, germanium or silicon.

10 As illustrated in FIG. 7, at layer 324, a 0.1 micron buffer can be grown utilizing 1e18 n, while at layer 326, a layer is generally formed based on a composition ramp from  $y = 0.0345$  to  $y = 0.52$  with a thickness of 10 nm, based on  $2.5e18$  n doping. Layer 328 can be approximately 10 nm thick, wherein  $y = 0.52$  nm and doping of 15  $2.5e18$  n doping. Layer 330, situated above layer 328, can also be 10 nm thick and is based on a ramp from  $y = 0.52$  to 0.42. Additionally, layer 330 can be based on a doping of  $2.5e18$ . Note that the units of doping referred to herein are generally in  $\text{cm}^3$ . Layer 332 is formed above layer 330 and is approximately 200 nm thick based on  $y = 0.42$  and a temperature ramp up to 640 C, along with a doping value of  $2.5E18$ . Layer 20 334, which is situated above layer 332, is approximately 500 nm thick and is based on  $y = 0.42$  with a high V/III ratio and a formation temperature of 640 C.

25 Layer 336 has a layer thickness equivalent to 0 and is formed based on an annealing ramp up to 750 C, and a 5 minute hold at 750 C temperature and a ramp to 640 C. The next layer formed, layer 338, is based on a 640 C, 0.2 micron,  $y = 0.42$  layer. Layer 340 comprises a strained layer wherein  $y = 0.44$ . Layer 340 also is a 30 thickness of 6 nm. Layer 342 can also be formed as a strained layer with a 6 nm thickness and based on  $y = 0.40$ . Note that the strained layers 340 to 342 can be formed over approximately one hundred periods and are designed to exclude dislocations. Layer 344 is formed as a strained layer of  $y = 0.45$  with a thickness of 6 nm. Similarly, layer 346 can be formed as a strained layer of  $y = 0.39$  with a thickness

of 6 nm. Note that the strained layers 344 to 346 can be formed over approximately one hundred periods. Additionally, layer 348 is created as a strained layer of  $y = 0.47$  and a thickness of 6 nm. Finally, layer 350 is formed as a strained layer of  $y = 0.37$  and a thickness of 6 nm. Strained layers 340 to 342 can be formed over approximately one hundred periods.

Thereafter, layer 352 can be formed based on  $y = 0.42$  and a thickness of 100 nm. Additionally layer 352 is generally based on  $5e17$  n-type doping. Layer 354 is formed above layer 352 as a 50 nm thick layer based on an x ramp value of  $x = 0$  to  $x = 0.25$  and a y value of 0.42. Layer 354 is additionally formed based on  $5e17$  n-type doping. Layer 356, which is formed above layer 354, comprises a 50 nm thick layer based on a ramp of  $x = 0.25$  and  $y = 0.42$ . Layer 356 comprises a layer that is 50 nm thick based on  $x = 0.25$  and  $y = 0.42$ , and n-type doping of  $5e17$ . Layer 358 is formed above layer 356 and is approximately 4 nm thick and based on  $3e17$  n-type doping. Additionally, layer 358 is formed based on  $x = 0.25$  and  $y = 0.42$ .

Layer 360 comprises a layer 10 nm thick based on  $x = 0.25$  and  $y = 0.42$  and is undoped. Note that Debye length doping occurs over 80 periods for layers 358 and 360. As explained previously, Debye length doping is a technique method for controlling low doping, which would otherwise be too low to intentionally dope. In Debye doping, the doping is turned on at a low level for only a short period of time. If the distance between these doped regions is less than the Debye length or the diffusion length, then it is effectively doped over the entire region with the average doping.

Layer 362 can be formed based on a ramp of  $x = 0.25$  to  $x = 0.225$ . Layer 352 also can be formed with a layer thickness of 3 nm and doping of  $3e17$  n. Layer 364 is formed based on ramping from  $x = 0.225$  to  $x = 0.2$  and  $y = 0.42$ , with an undoped thickness of 10 nm. Layer 366 is formed based on ramping from  $x = 0.2$  to  $x = 0.175$ , and  $y = 0.42$ . The resulting layer formed has a thickness of 3 nm based on n-type doping of  $3e17$  n. In layer 368, ramping occurs from  $x = 0.175$  to  $x = 0.15$  and  $y = 0.42$ .

to form a layer with an undoped thickness of 10 nm. In layer 370, ramping occurs from x = 0.15 to x = 0.125 and y = 0.42 to form a layer that is 3 nm thick, based on n-type doping of 3e17n. Likewise, ramping occurs for layer 372 from x = 0.125 to x = 0.1 and y = 0.42 to form an undoped layer of 10 nm thickness. Layer 374 is formed based on 5 ramping x = 0.1 to x = 0.075 and y = 0.42. Layer 374 formed also has a thickness of 3 nm based on n-type doping of 3e17. Layer 376 is formed based on ramping from x = 0.075 to x = 0.05 and y = 0.42. Layer 376 is an undoped layer 10 nm thick. Layer 378 can be formed based on ramping from x = 0.05 to x = 0.025 and y = 0.42. The resulting layer (i.e., layer 378) that is formed is approximately 3 nm thick based on doping of 10 3e17.

An active region can be then formed with n-type doping and p-type counter doping, with less than 5e15 n-type net. Layer 380 comprises this portion of the active region. As indicated previously, it is important that the lower portion of the active region 15 be n-type for speed. P-type doping can also be present, however, as explained previously. Other characteristics of layer 380 include a thickness of 2000 nm, based on x = 0 and y = 0.42. Layer 382 undergoes linear doping ramp from less than 5e15 N-type to 2e16 p with a resulting thickness of 500 nm with x = 0 and y = 0.42. Layer 382 forms an additional portion of the active region. Layer 384 comprises a portion of the 20 active region based on a linear p-doping grade from 2e16 p to 7e16 p wherein x = 0 and y = 0.42. Layer 384 has a resulting thickness of 500 nm. Layer 386, which is formed above the active region, has a thickness of 100 nm based on x = 0.05 to x = 0.8 and y = 0.42, and p-doping grade from 1.4e17 p to 3.4e18 p.

25 Layer 388 can be formed as a window and conduction layer based on x = 0.8 and y = 0.42. Layer 388 can also be formed based on p-type doping of 3.4e18, y = 0.42. The resulting layer formed (i.e., layer 388) is approximately 2000 nm thick. Thereafter, layer 390 is formed based on a ramp of x = 0.8 to x = 0.05 and y = 0.42. Layer 390 has a thickness of approximately 100 nm, and p-doping that occurs in the 30 ramp from 3.4e18 to 1e18. Finally, a cap layer is formed, which is referenced as layers

WO 02/058162

PCT/US02/01969

392 and 394 in FIG. 7. Layer 392 comprises a 20 nm layer based on  $x = 0.05$ ,  $y = 0.042$  and p-doping of  $1e18$ . Layer 394, formed above layer 392, has a thickness of approximately 50 nm and is formed based on  $x = 0$ ,  $y = 0.42$  and p-doping of  $1.3e18$ . The grading layers 326 and 330 of FIG. 7 can be approximated by steps or a digital alloy as is commonly done using MBE.

The embodiments and examples set forth herein are presented to best explain the present invention and its practical application and to thereby enable those skilled in the art to make and utilize the invention. Those skilled in the art, however, will 10 recognize that the foregoing description and examples have been presented for the purpose of illustration and example only. Other variations and modifications of the present invention will be apparent to those of skill in the art, and it is the intent of the appended claims that such variations and modifications be covered. The description as set forth is not intended to be exhaustive or to limit the scope of the invention. Many 15 modifications and variations are possible in light of the above teaching without departing from the spirit and scope of the following claims. It is contemplated that the use of the present invention can involve components having different characteristics. It is intended that the scope of the present invention be defined by the claims appended hereto, giving full cognizance to equivalents in all respects.

## CLAIMS

The embodiments of an invention in which an exclusive property or right is claimed are defined as follows:

1. A method for fabricating a semiconductor device upon a substrate having a grading layer formed thereon, said method comprising the steps of:

forming an intermediate layer, wherein said intermediate layer comprises a lattice constant greater than a lattice constant utilized for said semiconductor device;

5 forming an inverse grading layer which grades from said lattice constant of said intermediate layer to said lattice constant utilized for said semiconductor device;

annealing said grading layer to isolate dislocated material created as a result of forming said grading layer; and

10 creating a strained layer superlattice to further isolate dislocations from said semiconductor device formed thereon.

2. The method of claim 1 further comprising the step of:

forming said grading layer upon said substrate, wherein said grading layer grades a substrate lattice constant past said lattice constant utilized for said semiconductor device.

5

3. The method of claim 2 wherein said semiconductor device comprises a photodiode.

4. The method of claim 2 further comprising the step of forming said grading layer utilizing a (100) nominally on orientation substrate.

5. The method of claim 4 further comprising the step of forming said grading layer utilizing MOCVD.

6. The method of claim 2 wherein said substrate comprises a GaAs substrate.

7. The method of claim 2 wherein said substrate comprises a germanium substrate.

8. The method of claim 2 wherein said substrate comprises a silicon substrate.

9. The method of claim 2 further comprising the step of:

forming at least one grading layer based on an inverse grade on said substrate,

wherein:

said at least one grading layer is formed utilizing heavy n-type doping; and

5 grading material conduction through heavily dislocated regions are maintained utilizing InGaAs as grading material.

10. The method of claim 2 further comprising the step of forming a buffer layer matching a desired lattice constant.

11. The method of claim 3 further comprising the step of growing a p-type portion of an active utilizing carbon.

12. The method of claim 2 further comprising the step of forming at least one layer on said substrate utilizing Debye length doping.

13. The method of claim 2 wherein said strained layer superlattice comprises:

a lower strain;

a medium strain; and

a high strain, such that none of the individual layers of said strained layer

5 superlattice are so thick as to produce dislocations.

14. The method of claim 13 further comprising the step of creating said strained layer superlattice utilizing MOCVD.

15. The method of claim 3 further comprising the step of growing an n-type portion of an active region.

16. A semiconductor device formed upon a substrate, comprising:

at least one annealed grading layer that isolate dislocated material created as a result of forming at least one grading layer on said substrate; and

a strained layer superlattice configured on said at least one grading layer to grow a semiconductor device.

17. The semiconductor device of claim 16 wherein said at least one grading layer is formed utilizing an inverse grade on a (100) orientation substrate.

18. The semiconductor device of claim 17 wherein said at least one grading layer is grown utilizing MOCVD.

19. The semiconductor device of claim 17 wherein said substrate comprises a GaAs substrate.

20. The semiconductor device of claim 17 wherein said substrate comprises a germanium substrate.

21. The semiconductor device of claim 17 wherein said substrate comprises a silicon substrate.

22. The semiconductor device of claim 18 wherein said semiconductor device comprises a photodiode.

23. The semiconductor device of claim 18 wherein:

said at least one grading layer is formed utilizing heavy n-type doping; and

wherein grading material conduction is maintained through heavily dislocated regions utilizing InGaAs as said grading material.

5

24. The semiconductor device of claim 17 further comprising: