SCHWEIZERISCHE EIDGENOSSENSCHAFT

EIDGENÖSSISCHES INSTITUT FÜR GEISTIGES EIGENTUM

(11) CH 707 901 B1

(51) Int. Cl.: H01L 29/06 (2006.01)

### Erfindungspatent für die Schweiz und Liechtenstein

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

## (12) PATENTSCHRIFT

(21) Anmeldenummer: 01183/14

(73) Inhaber:

CREE, INC., 4600 Silicon Drive

Durham, North Carolina 27703 (US)

(22) Anmeldedatum: 05.02.2013

(72) Erfinder:

Lin Cheng, Chapel Hill, North Carolina 27514 (US)

Anant, Kumar Agarwal,

Chapel Hill, North Carolina 27514 (US)

Michael, John O'Loughlin,

Chapel Hill, North Carolina 27516 (US)

Albert, Augustus Burk Jr.,

Chapel Hill, North Carolina 27516 (US)

John, Williams Palmour, Cary, North Carolina 27511 (US)

(43) Anmeldung veröffentlicht: 15.08.2013

(74) Vertreter:

Riederer Hasler & Partner Patentanwälte AG,

Kappelestrasse 15

9492 Eschen (LI)

(30) Priorität: 06.02.2012 US 13/366,658

(86) Internationale Anmeldung:

PCT/US 2013/024740

(24) Patent erteilt: 15.09.2017

(87) Internationale Veröffentlichung:

WO 2013/119548

(45) Patentschrift veröffentlicht: 15.09.2017

### (54) SIC-Vorrichtung mit hoher Sperrspannung, abgeschlossen durch einen Abflachungskantenabschluss.

(57) Die vorliegende Erfindung betrifft eine Siliziumkarbid(SiC)-Halbleitervorrichtung, die sowohl eine hohe Sperrspannung als auch einen niedrigen Durchlasswiderstand aufweist. Die Halbleitervorrichtung weist eine Sperrspannung von wenigstens 10 Kilovolt (kV) und einen Durchlasswiderstand von weniger als 10 Milliohm-Quadratzentimeter ( $m\Omega \cdot cm^2$ ) und besonders bevorzugt von weniger als  $5 m\Omega \cdot cm^2$  auf. Gemäss einer Ausführungsform weist die Halbleitervorrichtung eine Sperrspannung von mindestens 15 kV und einen Durchlasswiderstand von weniger als  $15 m\Omega \cdot cm^2$  und besonders bevorzugt von weniger als  $7 m\Omega \cdot cm^2$  auf. Gemäss einer anderen Ausführungsform weist die Halbleitervorrichtung eine Sperrspannung von mindestens 20 kV und einen Durchlasswiderstand von weniger als  $20 m\Omega \cdot cm^2$  und besonders bevorzugt von weniger als  $10 m\Omega \cdot cm^2$  auf. Die Halbleitervorrichtung ist vorzugsweise, aber nicht notwendigerweise, ein Thyristor wie ein Leistungsthryistor, ein Bipolartransistor (BJT), ein Bipolartransistor mit isolierter Gate-Elektrode (IGBT) oder eine PIN-Diode.

## **Beschreibung**

### **Staatliche Unterstützung**

[0001] Diese Erfindung wurde mit staatlichen Mitteln unter der Vertragsnummer DAAD19-01-C-0067-Task Order 4, vergeben von der US Army, gefördert. Die US-Regierung kann Rechte an dieser Erfindung haben.

### **Verwandte Anmeldungen**

[0002] Diese Anmeldung ist eine Continuation-in-part-Anmeldung der US-Patentanmeldung Nr. 13/108 366, eingereicht im 16. Mai 2011, deren Offenbarung in ihrer Gesamtheit hiermit durch Bezugnahme mitaufgenommen ist.

### **Technisches Gebiet**

[0003] Die vorliegende Erfindung betrifft mit Siliziumkarbid (SiC) hergestellte Halbleitervorrichtungen.

### **Hintergrund**

[0004] Siliziumkarbid (SiC) ist ein bevorzugtes Material für Leistungs- und Hochtemperatur-Halbleitervorrichtungen aufgrund seiner hohen Durchbruchfeldstärke, hohen Wärmeleitfähigkeit und grossen Bandlücke. Um jedoch die Vorteile der hohen Durchbruchfeldstärke in einer Hochspannungsvorrichtung zu nutzen, wird ein effizienter Randabschluss benötigt. Genauer führen Feldverdichtungen an dem Rand der Vorrichtung zum Durchbruch an der Kante der Vorrichtung, was wiederum die Sperrspannung der Vorrichtung auf einen Wert deutlich unterhalb der idealen Sperrspannung (d.h. der Sperrspannung einer ideal parallelen Vorrichtung) verringert. Daher ist ein Randabschluss ein wichtiges Thema bei der Gestaltung von SiC-Halbleitervorrichtungen und insbesondere bei Leistungs-SiC-Halbleitervorrichtungen.

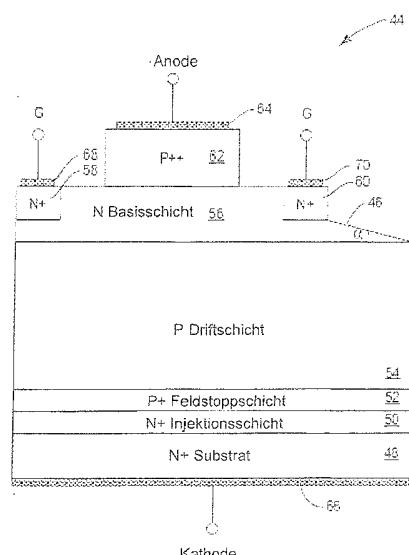

[0005] Eine Art von Randabschluss, die bei SiC-Halbleitervorrichtungen verwendet wird, ist eine planare Randstruktur zur Verbesserung der Durchbruchspannung (JTE). Fig. 1 zeigt eine beispielhafte SiC-Halbleitervorrichtung, nämlich einen Thyristor 10, der eine Anzahl von JTE-Schächten 12, 14 und 16 aufweist. Der Thyristor 10 weist ein Substrat 18, eine Injektionsschicht 20, eine Feldstoppschicht 22, eine Driftschicht 24, eine Basisschicht 26 und eine Anodenschicht 28 auf. Um die JTE-Schächte 12, 14 und 16 zu bilden wird, wie dargestellt, die Basisschicht 26 bis zur Driftschicht 24 geätzt. Die JTE-Schächte 12, 14 und 16 werden dann durch Ionenimplantation in einer freigelegten Oberfläche von der Driftschicht 24 gebildet. Ein Anodenkontakt 30 ist auf der Anodenschicht 28 gebildet, ein Kathodenkontakt 32 ist auf einer Bodenfläche des Substrats 18 gegenüber der Injektionsschicht 20 gebildet, und Gate-Kontakte 34 und 36 sind auf entsprechenden Gate-Bereichen 38 und 40 in der Basisschicht 26 gebildet. Als Ergebnis des Ätzens der Basisschicht 26 bis zu der Driftschicht 24, um die JTE-Schächte 12, 14, und 16 zu bilden, wird eine Ecke 42 gebildet. Die Ecke 42 verursacht elektrische Feldverdichtungen, was wiederum die Sperrspannung des Thyristors 10 auf einen kleineren Wert als die ideale Sperrspannung verringert.

[0006] Daher besteht ein Bedarf an einem Randabschluss für eine SiC-Halbleitervorrichtung, die zu einer Sperrspannung führt, deren Wert sich an die ideale Sperrspannung einer idealen Vorrichtung annähert.

### **Zusammenfassung**

[0007] Die vorliegende Erfindung betrifft eine Siliziumkarbid(SiC)-Halbleitervorrichtung, die sowohl eine hohe Sperrspannung als auch einen niedrigen Durchlasswiderstand aufweist. Die Halbleitervorrichtung weist eine Sperrspannung von wenigstens 10 Kilovolt (kV) und einen Durchlasswiderstand von weniger als 10 Milliohm-Quadratzentimeter ( $m\Omega \cdot cm^2$ ) und besonders bevorzugt von weniger als  $5 m\Omega \cdot cm^2$  auf. Gemäss einer Ausführungsform weist die Halbleitervorrichtung eine Sperrspannung von mindestens 15 kV und einen Durchlasswiderstand von weniger als  $15 m\Omega \cdot cm^2$  und besonders bevorzugt von weniger als  $7 m\Omega \cdot cm^2$  auf. Gemäss einer anderen Ausführungsform weist die Halbleitervorrichtung eine Sperrspannung von mindestens 20 kV und einen Durchlasswiderstand von weniger als  $20 m\Omega \cdot cm^2$  und besonders bevorzugt von weniger als  $10 m\Omega \cdot cm^2$  auf.

[0008] Die Halbleitervorrichtung weist einen negativen Abflachungskantenabschluss bzw. geschrägten oder mit einer Fase versehenen Kastenabschluss auf, der mehrere Stufen aufweist, die sich einem glatten negativen Abflachungskantenabschluss mit einer gewünschten Steigung annähern. Genauer, gemäss einer Ausführungsform, weist der negative Abflachungskantenabschluss wenigstens fünf Stufen auf. Gemäss einer anderen Ausführungsform weist der negative Abflachungskantenabschluss mindestens zehn Stufen auf. Gemäss einer anderen Ausführungsform weist der negative Abflachungskantenabschluss wenigstens fünfzehn Stufen auf. Die gewünschte Steigung beträgt, gemäss einer Ausführungsform, weniger oder gleich 15 Grad. Der negative Abflachungskantenabschluss führt zu einer Sperrspannung der Halbleitervorrichtung von mindestens 10 kV und einem Durchlasswiderstand von weniger als  $10 m\Omega \cdot cm^2$  und besonders bevorzugt von weniger als  $5 m\Omega \cdot cm^2$ . Gemäss einer Ausführungsform führt der negative Abflachungskantenabschluss zu einer Sperrspannung der Halbleitervorrichtung von mindestens 15 kV und einem Durchlasswiderstand von weniger als  $15 m\Omega \cdot cm^2$  und besonders bevorzugt von weniger als  $7 m\Omega \cdot cm^2$ . Gemäss einer anderen Ausführungsform führt der negative Abflachungskantenabschluss zu einer Sperrspannung der Halbleiteranordnung von mindestens 20 kV und einem Durchlasswiderstand von weniger als  $20 m\Omega \cdot cm^2$  und besonders bevorzugt von weniger als  $10 m\Omega \cdot cm^2$ .

**[0009]** Die Halbleitervorrichtung ist vorzugsweise, aber nicht notwendigerweise, ein Thyristor wie ein Leistungsthryistor, ein Bipolartransistor (BJT), ein Bipolartransistor mit isolierter Gate-Elektrode (IGBT) oder eine PIN-Diode. Ferner, gemäss einer Ausführungsform, weist die Halbleitervorrichtung eine Fläche grösser als oder gleich einem Quadratzentimeter auf.

**[0010]** Ein Fachmann wird den Schutzmfang der vorliegenden Offenbarung erfassen und weitere Aspekte nach dem Lesen der folgenden detaillierten Beschreibung der bevorzugten Ausführungsformen in Verbindung mit den beigefügten Zeichnungsfiguren erkennen.

#### **Kurze Beschreibung der Zeichnungsfiguren**

**[0011]** Die beigefügten Zeichnungen, die eingebunden sind und einen Teil dieser Beschreibung bilden, veranschaulichen verschiedene Aspekte der Offenbarung und dienen zusammen mit der Beschreibung dazu, die Prinzipien der Offenbarung zu erklären.

- Fig. 1 zeigt einen Siliziumkarbid(SiC)-Thyristor mit einer herkömmlichen, planaren Randstruktur zur Verbesserung der Durchbruchspannung (JTE);

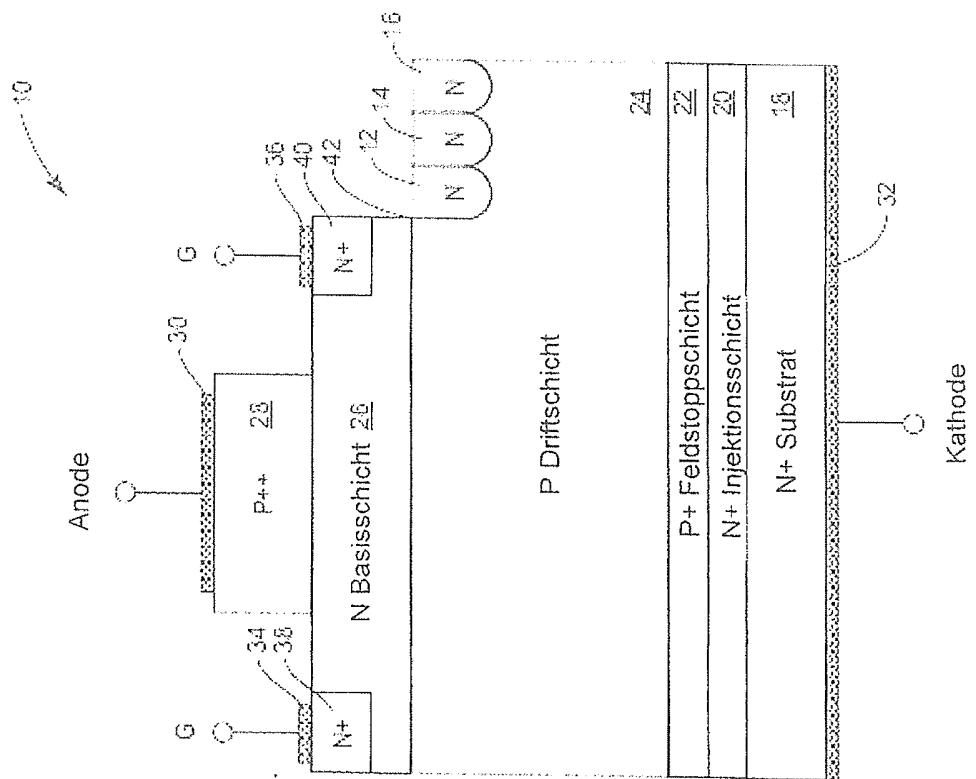

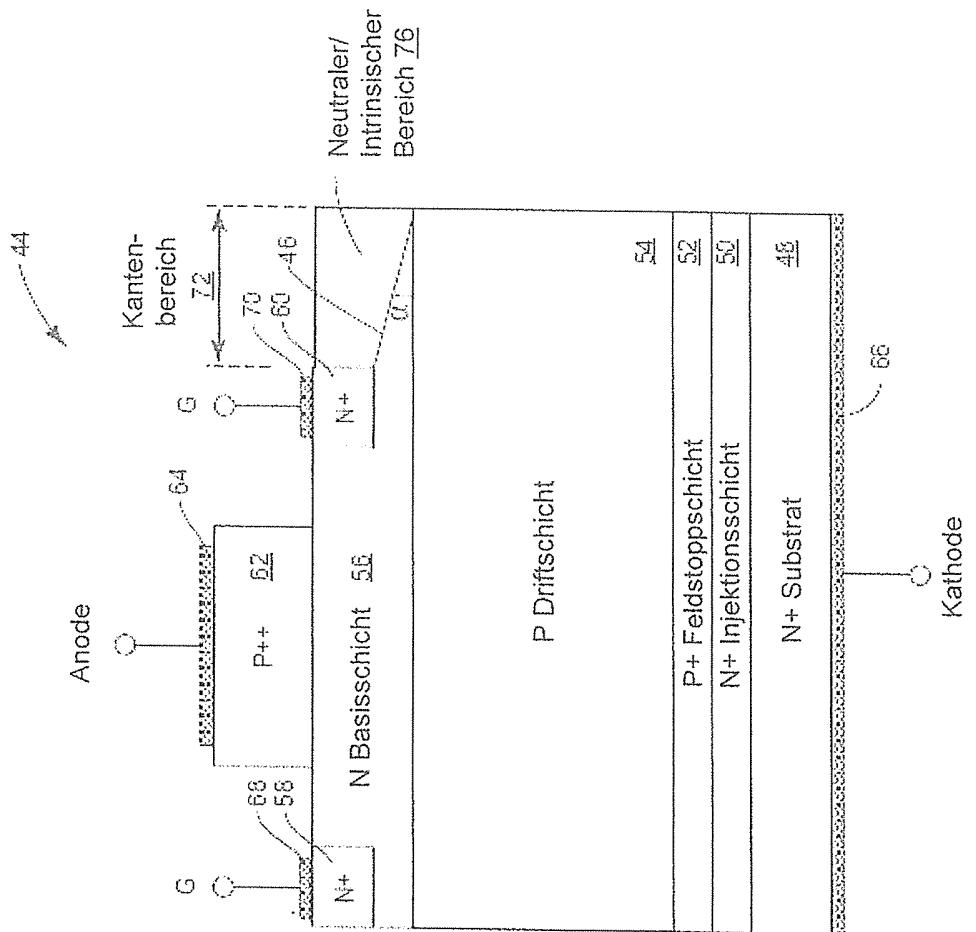

- Fig. 2 zeigt einen SiC-Thyristor mit einem negativen Abflachungskantenabschluss gemäss einem Ausführungsbeispiel der vorliegenden Offenbarung;

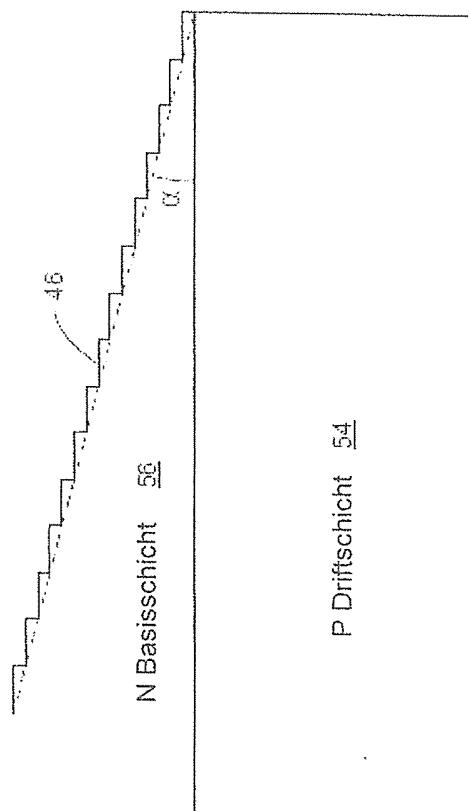

- Fig. 3 zeigt den negativen Abflachungskantenabschluss der Fig. 2 detaillierter, wobei der negative Abflachungskantenabschluss als ein mehrstufiger negativer Abflachungskantenabschluss implementiert ist, der eine Anzahl von Stufen aufweist, die auf einer Oberfläche einer entsprechenden Halbleiterschicht gebildet sind gemäss einer Ausführungsform der vorliegenden Offenbarung;

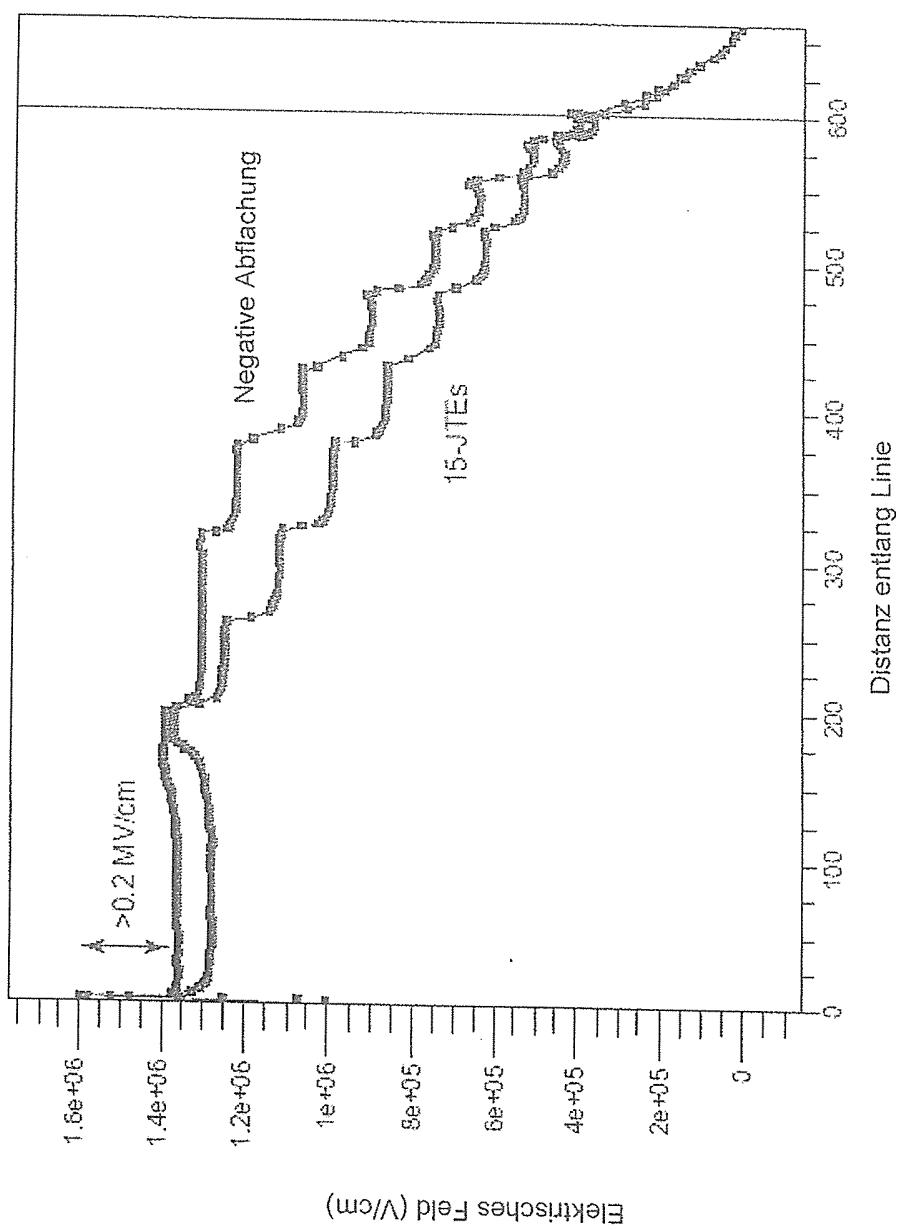

- Fig. 4 zeigt graphisch ein elektrisches Feld in dem mehrstufigen negativen Abflachungskantenabschluss der Fig. 3 im Vergleich zu der eines JTE-Abschlusses gemäss einer Ausführungsform der vorliegenden Offenbarung;

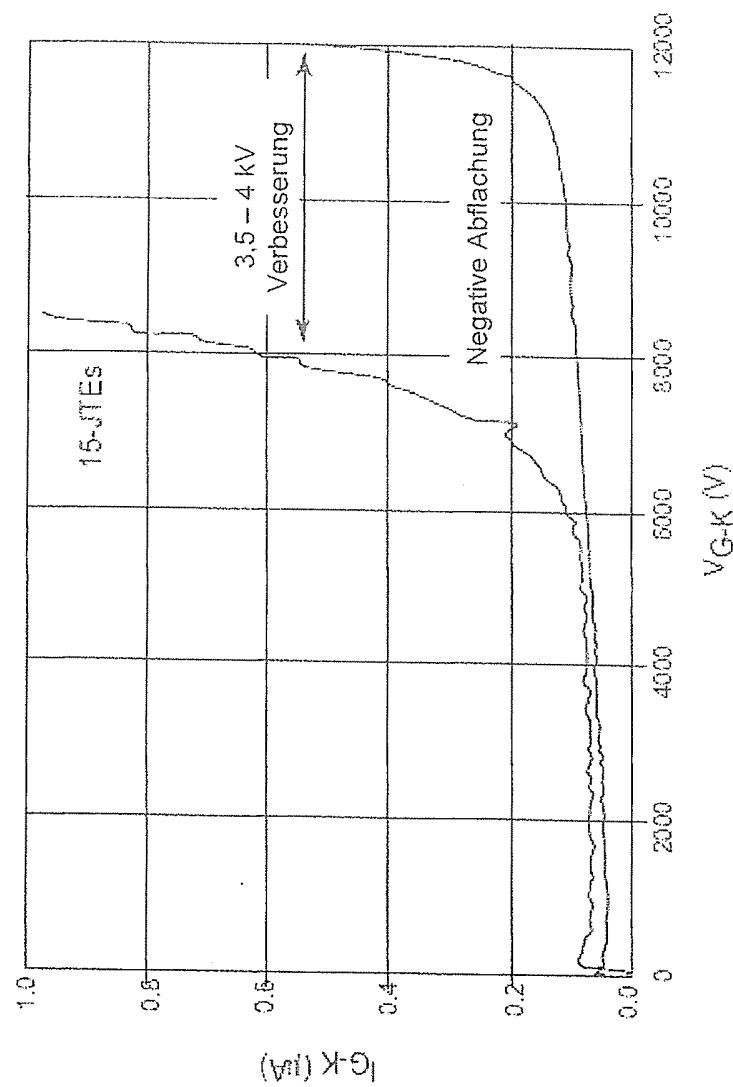

- Fig. 5 zeigt graphisch eine Sperrspannung von dem mehrstufigen negativen Abflachungskantenabschluss der Fig. 3 im Vergleich zu der eines JTE-Abschlusses gemäss einer Ausführungsform der vorliegenden Offenbarung;

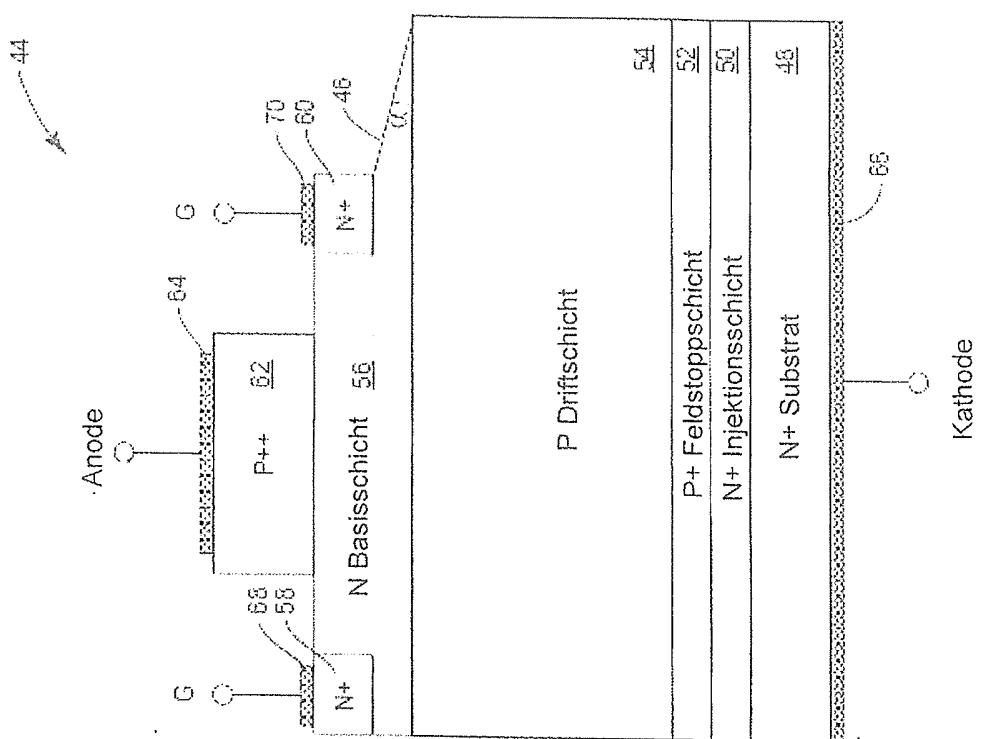

- Fig. 6 zeigt einen Thyristor mit einem mehrstufigen negativen Abflachungskantenabschluss, gebildet durch Gegendotierung der Basisschicht, gemäss einer anderen Ausführungsform der vorliegenden Offenbarung;

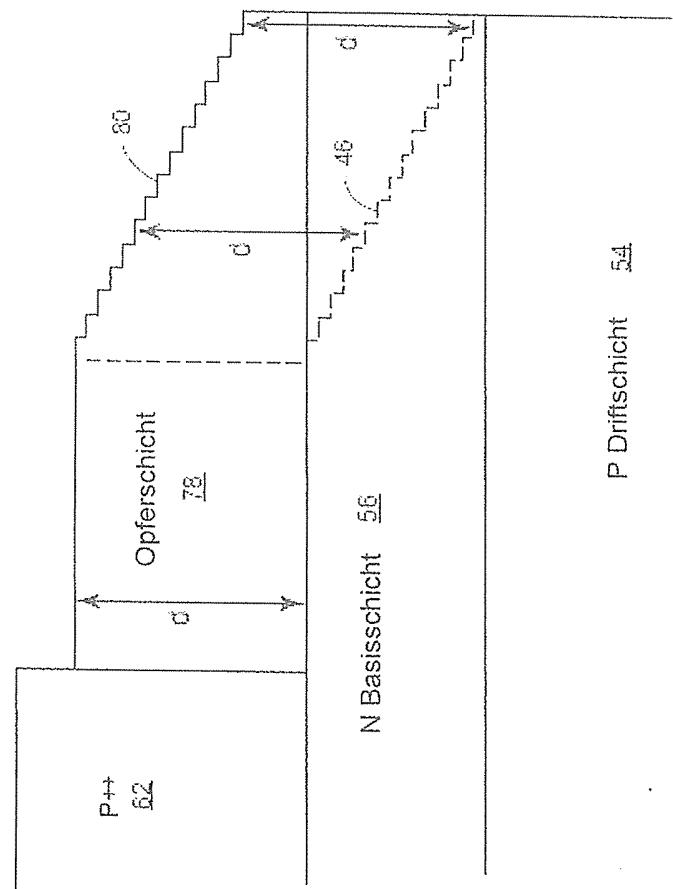

- Fig. 7 zeigt eine Ausführungsform, bei der ein mehrstufiger negativer Abflachungskantenabschluss vorgesehen ist durch Bilden einer Opferschicht auf der Basisschicht und anschliessendem Ätzen der Opferschicht, derart, dass die gewünschte Mehrstufencharakteristik auf die Basisschicht übertragen wird, um dadurch den mehrstufigen negativen Abflachungskantenabschluss bereitzustellen;

- Fig. 8 zeigt einen SiC-Bipolartransistor (BJT) mit einem negativen Abflachungskantenabschluss, wie in Fig. 3 dargestellt, gemäss einer Ausführungsform der vorliegenden Offenbarung;

- Fig. 9 zeigt einen SiC-BJT mit einem negativen Abflachungskantenabschluss, gebildet durch Gegendotierung der Basisschicht, gemäss einer anderen Ausführungsform der vorliegenden Erfindung;

- Fig. 10 zeigt einen P-Typ-SiC-Bipolartransistor mit isolierter Gate-Elektrode (IGBT) mit einem negativen Abflachungskantenabschluss, wie in Fig. 3 dargestellt, gemäss einer Ausführungsform der vorliegenden Offenbarung;

- Fig. 11 zeigt einen P-Typ-SiC-IGBT mit einem negativen Abflachungskantenabschluss, gebildet durch Gegendotierung der Basisschicht, gemäss einer anderen Ausführungsform der vorliegenden Offenbarung;

- Fig. 12 zeigt einen n-Typ-SiC-IGBT mit einem negativen Abflachungskantenabschluss, wie in Fig. 3 dargestellt, gemäss einer Ausführungsform der vorliegenden Offenbarung;

- Fig. 13 zeigt einen n-Typ-SiC-IGBT mit einem negativen Abflachungskantenabschluss, gebildet durch Gegendotierung der Basisschicht, gemäss einer anderen Ausführungsform der vorliegenden Offenbarung;

- Fig. 14 zeigt eine SiC-PIN-Diode mit einem negativen Abflachungskantenabschluss, wie in Fig. 3 dargestellt, gemäss einer Ausführungsform der vorliegenden Offenbarung;

- Fig. 15 zeigt eine SiC-PIN-Diode mit einem negativen Abflachungskantenabschluss, gebildet durch Gegendotierung einer der Halbleiterschichten, gemäss einer weiteren Ausführungsform der vorliegenden Offenbarung;

- Fig. 16 zeigt einen SiC-U-Kanal-Metall-Oxid-Halbleiter-Feldeffekttransistor (UMOSFET) mit einem negativen Abflachungskantenabschluss, wie in Fig. 3 dargestellt, gemäss einer anderen Ausführungsform der vorliegenden Offenbarung;

- Fig. 17 zeigt einen SiC-UMOSFET mit einem negativen Abflachungskantenabschluss, gebildet durch Gegendotierung der Basisschicht, gemäss einer anderen Ausführungsform der vorliegenden Offenbarung;

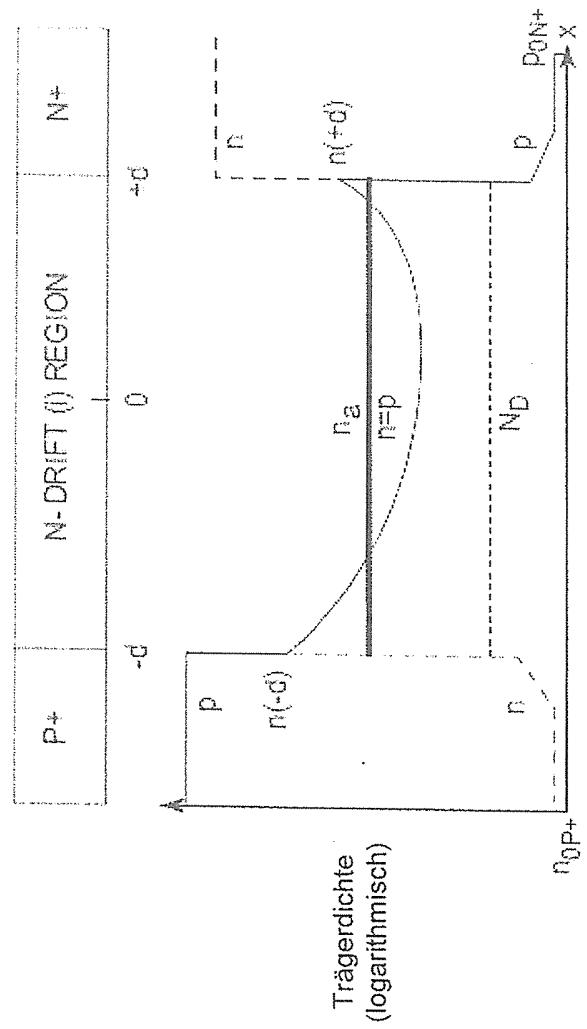

- Fig. 18 zeigt grafisch die Ladungsträgerverteilung innerhalb eines Leitungsthyristors im Durchlasszustand;

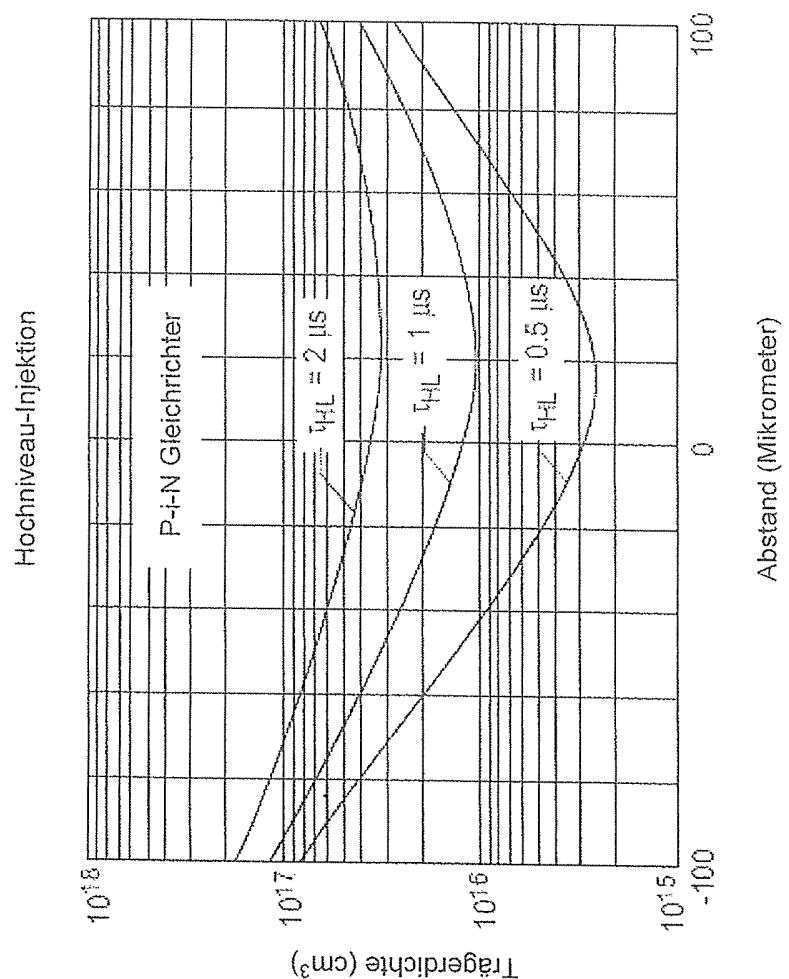

- Fig. 19 zeigt grafisch die Ladungsträgerverteilung unter Hochniveau-Injektionsbedingungen für einen PIN-Gleichrichter;

- Fig. 20 zeigt grafisch die Ladungsträgerverteilung als Funktion der Hochniveau-Trägerlebensdauer unter Hochniveau-Injektionsbedingungen für einen PIN-Gleichrichter;

- Fig. 21A bis 21D zeigen ein Verfahren zur Herstellung des SiC-Thyristors der Fig. 2, die eine Anzahl von Ladungsträgerlebensdauer-Verbesserungstechniken aufweist, die zu einem niedrigen Durchlasswiderstand des SiC-Thyristors gemäss einer Ausführungsform der vorliegenden Offenbarung führen;

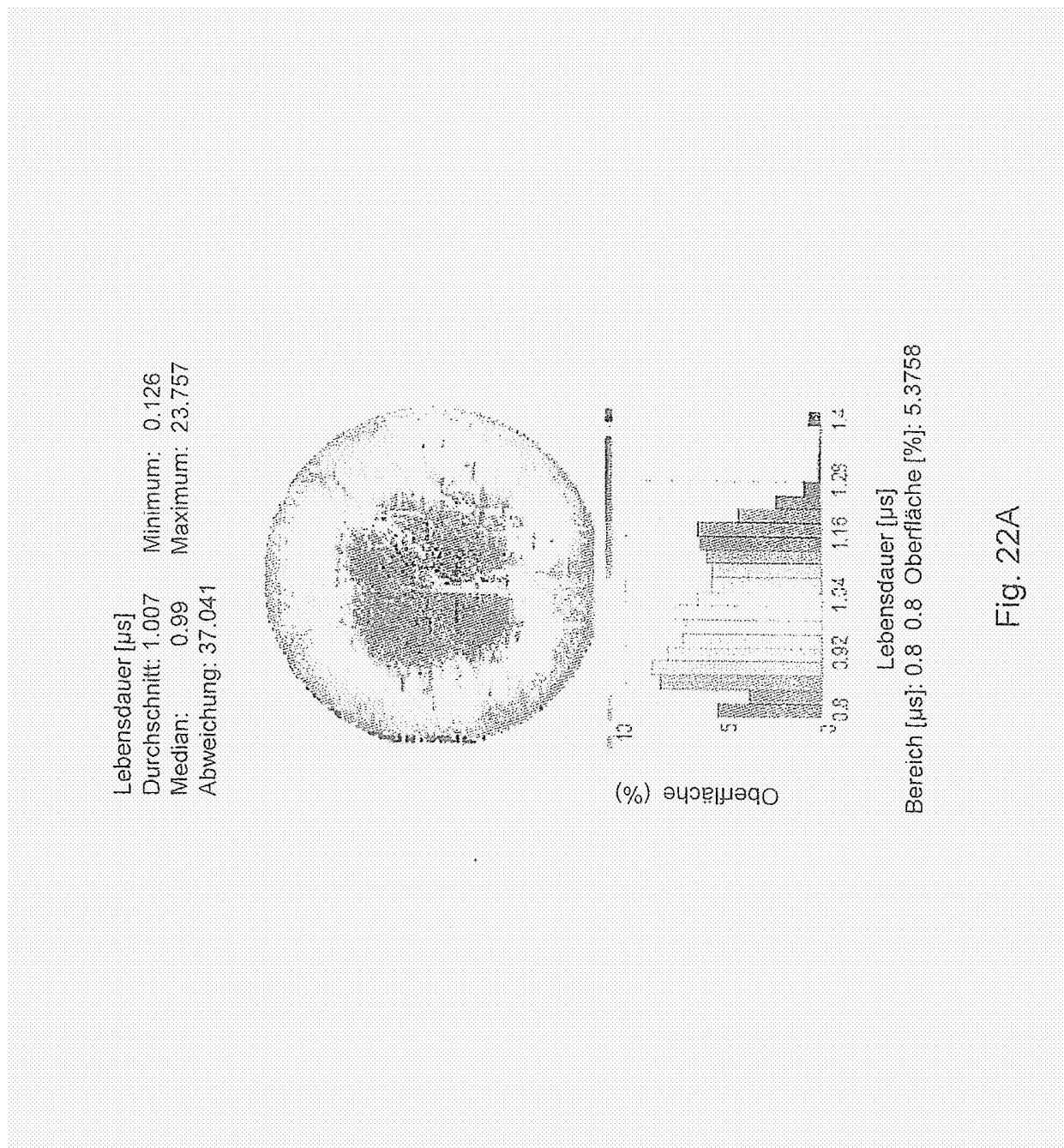

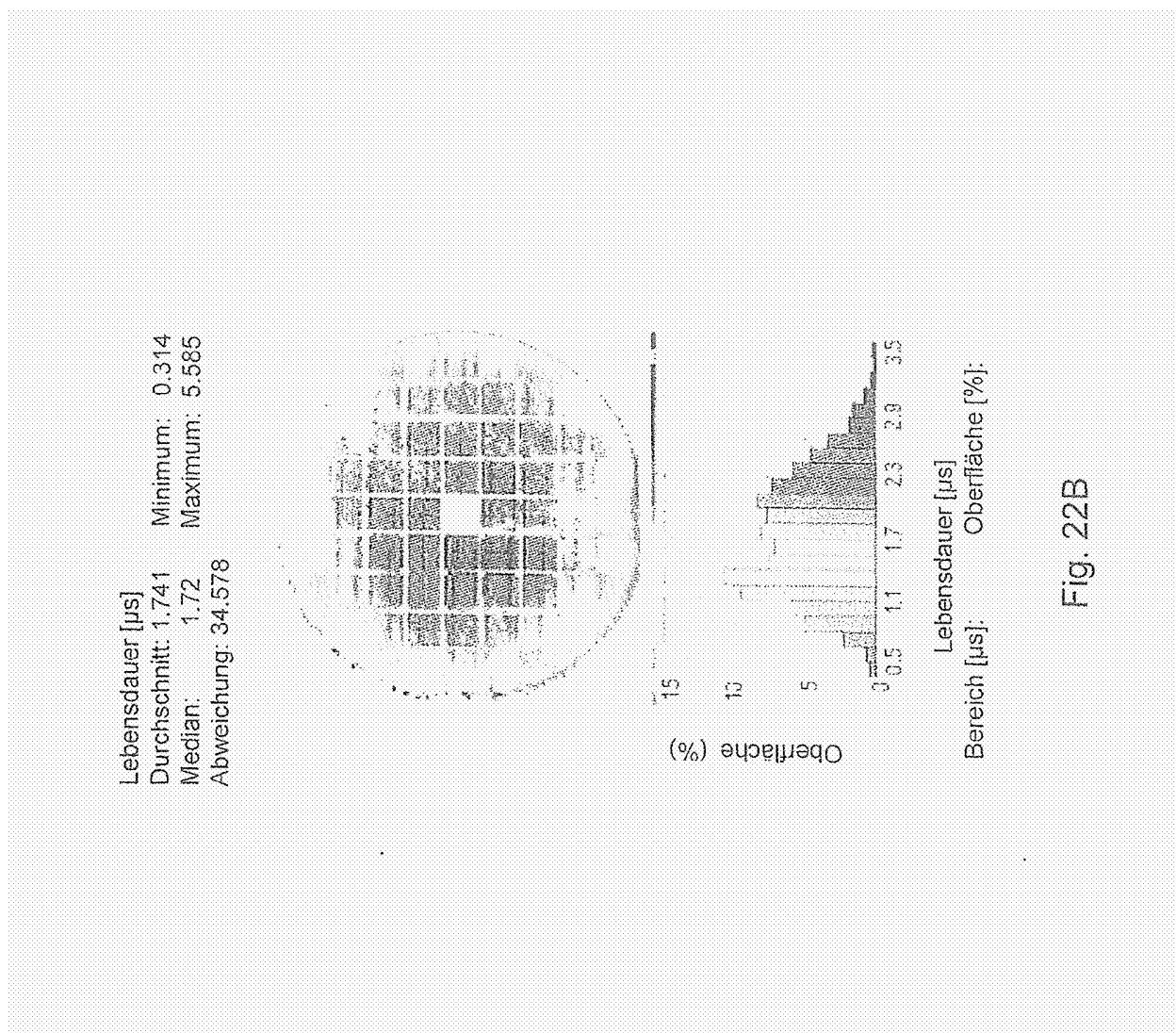

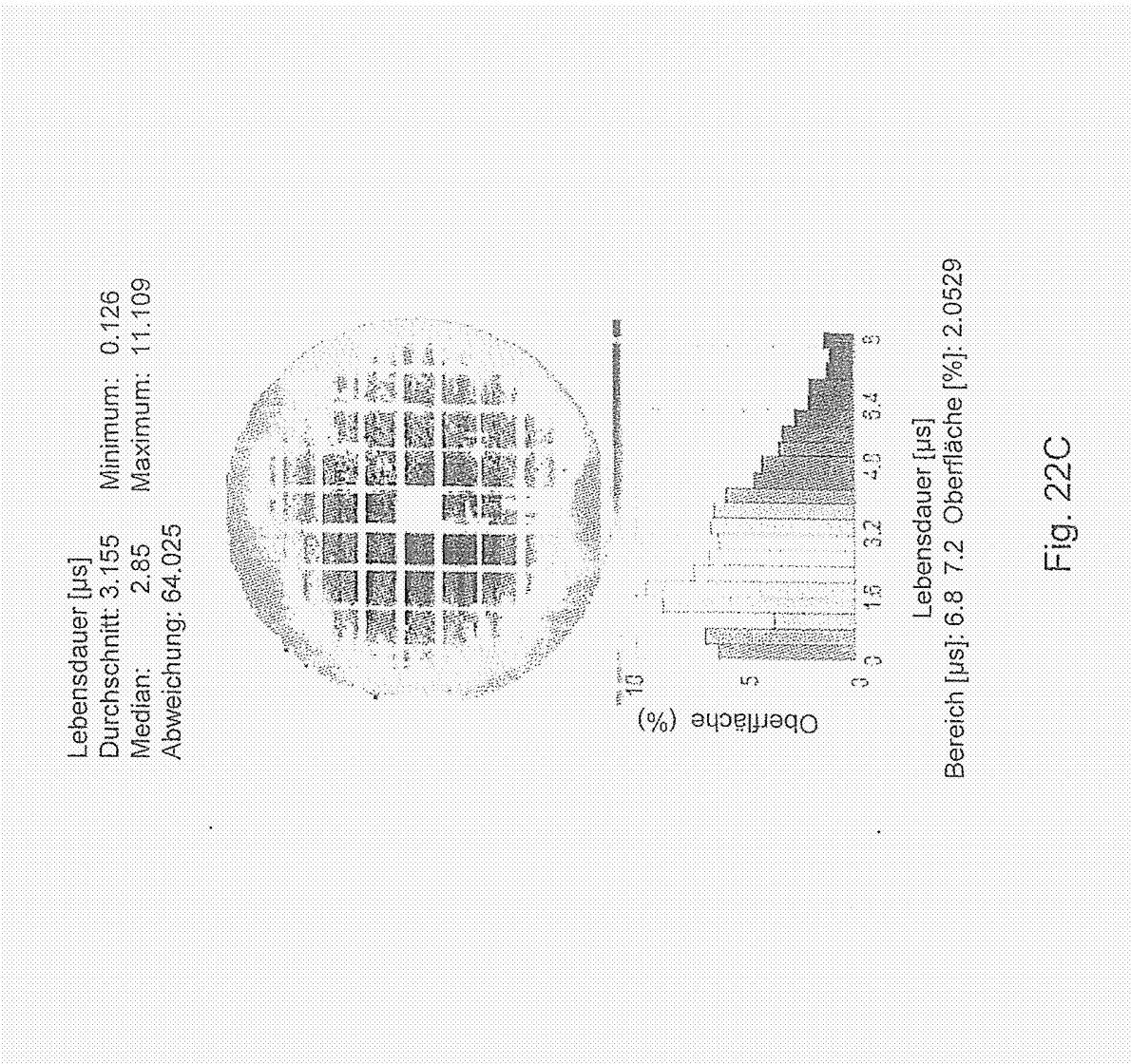

- Die Fig. 22A bis 22C zeigen graphisch Messungen der Ladungsträgerlebensdauer für eine Anzahl beispielhafter Thyristoren, die nach dem Verfahren gemäss der Fig. 21A bis 21D gefertigt sind; und

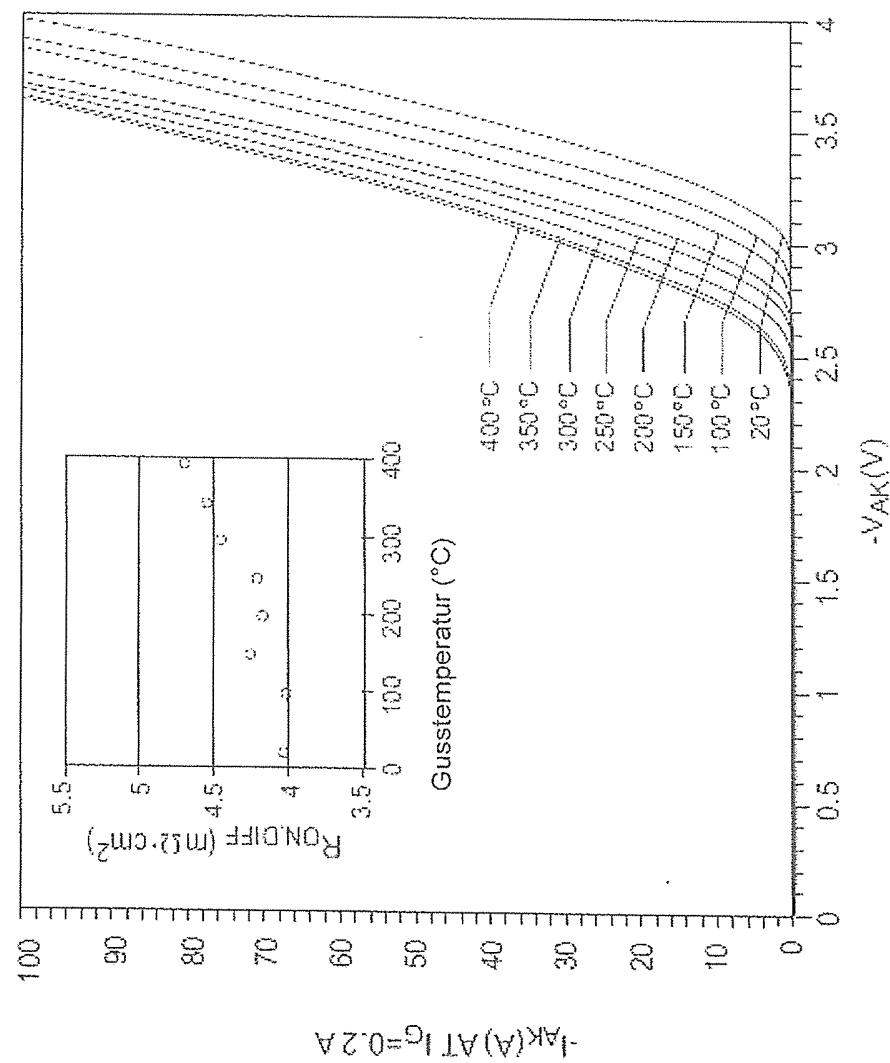

- Fig. 23 zeigt graphisch Durchlasseigenschaften, einschliesslich eines Durchlasswiderstands eines mit Ladungsträgerlebensdauer-Verbesserungstechniken hergestellten Thyristors gemäss einem Ausführungsbeispiel der vorliegenden Offenbarung.

### **Detaillierte Beschreibung**

**[0012]** Die nachfolgenden Ausführungsformen stellen die notwendigen Informationen für Fachleute auf dem Gebiet bereit, um die Ausführungsformen umzusetzen und veranschaulichen die beste Art der Umsetzung der Ausführungsformen. Beim Lesen der folgenden Beschreibung im Licht der beigefügten Zeichnungen wird der Fachmann die Konzepte der Offenbarung verstehen und Anwendungen dieser Konzepte erkennen, die hier nicht besonders abgehandelt wurden. Es sollte klar sein, dass diese Konzepte und Anwendungen innerhalb des Umfangs der Offenbarung und der beigefügten Ansprüche liegen.

**[0013]** Es versteht sich, dass, obwohl die Ausdrücke erste, zweite usw. verwendet werden können, um verschiedene Elemente zu beschreiben, diese Elemente nicht auf diese Ausdrücke beschränkt sind. Diese Ausdrücke werden nur verwendet, um ein Element von einem anderen zu unterscheiden. Zum Beispiel könnte ein erstes Element als ein zweites Element bezeichnet werden, und ähnlich kann ein zweites Element als ein erstes Element bezeichnet werden, ohne von dem Umfang der vorliegenden Offenbarung abzuweichen. Wie hier verwendet, bedeutet der Ausdruck «und/oder» jede und alle Kombinationen von einem oder mehreren der zugeordneten aufgelisteten Elementen.

**[0014]** Es versteht sich, dass, wenn ein Element wie eine Schicht, ein Bereich oder ein Substrat als «auf» oder als erstreckend «auf» ein anderes Element bezeichnet wird, sich es direkt auf oder sich direkt auf ein anderes Element erstrecken kann oder es können auch Elemente dazwischen vorhanden sein. Im Gegensatz dazu sind, wenn ein Element als «direkt an» oder als erstreckend «unmittelbar auf» ein anderes Element bezeichnet wird, keine dazwischenliegenden Elemente vorhanden. Es versteht sich ausserdem, dass, wenn ein Element als «verbunden» oder «gekoppelt» mit einem anderen Element bezeichnet wird, es direkt verbunden werden kann oder mit einem Element verbunden ist, oder es können dazwischenliegende Elemente vorhanden sein. Im Gegensatz dazu, wenn ein Element als «direkt verbunden» oder «direkt gekoppelt» mit einem anderen Element bezeichnet wird, sind keine dazwischenliegenden Elemente vorhanden.

**[0015]** Relative Begriffe wie «unten» oder «oben» oder «obere» oder «untere» oder «horizontal» oder «vertikal» können hier verwendet werden, um eine Beziehung eines Elements, einer Schicht oder eines Bereichs zu einem anderen Element, Schicht oder Region zu beschreiben, wie in den Figuren dargestellt. Es versteht sich, dass diese Begriffe und die oben diskutierten verschiedenen Orientierungen der Vorrichtung zusätzliche zu den in den Figuren dargestellten Orientierungen umfassen sollen.

[0016] Die hier verwendete Terminologie dient dem Zweck der Beschreibung bestimmter Ausführungsformen und ist nicht als Beschränkung der Offenbarung gedacht. Wie hier verwendet, sollen die Singularformen «ein», «eine» und «der» auch die Pluralformen umfassen, sofern der Kontext nicht eindeutig etwas anderes angibt. Es versteht sich ferner, dass, wenn hier verwendet, die Ausdrücke «umfasst», «umfassend», «enthält» und/oder «mit» die Anwesenheit von angegebenen Merkmalen, ganzen Zahlen, Schritten, Operationen, Elementen und/oder Komponenten spezifiziert, aber nicht die Anwesenheit oder Zugabe von einem oder mehreren anderen Merkmalen, ganzen Zahlen, Schritten, Operationen, Elementen, Komponenten und/oder Gruppen hiervon ausschliesst.

[0017] Soweit nicht anders definiert, haben alle hier verwendeten Ausdrücke (einschliesslich technischer und wissenschaftlicher Ausdrücke) die gleiche Bedeutung, wie sie allgemein von einem Fachmann auf dem Gebiet, auf dem diese Offenbarung liegt, verstanden wird. Es versteht sich ferner, dass Ausdrücke, die hier verwendet werden, eine Bedeutung aufweisen, die mit ihrer Bedeutung im Kontext von dieser Beschreibung und dem relevanten Stand der Technik konsistent ist und nicht in einem idealisierten oder übermässig formalen Sinn ausgelegt werden, wenn dies nicht ausdrücklich hier so definiert ist.

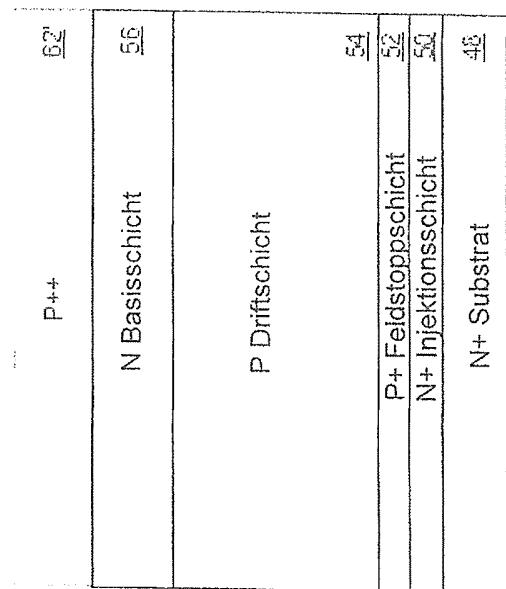

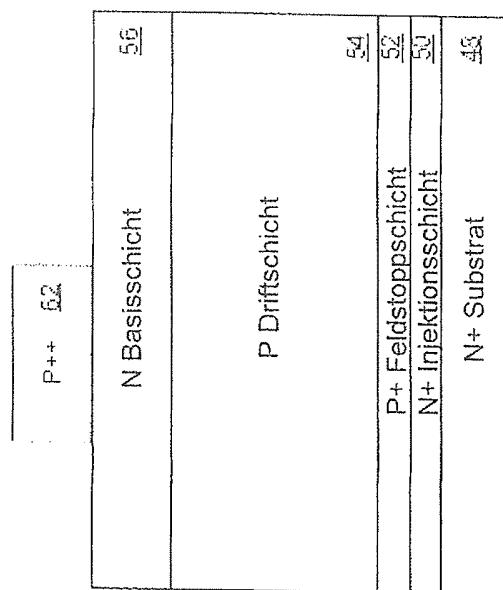

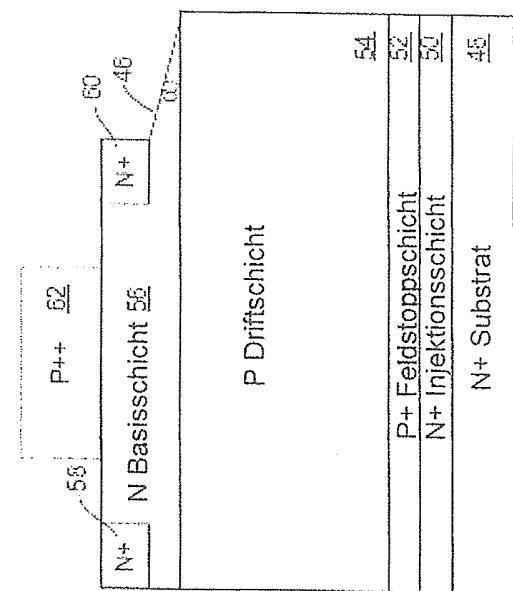

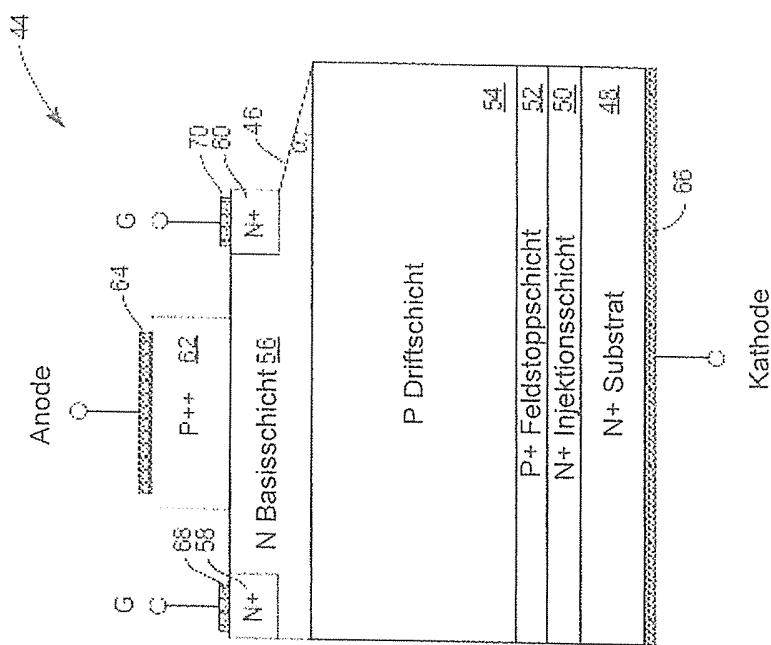

[0018] Fig. 2 zeigt einen Siliziumkarbid(SiC)-Thyristor 44 mit einem negativen Abflachungskantenabschluss 46 gemäss einer Ausführungsform der vorliegenden Offenbarung. Gemäss einer besonderen Ausführungsform ist der Thyristor 44 ein Abschalt-(GTO)-Thyristor. Vorab ist zu beachten, dass, während die Beschreibung sich hier auf SiC-Halbleitervorrichtungen konzentriert, die hierin offenbarten Konzepte gleichermassen auch auf Halbleitervorrichtungen anwendbar sind, die unter Verwendung von anderer Arten von Halbleitermaterialien (z.B. Silizium) hergestellt wurden. Wie dargestellt, weist der Thyristor 44 ein Substrat 48, eine Injektionsschicht 50 auf einer Oberfläche des Substrats 48, eine Feldstoppschicht 52 auf einer Oberfläche der Injektionsschicht 50 gegenüber dem Substrat 48, einer Driftschicht 54 auf einer Oberfläche der Feldstoppschicht 52 gegenüber der Injektionsschicht 50 und eine Basisschicht 56 auf einer Oberfläche der Driftschicht 54 gegenüber der Feldstoppschicht 52 auf. Gate-Bereiche 58 und 60 sind in einer Oberfläche der Basisschicht 56 gegenüber der Driftschicht 54 gebildet und durch einen gewünschten seitlichen Abstand voneinander getrennt. Eine Mesa-Anode oder einer Region 62 ist auf der Oberfläche der Basisschicht 56 zwischen den Gate-Bereichen 58 und 60 angeordnet. Ein Anodenkontakt 64 ist auf einer Oberfläche der Anode 62 gegenüber der Mesa-Basisschicht 56, ein Kathodenkontakt 66 ist auf einer Oberfläche des Substrats 48 gegenüber der Injektionsschicht 50 und Gate-Kontakte 68 und 70 sind auf der Oberfläche der Basisschicht 56 über den Gate-Bereichen 58 und 60 angeordnet. Insbesondere gemäss einem Ausführungsbeispiel ist der Thyristor 44 auf einem Halbleiterchip mit einer Fläche grösser als oder gleich 1 cm<sup>2</sup> hergestellt.

[0019] Das Substrat 48 ist vorzugsweise ein SiC-Substrat und die Injektionsschicht 50, die Feldstoppschicht 52, die Driftschicht 54, die Basisschicht 56 und die Mesa-Anode 62 sind vorzugsweise alle auf dem Substrat 48 mittels Epitaxie aufgebrachte SiC-Schichten. Die Gate-Bereiche 58 und 60 werden vorzugsweise durch Einbringen von Ionen in die Basischicht 56, durch z.B. Ionenimplantation, gebildet. Gemäss dieser besonderen Ausführungsform ist das Substrat 48 ein hochdotierter N-Typ (N +), die Injektionsschicht 50 ein hochdotierter N-Typ (N +), die Feldstoppschicht 52 ein hochdotierter P-Typ (P +), die Driftschicht 54 ist ein dotierter P-Typ (P), die Basisschicht 56 ist ein dotierter N-Typ (N), die Gate-Bereiche 58 und 60 sind stark dotierte N-Typen (N +) und die Mesa-Anode 62 ist ein sehr hoch dotierter P-Typ (p + +). Gemäss einer Ausführungsform weist das Substrat 48 ein Dotierungsniveau in einem Bereich von und einschliesslich 1 × 10<sup>18</sup> bis 1 × 10<sup>19</sup> cm<sup>-3</sup> und eine Dicke in einem Bereich von und einschliesslich etwa 100 bis 350 Mikrometer (μm) auf, die Injektionsschicht 50 weist ein Dotierungsniveau von mehr als oder gleich 1 × 10<sup>18</sup> cm<sup>-3</sup> und eine Dicke in einem Bereich von und einschliesslich 1 bis 5 μm auf, die Feldstoppschicht 52 weist ein Dotierungsniveau in einem Bereich von und einschliesslich 1 × 10<sup>16</sup> bis 5 × 10<sup>17</sup> cm<sup>-3</sup> und eine Dicke in einem Bereich von und einschliesslich 1 bis 5 μm auf, die Driftschicht 54 weist ein Dotierungsniveau kleiner als 2 × 10<sup>14</sup> cm<sup>-3</sup> und eine Dicke auf, die grösser als oder gleich 80 μm ist, die Basisschicht 56 weist ein Dotierungsniveau in einem Bereich von und einschliesslich 1 × 10<sup>16</sup> bis 1 × 10<sup>18</sup> cm<sup>-3</sup> und eine Dicke in einem Bereich von und einschliesslich 0,5 bis 5 μm auf, und die Mesa-Anode 62 weist ein Dotierungsniveau grösser als 1 × 10<sup>19</sup> cm<sup>-3</sup> und eine Dicke in einem Bereich von und einschliesslich 0,5 bis 5 μm auf. Gemäss einer besonderen Ausführungsform weist das Substrat 48 ein Dotierungsniveau in einem Bereich von und einschliesslich 1 × 10<sup>18</sup> bis 1 × 10<sup>19</sup> cm<sup>-3</sup> und eine Dicke in einem Bereich von und einschliesslich 100 bis 350 μm auf, die Injektionsschicht 50 weist ein Dotierungsniveau von 5 × 10<sup>18</sup> cm<sup>-3</sup> und eine Dicke von 1 μm auf, die Feldstoppschicht 52 weist ein Dotierungsniveau von 1 × 10<sup>16</sup> cm<sup>-3</sup> und eine Dicke von 4 μm, die Driftschicht 54 weist ein Dotierungsniveau kleiner als 2 × 10<sup>14</sup> cm<sup>-3</sup> und eine Dicke von 90 μm auf, die Basisschicht 56 weist ein Dotierungsniveau von 1 × 10<sup>17</sup> cm<sup>-3</sup> und eine Dicke von 2,5 μm auf, und die Mesa-Anode 62 weist ein Dotierungsniveau grösser als 2 × 10<sup>19</sup> cm<sup>-3</sup> und eine Dicke in einem Bereich von und einschliesslich 0,5 bis 5 μm auf, Die Gate-Bereiche 58 und 60 sind N +-Zonen, gemäss einer Ausführungsform mit einem Dotierungsniveau grösser als 1 × 10<sup>18</sup> cm<sup>-3</sup>. Schliesslich sind die Kontakte 64, 66, 68 und 70 aus einem geeigneten Kontaktmaterial (z.B. Metall, Metalllegierung etc.) gebildet.

[0020] Eine Kante des Thyristors 44 ist durch den negativen Abflachungskantenabschluss 46 abgeschlossen. Gemäss einer Ausführungsform beträgt eine Breite des negativen Abflachungskantenabschlusses 46 600 μm. Gemäss einer bevorzugten Ausführungsform beträgt ein Neigungswinkel ( $\alpha$ ) des negativen Abflachungskantenabschlusses 46 weniger als oder gleich 15 Grad. Wie detaillierter unten diskutiert wird, ist der negative Abflachungskantenabschluss 46 als mehrstufiger negativer Abflachungskantenabschluss 46 ausgebildet, der sich einer glatten Steigung annähert. Bemerkenswert ist, dass ein negativer Abflachungskantenabschluss mit einer glatten Steigung in SiC nicht realisierbar ist. Zum Beispiel kann Nassätzten verwendet werden, um eine negativen Abflachungskantenabschluss mit einer glatten Steigung für Siliziumvor-

richtungen zu bilden, aber Nassätzen ist nicht geeignet für SiC und kann daher nicht verwendet werden, um einen negativen Abflachungskantenabschluss mit einer glatten Steigung für SiC-Vorrichtungen zu bilden. Daher ist, wie hier diskutiert, der negative Abflachungskantenabschluss 46 als mehrstufiger negativer Abflachungskantenabschluss ausgebildet, der sich einer glatten Steigung annähert.

[0021] Gemäss einer Ausführungsform weist der mehrstufige negative Abflachungskantenabschluss 46 eine Reihe von Stufen auf, die sich einer gleichmässigen Flanke mit dem gewünschten Neigungswinkel ( $\alpha$ ) annähern. Gemäss einer Ausführungsform weist der mehrstufige negative Abflachungskantenabschluss mindestens 10 Stufen auf, die sich einer gleichmässigen Flanke mit dem gewünschten Neigungswinkel ( $\alpha$ ) annähern. Gemäss einer anderen Ausführungsform weist der mehrstufige negative Abflachungskantenabschluss 46 mindestens 15 Stufen auf, die sich einer gleichmässigen Flanke mit dem gewünschten Neigungswinkel ( $\alpha$ ) annähern. Als Ergebnis des negativen Abflachungskantenabschlusses 46 nähert sich eine Sperrspannung des Thyristors 44 einer Sperrspannung einer idealen parallelebenen Vorrichtung an. Gemäss dieser besonderen Ausführungsform ist die Sperrspannung grösser oder gleich 12 Kilovolt (kV). Wie hier verwendet, ist die Sperrspannung der Vorrichtung eine Spannung, bei der die Vorrichtung einen 1 Mikroampere ( $\mu$ A) starken Strom führt. Im Falle des Thyristors 44 ist die Sperrspannung eine Spannung, die zwischen dem Anodenkontakt 64 und dem Kathodenkontakt 66 angelegt einen durch den Thyristor 441  $\mu$ A Strom fliessenden Strom verursacht, wenn keine Spannung an den Gate-Kontakten 68 und 70 anliegt.

[0022] Fig. 3 zeigt den negativen Abflachungskantenabschluss 46 aus Fig. 2 detaillierter gemäss einem Ausführungsbeispiel der vorliegenden Offenbarung. Wie gezeigt, ist der negative Abflachungskantenabschluss 46 insbesondere ein mehrstufiger negativer Abflachungskantenabschluss 46. Gemäss dieser besonderen Ausführungsform weist der mehrstufige negative Abflachungskantenabschluss 4615 Stufen auf, die den gewünschten Neigungswinkel ( $\alpha$ ) annähern. Der mehrstufige negative Abflachungskantenabschluss baut Feldverdichtungen ab, wodurch die Sperrspannung erhöht wird. Wie unten diskutiert wird, wird gemäss einer Ausführungsform die Sperrspannung auf mindestens 12 kV erhöht. Der mehrstufige negative Abflachungskantenabschluss 46 dieser Ausführungsform wird durch Ätzen der Basisschicht 56 unter Verwendung einer geeigneten Anzahl von Masken gebildet. Gemäss einer Ausführungsform ist die Anzahl von Masken gleich der Anzahl der Stufen (z.B. 15 Masken, um 15 Stufen zu bilden). Gemäss einer anderen Ausführungsform kann die Anzahl von Masken optimiert werden, um die Anzahl der Ätzschritte zu reduzieren, so dass die Gesamtzahl der Masken kleiner als die Anzahl der Stufen des mehrstufigen negativen Abflachungskantenabschlusses 46 ist (z.B. 4 bis 15 Masken für 15 Stufen).

[0023] Fig. 4 vergleicht graphisch die Verteilung des elektrischen Feldes entlang des mehrstufigen negativen Abflachungskantenabschlusses 46 der Fig. 3 mit der einer 15 Schacht planaren Randstruktur zur Verbesserung der Durchbruchspannung (JTE) bei 12 kV gemäss einer Ausführungsform der vorliegenden Offenbarung. Wie gezeigt, verringert der mehrstufige negative Abflachungskantenabschluss 46 wirksam das elektrische Spitzenfeld an der Mesa-Grabenecke (beispielsweise die Ecke 42 des Thyristors 10 der Fig. 1) auf weniger als 1,4 Mega-Volt pro Zentimeter (MV/cm). Mit anderen Worten wird das elektrische Spitzenfeld an der Verbindungskante um mehr als 0,2 MV/cm reduziert.

[0024] Fig. 5 vergleicht graphisch die Sperrspannung des Thyristors 44 mit dem mehrstufigen negativen Abflachungskantenabschluss 46 der Fig. 3 mit dem von einem Thyristor (beispielsweise der Thyristor 10 von Fig. 1) mit einem 15-Schacht-JTE-Randabschluss gemäss einer Ausführungsform der vorliegenden Offenbarung. Wie dargestellt, weist als ein Ergebnis der mehrstufige negative Abflachungskantenabschluss 46 des Thyristors 44 eine Sperrspannung in einem Bereich von 11,5 bis 12 kV auf. Dies ist eine 3,5 bis 4 kV Verbesserung gegenüber der 9 kV Sperrspannung des 15-Schächte-JTE-Randabschlusses.

[0025] Fig. 6 zeigt den Thyristor 44 mit dem negativen Abflachungskantenabschluss 46 gemäss einer anderen Ausführungsform der vorliegenden Offenbarung. Gemäss dieser Ausführungsform wird anstelle von Ätzen der Basisschicht 56, um den mehrstufigen negativen Abflachungskantenabschluss 46 zu bilden, wie oben mit Bezug auf Fig. 3 erörtert, der negative Abflachungskantenabschluss 46 durch Gegendotierung der Basisschicht 56 mit P-Typ-Ionen in einer Kantenbereich 72 benachbart zu dem Gate-Bereich 60 gegenüber der Mesa-Anode 62 gebildet, die die n-Typ-Leitfähigkeit der Basisschicht 56 im Kantenbereich 72 ausgleichen, um einen neutralen oder intrinsischen Bereich 76 mit einer gewünschten negativen Abflachungskantenabschlusscharakteristik bereitzustellen. Die P-Typ-Ionen können beispielsweise Aluminium (Al), Bor (B) oder dergleichen sein. Der negative Abflachungskantenabschluss 46 wird dadurch an einer Schnittstelle des Neutralbereichs 76 und einem Rest der Basisschicht 56 gebildet. Insbesondere, gemäss einer Ausführungsform, werden Ionen in unterschiedliche Tiefen implantiert, die stufenweise ausgehend vom Ende des Randbereich 72 benachbart zu dem Gate-Bereich 60 zunehmen und sich nach aussen fortsetzen, um die gewünschte Anzahl von Stufen und Steigung (et) für den negativen Abflachungskantenabschluss 46 bereitzustellen.

[0026] Fig. 7 zeigt ein weiteres Verfahren, mit dem der negative Abflachungskantenabschluss 46 gebildet werden kann. Gemäss dieser Ausführungsform wird eine Opferschicht 78 auf der Oberfläche der Basisschicht 56 über einen Bereich, in dem der negative Abflachungskantenabschluss 46 gebildet werden soll, gebildet. Die Opferschicht 78 kann zum Beispiel SiO<sub>2</sub>, Fotolack oder ein ähnliches Material sein. Die Opferschicht 78 wird geätzt oder anderweitig strukturiert, um eine negative Fase 80 mit einer gewünschten mehrstufigen Charakteristik (d.h. die Anzahl von Stufen, Neigung, Breite etc.) für den negativen Abflachungskantenabschluss 46 bereitzustellen. Ein Ätzprozess wird dann durchgeführt, um die Opferschicht 78 zu entfernen. Insbesondere wird ein Ätzprozess durchgeführt, um bis zu einer gewünschten Tiefe (d) zu ätzen, die in diesem Beispiel gleich der Dicke der Opferschicht 78 und auch gleich der Dicke der Basisschicht 56 ist. Jedoch

ist die vorliegende Erfindung nicht darauf beschränkt. Als Folge des Ätzens wird die negative Fase 80 effektiv auf der Basisschicht 56 übertragen, um dadurch den mehrstufigen negativen Abflachungskantenabschluss 46 bereitzustellen.

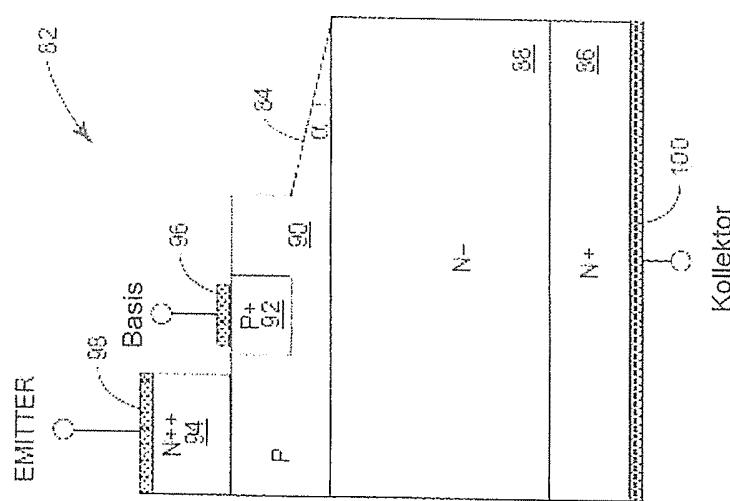

[0027] Die Fig. 8 bis 17 zeigen weitere, nicht einschränkende Beispiele für andere Arten von SiC-Vorrichtungen, die den oben mit Bezug auf den Thyristor 44 beschriebenen negativen Abflachungskantenabschluss nutzen können. Insbesondere Fig. 8 zeigt einen SiC-Bipolartransistor (BJT) 82 mit einem negativen Abflachungskantenabschluss 84 gemäss einer Ausführungsform der vorliegenden Offenbarung. Der BJT 82 weist ein N + -Substrat 86, eine n-Typ-Driftschicht 88 auf einer Oberfläche des Substrats 86, eine P-Typ-Basisschicht 90 auf einer Oberfläche der Driftschicht 88 gegenüber dem Substrat 86, einen P + -Basisbereich 92, gebildet in der Basisschicht 90, einen N + + Mesa-Emitter 94 auf der Oberfläche der Basisschicht 90 gegenüber der Drift-Schicht 88, einen Basiskontakt 96 auf dem Basisbereich 92, einen Emitter-Kontakt 98 über dem Mesa-Emitter 94 und einen Kollektorkontakt 100 auf einer Oberfläche des Substrats 86 gegenüber der Driftschicht 88 auf. Gemäss dieser Ausführungsform ist der negative Abflachungskantenabschluss 84 ein mehrstufiger negativer Abflachungskantenabschluss wie der gemäss Fig. 3. Als Folge des negativen Abflachungskantenabschlusses 84 nähert sich eine Sperrspannung des BJT 82 der Sperrspannung der idealen parallelen Vorrichtung an.

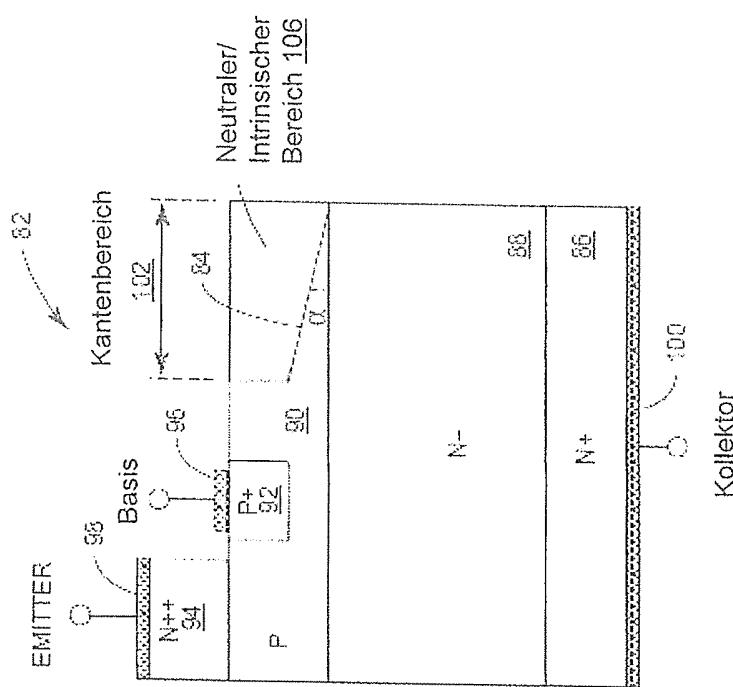

[0028] Fig. 9 zeigt den BJT 82 einschliesslich des negativen Abflachungskantenabschlusses 84 gemäss einer anderen Ausführungsform der vorliegenden Offenbarung. Gemäss diesem Ausführungsbeispiel wird der negative Abflachungskantenabschluss 84 durch Gegendotierung mit N-Typ-Ionen der P-Typ-Basisschicht 90 in einem Randbereich 102 benachbart zu dem P + -Basisbereich 92 gegenüber der Mesa-Emitter 94 gebildet, die die P-Leitfähigkeit der Basisschicht 90 in dem Randbereich 102 ausgleichen, um einen neutralen oder intrinsischen Bereich 106 mit einer gewünschten negativen Abflachungskantenabschlusscharakteristik bereitzustellen. Die N-Typ-Ionen können beispielsweise Stickstoff (N), Phosphor (P) oder dergleichen sein. Der negative Abflachungskantenabschluss 84 wird dadurch an einer Schnittstelle des neutralen Bereichs 106 und einem Rest der Basisschicht 90 gebildet. Insbesondere, gemäss einer Ausführungsform, werden Ionen in unterschiedliche Tiefen implantiert, die stufenweise ausgehend vom Ende des Randbereichs 102 benachbart zu dem P + -Basis-Bereich 92 zunehmen und sich nach aussen fortsetzen, um die gewünschte Anzahl von Stufen und Steigung ( $\alpha$ ) für den negativen Abflachungskantenabschluss 84 bereitzustellen.

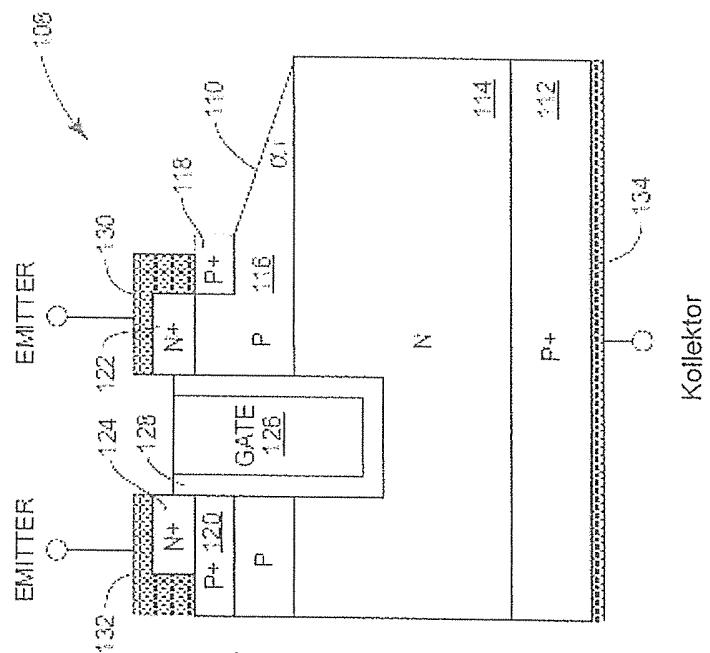

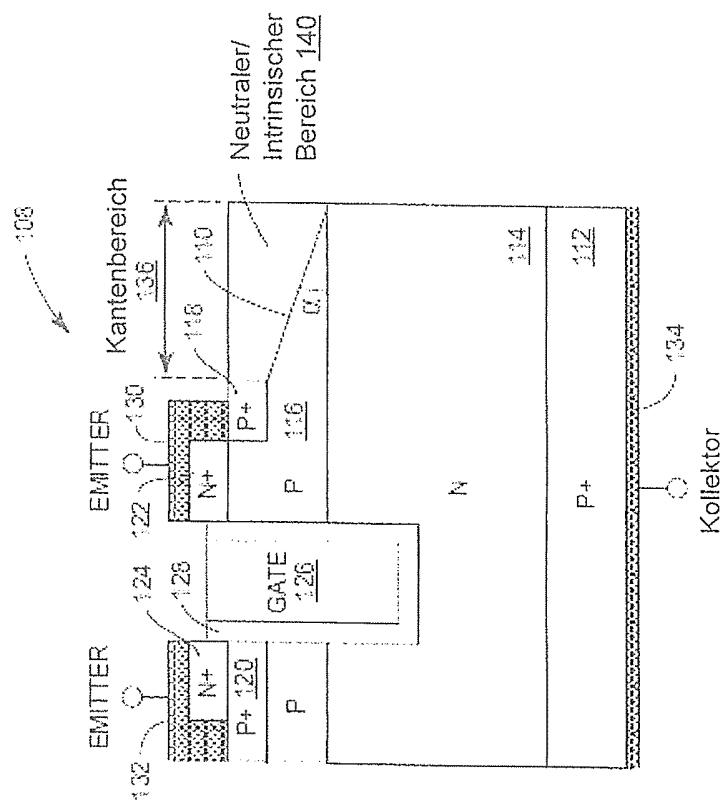

[0029] Fig. 10 zeigt einen P-Typ-SiC-Bipolartransistor mit isolierter Gate-Elektrode (1GBT) 108 mit einem negativen Abflachungskantenabschluss 110 gemäss einer Ausführungsform der vorliegenden Offenbarung. Wie dargestellt, weist der IGBT 108 ein P + -Substrat oder eine Epitaxie-Schicht 112, eine N-Typ-Driftschicht 114 auf einer Oberfläche des Substrats 112, eine Basisschicht 116 auf einer Oberfläche der Drift-Schicht 114 gegenüber dem Substrat 112, P + -Bereiche 118 und 120 auf der Oberfläche der Basisschicht 116 gegenüber der Drift-Schicht 114 und die Emitter-Bereiche 122 und 124 auf. Ein Gate-Kontakt 126 ist, wie gezeigt, in einem Graben gebildet und ist durch einen Gate-Isolator 128 isoliert. Emitter-Kontakte 130 und 132 sind jeweils auf den Emitter-Bereichen 122 und 124 angeordnet, und ein Kollektorkontakt 134 ist auf einer Oberfläche des Substrats 112 gegenüber der Driftschicht 114 angeordnet. Bei dieser Ausführungsform ist der negative Abflachungskantenabschluss 110 ein mehrstufiger negativer Abflachungskantenabschluss wie der von Fig. 3. Als Folge des negativen Abflachungskantenabschlusses 110 nähert sich eine Sperrspannung des 1GBT 108 der Sperrspannung der idealen parallelen Vorrichtung an.

[0030] Fig. 11 zeigt den IGBT 108 mit dem negativen Abflachungskantenabschluss 110 gemäss einer anderen Ausführungsform der vorliegenden Offenbarung. Gemäss diesem Ausführungsbeispiel wird der negative Abflachungskantenabschluss 110 durch Gegendotierung mit N-Typ Ionen der P-Basisschicht 116 in einem Randbereich 136 benachbart zu dem P + -Bereich 118 und dem N + -Emitter-Bereich 122 gegenüber dem Gate-Kontakt 126 gebildet, die die P-Leitfähigkeit der Basisschicht 116 im Randbereich 136 ausgleichen, um einen neutralen oder intrinsischen Bereich 140 mit einer gewünschten Abflachungskantenabschlusscharakteristik bereitzustellen. Die N-Typ-Ionen können beispielsweise Stickstoff (N), Phosphor (P) oder dergleichen sein. Der negative Abflachungskantenabschluss 110 wird dadurch an einer Schnittstelle des neutralen Bereichs 140 und einem Rest der Basisschicht 116 gebildet. Insbesondere, gemäss einer Ausführungsform, werden Ionen in unterschiedliche Tiefen implantiert, die stufenweise ausgehend vom Ende des Randbereichs 136 benachbart zu dem P + -Basis-Bereich 118 zunehmen und sich nach aussen fortsetzen, um die gewünschte Anzahl von Stufen und Steigung ( $\alpha$ ) für den negativen Abflachungskantenabschluss 110 bereitzustellen.

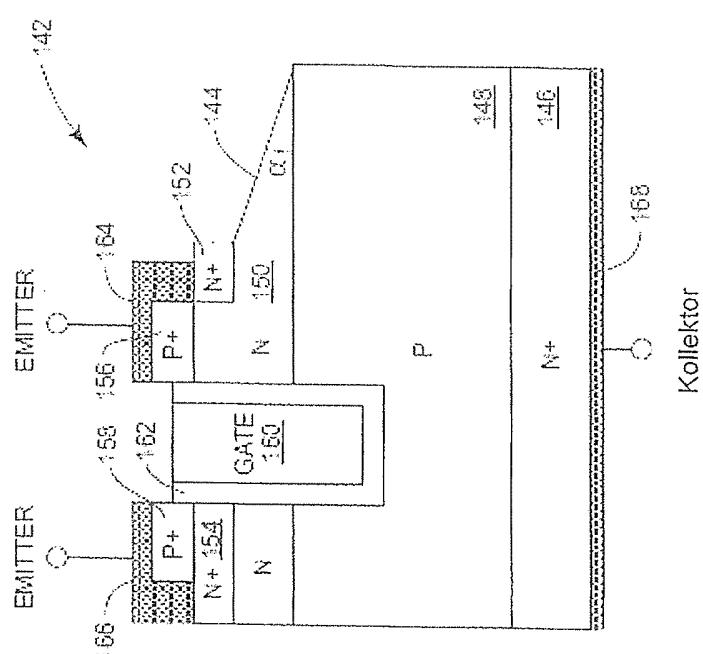

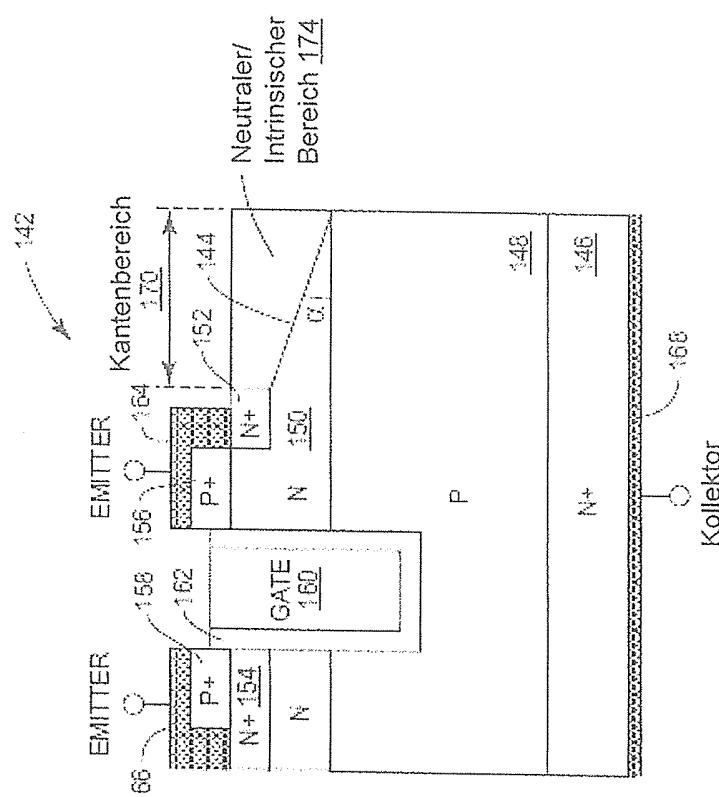

[0031] Fig. 12 zeigt einen n-Typ-SiC-IGBT 142 mit einem negativen Abflachungskantenabschluss 144 gemäss einer Ausführungsform der vorliegenden Offenbarung. Wie dargestellt, weist der IGBT 142 ein Substrat 146, eine Driftschicht 148 auf einer Oberfläche des Substrats 146, eine Basisschicht 150 auf einer Oberfläche der Driftschicht 148 gegenüber dem Substrat 146, N + -Bereiche 152 und 154 auf der Oberfläche der Basisschicht 150 gegenüber der Driftschicht 148 und die Emitter-Bereiche 156 und 158 auf. Ein Gate-Kontakt 160 ist, wie gezeigt, in einem Graben gebildet, und ist durch einen Gate-Isolator 162 isoliert. Emitter-Kontakte 164 und 166 sind auf den Emitter-Bereichen 156 und 158 angeordnet, und ein Kollektorkontakt 168 ist auf einer Oberfläche des Substrats 146 gegenüber der Driftschicht 148 angeordnet. Bei dieser Ausführungsform ist der negative Abflachungskantenabschluss 144 ein mehrstufiger negativer Abflachungskantenabschluss wie der von Fig. 3. Als Folge des negativen Abflachungskantenabschlusses 144 nähert sich eine Sperrspannung des IGBT 142 an die Sperrspannung des idealen parallelen Vorrichtung an.

[0032] Fig. 13 zeigt den IG BT 142 mit dem negativen Abflachungskantenabschluss 144 gemäss einer anderen Ausführungsform der vorliegenden Offenbarung. Gemäss diesem Ausführungsbeispiel wird der negative Abflachungskantenabschluss 144 durch Gegendotierung mit P-Typ-Ionen der n-Basisschicht 150 in einem Randbereich 170 angrenzend an den N + -Bereich 152 und den P + -Emitter-Bereich 156 gegenüber dem Gate-Kontakt 160 gebildet, die die N-Leitfähigkeit

der Basisschicht 150 im Randbereich 170 ausgleichen, um einen neutralen oder intrinsischen Bereich 174 mit einer gewünschten Abflachungskantenabschlusscharakteristik bereitzustellen. Die P-Typ-Ionen können beispielsweise Aluminium (Al), Bor (B) oder dergleichen sein. Der negative Abflachungskantenabschluss 144 wird dadurch an einer Schnittstelle des neutralen Bereichs 174 und einem Rest der Basisschicht 150 gebildet. Insbesondere, gemäss einer Ausführungsform, werden Ionen in unterschiedliche Tiefen implantiert, die stufenweise ausgehend vom Ende des Randbereichs 170 benachbart zu dem N + -Bereich 152 und dem P + -Emitter-Bereich 156 zunehmen und sich nach aussen fortsetzen, um die gewünschte Anzahl von Stufen und Steigung ( $\alpha$ ) für den negativen Abflachungskantenabschluss 144 bereitzustellen.

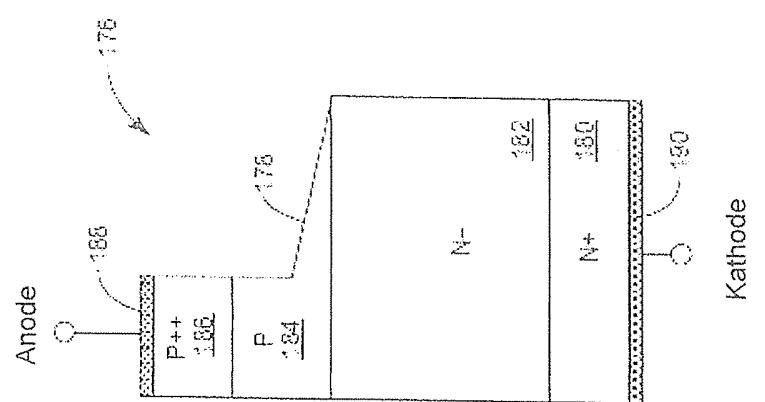

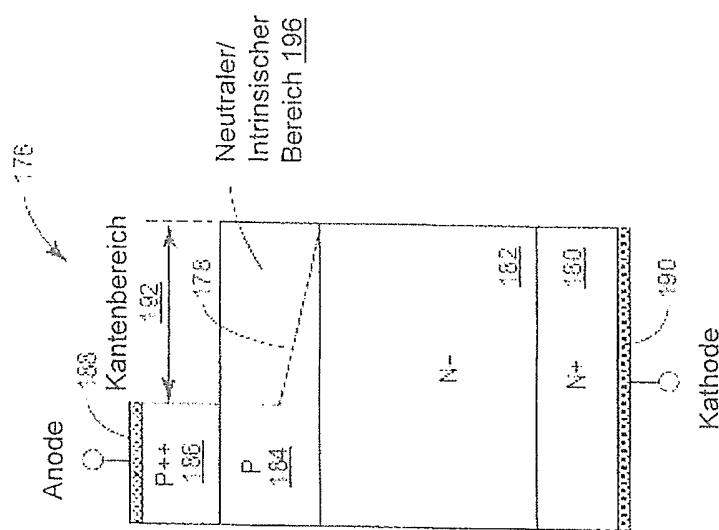

[0033] Fig. 14 zeigt eine SiC-PIN-Diode 176 mit einem negativen Abflachungskantenabschluss 178 gemäss einer Ausführungsform der vorliegenden Offenbarung. Wie dargestellt, weist die PIN-Diode 176 ein N + -Substrat 180, eine n-Driftschicht 182, eine P-Typ-Schicht 184 und eine P + + -Schicht 186 auf. Die N-Driftschicht 182 kann auch als eine intrinsische Schicht zwischen dem N + -Substrat 180 und der P-Typ-Schicht 184 bezeichnet werden, die die PIN-Diode 176 bildet. Die P + + -Schicht 186 kann auch als Mesa-Anode bezeichnet werden. Ein Anodenkontakt 188 ist auf der Oberfläche der P + + -Schicht 186 gegenüber der P-Typ-Schicht 184 angeordnet. Ein Kathodenkontakt 190 ist auf einer Oberfläche des N + -Substrats 180 gegenüber der N-Driftschicht 182 angeordnet. Gemäss diesem Ausführungsbeispiel ist der negative Abflachungskantenabschluss 178 ein mehrstufiger Abflachungskantenabschluss ähnlich dem der Fig. 3. Als Folge des negativen Abflachungskantenabschlusses 178 nähert sich eine Sperrspannung, insbesondere eine Durchbruchspannung der PIN-Diode 176, der Sperrspannung einer idealen parallelebenen Vorrichtung an.

[0034] Fig. 15 zeigt die PIN-Diode 176 mit dem negativen Abflachungskantenabschluss 178 gemäss einer anderen Ausführungsform der vorliegenden Offenbarung. Gemäss diesem Ausführungsbeispiel wird der negative Abflachungskantenabschluss 178 durch Gegendorierung der P-Typ-Schicht 184 mit N-Typ-Ionen in einem Randbereich 192 angrenzend an die P + + -Schicht 186 gebildet, die die P-Leitfähigkeit der P-Typ-Schicht 184 in dem Randbereich 192 ausgleichen, um einen neutralen oder intrinsischen Bereich 196 mit einer gewünschten negativen Abflachungskantenabschlusscharakteristik bereitzustellen. Die N-Typ-Ionen können beispielsweise Stickstoff (N), Phosphor (P) oder dergleichen sein. Der negative Abflachungskantenabschluss 178 wird dadurch an einer Schnittstelle des neutralen Bereichs 196 und einem Rest der P-Typ-Schicht 184 gebildet. Insbesondere, gemäss einer Ausführungsform, werden Ionen in unterschiedliche Tiefen implantiert, die stufenweise ausgehend vom Ende des Randbereichs 192 benachbart zu der P + + -Schicht zunehmen und sich nach aussen fortsetzen, um die gewünschte Anzahl von Stufen und Steigung ( $\alpha$ ) für den negativen Abflachungskantenabschluss 178 bereitzustellen.

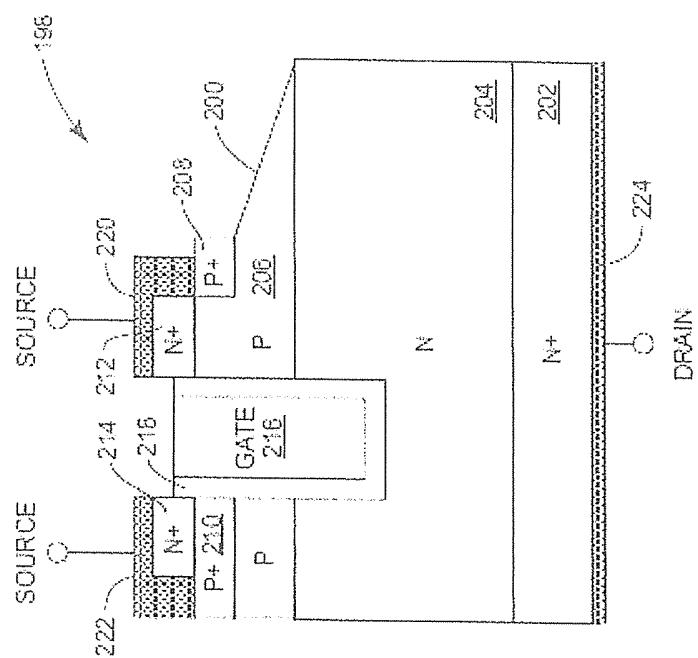

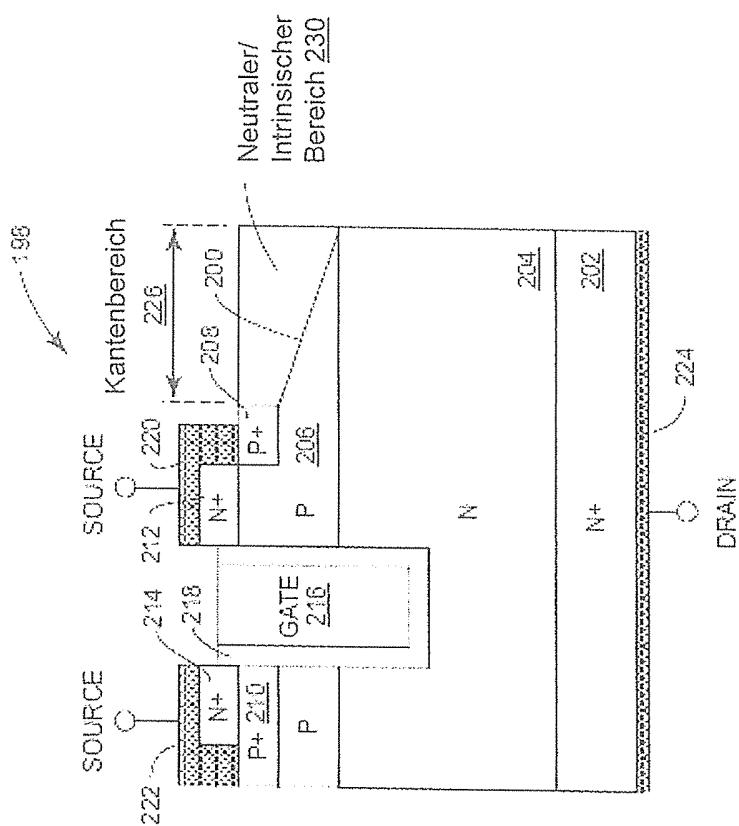

[0035] Fig. 16 zeigt einen SiC-U-Kanal-Metall-Oxid-Halbleiter-Feldeffekttransistor (UMOSFET) 198 mit einem negativen Abflachungskantenabschluss 200 gemäss einer Ausführungsform der vorliegenden Offenbarung. Wie dargestellt, weist der UMOSFET 198 ein N + -Substrat 202, eine N-Typ-Driftschicht 204 auf einer Oberfläche des Substrats 202, eine P-Basischicht 206 auf einer Oberfläche der Driftschicht 204 gegenüber dem Substrat 202, P + -Regionen 208 und 210 auf der Oberfläche der Basisschicht 206 gegenüber der Driftschicht 204 und N + -Source-Bereiche 212 und 214 auf. Ein Gate-Kontakt 216 ist, wie gezeigt, in einem Graben gebildet, und ist durch einen Gate-Isolator 218 isoliert. Source-Kontakte 220 und 222 sind auf den Source-Bereichen 212 bzw. 214 angeordnet und ein Drain-Kontakt 224 ist auf einer Oberfläche des Substrats 202 gegenüber der Driftschicht 204 angeordnet. Bei dieser Ausführungsform ist der Abflachungskantenabschluss 200 ein mehrstufiger negativer Abflachungskantenabschluss wie der von Fig. 3. Als Folge des negativen Abflachungskantenabschlusses 200 nähert sich eine Sperrspannung des UMOSFET 198 der Sperrspannung der idealen parallelebenen Vorrichtung an.

[0036] Fig. 17 zeigt den UMOSFET 198 mit dem negativen Abflachungskantenabschluss 200 gemäss einer anderen Ausführungsform der vorliegenden Offenbarung. Gemäss diesem Ausführungsbeispiel wird der negative Abflachungskantenabschluss 200 durch Gegendorierung mit N-Typ-Ionen der P-Basischicht 206 in einem Randbereich 226 benachbart zu dem P + -Bereich 208 und dem N + -Source-Bereich 212 gegenüber der Gate-Kontakt 216 gebildet, die die P-Leitfähigkeit der Basisschicht 206 im Randbereich 226 ausgleichen, um einen neutralen oder intrinsischen Bereich 230 mit einer gewünschten Abflachungskantenabschlusscharakteristik bereitzustellen. Die N-Typ-Ionen können beispielsweise Stickstoff (N), Phosphor (P) oder dergleichen sein. Der negative Abflachungskantenabschluss 200 wird dadurch an einer Schnittstelle des neutralen Bereichs 230 und einen Rest der Basisschicht 206 gebildet. Insbesondere, gemäss einer Ausführungsform, werden Ionen in unterschiedliche Tiefen implantiert, die stufenweise ausgehend vom Ende des Randbereichs 226 benachbart zu dem P + -Bereich 208 und dem N + -Source-Bereich 212 zunehmen und sich nach aussen fortsetzen, um die gewünschte Anzahl von Stufen und Steigung ( $\alpha$ ) für den negativen Abflachungskantenabschluss 200 bereitzustellen.

[0037] Schliesslich ist anzumerken, dass die Anzahl der Stufen des mehrstufigen negativen Abflachungskantenabschlusses 46, 84, 110, 144, 178 und 200 der verschiedenen hier beschriebenen Vorrichtungen je nach der speziellen Implementierung variieren kann. Einige beispielhafte Ausführungsformen des mehrstufigen negativen Abflachungskantenabschlusses 46, 84, 110, 144, 178 und 200 weisen zumindest 5 Stufen, mindestens 7 Stufen, mindestens 10 Stufen, mindestens 12 Stufen, mindestens 15 Stufen, mindestens 17 Stufen, mindestens 20 Stufen, eine Anzahl von Stufen in einem Bereich von und einschliesslich 5 bis 20 Stufen, eine Anzahl von Stufen in einem Bereich von und einschliesslich 10 bis 20 Stufen, eine Anzahl von Stufen in einem Bereich von und einschliesslich 15 bis 20 Stufen, und eine Reihe von Stufen in einem Bereich von und einschliesslich 10 bis 15 Stufen auf. Auch die Sperrspannungen der verschiedenen Vorrichtungen können in Abhängigkeit von der jeweiligen Implementierung variieren. Einige beispielhafte Ausführungsformen weisen eine Sperrspannung von wenigstens 10 kV, eine Sperrspannung von wenigstens 12 kV, eine Sperrspannung von wenigstens

15 kV, eine Sperrspannung von mindestens 17 kV, eine Sperrspannung von wenigstens 20 kV, ein Sperrspannung von mindestens 22 kV, eine Sperrspannung von mindestens 25 kV Sperrspannung in einem Bereich von und einschliesslich 10 kV bis 25 kV, eine Sperrspannung in einem Bereich von und einschliesslich 12 kV bis 25 kV, eine Sperrspannung in einem Bereich von und einschliesslich 15 kV bis 25 kV, eine Sperrspannung in einem Bereich von und einschliesslich 12 kV bis 20 kV, und eine Sperrspannung in einem Bereich von und einschliesslich 12 kV bis 15 kV auf.

**[0038]** Unter erneuter Bezugnahme auf Fig. 2 ist die Durchlasskennlinie des hochspannungsfesten (z.B.  $\geq 10$  kV) Thyristors 44, und damit eines Durchlasswiderstands des Thyristors 44 eine Funktion der Ladungsträgerlebensdauer in der Driftschicht 54. Jedoch ist aufgrund der hohen Sperrspannung des Thyristors 44 die Driftschicht 54 relativ dick (z.B. so dick wie 160 Mikrometer oder mehr für eine Sperrspannung von bis zu 20 kV) und hochohmig. Die Ladungsträgerlebensdauer in der Driftschicht 54 ist in der Regel relativ kurz, was zu einem anderen als einem optimalen Durchlasswiderstand des Thyristors 44 führt. Die folgende Beschreibung beschreibt eine Anzahl von Ladungsträgerlebensdauer-Verbesserungstechniken, die verwendet werden können, um einen niedrigen Durchlasswiderstand bei hoher Sperrspannung bereitzustellen.

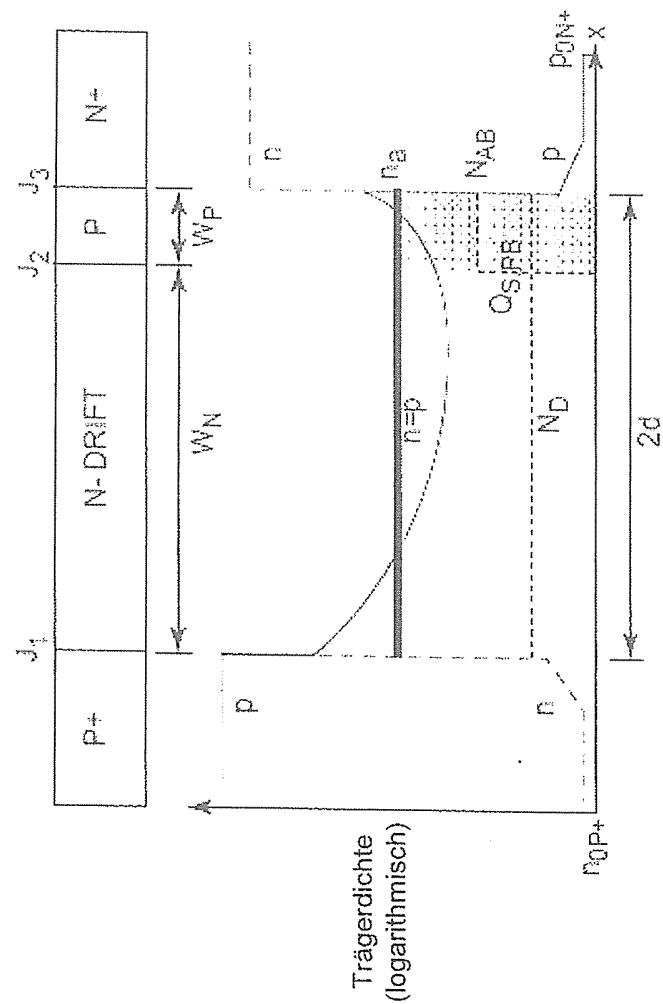

**[0039]** Vor der Beschreibung der Ladungsträgerlebensdauer-Verbesserungstechniken kann eine kurze Analyse der Durchlasskennlinie des Thyristors 44 vorteilhaft sein. Als Beispiel, um die Durchlasskennlinie zu analysieren, kann der Thyristor 44 als PIN-Gleichrichter betrachtet werden. Wie in Fig. 18 gezeigt, sind die Elektronen- und Löcherkonzentrationen innerhalb der N-Basis und der P-Basisbereiche des herkömmlichen Thyristors (PNPN) eine Kettenverteilung gemäss der Analyse für den P-i-N-Gleichrichter, der in Fig. 19 gezeigt ist. Weil sowohl Elektronen als auch Löcher für den Stromtransport unter Hochniveau-Injektionsbedingungen für den Stromtransport zu Verfügung stehen, können der Gesamtdurchlassstromfluss  $J_T$  und der spezifische Widerstand des Driftbereichs  $R_{d,SP}$ , aus der durchschnittliche Trägerdichte  $n_a$  in den Driftbereichen durch die Gleichungen (1) und (2) berechnet werden:

$$J_T = \frac{2 \cdot q \cdot n_a \cdot d}{\tau_{HL}} \text{ (A/cm}^2\text{)} \quad (1)$$

$$R_{d,SP} = \frac{2 \cdot d}{q \cdot (\mu_n + \mu_p) \cdot n_a} \text{ (}\Omega \cdot \text{cm}^2\text{)}, \quad (2)$$

wobei  $\tau_{HL}$  die Hochniveau-Trägerlebensdauer ist und  $d$  die Hälfte der Dicke der Driftschicht 54 ist. Umstellung der Gleichung (1) und dann Substituieren in Gleichung (2) gibt den spezifischen Widerstand der Driftschicht 54 in Gleichung (3) an:

$$R_{d,SP} = \frac{4 \cdot d^2}{(\mu_n + \mu_p) \cdot J_T \cdot \tau_{HL}} \text{ (}\Omega \cdot \text{cm}^2\text{)}. \quad (3)$$

**[0040]** Ein Spannungsabfall  $V^{\text{TM}}$  über die Driftschicht 54 ist dann durch die Gleichung (4) gegeben:

$$V_{\text{TM}} = J_T \cdot R_{d,SP} = \frac{4 \cdot d^2}{(\mu_n + \mu_p) \cdot \tau_{HL}} \text{ (V)}. \quad (4)$$

**[0041]** Es ist deutlich in den Gleichungen (3) und (4) dargestellt, dass sowohl der spezifische Widerstand als auch der Spannungsabfall in der Driftschicht 54 bei zunehmender Verringerung der Trägerlebensdauer, was auch durch Fig. 20 belegt wird, wo eine höhere Lebensdauer eine höhere Trägerdichte in dem Driftbereich ergibt. Somit erlaubt das Leitfähigkeitsmodulationsphänomen bei hohem Injektionsniveau die Aufrechterhaltung eines geringen Spannungsabfalls, über der Driftschicht 54, was vorteilhaft für das Erhalten eines niedrigen Durchlassspannungsabfalls bei bipolaren Dioden und Transistoren ist.

**[0042]** Die Fig. 21A bis 21D veranschaulichen ein Verfahren zum Herstellen des Thyristors 44 der Fig. 2 unter Verwendung einer Anzahl von Trägerlebens-Verbesserungstechniken, die zu dem Thyristor 44 mit einem niedrigen Durchlasswiderstand gemäss einer Ausführungsform der vorliegenden Offenbarung führen. Wie in Fig. 21A gezeigt, beginnt der Prozess mit einer epitaktischen Struktur mit dem Substrat 48, der Injektionsschicht 50, der Feldstoppschicht 52, der Driftschicht 54, der Basisschicht 56 und einer zu ätzenden Schicht 62', um die Mesa-Anode 62 zu bilden. Als Nächstes wird, wie in Fig. 21B gezeigt, die Schicht 62' geätzt, um die Mesa-Anode 62 zu bilden. Nach dem Ätzen der Schicht 62', um die Mesa-Anode 62 zu bilden, wird ein Oxidationsverfahren und ein anschliessender Oxid-Entfernungsprozess durchgeführt. Das Oxidationsverfahren ist vorzugsweise ein Trockenoxidationsverfahren, bei dem die Struktur der Fig. 21B auf eine Temperatur in einem Bereich von und einschliesslich 1200 °C bis 1450 °C für eine Dauer von 1 Stunde bis 15 Stunden erhitzt wird. Gemäss einer besonderen Ausführungsform wird das Trockenoxidationsverfahren durch Erhitzen der Struktur der Fig. 21B auf eine Temperatur von 1300 °C für 5 Stunden durchgeführt. Das Oxid auf der Oberfläche der Struktur, das aus dem Trockenoxidationsprozess resultiert, wird dann entfernt. Dieser Trockenoxidationsprozess erhöht die Ladungsträgerlebensdauer, und insbesondere die Lebensdauer der Minoritätsträger der Driftschicht 54.

**[0043]** Als Nächstes wird der negative Abflachungskantenabschluss 46 geätzt oder auf andere Weise gebildet, und die Dotierungsmittel (z.B. N +-Dotierungsmittel) in die Basisschicht 56 implantiert, um die Gate-Bereiche 58 und 60, wie in Fig. 21C dargestellt, zu bilden. Die implantierten Dotierungsmittel werden durch einen Temperprozess aktiviert. Der Temperprozess kann beispielsweise bei einer Temperatur von 1650 °C für 30 Minuten durchgeführt werden. Man beachte jedoch, dass die Tempertemperatur und Dauer verändert werden können. Insbesondere kann der Temperprozess bei einer Temperatur im Bereich von und einschliesslich 1500 °C bis 2000 °C und die Dauer 1 Minute bis 60 Minuten betragen. Vorzugsweise wird jedoch der Temperprozess bei einer Temperatur im Bereich von und einschliesslich 1600 °C bis 1800 °C mit einer Dauer von 10 bis 30 Minuten durchgeführt. Ein Opferoxidationsprozess, gefolgt von einem Oxid-Entfernungsverfahren, wird dann durchgeführt, um Schäden an der Oberfläche der Struktur der Fig. 21C von der Implantationsfläche zu entfernen. Genauer gesagt, in einer besonderen Ausführungsform, wird die Struktur der Fig. 21C auf eine Temperatur von 1200 °C für 2 Stunden erhitzt, gespült, auf eine Temperatur von 950 °C für 2 Stunden erhitzt und anschliessend wieder gespült. Es ist zu beachten, dass die Temperatur und Dauer des Erhitzens für diese Oxidationsverfahren variieren kann. Insbesondere die Opferoxidation wird bei einer Temperatur von 1150 °C bis 1450 °C mit einer Dauer von 1 Stunde bis 15 Stunden durchgeführt. Vorzugsweise wird jedoch der Opferoxidationsprozess bei einer Temperatur im Bereich von und einschliesslich 1200 °C bis 1300 °C mit einer Dauer von 1 Stunde bis 5 Stunden durchgeführt. Als Folge des Temperprozesses, gefolgt von dem Opferoxidationsprozess, wird die Trägerlebensdauer in der Driftschicht 54 weiter verbessert. Schliesslich werden die Anode, die Kathode und die Gate-Kontakte 64, 66, 68 und 70 wie in Fig. 21D dargestellt gebildet.

**[0044]** Mit Hilfe der Trägerlebensdauer-Verbesserungstechniken in dem Verfahren der Fig. 21A bis 21D weist der Thyristor 44 sowohl eine hohe Sperrspannung als auch einen geringen Durchlasswiderstand auf. Gemäss einer Ausführungsform weist der Thyristor 44 eine Sperrspannung von mindestens 10 kV und einen differentiellen Durchlasswiderstand von weniger als  $10 \text{ m}\Omega \cdot \text{cm}^2$ , bevorzugt von weniger als  $7 \text{ m}\Omega \cdot \text{cm}^2$  und besonders bevorzugt von weniger als  $5 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer Ausführungsform weist der Thyristor 44 eine Sperrspannung in einem Bereich von und einschliesslich 10 kV bis 15 kV und einen differentiellen Durchlasswiderstand von weniger als  $10 \text{ m}\Omega \cdot \text{cm}^2$ , bevorzugt von weniger als  $7 \text{ m}\Omega \cdot \text{cm}^2$  und besonders bevorzugt von weniger als  $5 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer anderen Ausführungsform weist der Thyristor 44 eine Sperrspannung von mindestens 10 kV oder im Bereich von 10 kV bis 15 kV und einen differentiellen Durchlasswiderstand im Bereich von 1 bis  $10 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 3 bis  $10 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 1 bis  $7 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 3 bis  $7 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 1 bis  $5 \text{ m}\Omega \cdot \text{cm}^2$  oder in dem Bereich von 3 bis  $5 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer anderen Ausführungsform weist der Thyristor 44 eine Sperrspannung von mindestens 15 kV und einen differentiellen Durchlasswiderstand von weniger als  $15 \text{ m}\Omega \cdot \text{cm}^2$ , bevorzugt von weniger als  $\text{m}\Omega \cdot \text{cm}^2$  und besonders bevorzugt von weniger als  $7 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer anderen Ausführungsform weist der Thyristor 44 eine Sperrspannung in einem Bereich von und einschliesslich 15 kV bis 20 kV und einen differentiellen Durchlasswiderstand von weniger als  $15 \text{ m}\Omega \cdot \text{cm}^2$ , bevorzugt von weniger als  $\text{m}\Omega \cdot \text{cm}^2$  und besonders bevorzugt von weniger als  $7 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer anderen Ausführungsform weist der Thyristor 44 eine Sperrspannung von mindestens 15 kV oder im Bereich von 15 kV bis 20 kV und einen differentiellen Durchlasswiderstand im Bereich von 1 bis  $15 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 3 bis  $15 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 1 bis  $10 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 3 bis  $10 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 1 bis  $7 \text{ m}\Omega \cdot \text{cm}^2$  oder in dem Bereich von 3 bis  $7 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer anderen Ausführungsform weist der Thyristor 44 eine Sperrspannung von mindestens 20 kV und einen differentiellen Durchlasswiderstand von weniger als  $20 \text{ m}\Omega \cdot \text{cm}^2$ , bevorzugt weniger als  $15 \text{ m}\Omega \cdot \text{cm}^2$  und besonders bevorzugt von weniger als  $10 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer anderen Ausführungsform weist der Thyristor 44 eine Sperrspannung in einem Bereich von und einschliesslich 20 kV bis 25 kV und einen differentiellen Durchlasswiderstand von weniger als  $20 \text{ m}\Omega \cdot \text{cm}^2$ , bevorzugt von weniger als  $15 \text{ m}\Omega \cdot \text{cm}^2$  und besonders bevorzugt von weniger als  $10 \text{ m}\Omega \cdot \text{cm}^2$  auf. Gemäss einer anderen Ausführungsform weist der Thyristor 44 eine Sperrspannung von mindestens 20 kV oder im Bereich von 20 kV bis 25 kV und einen differentiellen Durchlasswiderstand im Bereich von 1 bis  $20 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 3 bis  $20 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 7 bis  $20 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 1 bis  $15 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 3 bis  $15 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 7 bis  $20 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 1 bis  $10 \text{ m}\Omega \cdot \text{cm}^2$ , im Bereich von 3 bis  $10 \text{ m}\Omega \cdot \text{cm}^2$  oder im Bereich von 7 bis  $10 \text{ m}\Omega \cdot \text{cm}^2$  auf.

**[0045]** Mit Hilfe der Trägerlebensdauer-Verbesserungstechniken kann die Driftschicht 54 des Thyristors 44 dicker sein, und somit eine höhere Sperrspannung bereitstellen, während ein geeigneter Durchlasswiderstand beihalten werden kann. Zum Beispiel kann die Driftschicht 54 eine Dicke von mehr als 80 µm, eine Dicke von mehr als 100 µm, eine Dicke von mehr als 120 µm, eine Dicke von mehr als 140 µm, eine Dicke von mehr als 160 µm, eine Dicke im Bereich von und einschliesslich 80 µm bis 200 µm, eine Dicke im Bereich von und einschliesslich 80 µm bis 160 µm, eine Dicke im Bereich von und einschliesslich 100 µm bis 200 µm, eine Dicke im Bereich von und einschliesslich 100 µm bis 160 µm, eine Dicke in dem Bereich von und einschliesslich 140 µm bis 200 µm, oder eine Dicke im Bereich von und einschliesslich 140 µm bis 160 µm, oder eine Dicke im Bereich von einschliesslich 160 µm bis 200 µm aufweisen. Jedoch können auch andere Dicken, abhängig von der gewünschten Sperrspannung und der speziellen Ausführung, verwendet werden.

**[0046]** Die Fig. 22A bis 22C veranschaulichen Ergebnisse von Ladungsträgerlebensdauer-Messungen für eine Reihe von beispielhaften Thyristoren 44, hergestellt nach dem Verfahren der Fig. 21A bis 21D. Insbesondere zeigt Fig. 22A eine Durchschnittsträgerlebensdauer-Messung, eine mediane Trägerlebensdauermessung, eine minimale Trägerlebensdauermessung, eine maximale Ladungsträgerlebensdauer und eine Abweichung von der Trägerlebensdauermassnahmen für eine Vielzahl von Strukturen, wie der von Fig. 21A. In diesem Beispiel ist die Driftschicht 54 eine 90 µm dicke p-Typ-SiC-Material-Schicht und hat ein Dotierungsniveau kleiner  $2 \times 10^{14} \text{ cm}^{-3}$ , Fig. 22B zeigt ähnliche Trägerlebensdauer-Messungen

nach dem Ätzen der Mesa-Anode 62 und der Durchführung einer Trockenoxidation bei einer Temperatur von 1300 °C für 5 Stunden. Wie gezeigt, ist nach der Durchführung des Trockenoxidationsverfahrens die Ladungsträgerlebensdauer deutlich erhöht. Schliesslich zeigt Fig. 22C die Trägerlebensdauer-Messungen nach dem Ätzen des negativen Abflachungskantenabschlusses 46, Implantieren der Gate-Bereiche 58 und 60 und Durchführen des Opferoxidationsprozesses. In diesem speziellen Beispiel weist der Opferoxidationsprozess die Schritte Erhitzen auf eine Temperatur von 1200 °C für 2 Stunden, Spülen, Erhitzen auf eine Temperatur von 950 °C für 2 Stunden und dann nochmals Spülen auf. Wie dargestellt, erhöht das Implantattempern, gefolgt von dem Opferoxidationsprozess, weiter die Ladungsträgerlebensdauer in der Driftschicht 54.

**[0047]** Fig. 23 zeigt graphisch den Durchlasswiderstand eines Beispiels des Thyristors 44 mit einer Sperrspannung von wenigstens 10 kV, der mit den oben beschriebenen Trägerlebens-Verbesserungstechniken hergestellt wurde. Wie dargestellt, ist in diesem Beispiel der differentielle Durchlasswiderstand kleiner als  $5 \text{ m}\Omega \text{ cm}^2$  bei einer Stromdichte von  $100 \text{ A/cm}^2$  (z.B. Hohniveau-Injektionszustand) durch verbesserte Ladungsträgerlebensdauer. Insbesondere bei Gehäusetemperaturen von weniger als 100 °C beträgt der differentielle Durchlasswiderstand etwa  $4 \text{ m}\Omega \cdot \text{cm}^2$ .

**[0048]** Während die Trägerlebensdauer-Verbesserungstechniken zuvor in Bezug auf den Thyristor 44 beschrieben wurden, können die Trägerlebensdauer-Verbesserungstechniken für jede Halbleitervorrichtung verwendet werden, insbesondere für jede Art von SiC-Halbleitervorrichtung, das sind bipolare (d.h. Verwendung von sowohl Elektronen als auch Löchern zur Leitung). Beispielsweise können zusätzlich zu den Thyristor 44 der Fig. 2 und 6 die Trägerlebensdauer-Verbesserungstechniken bei der Herstellung des BJT 82 der Fig. 8 und 9, des IGBTs 108 und 142 der Fig. 10, 11, 12 und 13 und der PIN-Diode 176 der Fig. 14 und 15 verwendet werden, um ähnliche Durchlasswiderstandsverbesserungen zu erreichen.

**[0049]** Insbesondere bei der Herstellung des BJT 82 kann das oben beschriebene Oxidationsverfahren nach dem Ätzen der Mesa-Anode 62 des Thyristors 44 nach dem Ätzen des Mesa-Emitters durchgeführt werden. Ebenso können das Implantattempern und der Opferoxidationsprozess nach dem Ätzen oder anderweitiges Formen des negativen Abflachungskantenabschlusses 84 und das Implantieren der Basiszone 92 durchgeführt werden. Auf diese Weise wird die Trägerlebensdauer in der Driftschicht 88 verbessert, was wiederum den Durchlasswiderstand des BJTs 82 herabsetzt.

**[0050]** In ähnlicher Weise kann bei der Herstellung des IG BT 108 das Oxidationsverfahren wie oben beschrieben nach dem Ätzen der Mesa-Anode 62 des Thyristors 44 nach dem Ätzen des Gate-Grabens durchgeführt werden. In ähnlicher Weise kann das Implantattempern und der Opferoxidationsprozess nach dem Ätzen oder anderweitiges Formen des negativen Abflachungskantenabschlusses 110 und Implantieren der P+-Bereiche 118 und 120 und der Emitter-Bereiche 122 und 124 durchgeführt werden. Auf diese Weise wird die Trägerlebensdauer in der Driftschicht 114 verbessert, was wiederum den Durchlasswiderstand des BJTs 82 herabsetzt. Ebenso können die Trägerlebensdauertechniken für den IGBT 142 der Fig. 12 und 13 verwendet werden.

**[0051]** Schliesslich kann bei der Herstellung der PIN-Diode 176 der Fig. 14 und 15 das oben beschriebene Oxidationsverfahren nach dem Ätzen der Mesa-Anode 62 des Thyristors 44 nach dem Ätzen der p-Schicht 184 und der P++-Schicht 186 durchgeführt werden. Ebenso können das Implantattempern und der Opferoxidationsprozess nach der Implantation der P-Typ-Schicht 184 durchgeführt werden, um den negativen Abflachungskantenabschluss 178 in der Ausführungsform von Fig. 15 zu bilden. Auf diese Weise ist die Trägerlebensdauer in der N-Driftschicht 182 verbessert, was wiederum den Durchlasswiderstand der PIN-Diode 176 herabsetzt.

**[0052]** Der Fachmann wird Verbesserungen und Modifikationen der bevorzugten Ausführungsformen der vorliegenden Offenbarung erkennen. Alle derartigen Verbesserungen und Modifikationen liegen im Schutzmfang der hier offenbarten Konzepte und der folgenden Ansprüche.

## **Patentansprüche**

1. Siliziumkarbid, kurz SiC-Halbleitervorrichtung, welche sich der idealen Sperrspannung einer idealen parallelebenden Vorrichtung annähert, indem die Halbleitervorrichtung einen mehrstufigen negativen Abflachungskantenabschluss, der sich einer glatten Steigung annähernd ausgebildet ist und eine Sperrspannung von wenigstens 10 Kilovolt und einen Durchlasswiderstand von weniger als 10 Milliohm-Quadratzentimeter aufweist.

2. SiC-Halbleitervorrichtung nach Anspruch 1, wobei der Durchlasswiderstand ein differentieller Durchlasswiderstand ist.

3. SiC-Halbleitervorrichtung nach Anspruch 2, wobei der differentielle Durchlasswiderstand kleiner als  $5 \text{ m}\Omega \cdot \text{cm}^2$  ist.

4. SiC-Halbleitervorrichtung nach Anspruch 2, wobei die Sperrspannung in einem Bereich von und einschliesslich 10 kV bis 15 kV liegt und der differentielle Durchlasswiderstand kleiner als  $5 \text{ m m}\Omega \cdot \text{cm}^2$  ist.

5. SiC-Halbleitervorrichtung nach Anspruch 1 oder 2, wobei der mehrstufige Abflachungskantenabschluss wenigstens fünf Stufen und besonders bevorzugt wenigstens 15 Stufen aufweist.

6. SiC-Halbleitervorrichtung nach Anspruch 1 oder 2, wobei die Sperrspannung der SiC-Halbleitervorrichtung in einem Bereich von und einschliesslich 10 kV bis 25 kV liegt.

7. SiC-Halbleitervorrichtung nach Anspruch 1 oder 2, wobei ein Neigungswinkel des mehrstufigen negativen Abflachungskantenabschlusses kleiner oder gleich 15 Grad ist.

8. SiC-Halbleitervorrichtung nach Anspruch 1, wobei die SiC-Halbleitervorrichtung ein Thyristor ist mit:

einem Substrat eines ersten Leitfähigkeitstyps;

einer Driftschicht eines zweiten Leitfähigkeitstyps auf einer Oberfläche des Substrats;

einer Basisschicht des ersten Leitfähigkeitstyps auf einer Oberfläche der Driftschicht gegenüber dem Substrat;

einer Mesa-Anode des zweiten Leitfähigkeitstyps auf einer Oberfläche der Basisschicht gegenüber der Driftschicht;

und

einem Gate-Bereich, gebildet in der Oberfläche der Basisschicht;

wobei der mehrstufige negative Abflachungskantenabschluss in der Basisschicht benachbart zu dem Gate-Bereich gegenüber der Mesa-Anode gebildet ist.

9. SiC-Halbleitervorrichtung nach Anspruch 1, wobei die SiC-Halbleitervorrichtung ein Bipolartransistor ist mit:

einem Substrat eines ersten Leitfähigkeitstyps;

einer Driftschicht des ersten Leitfähigkeitstyps auf einer Oberfläche des Substrats;

einer Basisschicht eines zweiten Leitfähigkeitstyps, gebildet auf einer Oberfläche der Driftschicht gegenüber dem Substrat;

einem Basisbereich des zweiten Leitfähigkeitstyps, gebildet in einer Oberfläche der Basisschicht gegenüber der Driftschicht; und

einem Mesa-Emitter auf der Oberfläche der Basisschicht gegenüber der Driftschicht und benachbart zu dem Basisbereich;

wobei der mehrstufige Abflachungskantenabschluss in der Basisschicht benachbart zu dem Basisbereich gegenüber dem Mesa-Emitter ausgebildet ist.

10. SiC-Halbleitervorrichtung nach Anspruch 1, wobei die SiC-Halbleitervorrichtung ein Bipolartransistor ist mit:

einem Substrat eines ersten Leitfähigkeitstyps;

einer Driftschicht eines zweiten Leitfähigkeitstyps auf einer Oberfläche des Substrats;

einer Basisschicht des ersten Leitfähigkeitstyps auf einer Oberfläche der Driftschicht gegenüber dem Substrat;

einer Emitter-Region des zweiten Leitfähigkeitstyps auf einer Oberfläche der Basisschicht gegenüber der Driftschicht;

und

einem Gate-Graben, gebildet in einer Oberfläche des BJT benachbart zu der Emitter-Region und sich in die Driftschicht erstreckend;

wobei der mehrstufige Abflachungskantenabschluss in der Basisschicht benachbart zu der Emitter-Region gegenüber dem Gate-Graben ausgebildet ist.

11. SiC-Halbleitervorrichtung nach Anspruch 1, wobei die SiC-Halbleitervorrichtung eine PIN-Diode ist mit:

einem Substrat eines ersten Leitfähigkeitstyps;

einer Driftschicht des ersten Leitfähigkeitstyps auf einer Oberfläche des Substrats;

einer Halbleiterschicht eines zweiten Leitfähigkeitstyps auf einer Oberfläche der Driftschicht gegenüber dem Substrat;

einer Mesa-Anode auf einer Oberfläche der Halbleiterschicht des zweiten Leitfähigkeitstyps entgegengesetzt zu der Driftschicht;

einem Anodenkontakt auf einer Oberfläche der Mesa-Anode gegenüber der Driftschicht; und

einem Kathodenkontakt auf einer Oberfläche des Substrats gegenüber der Driftschicht;

wobei der mehrstufige Abflachungskantenabschluss in der Halbleiterschicht des zweiten Leitfähigkeitstyps benachbart zu der Mesa-Anode ausgebildet ist.

12. SiC-Halbleitervorrichtung nach Anspruch 1, mit einer Sperrspannung von wenigstens 15 Kilovolt und einem Durchlasswiderstand von weniger als 15 Milliohm-Quadratzentimeter.

13. SiC-Halbleitervorrichtung nach Anspruch 12, wobei der Durchlasswiderstand ein differentieller Durchlasswiderstand ist.

14. SiC-Halbleitervorrichtung nach Anspruch 13, wobei der differentielle Durchlasswiderstand kleiner als  $7 \text{ m}\Omega \cdot \text{cm}^2$  ist und die Sperrspannung in einem Bereich von und einschliesslich 15 kV bis 20 kV liegt.

15. SiC-Halbleitervorrichtung nach Anspruch 1, mit einer Sperrspannung von wenigstens 20 Kilovolt und einem Durchlasswiderstand von weniger als 10 Milliohm-Quadratzentimeter.

16. SiC-Halbleitervorrichtung nach Anspruch 15, wobei der Durchlasswiderstand ein differentieller Durchlasswiderstand ist.

17. SiC-Halbleitervorrichtung nach Anspruch 16, wobei der differentielle Durchlasswiderstand kleiner als  $10 \text{ m}\Omega \cdot \text{cm}^2$  ist und die Sperrspannung in einem Bereich von und einschliesslich 20 kV bis 25 kV liegt.

Fig. 1

Stand der Technik

Fig. 2

Fig. 3

Fig. 4

Fig. 5

四

Fig. 7

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 13

Fig. 14

Fig. 15

Fig. 16

Fig. 17

Fig. 18

Fig. 19

Fig. 20

Fig. 21A

Fig. 21B

Fig. 21C

Fig. 21D

**CH 707 901 B1**

Fig. 22A

Fig. 22B

Fig. 22C

Fig. 23