(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294577

(P2005-294577A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 21/3205

F 1

H01L 21/88

H01L 21/88

テーマコード(参考)

5 F O 3 3

J

T

審査請求 未請求 請求項の数 18 O L (全 24 頁)

(21) 出願番号

特願2004-108304 (P2004-108304)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人

N E C エレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人

100110928

弁理士 速水 進治

(72) 発明者

川野 連也

神奈川県川崎市中原区下沼部1753番地

N E C エレクトロニクス株式会社内F ターム(参考) 5F033 HH07 HH08 HH11 HH32 HH33

JJ04 JJ07 JJ08 JJ11 JJ19

KK01 KK07 KK11 MM01 MM12

MM13 MM30 PP06 PP15 PP27

PP28 QQ07 QQ09 QQ10 QQ11

QQ25 QQ37 QQ47 QQ48 RR01

RR04 RR06 RR09 RR22 RR24

SS15 SS21 TT02 TT07 VV07

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

**【課題】** 電極としての性能および製造安定性に優れた貫通電極を有する半導体装置を提供する。

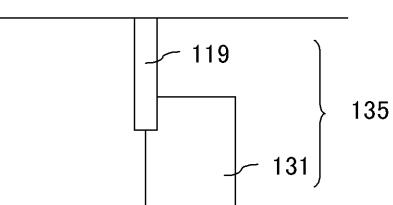

**【解決手段】** 半導体装置100に導電性の小径プラグ119と導電性の大径プラグ131とからなる貫通電極135を設ける。小径プラグ119の断面積を、それぞれ接続プラグ123の断面積および径よりも大きく大径プラグ131の断面積および径よりも小さくする。また、シリコン基板101から小径プラグ119が突出した突出部141を大径プラグ131の上面に貫入させる。また、小径プラグ119の上面を第一配線121と接続させる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体基板と、

前記半導体基板の素子形成面に設けられた絶縁層と、

前記半導体基板を貫通し、前記絶縁層の内部に設けられた導電部材と接続する貫通電極と、

を有し、

前記貫通電極は、

前記導電部材と接続する第一の導電プラグと、

前記半導体基板に設けられ、前記第一の導電プラグの断面積よりも大きい断面積を有し

、前記第一の導電プラグの一部を内包する第二の導電プラグと、

を有することを特徴とする半導体装置。 10

**【請求項 2】**

半導体基板と、

前記半導体基板の素子形成面に設けられたトランジスタ形成層と、

前記トランジスタ形成層の上部に設けられた配線層と、

前記配線層の上部に設けられた上部配線層と、

前記トランジスタ形成層および前記半導体基板を貫通する貫通電極と、

を有し、

前記貫通電極は、

前記トランジスタ形成層に設けられ前記配線層中に形成された配線に接続する第一の導電プラグと、

前記半導体基板に設けられ、前記第一の導電プラグの断面積よりも大きい断面積を有し

、前記第一の導電プラグと接続する第二の導電プラグと、

を有することを特徴とする半導体装置。 20

**【請求項 3】**

請求項 2 に記載の半導体装置において、前記第一の導電プラグの一部が前記第二の導電

プラグに内包されるように構成されたことを特徴とする半導体装置。

**【請求項 4】**

請求項 1 乃至 3 いずれかに記載の半導体装置において、複数の前記第一の導電プラグが

、一つの前記第二の導電プラグと電気的に接続されるように構成されたことを特徴とする

半導体装置。 30

**【請求項 5】**

請求項 1 乃至 4 いずれかに記載の半導体装置において、前記第二の導電プラグが前記半

導体基板の前記裏面から前記半導体基板の前記素子形成面の近傍にわたって形成されてい

ることを特徴とする半導体装置。

**【請求項 6】**

請求項 1 乃至 5 いずれかに記載の半導体装置において、前記第一の導電プラグの一部が

前記第二の導電プラグに貫入していることを特徴とする半導体装置。

**【請求項 7】**

請求項 1 乃至 6 いずれかに記載の半導体装置において、前記第二の導電プラグと前記半

導体基板とが絶縁膜を介して接していることを特徴とする半導体装置。 40

**【請求項 8】**

請求項 1 乃至 7 いずれかに記載の半導体装置において、前記第二の導電プラグが前記半

導体基板の前記裏面から突出していることを特徴とする半導体装置。

**【請求項 9】**

請求項 1 乃至 8 いずれかに記載の半導体装置において、前記第二の導電プラグの側面外

周に環筒状絶縁体が配設されたことを特徴とする半導体装置。

**【請求項 10】**

請求項 1 乃至 9 いずれかに記載の半導体装置において、前記半導体基板の前記素子形成 50

面における前記貫通電極の断面積が、前記半導体基板の前記裏面における前記貫通電極の断面積よりも小さいことを特徴とする半導体装置。

【請求項 1 1】

半導体基板の素子形成面の側に第一の孔を形成する工程と、

前記第一の孔の内壁に、絶縁材料からなるバリア膜を形成する工程と、

前記第一の孔の内部を埋め込むように第一の金属膜を埋設する工程と、

前記第一の孔の外部に形成された前記第一の金属膜を除去し、前記第一の孔の内部に第一の導電プラグを形成する工程と、

裏面の側から前記半導体基板を選択的に除去して第二の孔を形成し、前記第二の孔の内部に前記第一の導電プラグの一部を露出させる工程と、

露出した前記バリア膜の少なくとも一部を除去し、前記第一の金属膜を露出させる工程と、

第一の金属膜を露出させる前記工程の後、前記第二の孔を埋めるように第二の金属膜を成長させて、前記第一の導電プラグの一部を内包する第二の導電プラグを形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項 1 2】

請求項 1 1 に記載の半導体装置の製造方法において、

第一の孔を形成する前記工程の前に、前記素子形成面の側から前記半導体基板を選択的に除去して環筒状の孔を形成し、前記孔の内部に絶縁体を埋設して環筒状絶縁体を形成する工程を含み、

第一の孔を形成する前記工程は、前記半導体基板の前記環筒状絶縁体の内側の領域の一部を除去して前記第一の孔を形成する工程を含み、

第二の孔を形成する前記工程は、前記半導体基板の前記環筒状絶縁体の内側の領域の少なくとも一部を除去して前記第二の孔を形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項 1 3】

請求項 1 1 または 1 2 に記載の半導体装置の製造方法において、第一の孔を形成する前記工程は、前記半導体基板の前記素子形成面の側に絶縁膜を形成した後、前記絶縁膜および前記半導体基板を選択的に除去して前記第一の孔を形成する工程を含むことを特徴とする半導体装置の製造方法。

【請求項 1 4】

半導体基板の素子形成面の側から前記半導体基板を選択的に除去して孔を形成し、前記孔の内部に絶縁体を埋設し絶縁プラグを形成する工程と、

前記半導体基板の前記素子形成面の側に、前記絶縁プラグの一部が選択的に除去された第一の孔を形成する工程と、

前記第一の孔の内部を埋め込むように第一の金属膜を埋設する工程と、

前記第一の孔の外部に形成された前記第一の金属膜を除去し、前記第一の孔の内部に第一の導電プラグを形成する工程と、

裏面の側から前記半導体基板を選択的に除去する工程と、

半導体基板を除去する前記工程の後、前記絶縁プラグを選択的に除去して第二の孔を形成し、前記第二の孔の内部に前記第一の導電プラグの一部を露出させる工程と、

露出した前記第一の導電プラグの少なくとも一部を除去し、前記第一の金属膜を露出させる工程と、

第一の金属膜を露出させる前記工程の後、前記第二の孔を埋めるように第二の金属膜を成長させて、前記第一の導電プラグの一部を内包する第二の導電プラグを形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項 1 5】

請求項 1 4 に記載の半導体装置の製造方法において、第一の孔を形成する前記工程は、

前記半導体基板の前記素子形成面の側に絶縁膜を形成した後、前記絶縁膜および前記絶縁プラグを選択的に除去して前記第一の孔を形成する工程を含むことを特徴とする半導体装置の製造方法。

**【請求項 16】**

請求項 11乃至 15 いずれかに記載の半導体装置の製造方法において、前記第二の孔は、前記第一の孔よりも断面積が大きいことを特徴とする半導体装置の製造方法。

**【請求項 17】**

請求項 11乃至 16 いずれかに記載の半導体装置の製造方法において、

第一の導電プラグを形成する前記工程の後、前記素子形成面の上部に、前記第一の導電プラグに接続する配線を有する配線層を形成する工程を含むことを特徴とする半導体装置の製造方法。 10

**【請求項 18】**

請求項 11乃至 17 いずれかに記載の半導体装置の製造方法において、

第一の孔を形成する前記工程の前に、前記半導体基板の前記素子形成面の上部に設けられた絶縁層を設ける工程を有し、

第一の導電プラグを形成する前記工程は、前記絶縁層の内部に、前記第一の導電プラグと同時にトランジスタ素子へ接続する接続プラグを形成する工程を含むことを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

本発明は、半導体装置およびその製造方法に関する。

**【背景技術】**

**【0002】**

近年、半導体装置の軽薄短小化と高性能化が要求されており、マルチチップパッケージなどの半導体装置において、配線の高密度化、論理素子の微細化およびメモリの大容量化が進められている。

**【0003】**

こうした要請に対応する一つの手段として、半導体基板に貫通電極を設け、配線の高密度化等を図ることが試みられている。従来の貫通電極としては、たとえば特許文献 1 に記載されたものがある。同文献には、半導体素子基板を貫通する貫通孔内に中間絶縁層が周設され、その内側に導電層が充填された構成の貫通電極を有する半導体装置が開示されている。この構成を用いると、複数の半導体素子基板を高密度で三次元的に積層することができるとされている。

**【0004】**

また、技術分野は異なるが、半導体基板と金属膜を同時に除去する技術として、非特許文献 1 に記載されたものがある。非特許文献 1 には、電極形成後に裏面研削する工程を含む半導体基板が記載されているが、これについては後述する。

**【特許文献 1】特開 2000-311982 号公報**

30

**【非特許文献 1】Masataka Hoshino 他 5 名、「Wafer Process and Issue of Through Electrode in Si wafer Using Cu Damascene for Three Dimensional Chip Stacking」、2002 年、Proceedings of the International Interconnect Technology Conference p. 75 - 77**

40

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

ところが、上記特許文献 1 に記載の構成では、半導体素子基板を太い貫通電極が貫通し

50

ているため、貫通電極を形成した領域には、配線等を設けることができない構成となっていた。このため、配線等の集積度が低下してしまい、配線の高密度化の点でさらに改善の余地があった。また、貫通電極が素子形成後に作製されるため、貫通電極の形成時に素子の信頼性を低下させる懸念があった。

#### 【0006】

本発明は、上記事情に鑑みなされたものであり、その目的は、電極としての性能および製造安定性に優れた貫通電極を有する半導体装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0007】

本発明によれば、半導体基板と、前記半導体基板の素子形成面に設けられた絶縁層と、前記半導体基板を貫通し、前記絶縁層の内部に設けられた導電部材と接続する貫通電極と、を有し、前記貫通電極は、前記導電部材と接続する第一の導電プラグと、前記半導体基板に設けられ、前記第一の導電プラグの断面積よりも大きい断面積を有し、前記第一の導電プラグの一部を内包する第二の導電プラグと、を有することを特徴とする半導体装置が提供される。10

#### 【0008】

本明細書において、素子形成面は、半導体素子が形成される半導体基板の面のことである。また、第二の導電プラグは半導体基板に設けられるが、その一部が、素子形成面上に設けられた絶縁膜中に存在していても良い。

#### 【0009】

本発明の半導体装置では、第一の導電プラグの一部が第二の導電プラグに内包されている。このため、アンカー効果により、これらのプラグの密着性にすぐれた構成となっている。また、これらのプラグ間のコンタクト抵抗が低減される構成となっている。また、素子形成面側に断面積の小さい第一の導電プラグが配設されているため、貫通電極近傍の配線の集積度を向上させることができる。このため、小型化に適した構成となっている。20

#### 【0010】

本発明によれば、半導体基板と前記半導体基板の素子形成面に設けられたトランジスタ形成層と、前記トランジスタ形成層の上部に設けられた配線層と、前記配線層の上部に設けられた上部配線層と、前記トランジスタ形成層および前記半導体基板を貫通する貫通電極と、を有し、前記貫通電極は、前記トランジスタ形成層に設けられ前記配線層中に形成された配線に接続する第一の導電プラグと、前記半導体基板に設けられ、前記第一の導電プラグの断面積よりも大きい断面積を有し、前記第一の導電プラグと接続する第二の導電プラグと、を有することを特徴とする半導体装置が提供される。30

#### 【0011】

本発明の半導体装置では、上部絶縁層に被覆された配線層に第一の導電プラグが接続されている。また、第一の導電プラグの断面積が第二の導電プラグの断面積よりも小さい構成となっている。このため、当該配線層の上層の配線や素子の集積度を向上させることができる。よって、本発明の半導体装置は、小型化に適した構成となっている。なお、上記半導体装置において、第一の導電プラグはトランジスタ形成層に設けられるが、その一部が基板中に存在していてもよい。また、第二の導電プラグは半導体基板に設けられるが、その一部が、素子形成面上に設けられた絶縁膜中に存在していても良い。40

#### 【0012】

本発明の半導体装置において、前記上部配線層が前記配線層に接続する構成とすることができます。本発明の半導体装置は、上部配線層が配線層を介して貫通電極に接続する構成の場合にも、配線層に設けられた配線および上部配線層に設けられた上部配線の集積度を向上させることができる。

#### 【0013】

本発明の半導体装置において、前記第一の導電プラグが前記第二の導電プラグに内包されるように構成されてもよい。こうすることにより、アンカー効果を確実に得ることができる。このため、これらのプラグの密着性を向上させることができる。また、これらのブ50

ラグ間のコンタクト抵抗が低減される構成とすることができる。

【0014】

本発明の半導体装置において、複数の第一の導電プラグの一部が、一つの前記第二の導電プラグに内包されるように構成されてもよい。こうすることにより、前記アンカー効果をさらに確実に得ることができる。このため、これらのプラグの密着性をさらに向上させることができる。また、これらのプラグ間のコンタクト抵抗がさらに低減される構成とすることができる。

【0015】

本発明の半導体装置において、前記第二の導電プラグが前記半導体基板の前記裏面から前記半導体基板の前記素子形成面の近傍にわたって形成されていてもよい。また、本発明の半導体装置において、第二の導電プラグは、半導体基板の素子形成面よりも下方に位置することができる。こうすることにより、半導体基板上の素子や配線の集積度をさらに向上させることができる。

【0016】

本発明の半導体装置において、前記第一の導電プラグの一部が前記第二の導電プラグに貫入している構成とすることができます。こうすることにより、両プラグの密着性をさらに確実に向上させることができます。

【0017】

本発明の半導体装置において、前記第二の導電プラグと前記半導体基板とが絶縁膜を介して接している構成とすることができます。こうすることにより、製造容易性にすぐれた構成とすることができます。また、寄生容量を低下させることができます。たとえば、本発明において、前記絶縁膜を電着絶縁膜とすることができます。

【0018】

本発明の半導体装置において、前記第二の導電プラグが前記半導体基板の前記裏面から突出している構成とすることができます。こうすることにより、さらに製造安定性にすぐれた構成とすることができます。

【0019】

本発明の半導体装置において、前記第二の導電プラグの側面外周に環筒状絶縁体が配設された構成とすることができます。こうすることにより、寄生容量を確実に低減することができます。

【0020】

本発明の半導体装置において、前記半導体基板の前記素子形成面における前記貫通電極の断面積が、前記半導体基板の前記裏面における前記貫通電極の断面積よりも小さい構成とすることができます。こうすることにより、素子形成面の上部に形成された配線の集積度をさらに確実に高めることができます。

【0021】

本発明によれば、半導体基板の素子形成面の側に第一の孔を形成する工程と、前記第一の孔の内壁に、絶縁材料からなるバリア膜を形成する工程と、前記第一の孔の内部を埋め込むように第一の金属膜を埋設する工程と、前記第一の孔の外部に形成された前記第一の金属膜を除去し、前記第一の孔の内部に第一の導電プラグを形成する工程と、裏面の側から前記半導体基板を選択的に除去して第二の孔を形成し、前記第二の孔の内部に前記第一の導電プラグの一部を露出させる工程と、露出した前記バリア膜の少なくとも一部を除去し、前記第一の金属膜を露出させる工程と、第一の金属膜を露出させる前記工程の後、前記第二の孔を埋めるように第二の金属膜を成長させて、前記第一の導電プラグの一部を内包する第二の導電プラグを形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【0022】

この方法によれば、第一の導電プラグと第二の導電プラグとの密着性にすぐれた貫通電極を有する半導体装置を簡便なプロセスで安定的に製造することができます。

【0023】

10

20

30

40

50

なお、本発明において、第一の導電プラグは、第一の金属膜とバリア膜を含む。また、本発明において、第一の金属膜がバリアメタル膜を含んでもよい。

#### 【0024】

本発明の半導体装置の製造方法において、第一の孔を形成する前記工程の前に、前記素子形成面の側から前記半導体基板を選択的に除去して環筒状の孔を形成し、前記孔の内部に絶縁体を埋設して環筒状絶縁体を形成する工程を含み、第一の孔を形成する前記工程は、前記半導体基板の前記環筒状絶縁体の内側の領域の一部を除去して前記第一の孔を形成する工程を含み、第二の孔を形成する前記工程は、前記半導体基板の前記環筒状絶縁体の内側の領域の少なくとも一部を除去して前記第二の孔を形成する工程を含んでもよい。こうすることにより、寄生容量の発生が抑制された半導体装置を確実に得ることができる。

10

#### 【0025】

本発明の半導体装置の製造方法において、第一の孔を形成する前記工程は、前記半導体基板の前記素子形成面の側に絶縁膜を形成した後、前記絶縁膜および前記半導体基板を選択的に除去して前記第一の孔を形成する工程を含んでもよい。こうすることにより、第一の導電プラグが絶縁膜の上部の配線に接続する構成の半導体装置を安定的に得ることができる。

#### 【0026】

本発明によれば、半導体基板の素子形成面の側から前記半導体基板を選択的に除去して孔を形成し、前記孔の内部に絶縁体を埋設して絶縁プラグを形成する工程と、前記半導体基板の前記素子形成面の側に、前記絶縁プラグの一部が選択的に除去された第一の孔を形成する工程と、前記第一の孔の内部を埋め込むように第一の金属膜を埋設する工程と、前記第一の孔の外部に形成された前記第一の金属膜を除去し、前記第一の孔の内部に第一の導電プラグを形成する工程と、裏面の側から前記半導体基板を選択的に除去する工程と、半導体基板を除去する前記工程の後、前記絶縁プラグを選択的に除去して第二の孔を形成し、前記第二の孔の内部に前記第一の導電プラグの一部を露出させる工程と、露出した前記第一の導電プラグの少なくとも一部を除去し、前記第一の金属膜を露出させる工程と、第一の金属膜を露出させる前記工程の後、前記第二の孔を埋めるように第二の金属膜を成長させて、前記第一の導電プラグの一部を内包する第二の導電プラグを形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

20

30

#### 【0027】

この方法によれば、第一の導電プラグと第二の導電プラグとの密着性にすぐれた貫通電極を有する半導体装置をさらに安定的に製造することができる。

#### 【0028】

本発明の半導体装置の製造方法において、第一の孔を形成する前記工程は、前記半導体基板の前記素子形成面の側に絶縁膜を形成した後、前記絶縁膜および絶縁プラグを選択的に除去して前記第一の孔を形成する工程を含むことができる。こうすることにより、第一の導電プラグが絶縁膜の上部の配線に接続する構成の半導体装置を安定的に得ることができる。

#### 【0029】

本発明の半導体装置の製造方法において、第二の孔を形成する前記工程は、前記第一の孔よりも断面積が大きい孔を形成する工程を含んでもよい。こうすることにより、第一の導電プラグの一部を第二の導電プラグにさらに確実に内包させることができる。

40

#### 【0030】

本発明の半導体装置の製造方法において、第一の導電プラグを形成する前記工程の後、前記素子形成面の上部に、前記第一の導電プラグに接続する配線を有する配線層を形成する工程を含んでもよい。こうすることにより、第一の導電プラグに接続する配線と同層の配線の集積度を高めることができる。このため、配線の集積度の高い半導体装置を安定的に製造することができる。また、本発明の半導体装置の製造方法において、前記配線層の上部に、前記配線に接続する上部配線を形成する工程を含んでもよい。こうすることによ

50

り、配線層よりも上層に存在する上部配線の集積度の高い多層の半導体装置を安定的に製造することができる。

#### 【0031】

本発明の製造方法において、第一の孔を形成する前記工程の前に、前記半導体基板の前記素子形成面の上部に設けられた絶縁層を設ける工程を有し、第一の導電プラグを形成する前記工程は、前記絶縁層の内部に、前記第一の導電プラグと同時にトランジスタ素子へ接続する接続プラグを形成する工程を含んでもよい。こうすることにより、さらに簡便な製造手順とすることができます。

#### 【0032】

なお、これらの各構成の任意の組み合わせや、本発明の表現を方法、装置などの間で変換したものもまた本発明の態様として有効である。10

#### 【0033】

たとえば、本発明において、第一の導電プラグの一部を露出させる前記工程の後、第一の金属膜を露出させる前記工程の前に、前記第二の孔の内面の前記第一の導電プラグを除く領域に選択的に絶縁材料を付着させる工程をさらに含んでもよい。こうすることにより、簡便なプロセスで第二の導電プラグの表面の絶縁性にすぐれた半導体装置を製造することができます。

#### 【0034】

本発明の半導体装置の製造方法において、前記絶縁材料は電着材料であってもよい。こうすることにより、絶縁材料をさらに高い選択性で前記第二の孔の内面の前記第一の導電プラグを除く領域に付着させることができる。20

#### 【0035】

本発明の半導体装置の製造方法において、前記電着材料は電着ポリイミドであってもよい。こうすることにより、以降のプロセスにおける処理に対する絶縁材料の耐性を向上させることができる。よって、半導体装置のさらに高い歩留まりで安定的に製造することができます。

#### 【0036】

また、本発明において、第一の金属膜を埋設する前記工程は、前記第一の孔の内壁に、バリアメタル膜を形成する工程を含んでもよい。また、本発明において、第一の金属膜は、バリアメタル膜を含む積層膜とすることができる。こうすることにより、第一の導電プラグを構成する導電材料の半導体基板への拡散をより一層確実に抑制することができる。30

#### 【発明の効果】

#### 【0037】

以上説明したように本発明によれば、素子形成面側に設けられた第一の導電プラグと、半導体基板に設けられ、第一の導電プラグの断面積よりも大きい第二の導電プラグとにより貫通電極を構成しているため、電極としての性能および製造安定性に優れた貫通電極を有する半導体装置が提供される。

#### 【発明を実施するための最良の形態】

#### 【0038】

以下、本発明の実施形態について図面を参照して説明する。なお、すべての図面において、同様の構成要素には同一の符号を付し、以下の説明において詳細な説明を適宜省略する。また、以下の実施形態において、半導体基板の素子形成面側を半導体装置の上(表)側とし、半導体基板の裏面側を半導体装置の下(裏)側とする。40

#### 【0039】

##### (第一の実施形態)

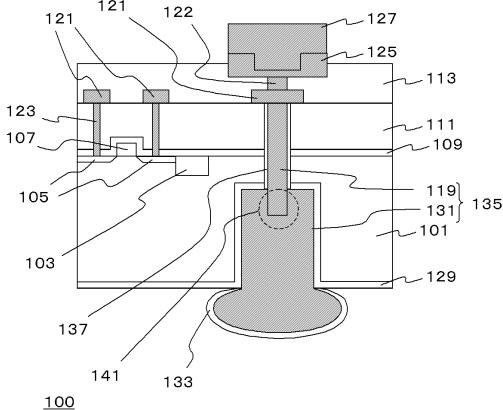

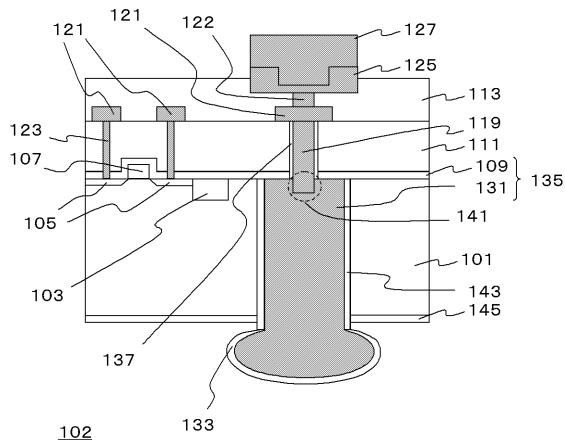

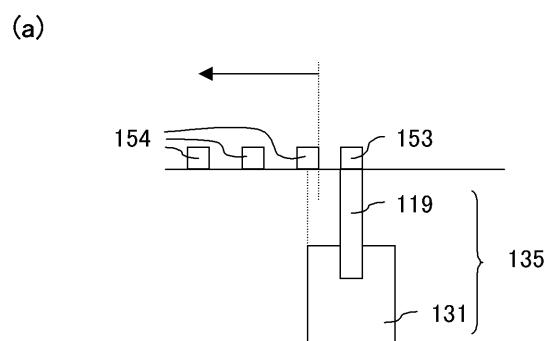

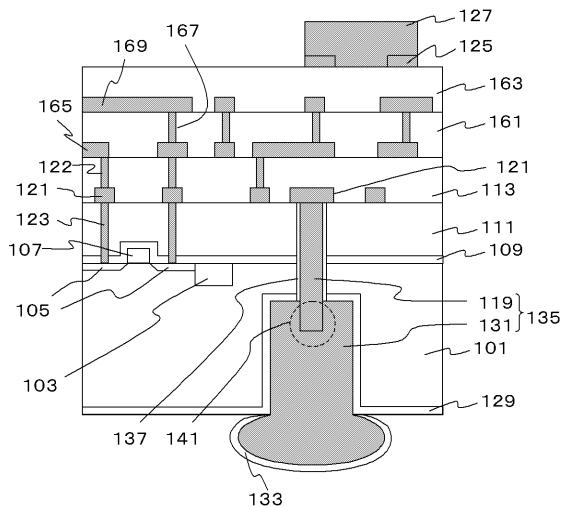

図1は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図1の半導体装置100は、シリコン基板101、エッチングストップ膜109、最下層絶縁膜111、第一配線層絶縁膜113の積層構造を有し、シリコン基板101、エッティングストップ膜109、および最下層絶縁膜111を貫通する貫通電極135が設けられている。

#### 【0040】

50

シリコン基板 101 の素子形成面に、拡散層 105、ゲート電極 107 等からなるMOSトランジスタおよび素子分離膜 103 が形成されている。MOSトランジスタおよび素子分離膜 103 を埋め込むように最下層絶縁膜 111 が形成されている。最下層絶縁膜 111 中には、シリコン基板 101 およびゲート電極 107 の上面に接してエッティングストップ膜 109 が設けられている。また、最下層絶縁膜 111 には、拡散層 105 に接続する接続プラグ 123 も設けられている。

#### 【0041】

第一配線層絶縁膜 113 には第一配線 121 および第一配線 121 に電気的に接続する接続プラグ 122 が設けられている。また、接続プラグ 122 の上部には、これと電気的に接続するパッド 125 およびパッド 125 と電気的に接続するバンプ 127 がこの順に形成されている。10

#### 【0042】

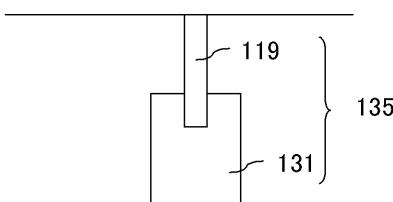

貫通電極 135 は、導電性の小径プラグ 119 と導電性の大径プラグ 131 とを有する。小径プラグ 119 の断面積および径は、それぞれ接続プラグ 123 の断面積および径よりも大きく大径プラグ 131 の断面積および径よりも小さい。また、シリコン基板 101 から小径プラグ 119 が突出した突出部 141 が大径プラグ 131 の上面に貫入している。20

#### 【0043】

小径プラグ 119 の径は、たとえば、 $1 \sim 5 \mu\text{m}$ 程度とすることができます。また、小径プラグ 119 はシリコン基板 101 中に  $20 \sim 50 \mu\text{m}$  程度貫入している構成とすることができます。さらに、大径プラグ 131 中に貫入している突出部 141 の長さを、たとえば  $1 \sim 50 \mu\text{m}$  程度とすることができます。また、大径プラグ 131 の径は、たとえば  $10 \sim 1000 \mu\text{m}$  程度とすることができます。20

#### 【0044】

小径プラグ 119 は、最下層絶縁膜 111 の上面からエッティングストップ膜 109、シリコン基板 101 をこの順に貫通し、その先端がシリコン基板 101 の外部に露出した突出部 141 となっている。小径プラグ 119 の上面は、第一配線層絶縁膜 113 の底面と同一平面内に底面を有する第一配線 121 と接触し、電気的な接続が確保されている。小径プラグ 119 の側面は、突出部 141 を除き SiN 膜 137 に被覆されている。30

#### 【0045】

また、大径プラグ 131 は、シリコン基板 101 の裏面から素子形成面に向かって形成されている。大径プラグ 131 の上面は、シリコン基板 101 の上面よりも下方に位置する。大径プラグ 131 の底面および側面、ならびにシリコン基板 101 の裏面に電着絶縁膜 129 が設けられている。また、大径プラグ 131 の表面はめっき膜 133 に被覆されている。30

#### 【0046】

小径プラグ 119 の材料に特に制限はないが、たとえば、W を用いることができる。こうすることにより、シリコン基板 101 への拡散が好適に抑制される。また、大径プラグ 131 およびめっき膜 133 の材料に特に制限はないが、それぞれ、たとえば Ni および Au とすることができる。40

#### 【0047】

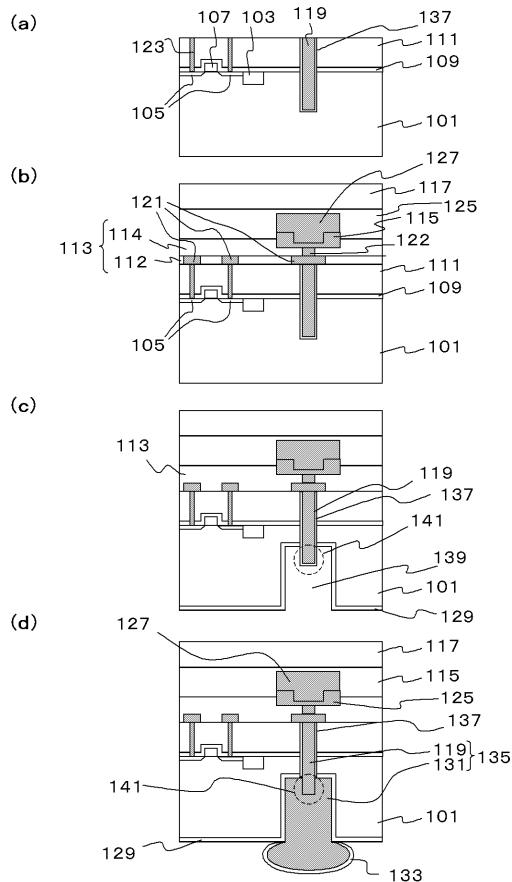

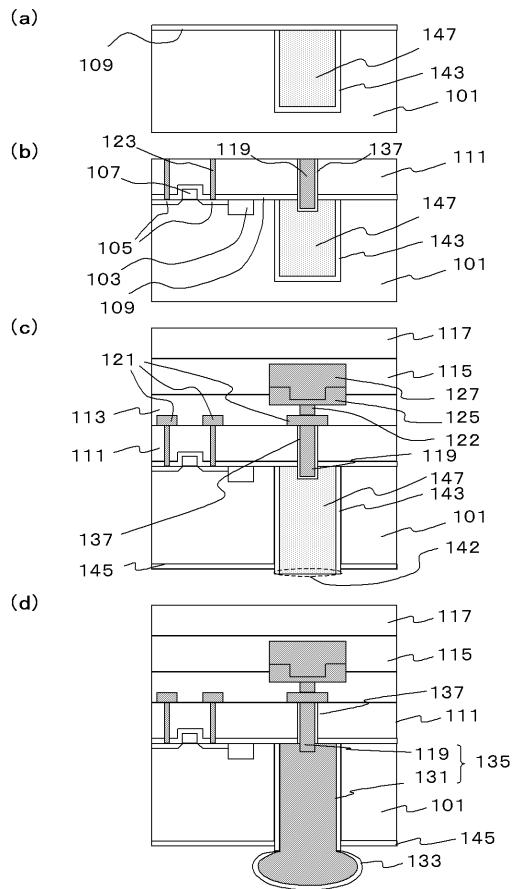

次に、半導体装置 100 の製造方法を説明する。図 2(a) ~ 図 2(d) は、図 1 に示した半導体装置 100 の製造工程を模式的に示す断面図である。

#### 【0048】

まず、シリコン基板 101 上にゲート電極 107、拡散層 105、素子分離膜 103 を形成する。素子分離膜 103 は、たとえば STI (シャロートレンチアイソレーション) とする。その後、シリコン基板 101 の上面全面にエッティングストップ膜 109 および最下層絶縁膜 111 をこの順に積層する。

#### 【0049】

このとき、エッティングストップ膜 109 として、たとえば SiN 膜をプラズマ CVD 法50

により 50 nm 成膜する。また、最下層絶縁膜 111 として、たとえば SiO<sub>2</sub> 膜をプラズマ CVD 法により 400 nm 成膜する。または、最下層絶縁膜 111 として、低誘電率層間絶縁膜である L-Ox (商標) 膜を塗布法により 300 nm 成膜し、L-Ox (商標) 膜の上面に SiO<sub>2</sub> 膜を 100 nm 成膜して、積層膜を形成してもよい。

#### 【0050】

次に、最下層絶縁膜 111 上に反射防止膜とフォトレジストをこの順に塗布し、フォトリソグラフィー技術を用いて小径プラグ 119 の形状に対応する開口部を有するレジストパターン (不図示) を形成する。フォトレジスト膜をマスクとして最下層絶縁膜 111 をドライエッティングして、小径プラグ 119 を設ける位置を開口させる。そして、ドライエッティングによりエッティングストップ膜 109 のエッチバックを行う。

10

#### 【0051】

その後、さらにエッティングガスを変えて、シリコン基板 101 を途中までエッティングする。たとえば、シリコン基板 101 の上面から 10 μm 以上 50 μm 以下の深さまでエッティングする。深さを 10 μm 以上とすることにより、突出部 141 の周囲を大径プラグ 131 に確実に接続することができる。また、50 μm 以下とすることにより、シリコン基板 101 の素子形成面からの小径プラグ 119 のシリコン基板 101 内部への突出量を減少させることができる。このため、開口部を安定的に形成することができる。開口部の径は、小径プラグ 119 の径がたとえば 1 ~ 5 μm 程度となるように選択される。そして、フォトレジスト膜および反射防止膜あるいはエッティングによるそれらの残渣を除去する。

#### 【0052】

次に、小径プラグ 119 の形状に対応した開口部が設けられたシリコン基板 101 の上面全面に SiN 膜 137 を 20 nm 成膜する。これにより、開口部の側面および底面に SiN 膜 137 が形成される。

20

#### 【0053】

そして、最下層絶縁膜 111 上に、新たに反射防止膜とフォトレジストをこの順に塗布し、フォトリソグラフィー技術を用いて接続プラグ 123 の形状に対応して開口するレジストパターン (不図示) を形成する。このフォトレジスト膜をマスクとして、最下層絶縁膜 111 をドライエッティングし、拡散層 105 の上部の接続プラグ 123 を設ける位置を開口させる。そして、ドライエッティングによりエッティングストップ膜 109 のエッチバックを行い、拡散層 105 の上面を露出させる。こうして、小径プラグ 119 および接続プラグ 123 を形成するための孔を得る。

30

#### 【0054】

次に、シリコン基板 101 の上面全面に、金属膜として W 膜を CVD 法により成膜する。W 膜の膜厚は、接続プラグ 123 および小径プラグ 119 の径に合わせて、その両方が埋め込められるような膜厚に設定される。たとえば、W の膜厚を 1 μm 程度とする。そして、最下層絶縁膜 111 上の W 膜および SiN 膜 137 を CMP (Chemical Mechanical polishing) により除去する。こうして、小径プラグ 119 および接続プラグ 123 が同時に形成される (図 2 (a))。

#### 【0055】

次に、シリコン基板 101 の上面全面に第一配線層絶縁膜 113 を設ける。第一配線層絶縁膜 113 は、図 2 (b) に示したように、配線用絶縁膜 112 およびプラグ用絶縁膜 114 が積層された構成である。

40

#### 【0056】

まず、シリコン基板 101 の上面全面を被覆し、第一配線層絶縁膜 113 の下層をなす配線用絶縁膜 112 を 300 nm 成膜する。配線用絶縁膜 112 は、たとえば、L-Ox (商標) 膜等の低誘電率膜とすることができます。このとき、最下層絶縁膜 111 上に Cu 拡散防止膜の SiCN 膜を設けてもよい。また、低誘電率膜上に SiO<sub>2</sub> 膜を 100 nm 成膜してもよい。次に、シリコン基板 101 の上面全面に反射防止膜およびフォトレジストを塗布し、フォトリソグラフィー技術を用いて、フォトレジストに溝配線用レジストパターンを形成する。そして、フォトレジストをマスクにして、第一配線層絶縁膜 113 を

50

エッチングし、第一配線 121 作製用の開口部を形成する。次に、アッシングによりフォトレジストと反射防止膜を除去する。

#### 【0057】

その後、スパッタリング法により、バリアメタル膜として TaN 膜を 30 nm 成膜し、TaN 膜の上にシード用の Cu 膜を 100 nm 成膜する。次に、電解メッキ法により Cu 膜を 700 nm 成膜し、次いで CMP 法により、第一配線 121 となる金属膜を形成する。その後、小径プラグ 119 および接続プラグ 123 の形成時と同様にして、配線用絶縁膜 112 上の Cu 膜およびバリアメタル膜を除去し、第一配線 121 が形成される。

#### 【0058】

その後、通常の配線作製工程により、配線用絶縁膜 112 上に、第一配線層絶縁膜 113 の上層をなすプラグ用絶縁膜 114 を形成する。プラグ用絶縁膜 114 中に、第一配線 121 と接続する接続プラグ 122 を形成する。そして、接続プラグ 122 に接続するパッド 125、およびバンプ 127 をこの順に形成する。パッドの材料は、たとえば Al、Cu、Ni、TiN 等とすることができる。また、バンプ 127 の材料は、たとえば Au、ハンダ等とすることができる。

#### 【0059】

なお、第一配線層絶縁膜 113 の上部にさらに所定の数の配線層等の上層を形成してもよい。

#### 【0060】

次に、シリコン基板 101 の上面に粘着剤層 115 を形成し、支持体 117 を貼付する(図 2(b))。粘着剤層 115 として、たとえば粘着テープを用いる。粘着テープは基材とその両面に形成された粘着層から構成されている。粘着テープを構成する基材としては、たとえば、ポリオレフィン系樹脂、ポリエステル系樹脂などが用いられる。また、粘着テープを構成する粘着剤としては、たとえば、アクリル系エマルジョン型粘着剤、アクリル系溶剤型粘着剤、ウレタン系粘着剤などが用いられる。

#### 【0061】

また、支持体 117 の材料は、後述する裏面研削によるシリコン基板 101 の薄化加工等のプロセスにおける、熱、薬剤、外力などに対する耐性を備えている材料であればよく、たとえば、石英やパイレックス(登録商標)等のガラスとすることができます。また、ガラス以外の材料としてもよい。たとえば、アクリル樹脂などのプラスチックス等のを用いてもよい。

#### 【0062】

次に、シリコン基板 101 の裏面研削を行う。裏面研削は、機械的研磨により行う。研削後のシリコン基板 101 の厚さは、小径プラグ 119 の底部が露出しない範囲で適宜選択することができるが、たとえば、50~200 μm 程度とすることができます。そして、シリコン基板 101 の裏面に反射防止膜およびフォトレジストをこの順に成膜し、フォトリソグラフィー技術を用いて大径プラグ 131 を形成する領域が開口するレジストパターン(不図示)を形成する。フォトレジスト膜をマスクとしてシリコン基板 101 をドライエッチングして選択的に除去し、後に大径プラグ 131 を設ける位置に開口部 139 を設ける。

#### 【0063】

開口部 139 は、シリコン基板 101 の裏面から素子形成面に向かい、上面がシリコン基板 101 の素子形成面の近傍よりも下方に位置する形状とする。また、開口部 139 は突出部 141 の底部に設けられ、その上面が小径プラグ 119 の底面よりも上方に位置する。小径プラグ 119 の表面に SiN 膜 137 が設けられており、前述のシリコン基板 101 をドライエッチングする際のエッチング条件は、シリコン膜と SiN 膜 137 との選択比が高い条件に設定されているため、開口部 139 の形成時に小径プラグ 119 は除去されず、小径プラグ 119 の側面外周のシリコン基板 101 が選択的に除去される。これにより、小径プラグ 119 の底面を含む姿態で開口部 139 が形成される。また、小径プラグ 119 の一部がシリコン基板 101 の外部に露出し、突出部 141 が形成される。

10

20

30

40

50

## 【0064】

次に、シリコン基板101の裏面に電着絶縁膜129を設ける(図2(c))。このとき、電着絶縁膜129は、シリコン基板101の裏面ならびに開口部139の底面および側面に選択的に成膜される。突出部141の表面は絶縁性のSiN膜137に被覆されているため、小径プラグ119の外側には電着絶縁膜129が形成されない。電着絶縁膜129の膜厚は、たとえば0.5~5μm程度とする。

## 【0065】

電着絶縁膜129は、たとえば電着ポリイミド膜とする。電着ポリイミド膜の材料として、カチオン型ポリイミド電着塗料またはアニオン型ポリイミド電着塗料を用いることができる。具体的には、たとえば、シミズ社製エレコートPI等を用いることができる。なお、電着絶縁膜129の材料はポリイミドには限定されず、エポキシ系の電着塗料、アクリル系の電着塗料、フッ素系の電着塗料等、他の電着高分子塗料を用いてもよい。電着絶縁膜129の材料としてポリイミドを用いることにより、電着絶縁膜129の耐熱性を向上させることができる。このため、その後の製造プロセスにおける劣化が好適に抑制され、高い歩留まりで安定的に製造可能な構成とすることができます。

## 【0066】

電着絶縁膜129の形成は、たとえば以下のようにして行う。シリコン基板101を一方の電極とし、他方の対極とともに電着塗料の液体中に浸漬させる。そして、シリコン基板101および対極に電着塗料中の高分子の電荷に応じて所定の電位を印加する。こうすると、シリコン基板101の表面に高分子が付着する。所定の膜厚が得られたら、塗料からシリコン基板101を取り出し、水洗する。その後、シリコン基板101を焼成することにより、その裏面に電着絶縁膜129が形成される。

## 【0067】

次に、SiN膜137のエッチバックを行う。これにより、突出部141の先端部においてSiN膜137が除去されて小径プラグ119の表面を露出させる。このとき、シリコン基板101の裏面には電着絶縁膜129が形成されているため、シリコン基板101は除去されず、SiN膜137が選択的に除去される。なお、図1および図2(d)においては、突出部141におけるSiN膜137がすべて除去されている構成を例示したが、小径プラグ119のプラグ底部を含む少なくとも一部が露出していればよい。

## 【0068】

次いで、無電解めっきにより小径プラグ119の露出部を起点としてNi膜を成長させて、開口部139を埋め込むとともに、開口部139の外部にバンプを一体に形成する。そして、バンプの表面にAuのめっき膜133を設けることにより、大径プラグ131が形成される(図2(d))。

## 【0069】

このとき、大径プラグ131の形成を、裏面の開口部139の埋め込み工程と、裏面のバンプ形成工程に分けて行ってもよい。

## 【0070】

その後、粘着剤層115をシリコン基板101の素子形成面から剥離することにより、支持体117が除去され、図1に示した半導体装置100が得られる。

## 【0071】

次に、図1に示した半導体装置100の効果を説明する。

まず、半導体装置100においては、貫通電極135が小径プラグ119および大径プラグ131の二つのプラグからなる。小径プラグ119の端部の突出部141は、大径プラグ131に内包されている。

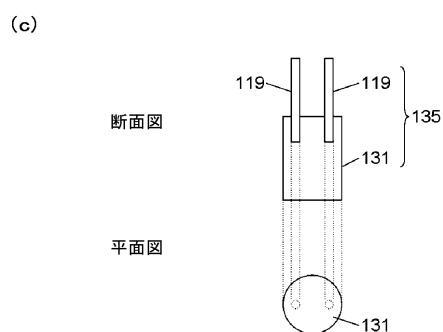

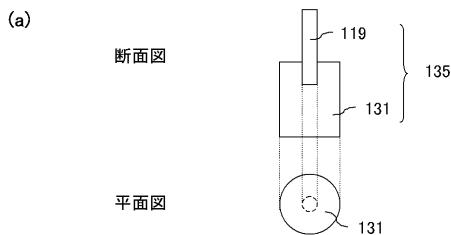

## 【0072】

図7(a)および図7(b)は、太さの異なる2本のプラグからなる貫通電極の構成を模式的に示す図である。各分図において、上の図が断面図であり、下の図が平面図である。図7(a)は、本実施形態に係る貫通電極135の構成を示す図である。また、図7(b)は、小径プラグ219と大径プラグ231とが平坦面において接続した形状の貫通電

10

20

30

40

50

極 235 を示す図である。

【 0073 】

図 7 ( a ) の構成では、アンカー効果による両プラグの密着性の向上が図られる。このため、図 7 ( b ) の構成のように、これらの端部同士が単に接触している場合に比べて密着した構成とすることができる。また、シリコン基板 101 の裏面側から選択成長で大径プラグ 131 を形成可能な構成とすることができます。このため、製造プロセスの簡素化が可能な構成となっている。また、この構成により、両プラグ間のコンタクト抵抗の低減が図られる。このため、半導体装置 100 の電気的特性を向上させることができる。

【 0074 】

また、図 7 ( c ) に示したように、貫通電極 135 が大径プラグ 131 に内包される二つの小径プラグ 119 および大径プラグ 131 の三つのプラグからなる構造では、アンカー効果によるプラグの密着性はさらに向上し、コンタクト抵抗のさらなる低減が図られる。

【 0075 】

なお、小径プラグ 119 は、大径プラグ 131 の裏面側まで貫通する必要はない。突出部 141 の深さを浅くすることができるため、埋め込みによる小径プラグ 119 の製造が安定的に行える構成である。

【 0076 】

また、貫通電極 135 においては、小径プラグ 119 の径が大径プラグ 131 の径よりも小さい構成となっている。このため、小径プラグ 119 に電気的に接続する第一配線 121 の大きさを小さくすることができる。また、最下層絶縁膜 111 中の素子の集積度を向上させることができると可能な構成となっている。よって、装置全体の小型化に好適な構成となっている。

【 0077 】

また、小径プラグ 119 が接続プラグ 123 と同時に成形可能であるため、製造プロセスの簡素化およびそれに伴う製造コストの低減が可能な構成となっている。また、小径プラグ 119 の成形がトランジスタの成形工程に与える影響が小さく、貫通電極 135 の形成によるトランジスタへのダメージが少ない構成となっている。

【 0078 】

また、貫通電極 135 の上部において、小径プラグ 119 が最下層配線である第一配線層絶縁膜 113 内の第一配線 121 に接続しており、貫通電極 135 が第一配線層絶縁膜 113 に突出しない構成となっている。このため、第一配線層絶縁膜 113 内の配線密度を向上させることができると可能な構成となっている。よって、貫通電極 135 の設置が回路の構成に与える影響が小さく、半導体装置 100 は素子や配線の配置の選択の自由度が高く、また、第一配線層絶縁膜 113 のデッドスペースの減少および第一配線 121 の集積度を高くすることができると可能な構成とすることができます。

【 0079 】

また、半導体装置 100 においては、開口部 139 の内面の突出部 141 の表面を除く領域に電着絶縁膜 129 が選択的に設けられている。このため、大径プラグ 131 を形成する以降の工程において、電着絶縁膜 129 を保護膜として用いることができるため、大径プラグ 131 形成用のレジストパターンをシリコン基板 101 の裏面に形成する必要がない。このため、簡便なプロセスで大径プラグ 131 を安定的に製造可能な構成となっている。

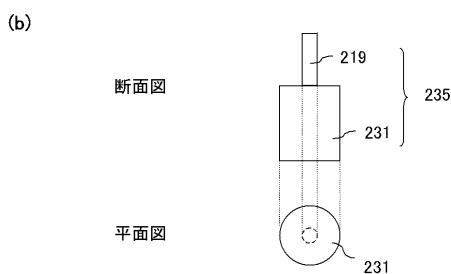

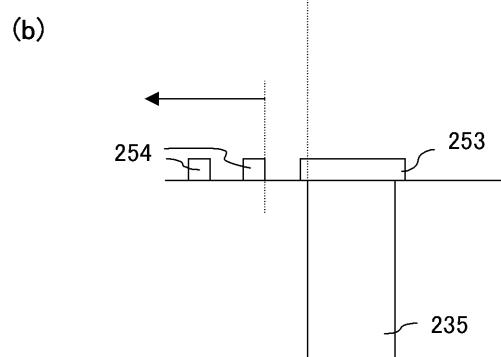

【 0080 】

次に、小径プラグ 119 と大径プラグ 131 からなる貫通電極 135 の構成を従来の貫通電極の構成と対比してさらに説明する。図 8 ( a ) および図 8 ( b ) は、貫通電極の構成を模式的に示す断面図である。図 8 ( a ) は本実施形態に係る貫通電極 135 の構成を模式的に示した図である。また、図 8 ( b ) は、従来の貫通電極 235 の構成を模式的に示した図である。

【 0081 】

10

20

30

40

50

図8(b)に示したように、従来の貫通電極235は、太い一本のプラグからなり、その上面で配線253に接触している。このため、貫通電極235の上部の配線253の面積が比較的大きくなる傾向にあった。また、貫通電極235に接触する配線253の層においては、貫通電極235の近傍に、貫通電極235に接触する配線253以外の配線254を設けることができなかった。このため、図中に矢印で示したように、貫通電極235の上面およびその近傍から離れた領域にのみ、貫通電極235に接触する配線253以外の配線254を形成することが可能であった。よって、貫通電極235に接触する配線253以外の配線254の集積度の向上の点で改善の余地があった。

#### 【0082】

これに対し、図8(a)に示したように、本実施形態に係る貫通電極135では、小径プラグ119の上面で配線153に接触している。このため、小径プラグ119の上部の配線153の断面積を小さくすることができる。また、配線153に接続するプラグ119が小径プラグ119である。このため、図中に矢印で示したように、小径プラグ119に接触する配線153以外の配線154を形成可能な領域が広い。このため、小径プラグ119に接触する配線153以外の配線154の集積度を向上させることができる。また、配線層近傍ではプラグの径を低くして配線密度を充分に確保しつつ、配線層の近傍以外ではプラグの径を太くして電気抵抗を低減することができる。

#### 【0083】

また、図8(a)の貫通電極135は、図7(a)および図7(b)を用いて前述したように、小径プラグ119の一部が大径プラグ131に貫入した構成である。このため、図8(b)の構成とは異なり2本のプラグを用いた場合にも、図7(b)の構成と比較した場合に、これらのプラグの間の接触抵抗が充分に小さく、貫通電極としての特性に優れた構成となっている。

#### 【0084】

なお、図1には示していないが、半導体装置100において、第一配線層絶縁膜113の上層の構成は、装置設計に応じて適宜選択することができる。第一配線層絶縁膜113の上部にさらに配線層等が積層されていてもよい。

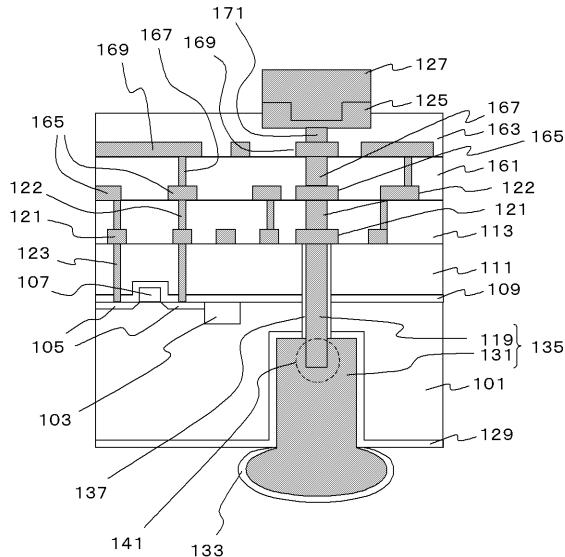

#### 【0085】

たとえば、図10は、配線層が積層された半導体装置の構成を模式的に示す断面図である。図10の半導体装置の構成は基本的には図1に示した半導体装置100と同様であるが、シリコン基板101上に、最下層絶縁膜111、第一配線層絶縁膜113に加え、さらに絶縁層161および絶縁層163が積層されている。絶縁層161には、配線165および接続プラグ167が形成されている。絶縁層163には、配線169および接続プラグ171が形成されている。

#### 【0086】

図10に示したように、本実施形態に係る貫通電極135は、素子形成面側に断面積の小さい小径プラグ119が設けられ、これが積層体中の下層に設けられた第一配線121と接続している。このため、上層の配線の集積度を向上させることができる。

#### 【0087】

また、図11は、配線層が積層された半導体装置の別の構成を模式的に示す断面図である。図11に示したように、小径プラグ119が第一配線121と接続しているため、第一配線121よりも上層の設計の自由度にすぐれている。たとえば、貫通電極135がバンプ127に接続していない構成や、貫通電極135の直上にバンプ127を形成せずに、不図示の配線を介して貫通電極135とバンプ127とを接続した構造等とすることができる。

#### 【0088】

また、本実施形態および以下の実施形態に係る半導体装置において、貫通電極135を構成する小径プラグ119の一部が大径プラグ131に内包する態様として、たとえば、小径プラグ119の断面の一部が内包される態様および断面すべてが内包される態様が挙げられる。図12(a)および図12(b)は、こうした貫通電極135の構成を模式的

10

20

30

40

50

に示す断面図である。図12(a)は、小径プラグ119の断面のすべてが大径プラグ131に内包されている構成を示す図である。また、図12(b)は、小径プラグ119の断面の一部が大径プラグ131に内包されている構成を示す図である。小径プラグ119の内包のされ方により、大径プラグ131に形成される凹部の形状が異なっている。

#### 【0089】

図12(a)および図12(b)のように、小径プラグ119の断面の少なくとも一部が大径プラグ131に内包される構成とすることにより、小径プラグ119が大径プラグ131に複数の面で接触する構成とすることができます。このため、図7(b)を用いて前述した構成に比べ、小径プラグ119と大径プラグ131との密着性を向上させることができる。また、図12(a)に示したように、小径プラグ119の断面すべてが大径プラグ131に貫入し、内包される構成とすることにより、これらの密着性をさらに向上させることができる。

10

#### 【0090】

以下の実施形態では、第一の実施形態と異なる点を中心に説明する。

#### 【0091】

##### (第二の実施形態)

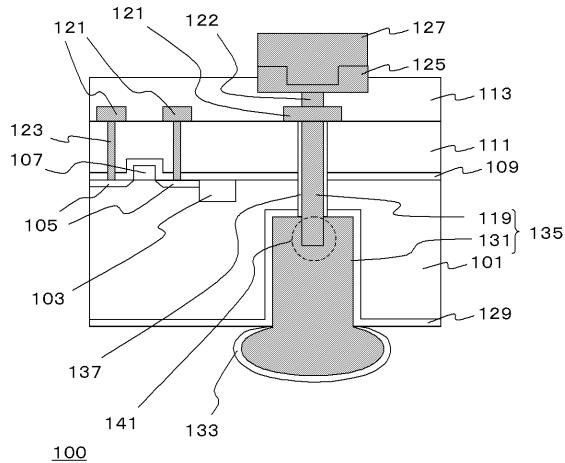

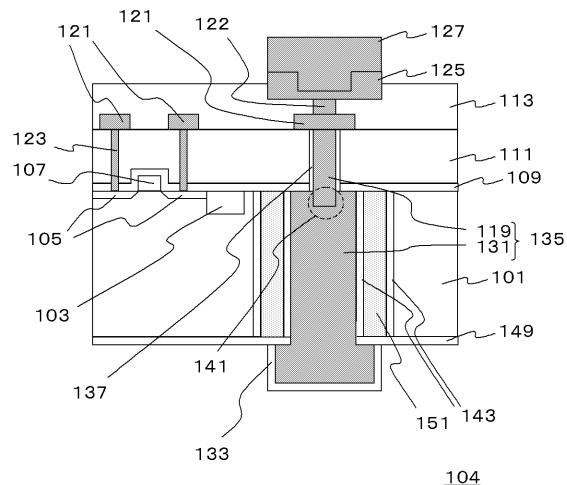

図3は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図3に示した半導体装置102においては、大径プラグ131の上面がシリコン基板101の上面すなわち素子形成面に一致している。また、半導体装置102では、図1に示したシリコン基板101における電着絶縁膜129に代わり、大径プラグ131の側面にSiN膜143が形成され、シリコン基板101の裏面にSiN膜145が形成されている。

20

#### 【0092】

次に、半導体装置102の製造方法を説明する。図4(a)～図4(d)は、図2に示した半導体装置102の製造工程を模式的に示す断面図である。

#### 【0093】

まず、シリコン基板101に、反射防止膜とフォトレジストをこの順に塗布し、フォトリソグラフィー技術を用いて大径プラグ131の形状に対応する開口部を有するレジストパターン(不図示)を形成する。このフォトレジスト膜をマスクとして、シリコン基板101をドライエッチングし、大径プラグ131を設けるための開口部を形成する。このとき、開口部の深さは適宜選択されるが、たとえば50μm以上200μm以下とすることができます。そして、フォトレジスト膜および反射防止膜を除去する。

30

#### 【0094】

次に、大径プラグ131の形状に対応した開口部が設けられたシリコン基板101の上面全面にSiN膜143を100nm成膜する。そして、開口部を埋め込むようにシリコン基板101の素子形成面の全面にSiO<sub>2</sub>膜147をSOG(スピンドルオングラス)塗布する。次に、開口部以外の領域に成膜されたSiO<sub>2</sub>膜147をCMPにより除去し、SiN膜143の上面を露出させる。次いで、エッチングストップ膜109としてSiN膜を成膜し、SiO<sub>2</sub>膜147の上面をエッチングストップ膜109で被覆する(図4(a))。

40

#### 【0095】

次に、第一の実施形態と同様にして、素子分離膜103、拡散層105、ゲート電極107を設ける。さらに、第一の実施形態と同様にして最下層絶縁膜111を形成し、最下層絶縁膜111を貫通する小径プラグ119および接続プラグ123を同時に形成する(図4(b))。なお、半導体装置102では、小径プラグ119がSiO<sub>2</sub>膜147の内部にたとえば深さ1～50μm程度貫入した構成とすることができます。

#### 【0096】

そして、第一の実施形態と同様にして、第一配線層絶縁膜113、第一配線121、接続プラグ122、パッド125、バンプ127を形成する。そして、粘着剤層115を介して支持体117の表面にシリコン基板101の素子形成面の側を固定する。

#### 【0097】

50

次に、シリコン基板 101 の裏面研削を行い、 $\text{SiO}_2$  膜 147 の底面に設けられている  $\text{SiN}$  膜 143 の下面を露出させる。このとき、さらに裏面研削を進めて  $\text{SiO}_2$  膜 147 を露出させてもよい。この  $\text{SiN}$  膜 143 あるいは  $\text{SiO}_2$  膜 147 をマスクとして、シリコン基板 101 の裏面をさらにドライエッティングする。これにより、シリコン基板 101 の裏面側に突出部 142 が形成される。そして、シリコン基板 101 の裏面側の表面全面に  $\text{SiN}$  膜 145 を成膜する。そして、シリコン基板 101 の裏面において  $\text{SiN}$  の CMP を行い、突出部 142 において  $\text{SiO}_2$  膜 147 の下面を露出させる（図 4(c)）。

#### 【0098】

次に、ウェットエッティングにより  $\text{SiO}_2$  膜 147 を除去する。エッティング液として、たとえば 40 ~ 49 重量% 程度の濃 HF 水溶液を用いる。このとき、 $\text{SiO}_2$  膜 147 の上面および側面にはエッティングストップ膜 109 および  $\text{SiN}$  膜 143 がそれぞれ設けられているため、 $\text{SiO}_2$  膜 147 が選択的に除去される。こうして、大径プラグ 131 の形状の開口部が得られ、突出部 141 が露出する。

#### 【0099】

そして、第一の実施形態と同様にして  $\text{SiN}$  膜 137 のエッチバックを行い、無電解めっきにより小径プラグ 119 の露出部を起点として  $\text{Ni}$  膜を成長させて、開口部 139 を埋め込むとともに、開口部 139 の外部にバンプを一体に形成する。そして、バンプの表面に Au のめっき膜 133 を設けることにより、大径プラグ 131 が形成される（図 4(d)）。

#### 【0100】

そして、粘着剤層 115 をシリコン基板 101 の素子形成面から剥離することにより、支持体 117 が除去され、図 3 に示した半導体装置 102 が得られる。

#### 【0101】

次に、図 3 に示した半導体装置 102 の効果を説明する。半導体装置 102 は、第一の実施形態に記載の半導体装置 100 の効果に加えて以下の効果を有する。

#### 【0102】

半導体装置 102 は、トランジスタの形成前に大径プラグ 131 の位置に  $\text{SiO}_2$  膜 147 が形成される構成である。このため、大径プラグ 131 形成のための深いエッティングを素子形成前に行なうことが可能な構成となっている。よって、裏面研削の後、大径プラグ 131 を形成するための開口部を裏面側に設ける際に、 $\text{SiO}_2$  膜 147 を除去すればよい。したがって、トランジスタ形成後のシリコン基板 101 の深いエッティングを行うことなく大径プラグ 131 を形成することができる。このため、プラズマ照射等によるトランジスタ等の受けるダメージが少なく、信頼性がさらに向上されている。

#### 【0103】

また、半導体装置 102 においては、シリコン基板 101 の裏面側に突出部 142 が形成されている。このため、 $\text{Ni}$  膜が大径プラグ 131 やバンプの側面でシリコン基板 101 と接触することの抑制が図られる。このため、信頼性にすぐれた構成となっている。

#### 【0104】

また、シリコン基板 101 の裏面研削の際に、 $\text{SiO}_2$  膜 147 とシリコン基板 101 が同時に研磨される構成となっている。このため、金属膜とシリコン基板 101 とを同時に研削する場合と比べて、研磨比の違いによる貫通電極 135 の裏面の粗面化が抑制された構成となっている。

#### 【0105】

一方、従来の貫通電極においては、たとえば、前述の非特許文献 1 に記載されているように、電極形成後に裏面研削がなされる構成となっている。このため、裏面研削の際にシリコン基板と金属膜とを同時に研削しなければならなかった。ところが、これらの研磨比が比較的大きいため、貫通電極の裏面が粗面化しやすかった。また、金属膜は延性が強いため裏面電極周辺がダレが生じて Si 面上に付着し、Cu 等の比較的 Si 中に拡散しやすい金属を含む場合、金属がシリコン基板中に拡散することがあった。このため、トランジ

10

20

30

40

50

スタ等の素子の信頼性を低下させることがあった。

#### 【0106】

これに対し、図3に示した半導体装置102においては、裏面研削においてSiO<sub>2</sub>膜147とシリコン基板101の同時研磨が行われる構成であるため、裏面研削の制御が容易であり、安定的に研削可能な構成であり、また平坦な裏面を有する構成とすることができる。また、安定的な大径プラグ131の形成が可能な構成となっている。また、大径プラグ131の側面および底面がそれぞれSiN膜143およびSiN膜145により被覆されているため、大径プラグ131中に含まれる金属のシリコン基板101中への拡散が好適に抑制される構成となっている。このため、トランジスタ等の素子の信頼性に優れた構成が実現される。また、裏面研削の際の製造コストを低減可能な構成となっている。

10

#### 【0107】

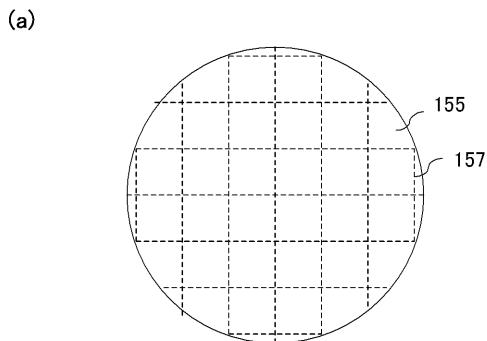

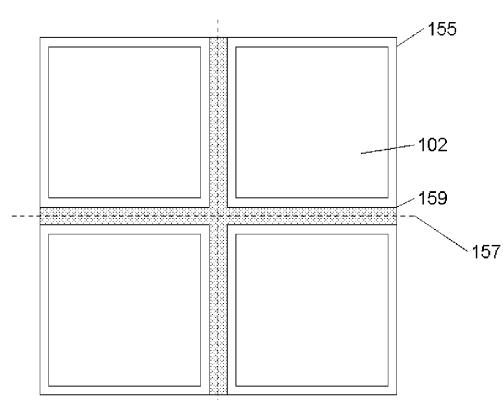

なお、本実施形態に係る半導体装置102を作製する際には、上述のようにシリコン基板101をドライエッチングし、大径プラグ131を設けるための開口部（図4（a）では不図示）を形成する。この手順を、ウエハ上に複数の半導体装置102を同時に作製する際のダイシングに利用することができる。

#### 【0108】

図9（a）および図9（b）は、半導体装置102を作製するウエハ155の構成を模式的に示す平面図である。図9（a）は、ダイシング前のウエハ155を示しており、図中に点線で示したのがダイシングライン157である。また、図9（b）は、図9（a）のダイシングライン157近傍を拡大した図である。なお、ウエハ155は半導体装置102におけるシリコン基板101に対応している。

20

#### 【0109】

図9（a）および図9（b）に示したように、ウエハ155の表面に複数の半導体装置102が形成される。半導体装置102の形成において、シリコン基板101に大径プラグ131の形成と同時にダイシングライン157上にダイシングのための溝を形成しておく。その後、上述した方法で半導体装置102を作製する。このとき、ダイシングライン157近傍に形成された開口部は、裏面研削により貫通溝159となっている。そして、ウェハ全体を引っ張るか、ローラー等に押しつけて変形させることにより、ダイシングライン157にそって破断し、複数の半導体装置102を得る。

30

#### 【0110】

この方法では、複数の半導体装置102が形成されたウエハ155において、半導体装置102の形成領域間に貫通溝159を設けることができる。貫通溝159の内部のウエハ155が除去されているため、貫通溝159の形成領域を他の領域よりも薄化することができる。このため、この部分をダイシング領域とすることにより、確実にウエハ155の分割が可能となる。

#### 【0111】

また、この方法では、ダイシングライン157の近傍に貫通溝159を形成することができる。このため、ダイシングが容易な構成とすることができます。貫通溝159は、大径プラグ131の形成用の開口部と同時に得られるため、貫通溝159を作製するための独立のプロセスを経る必要がない。このため、低コストのダイシングが可能な構成となっている。このため、裏面工程でコストアップなくダイシング工程を含めることができる。また、貫通溝159の間隔、大きさを調節することにより、ダイシングの条件に適したスクライプ領域を得ることができる。このため、たとえば貫通溝159の集積度を向上させることにより、狭いピッチでのダイシングが可能である。すなわち、このようなダイシング方法においては、通常のブレードを用いる方法と比較して、ダイシング幅を非常に小さくでき、ウェハ1枚からのチップの取り数を大きくすることができる。

40

#### 【0112】

##### （第三の実施形態）

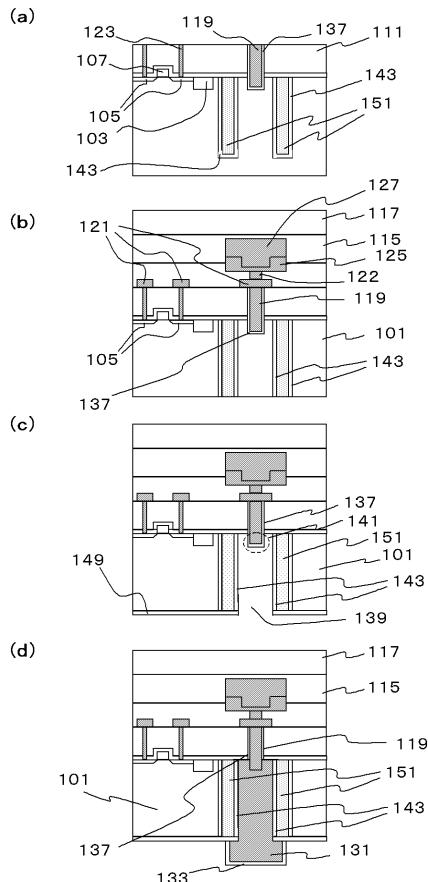

図5は、本実施形態に係る半導体装置の構成を模式的に示す断面図である。図5に示した半導体装置104においては、大径プラグ131の周囲を覆うSiO<sub>2</sub>リング151が

50

設けられている。SiO<sub>2</sub>リング151は、大径プラグ131の側面において、SiN膜143に接して設けられている。SiO<sub>2</sub>リング151の側面は、SiN膜143を介してシリコン基板101に接している。また、第二の実施形態と同様に、シリコン基板101の裏面にSiN膜149が設けられている。

#### 【0113】

次に、半導体装置104の製造方法を説明する。図6(a)～図6(d)は、図5に示した半導体装置104の製造工程を模式的に示す断面図である。

#### 【0114】

まず、図6(a)に示した構成を形成する。はじめに、シリコン基板101に、反射防止膜とフォトレジストをこの順に塗布し、フォトリソグラフィー技術を用いてSiO<sub>2</sub>リング151の形状に対応する円筒環形状の開口部を有するレジストパターン(不図示)を形成する。このフォトレジスト膜をマスクとして、シリコン基板101をドライエッティングし、SiO<sub>2</sub>リング151を設けるための開口部を形成する。このとき、開口部の深さは適宜選択されるが、たとえば50μm以上200μm以下とすることができる。そして、フォトレジスト膜および反射防止膜を除去する。10

#### 【0115】

次に、SiO<sub>2</sub>リングの形状に対応した開口部が設けられたシリコン基板101の上面全面にSiN膜143を100nm成膜する。そして、開口部を埋め込むようにシリコン基板101の素子形成面の全面にSiO<sub>2</sub>膜をSOG(スピンドルオングラス)塗布する。次に、開口部以外の領域に成膜されたSiO<sub>2</sub>膜をCMPにより除去し、SiN膜143の上面を露出させる。こうして、SiO<sub>2</sub>リングが得られる。そして、エッティングストップ膜109としてSiN膜を成膜し、SiO<sub>2</sub>膜147の上面をエッティングストップ膜109で被覆する。20

#### 【0116】

次に、第一の実施形態と同様にして、素子分離膜103、拡散層105、ゲート電極107を設ける。さらに、第一の実施形態と同様にして最下層絶縁膜111を形成し、最下層絶縁膜111を貫通する小径プラグ119および接続プラグ123を同時に形成する。なお、半導体装置102では、小径プラグ119がシリコン基板101の内部にたとえば深さ1～50μm程度貫入した構成とすることができます。

#### 【0117】

次に、図6(b)に示した構成を形成する。まず、第一の実施形態と同様にして、第一配線層絶縁膜113、第一配線121、接続プラグ122、パッド125、バンプ127を形成する。そして、素子形成面を粘着剤層115を介して支持体117の表面に固定する。30

#### 【0118】

次に、第一の実施形態と同様にしてシリコン基板101の裏面研削を行う。研削後のシリコン基板101の厚さは、本実施形態においてもたとえば50～200μm程度とすることができる。

#### 【0119】

次に、図6(c)に示した構成を形成する。はじめに、研削後のシリコン基板101の裏面全面にSiN膜149を20nm成膜する。40

#### 【0120】

そして、シリコン基板101の裏面に反射防止膜とフォトレジストをこの順に塗布し、フォトリソグラフィー技術を用いてSiO<sub>2</sub>リング151の内側が開口するレジストパターン(不図示)を形成する。このフォトレジスト膜をマスクとして、シリコン基板101の裏面をさらにウエットエッティングする。このとき、たとえば濃フッ硝酸を用いてウエットエッティングを行う。これにより、SiO<sub>2</sub>リング151により囲まれた領域のシリコン基板101が除去されて、シリコン基板101の裏面側に開口部139が形成される。また、突出部141が開口部139内に露出する。

#### 【0121】

10

20

30

40

50

次に、図6(d)に示した構成を形成する。フォトレジストおよび反射防止膜を除去した後、SiN膜149をエッチバックする。このとき、小径プラグ119の先端部分のSiN膜137も除去される。そして、シリコン基板101の裏面全面にバリアメタル膜としてTiW膜とCu膜をスパッタ法によりこの順に成膜する。そして、シリコン基板101の裏面に開口部139を開口させたフォトレジストを設け、電解めっきによりNi膜を成長させて、開口部139を埋め込むとともに、開口部139の外部にバンプを一体に形成する。そして、バンプの表面にAuのめっき膜133を設け、大径プラグ131を得る。なお、大径プラグ131の形成と同時に、裏面配線を形成してもよい。

#### 【0122】

そして、フォトレジストを除去し、ウエットエッチングによりシリコン基板101の表面のバリアメタル膜を除去する。そして、粘着剤層115をシリコン基板101の素子形成面から剥離することにより、支持体117が除去され、図5に示した半導体装置104が得られる。10

#### 【0123】

次に、図5に示した半導体装置104の効果を説明する。半導体装置102は、第一の実施形態に記載の半導体装置100(図1)の効果に加えて以下の効果を有する。

#### 【0124】

半導体装置104においては、シリコン基板101内の貫通電極135の側方にSiO<sub>2</sub>リング151が形成されている。SiO<sub>2</sub>の厚い壁を大径プラグ131の周囲に設けることにより、寄生容量を減少させることができる。よって、半導体装置の動作を高速化させることができる。20

#### 【0125】

また、SiO<sub>2</sub>リング151は、トランジスタ等の素子の形成前にシリコン基板101中に設けられる。このため、第二の実施形態の場合と同様に、SiO<sub>2</sub>リング151の形成による素子の信頼性の低下が抑制された構成となっている。

#### 【0126】

なお、半導体装置104では、大径プラグ131の側方にSiO<sub>2</sub>リング151を形成したが、リングの材料はその後の素子形成過程での加熱に対する耐性を有する絶縁材料であれば、SiO<sub>2</sub>以外の材料とすることもできる。また、SiO<sub>2</sub>リング151の断面形状は、閉じていれば円筒環には限定されず、たとえば断面が矩形の環状の筒状体としてもよい。30

#### 【0127】

また、本実施形態に係る半導体装置104においても、第二の実施形態に記載の半導体装置102(図3)の場合と同様に、SiO<sub>2</sub>リング151を大径プラグ131の側方に加え、ウエハ155のダイシングライン157の近傍に形成しておくことにより、ダイシング特性にすぐれた構成とすることができます。

#### 【0128】

以上、発明の好適な実施形態を説明した。しかし、本発明は上述の実施形態に限定されず、当業者が本発明の範囲内で上述の実施形態を変形可能なことはもちろんである。

#### 【0129】

たとえば、以上の実施形態においては、半導体基板としてシリコン基板を用いたが、GaAs基板等の化合物半導体基板としてもよい。40

#### 【0130】

また、以上の実施形態においては、小径プラグ119の材料としてWを用いたが、導電率の高い他の材料を用いてもよい。たとえば、Cu、Al、Ni、ポリシリコンなどの材料を用いてもよい。

#### 【0131】

また、以上の実施形態においては、貫通電極135を構成する小径プラグ119が第一配線層絶縁膜113に接続される構成について説明したが、第二配線層以上の第一配線層絶縁膜113より上部の下層配線層に接続される構成としてもよい。

10

20

30

40

50

## 【0132】

また、以上の実施形態においては、一つの大径プラグ131の上面に一つの小径プラグ119が貫入した構成を例に説明したが、図7(c)に示したように、一つの大径プラグ131に二つ以上の小径プラグ119が貫入した構成とすることもできる。こうすることにより、アンカー効果をさらに確実に発揮させることができる。よって、小径プラグ119と大径プラグ131との電気的接触をさらに確実なものとすることができます。

## 【0133】

また、貫通電極135を構成する小径プラグ119および大径プラグ131がともに円柱である場合を例に説明したが、二つのプラグの断面積が異なっていれば、径の異なる円柱を組み合わせる様には限られない。小径プラグ119または大径プラグ131を柱状体とすることができる、たとえばその形状は、円柱、楕円柱、または角柱等の上面および底面の面積が略等しい形状であってもよい。また、上面に先端部を有しない円錐台、楕円錐台、または角錐台の形状であってもよい。また、柱状体は、一方向に延在するストライプ状であってもよい。

10

## 【0134】

また、以上の実施形態において、大径プラグ131の上面がシリコン基板101の素子形成面の下方に位置している構成とすることもできるし、大径プラグ131がシリコン基板101の裏面から素子形成面の近傍にわたって設けられている構成とすることもできる。また、大径プラグ131の上面が多少シリコン基板101の素子形成面から突出しても、大径プラグ131が上面で絶縁された構成であればよい。

20

## 【0135】

また、以上の実施形態においては、粘着剤層115および支持体117をシリコン基板101の素子形成面から剥離したが、必要に応じて剥離させずにそのまま半導体装置の一部としてもよい。

20

## 【図面の簡単な説明】

## 【0136】

【図1】本実施形態に係る半導体装置の構成を模式的に示す断面図である。

【図2】図1の半導体装置の製造工程を説明する断面図である。

【図3】本実施形態に係る半導体装置の構成を模式的に示す断面図である。

30

【図4】図3の半導体装置の製造工程を説明する断面図である。

【図5】本実施形態に係る半導体装置の構成を模式的に示す断面図である。

【図6】図5の半導体装置の製造工程を説明する断面図である。

【図7】貫通電極の構成を模式的に示す図である。

【図8】貫通電極の構成を模式的に示す断面図である。

【図9】本実施形態に係る半導体装置の製造方法を説明する平面図である。

【図10】本実施形態に係る半導体装置の構成を模式的に示す断面図である。

【図11】本実施形態に係る半導体装置の構成を模式的に示す断面図である。

【図12】本実施形態に係る貫通電極の構成を模式的に示す断面図である。

## 【符号の説明】

## 【0137】

40

100 半導体装置

101 シリコン基板

102 半導体装置

103 素子分離膜

104 半導体装置

105 拡散層

107 ゲート電極

109 エッチングストップ膜

112 配線用絶縁膜

113 第一配線層絶縁膜

50

|       |                      |    |

|-------|----------------------|----|

| 1 1 4 | プラグ用絶縁膜              |    |

| 1 1 5 | 粘着剤層                 |    |

| 1 1 7 | 支持体                  |    |

| 1 1 9 | 小径プラグ                |    |

| 1 2 1 | 第一配線                 |    |

| 1 2 2 | 接続プラグ                |    |

| 1 2 3 | 接続プラグ                |    |

| 1 2 5 | パッド                  |    |

| 1 2 7 | バンプ                  |    |

| 1 2 9 | 電着絶縁膜                | 10 |

| 1 3 1 | 大径プラグ                |    |

| 1 3 3 | めつき膜                 |    |

| 1 3 5 | 貫通電極                 |    |

| 1 3 7 | SiN膜                 |    |

| 1 3 9 | 開口部                  |    |

| 1 4 1 | 突出部                  |    |

| 1 4 2 | 突出部                  |    |

| 1 4 3 | SiN膜                 |    |

| 1 4 5 | SiN膜                 |    |

| 1 4 7 | SiO <sub>2</sub> 膜   | 20 |

| 1 4 9 | SiN膜                 |    |

| 1 5 1 | SiO <sub>2</sub> リング |    |

| 1 5 3 | 配線                   |    |

| 1 5 4 | 配線                   |    |

| 1 5 5 | ウエハ                  |    |

| 1 5 7 | ダイシングライン             |    |

| 1 5 9 | 貫通溝                  |    |

| 1 6 1 | 絶縁層                  |    |

| 1 6 3 | 絶縁層                  |    |

| 1 6 5 | 配線                   | 30 |

| 1 6 7 | 接続プラグ                |    |

| 1 6 9 | 配線                   |    |

| 1 7 1 | 接続プラグ                |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【 図 9 】

(b)

【 図 1 0 】

【 図 1 1 】

【図12】

(a)

(b)