(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7033069号

(P7033069)

(45)発行日 令和4年3月9日(2022.3.9)

(24)登録日 令和4年3月1日(2022.3.1)

(51)国際特許分類

|        |                 |        |       |         |

|--------|-----------------|--------|-------|---------|

| H 01 L | 21/60 (2006.01) | H 01 L | 21/92 | 6 0 2 K |

| H 05 K | 3/34 (2006.01)  | H 05 K | 3/34  | 5 0 1 E |

| H 05 K | 3/00 (2006.01)  | H 01 L | 21/92 | 6 0 2 J |

| H 05 K | 1/18 (2006.01)  | H 05 K | 3/00  | X       |

|        |                 | H 05 K | 1/18  | L       |

請求項の数 15 (全19頁)

(21)出願番号 特願2018-538737(P2018-538737)

(86)(22)出願日 平成28年12月21日(2016.12.21)

(65)公表番号 特表2019-511832(P2019-511832

A)

(43)公表日 平成31年4月25日(2019.4.25)

(86)国際出願番号 PCT/US2016/068033

(87)国際公開番号 WO2017/136061

(87)国際公開日 平成29年8月10日(2017.8.10)

審査請求日 令和1年12月4日(2019.12.4)

(31)優先権主張番号 62/289,636

(32)優先日 平成28年2月1日(2016.2.1)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 15/077,869

(32)優先日 平成28年3月22日(2016.3.22)

最終頁に続く

(73)特許権者 507364838

クアルコム, インコーポレイテッド

アメリカ合衆国 カリフォルニア 9 2 1

2 1 サン デイエゴ モアハウス ドライ

ブ 5 7 7 5

(74)代理人 100108453

弁理士 村山 靖彦

(74)代理人 100163522

弁理士 黒田 晋平

(72)発明者 デイク・ダニエル・キム

アメリカ合衆国・カリフォルニア・ 9 2

1 2 1 - 1 7 1 4 · サン・ディエゴ・モ

アハウス・ドライヴ・ 5 7 7 5

(72)発明者 マリオ・フランシスコ・ヴェレス

アメリカ合衆国・カリフォルニア・ 9 2

最終頁に続く

(54)【発明の名称】 オープンパッセーションボールグリッドアレイパッド

## (57)【特許請求の範囲】

## 【請求項1】

導電バンプアセンブリを製作するための方法であって、受動基板上に直接第3のパッセーション層を堆積させるステップと、前記第3のパッセーション層上に直接第2のパッセーション層を堆積させるステップと、前記第2のパッセーション層上に直接第1のパッセーション層を堆積させるステップと、前記導電バンプアセンブリを支持する前記受動基板の縁部に複数の導電バンプパッドを製作するステップであって、前記第2のパッセーション層上に前記複数の導電バンプパッドを形成し、前記導電バンプパッドの上面が前記第2のパッセーション層の上面よりも高い、ステップと、前記複数の導電バンプパッドをそれぞれ取り囲む前記第1のパッセーション層の複数の開口部を、前記受動基板の前記縁部に近接する前記複数の導電バンプパッドを取り囲む第2のパッセーション層開口部と組み合わせ、それによって、前記第1のパッセーション層が前記受動基板の前記縁部に近接する前記導電バンプパッドを部分的にのみ取り囲む、ステップと、前記第1のパッセーション層および前記第2のパッセーション層をマスクして、前記組み合わされた第1および第2のパッセーション層開口部を形成するステップと、前記導電バンプパッド上に導電材料を堆積させるステップと、を含むことを特徴とする、

方法。

**【請求項 2】**

前記複数の導電バンプパッドを製作する前記ステップは、

前記導電バンプパッドと前記受動基板の前記縁部におけるダイシングストリートの一部との間の第1のパッシベーション層プロックを除去するステップと、

前記受動基板の前記縁部における前記ダイシングストリートの前記一部に近接する第2のパッシベーション層上に前記導電バンプパッドを配置するステップとを含む、請求項1に記載の方法。

**【請求項 3】**

非はんだマスク定義（NSMD）プロセスを使用して第2のパッシベーション層上にランディングパターンを画定するステップと、

前記ランディングパターン内に配線工程（B E O L）導電相互接続層を前記導電バンプパッドとして堆積させるステップとをさらに含む、請求項2に記載の方法。

**【請求項 4】**

前記導電材料を堆積させるステップは、前記導電バンプパッド上にはんだ材料をはんだボールとして堆積させるステップを含む、請求項1に記載の方法。

**【請求項 5】**

前記導電バンプアセンブリを無線周波数（RF）フロントエンドモジュールのプリント回路板（PCB）上に組み立てるステップをさらに含む、請求項1に記載の方法。

**【請求項 6】**

受動基板と、

前記受動基板によって支持され、第1のパッシベーション層内の複数の開口部によってそれぞれ取り囲まれた複数の導電バンプパッドと、

前記第1のパッシベーション層を支持し、前記受動基板を露出させ前記第1のパッシベーション層内の前記開口部と組み合わされる開口部を有し、それによって、前記第1のパッシベーション層が前記受動基板の縁部に近接する前記導電バンプパッドを部分的にのみ取り囲む第2のパッシベーション層と、

前記導電バンプパッド上の組立てのための手段とを備え、

前記複数の導電バンプパッドが、前記第2のパッシベーション層内の前記開口部によって取り囲まれ、

前記導電バンプパッドの上面が前記第2のパッシベーション層の上面よりも高いことを特徴とする導電バンプアセンブリ。

**【請求項 7】**

前記導電バンプパッドは、非はんだマスク定義（NSMD）パッドを含む、請求項6に記載の導電バンプアセンブリ。

**【請求項 8】**

前記導電バンプパッドと前記受動基板の前記縁部との間の距離は約42.5ミクロンである、請求項6に記載の導電バンプアセンブリ。

**【請求項 9】**

前記受動基板の前記縁部は、ダイシングストリートの一部を含む、請求項6に記載の導電バンプアセンブリ。

**【請求項 10】**

前記導電バンプアセンブリは、ボールグリッドアレイ（BGA）アセンブリを含む、請求項6に記載の導電バンプアセンブリ。

**【請求項 11】**

前記組立て手段は、はんだボールを含む、請求項6に記載の導電バンプアセンブリ。

**【請求項 12】**

フィルタに組み込まれ、前記受動基板がガラス基板を含む、請求項6に記載の導電バンプアセンブリ。

**【請求項 13】**

10

20

30

40

50

前記フィルタは、ダイプレクサ、トリプレクサ、ローパスフィルタ、および／またはノッチフィルタを含む、請求項 1 2 に記載の導電バンプアセンブリ。

【請求項 1 4】

前記フィルタは、無線周波数 (R F) フロントエンドモジュールのプリント回路板 (P C B) 上に組み立てられる、請求項 1 2 に記載の導電バンプアセンブリ。

【請求項 1 5】

無線周波数 (R F) フロントエンドモジュールに組み込まれ、前記 R F フロントエンドモジュールが、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、携帯情報端末 (P D A)、固定ロケーションデータユニット、モバイル電話、およびポータブルコンピュータのうちの少なくとも 1 つに組み込まれる、請求項 6 に記載の導電バンプアセンブリ。

10

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

関連出願の相互参照

本出願は、2016年2月1日に出願された「OPEN-PASSIVATION BALL GRID ARRAY PADS」という名称の米国仮特許出願第 62/289,636 号に対する利益を米国特許法第 119 条 (e) の下に主張するものであり、この仮特許出願の開示全体は参考により本明細書に明確に組み込まれる。

【0 0 0 2】

20

本開示は、一般に集積回路 (I C) に関する。より詳細には、本開示は、オープンパッセーションボールグリッドアレイパッドに関する。

【背景技術】

【0 0 0 3】

集積回路 (I C) の半導体製作のプロセスフローは、基板 (F E O L) 工程、中間 (M O L) 工程、および配線 (B E O L) 工程を含んでもよい。基板工程は、ウエハ作製、絶縁、ウェル形成、ゲートパターニング、スペーサ、エクステンションおよびソース／ドレイン注入、シリサイド形成、ならびにデュアルストレスライナー形成を含んでもよい。中間工程は、ゲートコンタクト形成を含んでもよい。中間工程層は、半導体デバイストランジスタまたは他の能動デバイスに近接した中間工程コンタクト、ビア、または他の層を含む場合があるが、これらに限定されない。配線工程は、基板工程および中間工程中に作製された半導体デバイスを相互接続するための一連のウエハ処理ステップを含んでもよい。

30

【0 0 0 4】

現代の半導体チップ製品を首尾よく製作するには、採用される材料とプロセスとの間の相互作用が必要である。具体的には、配線工程における半導体製作のための導電性材料めつきの形成は、プロセスフローのうちの次第に困難になっている部分である。これは、小さなフィーチャサイズを維持するという観点において特に当てはまる。受動オンガラス (P O G) 技術でも、小さなフィーチャサイズを維持することに関する同じ問題があり、その技術では、インダクタおよびキャパシタのような高性能構成要素が、同じく損失が非常に少ない場合がある絶縁性の高い基板上に構築される。

40

【0 0 0 5】

受動オンガラスデバイスは、モバイル無線周波数 (R F) チップ構成 (たとえば、モバイル R F トランシーバ) を製作する際に広く使用されている表面実装技術または多層セラミックチップのような他の技術より優れた種々の利点を有する高性能インダクタ構成要素およびキャパシタ構成要素を含む。モバイル R F トランシーバの設計については、コストおよび電力消費量の問題に起因するディープサブミクロンプロセスノードへの移行によって複雑さが増している。間隔の問題もモバイル R F トランシーバ設計ディープサブミクロンプロセスノードに影響を与える。たとえば、モバイル R F トランシーバの製作には、無駄になる空間を占有しコストの増大を伴うダイ領域境界におけるダミー領域が含まれることがある。

50

**【発明の概要】****【課題を解決するための手段】****【0006】**

導電バンプアセンブリは、受動基板を含んでもよい。導電バンプアセンブリはまた、受動基板によって支持され、第1のパッシベーション層開口部によって取り囲まれた導電バンプパッドを含んでもよい。導電バンプアセンブリは、受動基板上に第2のパッシベーション層開口部をさらに含んでもよい。第2のパッシベーション層開口部は、受動基板の縁部に近接する導電バンプパッドを取り囲む第1のパッシベーション層開口部と組み合わされてもよい。導電バンプアセンブリはまた、導電バンプパッド上に導電バンプを含んでもよい。

10

**【0007】**

導電バンプアセンブリを製作するための方法は、導電バンプアセンブリを支持する受動基板の縁部に導電バンプパッドを製作するステップを含んでもよい。この方法はまた、導電バンプパッドを取り囲む第1のパッシベーション層開口部を第2のパッシベーション層開口部と組み合わせるステップを含んでもよい。第2のパッシベーション層開口部は、受動基板の縁部に近接する導電バンプパッドを取り囲んでもよい。この方法は、導電バンプパッドの上に導電材料を堆積させるステップをさらに含んでもよい。

**【0008】**

導電性バンプアセンブリは、受動基板を含んでもよい。導電バンプアセンブリはまた、受動基板によって支持され、第1のパッシベーション層開口部によって取り囲まれた導電バンプパッドを含んでもよい。導電バンプアセンブリは、受動基板上に第2のパッシベーション層開口部をさらに含んでもよい。第2のパッシベーション層開口部は、受動基板の縁部に近接する導電バンプパッドを取り囲む第1のパッシベーション層開口部と組み合わされてもよい。導電バンプアセンブリはまた、導電バンプパッド上に組立てのための手段を含んでもよい。

20

**【0009】**

上記では、後続の詳細な説明をより良く理解することができるよう、本開示の特徴および技術的利点について、かなり大まかに概説してきた。本開示の追加の特徴および利点について以下において説明する。本開示が、本開示と同じ目的を果たすための他の構造を変更または設計するための基礎として容易に利用できることを、当業者は理解されたい。そのような同等な構成が、添付の特許請求の範囲に記載されるような本開示の教示から逸脱しないことも、当業者には理解されたい。本開示の構成と動作方法の両方に関して本開示の特徴になると考えられる新規の特徴が、さらなる目的および利点とともに、以下の説明を添付の図と併せて検討することからより良く理解されるであろう。しかしながら、図の各々が、例示および説明のために提供されるにすぎず、本開示の範囲を定めるものではないことは明確に理解されたい。

30

**【0010】**

本開示をより完全に理解できるように、ここで、添付の図面と併せて以下の説明を参照する。

40

**【図面の簡単な説明】****【0011】**

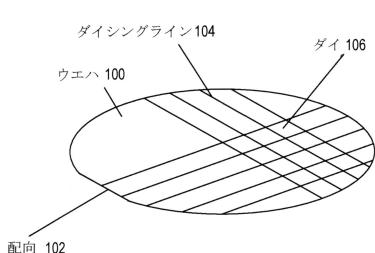

【図1】本開示の一態様における半導体ウエハの斜視図である。

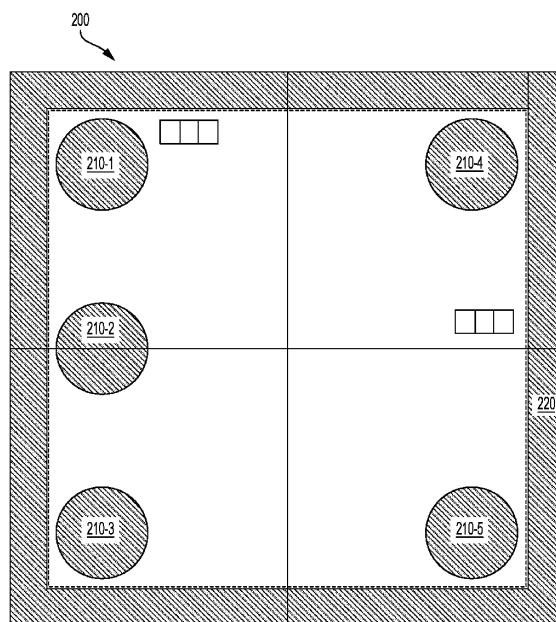

【図2A】ウエハ上に受動オンガラスデバイスを製作した後のウエハのガラスダイを示す図である。

【図2B】図2Aのガラスダイの角部の拡大図である。

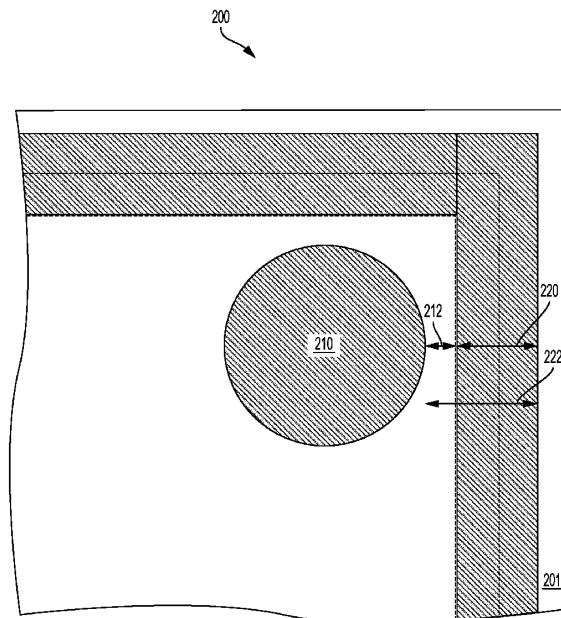

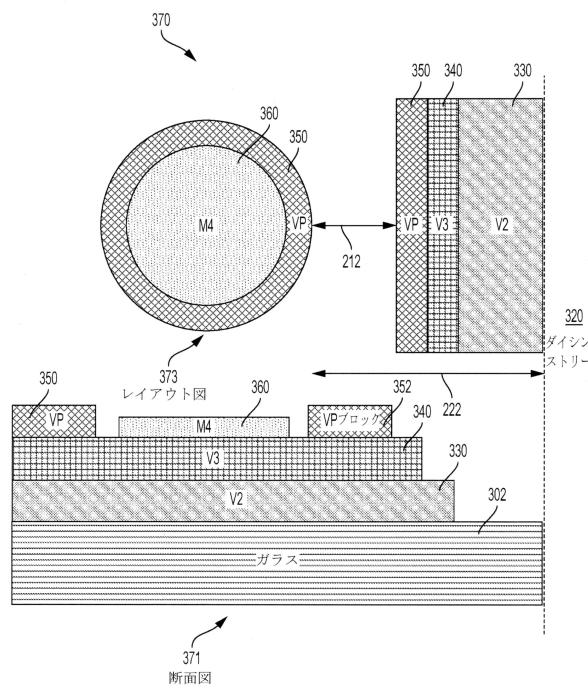

【図3A】本開示の一態様によるオープンパッシベーション導電パッドを含む導電バンプアセンブリのレイアウト図および断面図である。

【図3B】図2Aおよび図2Bに示すガラスダイの導電バンプアセンブリの断面図およびレイアウト図である。

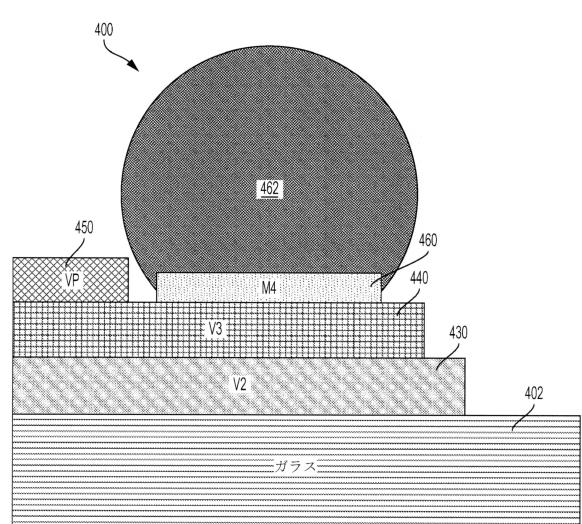

【図4A】本開示の一態様によるオープンパッシベーション導電バンプパッドを含む導電

50

バンプアセンブリの断面図である。

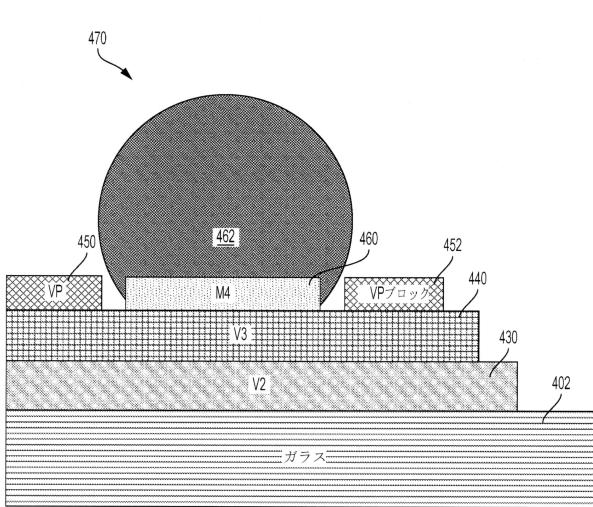

【図4B】図3Bに示す導電バンプアセンブリのさらなる断面図である。

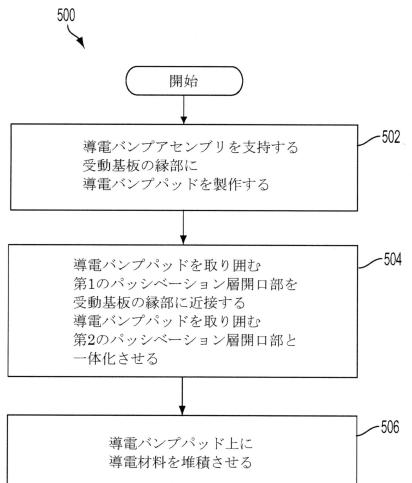

【図5】本開示の態様によるオープンパッシベーション導電バンプパッドを含む導電バンプアセンブリを構築する方法を示すプロセスフロー図である。

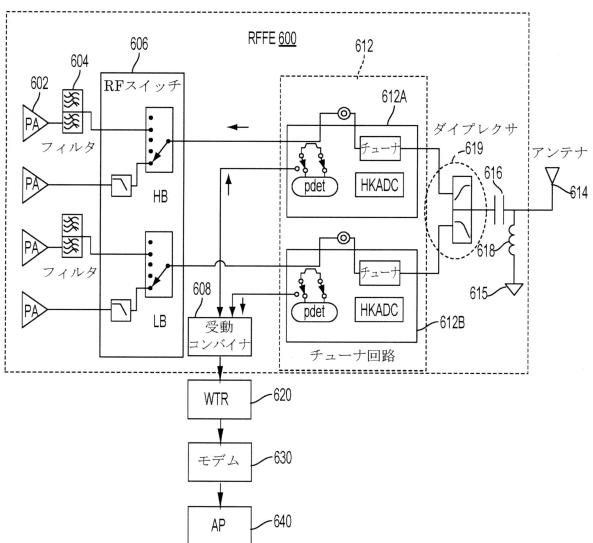

【図6】本開示の一態様による、ダイプレクサを使用する無線周波数（RF）フロントエンド（RFFE）モジュールの概略図である。

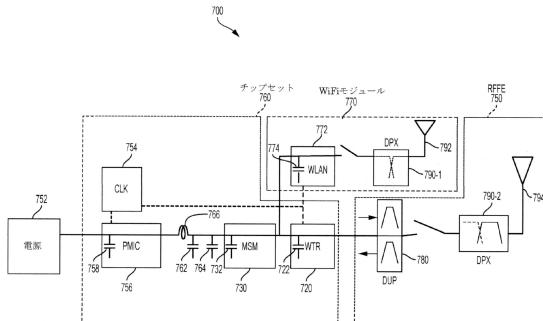

【図7】本開示の態様による、チップセット用のダイプレクサを使用してキャリアアグリゲーションを実現するWi-Fiモジュールおよび無線周波数（RF）フロントエンド（RFFE）モジュールの概略図である。

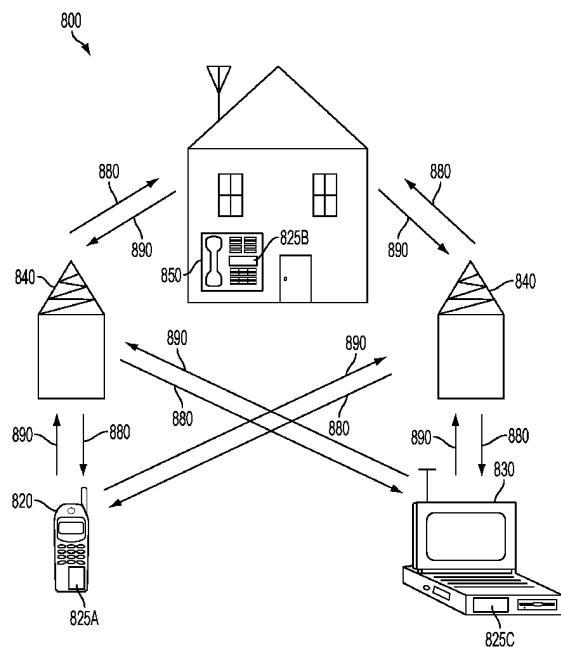

【図8】本開示の一構成が有利に採用される場合がある例示的なワイヤレス通信システムを示すブロック図である。

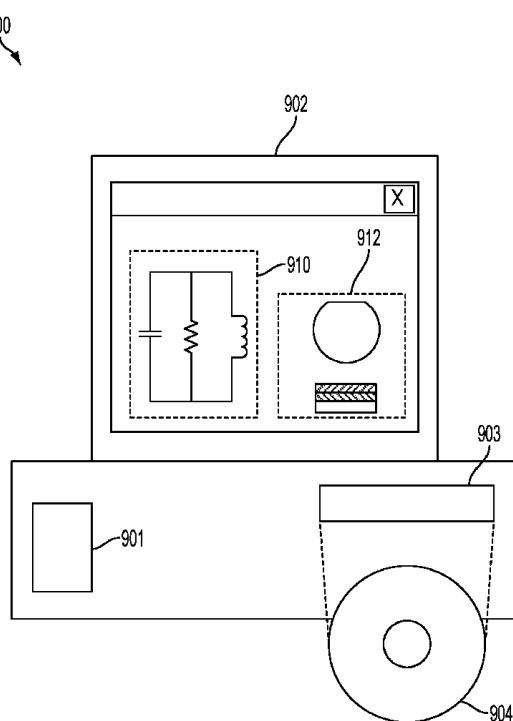

【図9】一構成による、半導体構成要素の回路設計、レイアウト設計、および論理設計に使用される、設計用ワークステーションを示すブロック図である。

【発明を実施するための形態】

【0012】

添付の図面に関して以下に記載する詳細な説明は、様々な構成について説明するものであり、本明細書で説明する概念が実践されてもよい唯一の構成を表すものではない。詳細な説明は、様々な概念を完全に理解できるようにすることを目的とした具体的な詳細を含む。しかしながら、これらの概念がこれらの具体的な詳細なしに実践されてもよいことは、当業者には明らかであろう。場合によっては、そのような概念を曖昧にするのを回避するために、よく知られている構造および構成要素がブロック図の形態で示される。本明細書において説明されるときに、「および／または」という用語の使用は、「包含的論理和」を表すことが意図されており、「または」という用語の使用は、「排他的論理和」を表すことが意図されている。

【0013】

現代の半導体チップ製品を首尾よく製作するには、採用される材料とプロセスとの間の相互作用が必要である。具体的には、配線工程（B E O L）プロセスにおける半導体製作のための導電材料めっきの形成は、プロセスフローにおいてますます困難になっている部分である。これは、小さなフィーチャサイズを維持するという観点において特に当てはまる。小さなフィーチャサイズを維持することに関する同じ課題が受動オンガラス（POG）技術にも当てはまり、その技術では、インダクタおよびキャパシタのような高性能構成要素が、同じく損失が非常に少なくなる場合がある絶縁性の高い基板上に構築される。

【0014】

受動オンガラスデバイスは、モバイル無線周波数（RF）チップ構成（たとえば、モバイルR Fトランシーバ）の製作において通常使用される表面実装技術または多層セラミックチップのような、他の技術より優れた種々の利点を有する高性能インダクタ構成要素およびキャパシタ構成要素を含む。モバイルR Fトランシーバの設計については、コストおよび電力消費量の問題に起因するディープサブミクロンプロセスノードへの移行によって複雑さが増している。間隔の問題もモバイルR Fトランシーバ設計ディープサブミクロンプロセスノードに影響を与える。たとえば、モバイルR Fトランシーバの製作には、無駄になる空間を占有しコストの増大を伴うダイ領域境界におけるダミー領域が含まれることがある。

【0015】

本開示の様々な態様は、オープンパッシベーションボールグリッドアレイパッドに関する技法を提供する。オープンパッシベーションボールグリッドアレイパッドの半導体製作のためのプロセスフローは、基板工程（F E O L）プロセス、中間工程（M O L）プロセス、および配線工程（B E O L）プロセスを含んでもよい。「層」という用語は、膜を含み、別段述べられていない限り、垂直厚または水平厚を示すものと解釈されるべきではないことが理解されよう。本明細書において説明するように、「基板」という用語は、ダイシングされたウエハの基板を指す場合があるか、または、ダイシングされていないウエハの

10

20

30

40

50

基板を指す場合がある。同様に、チップおよびダイという用語は、入れ換えられると信じることが難しくない限り、互換的に使用することができる。

【 0 0 1 6 】

本明細書で説明するように、配線工程相互接続層は、集積回路の基板工程能動デバイスに電気的に結合するための導電相互接続層（たとえば、金属1（M1）、金属2（M2）、金属3（M3）、金属4（M4）など）を指すことがある。配線工程相互接続層は、たとえば、集積回路の酸化物拡散（OD）層にM1を接続するために中間工程相互接続層に電気的に結合してもよい。配線工程第1ビア（V2）は、配線工程相互接続層のM3または他の金属にM2を接続してもよい。

【 0 0 1 7 】

本開示の様々な態様は、コストを削減するためにダイ領域境界におけるダミー領域を縮小するための技法を提供する。一般に、ウエハ上への集積回路の製作が完了した後、ウエハはダイシングライン（たとえば、ダイシングストリート）に沿って分割される。ダイシングラインは、ウエハをどこでいくつかの部片に分割または分離すべきであるかを示す。ダイシングラインは、ウエハ上に製作された様々な集積回路の輪郭を画定してもよい。ダイシングラインが画定された後、ウエハは、いくつかの部片に切断されるかまたはその他の方法によって分離されダイが形成される。このプロセスの後、ダイ領域境界は、ダイシングソーブレード（Kerf）によって形成されるグループおよび最終パッシベーション層（VP）間に応じた非機能的境界領域を含んでもよい。この例では、非機能的境界領域の幅によって、物理ダイ領域の顕著な割合を占めることがあるダミー領域が生じる。

10

【 0 0 1 8 】

本開示の一態様では、オープンパッシベーションボールグリッドアレイパッドを含む導電バンプアセンブリは、ダイ領域境界におけるダミー領域を縮小するのを可能にする。導電バンプアセンブリは、受動基板によって支持され、第1のパッシベーション層開口部によって取り囲まれた導電バンプパッドを含んでもよい。導電バンプアセンブリはまた、受動基板上の第2のパッシベーション層開口部であって、受動基板の縁部に近接する導電バンプパッドを取り囲む第1のパッシベーション層開口部と組み合わされた第2のパッシベーション層開口部を含んでもよい。この構成では、導電バンプパッドとダイシングストリートとの間の第1のパッシベーション層プロックが、導電バンプアセンブリを支持する受動基板の縁部において除去される。除去された後、導電バンプパッドを取り囲む第1のパッシベーション層開口部が、受動基板の縁部におけるダイシングストリートに近接する導電バンプパッドを取り囲む第2のパッシベーション層開口部と組み合わされる。

20

【 0 0 1 9 】

図1は、本開示の一態様におけるウエハの斜視図を示す。ウエハ100は、半導体ウエハであってもよく、あるいはウエハ100の表面上に材料の1つまたは複数の層を有する基板材料であってもよい。ウエハ100は、ガリウムヒ素（GaAs）または窒化ガリウム（GaN）などの複合材料、インジウムガリウムヒ素（InGaAs）などの3元材料、4元材料、シリコン、石英、ガラス、あるいは基板材料とすることができる任意の材料であってもよい。多くの材料は本質的に結晶性を有する場合があるが、多結晶材料またはアモルファス材料がウエハ100に使用されてもよい。たとえば、基板用の様々なオプションには、ガラス基板、半導体基板、コア積層基板、コアレス基板、プリント回路板（PCB）基板、または他の同様の基板が含まれる。

30

【 0 0 2 0 】

ウエハ100、またはウエハ100に結合された層は、ウエハ100内またはウエハ100上に様々な種類の電子デバイスを形成するのを可能にする材料を供給されてもよい。さらに、ウエハ100は、ウエハ100の結晶配向を示す配向102を有してもよい。配向102は、図1に示すようにウエハ100の平坦な縁部であっても、あるいはウエハ100の結晶配向を示すための切欠きまたは他の表示であってもよい。配向102は、半導体ウエハを仮定すると、ウエハ100内の結晶格子の平面に関するミラー指数を示す場合がある。

40

50

## 【0021】

ウエハ100が必要に応じて処理されると、ウエハ100は、ダイシングライン104に沿って分割される。たとえば、ウエハ100上への集積回路の製作を完了した後、ウエハ100はダイシングライン104に沿って分割され、ダイシングライン104は本明細書では「ダイシングストリート」と呼ばれる場合がある。ダイシングライン104は、ウエハ100がどこで分けられるまたは分割されるべきかを示す。ダイシングライン104は、ウエハ100上に製作された様々な集積回路の輪郭を画定してもよい。

## 【0022】

ダイシングライン104が画定された後、ウエハ100は、いくつかの部片として切断されるかまたはその他の方法によって分離されダイ106が形成される。各ダイ106は、多数のデバイスを有する集積回路であってもよく、または単一の電子デバイスであってもよい。ダイ106の物理的サイズは、チップまたは半導体チップと呼ばれる場合もあり、ウエハ100を特定のサイズに分離する能力およびダイ106が含むように設計される個々のデバイスの数に少なくとも部分的に依存する。

10

## 【0023】

ウエハ100が1つまたは複数のダイ106に分離された後、ダイ106はパッケージ内に実装され、ダイ106上に製作されたデバイスおよび/または集積回路の取り扱いを可能にしてもよい。パッケージには、シングルインラインパッケージ、デュアルインラインパッケージ、マザーボードパッケージ、フリップチップパッケージ、インジウムドット/バンプパッケージ、またはダイ106の取り扱いを可能にする他の種類のデバイスを含めてもよい。ダイ106は、ダイ106を別個のパッケージに実装されることなくワイヤボンディング、プロープ、または他の接続部を通して直接取り扱われてもよい。

20

## 【0024】

インダクタ、およびキャパシタなどの他の受動デバイスが、ダイ上に形成されてもよい。これらの構成要素は、受動オンガラス技術を使用する、たとえば、図6および図7に示されているような無線周波数(RF)フロントエンドモジュールを形成する際に有用なフィルタ、ダイプレクサ、トリプレクサ、ローパスフィルタ、および/またはノッチフィルタ、あるいは他の同様の受動回路素子を形成するために使用されてもよい。

## 【0025】

図2Aは、ウエハ201上に受動オンガラスデバイスを製作した後のウエハ201(図2B)のガラスダイ(200)を示す図である。受動オンガラスデバイスは、モバイル無線周波数(RF)チップ構成(たとえば、モバイルRFトランシーバ)の製作において通常使用される表面実装技術または多層セラミックチップのような、他の技術より優れた種々の利点を有する高性能インダクタ構成要素およびキャパシタ構成要素を含む。この構成では、ガラスダイ200は、ボールグリッドアレイ(BGA)アセンブリを配置するのを可能にするためにパッシベーション開口部210(210-1、210-2、210-3、210-4、および210-5)を含む。この例では、ガラスダイは、ダイシングラインに沿ってダイシングされる前であり、ガラスダイがダイシングストリート220によって取り囲まれている状態が示されている。ダイシングストリート220は、ウエハ201をどこでいくつかの部片に分割または分離すべきであるかを示すダイシングラインから構成される。ダイシングストリート220が画定された後、ウエハ201は、いくつかの部片に切断されるかまたはその他の方法によって分離されガラスダイ200が形成される。残念ながら、パッシベーション開口部210の配置によって、図2Bにさらに示すように、ガラスダイ200のダイ領域境界にダミー領域が生じる。

30

## 【0026】

図2Bは、図2Aのガラスダイ200の角部の拡大図である。受動オンガラスデバイスの製作は、非機能的境界領域222がガラスダイ200を取り囲むのでコストがかかる。たとえば、ガラスダイ200の物理的ダイサイズが $2.25\text{ mm}^2$ であると仮定すると、ダイ領域境界は、ダイシングソープレード(Kerf)によって形成されるグループ(たとえば、ダイシングストリート220の一部)および最終パッシベーション層(VP)間隔

40

50

212に応じた非機能的境界領域を含む場合がある。この例では、非機能的境界領域222の幅は0.78mm<sup>2</sup>であり、それによって、ガラスダイ200の物理的ダイ領域の約35%であるダミー領域が生じる。この構成では、ガラスダイの縁部におけるパッシベーション開口部とダイシングストリート220との間の距離は約85ミクロンである。

#### 【0027】

図3Aは、本開示の一態様によるオープンパッシベーション導電バンプパッドを含む導電バンプアセンブリの断面図301およびレイアウト図303である。オープンパッシベーション導電バンプパッドは、表面実装技術(SMT)を使用してRFフロントエンドモジュール内に受動オンガラスデバイスを組み込むのを可能にする。SMT組立てプロセスは、ウエハ(たとえば、プリント回路板(PCB))上にはんだペーストをスクリーン印刷することを含んでもよい。はんだペースト印刷に続いて、各構成要素がウエハ上に配置される。構成要素の配置が完了した後、はんだリフローが行われ、その後フラックスが除去される。さらに、SMT組立てプロセスは一般に、表面実装パッケージ用の2種類のランドパターンを含む。第1の種類のランドパターンは、非はんだマスク定義(NSMD)パッドである。これらのパッドは一般に、金属パッドよりも幅の広いマスク開口部を有する。第2の種類のランドパターンは、はんだマスク定義(SMD)パッドである。これらのパッドは、金属パッドと比較して縮小されたはんだマスク開口部を有する。

10

#### 【0028】

図3Aの断面図301に示すように、導電バンプアセンブリ300は、複数のパッシベーション(たとえば、誘電性)層および導電バンプパッド360を支持するガラス基板302を含む。断面図301に示す導電バンプアセンブリ300は、図2Bに示す図2Aのガラスダイ200の角部の分解図と類似する場合がある。しかし、この構成では、図2Bに示すVP間隔212を除去することによって導電バンプパッド360がダイシングストリート320と結合される。その結果、レイアウト図303に示す非機能的境界領域322は、図2Bに示す非機能的境界領域222に対して縮小される。

20

#### 【0029】

断面図301に示すように、第1のパッシベーション層350(VP)は、第3のパッシベーション層330(V2)によって支持される第2のパッシベーション層340(V3)によって支持される。レイアウト図303に示すように、第2のパッシベーション層340(V3)の第2のパッシベーション層開口部は、ダイシングストリート320に近接する導電バンプパッド360を取り囲む第1のパッシベーション層350(VP)の第1のパッシベーション層開口部と組み合わされる。導電バンプパッド360は、第2のパッシベーション層340上に配線工程(BEOL)相互接続層(たとえば、金属4(M4))を堆積させることによって形成されてもよい。導電バンプパッド360は、非はんだマスク定義(NSMD)パッドであってもよい。3つのパッシベーション層として示されているが、導電バンプアセンブリは、この構成に限定されず、ウエハ製作のそれぞれに異なる段階の間に堆積される複数のパッシベーション層を含む任意の構成を含んでもよい。パッシベーション層は、ポリイミドまたは他の同様の誘電材料から構成されてもよい。

30

#### 【0030】

図3Bは、図2Aおよび図2Bに示すガラスダイ200の導電バンプアセンブリの断面図371およびレイアウト図373を示す。図3Bの断面図371に示すように、導電バンプアセンブリ370は、複数のパッシベーション(たとえば、誘電)層および導電バンプパッド360を支持するガラス基板302を含む。断面図301に示す導電バンプアセンブリ300は、図2Bに示す図2Aのガラスダイ200の角部の分解図をさらに示す。この構成では、導電バンプパッド360は、レイアウト図373に示すVP間隔212(たとえば、42.5ミクロン)に応じた第1のパッシベーション層350のVPブロック352によってダイシングストリート320からずれている。

40

#### 【0031】

断面図371に示すように、VPブロック352は、導電バンプパッド360とダイシングストリート320との間に配置され、レイアウト図373に示す非機能境界領域222

50

を生じさせる。特に、V P ブロック 3 5 2 は、レイアウト図 3 7 3 に示す V P 間隔 2 1 2 によって測定されるダミー領域をガラスダイ 2 0 0 の周囲に生じさせる。したがって、図 3 B のレイアウト図 3 7 3 に示す非機能的境界領域 2 2 2 (たとえば、8 5 ミクロン) は、図 3 A に示す非機能的境界領域 3 2 2 (たとえば、4 2 . 5 ミクロン) と比較して大きい。本開示の態様では、図 3 A に示すように、V P ブロック 3 5 2 を除去し、導電バンプパッド 3 6 0 をダイシングストリート 3 2 0 と結合することによって、V P 間隔 2 1 2 の幅に応じて非機能境界領域 3 2 2 が縮小される。

#### 【 0 0 3 2 】

図 4 A は、本開示の一態様によるオープンパッシベーション導電パッドを含む導電バンプアセンブリの断面図を示す。典型的には、導電バンプアセンブリ 4 0 0 はまた、パッシベーション (たとえば、誘電) 層および導電バンプパッド 4 6 0 を支持するガラス基板 4 0 2 を含む。導電バンプアセンブリ 4 0 0 は、図 3 A に示す導電バンプアセンブリ 3 0 0 と同様であってもよい。しかし、この構成では、導電バンプアセンブリ 4 0 0 を完成するために導電バンプパッド 4 6 0 上に導電バンプ 4 6 2 が製作される。

10

#### 【 0 0 3 3 】

導電バンプアセンブリ 4 0 0 は、第 3 のパッシベーション層 4 3 0 (V 2) によって支持される第 2 のパッシベーション層 4 4 0 (V 3) によって支持される第 1 のパッシベーション層 4 5 0 (V P) を含む。この構成では、第 2 のパッシベーション層 4 4 0 (V 3) の第 2 のパッシベーション層開口部も、導電バンプパッド 4 6 0 を取り囲む第 1 のパッシベーション層 4 5 0 (V P) の第 1 のパッシベーション層開口部と組み合わされる。このプロセスでは、ダイシングストリート 3 2 0 (図 3 A) により近い導電バンプパッド 4 6 0 の位置を押すことによって、フットプリントが縮小された (たとえば、1 . 5 × 1 . 5 mm<sup>2</sup>) 導電バンプアセンブリ 4 0 0 が形成される。導電バンプアセンブリ 4 0 0 のフットプリントの縮小には、図 4 B に示すように V P ブロック 4 5 2 を除去することによってサイズを顕著に縮小する (たとえば、8 5 ミクロン) ことが含まれる。

20

#### 【 0 0 3 4 】

図 4 B は、図 3 B に示す導電バンプアセンブリの断面図をさらに示す。導電バンプアセンブリ 4 7 0 は、図 3 B に示す導電バンプアセンブリ 3 7 0 と同様であってもよく、ガラス基板 4 0 2 上の第 3 のパッシベーション層 4 3 0 (V 2) によって支持される第 2 のパッシベーション層 4 4 0 (V 3) によって支持される第 1 のパッシベーション層 4 5 0 (V P) を含む。しかし、この構成では、導電バンプアセンブリ 4 7 0 を完成するために導電バンプパッド 4 6 0 上に導電バンプ 4 6 2 が製作される。

30

#### 【 0 0 3 5 】

この構成では、導電バンプパッド 4 6 0 は、第 1 のパッシベーション層 4 5 0 の V P ブロック 4 5 2 によってダイシングストリート 3 2 0 (図 3 B) からずらされている。V P ブロック 4 5 2 によって消費される空間によって、導電バンプアセンブリ 4 7 0 は、図 4 A に示す導電バンプアセンブリ 4 0 0 の縮小されたフットプリント (たとえば、1 . 5 × 1 . 5 mm<sup>2</sup>) と比較して拡大されたフットプリント (たとえば、1 . 6 × 1 . 6 mm<sup>2</sup>) を有する。導電バンプアセンブリ 4 0 0 のフットプリントの縮小には、図 4 B に示すように V P ブロック 4 5 2 を除去することによってサイズを実質的に縮小する (たとえば、1 1 %) ことが含まれる。V P ブロック 4 5 2 を除去すると、導電バンプアセンブリ 4 7 0 の V P 間隔規則を回避することによって導電バンプアセンブリ 4 0 0 を製作することが可能になる。

40

#### 【 0 0 3 6 】

図 5 は、本開示の一態様によるオープンパッシベーション導電バンプパッドを含む導電バンプアセンブリを構築する方法 5 0 0 を示すプロセスフロー図である。ブロック 5 0 2 では、導電バンプアセンブリを支持する受動基板の縁部に導電バンプパッドを製作する。たとえば、図 3 A に示すように、導電バンプパッド 3 6 0 は、ガラス基板 3 0 2 の縁部におけるダイシングストリート 3 2 0 に近接する第 2 のパッシベーション層 3 4 0 上に配線工程 (B E O L) 導電相互接続層 (たとえば、金属 4 (M 4)) を堆積させることによって

50

形成されてもよい。この構成では、図3Bに示すV P ブロック352を除去することによって導電バンプパッド360の位置がダイシングストリート320まで押される。

#### 【0037】

再び図5を参照するとわかるように、ブロック504において、導電バンプパッドを取り囲む第1のパッシベーション層開口部を、受動基板の縁部に近接する導電バンプパッドを取り囲む第2のパッシベーション層開口部と組み合わせる。たとえば、図3Aのレイアウト図303に示すように、第2のパッシベーション層340(V3)の第2のパッシベーション層開口部が、ダイシングストリート320に近接する導電バンプパッド360を取り囲む第1のパッシベーション層350(VP)の第1のパッシベーション層開口部と組み合わされる。図5のブロック506において、導電バンプパッド上に導電材料を堆積させる。

10

#### 【0038】

図4Aに示すように、導電バンプアセンブリ400を完成するために導電バンプパッド460上に導電バンプ462が製作される。この構成では、導電バンプ462は、導電バンプパッド460上の導電バンプパッド上にはんだ材料を堆積させて導電バンプ462をはんだボールとして形成することによって製作される。このプロセスは、まず非はんだマスク定義(NSMD)プロセスを使用して第2のパッシベーション層440上にランディングパターンを画定することによって実行されてもよい。

#### 【0039】

本開示のさらなる一態様に従って、オープンパッシベーション導電バンプパッドを含む導電バンプアセンブリについて説明する。導電バンプアセンブリは、受動基板の縁部に近接する導電バンプパッドを取り囲む第1のパッシベーション層開口部と組み合わされた受動基板上の第2のパッシベーション層開口部を含む。導電バンプアセンブリはまた、導電バンプパッド上に組立てのための手段を含む。組立て手段は、図4Aに示される導電バンプ462であってもよい。別の態様では、前述の手段は、前述の手段によって列挙された機能を実行するように構成された任意の層、モジュール、または任意の装置であってもよい。

20

#### 【0040】

本開示の様々な態様は、ダイ領域境界におけるダミー領域を縮小して、RFフロントエンド適用例およびキャリアアグリゲーション適用例用の低コスト高性能RFデバイス技術プラットフォームを可能にするための技法を提供する。一般に、ウエハ上への集積回路の製作が完了した後、ウエハはダイシングライン(たとえば、ダイシングストリート)に沿って分割される。ダイシングラインは、ウエハをどこでいくつかの部片に分割または分離すべきであるかを示す。ダイシングラインは、ウエハ上に製作された様々な集積回路の輪郭を画定してもよい。ダイシングラインが画定された後、ウエハは、いくつかの部片に切断されるかまたはその他の方法によって分離されダイが形成される。このプロセスの後、ダイ領域境界は、ダイシングソーブレード(Kerf)によって形成されるグループおよび最終パッシベーション層(VP)間に応じた非機能的境界領域を含んでもよい。この例では、非機能的境界領域の幅によって、物理ダイ領域の顕著な割合を占めることがあるダミー領域が生じる。

30

#### 【0041】

本開示の一態様では、オープンパッシベーションボールグリッドアレイパッドを含む導電バンプアセンブリは、ダイ領域境界におけるダミー領域を縮小するのを可能にする。導電バンプアセンブリは、受動基板によって支持され、第1のパッシベーション層開口部によって取り囲まれた導電バンプパッドを含んでもよい。導電バンプアセンブリはまた、受動基板上の第2のパッシベーション層開口部であって、受動基板の縁部に近接する導電バンプパッドを取り囲む第1のパッシベーション層開口部と組み合わされた第2のパッシベーション層開口部を含んでもよい。この構成では、導電バンプパッドとダイシングストリートとの間の第1のパッシベーション層ブロックが、導電バンプアセンブリを支持する受動基板の縁部において除去される。除去された後、導電バンプパッドを取り囲む第1のパッシベーション層開口部が、受動基板の縁部におけるダイシングストリートに近接する導電

40

50

バンプパッドを取り囲む第2のパッシベーション層開口部と組み合わされる。

【0042】

図6は、本開示の一態様による、オープンパッシベーションボールグリッドアレイパッドを含む受動オンガラスデバイスを使用する無線周波数(RF)フロントエンド(RFFE)モジュール600の概略図である。RFフロントエンドモジュール600は、電力増幅器602と、デュプレクサ/フィルタ604と、無線周波数(RF)スイッチモジュール606とを含む。電力増幅器602は、信号を送信のための特定の電力レベルに増幅する。デュプレクサ/フィルタ604は、周波数、挿入損失、拒絶、または他の同様のパラメータを含む様々な異なるパラメータに応じて入出力信号をフィルタ処理する。さらに、RFスイッチモジュール606は、RFフロントエンドモジュール600の残りの部分に渡す入力信号の特定の部分を選択してもよい。

10

【0043】

RFフロントエンドモジュール600はまた、チューナ回路612(たとえば、第1のチューナ回路612Aおよび第2のチューナ回路612B)と、ダイプレクサ619と、キャパシタ616と、インダクタ618と、接地端子615と、アンテナ614とを含む。チューナ回路612(たとえば、第1のチューナ回路612Aおよび第2のチューナ回路612B)は、チューナ、ポータブルデータ入力端末(PDET)、およびハウスキーピングアナログデジタル変換器(HKADC)などの構成要素を含む。チューナ回路612は、アンテナ614のインピーダンス同調(たとえば、電圧定在波比(VSWR)最適化)を実行してもよい。RFフロントエンドモジュール600は、ワイヤレストランシーバ(WTR)620に結合された受動コンバイナ108も含む。受動コンバイナ608は、第1のチューナ回路612Aおよび第2のチューナ回路612Bからの検出された電力を組み合わせる。ワイヤレストランシーバ620は、受動コンバイナ108からの情報を処理し、この情報をモデム630(たとえば、移動局モデム(MSM))に提供する。モデム630は、デジタル信号をアプリケーションプロセッサ(AP)640に与える。

20

【0044】

図6に示すように、ダイプレクサ619は、チューナ回路612のチューナ構成要素とキャパシタ616、インダクタ618、およびアンテナ614との間に位置する。ダイプレクサ619は、アンテナ614とチューナ回路612との間に配置され、RFフロントエンドモジュール600から、ワイヤレストランシーバ620と、モデム630と、アプリケーションプロセッサ640とを含むチップセットへ高システム性能を提供することができる。ダイプレクサ619は、ハイバンド周波数とローバンド周波数の両方に対して周波数ドメイン多重化も実行する。ダイプレクサ619が入力信号に対してダイプレクサ619の周波数多重化機能を実行した後、ダイプレクサ619の出力が、キャパシタ616とインダクタ618とを含む任意のLC(インダクタ/キャパシタ)ネットワークに送られる。LCネットワークは、必要に応じて、アンテナ614の追加のインピーダンス整合構成要素を構成してよい。その場合、特定の周波数を有する信号がアンテナ614によって送受信される。単一のキャパシタおよびインダクタが示されているが、複数の構成要素も企図される。

30

【0045】

図7は、本開示の一態様による、キャリアアグリゲーションを実現するためのチップセット760用の、第1のダイプレクサ790-1を含むWi-Fiモジュール770および第2のダイプレクサ790-2を含むRFフロントエンドモジュール750の概略図700である。Wi-Fiモジュール770は、アンテナ792をワイヤレスローカルエリアネットワークモジュール(たとえば、WLANモジュール772)に通信可能に結合する第1のダイプレクサ790-1を含む。RFフロントエンドモジュール750は、アンテナ794をデュプレクサ780を介してワイヤレストランシーバ(WTR)720に通信可能に結合する第2のダイプレクサ790-2を含む。ワイヤレストランシーバ720およびWi-Fiモジュール770のWLANモジュール772は、電力管理集積回路(PMIC)756を介して電源752によって電力を供給されるモデム(MSM、たとえばベース

40

50

バンドモデム) 730に結合される。チップセット760は、信号完全性を実現するためにはキャパシタ762および764ならびにインダクタ766も含む。PMIC756、モデム730、ワイヤレストランシーバ720、およびWLANモジュール772の各々は、キャパシタ(たとえば、758、732、722、および774)を含み、クロック754に従って動作する。チップセット760における様々なインダクタ構成要素およびキャパシタ構成要素の形状および配置によって、各構成要素間の電磁結合が低減し得る。

#### 【0046】

図8は、本開示の一態様が有利に使用される場合がある例示的なワイヤレス通信システム800を示すブロック図である。説明を目的として、図8は、3つの遠隔ユニット820、830および850、ならびに2つの基地局840を示す。ワイヤレス通信システムがより多くの遠隔ユニットおよび基地局を有してもよいことが認識されよう。遠隔ユニット820、830、および850は、開示されたオープンパッショナリティボールグリッドアレイパッドを含むICデバイス825A、825C、および825Bを含む。基地局、スイッチングデバイス、およびネットワーク機器などの他のデバイスも、開示されたオープンパッショナリティボールグリッドアレイパッドを含む場合があることが認識されよう。図8は、基地局840から遠隔ユニット820、830、および850への順方向リンク信号880、ならびに、遠隔ユニット820、830、および850から基地局840への逆方向リンク信号890を示す。

#### 【0047】

図8では、遠隔ユニット820は、モバイル電話として示され、遠隔ユニット830は、ポータブルコンピュータとして示され、遠隔ユニット850は、ワイヤレスローカルループシステム内の固定位置遠隔ユニットとして示される。たとえば、遠隔ユニットは、モバイルフォン、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末(PDA)などのポータブルデータユニット、GPS対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、メーター読み取り機器などの固定位置データユニット、またはデータもしくはコンピュータ命令を記憶するもしくは取り出す他の通信デバイス、あるいはそれらの組合せであってよい。図8は本開示の態様による遠隔ユニットを示すが、本開示は、これらの示された例示的なユニットには限定されない。本開示の態様は、開示されたオープンパッショナリティボールグリッドアレイパッドを含む多くのデバイスにおいて適切に利用されることがある。

#### 【0048】

図9は、上記で開示されたオープンパッショナリティボールグリッドアレイパッドなどの半導体構成要素の回路設計、レイアウト設計、および論理設計に使用される、設計用ワークステーションを示すブロック図である。設計用ワークステーション900は、オペレーティングシステムソフトウェア、支援ファイル、およびCadenceまたはOrCADなどの設計用ソフトウェアを含むハードディスク901を含む。設計用ワークステーション900はまた、回路910またはオープンパッショナリティボールグリッドアレイパッドなどの半導体構成要素912の設計を容易にするために、ディスプレイ902を含む。回路設計910または半導体構成要素912を有形に記憶するために記憶媒体904が設けられる。回路設計910または半導体構成要素912は、GDSIIまたはGERBERなどのファイルフォーマットで記憶媒体904上に記憶されてもよい。記憶媒体904は、CD-ROM、DVD、ハードディスク、フラッシュメモリ、または他の適切なデバイスであってよい。さらに、設計用ワークステーション900は、記憶媒体904からの入力を受け入れるか、または記憶媒体904に出力を書き込むための駆動装置903を含む。

#### 【0049】

記憶媒体904上に記録されたデータは、論理回路構成、フォトリソグラフィマスクのためのパターンデータ、または電子ビームリソグラフィなどのシリアル書き込みツールのためのマスクパターンデータを指定してもよい。データはさらに、論理シミュレーションに關

10

20

30

40

50

連したタイミング図やネット回路などの論理検証データを含んでもよい。記憶媒体 904 上にデータを備えると、半導体ウエハを設計するためのプロセス数が減ることによって、回路設計 910 または半導体構成要素 912 の設計が容易になる。

【0050】

ファームウェアおよび/またはソフトウェアの実装形態の場合、この方法は、本明細書で説明した機能を実行するモジュール（たとえば、プロシージャ、関数など）を用いて実装されてもよい。本明細書で説明する方法を実施する際に、命令を有形に具現する機械可読媒体が使用されてもよい。たとえば、ソフトウェアコードは、メモリに記憶され、プロセッサユニットによって実行されてもよい。メモリは、プロセッサユニット内またはプロセッサユニットの外部に実装されてもよい。本明細書において使用される「メモリ」という用語は、長期メモリ、短期メモリ、揮発性メモリ、不揮発性メモリ、または他のメモリのタイプを指し、特定のタイプのメモリもしくは特定の数のメモリ、またはメモリが格納される媒体のタイプに限定すべきではない。

【0051】

各機能は、ファームウェアおよび/またはソフトウェアにおいて実装される場合、コンピュータ可読媒体上の1つまたは複数の命令またはコードとして記憶されてもよい。例には、データ構造を用いて符号化されたコンピュータ可読媒体、およびコンピュータプログラムを用いて符号化されたコンピュータ可読媒体が含まれる。コンピュータ可読媒体は、物理的なコンピュータ記憶媒体を含む。記憶媒体は、コンピュータによってアクセスできる入手可能な媒体であってもよい。限定ではなく例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROMもしくは他の光ディスクストレージ、磁気ディスクストレージもしくは他の磁気記憶デバイス、または、所望のプログラムコードを命令もしくはデータ構造の形で記憶するために使用することができるとともに、コンピュータによってアクセスされ得る他の媒体を含むことができ、本明細書で使用するディスク（disk）およびディスク（disc）は、コンパクトディスク（disc）（CD）、レーザーディスク（登録商標）（disc）、光ディスク（disc）、デジタル多用途ディスク（disc）（DVD）、フロッピーディスクおよびブルーレイディスク（disc）を含み、ディスク（disk）は通常、データを磁気的に再生し、ディスク（disc）はレーザーを用いてデータを光学的に再生する。上記の組合せはまた、コンピュータ可読媒体の範囲内に含まれるものとする。

【0052】

コンピュータ可読媒体上のストレージに加えて、命令および/またはデータは、通信装置に含まれる伝送媒体上の信号として備えられてもよい。たとえば、通信装置は、命令およびデータを表す信号を有するトランシーバを含んでもよい。命令およびデータは、1つまたは複数のプロセッサに、特許請求の範囲において概説する機能を実装させるように構成される。

【0053】

本開示およびその利点について詳細に説明したが、添付の特許請求の範囲によって定義される本開示の技術から逸脱することなく、明細書において様々な変更、置換、および改変を施すことができることを理解されたい。たとえば、「上」および「下」などの関係語が、基板または電子デバイスに関して使用される。当然、基板または電子デバイスが反転される場合、上は下に、下は上になる。加えて、横向きの場合、上および下は、基板または電子デバイスの側面を指すことがある。さらに、本出願の範囲は、本明細書で説明したプロセス、機械、製造、ならびに組成物、手段、方法、およびステップの特定の構成に限定されることを意図していない。本開示から当業者が容易に諒解するように、本明細書で説明する対応する構成と実質的に同じ機能を実行するかまたは実質的にそれと同じ結果を達成する、現存するかまたは今後開発されるプロセス、機械、製造、組成物、手段、方法、またはステップが、本開示に従って利用されてもよい。したがって、添付の特許請求の範囲は、そのようなプロセス、機械、製造、組成物、手段、方法、またはステップをそれらの範囲内に含むことを意図する。

10

20

30

40

50

## 【符号の説明】

## 【0 0 5 4】

1 0 0 ウエハ

1 0 2 配向

1 0 4 ダイシングライン

1 0 6 ダイ

2 0 0 ガラスダイ

2 0 1 ウエハ

2 1 0 ( 2 1 0 - 1 、 2 1 0 - 2 、 2 1 0 - 3 、 2 1 0 - 4 、 2 1 0 - 5 ) パッシベーション開口部

10

2 1 2 最終パッシベーション層 ( V P ) 間隔

2 2 0 ダイシングストリート

2 2 2 非機能境界領域

3 0 1 断面図

3 0 2 ガラス基板

3 0 3 レイアウト図

3 2 0 ダイシングストリート

3 2 2 非機能境界領域

3 3 0 第3のパッシベーション層 ( V 2 )

20

3 4 0 第2のパッシベーション層 ( V 3 )

3 5 0 第1のパッシベーション層 ( V P )

3 5 2 V P ブロック

3 6 0 導電バンプパッド

3 7 0 導電バンプアセンブリ

3 7 1 断面図

3 7 3 レイアウト図

4 0 0 導電バンプアセンブリ

4 0 2 ガラス基板

4 3 0 第3のパッシベーション層 ( V 2 )

30

4 4 0 第2のパッシベーション層 ( V 3 )

4 5 0 第1のパッシベーション層 ( V P )

4 5 2 V P ブロック

4 6 0 導電バンプパッド

4 6 2 導電バンプ

4 7 0 導電バンプアセンブリ

6 0 0 無線周波数 ( R F ) フロントエンド ( R F F F ) モジュール

6 0 2 電力増幅器

6 0 4 デュブレクサ / フィルタ

6 0 6 無線周波数 ( R F ) スイッチモジュール

6 0 8 受動コンバイナ

40

6 1 2 チューナ回路

6 1 2 A 第1のチューナ回路

6 1 2 B 第2のチューナ回路

6 1 4 アンテナ

6 1 5 接地端子

6 1 6 キャパシタ

6 1 8 インダクタ

6 1 9 ダイブレクサ

6 2 0 ワイヤレストラシーバ

6 3 0 モデム

50

640 アプリケーションプロセッサ ( A P )

700 概略図

722、732、758、774 キャパシタ

730 モデム

750 R F フロントエンドモジュール

752 電源

754 クロック

756 電力管理集積回路 ( P M I C )

760 チップセット

762、764 キャパシタ

770 Wi-Fi モジュール

772 WLAN モジュール

780 デュブレクサ

790-1 第1のダイブレクサ

790-2 第2のダイブレクサ

792 アンテナ

794 アンテナ

820、830、850 遠隔ユニット

825A、825C、825B I C デバイス

840 基地局

880 順方向リンク信号

890 逆方向リンク信号

900 設計用ワークステーション

901 ハードディスク

902 ディスプレイ

903 駆動装置

904 記憶媒体

910 回路、回路設計

912 半導体構成要素

【図面】

【図1】

FIG. 1

【図2A】

FIG. 2A

10

20

30

40

50

## 【図2B】

**FIG. 2B**

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図4A】

FIG. 4A

【図 4 B】

FIG. 4B

【図 5】

FIG. 5

【図 6】

FIG. 6

【図 7】

FIG. 7

【図 8】

FIG. 8

【図 9】

FIG. 9

10

20

30

40

50

## フロントページの続き

(33)優先権主張国・地域又は機関

米国(US)

## 前置審査

121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 チャンハン・ホビー・ユン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 チェンジエ・ズオ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 デイヴィッド・フランシス・バーディ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 ジョンヘ・キム

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

(72)発明者 ニランジャン・スニル・ムダカッテ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライブ・5775

審査官 山口 祐一郎

(56)参考文献 国際公開第2012/144370 (WO, A1)

特開2008-047652 (JP, A)

特開2007-059470 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/60

H05K 3/34

H05K 3/00

H05K 1/18