## AMT FÜR ERFINDUNGS- UND PATENTWESEN

In der vom Anmelder eingereichten Fassung veröffentlicht

(21) WP G 05 D / 303 510 8

(22) 04.06.87

(44) 02.11.88

(71) VEB Feinmeßzeugfabrik Suhl, Rimbachstraße 53, Suhl, 6000, DD

(72) Wagner, Gerald, Dipl.-Ing.; Holzbrecher, Christian, Dipl.-Ing.; Knospe, Ralf, Dipl.-Ing., DD

## (54) Schaltung zur Auswertung der Signale eines inkrementalen Wegmeßwandlers

(55) Meßsignale, inkrementaler Wegmeßwandler, getakteter Interpolator, Einchipmikrorechner, dynamische Messungen

(57) Geschaffen wird eine Schaltungsanordnung zur Auswertung der Signale eines inkrementalen Wegmeßwandlers. Die Schaltung ermöglicht ein sicheres Arbeiten bei hoher Genauigkeit. Sie arbeitet ohne die ständige Ausgabe eines Übernahmesignals vom Rechner und übernimmt trotzdem nur stabile Zählerstände in allen Betriebsarten. Ein Interpolator, bestehend aus einem Vierfach D-Flipflop dessen Ausgänge über drei Exklusiv-OR-Gatter verknüpft sind, werden getaktet, wodurch die interpolierten Meßsignale in eine feste Beziehung zum Takt aus dem Rechner stehen. Durch den gleichen Takt wird auch eine Logik zur Übernahme der Meßwerte aus dem Zähler im Register gesteuert. Fig. 1

Fig. 1

### Patentansprüche:

1. Schaltungsanordnung zur Auswertung der Signale eines inkrementalen Wegmeßwandlers bestehend aus einem Rechner, Registern, Zählern und einem Interpolator, **dadurch gekennzeichnet**, daß die Signale eines inkrementalen Wegmeßwandlers (1) in bekannter Weise in einer Eingangsschaltung (2) in zwei  $90^\circ$  phasenverschobene Rechtecksignale ( $Z_1, Z_2$ ) geformt werden, die dann an ein Vierfach-D-Flipflop (5) gelangen, die Ausgänge (A, B, C und  $\bar{E}$ ) des Vierfach-D-Flipflops (5) über drei Exklusiv-OR-Gatter (6, 7, 8) verknüpft sind, wobei die Signalverarbeitung durch einen Takt ( $SCLK$ ) gesteuert ist, die Zählimpulse (ZI) aus dem Exklusiv-OR-Gatter (8) und die Richtungsimpulse (RI) aus dem Exklusiv-OR-Gatter (7) an einen Zähler (9) gelangen und die Meßwerte (MW) aus dem Zähler (9) in Register (11) gelangen, die neben anderen Registern (14, 15, 16), wie externe Speicher ansprechbar sind, wenn von einer Logik (10), die von demselben Takt ( $SCLK$ ) wie der Interpolator (5...8) gesteuert ist, ein Impuls (STB) an die Register (11, 14, 15, 16) gelangt, wobei die Logik (10) mehrere unabhängige Eingänge besitzt.

2. Schaltung nach Anspruch 1, **dadurch gekennzeichnet**, daß die um  $90^\circ$  phasenverschobenen Rechtecksignale ( $Z_1, Z_2$ ) an die D-Eingänge zweier flankengetriggter Flipflops gelangen, deren Ausgänge (A, B) über ein erstes Exklusiv-OR-Gatter (6) verknüpft sind, der Ausgang A des ersten Flipflops gleichzeitig mit einem zweiten Exklusiv-OR-Gatter (7) verbunden ist, an dessen zweiten Eingang der Ausgang (C) eines vierten Flipflops angeschlossen ist, an dessen D-Eingang der Ausgang (B) des zweiten Flipflops liegt, der Ausgang (D) des ersten Exklusiv-OR-Gatters (6) mit einem dritten Exklusiv-OR-Gatter (8) gekoppelt ist, an dessen zweiten Eingang der Ausgang ( $\bar{E}$ ) eines dritten Flipflops liegt, dessen D-Eingang ebenfalls mit dem Ausgang D des ersten Exklusiv-OR-Gatters (6) verbunden ist.

3. Schaltung nach Anspruch 1, **dadurch gekennzeichnet**, daß an die Logik (10) Referenzsignale (REF) gelangen, die mit einem ersten Meßsignal ( $\bar{A}$ ) UND-verknüpft, an ein zweites UND-Gatter (21) gelangen, an das auch die aus einem zweiten Meßsignal (B) durch eine Exklusiv-OR-Verknüpfung dieses Meßsignals (B) mit dem durch eine Taktung dieses Meßsignals (B) mit dem negativen Takt ( $\bar{SCLK}$ ) an einem D-Flipflop (17) gewonnene verzögerte Meßsignal erzeugten Impulse (K) gelangen, wodurch ein Impuls ( $\bar{U}$ ) zur Übernahme von Meßwerten aus dem Zähler (9) in die Register (11) entsteht.

4. Schaltung nach Anspruch 1, **dadurch gekennzeichnet**, daß an die Logik (10) ein Übernahmesignal ( $\bar{U}$ ) vom Rechner (12) gelangt, das an einem ersten D-Flipflop (18) mit dem Takt ( $\bar{SCLK}$ ) getaktet wird, der negierte Ausgang (L) des D-Flipflops (18) mit einem zweiten D-Flipflop (19) verbunden ist, das mit dem negierten Takt ( $\bar{SCLK}$ ) getaktet ist und die Ausgänge (M, N) der beiden D-Flipflops (18, 19) an einem UND-Gatter (23) angeschlossen sind, an dessen Ausgang ein Signal ( $\bar{U}$ ) zur Übernahme von Meßwerten (MW) aus dem Zähler (9) in die Register (11) entsteht.

Hierzu 3 Seiten Zeichnungen

### Anwendungsgebiet der Erfindung

Die Schaltung wird vorzugsweise verwendet in inkrementalen Wegmeßgeräten in denen ein Einchipmikrorechner zur Anwendung kommt.

### Charakteristik der bekannten technischen Lösungen

Bekannt ist eine „Schaltung zum Entnehmen von dynamischen Meßwerten aus einem inkrementalen Lagemeßsystem“ DE-OS 3111068. Zwischen einem Zähler und einem Rechner ist ein Zwischenspeicher vorgesehen, und über eine Synchronisationsschaltung steuert der Rechner den Zwischenspeicher nach Priorität derart, daß dieser dem Zähler Zählerstände nur in Zeitintervallen entnimmt, die größer als die Zählerarbeitszeit oder höchstens gleich dieser sind. Nachteil dieser Lösung ist, daß zum ruhigen Lesen der Meßwerte ständig ein Übernahmesignal vom Rechner bereitgestellt werden muß und ein relativ großer Aufwand zur Synchronisation erforderlich ist.

### Ziel der Erfindung

Ziel der Erfindung ist es, die Nachteile des Standes der Technik zu beseitigen und eine Schaltung zur Auswertung der Signale eines inkrementalen Wegmeßwandlers zu schaffen, die ein sicheres Arbeiten bei hoher Genauigkeit ermöglicht und nur einen geringen Bauelementeaufwand benötigt.

## Wesen der Erfindung

Die Erfindung löst die Aufgabe, eine Schaltung zur Auswertung der Signale eines inkrementalen Wegmeßwandlers zu schaffen die ohne die ständige Ausgabe eines Übernahmesignals vom Rechner nur stabile Zählerstände übernimmt, auch wenn die Übernahme von einer Referenzmarke oder eines externen Indikators ausgelöst wird.

Gelöst wird die Aufgabe dadurch, daß die Signale eines inkrementalen Wegmeßwandlers in bekannter Weise in einer Eingangsschaltung in zwei  $90^\circ$  phasenverschobene Rechecksignale geformt werden, die dann an ein Vierfach-D-Flipflop gelangen, die Ausgänge des Vierfach-D-Flipflops über drei Exklusiv-OR-Gatter verknüpft sind, wobei die Signalverarbeitung durch einen Takt gesteuert ist, die Zählimpulse aus dem Exklusiv-OR-Gatter und die Richtungsimpulse aus dem Exklusiv-OR-Gatter an einen Zähler gelangen und die Meßwerte aus dem Zähler in Register gelangen, die neben anderen Registern, wie externe Speicher ansprechbar sind, wenn von einer Logik, die von demselben Takt wie der Interpolator gesteuert ist, ein Impuls an die Register gelangt, wobei die Logik mehrere unabhängige Eingänge besitzt.

## Ausführungsbeispiel

Die Erfindung soll anhand einer Zeichnung näher erläutert werden.

Die einzelnen Figuren zeigen:

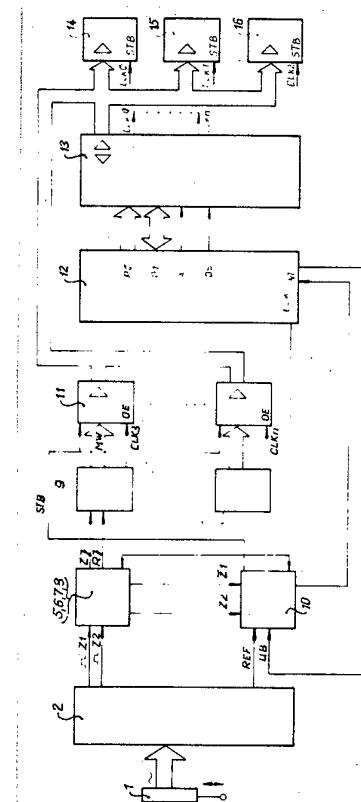

Figur 1: Blockschaltbild der gesamten Auswerteschaltung

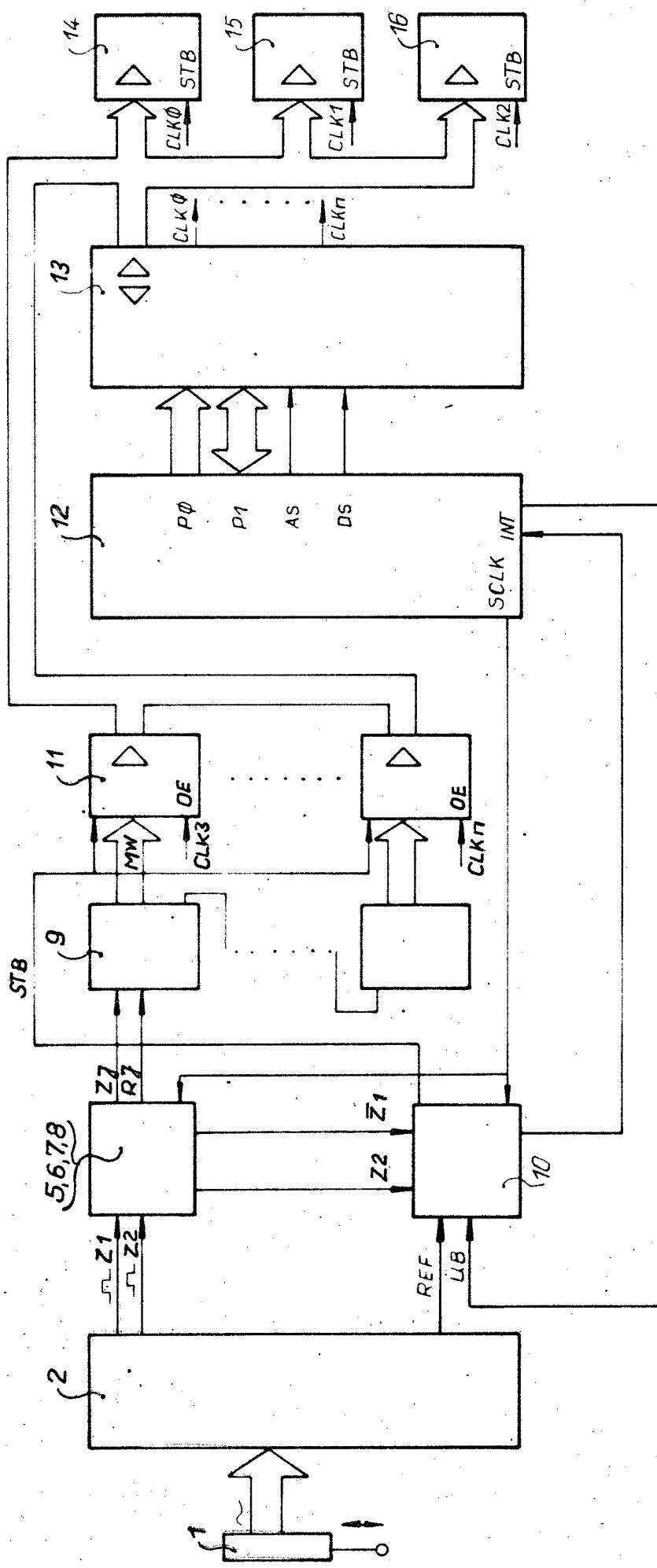

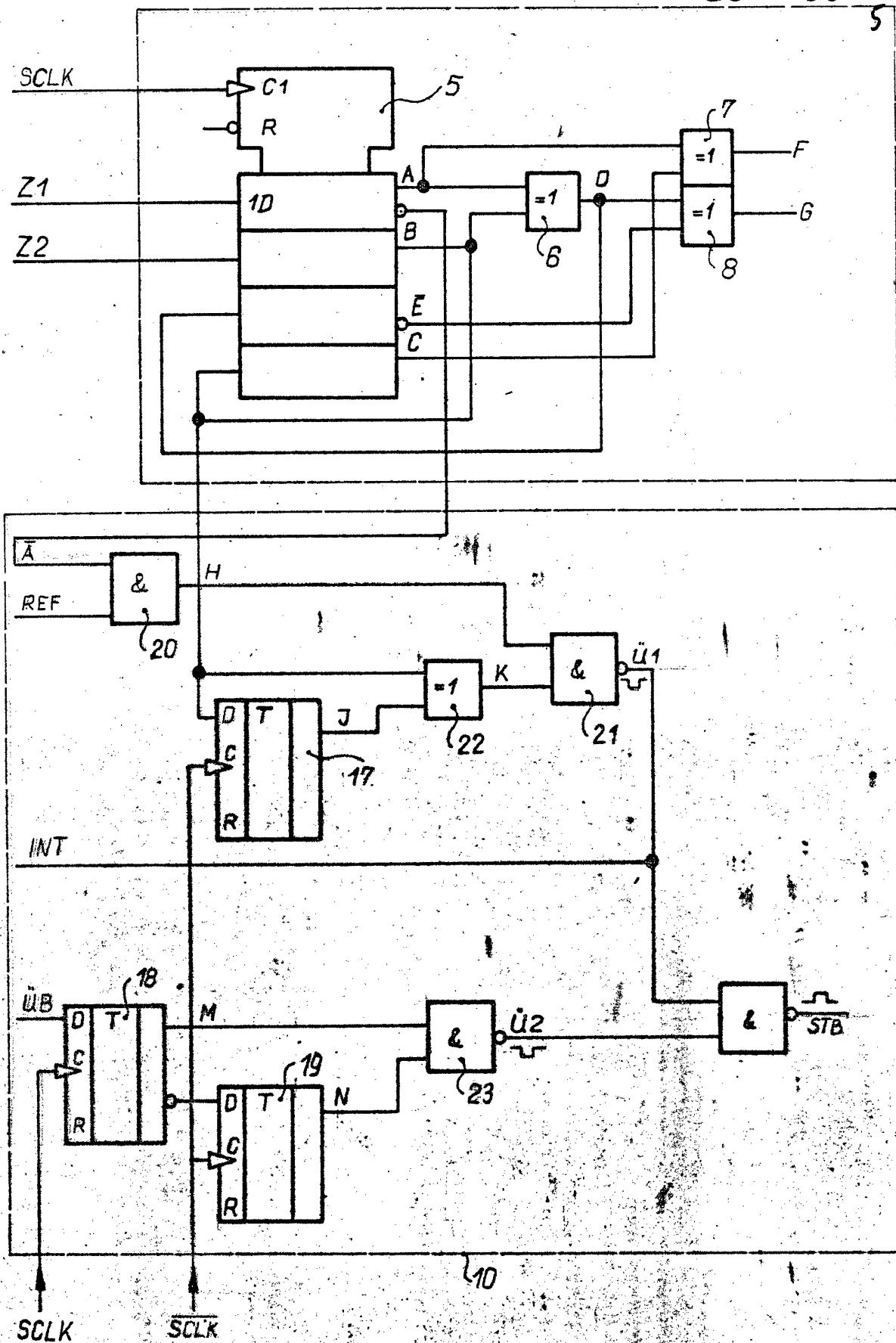

Figur 2: Schaltbild für den Interpolator und die Übernahmelogik

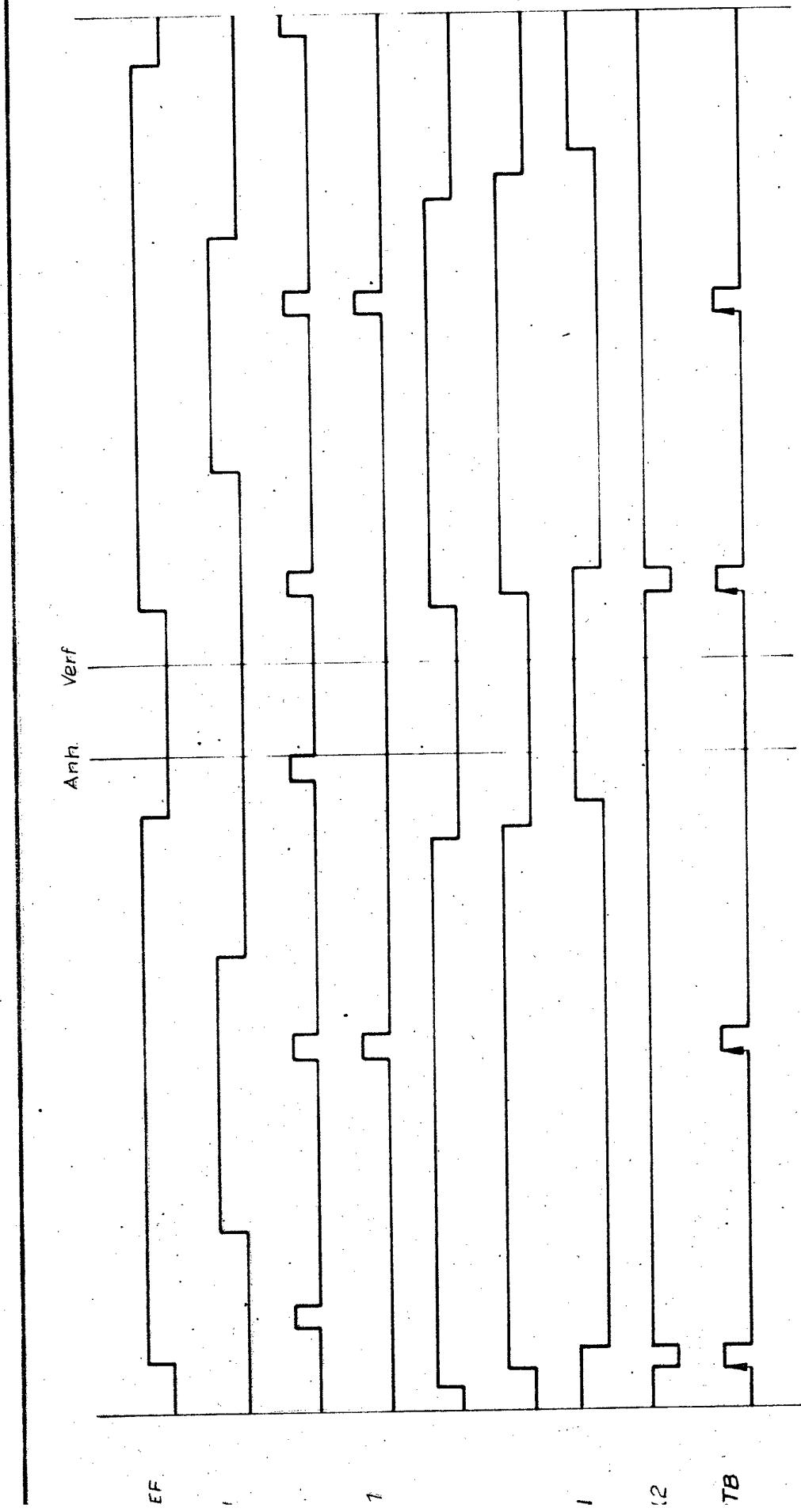

Figur 3: Taktdiagramm für die Schaltung nach Figur 2.

In Figur 1 ist ein inkrementaler Wegmeßwandler 1, beispielsweise eine digitale Meßuhr, mit einer Eingangsschaltung 2 verbunden.

Die zu Rechtecksignalen geformten Meßsignale  $Z_1, Z_2$  gelangen von der Eingangsschaltung 2 an eine Interpolationsschaltung 5, 6, 7, 8, deren Interpolationsfaktor umschaltbar ist und von da an eine erste Logik 10 zur Steuerung der Übernahme der Meßwerte MW von einem Zähler 9 in Register 11.

Der vom Einchipmikrorechner 12 kommende Takt (SCLK) steuert die Interpolationsschaltung 5, 6, 7, 8 und die erste Logik 10. Die erste Logik 10 hat mehrere unabhängige Eingänge für Referenz- und Übernahmesignale.

Der Einchipmikrorechner 12 ist mit allen Registern 11, 14, 15, 16 verbunden und übernimmt über eine zweite Logik 13 den gesamten Datenaustausch und die Berechnung der Meßergebnisse sowie weiterer Daten.

In Figur 2 gelangen die beiden Meßsignale  $Z_1, Z_2$  an die ersten beiden D-Flipflops des Vierfach-D-Flipflops 5. Der Ausgang A des ersten D-Flipflops ist mit zwei Exklusiv-OR-Gattern 6, 7 verbunden.

Der Ausgang B des zweiten D-Flipflops ist mit dem ersten Exklusiv-OR-Gatter 6 gekoppelt und mit einem vierten D-Flipflop verbunden, dessen Ausgang C an das zweite Exklusiv-OR-Gatter 7 gelangt.

Nach dem Durchlauf der Meßsignale  $Z_1, Z_2$  durch die ersten beiden D-Flipflops stehen die Meßsignale  $Z_1, Z_2$  an den Ausgängen A, B in einer festen Beziehung zum Takt (SCLK).

Am Exklusiv-OR-Gatter 7 werden das erste Meßsignal vom ersten D-Flipflop und das zweite um eine Taktperiode verzögerte Meßsignal B verknüpft. Die Richtungsimpulse RI am Ausgang des Exklusiv-OR-Gatters 7 sind in einer Zählrichtung beim Auftreten der Zählimpulse ZI0 und in der entgegengesetzten Zählrichtung 1.

Die beiden, am ersten Exklusiv-OR-Gatter 6 verknüpften Meßsignale A, B liefern am Ausgang D des Exklusiv-OR-Gatters 6 eine Impulsfolge mit doppelter Frequenz.

Diese Impulsfolge D ist an ein drittes Exklusiv-OR-Gatter 8 geschaltet und liegt am Eingang eines dritten D-Flipflops an.

Am dritten Exklusiv-OR-Gatter 8 werden die Impulsfolge D und die um eine Taktperiode verzögerte negierte Impulsfolge  $\bar{D}$  verknüpft, wodurch am Ausgang G des dritten Exklusiv-OR-Gatters 8 bei jeder auftretenden Signalfanke der Meßimpulse A, B ein Zählimpuls ZI entsteht.

Die Zähl- und Richtungsimpulse gelangen ständig an den Zähler 9. In Figur 2 ist an die Logik 10 ein Referenzimpuls REF geführt. Dieser kann von einer internen Referenzmarke des inkrementalen Wegmeßwandlers 1 oder einem externen Indikator 3 stammen.

Das Referenzsignal REF wird zuerst mit dem ersten negierten Meßsignal  $\bar{A}$  UND verknüpft zu einem Signal H.

An einem ersten D-Flipflop 17 wird das zweite Meßsignal B mit dem negierten Takt  $\bar{SCLK}$  getaktet.

Das auf diese Weise um eine Taktperiode verzögerte Signal I wird mit dem Meßsignal B Exklusiv-OR verknüpft und danach mit dem Signal H UND verknüpft.

Am Ausgang des zweiten UND-Gliedes 21 entsteht damit immer an einer bestimmten Stelle des Referenzsignals REF ein Impuls Ü zur Übernahme der Meßwerte MW aus dem Zähler 9 in die Register 11, dessen Schaltflanke nicht gleichzeitig mit der Schaltflanke der Zählimpulse auftritt.

An die Logik 10 gelangen auch Übernahmeimpulse ÜB vom Rechner 12. Diese werden an ein D-Flipflop 18 mit dem Takt SCLK getaktet. Der negierte Ausgang L des D-Flipflops 18 ist mit einem D-Flipflop 19 verbunden, welches vom negierten Takt  $\bar{SCLK}$  gesteuert wird.

Die Ausgänge M, N dieser beiden D-Flipflops 18, 19 sind UND verknüpft, wodurch sofort nach dem Eintreffen des Übernahmeimpulses ÜB mit dem nächsten Takt ein Signal Ü zur Übernahme der Meßwerte vom Zähler 9 in die Register 11 vom UND-Gatter 23 abgegeben wird. Die Schaltflanke des Signals Ü zur Meßwertübernahme tritt ebenfalls nur auf, wenn keine Schaltflanke der Zählimpulse ZI eintrifft.

Die Auswerteschaltung eignet sich besonders gut für dynamische Messungen, denn die Schaltung ermöglicht eine schnelle Übernahme der Meßwerte. Durch die getaktete Arbeitsweise des Interpolators und der ersten Logik wird auch bei großen Verarbeitungsgeschwindigkeiten eine hohe Zuverlässigkeit erreicht, insbesondere bei schnellem Richtungswechsel treten keine Signalverluste auf.

Die große Verarbeitungsgeschwindigkeit wird dadurch erreicht, daß alle Register wie externe Speicher ansprechbar sind.

Beim Überfahren von Referenzmarken sind große Verfahrgeschwindigkeiten des Meßsystems möglich.

Eine gute Reproduzierbarkeit beim Positionieren wird mit der Verwendung von externen Referenzmarken erreicht. Die gesamte Schaltung zeichnet sich durch einen geringen Bauelementenaufwand aus.

---

054 DD

Fig. 1

264 663

5

Fig. 2

054 00

261 663 6

054 00

Fig. 3