(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7252845号

(P7252845)

(45)発行日 令和5年4月5日(2023.4.5)

(24)登録日 令和5年3月28日(2023.3.28)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 11/16 (2006.01) | F I | G 0 6 F | 11/16 | 6 6 6   |

| G 0 6 F | 12/06 (2006.01) |     | G 0 6 F | 12/06 | 5 1 5 Q |

| G 0 6 F | 11/10 (2006.01) |     | G 0 6 F | 11/10 | 6 6 2   |

請求項の数 20 (全25頁)

|                   |                             |          |                                                                                                                                                                              |

|-------------------|-----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2019-123601(P2019-123601) | (73)特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 12<br>9<br>129, Samsung-ro, Yeo<br>ngtong-gu, Suwon-si<br>, Gyeonggi-do, Repub<br>lic of Korea |

| (22)出願日           | 令和1年7月2日(2019.7.2)          | (74)代理人  | 110000051<br>弁理士法人共生国際特許事務所                                                                                                                                                  |

| (65)公開番号          | 特開2020-9441(P2020-9441A)    | (72)発明者  | 牛 迪民<br>アメリカ合衆国, 94087 カリフォ<br>ルニア州, サニーベール, ホルトハウス<br>最終頁に続く                                                                                                                |

| (43)公開日           | 令和2年1月16日(2020.1.16)        |          |                                                                                                                                                                              |

| 審査請求日             | 令和4年6月30日(2022.6.30)        |          |                                                                                                                                                                              |

| (31)優先権主張番号       | 62/692,960                  |          |                                                                                                                                                                              |

| (32)優先日           | 平成30年7月2日(2018.7.2)         |          |                                                                                                                                                                              |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |          |                                                                                                                                                                              |

| (31)優先権主張番号       | 16/150,239                  |          |                                                                                                                                                                              |

| (32)優先日           | 平成30年10月2日(2018.10.2)       |          |                                                                                                                                                                              |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |          |                                                                                                                                                                              |

| 早期審査対象出願          |                             |          |                                                                                                                                                                              |

(54)【発明の名称】 高帯域幅メモリのR A S (信頼性、アクセシビリティ、及びサービスアビリティ) キャッシュ構造

## (57)【特許請求の範囲】

## 【請求項1】

装置であつて、

積層された集積回路ダイを備え、

前記積層された集積回路ダイは、

メモリアドレスに基づいて、少なくとも部分的に、データを格納するように構成されたメモリセルダイと、

ロジックダイと、を含み、

前記ロジックダイは、

前記積層された集積回路ダイに連結され、前記メモリセルダイと外部装置との間でメモリアクセスを通信するように構成されたインターフェースと、

信頼性回路と、を含み、

前記信頼性回路は、

データを格納するように構成された補助メモリと、

エラーに関連付けられたメモリアドレスを前記補助メモリの部分にマッピングするよう構成されたアドレステーブルを含み、

前記信頼性回路は、

前記ロジックダイの外部のプロセッサから受信した前記メモリセルダイのエラーが検出されたメモリアドレスに基づいて、前記アドレステーブルのメモリアドレスのエントリを編集するよう構成され、

前記積層された集積回路ダイへのメモリアクセスに基づいて、前記メモリアクセスがエラーに関連付けられているメモリアドレスであると判定した場合、少なくとも部分的に、前記補助メモリを使用して、前記メモリアクセスを完了するように構成されたことを特徴とする装置。

【請求項 2】

前記アドレステーブルは、

前記アドレステーブル内のエラーから保護するエラー訂正コードの部分と、

前記メモリアドレスのエントリがアクティブ状態であることを示すように構成された有効フラグと、を含むことを特徴とする請求項 1 に記載の装置。

【請求項 3】

10

前記信頼性回路は、

メモリアドレスのデータに対するライト (write) のメモリアクセスを外部装置から受信し、

前記メモリアドレスがエラーに関連付けられていると判定した場合、

前記データを前記補助メモリの部分に格納するように構成されたことを特徴とする請求項 1 に記載の装置。

【請求項 4】

前記信頼性回路は、前記メモリアドレスがメモリアドレスのエントリとして、前記アドレステーブルに格納されていると判定し、且つ有効フラグが前記メモリアドレスのエントリがアクティブ状態であることを示すと判定することにより、前記メモリアドレスがエラーに関連付けられていると判定するように構成されたことを特徴とする請求項 3 に記載の装置。

20

【請求項 5】

前記信頼性回路は、

メモリアドレスのデータに対するリード (read) のメモリアクセスを外部装置から受信し、

前記メモリアドレスがエラーに関連付けられていると判定した場合、

前記補助メモリの部分から前記データを回収するように構成されたことを特徴とする請求項 1 に記載の装置。

【請求項 6】

30

前記信頼性回路は、

メモリアドレスがエラーに関連付けられていることを示すメッセージを外部装置から受信し、

前記アドレステーブルに前記メモリアドレスを位置させ、

前記メモリアドレスを前記補助メモリの前記部分に関連付けるように構成されたことを特徴とする請求項 1 に記載の装置。

【請求項 7】

前記信頼性回路は、予め定められたメモリアドレスへのライト (write) のメモリアクセスを受信することにより、前記メモリアドレスがエラーに関連付けられていることを示すメッセージを外部装置から受信するように構成され、

40

前記予め定められたメモリアドレスは、前記アドレステーブルに関連付けられていることを特徴とする請求項 6 に記載の装置。

【請求項 8】

前記信頼性回路は、

前記補助メモリの使用レベルを監視し、

予め定められたメモリアドレスに前記使用レベルのインジケーターを格納するように構成され、

前記インターフェースは、

前記予め定められたメモリアドレスへのリード (read) のメモリアクセスを受信し、前記リードのメモリアクセスに基づいて、前記補助メモリの前記使用レベルの前記イン

50

ジケーターを提供することを特徴とする請求項 1 に記載の装置。

【請求項 9】

システムであって、

プロセッサと、

前記プロセッサとは別の高帯域幅メモリダイのスタックと、を備え、

前記プロセッサは、

前記プロセッサとの間のデータの流れを管理するように構成されたメモリコントローラーと、

格納されたデータに関連するエラーを検出するように構成されたエラー訂正回路と、を含み、

前記高帯域幅メモリダイのスタックは、

メモリアドレスに基づいて、少なくとも部分的に、データを格納するように構成されたメモリセルアレイが分散配置された複数の集積回路ダイと、

信頼性回路と、を含み、

前記信頼性回路は、

データを格納するように構成された補助メモリと、

前記エラーに関連付けられたメモリアドレスを前記補助メモリの部分にマッピングするように構成されたアドレステーブルと、を含み、

前記信頼性回路は、前記高帯域幅メモリダイのスタックへのメモリアクセスに基づいて、前記メモリアクセスが前記エラー訂正回路によって検出されたエラーに関連付けられていると判定した場合、少なくとも部分的に、前記補助メモリを使用して、前記メモリアクセスを完了するように構成されたことを特徴とするシステム。

【請求項 10】

前記プロセッサは、

前記補助メモリが前記エラーを、少なくとも部分的に、訂正するのに十分な自由容量を含んでいると判定し、

前記エラーに関連付けられている前記メモリアドレスを前記補助メモリの部分にマッピングすることを特徴とする請求項 9 に記載のシステム。

【請求項 11】

前記信頼性回路は、

メモリアドレスのデータに対するライト (write) のメモリアクセスを前記プロセッサから受信し、

前記メモリアドレスがエラーに関連付けられていると判定した場合、

前記データを前記補助メモリのマッピングされた部分に格納するように構成されたことを特徴とする請求項 9 に記載のシステム。

【請求項 12】

前記信頼性回路は、

メモリアドレスのデータに対するリード (read) のメモリアクセスを、前記プロセッサから受信し、

前記メモリアドレスがエラーに関連付けられていると判定した場合、

前記データを前記補助メモリのマッピングされた部分から回収するように構成されたことを特徴とする請求項 9 に記載のシステム。

【請求項 13】

前記プロセッサは、予め定められたメモリアドレスへのライト (write) のメモリアクセスを発行するように構成され、

前記予め定められたメモリアドレスは、前記アドレステーブルに関連付けられ、

前記ライト (write) のメモリアクセスは、データの一部として、前記エラーに関連付けられている前記メモリアドレスを含み、

前記信頼性回路は、

メモリアドレスがエラーに関連付けられていることを示すメッセージを前記プロセッサ

10

20

30

40

50

から受信し、

前記メモリアドレスを前記アドレステーブルに位置させ、

前記メモリアドレスを前記補助メモリの前記部分に関連させるように構成されたことを特徴とする請求項 9 に記載のシステム。

【請求項 14】

前記信頼性回路は、

前記補助メモリの使用レベルを監視し、

予め定められたメモリアドレスで前記使用レベルのインジケーターを格納するように構成され、

前記プロセッサは、

前記予め定められたメモリアドレスへのリード (read) のメモリアクセスを発行し、

前記リード (read) のメモリアクセスに基づいて、前記補助メモリの前記使用レベルの前記インジケーターを受信するように構成されたことを特徴とする請求項 9 に記載のシステム。

【請求項 15】

前記プロセッサは、それぞれのエラーに関連付けられているメモリアドレスのリストを格納するように構成された不揮発性メモリを含み、

前記エラー訂正回路は、格納されたデータに対するエラーの検出に基づいて、前記エラーに関連付けられている、前記メモリアドレスが前記不揮発性メモリと前記アドレステーブルの両方によって格納されるように構成されることを特徴とする請求項 9 に記載のシステム。

【請求項 16】

前記不揮発性メモリは、それぞれのエラーに関連付けられている、前記メモリアドレスの前記リストの 1 つ以上を前記アドレステーブルに追加するように構成され、

前記信頼性回路は、前記メモリアドレスの 1 つ以上を前記補助メモリのそれぞれの部分にマッピングするように構成されたことを特徴とする請求項 15 に記載のシステム。

【請求項 17】

前記信頼性回路は、前記プロセッサをリセットすることなく、前記メモリセルアレイ内のデータエラーをリマッピングするように構成されたことを特徴とする請求項 9 に記載のシステム。

【請求項 18】

装置であって、

ロジックダイを備え、

前記ロジックダイは、

メモリアドレスに基づいて、データを格納するように構成された高帯域幅メモリダイに連結された内部インターフェースと、

前記高帯域幅メモリダイと、少なくとも 1 つの外部装置との間でメモリアクセスを通信するように構成された外部インターフェースと、

信頼性回路と、を含み、

前記信頼性回路は、

データを格納するように構成された補助メモリと、

エラーに関連付けられたメモリアドレスを前記補助メモリの部分にマッピングするように構成されたアドレステーブルを含み、

前記信頼性回路は、

前記ロジックダイの外部のプロセッサから受信した前記高帯域幅メモリダイのエラーが検出されたメモリアドレスに基づいて、前記アドレステーブルのメモリアドレスのエントリを編集するよう構成され、

前記高帯域幅メモリダイへのメモリアクセスに基づいて、前記メモリアクセスがエラーに関連付けられているメモリアドレスであると判定した場合、少なくとも部分的に、前記補助メモリを使用して、前記メモリアクセスを完了するように構成されたことを特徴とす

10

20

30

40

50

る装置。

【請求項 19】

前記信頼性回路は、

メモリアドレスのデータに対するライト (write) のメモリアクセスを、前記外部装置から受信し、

前記メモリアドレスがエラーに関連付けられていると判定した場合、

前記補助メモリの部分に前記データを格納するように構成されたことを特徴とする請求項 18 に記載の装置。

【請求項 20】

前記信頼性回路は、

メモリアドレスのデータに対するリード (read) のメモリアクセスを、前記外部装置から受信し、

前記メモリアドレスがエラーに関連付けられていると判定した場合、

前記補助メモリのマッピングされた部分から前記データを回収するように構成されたことを特徴とする請求項 18 に記載の装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリエラー訂正に関し、より詳しくは、高帯域幅メモリ (HBM : h i g h - b a n d w i d t h m e m o r y ) の R A S ( r e l i a b i l i t y , a c c e s s i b i l i t y , a n d s e r v i c e a b i l i t y : 信頼性、アクセシビリティ、及びサービスabiliti ) キャッシュ構造に関する。

【背景技術】

【0002】

HBM ( H i g h B a n d w i d t h M e m o r y ) は、積層されたダイナミックランダムアクセスメモリ ( s t a c k e d D R A M : s t a c k e d d y n a m i c r a n d o m a c c e s s m e m o r y ) のための高性能 RAM インターフェースである。 HBM は、一般的に、高性能グラフィックスアクセラレータ及びネットワーク装置とともに使用される。 HBM を使用した最初の装置は、 G P U ( g r a p h i c a l p r o c e s s i n g u n i t ) である。

【0003】

HBM は、 D D R 4 ( d o u b l e d a t a r a t e f o u r t h - g e n e r a t i o n s y n c h r o n o u s D R A M ) 又は G D D R 5 ( d o u b l e d a t a r a t e t y p e f i v e s y n c h r o n o u s g r a p h i c s r a n d o m - a c c e s s m e m o r y ) よりも実質的にもっと小さいフォームファクタで、より少ない電力を使用しながら、より高い帯域幅を達成する。これは、多数 ( 例えば、 8 個 ) の D R A M ダイを積層し、メモリコントローラーを有する、選択的な基本的ダイを追加することによって達成される。これらは T V S ( t h r o u g h - s i l i c o n v i a s ) 及びマイクロバンプによって連結される。

【0004】

HBM メモリバスは、 D D R 4 又は G D D R 5 のような他の D R A M メモリに比べて非常に広い。 4 つの D R A M ダイの HBM スタック ( 4 - H i ) は、一般的に、ダイ当たり 2 つの 128 ビットチャネルからなる総計 8 つのチャネルを有し、全体で 1024 ビットの幅を有する。したがって、 4 つの 4 - H i HBM スタックを有するグラフィックカード / G P U は 4096 ビットの幅を有するメモリバスを含む。これに比べて、 G D D R メモリのバス幅は 32 ビットであり、 512 ビットのメモリインターフェースを有するグラフィックスカードについて 16 チャンネルである。

【0005】

D D R 4 又は G D D R 5 より相対的にメモリへのより多くの連結は、 HBM メモリを G P U ( 又は他のプロセッサ ) に連結するための新しい方法を必要とする。一部の企業

10

20

30

40

50

はインターポーザー (interposer) と呼ばれる特殊製作されたシリコンチップ (purpose built silicon chips) を使用して、メモリとGPUとを連結する。このようなインターポーザーは、メモリ及びプロセッサが物理的に近づいてメモリバスを減少させる利点を有する。しかし、半導体装置の製造は、プリント回路基板の製造よりも非常に高価なので、これは最終的な製品のコストに追加される。

【先行技術文献】

【特許文献】

【0006】

【文献】米国特許第8898437号明細書

米国特許出願公開第2006/0080572号明細書

10

米国特許出願公開第2010/0070809号明細書

米国特許出願公開第2015/0235716号明細書

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、上記従来の問題点に鑑みてなされたものであって、本発明の目的は、向上された信頼性を有するHBM (high-bandwidth memory) のRAS (reliability, accessibility, and serviceability: 信頼性、アクセシビリティ、及びサービスアビリティ) キャッシュ構造を提供することにある。

20

【課題を解決するための手段】

【0008】

上記目的を達成するためになされた本発明の一態様による装置は、複数の積層された集積回路ダイを備え、前記複数の積層された集積回路ダイは、メモリアドレスに基づいて、ランダムアクセス方式でデータを格納するように構成されたメモリセルダイと、ロジックダイと、を含み、前記ロジックダイは、前記複数の積層された集積回路ダイに連結され、前記メモリセルダイと少なくとも1つの外部装置との間でメモリアクセスを通信するように構成されたインターフェースと、前記メモリセルダイ内のデータのエラーを改善するように構成された信頼性回路と、を含み、前記信頼性回路は、ランダムアクセス方式でデータを格納するように構成された補助メモリと、エラーに関連付けられたメモリアドレスを前記補助メモリの部分にマッピングするように構成されたアドレステーブルと、を含み、前記信頼性回路は、前記複数の積層された集積回路ダイへのメモリアクセスが発生した場合、前記メモリアクセスが前記エラーに関連付けられているか否かを判定し、前記メモリアクセスが前記エラーに関連付けられている場合、少なくとも部分的に前記補助メモリを使用して、前記メモリアクセスを完了するように構成されたことを特徴とする。

30

【0009】

上記目的を達成するためになされた本発明の一態様によるシステムは、プロセッサと、高帯域幅メモリスタックの集積回路と、を備え、前記プロセッサは、前記プロセッサへのデータの流れを管理するように構成されたメモリコントローラーと、格納されたデータにエラーが発生したかを検出するように構成されたエラー訂正回路と、を含み、前記高帯域幅メモリスタックの集積回路は、メモリアドレスに基づいて、データを格納するように構成された高帯域幅メモリセルと、前記高帯域幅メモリセル内のデータのエラーを改善するように構成された信頼性回路と、を含み、前記信頼性回路は、データを格納するように構成された補助メモリと、前記エラーに関連付けられたメモリアドレスを前記補助メモリの部分にマッピングするように構成されたアドレステーブルと、を含み、前記信頼性回路は、前記高帯域幅メモリスタックの集積回路へのメモリアクセスが発生した場合、前記メモリアクセスがエラーに関連付けられているか否かを判定し、前記メモリアクセスが前記エラーに関連付けられている場合、前記補助メモリを少なくとも部分的に使用して、前記メモリアクセスを完了するように構成されたことを特徴とする。

40

【0010】

50

上記目的を達成するためになされた本発明の他の態様による装置は、ロジックダイを備え、前記ロジックダイは、メモリアドレスに基づいて、データを格納するように構成された高帯域幅メモリダイに連結された内部インターフェースと、前記高帯域幅メモリダイと、少なくとも1つの外部装置との間でメモリアクセスを通信するように構成された外部インターフェースと、前記高帯域幅メモリダイ内のデータエラーを改善するように構成された信頼性回路と、を含み、前記信頼性回路は、データを格納するように構成された補助メモリと、エラーに関連付けられたメモリアドレスを前記補助メモリの部分にマッピングするように構成されたアドレステーブルを含み、前記信頼性回路は、前記高帯域幅メモリダイへのメモリアクセスが発生した場合、前記メモリアクセスがエラーに関連付けられているか否かを判定し、前記メモリアクセスがエラーに関連付けられている場合、前記補助メモリを少なくとも部分的に使用して、前記メモリアクセスを完了するように構成されたことを特徴とする。

【発明の効果】

【0011】

本発明によれば、向上された信頼性を有するHBM (high-bandwidth memory) のRAS (reliability, accessibility, and serviceability: 信頼性、アクセシビリティ、及びサービスアビリティ) キャッシュ構造が提供される。

【図面の簡単な説明】

【0012】

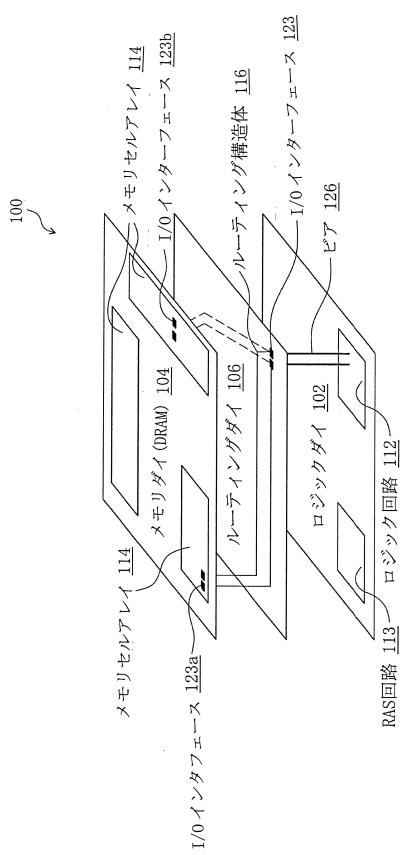

【図1】本発明の一実施形態による装置の例示的な実施例を示す斜視図である。

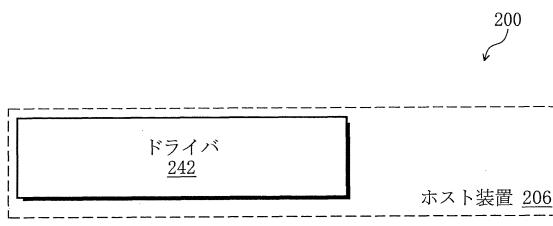

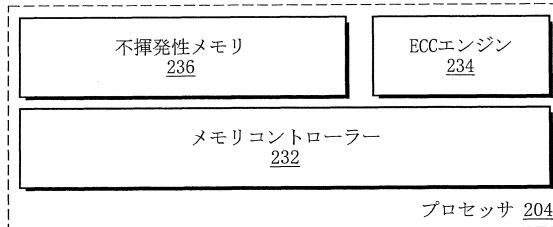

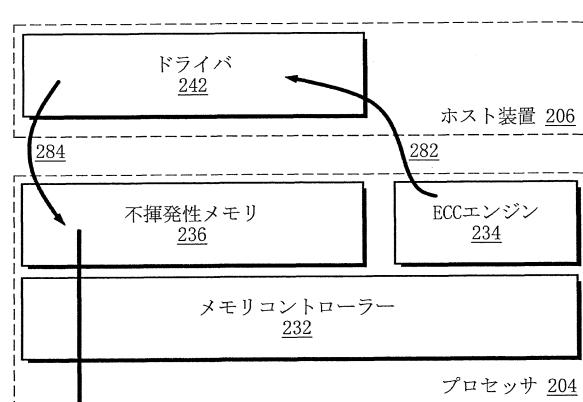

【図2A】本発明の一実施形態によるシステムの例示的な実施例を示すブロック図である。

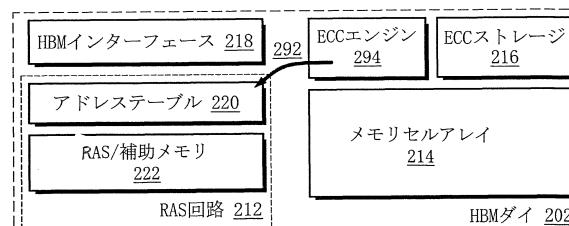

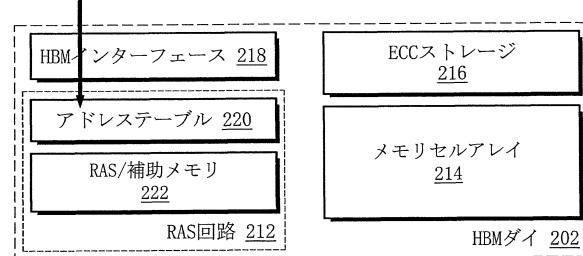

【図2B】本発明の一実施形態によるシステムの例示的な実施例を示すブロック図である。

【図2C】本発明の一実施形態によるシステムの例示的な他の実施例を示すブロック図である。

【図3】本発明の一実施形態によるデータ構造の一例を示す図である。

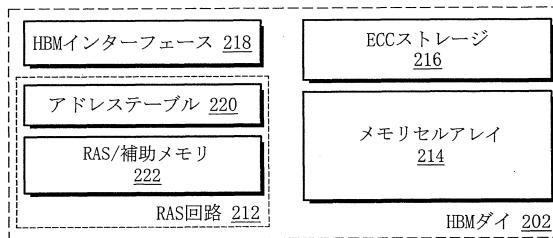

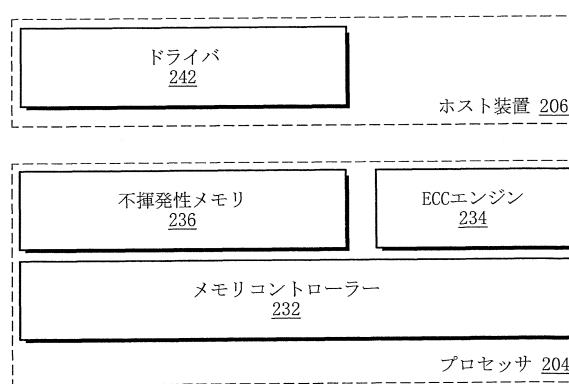

【図4A】本発明の一実施形態によるシステムの例示的な実施例を示すブロック図である。

【図4B】本発明の一実施形態によるシステムの例示的な実施例のブロック図である。

【図5】本発明の実施形態の原理に基づいて形成された装置を含む情報処理システムの概念的なブロック図である。

【発明を実施するための形態】

【0013】

多様な例示的な実施例が、一部の例示的な実施例を示す図面を参照して、より詳細に説明される。しかし、本明細書に記載された内容は、他の多様な形態で具現可能であり、本明細書に記載された例示的な実施例に限定されない。代わりに、このような例示的な実施例は、詳細な説明が完全であり、当業者に本発明の技術的思想を完全に伝達されるよう提供される。図面では、層と領域のサイズ及び相対的なサイズは、明確化のために、誇張される。

【0014】

構成や層が、他の構成や階層に「連結された」と記載される場合、これは直接的に他の構成や階層に連結されるか、または1つ以上の中間の構成や階層が存在し得る。対照的に、構成や階層が他の構成や階層に「直接に連結された」と記載される場合、中間の構成又は階層は存在しない。類似の参照番号は、明細書全体的に類似の構成を示す。本明細書で使用される「及び／又は」は、関連して羅列されたリストの中の1つ又はそれ以上の組み合わせの一部及び全部を含む。

【0015】

「第1」、「第2」、「第3」などのような用語は、多様な要素、構成、領域、階層、及び／又はセクションを説明するために本明細書で使用されるが、このような要素、構成、領域、階層、及び／又はセクションは、このような用語で限定されない。このような用語は、1つの要素、構成、領域、階層、又はセクションを他の1つの要素、構成、領域、

階層、又はセクションから区別するためにだけ使用される。つまり、以下で記載する第1の要素、構成、領域、階層、又はセクションは、本発明の思想と技術範囲から逸脱することなく、第2の要素、構成、領域、階層、又はセクションと呼ばれ得る。

【0016】

「～の下」、「～の上」などのような空間的に相対的な用語は、図面に示された1つの要素や特徴を他の1つの要素や特徴との関連性を容易に説明するために、本明細書で使用される。空間的に相対的な用語は、図面に示された方向に加えて、動作や使用において装置の他の方向(orientation)を含む。例えば、図面で、装置が裏返される場合、他の要素や特徴の「下」にと説明された要素は、他の要素や特徴の「上部」を向く。つまり、「下」との例示的な用語は、上及び下の両方の方向を含み得る。装置は他の方向(例えば、90度回転したり、又は他の方向)を向くことができ、本明細書で使用される空間的に相対的な説明は、それに応じて解釈される。

10

【0017】

同様に、「高( high )」、「低( low )」、「プルアップ」、「プルダウン」、「1」、「0」などのような電気的な用語は、図面で示されるように、他の電圧レベル、他の構成や特徴との相対的な電圧レベル及び電流を示す説明の便宜のために、詳細な説明で使用される。電気的に相対的な用語は、図面に示された電圧又は電流に加えて使用や動作で、装置の他の基準電圧を含む。例えば、図面で、装置又は信号が反転されるか、他の基準電圧、電流又は電荷を使用している場合、「高」又は「プルアップ」と説明される構成は、新しい基準電圧又は電流と比較して、「低」又は「プルダウン」であり得る。つまり、「高」の用語は、相対的に低い又は高い電圧や電流のすべてを含み得る。装置は、他の電気的なフレームの基準に基づくことができ、詳細な説明で使用される電気的に相対的な説明に基づいて解釈される。

20

【0018】

詳細な説明で使用される用語は、単に特定の実施例について説明する目的のものであり、本発明の限定を意図するものではない。詳細な説明で使用されるように、単数形は、明確に別の方法で定義されていない限り、複数形を含む。「含む」という用語は、詳細な説明に使用される場合、列挙された特徴、ステップ、動作、要素、及び/又は構成の存在を特定するが、1つ又はそれ以上の他の特徴、ステップ、動作、要素、構成、及び/又はそれらのグループの追加若しくは存在を排除しない。

30

【0019】

例示的な実施例が理想的な実施例(及び中間構造)の例示的な図面である断面図を参照して、詳細な説明で説明される。このように、例えば、製造技術や許容誤差のような結果としての図面の形状からの変形が予想される。つまり、例示的な実施例は、詳細な説明で図示された特定の形状の領域に限定されず、例えば、製造からもたらされる形状の偏差を含む。例えば、長方形で図示された、注入領域は、一般的に、注入領域から注入されていない領域へのバイナリ変化というよりは、円形又は曲線のフィーチャー及び/又はエッジでの注入濃度の勾配を有する。同様に、注入によって形成された埋め込み領域は、埋め込み領域と注入される表面との間の領域に若干の注入をもたらし得る。したがって、図面に示された領域は、本質的に概略であり、その形状はデバイス領域の実際の形状を説明するものではなく、本発明の技術範囲を制限するものではない。

40

【0020】

別の方法で定義されていない限り、本明細書で使用されるすべての用語(技術的及び科学的用語を含む)は、当業者によって一般的に理解される意味を有する。さらに、一般的に使用される辞典に定義された用語のような用語は、関連技術のコンテキストにおける意味と一致する意味を有するものと解釈され、本明細書で定義されていない限り、理想的又は過度に形式的な意味として解釈されない。

【0021】

以下、本発明を実施するための形態の具体例を、図面を参照しながら詳細に説明する。

【0022】

50

図1は、本発明の一実施形態による装置の例示的な実施例を示す斜視図である。図1に示す実施例では、多数の集積回路ダイが積層されるか、又は集積されてマルチチップシステムを形成する。多様な実施例で、マルチチップシステムの装置100は、以下で説明するように、RASキャッシュやRAS回路を含むことができる。

【0023】

多様な実施例で、HBM(High Bandwidth Memory)は、高性能な形態のRAM(high-performance form of random access memory)を含むことができる。一部の実施例で、HBMは、TSV(through-silicon via)を使用して通信する積層されたDRAM(stacked dynamic RAM)メモリを含むことができる。一般的に、HBMはTSV(through-silicon via)とマイクロバンプとを組み合わせて、複数(例えば、4個、8個など)のダイ(die)のメモリセルアレイを互いの上部で連結する。一部の実施例で、メモリコントローラーは、積層の最下段に位置した別のダイに含まれ得る。

【0024】

図1に示す実施例で、装置100は、1つ又は1つ以上のメモリダイ(例えば、DRAMなど)104及びロジックダイ102を含むことができる。一実施例で、メモリダイ104及びロジックダイ102は、同一の製造工程を使用して製造されるか、生成され、又はそうでない可能性もある。

【0025】

図1に示す実施例で、メモリダイ104は、複数のメモリセルアレイ114を含むことができる。このような実施例で、メモリセルアレイ114は、データの多様な部分を格納するように構成され得る。一部の実施例で、データは、ロジックダイ102又は外部装置(例えば、以下で説明する外部プロセッサ又はホスト)によってアクセスされ得る。

【0026】

図1に示す実施例で、ロジックダイ102は、1つ又はそれ以上のロジック回路112を含むことができる。このような実施例で、ロジック回路112は、読み取り(リード)/書き込み(ライト)要請、又はより一般的にメモリセルアレイ114内にデータを格納したり、読み取ったりするメモリアクセスを受信するためのインターフェース(内部インターフェース)を含むことができる。多様な実施例で、ロジックダイ102は、以下で説明するように、RASキャッシュ又はRAS回路113を含むことができる。

【0027】

多様な実施例で、ロジック回路112は、1つ又はそれ以上のピア126(又はマイクロバンプなど)を使用して、メモリセルアレイ114と通信することができる。このような実施例では、バス又は外部インターフェースを介した通信に対する要求なしに、処理構成要素(例えば、ロジック回路112)と格納されたデータ(メモリセルアレイ114)との間の高速通信を可能する。

【0028】

多様な実施例で、装置100は、ルーティングダイ106を含むことができる。ルーティングダイ106は、ロジックダイ102とメモリダイ104との間で信号を動的に伝送するように構成され得る。多様な実施例で、ルーティングダイ106は、1つ又はそれ以上のピア126によってロジックダイ102に連結され得る。ピア126(又はそれらの部分)は、入力/出力(I/O: input/output)端子又はI/Oインターフェース123に接続され得る。このような実施例で、ルーティングダイ106は、I/Oインターフェース123と意図されたデータを格納するメモリセルアレイ114との間で信号を動的にルーティングすることができる。

【0029】

多様な実施例で、ルーティングは、ルーティング構造体116によって達成される。多様な実施例で、ルーティング構造体116は、例えば、マルチプレクサ、デマルチプレクサ、クロスバースイッチ、スイッチ、ロータリスイッチ、メモリスイッチ、クロスオーバ

10

20

30

40

50

ースイッチなど、多様なルーティング装置を含むことができる。上述した構成は、単に一部の例示的な実施例であり、本発明はこれに限定されない。

【0030】

一部の実施例で、ルーティング構造体116は、ロジック回路112のI/Oインターフェース123とメモリセルアレイ114の類似したI/Oインターフェース(123a又は123b)との間の入力/出力信号をルーティングするように構成され得る。図1に示す実施例では、2つの可能なルーティング方式が図示される。例えば、実線は、ロジック回路112を第1メモリ(メモリダイ104の左下隅に示す)のI/Oインターフェース123aに連結するのに使用される第1ルーティングを示す。点線は、ロジック回路112を第2メモリ(メモリダイ104の右側に示す)のI/Oインターフェース123bに連結するのに使用される第2ルーティングを示す。しかし、多様な実施例で、メモリセルアレイ114は、図1に示すように、分割されず、モノリシック(monolithic)であり得る。上述した内容は、単に一部の例示的な実施例であり、本発明はこれに限定されるものではない。

10

【0031】

図2Aは、本発明の一実施形態によるシステムの例示的な実施例を示すブロック図である。多様な実施例で、システム200は、多数の区分された集積回路、MCM、及び/又はシステム・オン・チップ(SoC:system-on-chip)の一部であり得る。多様な実施例で、システム200は、例えば、ラップトップ、デスクトップ、ワークステーション、PDA(personal digital assistant)、スマートフォン、タブレット、その他の適切なコンピュータ、又は仮想マシン若しくはそれらの仮想コンピューティング装置で使用され得る。

20

【0032】

一実施例で、システム200は、ホスト装置206を含むことができる。多様な実施例で、このようなホスト装置は、中央処理ユニット(CPU:central processing unit)、マザーボード(motherboard)、コンピューティングシステムを含むことができる。多様な実施例で、ホスト装置206は、コマンドを実行して、一般的に、データを読み書きするプロセッサ(図示せず)を含むことができる。これの一部として、ホスト装置206は、ソフトウェア又はファームウェアからなるドライバ242を実行することができる。図2Aに示す実施例で、ホスト装置206のドライバ242は、コンピュータに付着された、特定タイプの装置(例えば、プロセッサ204又はHBMダイ202)を制御したり、駆動したりするコンピュータプログラムを含むことができる。このような実施例で、ドライバ242は、ハードウェア装置にソフトウェイインターフェースを提供して、使用されているハードウェアの細かい項目を知らなくても、オペレーティングシステム(operating systems)及び他のコンピューティングプログラムがハードウェアの機能にアクセスできるようにする。

30

【0033】

図2Aに示す実施例で、システム200は、プロセッサ204を含むことができる。多様な実施例で、プロセッサ204は、多様なタイプのプロセッサ(例えば、グラフィックスプロセッサ(graphic processor)、中央プロセッサ(central processor)、装置専用プロセッサ(device specific processor)、物理演算プロセッサ(physics processor)など)のいずれか1つを含むことができる。説明の便宜のために、プロセッサ204は、グラフィックス処理ユニットGPU(graphic processing unit)であるとして説明するが、これは単に1つの例示的な実施例であり、本発明はこれに限定されるものではない。多様な実施例で、GPUであるプロセッサ204は、グラフィックスデータを生成したり、または作業を大量に並列演算するために使用される。

40

【0034】

多様な実施例で、プロセッサ204は、メモリコントローラ232を含むことができる。このような実施例で、メモリコントローラ232は、プロセッサ204からの、そ

50

してプロセッサ 204へのデータの流れを管理するように構成され得る。特に、図 2A に示す実施例で、メモリコントローラー 232 は、プロセッサ 204 と HBM ダイ 202 との間でのデータの流れを管理するように構成され得る。

【0035】

図 2A に示す実施例で、プロセッサ 204 は、ECC (error correction or correction) エンジン (又はエラー訂正回路) 234 を含むことができる。このような実施例で、ECC エンジン (又はエラー訂正回路) 234 は、HBM ダイ 202 から受信したデータの一部に、エラーが発生したか否かを検出するように構成され得る。多様な実施例で、ECC エンジン 234 は、メモリコントローラー 232 の一部であるか、またはメモリコントローラー 232 とともに集積され得る。多様な実施例で、ECC エンジン 234 はシングル又はダブルビットエラー (single or double bit errors) を検出するように構成され得る。上述した内容は、単に一部の例示的な実施例であり、本発明はこれに限定されない。

10

【0036】

図 2A に示す実施例で、プロセッサ 204 は、不揮発性メモリ 236 を含むことができる。多様な実施例で、メモリは、以下で説明するように、揮発性であるか、またはプロセッサ 204 の外部に位置し得る。このような実施例で、不揮発性メモリ 236 は、エラーがどのメモリアドレスに関連付けられているかについての情報を格納するように構成される。一部の実施例で、不良又はエラーの起きたメモリアドレスは、回避 (avoid) され得る。他の実施例で、不良又はエラーの起きたメモリアドレスは、良好な又は動作メモリセルにリマップされ得る。

20

【0037】

上述したように、図 2A に示す実施例で、不揮発性メモリ 236 により、このような不良又はエラーの起きたメモリアドレスは、プロセッサ 204 のパワーサイクリング中、記憶され得る。他の実施例では、揮発性メモリが使用され、不良又はエラーの起きたメモリアドレスは、各パワーサイクルで再検索される。他の実施例で、プロセッサ 204 は、ローカル又は集積された揮発性メモリを含むことができるが、プロセッサ 204 のパワーサイクルが終了した場合、プロセッサ 204 の外部に位置するか、または遠隔に位置する不揮発性メモリ (たとえば、ハードドライブ) にデータを格納することができ、プロセッサ 204 が再起動された場合、データを回収することができる。上述した内容は、単に一部の例示的な実施例であり、本発明はこれに限定されない。

30

【0038】

図 2A に示す実施例で、システム 200 は、上述のように、HBM ダイ、又はより正確には、HBM ダイ 202 のスタックを含むことができる。多様な実施例で、HBM ダイ 202 は、上述したように、複数のメモリセルアレイ 214 を含むことができる。多様な実施例で、メモリセルアレイ 214 は、複数の集積回路 (IC : integrated circuit) ダイ上に分散され、それぞれのメモリアドレスにデータを格納するように構成され得る。

30

【0039】

多様な実施例で、HBM ダイ 202 は、メモリセルアレイの ECC ストレージ 216 を含むことができる。このような実施例で、ECC ストレージ 216 は、メモリセルアレイ 214 に格納されたデータ内のエラーの検出を許容するか、または可能にする追加ビットの情報 (たとえば、パリティ) を含むことができる。多様な実施例で、ECC ストレージ 216 は、メモリセルアレイ 214 の一部であるか、又は物理的に分離されて、先に説明したのと同様に、複数の集積回路 (IC) ダイ上に分散され得る。このような実施例で、ECC データは、エラーを検出するために、ECC エンジン 234 によって使用される。

40

【0040】

多様な実施例で、HBM ダイ 202 は、プロセッサ 204 とホスト装置 206 との間で、それらと通信するように構成された HBM インターフェース 218 を含むことができる。多様な実施例で、システム 200 は、内部ダイ (例えば、プロセッサ 204 と HBM ダ

50

イ202との間)の通信を可能にする1つ又はそれ以上の通信バス(図示せず)を含むことができる。このような実施例で、これは、要請及び応答のようなメモリアクセスの伝送(transmission of memory accesses)を含むことができる。

#### 【0041】

多様な実施例で、HBMダイ202は、RAS(reliability, accessibility, and serviceability)キャッシュ又はRAS回路(又は信頼性回路)212を含むことができる。これらの実施例では、RAS回路212は、高速アクセス方式で少量のデータを格納する従来のキャッシュのように動作するよう構成されていない可能性があり、より大きなメモリは、追加のストレージを提供する。代わりに、RASキャッシュ又はRAS回路212は、メモリセルアレイ214内に発見されたエラーを訂正(又は訂正されたように見えるように)するか、または改善するためのバックアップ又は補助メモリとして動作するよう構成され得る。以下で説明するように、従来、メモリセルアレイ214内でエラーが検出された場合、広範かつ時間のかかる動作を行うことなく、エラーが訂正されるか、または回復されない可能性がある。RASキャッシュ又はRAS回路212を使用すれば、このような回復又は訂正がより迅速かつ効率的に達成され得る。

#### 【0042】

多様な実施例では、RAS回路212は、RASメモリ又は補助メモリ222(若しくは補助ストレージ)を含むことができる。多様な実施例で、補助メモリ222は、エラーに関連するか、または破損したメモリセルアレイ214の部分に対するデータを格納するよう構成され得る。このような構成の動作を、以下で説明する。

#### 【0043】

多様な実施例で、RAS回路212は、エラーに関連付けられているメモリアドレス(メモリセルアレイ214内の)のリストを格納して、このようなメモリアドレスエラーを補助メモリ222の部分にマッピングするよう構成されたアドレステーブル220を含むことができる。

#### 【0044】

図2Bは、本発明の一実施形態によるシステムの例示的な実施例を示すブロック図である。図2Bに示すシステム200は、システムがエラーを検出するのに伴う情報の流れとイベントの相対的なタイミングを示す。上述した内容は、単に1つの例示的な実施例であり、本発明はこれに限定されない。

#### 【0045】

エラー管理及び検出に関して、従来のGPUのメモリエラー管理は、一般的に以下のように処理される。まず、ECCエンジン234によって復旧不可能なエラー(non-recoverable error)が検出される。このようなエラーは、メモリセルアレイ214の特定のメモリアドレスに関連付けられ、一般的にダブルビットエラー又は2つのシングルビットエラーを含む。このようなエラーは、ドライバ242に通知される。

#### 【0046】

このような実施例で、ドライバ242は、この通知に従ってエラーをアプリケーション(図示せず)やホスト装置206の一部に報告する。ドライバ242は、メモリエラーをGPUの不揮発性メモリ236に記録(log)する。通常的には、現行のGPUの相互作用が発生するうちに、システムは、このようなエラーの再発を防止したり、または改善(回復)することができなかった。

#### 【0047】

しかしながら、システムの次の再付着(reattachment)、リセット(reset)、再起動(reboot)、又はGPUの相互作用の次のシーケンス若しくはシリーズにおいて、フレームバッファマネージャー(図示しないが、プロセッサ204の一部)は、エラーを含むリタイアされたページ(retired pages)をブラックリストに載せることができる。このような実施例で、メモリアドレス又はページは、これ

10

20

30

40

50

以上ストレージのために使用されない可能性がある。このように、メモリアドレス又はページは恒久的にリタイアされ、メモリの機能的な容量が減少する。

【0048】

このような従来の処理は、いくつかの問題点を有する。第1に、クライアント（例えば、ホスト装置やそこで駆動されるソフトウェア）が動作を維持しながら、ページをブラックリストに載せることは不可能である。第2に、部分的にGPUの現在のNVM（不揮発性メモリ）の容量のために、現在のGPUにおいてリタイア可能なページ又はメモリアドレスの個数が制限される。第3に、大きなリタイアグラニュラリティ（large retire granularity）が存在する。つまり、2ビットエラーは4KB（kilobyte）ページのリタイアを引き起こす。また、このような従来の処理は、結果的に、メモリセルアレイ214のより多くの部分がブラックリストに載るほど、より多くのメモリ容量の減少を起こす。

【0049】

図2Bに示す実施例で、システム200は、HBMモジュール又はHBMダイ202上に追加のロジック及びメモリを提供し、エラーをキャッシングして復旧することにより、このような状況を改善する。より詳細には、RAS回路212は、少なくとも数キロバイトの大きさでHBMのロジックダイに具現され得る。これは単に例示的な実施例であり、本発明はこれに限定されない。このようなRAS回路212は、ホスト装置206又はプロセッサ204によって受信されたメモリアドレスを格納するインデックス領域（index region）又はアドレステーブル220を含むことができ、HBMダイ202の内部エラー訂正メカニズムによって保護され得る。RAS回路212は、復旧されたデータ（与えられたサイズであり得る）を格納するように構成されたデータ領域（data region）又は補助メモリ222を含むことができる。アドレステーブル220と補助メモリ222の領域とは、1対1のマッピングを含むことができる。なお、このような領域は、HBMロジックダイと互換性のある技術（DRAM、SRAM、フラッシュなどの技術）で具現され得る。

【0050】

図2Bに示す実施例で、エラー検出処理は、与えられたメモリアドレスでエラーが発生したことを検出するECCエンジン234から開始される。矢印282で示すように、ECCエンジン234は、上述したように、ドライバ242に通知することができる。また、矢印284で示すように、ドライバ242は、これを不揮発性メモリ236に記録することができる。

【0051】

しかし、メモリアドレス又はページをブラックリストに載せて、プロセッサ204が、これ以上、即時使用されなくなるまで待つ代わりに、プロセッサ204は、HBMダイ202（またはHBMダイ202のロジックダイ）に与えられたメモリアドレスが不良（バッド）であることを知らせることができる（矢印286で示す）。HBMダイ202、より詳細には、RAS回路212は、エラー訂正動作を行うことができる。

【0052】

図2Bに示す実施例で、RAS回路212は、不良メモリアドレスをアドレステーブル220に記録するか、または入力することができる。不良メモリアドレスは、補助メモリ222の一部又はメモリアドレスにマッピングすることができる。多様な実施例で、当該メモリアドレスでメモリセルアレイ214に含まれるデータは、補助メモリ222のマッピングされた部分にコピー（エラーと全体）され得る。しかし、これはデータがエラーを含むので、好ましくない可能性がある。このような実施例で、プロセッサ204は、新しいデータ（エラーがないデータ）が再読み込みされる前に、HBMダイ202に格納される（書き込まれる）ことを要求できる。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

【0053】

このような実施例で、新しいメモリアクセス（例えば、読み込み又は書き込み）がメモ

10

20

30

40

50

リアドレスに発生した場合、R A S回路2 1 2は、そのメモリアドレスがアドレステーブル2 2 0に含まれているか（したがって、エラーに関連付けられているか）をチェックする。もしそうでなければ、メモリへのアクセスは正常に処理される。メモリアクセスは、メモリセルアレイ2 1 4によって遂行される。メモリアドレスがエラーに関連付けられている場合、メモリアクセスは、補助メモリ2 2 2、特にアドレステーブル2 2 0によってマップされたメモリアドレスの部分によって遂行される。

#### 【0 0 5 4】

このような本発明による実施例は、いくつかの利点を有する。第1に、不良メモリアドレスへのすべてのメモリアクセスは、補助メモリ2 2 2によって（プロセッサ2 0 4又はホスト装置2 0 6に）スムーズに遂行され得る。プロセッサ2 0 4は、クライアントに結合された途中であっても、これを達成し得る。プロセッサ2 0 4が結合解除されるか、使用されないか、または再付着の一部であるまで待つ必要がない。第2に、特定のメモリアドレスを補助メモリ2 2 2に再びマッピングすることにより、H B Mダイ2 0 2のストレージ容量が減少しない。ブラックリストに載せることなしに、H B Mダイ2 0 2は、同じ大きさのストレージ容量を有するように見える。第3に、R A S回路2 1 2は、多様なメモリマッピングの単位を提供することができる。従来の方法が、4 K Bページのブラックリストとリタイアを必要とするのに対し、R A S回路2 1 2は、キャッシュライン、ページ、及びメモリの他のサイズのマッピングを許容することができる。

#### 【0 0 5 5】

多様な実施例で、アドレステーブル2 2 0への新たなメモリアドレスの追加（矢印2 8 6）は、予め定められた、又は予備のメモリアドレス（p r e d e f i n e d o r r e s e r v e d m e m o r y a d d r e s s）への書き込み（ライト）のメモリアクセスを遂行するプロセッサ2 0 4（またはホスト装置2 0 6）を含むことができる。このような実施例で、R A S回路2 1 2は、このようなメモリアドレスへのある書き込みが、新たなエントリがアドレステーブル2 2 0に位置されることを意味するものと知ることができる。このような実施例で、書き込みのメモリアクセスのデータ部分は、不良メモリアドレスを含み得る。他の実施例で、アドレステーブル2 2 0への新たなメモリアドレスの追加（矢印2 8 6）は、新しいメッセージタイプやプロトコルの使用を伴い得る。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0 0 5 6】

多様な実施例で、プロセッサ2 0 4又はホスト装置2 0 6は、他の予め定められた、または予備のメモリアドレスへの読み込み（リード）のメモリアクセスを行うことにより、リマッピングのために利用可能な、または使用される補助メモリ2 2 2がどれくらい多いのかをチェックすることができる。このため、R A S回路（又は信頼性回路）は補助メモリの使用レベルを監視し、予め定められたメモリアドレスに使用レベルのインジケーターを格納するように構成される。このような実施例で、R A S回路は補助メモリ2 2 2の現在のストレージ容量や使用レベルでレジスタ又はメモリアドレスをアップデートすることができ、必要なときごとに、プロセッサ2 0 4又はホスト装置2 0 6は、メモリアドレスからリード（r e a d）することができる。多様な実施例で、リードは、このような空間が利用可能なことを確認するために、矢印2 8 6の動作の以前に行われ得る。いくつかの実施例で、補助メモリ2 2 2がいっぱいになるか、またはすべて使用中の場合は、プロセッサ2 0 4及びホスト装置2 0 6は、従来のブラックリスト／リタイア技法を使用することができる。他の実施例で、補助メモリ2 2 2の自由容量をチェックするのは、新しいメッセージタイプ又はプロトコルの使用を伴い得る。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0 0 5 7】

多様な実施例で、システム2 0 0が初期化されるときに（たとえば、ブートアップのとき）、情報がH B Mダイ2 0 2から（ホスト装置2 0 6又はプロセッサ2 0 4のいずれか1つによって）リード（r e a d）される。一実施例で、H B Mダイ2 0 2がR A S回路2 1 2をサポートするか、または含むかを判定することができる。一実施例で、使用され

10

20

30

40

50

るリマッピングユニットのレベル（例えば、256ビット、512ビットなど）が何なのかを判定することができる。他の実施例で、キャッシュ又は補助メモリ222のエントリ及び／又はアドレステーブル220のエントリがどのようにサポートされているかを判定することができる。多様な実施例で、このような確認は、予め定められた、若しくは予備のアドレスへのリード（read）のメモリアクセスによって、又は特定のメッセージやプロトコルによって行われる。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0058】

同様に、多様な実施例で、システム200が初期化されるときに（たとえば、ブートアップのとき）、情報又は設定が、HBMダイ202に（ホスト装置206又はプロセッサ204のいずれか1つによって）記入（格納）され得る。一実施例で、不良（バッド）メモリアドレスの既存のリストが（例えば、不揮発性メモリ236から）アドレステーブル220に格納される。他の実施例で、リマッピングユニットのレベル（例えば、256ビット、512ビットなど）が補助メモリ222に対して設定される。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0059】

図2Cは、本発明の一実施形態によるシステムの例示的な他の実施例を示すブロック図である。多様な実施例で、システム201は、先に説明した実施例の他の変形を示す。

#### 【0060】

この実施例では、ホスト装置206、プロセッサ204、及び先に説明した実施例と同じ構成要素を含むことができる。HBMダイ202、特にロジックダイは、独自のECCエンジン294を含むことができる。このような実施例で、HBMダイ202は、ホスト装置206及びプロセッサ204の支援を借りずに、メモリセルアレイ214内のエラーを検出し、補助メモリ222に不良メモリアドレスをリマッピングすることができる。多様な実施例で、不揮発性メモリの使用を通じて、リマップされたものが、実質的に永久的に維持され得る。他の実施例で、これがそれほど効率的ではないか、または好ましくないことで有り得るが、リマッピングが再起動後ごとに発生され得る。

#### 【0061】

このような実施例で、ECCエンジン294は、ECCエンジン234の代わりにエラーを検出することができる。このような実施例で、ホスト装置206及びプロセッサ204は、このようなエラーを認識しない可能性がある。多様な実施例で、ホスト装置206及びプロセッサ204は、上述した従来のブラックリスト／リタイア技法を使用し続けることができるが、HBMダイ202の内部改善活動により、ブラックリスト／リタイアが発生しないか、または稀にしか現れない。

#### 【0062】

多様な実施例で、矢印292で示すように、HBMダイ202のECCエンジン294は、不良メモリアドレスをアドレステーブル220に追加することができる。不良メモリアドレスは、その後、補助メモリ222の部分にマッピングされ、以後のメモリアクセスは、上述したように発生し得る。

#### 【0063】

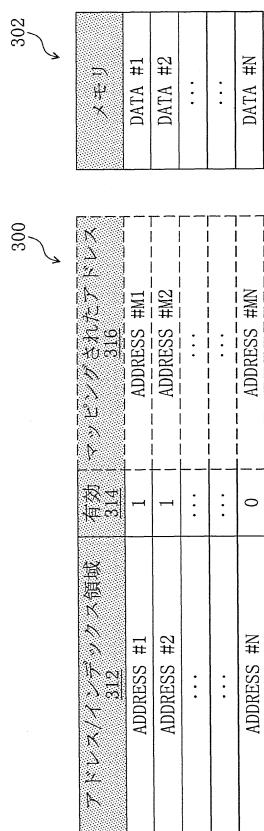

図3は、本発明の一実施形態によるデータ構造の一例を示す図である。図3に示す実施例で、データ構造（300、302）は、上述したように、RAS回路のアドレステーブル及び補助メモリを表すことができる。

#### 【0064】

図3に示す実施例で、データ構造300は、上述したアドレステーブル又はインデックス領域の1つの可能な実施例を表すことができる。このような実施例で、データ構造300（アドレステーブル又はインデックス領域）は、不良又はエラーの起きたメモリアドレス（またはページのようなメモリ領域）を格納するように構成され得る。多様な実施例で、このような不良メモリアドレスは、ホスト装置又はプロセッサから受信され得る。多様な実施例で、データ構造300は、ECC独自の形態により保護され得る。いくつかの実

10

20

30

40

50

施例では、図示しないが、データ構造 300 (アドレステーブル又はインデックス領域) は、データ構造 300 (アドレステーブル又はインデックス領域) 内のエラーから保護するエラー訂正コードの部分をさらに含み得る。

#### 【0065】

図 3 に示す実施例で、データ構造 300 の各行は、メモリアドレスのエントリと見なすことができる。このような実施例で、データ構造 300 は、どのメモリアドレスが不良であるかを指定する列 312 を含むことができる。これは、メモリアクセスが発生するときにチェックされて、上述のように、メモリアクセスが HBM メモリセルによって遂行されるか、または補助メモリによって遂行されるかを判定する列 312 であり得る。

#### 【0066】

図 3 に示す実施例で、各メモリアドレスのエントリは、有効ビット又は有効フラグ 314 の列を含み得る。このような実施例で、有効フラグ 314 は、それぞれのメモリアドレスのエントリが使用中であるか否かを示す。即ち、メモリアドレスのエントリがアクティブ状態であるか否かを示す。この実施例では、ホスト又はプロセッサがデータ構造 300 にエントリを格納するときに、有効フラグ 314 が設定され得る。他の実施例で、データ構造 300 は、周期的に (例えば、再起動の一部として) 消去され、有効フラグ 314 を含んでいない可能性がある。

#### 【0067】

多様な実施例では、各メモリアドレスのエントリは、タイプフィールドの列 (図示せず) を含むことができる。このような実施例で、エラーの改善がすべてのアドレスの使用を通じて、均一又は同一のサイズ (例えば、ワードや行ベース) で、フィールドが含まれていない可能性がある。しかし、図 3 に示す実施例で、各アドレスは、1 ビット、1 ワード、又は多様な個数のビットとともにエラー改善の他のレベル、サイズ、又はタイプと関連付けられる。いくつかの実施例では、フィールドは、修正されたメモリアドレスを通ったビット数を含むことができる。しかし、図 3 に示す実施例で、1 ビットの場合は値 1、1 ワードの場合は値 2 などのように予め定められた値が使用され得る。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0068】

図 3 に示す実施例で、各メモリアドレスのエントリは、マッピングされたアドレス 316 の列を含むことができる。この実施例で、マッピングされたアドレス 316 は、不良メモリアドレス (列 312) に関連付けられたデータが実際に格納される補助メモリ内のメモリアドレス又は位置であり得る。このような実施例で、メモリアクセスが不良メモリアドレスに対して発生する場合は、そのアクセスは予備のストレージにリダイレクトされるだけでなく、マッピングされたメモリアドレス 316 に再びアドレス指定される。多様な実施例で、これは固定マッピングであり得る。図 3 に示す実施例で、マッピングは 1 対 1 である。しかし、他の実施例で、マッピングは、関連性を有するように設定したり、または他の方式を使用したりできる。

#### 【0069】

図 3 に示す実施例では、データ構造 300 は、1 (又は Set) の有効フラグを含んで、アドレス (#M1) にマッピングされたメモリアドレスのエントリ (Address #1) を含むことができる。同様に、メモリアドレスのエントリ (Address #2) は、1 (又は Set) の有効フラグを含んで、アドレス (#M2) にマッピングされ得る。多数の他のメモリアドレスのエントリが存在し得る。最後に、メモリアドレスのエントリ (Address #N) は、0 (又は cleared) の有効フラグを含んで、アドレス (#MN) にマッピングされ得る。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0070】

図 3 に示す実施例で、データ構造 302 は、複数のメモリセルを含むことができ、複数のメモリセルのそれぞれは、それぞれのメモリアドレスからデータを格納するように構成され得る。多様な実施例で、データ構造 302 は、ECC 保護を使用することができる。

10

20

30

40

50

上述したように、不良メモリアドレスへのライト (write) のメモリアクセスが発生した場合、新しいデータは補助メモリ又はデータ構造 302 (例えば、Data #1、Data #2、Data #N) に格納される。上述したように、データが格納される位置は、メモリアドレスのエントリに基づく。

#### 【0071】

多様な実施例で、データ構造 302 は、任意の大きさであり得る。この実施例で、データ構造 302 は、150KB を含むことができるが、これは単に 1 つの例示的な実施例であり、本発明はこれに限定されない。多様な実施例では、単位のレベルは可変されるサイズ (例えば、256 ビット) であり得る。

#### 【0072】

いくつかの実施例で、RAS 回路は、他のサイズやエラーパターンを収容するための複数のデータ構造 (302、300) を含むことができる。例えば、多様な実施例で、RAS 回路はシングルビットデータエラー、シングルワードデータエラー、シングル行データエラー、及び / 又はシングル列データエラーのエラーパターンを収容し、それらのためのデータ構造を含むことができる。これは単に 1 つの例示的な実施例であり、本発明はこれに限定されない。

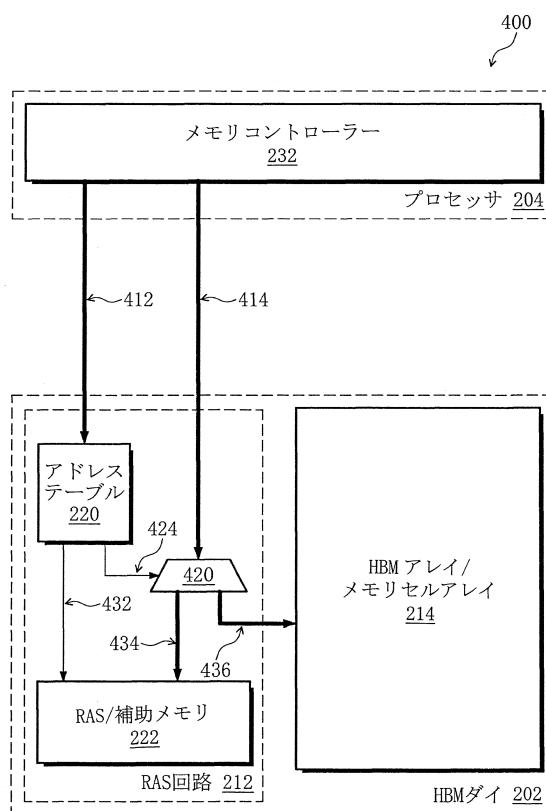

#### 【0073】

図 4A は、本発明の一実施形態によるシステムの例示的な実施例を示すブロック図である。図 4A に示す実施例では、ライト (write) のメモリアクセスが示される。これは単に 1 つの例示的な実施例であり、本発明はこれに限定されない。

10

20

#### 【0074】

図 4A に示す実施例で、システム 400 は、上述したように、プロセッサ 204 及び HBM ダイ 202 を含むことができる。多様な実施例で、プロセッサ 204 は、メモリコントローラ 232 を含むことができる。HBM ダイ 202 は、上述のように、HBM アレイ又はメモリセルアレイ 214 (ECC ストレージを含むことができる)、及び RAS 回路 212 を含むことができる。図 4A に示す実施例で、RAS 回路 212 は、上述のように、インデックス領域又はアドレステーブル 220、及び RAS メモリ又は補助メモリ 222 を含むことができる。図 4A に示す実施例で、システム 400 は、コマンドバス 412 及びデータバス 414 をさらに含むことができる。

#### 【0075】

30

図 4A に示す実施例で、メモリコントローラ 232 は、HBM ダイ 202 へのライト (write) のメモリアクセスを発行することができる。この実施例で、コマンド自体 (およびメモリアドレス) は、コマンドバス 412 によって伝送され、格納されるデータは、データバス 414 によって伝送される。これは単に 1 つの例示的な実施例であり、本発明はこれに限定されない。

#### 【0076】

ライト (書き込み) のメモリアクセスが受信された場合、RAS 回路 212 は、メモリアクセスに関連付けられたメモリアドレスがアドレステーブル 220 に格納されているか (そして有効であるか) 否かを判定する。アドレステーブル 220 は、アドレステーブルのヒット (アドレスが格納されている場合)、またはアドレステーブルのミス (アドレスが格納されていない場合) の信号を発生させ得る。これは信号 424 で示される。

40

#### 【0077】

図 4A に示す実施例で、RAS 回路 212 は、デマルチプレクサ (Demux : demultiplexer) 又はルーティング回路 420 を含むことができる。ルーティング回路 420 は、アドレステーブルのヒット / ミスの信号 424 に基づいて、データをメモリセルアレイ 214 又は補助メモリ 222 のいずれか 1 つへ伝送するように構成され得る。上述のように、アドレステーブルのヒットが発生した場合、ルーティング回路 420 は、格納されるデータを補助メモリに伝送する (矢印 434 で示される)。同様に、アドレステーブル 220 は、マッピングされたメモリアドレス 432 を生成し、それを補助メモリ 222 に伝送する。逆に、上述のように、アドレステーブルのミスが発生した場合、ル

50

ーティング回路 420 は、格納されるデータをメモリセルアレイ 214 に伝送する（矢印 436 で示される）。同様に、図示されていないが、コマンドバス 412 からのメモリアドレスは、データを格納するために、メモリセルアレイ 214 によって使用される。

【0078】

多様な実施例で、アドレステーブルのヒット／ミスの発生とは無関係に、データはメモリセルに常に格納され得る。このような実施例で、メモリセルアレイ 214 へのメモリアクセスを遂行するロジックは、RAS 回路 212 の追加を収容するように変更する必要はない。このような実施例で、アドレステーブルのヒットが発生した場合、データはメモリセルアレイ 214 及び補助メモリ 222 の両方に格納されるが、メモリセルアレイ 214 のデータは、以下に示すように、無視される。これは単に 1 つの例示的な実施例であり、本発明はこれに限定されない。

10

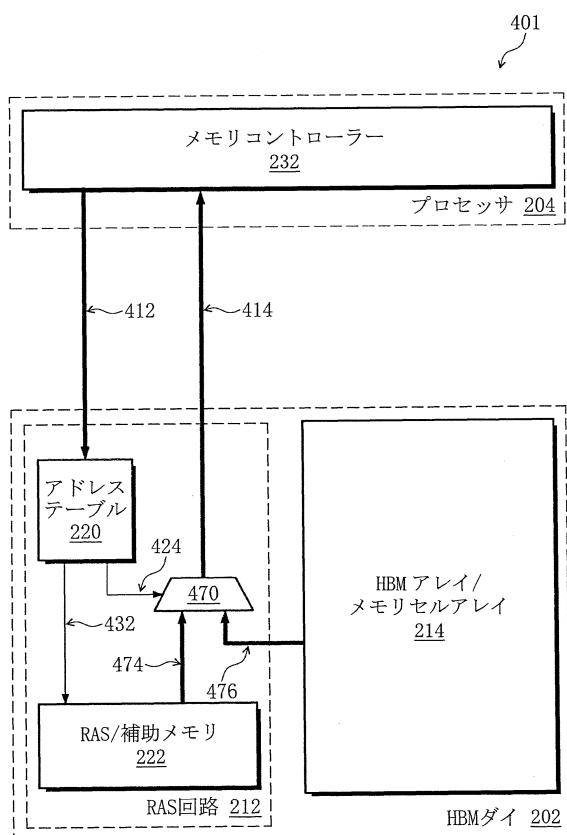

【0079】

図 4B は、本発明の一実施形態によるシステムの例示的な実施例を示すブロック図である。図 4B に示す実施例では、リード（read）のメモリアクセスが図示されている。これは単に 1 つの例示的な実施例であり、本発明はこれに限定されない。

【0080】

図 4B に示す実施例で、システム 401 は、上述のように、プロセッサ 204 及び HBM ダイ 202 を含むことができる。多様な実施例で、プロセッサ 204 は、メモリコントローラー 232 を含むことができる。HBM ダイ 202 は、上述のように、HBM アレイ又はメモリセルアレイ 214（ECC ストレージを含むことができる）、及び RAS 回路 212 を含むことができる。図 4B に示す実施例で、RAS 回路 212 は、上述のように、インデックス領域又はアドレステーブル 220、及び RAS 又は補助メモリ 222 を含むことができる。図 4B に示す実施例で、システム 401 は、コマンドバス 412 及びデータバス 414 をさらに含むことができる。

20

【0081】

図 4B に示す実施例で、メモリコントローラー 232 は、HBM ダイ 202 へのリード（read）のメモリアクセスを発行することができる。このような実施例で、コマンド自体（およびメモリアドレス）は、コマンドバス 412 によって伝送され、データはデータバス 414 によってリターンされる。これは単に 1 つの例示的な実施例であり、本発明はこれに限定されない。

30

【0082】

リード（read）のメモリアクセスが受信された場合、RAS 回路 212 は、メモリアクセスに関連付けられたメモリアドレスがアドレステーブル 220 に格納されているか（そして有効であるか）否かを判定する。アドレステーブル 220 は、アドレステーブルのヒット（アドレスが格納されている場合）、またはアドレステーブルのミス（アドレスが格納されていない場合）を発生する。これは信号 424 で示される。

【0083】

図 4B に示す実施例で、RAS 回路 212 は、マルチプレクサ（MUX：m u l t i p l e x e r）、ゲーティング、又はルーティング回路 470 を含むことができる。ルーティング回路 470 は、アドレステーブルのヒット／ミスの信号 424 に基づいて、メモリセルアレイ 214 又は補助メモリ 222 のいずれか 1 つからのデータをデータバス 414 に伝送するように構成される。上述のように、アドレステーブルのヒットが発生した場合、ルーティング回路 470 は、補助メモリから回収されたデータ（矢印 474 によって図示される）をデータバス 414 に伝送する。同様に、アドレステーブル 220 は、マッピングされたメモリアドレス 432 を生成し、それを補助メモリ 222 に伝送する。逆に、上述のように、アドレステーブルのミスが発生した場合、ルーティング回路 470 は、メモリセルアレイ 214 から回収されたデータ（矢印 476 によって図示される）をデータバス 414 に伝送する。同様に、図示されていないが、コマンドバス 412 からのメモリアドレスは、データを回収するために、メモリセルアレイ 214 によって使用される。

40

【0084】

50

多様な実施例で、上述のように、アドレステーブルのヒット／ミスの発生とは無関係に、データはメモリセルに常にライト（`w r i t e`）され得る。このような実施例で、データがメモリセルアレイ 214 のうちの不良又はエラーの起きたメモリアドレスに格納されても、ルーティング回路 470 は、不良又はエラーの起きたデータがデータバス 414 に存在することを防止できる。代わりに、補助メモリ 222 からの有用なデータ（`g o o d d a t a`）が使用される。このような実施例で、データはメモリセルアレイ 214 から常にリード（`r e a d`）され、その後、ルーティング回路 470 によってゲーティングされ得る。

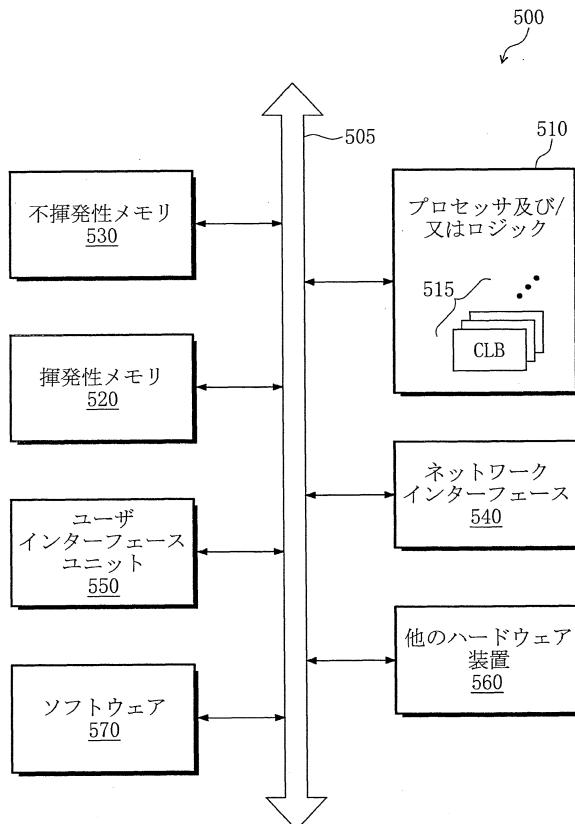

【 0 0 8 5 】

図 5 は、本発明の実施形態の原理に基づいて形成された半導体装置を含む情報処理システムの概念的なブロック図である。

10

【 0 0 8 6 】

図 5 を参照すると、情報処理システム 500 は、本発明の実施形態の原理に基づいて構成された 1 つ又はそれ以上の装置を含むことができる。他の実施例で、情報処理システム 500 は、本発明の実施形態の原理に基づく 1 つ又はそれ以上の技法を使用するか、または実行することができる。

20

【 0 0 8 7 】

多様な実施例で、情報処理システム 500 は、例えば、ラップトップ、デスクトップ、ワークステーション、サーバ、ブレードサーバ、P D A ( *personal digital assistant* )、スマートフォン、タブレット及び他の適切なコンピュータのようなコンピューティング装置、又は仮想マシン若しくはそれらの仮想コンピューティングデバイスを含むことができる。多様な実施例で、情報処理システム 500 は、ユーザー（図示せず）によって使用され得る。

30

【 0 0 8 8 】

本発明による情報処理システム 500 は、中央処理ユニット（C P U : *central processing unit* ）、ロジック又はプロセッサ 510 をさらに含むことができる。一部の実施例で、プロセッサ 510 は、1 つ又はそれ以上の機能ユニットブロック（F U B ）や組み合わせ論理ブロック（C L B ）515 を含むことができる。このような実施例で、組み合わせ論理ブロックは、多様なブーリアン方式のロジック動作（例えば、N A N D 、N O R 、N O T 、X O R ）、安定化ロジックデバイス（例えば、フリップフロップ、ラッチ）、他のロジックデバイス、又はそれらの組み合わせを含むことができる。このような組み合わせロジックの動作は、単純又は複雑な方式で入力信号を処理して意図された結果を達成するように構成され得る。同期式組み合わせロジックの動作の一部の例示的な実施例を説明したが、本発明はこれに限定されるものではなく、非同期式動作、又はそれらの組み合わせを包含できる。一実施例で、組み合わせロジックの動作は、複数のC M O S ( *complementary metal oxide semiconductor* ) トランジスタを含むことができる。多様な実施例で、このようなC M O S トランジスタは、ロジック動作を遂行するゲートに整列され得るが、ただし、本発明の技術範囲に属する他の技術が使用され得る。

30

【 0 0 8 9 】

本発明による情報処理システム 500 は、揮発性メモリ 520（例えば、ランダムアクセスメモリ R A M ( *random access memory* ) ）をさらに含むことができる。本発明による情報処理システム 500 は、不揮発性メモリ 530（例えば、ハードドライブ、光メモリ、N A N D 又はフラッシュメモリ）をさらに含むことができる。一部の実施例で、揮発性メモリ 520 、不揮発性メモリ 530 、又はそれらの組み合わせ若しくは一部は、「記憶媒体（*storage medium* ）」と称される。多様な実施例で、揮発性メモリ 520 及び／又は不揮発性メモリ 530 は、半永久的な又は実質的に永続的な形態でデータを格納するように構成される。

40

【 0 0 9 0 】

多様な実施例で、情報処理システム 500 は、情報処理システム 500 が通信ネットワ

50

ークの一部となって、この通信ネットワークを通じて通信するように構成された1つ又はそれ以上のネットワークインターフェース540を含むことができる。Wi-Fi(登録商標)プロトコルの例として、IEEE (Institute of Electrical and Electronics Engineers) 802.11g、IEEE 802.11nを含むことができるが、これに限定されない。セルラープロトコルの例は、IEEE 802.16m(別名、Wireless-MAN (Metropolitan Area Network) Advanced)、LTE(登録商標)(Long Term Evolution) Advanced、Enhanced Data rates for GSM(登録商標)(Global System for Mobile Communications) Evolution (EDGE)、Evolved High-Speed Packet Access (HSPA+)を含むことができるが、これに限定されない。有線プロトコルの例は、IEEE 802.3(別名、Ethernet)、ファイバチャネル(Fibre Channel)、電力線通信(Power Line communication)(例えば、ホームプラグ、IEEE 1901)を含むことができるが、これに限定されない。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0091】

本発明による情報処理システム500は、ユーザーインターフェースユニット550(例えば、ディスプレイアダプタ、ハブティックインターフェース、ヒューマンインターフェース装置)をさらに含むことができる。多様な実施例で、このようなユーザーインターフェースユニット550は、ユーザーから入力を受信したり、ユーザーに出力を提供したりするように構成され得る。他の種類の装置がユーザーとの相互作用を提供するために使用されることができ、例えば、ユーザーに提供されるフィードバックは、感覚フィードバック(sensory feedback)の形態(例えば、視覚フィードバック、聴覚フィードバック、又は触覚フィードバック)であり、ユーザーからの入力は、音、音声、又は触覚入力の形態で受信され得る。

#### 【0092】

多様な実施例で、情報処理システム500は、1つ又はそれ以上の他の装置やハードウェア構成(例えば、ディスプレイ又はモニター、キーボード、マウス、カメラ、指紋リーダー、ビデオプロセッサ)(以下、他のハードウェア装置560という)を含むことができる。上述した内容は、単にいくつかの例示的な実施例であり、本発明はこれに限定されない。

#### 【0093】

本発明による情報処理システム500は、1つ又はそれ以上のシステムバス505をさらに含むことができる。このような実施例で、システムバス505は、プロセッサ510、揮発性メモリ520、不揮発性メモリ530、ネットワークインターフェース540、ユーザーインターフェースユニット550、並びに1つ又はそれ以上のハードウェア構成560を通信的に連結するように構成され得る。プロセッサ510によって処理されたデータ、又は不揮発性メモリ530の外部から入力されたデータは、不揮発性メモリ530又は揮発性メモリ520のいずれか1つに格納され得る。

#### 【0094】

多様な実施例では、情報処理システム500は、1つ又はそれ以上のソフトウェア構成(以下、ソフトウェア570という)を含むか、または実行することができる。一部の実施例で、ソフトウェア570は、オペレーティングシステムOS (operating system)及び/又はアプリケーションを含み得る。いくつかの実施例で、OSは、1つ又はそれ以上のサービスをアプリケーションとして提供し、アプリケーションと情報処理システム500の多様なハードウェア構成(例えば、プロセッサ510、ネットワークインターフェース540)との間の仲介者(intermediary)として管理し、または動作させることができる。このような実施例で、情報処理システム500は、ローカルに(例えば、不揮発性メモリ530内に)設置され、プロセッサ510によって直

10

20

30

40

50

接実行され、OSと直接相互作用するように構成された1つ又はそれ以上のネイティブ(native)アプリケーションを含むことができる。このような実施例で、ネイティブアプリケーションは、予めコンパイルされたマシン実行可能なコード(pre-compiled machine executable code)を含むことができる。一部の実施例で、ネイティブアプリケーションは、ソース又はオブジェクトコードをプロセッサ510によって実行される実行可能なコードに変換するように構成されたVM(virtual execution machine)(例えば、the Java(登録商標)Virtual Machine、the Microsoft(登録商標)Common Language Runtime)、又はスクリプトインターパリター(script interpreter)(例えば、csh(C shell)、AppleScript、AutoHotkey)を含むことができる。

#### 【0095】

上述の半導体装置は、多様なパッケージング技法を使用してカプセル化され得る。例えば、本発明の技術的思想に基づいて構成された半導体装置は、POP(package on package)技法、BGA(ball grid array)技法、CSP(chip scale package)技法、PLCC(plastic leaded chip carrier)技法、PDIP(plastic dual in-line package)技法、ダイ・インワッフルパック技法(die in waffle pack technique)、ダイ・インウェハー形成技法(die in wafer form technique)、COB(chip on board)技法、CERDIP(ceramic dual in-line package)技法、PMQFP(plastic metric quad flat package)技法、PQFP(plastic quad flat package)技法、SOIC(small outline package)技法、SSOP(shrink small outline package)技法、TSOP(thin small outline package)技法、TQFP(thin quad flat package)技法、SIP(system in package)技法、MCP(multi-chip package)技法、WFP(wafer-level fabricated package)技法、WSP(wafer-level processed stack package)技法、又は当業者によってよく知られている他の技法のいずれか1つを使用してカプセル化され得る。

#### 【0096】

方法のステップは、コンピュータプログラムを実行して、入力データに対して動作するか、または出力を生成することにより、機能を実行する1つまたはそれ以上のプログラム可能なプロセッサによって遂行される。方法のステップはまた、例えば、FPGA(field programmable gate array)又はASIC(application-specific integrated circuit)のような特定用途向けのロジック回路によって遂行され、装置は、特定用途向けのロジック回路として具現され得る。

#### 【0097】

多様な実施例で、コンピュータ読み取り可能な記憶媒体は、コマンドを含むことができ、コマンドが実行される場合、装置は、方法のステップの少なくとも一部を遂行することができる。一部の実施例で、コンピュータ読み取り可能な記憶媒体は、磁気媒体(magnetic medium)、光媒体(optical medium)、他の媒体、又はそれらの組み合わせ(例えば、CD-ROM、ハードドライブ、読み取り専用メモリ、フラッシュドライブ)が含まれる。このような実施例で、コンピュータ読み取り可能な記憶媒体は明確かつ非一時的に形象化された製造品であり得る。

#### 【0098】

本発明の技術的思想が例示的な実施例を参照して説明されたが、当業者は、本発明の思想及び技術範囲から逸脱せずに多様な変形及び変更を行うことができる。したがって、上

述した実施例は、単に説明のためのものであり、限定されないことが理解される。本発明の技術範囲は、上述の説明によって制限されたり、または限定されない。したがって、本発明の技術範囲は、実施例の範囲内でこのような変形及び修正のすべてを含むことが理解される。

## 【符号の説明】

## 【0099】

|                 |                  |    |

|-----------------|------------------|----|

| 100             | 装置               |    |

| 102             | ロジックダイ           |    |

| 104             | メモリダイ            |    |

| 106             | ルーティングダイ         | 10 |

| 112             | ロジック回路           |    |

| 113、212         | R A S回路          |    |

| 114、214         | メモリセルアレイ         |    |

| 116             | ルーティング構造体        |    |

| 123、123a、123b   | I/Oインターフェース      |    |

| 126             | ビア               |    |

| 200、201、400、401 | システム             |    |

| 202             | HBMダイ            |    |

| 204、510         | プロセッサ            |    |

| 206             | ホスト装置            | 20 |

| 216             | ECCストレージ         |    |

| 218             | HBMインターフェース      |    |

| 220             | アドレステーブル         |    |

| 222             | 補助メモリ            |    |

| 232             | メモリコントローラ        |    |

| 234、294         | ECCエンジン          |    |

| 236             | 不揮発性メモリ          |    |

| 242             | ドライバ             |    |

| 412             | コマンドバス           |    |

| 414             | データバス            | 30 |

| 420             | ルーティング回路         |    |

| 424             | 信号               |    |

| 432             | マッピングされたメモリアドレス  |    |

| 470             | ルーティング回路         |    |

| 500             | 情報処理システム         |    |

| 505             | システムバス           |    |

| 520             | 揮発性メモリ           |    |

| 530             | 不揮発性メモリ          |    |

| 540             | ネットワークインターフェース   |    |

| 550             | ユーザーインターフェースユニット | 40 |

| 560             | ハードウェア構成         |    |

| 570             | ソフトウェア構成         |    |

【図面】

【図 1】

【図 2 A】

10

20

30

【図 2 B】

【図 2 C】

40

50

【図3】

【図4 A】

10

20

30

40

【図4 B】

【図5】

50

---

フロントページの続き

テラス 527

(72)発明者 マラディ , クリシュナ

アメリカ合衆国 , 95135 カリフォルニア州 , サンノゼ , ロートレック ドライブ 4196

(72)発明者 チヨン 宏 忠

アメリカ合衆国 , 95032 カリフォルニア州 , ロスガトス , #6 カールトン アベニュー 120

審査官 坂東 博司

(56)参考文献 米国特許出願公開第2015/0199246 (US, A1)

特開2015-135577 (JP, A)

米国特許出願公開第2014/0082411 (US, A1)

(58)調査した分野 (Int.Cl. , DB名)

G06F 11/16

G06F 12/06

G06F 11/10