(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) 。 Int. Cl.

*H01L 29/78* (2006.01)

(45) 공고일자 2007년01월17일

(11) 등록번호 10-0670226

(24) 등록일자 2007년01월10일

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 사이프러스, 핀란드,

(30) 우선권주장 09/421,305 1999년 10월 20일 미국(US)

(73) 특허권자 어드밴스드 마이크로 디바이시즈, 인코포레이티드

미국 캘리포니아 94088-3453 서니베일 원 에이엠디 플레이스 메일 스텝68

(72) 발명자 주동-혁

미국캘리포니아95014쿠퍼티노스토니데일드라이브10220

## (74) 대리인

심사관 : 박근용

전체 청구항 수 : 총 23 항

(54) 비-부동 바디를 구비한 전계 효과 트랜지스터와 벌크실리콘 웨이퍼 상에 상기 전계 효과 트랜지스터를 형성하는 방법

### (57) 요약

실리콘 절연체(SOI) 전계 효과 트랜지스터(FET) 구조는 종래의 벌크 실리콘 웨이퍼 상에 형성된다. 상기 구조는 상기 FET의 과거 동작으로 인한 채널 영역들에서의 전하 축적에 의해 야기되는 부동 바디 효과를 제거하기 위해 상기 벌크 실리콘 기판과 상기 FET의 채널 영역 간의 전기적 연결부를 구비한다. 상기 구조를 형성하는 방법은 상기 FET 주변부 주위에 절연 트렌치를 형성하고, 상기 소스와 드레인 영역들과 상기 실리콘 기판 간의 결합 캐패시턴스를 감소시키거나 제거하기 위해 상기 활성 영역 밑에 언더컷을 형성함으로써, 상기 실리콘 기판의 다른 구조들로부터 상기 FET 활성 영역을 격리시키는 단계를 포함한다.

## 대표도

도 10

### 특허청구의 범위

#### 청구항 1.

반도체 기판 상에 전계 효과 트랜지스터를 형성하는 방법에 있어서,

- a) 상기 트랜지스터의 활성 영역을 상기 기판 상의 다른 구조들로부터 격리시키기 위해 상기 트랜지스터의 활성 영역 주변 부근에 절연 트렌치를 식각하는 단계;

- b) 상기 기판으로부터 상기 활성 영역의 하부 표면의 적어도 일부분을 격리시키기 위해 상기 절연 트렌치의 바닥에 절연 언더컷을 식각하는 단계; 및

- c) 중앙 채널 영역의 대향측 상에 소스 영역 및 드레인 영역의 각각으로부터 상기 활성 영역의 일부분을 도핑하는 단계를 포함하고, 여기서 상기 절연 언더컷은 상기 반도체 기판으로부터 상기 소스 영역 및 상기 드레인 영역 양쪽의 적어도 일부분을 격리시키거나, 혹은 상기 반도체 기판으로부터 상기 중앙 채널 영역의 적어도 일부분을 격리시키거나, 혹은 상기 소스 영역으로부터 상기 드레인 영역 방향으로 상기 중앙 채널 영역 아래로 연장하며;

여기서 상기 언더컷의 식각 및 도핑은 상기 중앙 채널 영역과 상기 기판 사이의 도전성 브리지를 형성하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 2.

제 1 항에 있어서, 상기 언더컷을 식각하는 단계는:

- a) 상기 트렌치의 측벽 및 바닥 상에 보호층을 형성하는 단계;

- b) 상기 층의 수직 비등방성 식각을 행하여 상기 층을 제거함으로써 상기 트렌치의 바닥에서 상기 반도체 기판을 노출시키는 단계; 및

- c) 상기 반도체 기판의 등방성 식각을 행하여 상기 언더컷을 형성하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 3.

제 2 항에 있어서, 상기 보호층은 실리콘 이산화물인 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 4.

제 2 항에 있어서, 상기 등방성 식각은 KOH 습식 식각을 이용하여 수행되는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 5.

제 2 항에 있어서, 상기 절연체를 형성하는 단계는 TEOS 또는 SiH<sub>4</sub> 중 적어도 하나를 이용하는 화학 기상 증착 공정을 이용하여, 상기 언더컷 및 상기 트렌치의 적어도 일부분을 충전하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 6.

제 1 항에 있어서, 상기 도전성 브리지는 상기 중앙 채널 영역보다 작은 단면 영역을 갖는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 7.

제 6 항에 있어서, 상기 도전성 브리지는 모든 대응하는 방향에서 상기 중앙 채널 영역보다 좁은 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 8.

제 1 항에 있어서, 상기 언더컷의 식각 및 도핑은 상기 중앙 채널 영역과 상기 기판 사이의 도전성 브리지를 형성하고, 상기 도전성 브리지는 상기 활성 영역보다 상당히 작은 단면 영역을 갖는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 9.

제 1 항에 있어서, 상기 도핑 전에, 상기 활성 영역 상에 게이트를 형성하는 단계를 더 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 10.

제 9 항에 있어서, 상기 게이트는 상기 도핑을 위한 마스크로서 동작하고, 그럼으로써 상기 중앙 채널 영역을 한정하고 상기 소스 영역 및 상기 게이트 영역과 상기 게이트를 정렬하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 11.

제 1 항에 있어서, 상기 절연 트렌치의 식각은 실리콘 질화물층을 형성하는 단계, 상기 실리콘 질화물층을 선택적으로 식각하는 단계 및 상기 절연 트렌치의 식각을 위해 상기 실리콘 질화물층을 식각 마스크로서 이용하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 12.

제 2 항에 있어서, 상기 반도체 기판의 등방성 식각을 수행하는 단계는 1,000 ~ 2,000Å 사이의 깊이로 상기 언더컷을 형성하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 13.

제 12 항에 있어서, 상기 반도체 기판의 등방성 식각을 수행하는 단계는 상기 활성 부분 아래로 1,000 ~ 2,000Å 사이의 거리를 연장하도록 상기 언더컷을 형성하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 14.

반도체 기판 상에 전계 효과 트랜지스터를 형성하는 방법에 있어서,

- a) 상기 기판 상의 다른 구조로부터 상기 활성 영역을 격리시키기 위해 상기 트랜지스터의 활성 영역의 주변 부근에 절연 트렌치를 식각하는 단계;

- b) 상기 기판으로부터 상기 활성 영역의 하부 표면의 적어도 일부분을 격리시키기 위해 상기 절연 트렌치의 하부에서 절연 언더컷을 식각하는 단계를 포함하고, 상기 단계는:

- i) 트렌치의 측벽 및 하부 상에 보호층을 형성하는 단계;

- ii) 상기 층의 수직 비등방성 식각을 행하여 상기 층을 제거함으로써 상기 트렌치의 하부에서 상기 반도체 기판을 노출시키는 단계; 및

- iii) 상기 반도체 기판의 등방성 식각을 행하여 상기 언더컷을 형성하는 단계를 포함하고;

- c) 상기 활성 영역 상에 게이트를 형성하는 단계;

- d) 상기 활성 영역의 일부분을 도핑하여 중앙 채널 영역의 대향측 상에 소스 영역 및 드레인 영역의 각각을 형성하는 단계를 포함하며, 여기서 상기 게이트는 상기 도핑을 위한 마스크로서 동작하고, 그럼으로써 상기 중앙 채널 영역을 한정하고 상기 소스 영역 및 상기 게이트 영역을 상기 게이트와 정렬시키며, 여기서 상기 절연 언더컷은 상기 반도체 기판으로부터 상기 소스 영역 및 상기 드레인 영역 양쪽의 적어도 일부분을 격리시키거나, 혹은 상기 반도체 기판으로부터 상기 중앙 채널 영역의 적어도 일부분을 격리시키거나, 혹은 상기 소스 영역으로부터 상기 드레인 영역 방향으로 상기 중앙 채널 영역 아래로 연장하며;

여기서 상기 언더컷의 식각 및 도핑은 상기 중앙 채널 영역과 상기 기판 사이의 도전성 브리지를 형성하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 15.

제 14 항에 있어서, 상기 도전성 브리지는 상기 중앙 채널 영역보다 작은 단면 영역을 갖는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 16.

제 15 항에 있어서, 상기 도전성 브리지는 모든 대응하는 방향에서 상기 중앙 채널 영역보다 좁은 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

#### 청구항 17.

제 14 항에 있어서, 상기 언더컷의 식각 및 도핑은 상기 중앙 채널 영역과 상기 기판 사이의 도전성 브리지를 형성하고, 상기 도전성 브리지는 상기 활성 영역보다 상당히 작은 단면 영역을 갖는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

**청구항 18.**

제 14 항에 있어서, 상기 반도체 기판의 등방성 식각을 수행하는 단계는 1,000 ~ 2,000Å 사이의 깊이로 상기 언더컷을 형성하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

**청구항 19.**

제 18 항에 있어서, 상기 반도체 기판의 등방성 식각을 수행하는 단계는 상기 활성 부분 아래로 1,000 ~ 2,000Å 사이의 거리를 연장하도록 상기 언더컷을 형성하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

**청구항 20.**

전계 효과 트랜지스터를 형성하는 방법에 있어서,

- a) 반도체 기판 내에 절연 트렌치를 식각하여 활성 영역을 한정하는 단계;

- b) 상기 절연 트렌치의 하부에 절연 언더컷을 형성하여 상기 기판의 나머지로부터 상기 활성 영역의 하부 표면의 일부분을 격리시키는 단계를 포함하고, 상기 단계는:

- i) 트렌치의 측벽 및 하부 상에 보호층을 형성하는 단계;

- ii) 상기 층의 수직 비등방성 식각을 수행하여 상기 층을 제거함으로써 상기 트렌치의 하부에서 상기 반도체 기판을 노출시키는 단계; 및

- iii) 상기 반도체 기판의 등방성 식각을 행하여 상기 언더컷을 형성하는 단계를 포함하고;

- c) 상기 활성 영역 상에 게이트를 형성하는 단계;

- d) 상기 활성 영역의 일부분을 도핑하여 중앙 채널 영역의 대향측 상에 소스 영역 및 드레인 영역의 각각을 형성하는 단계를 포함하며, 여기서 상기 게이트는 상기 도핑을 위한 마스크로서 동작하고, 그럼으로써 상기 중앙 채널 영역을 한정하고 상기 소스 영역 및 상기 게이트 영역을 상기 게이트와 정렬시키며, 여기서 상기 절연 언더컷은 상기 반도체 기판으로부터 상기 소스 영역 및 상기 드레인 영역 양쪽의 적어도 일부분을 격리시키거나, 혹은 상기 반도체 기판으로부터 상기 중앙 채널 영역의 적어도 일부분을 격리시키거나, 혹은 상기 소스 영역으로부터 상기 드레인 영역 방향으로 상기 중앙 채널 영역 아래로 연장하며;

여기서 상기 언더컷의 식각 및 도핑은 상기 중앙 채널 영역과 상기 기판의 나머지 사이의 도전성 브리지를 형성하고, 그럼으로써 상기 도전성 브리지를 통해 상기 중앙 채널 영역과 상기 기판의 나머지 사이에 전기적 연결부를 남겨두며; 그리고

상기 도전성 브리지는 상기 중앙 채널 영역보다 작은 단면 영역을 갖는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

**청구항 21.**

제 20 항에 있어서, 상기 도전성 브리지는 모든 대응하는 방향에서 상기 중앙 채널 영역보다 좁은 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

**청구항 22.**

제 20 항에 있어서, 상기 반도체 기판의 등방성 식각을 수행하는 단계는 1,000 ~ 2,000Å 사이의 깊이로 상기 언더컷을 형성하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

### 청구항 23.

제 22 항에 있어서, 상기 반도체 기판의 등방성 식각을 수행하는 단계는 상기 활성 부분 아래로 1,000 ~ 2,000Å의 거리를 연장하도록 상기 언더컷을 형성하는 단계를 포함하는 것을 특징으로 하는 전계 효과 트랜지스터 형성 방법.

**명세서**

#### 기술분야

본 발명은 실리콘 절연막(silicon on insulator: SOI) 전계 효과 트랜지스터 구조에 관한 것으로, 특히 종래의 실리콘 벌크 웨이퍼 상에 형성된 상기 구조에 관한 것이다.

#### 배경기술

종래의 반도체 디바이스 또는 벌크 반도체 디바이스는 P-형 또는 N-형 도전체 실리콘 중의 어느 하나의 웰(well)을 상기 반대 도전체의 실리콘 기판 웨이퍼에 주입함(implanting)으로써 반도체 재료에 형성된다. 게이트와 소스/드레인 확산들은 일반적으로 알려진 프로세스에 의해 제조된다. 상기 확산들은 금속-산화물-반도체(metal-oxide-semiconductor: MOS) 전계 효과 트랜지스터(field effect transistors: FETs)로서 알려진 디바이스들을 형성한다. 소정의 칩이 P-형과 N-형을 모두 사용하는 경우, 이는 상보형 금속 산화 반도체(complimentary metal oxide semiconductor: CMOS)로 알려진다. 상기 트랜지스터들의 각각은 회로들을 단락시키는 것을 방지하기 위해 다른 트랜지스터들로부터 전기적으로 격리되어야 한다. 상대적으로 넓은 범위의 표면 영역이 다양한 트랜지스터들의 전기적 격리를 위해 요구된다. 이 점에서 현재 기술의 목적인 크기 감소는 바람직하지 않다. 또한, 상기 소스/드레인과 벌크 기판간의 접합 커패시턴스(junction capacitance)와, 상기 드레인에서부터 상기 소스로의 "오프(off)" 상태 누설(state leakage) 모두는 전력 소모를 증가시킨다. 상기 접합 커패시턴스는 상기 트랜지스터를 사용하는 디바이스가 동작할 수 있는 속도를 저하시킨다. 상기 문제들은 CMOS 기술 디바이스의 크기, 전력 소모, 및 전압의 감소 상에서의 어려움을 야기한다.

상기 접합 커패시턴스 문제를 해결하기 위해, 실리콘 절연막 기술이 더욱 사용되고 있다. 그러나, SOI 전계 효과 트랜지스터는 부동 바디 효과(floating body effect)로 인한 어려움이 있다. 상기 트랜지스터의 채널 또는 바디가 고정 전위에 연결되지 않음으로써 상기 바디가 상기 트랜지스터의 최근 동작에 의존하는 전하를 띠기 때문에, 상기 부동 바디 효과가 발생한다.

상기 부동 바디 효과는 상기 트랜지스터에서의 전류-대-전압 곡선을 왜곡시키거나 비틀어지게 하며, 반대로 상기 트랜지스터를 동작시키는 동안에 임계 전압이 변동되도록 한다. 상기 문제는 특히 동적 랜덤 액세스 메모리(dynamic random access memory: DRAM)에서 사용되는 것과 같은 패스게이트(passgate) 디바이스에서 명백하고, 상기 임계 전압이 고정되어서 상기 트랜지스터가 상기 저장 커패시터로부터의 전하 누설을 방지하는 "오프" 위치에 있도록 하는 것이 중요하다.

따라서, 상기 SOI FET의 낮은 결합 커패시턴스와 낮은 "오프" 상태 누설 특성을 구비하고 부동 바디 전위의 단점을 겪지 않는 반도체 전계 효과 트랜지스터 구조, 및 그 구조를 형성하는 방법이 종래 기술에 매우 강하게 요구된다.

#### 발명의 상세한 설명

본 발명의 제 1 목적은 반도체 기판 상에 전계 효과 트랜지스터를 형성하는 방법을 제공하는 것으로, 상기 방법은 상기 기판 상의 다른 구조들로부터 활성 영역을 격리하기 위해 상기 트랜지스터의 상기 활성 영역의 주변 주위에 절연 트렌치(insulating trench)를 식각하는 단계 및, 상기 기판으로부터 상기 활성 영역의 표면의 하부의 적어도 일부를 격리하기 위해 상기 절연 트렌치의 하부에 절연 언더컷(insulating undercut)을 식각하는 단계를 포함한다. 상기 활성 영역의 일부는 중앙 채널 영역의 대향면상에 소스 영역과 드레인 영역을 각각 형성하기 위해 도핑될 것이다. 상기 절연 언더컷은 상기 소스 영역 및 드레인 영역 모두의 적어도 일부를 상기 실리콘 기판으로부터 격리시킬 수 있다. 또한, 상기 절연 언더컷은 상기 중앙 채널 영역의 적어도 일부분을 상기 실리콘 기판으로부터 격리시킬 수 있다.

상기 언더컷을 식각하는 단계는: a)상기 트렌치의 측벽과 하부 상에 보호층을 형성하는 단계와; b)상기 층의 수직 비등방성 식각을 수행하여 상기 층을 제거함으로써 상기 트렌치 하부에 실리콘 기판을 노출시키는 단계 및; c)상기 실리콘 기판의 등방성 식각을 수행하여 상기 언더컷을 형성하는 단계를 포함한다. 상기 등방성 식각은 KOH 습식 식각을 사용하여 수행될 수 있다. 상기 보호층은 실리콘 이산화물이고, 상기 언더컷을 채우는 단계는 SiH<sub>4</sub> 및 TEOS 중의 적어도 하나를 사용하는 화학 기상 증착을 수행하는 단계를 포함할 수 있다.

본 발명의 제 2 목적은 중앙 채널 영역과, 상기 중앙 채널 영역의 대향측들에 위치된 소스 영역과 드레인 영역을 포함하는 활성 영역과, 상기 활성 영역의 단면부보다 더 작은 단면 영역을 구비하고 상기 반도체 기판과 상기 중앙 채널 영역을 연속적으로 연결하는 브리지(bridge) 영역 및; 상기 반도체 기판 상에 형성된 다른 구조들로부터 상기 활성 영역과 브리지 영역을 격리시키는 절연체(insulator)를 포함하는 반도체 기판 상에 형성된 전계 효과 트랜지스터를 제공하는 것이다. 상기 중앙 채널 영역과, 상기 브리지 영역 및 반도체 기판은 동일한 도전성일 것이고, 상기 소스 영역과 드레인 영역은 반대의 도전성일 수도 있다. 상기 절연체는 상기 소스 영역과 상기 실리콘 기판 및 드레인 영역과 실리콘 기판간의 반도체 접합들이 적어도 크기에서 감소되거나 제거되는 것 중 하나가 되도록 상기 실리콘 기판으로부터 상기 소스 영역과 드레인 영역을 적어도 부분적으로 격리하기 위해 상기 활성 영역의 하부 표면에 도달할 수도 있다. 상기 절연체는 실리콘 이산화물일 수도 있다.

본 발명의 제 3 목적은 반도체 기판 상에 형성된 다수의 전계 효과 트랜지스터들을 포함하는 반도체 디바이스를 제공하는 것으로, 각 트랜지스터는: a)중앙 채널 영역과, 상기 중앙 채널 영역의 대향측들에 각각 소스 영역과 드레인 영역을 구비하는 활성 영역과; b)상기 활성 바디 영역의 단면부보다 더 적은 단면 영역을 구비하고, 상기 반도체 기판과 상기 중앙 채널 영역을 도전성으로 연결하는 브리지 영역 및; c)상기 다수의 트랜지스터들의 적어도 서로 다른 하나로부터 상기 활성 바디 영역과 브리지 영역을 격리시키는 절연체를 구비한다. 상기 중앙 채널 영역, 상기 브리지 영역과, 반도체 기판은 모두 동일한 도전성일 것이고, 상기 소스 영역과 드레인 영역은 반대 도전성일 수도 있다. 상기 절연체는 상기 소스 영역과 상기 실리콘 기판 및 드레인 영역과 실리콘 기판간의 반도체 접합들이 적어도 크기에서 감소되거나 제거되는 것 중의 하나가 되도록 상기 실리콘 기판으로부터 상기 소스 영역과 드레인 영역을 적어도 부분적으로 격리시키기 위해 상기 활성 영역의 하부 표면에 도달할 수도 있다. 상기 다수의 트랜지스터들 중의 적어도 2개를 격리시키는 절연체는 실리콘 이산화물일 수도 있다. 그러나, 종래의 실리콘 기술에 따르면, 상기 채널 영역(26)은 N-도전성 실리콘이고, 반면에 상기 소스 영역(28)과 드레인 영역(30) 각각은 P-도전성 실리콘이다.

### 실시예

본 발명은 도면들과 함께 상세히 하기에서 개시될 수도 있다. 도면에서, 동일한 참조번호는 전체적으로 동일한 구성요소를 지적하는데 사용된다.

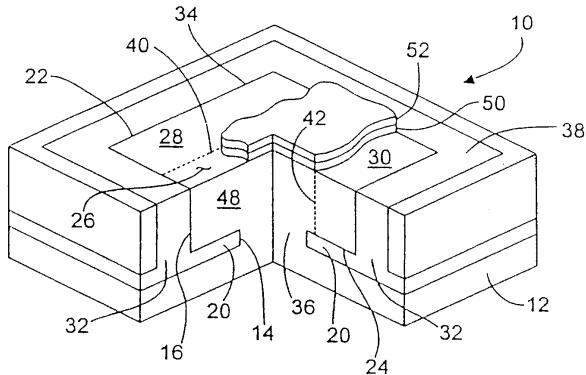

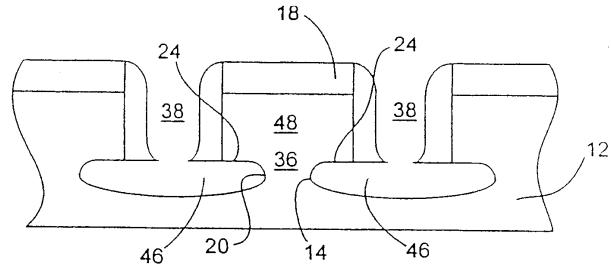

도 1은 본 발명에 따른 전계 효과 트랜지스터(10)의 활성 영역(48)이 채널 영역(26), 소스 영역(28) 및 드레인 영역(30)을 구비하는 것을 도시한다. 본 발명의 실시예에서, 상기 채널 영역(26)은 바람직하게는 P-도전성 실리콘이고, 반면에 상기 소스 영역(28)과 드레인 영역(30)은 각각 N-도전성 실리콘이고, 2개의 반도체 접합(40, 42)을 형성한다. 그러나, 종래 실리콘 기술에 따르면, 상기 채널 영역(26)은 N-도전성 실리콘이고, 반면에, 상기 소스 영역(28)과 드레인 영역(30)의 각각은 P-도전성 실리콘이다. 상기 활성 영역은 상기 FET(10)의 활성 영역(48)의 주변부(22)를 형성하는 측벽(16)을 구비한 절연 트렌치(32)에 의해 격리된다. 상기 절연 트렌치(32)는 상기 실리콘 기판(12)에 형성된 다른 구조들로부터 상기 활성 영역(48)을 절연시킨다. 상기 절연 트렌치(32)는 상기 활성 영역(48)의 하부 표면(24)을 형성하고 브리지 영역(36)의 측벽(14)을 형성하는 언더컷 영역(20)을 구비하고, 상기 브리지 영역(36)은 상기 활성 영역(48)의 채널 영역(26)을 상기 벌크 실리콘 기판(12)과 전기적으로 연결시킨다. 상기 활성 영역(48)과 브리지 영역(36)은 본 발명의 상기 FET(10)의 바디(34)를 함께 형성한다.

상기 브리지 영역(36)이 상기 채널 영역(26)과 상기 벌크 실리콘 기판(12)을 전기적으로 연결하기 때문에, 상기 채널 영역(26) 전위는 상기 실리콘 기판(12)의 전위 그대로이고, 상기 FET(10)의 과거(historical) 동작을 기준으로 하여 전하를 축적, 또는 부동(float)할 수 없음이 명백하다. 상기 절연 트렌치(32)는 언더컷 영역(20)을 포함하기 때문에, 상기 브리지 영역(36)의 단면 영역은 상기 활성 영역(48)의 단면 영역보다 현저하게 작고, 따라서 상기 소스 영역(28) 또는 상기 드레인 영역(30)과 상기 실리콘 기판(12) 간의 반도체 결합 또는 최소 크기 반도체 결합이 없으므로 결합 커페시턴스를 감소시키는 것이 명백하다.

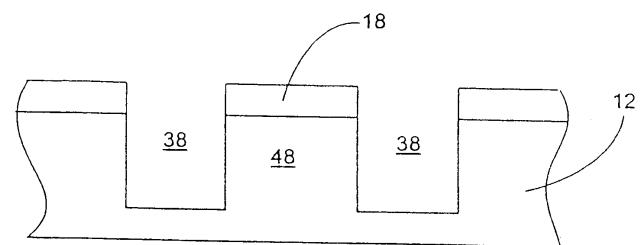

본 발명의 상기 FET(10)를 제조하는 제 1 단계는, 도 2에 나타난 대로, 약 1,500~2,000 Å 두께의 실리콘 질화물층(18)이 상기 벌크 실리콘 기판(12)의 표면 상의 약 150~200 Å의 산화물 박막(도시되지 않음)의 상부에 형성되는 것이다.

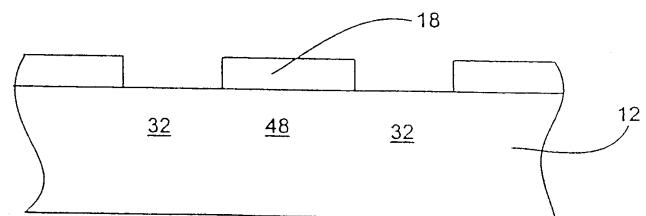

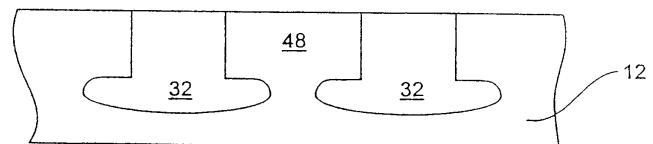

제 2 단계로, 상기 실리콘 질화물(18)은 상기 활성 영역(48)에 걸쳐 실리콘 질화물 마스크를 형성하기 위해 패턴되어 식각되고, 상기 절연 트렌치(32)가 도 3에서와 같이 형성된 상기 영역들에서의 상기 실리콘 기판을 노출시킨다. 상기 실리콘 질화물 마스크를 형성하기 위해 상기 실리콘을 패턴하고 식각하는 단계는 하기의 종래의 포토리소그래피 기술을 사용하여 수행되고, 상기 기술은 1)UV 감광성 포토레지스트층(photoresist layer)이 상기 실리콘 질화물(18)의 표면에 사용된다; 2)UV 조사 소스(illumination source) 및 레티클(reticle)은 상기 포토레지스트를 노출하고 패터닝하기 위해 시준된 광(collimated light)을 제공한다; 3)현상 용제(developer solution)가 상기 포토레지스트의 노출되지 않은 영역을 경화시키고, 상기 UV 광이 잃어지고 상기 현상액이 상기 노출된 부분들을 항상 세척하여 상기 노출된 부분이 상기 실리콘 질화물(18)의 표면 상에 마스크로서 잔재하도록 한다; 4)실리콘 질화물을 식각하고 상기 포토레지스트를 식각하지 않는 애칭 화합물을 사용하는 건식 식각은 상기 포토레지스트로 마스크되지 않은 영역내의 상기 실리콘 질화물층(18)을 제거하여 상기 실리콘 질화물 마스크를 생성한다.

본 발명의 상기 FET의 제조에서의 제 3 단계는, 상기 실리콘 기판(12)의 마스크되지 않은 부분(예를 들면, 상기 실리콘 질화물 마스크가 상기 제 2 단계에서 식각되지 않은 부분)이 도 4에 도시된 바와 같이 개방 트렌치(open trench)(38)를 형성하도록 약 2,000~4,000Å의 깊이로 식각된다. 상기 개방 트렌치(38)는 후에 실리콘 이산화물로 채워져서 도 1에 개시된 절연 트렌치(32)가 된다. 상기 실리콘 기판에 대한 식각 공정은 상기 실리콘 기판(12)을 식각하고 상기 실리콘 질화물(18)을 식각하지 않는 선택 특성을 지닌 취화 수소(hydrogen bromide)(HBr)를 사용하는 비등방성 건식 식각이다.

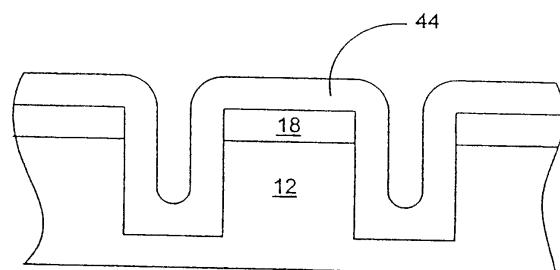

본 발명의 상기 FET(10)의 제조에서의 제 4 단계는 도 5에 도시된 바와 같이 상기 실리콘 질화물층의 전체 상부와 개방 트렌치(38)의 측벽과 하부를 포함하는 상기 웨이퍼의 모든 노출된 표면에 걸쳐 약 500~1,000Å의 실리콘 이산화물층(44)을 적층하는 단계를 포함한다. 상기 실리콘 이산화물층(44)을 적층하는 단계는 SiH<sub>4</sub>와 같은 가스를 사용하는 종래의 화학 기상 증착(CVD)을 이용하여 전형적으로 수행된다.

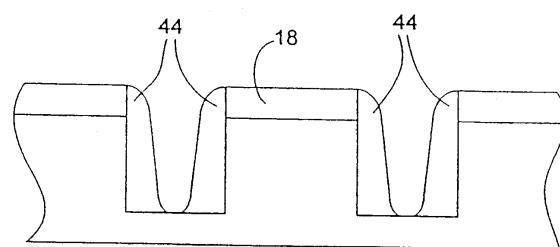

상기 실리콘 이산화물(44)의 적층에 이어, 상기 실리콘 이산화물층(44)의 수직 비등방성 식각은 상기 실리콘 질화물(18)의 표면과 상기 개방 트렌치(38)의 하부를 포함하여 모든 수평 표면으로부터 상기 실리콘 이산화물을 제거한다. 수직 비등방성 식각의 예는 CHF<sub>3</sub>를 사용하는 플라즈마 식각을 포함한다. 이러한 식각 기술은 상기 수직 식각의 순수 결과(net result)가, 수직 방향으로 균일한 두께의 이산화물층을 제거하여 실리콘 이산화물층이 상기 개방 트렌치(38)의 측벽(16)에 남아 있고 트렌치(38)의 하부는 노출된 실리콘 기판(12)인 것을 명백하게 한다.

본 발명의 상기 FET(10)의 제조에 있어서의 제 6 단계에서, 도 7에 도시된 바와 같이, 상기 개방 트렌치(38)의 하부에서의 상기 벌크 실리콘에 대한 등방성 식각이 수행되어 수평 및 수직 방향으로 약 1,000~2,000Å의 물질을 제거하고, 후속 단계에서 실리콘 이산화물로 충전되어 절연 트렌치(32)의 언더컷 영역(20)을 형성하는 개방 언더컷(46)을 형성한다. 상기 등방성 식각 단계는 바람직하게는 종래의 KOH 습식 식각이다. 또한, 그와 같은 식각 화합물을 상기 노출된 실리콘 기판(12)을 고속으로 식각하고 상기 개방 트렌치(38)의 측벽 상의 상기 실리콘 이산화물 피복(44)을 물질적으로 식각하지 않도록 선택 특성으로 선택되어야 하는 것이 명백하다. 상기 언더컷 영역(20)은 상기 활성 영역(48)의 하부 표면(24)과 상기 브리지 영역(36)의 측벽(14)을 한정한다.

상기 언더컷 영역(20)의 생성에 이어, 상기 개방 트렌치(38)는 실리콘 이산화물로 채워져서 절연 트렌치(32)를 형성한다. 상기 개방 트렌치(38)를 채우는 단계는 SiH<sub>4</sub> 또는 TEOS 등의 가스를 사용하는 종래의 CVD 공정을 사용하는 것이 바람직하다. 상기 개방 트렌치(38)를 채운 후, 도 8에 도시된대로, 상기 웨이퍼의 표면은 화학 기계적 연마(chemical mechanical polish)를 사용하여 연마되어 잉여의 실리콘 이산화물층과 남아있는 실리콘 질화물 마스크를 제거한다.

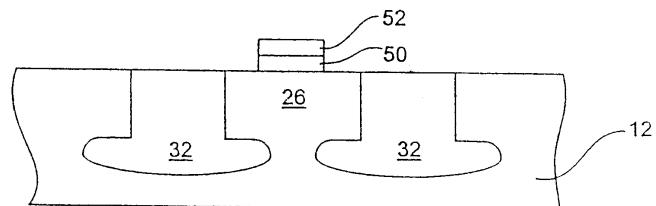

제 7 단계에서, 게이트 산화물층으로서 작용하는 실리콘 이산화물층(50)과 폴리실리콘 게이트(52)는 상기 기판의 상부 표면에 형성된다. 상기 실리콘 이산화물(50)은 열 산화 공정(thermal oxidation process)을 이용하여 상기 활성 영역(48)의 표면에서 전형적으로 성장되고 상기 폴리실리콘층은 저압 화학 기상 증착(low pressure CVD: LPCVD) 공정을 사용하여 상기 실리콘 질화물층(50)상에 증착된다. 상기 폴리실리콘층은 이전에 상술된 포토리토그래피 방법을 사용하여 패턴되고 식각되어 도 9에 도시된 바와 같이 종래의 자기 정렬 게이트, 소스 및 드레인 공정에서 상기 FET(10)의 상기 채널 영역을 한정하고 마스크한다.

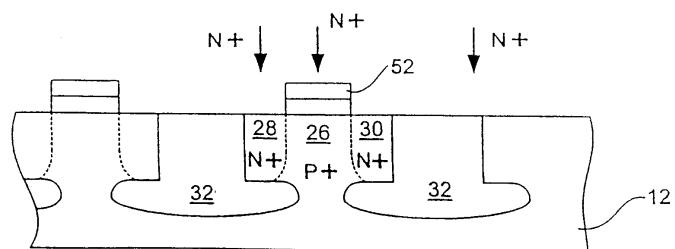

제 8 단계에서, 제 7 단계에서 적용된 게이트에 의해 마스크되지 않은 상기 FET(10)의 상기 채널 영역에서의 P-형 실리콘의 대향하는 측에 있는 상기 실리콘 기판의 일부분들이 N-형 실리콘으로 도핑된다. 도핑은 전형적으로 이온 주입 기술

(Ion implantation techniques)에 의해 수행된다. 비소(54)와 같은 불순물의 이온들은 전계에서 고속으로 가속되어 상기 타겟 웨이퍼에 충돌한다. 상기 이온들이 상기 폴리실리콘 게이트를 투과할 수 없기 때문에, 상기 폴리실리콘 게이트는 도 10에서 도시된 상기 노출된 소스 영역(28)과, 드레인 영역(30) 및 폴리실리콘 게이트(52)를 도핑하는 마스크로서 효율적으로 동작한다.

비록 본 발명이 특정의 바람직한 실시예로서 개시되지만, 균등물들과 변형물들은 본 명세서를 읽어 이해하는 때에 종래의 기술에 익숙한 사람에게 발생하는 것이 명백하다. 예를 들면, 실시예에서, 2개의 마스킹 단계들이 상기 개방 트렌치 영역(38)을 마스크하고 식각하는 데 사용된다. 포토레지스트 마스크는 실리콘 질화물 마스크를 생성하는데 사용되고 상기 개방 트렌치(38)의 식각에 영향을 미친다. 당업자는 만약 화합물이 상기 포토레지스트와 실리콘 기판 간에 선택적이면(예를 들면 상기 실리콘 기판을 식각하고 포토레지스트 마스크에 물질적으로 영향을 미치지 않는), 상기 포토레지스트 마스크는 상기 실리콘 기판에서 상기 개방 트렌치들을 직접적으로 식각하는데 사용되는 것으로 이해될 수 있다. 본 발명은 이러한 모든 균등물들과 변형물을 포함하고, 하기 청구범위의 범위에 의해서만 한정된다.

## 도면의 간단한 설명

도 1은 본 발명에 따른 실리콘 기판에 형성된 전계 효과 트랜지스터(FET)의 사시도, 부분적으로 단면도를 도시한다.

도 2는 본 발명인 상기 FET의 제공 단계에서의 제 1 단계의 단면도이다.

도 3은 본 발명인 상기 FET의 제공 단계에서의 제 2 단계의 단면도이다.

도 4는 본 발명인 상기 FET의 제공 단계에서의 제 3 단계의 단면도이다.

도 5는 본 발명인 상기 FET의 제공 단계에서의 제 4 단계의 단면도이다.

도 6은 본 발명인 상기 FET의 제공 단계에서의 제 5 단계의 단면도이다.

도 7은 본 발명인 상기 FET의 제공 단계에서의 제 6 단계의 단면도이다.

도 8은 본 발명인 상기 FET의 제공 단계에서의 제 7 단계의 단면도이다.

도 9는 본 발명인 상기 FET의 제공 단계에서의 제 8 단계의 단면도이다.

도 10은 본 발명인 상기 FET의 단면도이다.

## 도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10