(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2014/107665 A1

(43) International Publication Date

10 July 2014 (10.07.2014)

(51) International Patent Classification:

H01L 21/02 (2006.01)

(21) International Application Number:

PCT/US2014/010349

(22) International Filing Date:

6 January 2014 (06.01.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/749,872 7 January 2013 (07.01.2013) US

13/787,178 6 March 2013 (06.03.2013) US

(71) Applicant: KLA-TENCOR CORPORATION [US/US]; Legal Department, One Technology Drive, Milpitas, California 95035 (US).

(72) Inventors: SUN, Mei; 1059 Eastwood Drive, Los Altos, California 94024 (US). JENSEN, Earl; 625 Barto Street, Santa Clara, California 95051 (US). QULI, Farhat; 4324 Queen Anne Drive, Union City, California 94587 (US). SHARRATT, Stephen; 50 East Middlefield Road, Mountain View, California 94043 (US).

(74) Agent: MCANDREWS, Kevin; Kla-Tencor Corp., Legal Department, One Technology Drive, Milpitas, California 95035 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: HIGH TEMPERATURE SENSOR WAFER FOR IN-SITU MEASUREMENTS IN ACTIVE PLASMA

100

FIG. 1A

(57) Abstract: Aspects of the present disclosure disclose a component module in a process condition measuring device comprises a support for supporting a component, one or more legs configured to suspend the support in a spaced-apart relationship with respect to a substrate. An electrically conductive or low-resistivity semiconductor enclosure is configured to enclose the component, the support and the legs between the substrate and the enclosure. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

**HIGH TEMPERATURE SENSOR WAFER FOR IN-SITU MEASUREMENTS IN

ACTIVE PLASMA**

**CLAIM PRIORITY**

This application claims the priority benefit of commonly owned, co-pending U.S. Provisional

5 Patent Application number 61/749,872, to Mei Sun, filed January 7, 2013, and entitled

“HIGH TEMPERATURE SENSOR WAFER FOR IN-SITU MEASUREMENTS IN

ACTIVE PLASMA” the entire disclosures of which are incorporated herein by reference.

**FIELD OF THE INVENTION**

10 Embodiments of the present invention relate to high temperature process condition measuring

devices, and more particularly to an apparatus and a method that keeps the components of the

measuring device at an appropriate operating temperature and isolated from the plasma while

the device is exposed in a high temperature environment and/or an operational plasma

processing environment over an extend period of time.

**BACKGROUND OF THE INVENTION**

15 Semiconductor fabrication generally involves numerous sophisticated and complex

processing steps. Monitoring and evaluation of each process step is crucial to ensure the

manufacturing accuracy and to ultimately achieve the desired performance of a finished

device. Throughout numerous processes, such as the imaging process, deposition and growth

process, etching and masking process, it is critical, for example, that temperature, gas flow,

20 vacuum pressure, gas chemistry or plasma composition and exposure distance be carefully

controlled during each step. Careful attention to the various processing conditions involved

in each step is a requirement of optimal semiconductor or thin film processes. Any deviation

from optimal processing conditions may cause the ensuing integrated circuit or device to

perform at a substandard level or, worse yet, fail completely.

25 Within a processing chamber, processing conditions can vary. The variations in processing

conditions such as temperature, gas flow rate and/or gas composition greatly affect the

formation and thus the performance of the integrated circuit. Using a substrate-like device to

measure the processing conditions that is of the same or similar material as the integrated

30 circuit or other device provides the most accurate measure of the conditions because the

thermal conductivity of the substrate is the same as the actual circuits that will be processed. Gradients and variations exist throughout the chamber for virtually all processing conditions.

These gradients therefore also exist across the surface of a substrate. In order to precisely control processing conditions at the substrate, it is critical that measurements be taken upon

5 the substrate and that the readings are available to an automated control system or operator so that the optimization of the chamber processing conditions can be readily achieved.

Processing conditions include parameters used to control semiconductor or other device manufacture or conditions a manufacturer would desire to monitor.

Low profile wireless measuring devices are typically mounted on the substrate to measure the 10 processing conditions. For a low profile wireless measuring device to work in a high

temperature environment (e.g., temperatures greater than about 150°C), certain key

components of the device, such as thin batteries and microprocessors, must be able to function when the device is exposed to the high temperature environment. In general, the

back AR coating (BARC) process operates at 250°C; a PVD process may operate at about

15 300°C and a CVD process may operate at a temperature of about 500°C. Unfortunately,

batteries and microprocessors suitable for being used with the measuring devices cannot withstand temperature above 150°C. In addition, the measuring devices may be used for

measurement in an operational plasma processing environment. These devices may be exposed to harsh conditions such as excessive temperatures, corrosive chemicals, and

20 bombardment by high energy ions, and high levels of electromagnetic and other radiative

noise. Thus, it is desirable to have shielding that may block electrostatic fields and electromagnetic fields from interference with the signals from the measuring devices.

An additional challenge faced by such measuring devices is minimization of the device profile. Such devices should keep a profile of 5 mm or less above the top surface of the

25 substrate in order to fit into various process chambers.

It is within this context that embodiments of the present invention arise.

## SUMMARY OF THE INVENTION

According to aspects of the present disclosure, a component module in a process condition measuring device comprises a support configured to support a component; one or more legs

30 configured to suspend the support in a spaced-apart relationship with respect to a substrate;

and an electrically conductive or low-resistivity semiconductor enclosure configured to enclose the component, the support and the legs between the substrate and the enclosure.

According to additional aspects of the present disclosure, a process condition measuring device comprises a substrate; and one or more component modules mounted on the substrate.

- 5 The one or more component modules include a support for supporting a component, one or more legs configured to suspend the support in a spaced-apart relationship with respect to a substrate, and an electrically conductive or low-resistivity semiconductor enclosure configured to enclose the component, the support and the legs between the substrate and the enclosure.

- 10 An additional aspect of the present disclosure describes a process condition measuring device comprising a substrate with a shielding layer covering the substrate and one or more component modules mounted on the substrate. The one or more component modules are covered by an electrically conductive module shielding configured to provide electrical and thermal protection of the one or more component modules.

#### 15 BRIEF DESCRIPTION OF THE DRAWINGS

Objects and advantages of the invention will become apparent upon reading the following detailed description and upon reference to the accompanying drawings in which:

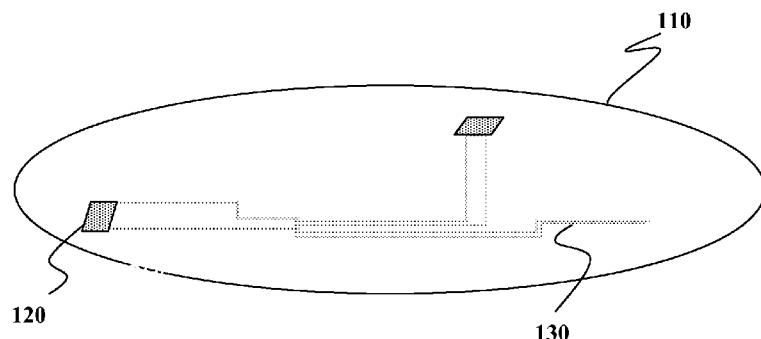

FIG. 1A is a schematic diagram of a process condition measuring device according to an embodiment of the present disclosure.

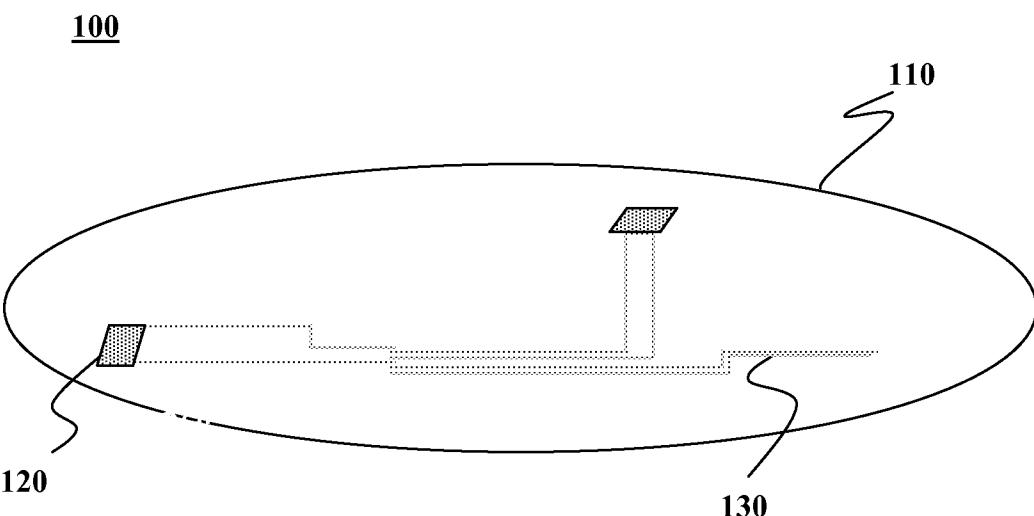

- 20 FIG. 1B is a schematic diagram of a process condition measuring device according to an embodiment of the present disclosure.

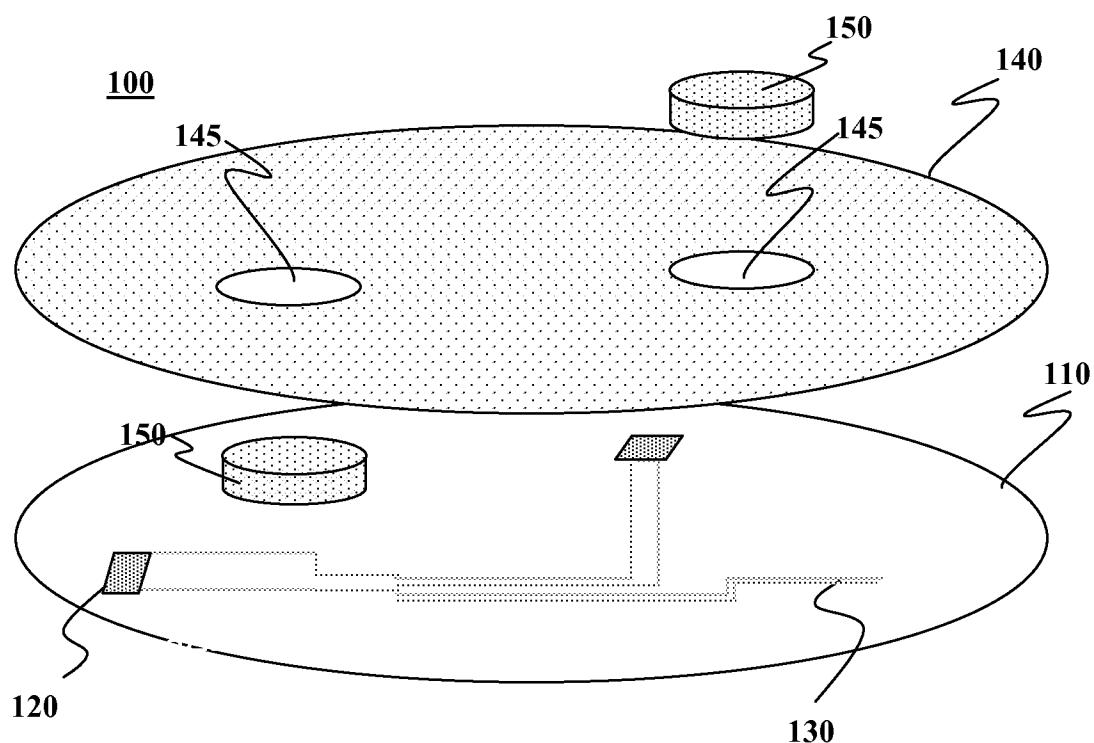

FIG. 2A is a cross-sectional view of a process condition measuring device with a component module according to an embodiment of the present disclosure.

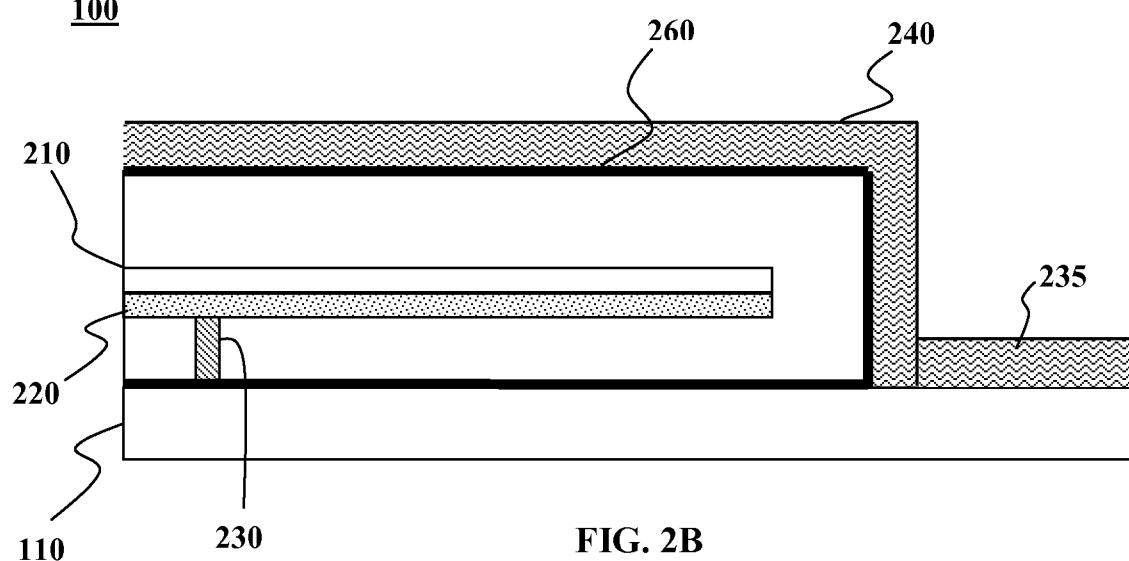

- 25 FIG. 2B is an enlarged cross-sectional view of a component module mounted on a process condition measuring device in accordance with an embodiment of the present disclosure.

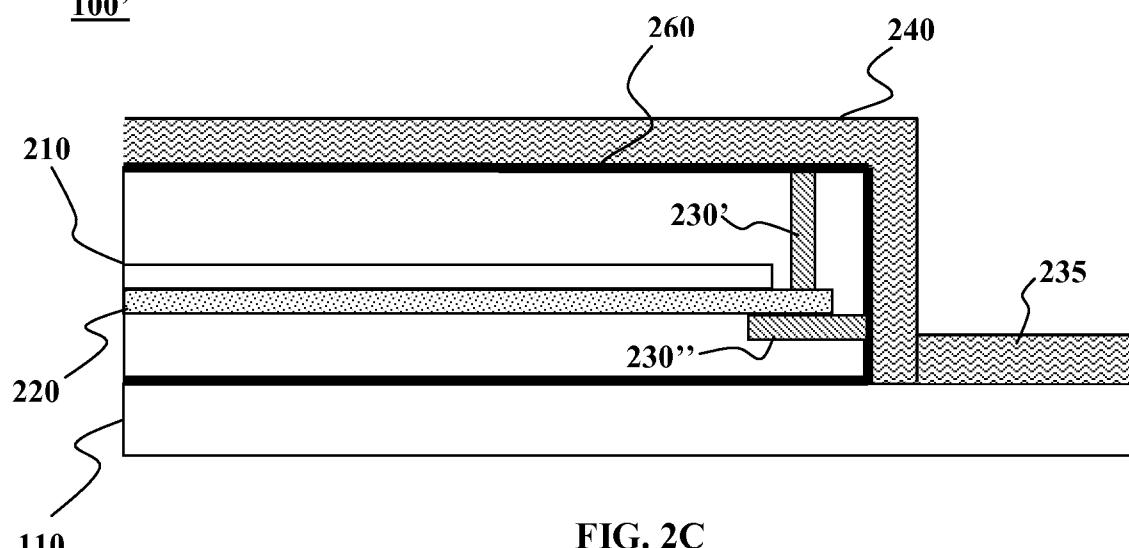

FIG. 2C is an enlarged cross-sectional view of a component module mounted on a process condition measuring device in accordance with an alternative embodiment of the present disclosure.

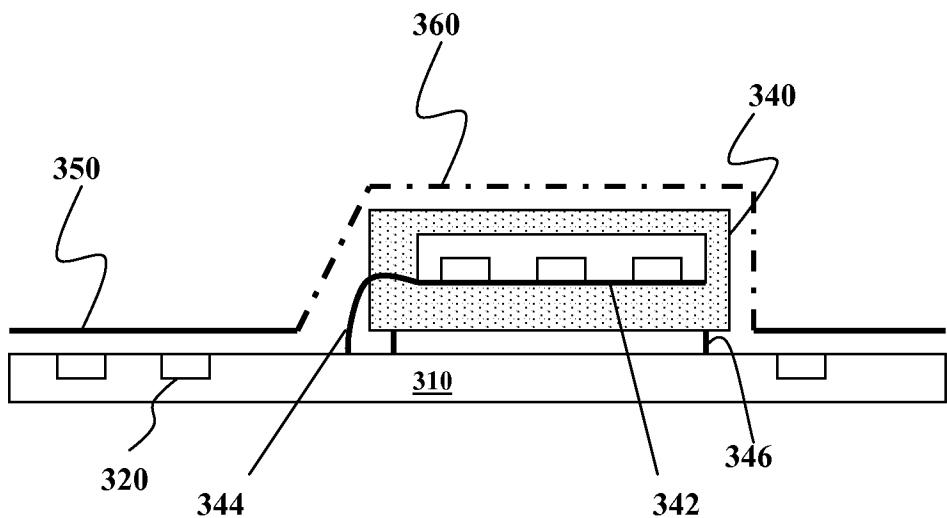

FIG. 3 is a cross-sectional view of a process condition measuring device with a component module according to an embodiment of the present disclosure.

#### DESCRIPTION OF THE SPECIFIC EMBODIMENTS

Although the following detailed description contains many specific details for the purposes of illustration, anyone of ordinary skill in the art will appreciate that many variations and alterations to the following details are within the scope of the invention. Accordingly, the exemplary embodiments of the invention described below are set forth without any loss of generality to, and without imposing limitations upon, the claimed invention. Additionally, because components of embodiments of the present invention can be positioned in a number of different orientations, the directional terminology is used for purposes of illustration and is in no way limiting. It is to be understood that other embodiments may be utilized and structural or logical changes may be made without departing from the scope of the present invention.

In this document, the terms “a” and “an” are used, as is common in patent documents, to include one or more than one. In this document, the term “or” is used to refer to a nonexclusive “or,” such that “A or B” includes “A but not B,” “B but not A,” and “A and B,” unless otherwise indicated. The following detailed description, therefore, is not to be taken in a limiting sense, and the scope of the present invention is defined by the appended claims.

Additionally, concentrations, amounts, and other numerical data may be presented herein in a range format. It is to be understood that such range format is used merely for convenience and brevity and should be interpreted flexibly to include not only the numerical values explicitly recited as the limits of the range, but also to include all the individual numerical values or sub-ranges encompassed within that range as if each numerical value and sub-range is explicitly recited. For example, a thickness range of about 1 nm to about 200 nm should be interpreted to include not only the explicitly recited limits of about 1 nm and about 200 nm, but also to include individual sizes such as but not limited to 2 nm, 3 nm, 4 nm, and sub-ranges such as 10 nm to 50 nm, 20 nm to 100 nm, etc. that are within the recited limits.

The remainder of the specification makes reference to components of process condition measuring devices when describing embodiments of the present disclosure. By way of example, and not by way of limitation, the electronic components may comprise a power or

energy source such as a battery, memory, transceiver, CPU, or any other electronic components configured to facilitate measurement and analysis of process conditions.

As defined herein, “processing conditions” refer to various processing parameters used in

manufacturing an integrated circuit. Processing conditions include any parameter used to

5 control semiconductor manufacture or any condition a manufacturer would desire to monitor such as, but not limited to, temperature, etch rate, thickness of a layer on a substrate,

processing chamber pressure, gas flow rate within the chamber, gaseous chemical

composition within the chamber, position within a chamber, electrical plasma properties,

light energy density, and vibration and acceleration of a wafer or other substrate within a

10 chamber or during movement to or from a chamber. Different processes will inevitably be developed over the years, and the processing conditions will, therefore, vary over time.

Whatever the conditions may be, it is foreseen that the embodiments described below can

measure such condition. In addition to measuring these conditions during the processing of

semiconductor wafers, the systems and techniques described herein may also be applied to

15 monitoring similar conditions during processing of other type of substrates, such as wafer masks.

FIG. 1A is a schematic diagram of a process condition measuring device. The measuring device **100** includes a substrate **110** with at least one sensor element **120** and necessary interconnect wiring **130**.

20 The substrate **110** may be the same size and shape as a standard substrate processed by a substrate processing system. The substrate **110** may be made of the same material as a standard substrate processed by the system. For example, if the measuring device is used to monitor process conditions in a semiconductor wafer processing system that processes silicon wafers, the substrate **110** may be made of silicon. Examples of standard sized silicon

25 substrate include, but are not limited to 150 mm, 200 mm, 300 mm and 450 mm.

Sensor element **120** and interconnect wiring **130** may be formed directly on the substrate

surface. By way of example, and not by way of limitation, sensor element **120** may be an

electromagnetic sensor, a thermal sensor, an optical or an electrical sensor. In one example,

sensors are made of a meandering conductive material. Details of various types of sensors

30 can be found in commonly assigned, co-pending U.S. Patent Application Ser. No. 12/892,841 filed September 28, 2010 and fully incorporated herein by reference for all purpose.

The device **100** may include a component module **150** that includes an electronic component. By way of example, and not by way of limitation, the component module **150** may include a power source, a memory, or a processor configured to execute instructions stored in the main memory in order for the measuring device **100** to properly measure and record process

5 parameters when the device is placed within a substrate processing tool. Certain elements of the measurement electronics may be included within a component module. By way of example, and not by way of limitation, a power source and a CPU each may be enclosed in a component module. As described in detailed below, one or more component modules are mounted on the substrate **110**.

10 Optionally, a cover **140** may be formed over the substrate **110** to cover the measurement sensor element **120** and interconnect wiring **130**. In one example, the cover **140** is made of high conductivity type silicon. Examples are highly Phosphorus doped Silicon, P+ and heavily Boron doped Silicon, N+ silicon. As shown in FIG. 1B, the cover **140** may have one or more through holes **145** to accommodate the component modules **150** which may be

15 mounted to the substrate **110** as described below. Alternatively, the component module **150** may be mounted to the cover **140**, which in turn covers substrate **110**.

FIG. 2A is a cross-sectional view of a process condition measuring device with component modules according to an embodiment of the present invention. As shown in FIG. 2A, two component modules **200** are mounted on the substrate **110**. FIG. 2B is an enlarged cross-sectional view of one component module **200**. The component module **200** includes temperature sensitive components with limited operational temperature range **210**, a support **220** for the component and a set of one or more legs **230** to be mounted to a substrate **110**. As shown in FIG. 2B, a support **220** may be mounted to the top surface of the substrate **110** by the one or more leg **230**. Alternatively, a support **220** may be mounted on the legs **230** 20 into substrate cavities formed in the top surface of the substrate (not shown).

25 By way of example, the components with limited operational temperature range **210** may be power source (e.g., battery, supercapacitor photovoltaic device), memory, transceiver, CPU, etc. There may be a single power source or alternatively more than one power source, depending on the application and resulting power needs. The component **210** may be very thin. By way of example, the component may have a total thickness of about 0.15 mm or less.

A component **210** is placed upon and supported by a support **220**. The support **220** may be made of a thin, flat and a high volumetric heat capacity material. In one example, the support is made of sapphire or alumina ( $Al_2O_3$ ). In one example, the support may have a cavity or recess so that the component may be sized and shaped to fit within the cavity or recess in the support **220**. The thickness of the support **220** may be about 0.5 mm.

One or more legs or posts **230** are mounted to a bottom surface of the support **220**. The legs **230** allow the component module **200** to be positioned away from the substrate **110** to form a gap between a top surface of the substrate or a surface of the enclosure **110** and a surface of the support **220**. Such a gap may be a vacuum, or at a very low pressure which provides an additional layer of thermal insulation. Thus, the thermal energy of substrate **110** is only poorly transferred to the support **220** and the component **210** because of the insulating layer formed by the gap/vacuum and the low thermal conductivity of the legs **230**. The gap need not be very large in order to obtain effective thermal insulation. By way of example, and not by way of limitation, effective thermal insulation may be obtained if the distance *d* between the top surface of the substrate and the bottom surface of the support is about 0.25 mm.

Additionally, the legs **230** may be configured to provide a very limited conductive thermal energy transfer path from the substrate **110** to the support **220**. In one example, legs **230** may be 1 mm in diameter or width (if not round) and 1 mm in height. Additionally, the cross-sectional dimensions of the legs **230** may be such that the legs are relatively long and thin in order to reduce the thermal energy transfer through the legs. Moreover, the thermal energy transfer efficiency between the substrate **110** and the support **220** may be limited by making the legs **230** from a high-strength low thermal conductivity material. By way of example, and not by way of limitation, these legs **230** may be composed of stainless steel, quartz, glass, foams or aerogels, or any other materials that are strong enough to hold the support **230** above the substrate and exhibit low thermal energy transfer characteristics.

An enclosure **240** is provided to cover the component **210**, the support **220** and the legs **230** for protection of the component inside the enclosure from ion bombardment and subsequent heating. The component module **200** may have a total thickness less than 3 millimeter. The enclosure **240** is preferably made of a semiconductor material that is the same material as standard production wafers. By way of example, the enclosure **240** and the substrate **110** may be made of a low resistivity semiconductor material, such as P+ silicon. Such a configuration is advantageous in that all exposed surfaces of the measuring device **100** are silicon. In some implementations, a cover **235** may be mounted over the substrate **110**, e.g.,

as illustrated in FIG. 1B. The cover **235** may include through-holes configured to receive the enclosure **240**. In such a case, the cover **235** and the enclosure **240** may be made of the same material, e.g., a conductive material or low-resistivity semiconductor, such as P+ silicon.

The thickness of the wall of the enclosure may be about 0.5 mm. The enclosure **240** is

5 evacuated and bonded to the substrate **110** or the cover **140** to form a vacuum seal and thereby further insulating the component **210**. Alternatively, the enclosure **240** need not be vacuum tight if the processing environment is maintained at a low enough vacuum level to increase the thermal delay. By way of example, a vacuum level in the enclosure **240** may be less than 20 mTorr.

10 The inside of the enclosure **240** may be polished to provide a low emissivity surface for further heat shielding. The surfaces of support **220** and the components **210** may also be treated to absorb less thermal energy. This can be achieved by polishing and or coating the surface with a low emissivity film. Alternatively the inside of the enclosure **240** may be coated with a low emissivity thin film material **260**. As used herein, a material having a

15 surface with an emissivity between 0.0 and 0.2 can be considered “low emissivity”.

Radiation from the process chamber, ion bombardment, and conduction from the substrate **110** contributes to the temperature increase on the top portion and sidewalls of the enclosure **240**. By polishing and coating, a significant reduction of the heat radiating from the inside portion of the top and sidewalls of the enclosure will be ensured. This will reduce heat

20 transfer by radiation to the components **210** and support **220** from the enclosure **240**, which would result in slower heating of the component **210**. By the way of example, a highly reflective material, e.g., gold, platinum, aluminum or any highly reflective film, may be coated on the inside of the enclosure to reduce emissivity and heat radiation from substrate **110** and enclosure **240**.

25 After one or more enclosure **240** is aligned on the substrate **110**, it is physically and electrically connected by bonding processes. The dimensions of the component module **200** may be constrained by the dimensions of the processing chamber in which the measuring device **100** is used. Consequently, the height of the component module **200** may be configured to meet the specification of the processing chamber. The height of the module

30 refers to the distance between the top surface of the substrate and the top surface of the enclosure **240**. By way of example, and not by way of limitation, the height of the module **200** may less than 3 mm, and preferably, less than 2 mm.

It is noted that many variations are possible on the implementation illustrated in FIG. 2B. For example, in some alternative implementations, the support **220** may be suspended from the inside of the enclosure **240**, e.g., as shown in the device **100'** depicted in FIG. 2C. In particular, the support **220** may be suspended from a top portion of the enclosure **240** e.g., by legs **230'** that extend downwards from a top of the enclosure. Alternatively, the support **220** may be suspended by legs **230''** that are attached one or more sides of the enclosure **240** that extend inward. In some implementations, the support **220** may be supported by a combination involving two or more of upward extending legs **230** attached to the substrate **110**, legs **230'** that extend from the top portion of the enclosure **240**, or legs **230''** attached to one or more sides of the enclosure that extend inward. As such, embodiments of the present disclosure are not limited to the implementations illustrated.

In some embodiments of the present disclosure described above, all exposed portions of the measuring device **100** may be made of high conductivity type silicon (e.g., P+ silicon) which is the same material as a standard silicon wafer. As a result, any contamination concerns can be eliminated. Additionally, the component module with a high conductivity type silicon enclosure electrically connects to a high conductivity type silicon substrate, thereby forming a Faraday shield around the component to prevent RF interference. Also, the component module is evacuated and vacuum sealed to the substrate or the cover so that the component inside the module has a significant delay of temperature rise relative to the wafer temperature. This would allow sufficient time for the measuring electronics to collect data in the chamber.

According to an aspect of the present disclosure, a measuring device **300** includes a substrate **310** with sensors **320** and interconnect wiring (not shown) formed on the surface of the substrate, and at least one component module **340** mounted on the substrate. The component module **340** may be any conventional module for enclosing temperature sensitive

components **342**, such as CPU or batteries. In one example, the component module **340** may be made of a high volumetric heat capacity material such as stainless steel. Stainless steel has high volumetric heat capacity, and as such requires a large input of thermal energy to rise in temperature. Alternatively, the module **340** may be composed of sapphire, Kovar®, Invar®, or any other material that exhibits a heat capacity similar to that of stainless steel.

Kovar is a trademark of Carpenter Technology Corporation of Reading, Pennsylvania. Kovar refers to a nickel-cobalt ferrous alloy designed to be compatible with the thermal expansion characteristics of borosilicate glass. The composition of Kovar is about 29% nickel, 7%

cobalt, less than 0.1% carbon, 0.2% silicon, 0.3% manganese with the balance being iron. Invar is a trademark of Imphy Alloys Joint Stock Company France of Hauts-De-Seine, France. Invar, also known generically as FeNi36 (64FeNi in the U.S.), is a nickel steel alloy notable for its uniquely low coefficient of thermal expansion. The component module 340 5 may be separated from substrate 310 on one or more legs 346. The component 342 may be electrically connected to the traces on the substrate 110 by wire bonding 344.

A shield layer 350 may cover sensors 320 and the interconnect wiring on the substrate 310. In one example, the shield layer 350 could be made of stainless steel, aluminum or copper. As for the component module 340, a module shielding 360 is provided to electrically and 10 thermally protect the component modules. As an example, the module shielding 360 may be made of stainless steel or aluminum foil. The module shielding 360 may be solid or mesh. The device 300 may have a thickness less than about 3 millimeters (e.g., about 2 to 3 millimeters) measured from a top of the shield layer 350 to a top surface of the substrate 310.

Aspects of the present disclosure provide component modules for process condition 15 measuring devices having robust electrical, thermal and electromagnetic shielding. Such shielding of component modules facilitates use of a process condition measuring device in a plasma environment.

The appended claims are not to be interpreted as including means-plus-function limitations, unless such a limitation is explicitly recited in a given claim using the phrase "means for."

20 Any element in a claim that does not explicitly state "means for" performing a specified function, is not to be interpreted as a "means" or "step" clause as specified in 35 USC § 112, ¶ 6. In particular, the use of "step of" in the claims herein is not intended to invoke the provisions of 35 USC § 112, ¶ 6.

## WHAT IS CLAIMED IS:

1. 1. A component module in a process condition measuring device, comprising:

2. a support configured to support a component;

3. one or more legs configured to suspend the support in a spaced-apart relationship with respect to a substrate; and

5. an electrically conductive or low-resistivity semiconductor enclosure configured to enclose the component, the support and the legs between the substrate and the enclosure.

1. 2. The component of claim 1, wherein the one or more legs are attached to a bottom surface of the support at one end and configured to attach to a top surface of a substrate at another end.

1. 3. The component of claim 1, wherein the one or more legs are attached to a top portion of the enclosure at one end and configured to suspend the support at another end.

1. 4. The component of claim 1, wherein the one or more legs are attached to a side of the enclosure at one end and configured to suspend the support at another end.

1. 5. The component module of claim 1, wherein the support is made of a high heat capacity material.

1. 6. The component module of claim 1, wherein the support is made of sapphire or alumina.

1. 7. The component module of claim 1, wherein the legs are made of stainless steel, quartz or glass.

1. 8. The component module of claim 1, wherein the legs are made of aerogel or foam.

2. 9. The component module of claim 1, wherein the enclosure is made of high conductivity type silicon.

1. 10. The component module of claim 1, wherein the pressure in the enclosure is less than 20 mTorr.

1. 11. A component module of claim 1, wherein inner surfaces of the enclosure are polished to form low emissivity surfaces.

- 1 12. A component module of claim 1, wherein inner surfaces of the enclosure are coated with

- 2 a low emissivity material.

- 1 13. A component module of claim 1, wherein an inside surface of the enclosure is polished or

- 2 coated with gold, platinum, aluminum or any highly reflective film.

- 1 14. A component module of claim 1, wherein the component module has a total thickness

- 2 less than 3 millimeter.

- 1 15. A component module of claim 1, wherein the component includes one or more power

- 2 sources.

- 1 16. A component module of claim 1, wherein the component includes a central processing

- 2 unit.

- 1 17. A process condition measuring device, comprising:

- 2 a substrate; and

- 3 one or more component modules mounted on the substrate,

- 4 wherein the one or more component modules include a support for supporting a

- 5 component, one or more legs configured to suspend the support in a spaced-apart

- 6 relationship with respect to a substrate, and an electrically conductive or low-resistivity

- 7 semiconductor enclosure configured to enclose the component, the support and the legs

- 8 between the substrate and the enclosure.

- 1 18. The device of claim 17, further comprising a cover covering the substrate, wherein the

- 2 cover has one or more through holes configured to accommodate the one or more

- 3 component modules.

- 1 19. The device of claim 18, wherein the cover and the enclosure are made of the same

- 2 material.

- 1 20. The device of claim 18, wherein the cover and the enclosure are made of high

- 2 conductivity type silicon

- 1 21. The device of claim 18, wherein the enclosure is sealed to the cover and has a pressure

- 2 less than 20 mTorr.

- 1 22. The device of claim 17, wherein the substrate and the enclosure are made of the same

- 2 material.

- 1 23. The device of claim 17, wherein the substrate and the enclosure are made of high

- 2 conductivity type silicon.

- 1 24. The device of claim 17, wherein inner surfaces of the enclosure are polished to form a

- 2 low emissivity surface.

- 1 25. The device of claim 17, wherein inner surfaces of the enclosure are coated with a low

- 2 emissivity material.

- 1 26. The device of claim 17, wherein the component module has a total thickness less than 3

- 2 millimeter.

- 1 27. The device of claim 7, wherein the enclosure is sealed to the substrate and has a pressure

- 2 less than 20 mTorr.

- 1 28. The device of claim 17, wherein the component includes one or more batteries.

- 1 29. The device of claim 17, wherein the component includes a central processing unit.

- 1 30. The device of claim 17, wherein the one or more legs are attached to a bottom surface of

- 2 the support at one end and configured to attach to a top surface of a substrate at another

- 3 end.

- 1 31. The device of claim 17, wherein the one or more legs are attached to a top portion of the

- 2 enclosure at one end and configured to suspend the support at another end.

- 1 32. The device of claim 17, wherein the one or more legs are attached to a side of the

- 2 enclosure at one end and configured to suspend the support at another end.

- 1 33. A process condition measuring device, comprising:

- 2 a substrate with a shielding layer covering the substrate; and

- 3 one or more component modules mounted on the substrate, wherein the one or more

- 4 component modules is covered by an electrically conductive module shielding configured

- 5 to provide electrical and thermal protection of the one or more component modules.

- 1 34. The device of claim 33, wherein the component modules are mounted on the substrate by

- 2 one or more legs.

- 1 35. The device of claim 33, wherein the shielding layer is made of high conductivity type

- 2 silicon, copper, aluminum or stainless steel.

- 1 36. The device of claim 33, wherein the module shielding is made of aluminum or stainless

- 2 steel.

- 1 37. The device of claim 33, wherein the module shielding is solid or mesh.

- 1 38. The device of claim 33, wherein the device has a thickness less than 3 millimeters from a

- 2 top of the module shielding to a top surface of the substrate.

1/3

FIG. 1A

FIG. 1B

2/3

100100100'

3/3

300

FIG. 3

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US2014/010349

## A. CLASSIFICATION OF SUBJECT MATTER

H01L 21/02(2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01L 21/02; G01P 1/02; H01R 33/00; G01P 15/02; H01L 31/09; G01J 1/02; H01L 27/14; H01L 21/00; H01L 23/04

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Korean utility models and applications for utility models

Japanese utility models and applications for utility modelsElectronic data base consulted during the international search (name of data base and, where practicable, search terms used)

eKOMPASS(KIPO internal) & Keywords: leg, component module, spaced-apart, enclosure, cover, sensor, shield

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                             | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | JP 2010-127657 A (PANASONIC ELECTRIC WORKS CO., LTD.) 10 June 2010<br>See abstract; paragraphs [0030]–[0083]; claims 1–7 and figures 1, 4, 13. | 1–2, 5–30             |

| Y         |                                                                                                                                                | 3–4, 31–32            |

| Y         | US 2005-0101161 A1 (KURT WEIBLEN et al.) 12 May 2005<br>See abstract; paragraphs [0035]–[0037] and figures 6a–7.                               | 3–4, 31–32, 34        |

| X         | US 2006-0065941 A1 (GILLES DELAPIERRE) 30 March 2006<br>See abstract; paragraphs [0029]–[0030], [0038] and figure 1.                           | 33, 35–38             |

| Y         |                                                                                                                                                | 34                    |

| A         | US 2010-0269590 A1 (SEBASTIAN GUENTHER et al.) 28 October 2010<br>See abstract; paragraphs [0019]–[0022]; claims 1–13 and figures 1–4.         | 1–38                  |

| A         | KR 10-0715112 B1 (OCAS INC.) 10 May 2007<br>See abstract; paragraphs [0020]–[0026]; claim 1 and figure 2.                                      | 1–38                  |

Further documents are listed in the continuation of Box C. See patent family annex.

|                                                                                                                                                                         |                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:                                                                                                                                |                                                                                                                                                                                                                                                  |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                                | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| "E" earlier application or patent but published on or after the international filing date                                                                               | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                                            | "&" document member of the same patent family                                                                                                                                                                                                    |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                  |                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                           |                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Date of the actual completion of the international search<br>30 April 2014 (30.04.2014)                                                                                                                                                   | Date of mailing of the international search report<br><b>30 April 2014 (30.04.2014)</b> |

| Name and mailing address of the ISA/KR<br>International Application Division<br>Korean Intellectual Property Office<br>189 Cheongsa-ro, Seo-gu, Daejeon Metropolitan City, 302-701,<br>Republic of Korea<br>Facsimile No. +82-42-472-7140 | Authorized officer<br>CHOI, Sang Won<br>Telephone No. +82-42-481-8291                   |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No.

**PCT/US2014/010349**

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                | Publication date                                                                               |

|----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| JP 2010-127657 A                       | 10/06/2010       | JP 5123146 B2                                                                                                          | 16/01/2013                                                                                     |

| US 2005-0101161 A1                     | 12/05/2005       | DE 10352002 A1<br>KR 10-1026556 B1<br>KR 10-2005-0044265 A<br>US 7323766 B2                                            | 09/06/2005<br>31/03/2011<br>12/05/2005<br>29/01/2008                                           |

| US 2006-0065941 A1                     | 30/03/2006       | EP 1640335 A2<br>EP 1640335 A3<br>EP 1640335 B1<br>FR 2875948 A1<br>FR 2875948 B1<br>JP 2006-095681 A<br>US 7745891 B2 | 29/03/2006<br>03/10/2007<br>12/06/2013<br>31/03/2006<br>08/12/2006<br>13/04/2006<br>29/06/2010 |

| US 2010-0269590 A1                     | 28/10/2010       | DE 102009002559 A1                                                                                                     | 28/10/2010                                                                                     |

| KR 10-0715112 B1                       | 10/05/2007       | None                                                                                                                   |                                                                                                |