(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-55500

(P2011-55500A)

(43) 公開日 平成23年3月17日(2011.3.17)

(51) Int.Cl.

H04L 1/00 (2006.01)

F 1

H04L 1/00

テーマコード(参考)

B 5K014

審査請求 未請求 請求項の数 9 O L (全 14 頁)

(21) 出願番号 特願2010-196274 (P2010-196274)

(22) 出願日 平成22年9月2日 (2010.9.2)

(31) 優先権主張番号 2125/CHE/2009

(32) 優先日 平成21年9月2日 (2009.9.2)

(33) 優先権主張国 インド (IN)

(特許庁注: 以下のものは登録商標)

1. イーサネット

(71) 出願人 500587067

アギア システムズ インコーポレーテッド

アメリカ合衆国, 18109 ペンシルヴァニア, アレンタウン, アメリカン パークウェイ エヌイー 1110

(74) 代理人 100094112

弁理士 岡部 謙

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100104352

弁理士 朝日 伸光

最終頁に続く

(54) 【発明の名称】誤り保護されたパケットベース・フレーム用の受信機

## (57) 【要約】

【課題】FEC復号化の待ち時間およびパケット・バッファのサイズが著しく低減する、FEC復号化のための受信機および方法を提供すること。

【解決手段】一実施形態では、リアルタイム伝送プロトコル (RTP) および前方誤り訂正 (FEC) を利用するメディア・パケットのフレーム用の受信機を開示する。この受信機は、パケット・バッファおよびFECデコーダを備える。パケット・バッファがパケットを受信した後に、FECデコーダは、このパケットを読み取り、FEC処理の一部として、フレーム全体 (または、実際にはフレームの任意の後続パケット) を受信するのを待つことなく、このパケットに対して XOR 演算を実行する。フレーム内の欠落パケットを再構成するのに十分なパケットを受信するまで、XOR 演算の結果が蓄積される。このXOR演算は、後続のパケットを待つことによるいかなる遅延もなく、パケットを受信した後ただちに実行されるので、受信機の待ち時間は非常に少なく、パケット・バッファは相対的に小さくてもよい。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

- 受信機内で誤り訂正(ＥＣ)処理を実行するための方法であって、

(a) 3つ以上のデータ・パケットおよびＥＣパケットを含む第1のフレームのパケットのサブセットを連続的に受信すること、ならびに

(b) 前記第1のフレームのパケットの前記サブセットにＥＣ処理を実行して、前記第1のフレームのうちの少なくとも1つのパケットを再構成することであって、前記ＥＣ処理が、パケットの前記サブセット全体を受信する前に開始されることを含む方法。

**【請求項 2】**

前記ＥＣ処理は、前記サブセット内の後続パケットの受信を待つことなく、受信すると前記サブセット内の各パケットを処理することを含む、請求項1に記載の発明。 10

**【請求項 3】**

- 前記サブセット内の少なくとも1つの受信パケットについて、前記ＥＣ処理は、

(b1) 前記受信パケット、およびメモリに格納された値に数学演算を実行すること、ならびに

(b2) 後続の数学演算用に前記メモリ内に格納される値として、前記数学演算の結果を格納することを含む、請求項2に記載の発明。

**【請求項 4】**

- 前記サブセット内の最後の受信パケットについて、前記ＥＣ処理は、

(b3) 前記最後の受信パケット、および前記メモリに格納された前記値に最後の数学演算を実行すること、ならびに

(b4) 前記最後の数学演算の結果に基づいて、前記第1のフレームの欠落データ・パケットを再構成することを含む、請求項3に記載の発明。 20

**【請求項 5】**

- (c) 3つ以上のデータ・パケットおよびＥＣパケットを含む第2のフレームのパケットのサブセットを連続的に受信すること、ならびに

(d) 前記第2のフレームのパケットの前記サブセットにＥＣ処理を実行して、前記第2のフレームのうちの少なくとも1つのパケットを再構成することであって、前記第2のフレームの前記ＥＣ処理が、前記第1のフレームの前記ＥＣ処理が完了する前に開始されることをさらに含む、請求項1に記載の発明。 30

**【請求項 6】**

前記第1のフレームの前記ＥＣ処理は、前記第2のフレームの前記ＥＣ処理が開始する前に開始される、請求項5に記載の発明。

**【請求項 7】**

- (a1) 前記第1のフレームのパケットの前記サブセット内の各パケットを、パケット・バッファ内に格納すること、

(a2) 前記パケットにＥＣ処理を実行する前に、前記パケット・バッファから各パケットを読み取ること、および

(c) 前記第1のフレームのパケットの前記サブセット内の各パケットへのＥＣ処理が完了した後に、再構成されたパケットを前記パケット・バッファ内に格納することをさらに含む、請求項1に記載の方法。 40

**【請求項 8】**

3つ以上のデータ・パケットおよび誤り訂正(ＥＣ)パケットを含む第1のフレームのパケットのサブセットを連続的に受信するように構成されたパケット・バッファ、ならびに

前記第1のフレームのパケットの前記サブセットにＥＣ処理を実行して、前記第1のフレームのうちの少なくとも1つのパケットを再構成するように構成されたＥＣデコーダであって、前記ＥＣ処理が、パケットの前記サブセット全体を受信する前に開始されるＥＣデコーダを備える受信機。

**【請求項 9】**

10

20

30

40

50

受信機内で誤り訂正(ＥＣ)処理を実行する装置であって、

(a) 3つ以上のデータ・パケットおよびＥＣパケットを含む第1のフレームのパケットのサブセットを連続的に受信する手段、ならびに

(b) 前記第1のフレームのパケットの前記サブセットにＥＣ処理を実行して、前記第1のフレームのうちの少なくとも1つのパケットを再構成する手段であって、前記ＥＣ処理が、パケットの前記サブセット全体を受信する前に開始される手段を備える装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、誤り訂正デコーダ、および詳細には前方誤り訂正(ＦＥＣ)デコーダを有する受信機におけるバッファ・メモリ管理に関する。 10

【背景技術】

【0002】

ＦＥＣ技法は、普通はインターネットなどのパケットベースのネットワークで使用されて、パケット損失を補償する。リアルタイム伝送プロトコル(ＲＴＰ)を利用するリアルタイム・メディアのパケットとともに使用するのに適したＦＥＣ技法は、米国特許第6,141,788号、およびインターネット協会から1999年12月発行のJ. Rosenbergらによる「An RTP Payload Format for Generic Forward Error Correction」と題するインターネット標準化過程プロトコル番号RFC-2733に記載されており、それぞれその全体を参照により本明細書に組み込む。この技法によれば、伝送する前に、チェックサム・パケットまたはＦＥＣパケットと呼ばれる追加のパケットが、メディア・フレームまたはデータ・パケットのブロックに追加される。受信機において、チェックサム・パケットと首尾よく受信したデータ・パケットとを組み合わせることにより、フレーム内の損失データ・パケットを回復し再構成することができる。より具体的には、チェックサム・パケットと首尾よく受信したデータ・パケットに数学演算(たとえば、排他的論理和(ＸＯＲ)論理演算)を実行することにより、損失データ・パケットが回復される。次いで、この数学演算の結果から、損失データ・パケットを再構成することができる。 20

【0003】

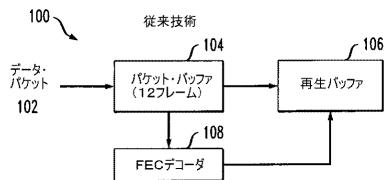

図1には、インターネット標準化過程プロトコル番号RFC-2733によるＦＥＣ復号化を利用する、従来の受信機100が示してある。受信機100は、ＦＥＣデコーダ108および再生バッファ106に接続されたパケット・バッファ104を備える。ＦＥＣデコーダ108も、再生バッファ106に接続されている。 30

【0004】

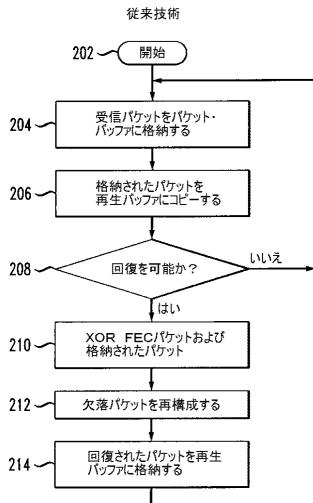

図2には、従来の受信機100の動作が示してある。ブロック202で動作が始まる。ブロック204で、受信パケット102が、パケット・バッファ104に格納される。ブロック206で、パケット102のコピーが再生バッファ106に転送されるが、パケット102は、ＦＥＣデコーダ108による後続処理のためにパケット・バッファ104内に保持される。ブロック208で、ＦＥＣデコーダ108は、(たとえば、所与のメディア・フレームFについて、ＦＥＣパケットおよび1つのデータ・パケットを除くすべてのデータ・パケットを受信したとき)、パケット102の属するメディア・フレームFがＦＥＣ復号化可能かどうか判定する。符号化が可能でない場合には、動作はブロック204に戻り、そこで後続のパケットを受信して格納する。しかし、フレームFがＦＥＣ復号化可能である場合、ブロック210で、ＦＥＣデコーダ108は、メディア・フレームFについての受信パケット(すなわち、1つのデータ・パケットを除くすべてのデータ・パケットおよびＦＥＣパケット)をパケット・バッファ104から読み取り、受信パケットに数学演算(たとえば、ＸＯＲ論理演算)を実行する。ブロック212で、よく知られた技法により、ＦＥＣデコーダ108は、数学演算の結果に基づいて欠落パケットを再構成する。ブロック214で、ＦＥＣデコーダ108は、回復したパケットを再生バッファ106に転送する。 40

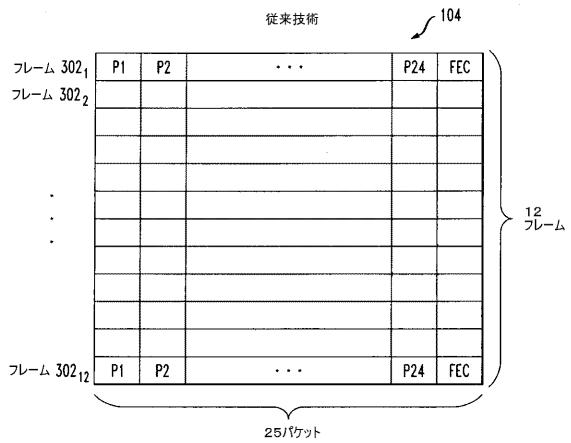

## 【0005】

しかし、従来の受信機100の不利な点は、パケット・バッファ104のサイズが相対的に大きくなることである。たとえば、MPEGメディア・フレームは、24までのデータ・パケットに加えて1つのFECパケットの、合計25のパケットを有することができる。したがって、MPEGメディア・フレームを格納する必要があるパケット・バッファ104内のバッファ・メモリの量MemPerFrameは、以下の通り定義することができる。

## 【0006】

## 【数1】

$$MemPerFrame = \sum_{j=1}^{25} SizeOf(Packet(j))$$

10

20

30

40

50

さらに、各パケットは、最大サイズのユーザデータグラムプロトコル(UDP)最大パケット・サイズ(たとえば、従来のイーサネットの最大伝送単位(MTU)のサイズである1.5KB)を有することがある。したがって、サイズが1.5KBの25のパケットを有するMPEGメディア・フレームは、37.5KBのメモリを必要とするはずである。

## 【0007】

こうしたm個のフレームを格納するために必要となる合計バッファ・メモリは、(m × MemPerFrame)である。パケット・バッファ104に格納しなければならないフレームの数mは、いくつかの変数の関数であり、それらの変数は(i) FECデコーダ108の待ち時間(すなわち、フレームの第1のパケットの受信と、そのフレームに対するFEC復号化の開始との間の期間)、(ii) FEC復号化の遅延(すなわち、たとえばフレームに対して24組のXOR論理演算を実行することを含む、フレームに対するFEC復号化の開始からFEC復号化の完了までの期間)、および(iii) 入力パケットのパケット・ジッタを含む。従来の受信機100では、パケット・バッファ104内に格納されるフレームの数mは、通常12から30の間である。したがって、従来の受信機100が、MPEGメディア・パケットを受信するように設計されている場合、パケット・バッファ104は、450KBから1.125MBの間のメモリを通常必要とするはずである。

## 【0008】

この説明では、図3には、パケット・バッファ104の例示的な実装形態が示しており、このパケット・バッファには12のメディア・フレーム302<sub>1</sub>～302<sub>12</sub>(それぞれ25のパケットを有する)を格納することができる。

## 【先行技術文献】

## 【特許文献】

## 【0009】

## 【特許文献1】米国特許第6,141,788号

## 【非特許文献】

## 【0010】

【非特許文献1】インターネット協会から1999年12月発行のJ. Rosenbergらによる「An RTP Payload Format for Generic Forward Error Correction」と題するインターネット標準化過程プロトコル番号RFC-2733

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0011】

本発明の例示的な実施形態は、FEC復号化の待ち時間およびパケット・バッファのサイズが著しく低減する、FEC復号化のための受信機および方法を提供する。

## 【課題を解決するための手段】

## 【0012】

したがって、第1の実施形態では、本発明は、受信機内で誤り訂正（ECC）処理を実行するための方法である。3つ以上のデータ・パケットおよびECCパケットを含む第1のフレームのパケットのサブセットが連続的に受信される。この第1のフレームのパケットのサブセットにECC処理が実行されて、第1のフレームのうちの少なくとも1つのパケットを再構成する。このECC処理は、パケットのサブセット全体を受信する前に開始される。

## 【0013】

他の実施形態では、本発明は受信機である。この受信機は、3つ以上のデータ・パケットおよび誤り訂正（ECC）パケットを含む第1のフレームのパケットのサブセットを連続的に受信するように構成されたパケット・バッファを備える。この受信機はさらに、第1のフレームのパケットのサブセットにECC処理を実行して、第1のフレームのうちの少なくとも1つのパケットを再構成するように構成されたECCデコーダを備え、このECC処理は、パケットのサブセット全体を受信する前に開始される。

10

## 【0014】

本発明の他の態様、特徴、および利点は、以下の詳細な説明、添付特許請求の範囲、および添付図面から、より完全に明白になるであろう。各図面において、同じ参照番号は、同様のまたは同一の要素を指す。

## 【図面の簡単な説明】

## 【0015】

20

【図1】FEC復号化を利用する従来の受信機の簡略化されたブロック図である。

【図2】図1の従来の受信機の動作を示す流れ図である。

【図3】図1の従来の受信機でのパケット・バッファの説明図である。

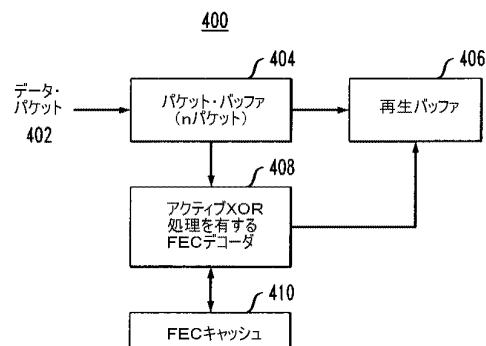

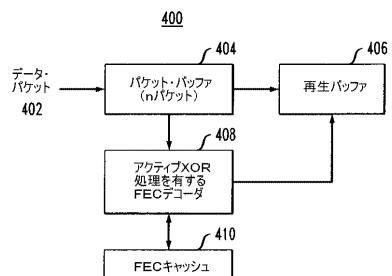

【図4】本発明によるFEC復号化を利用する受信機の一実施形態の簡略化されたブロック図である。

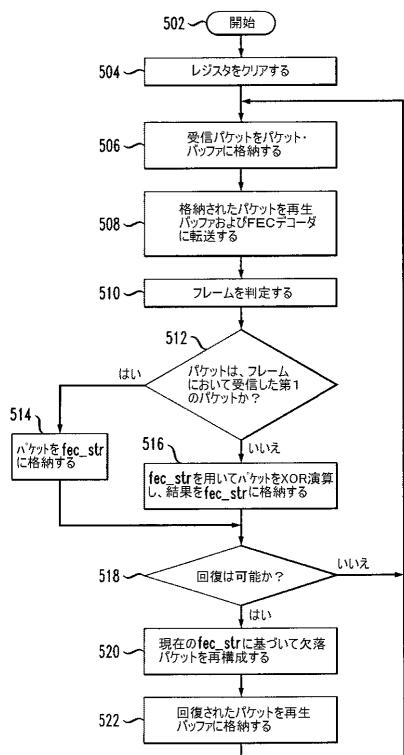

【図5】図4に示した受信機の動作を示す流れ図である。

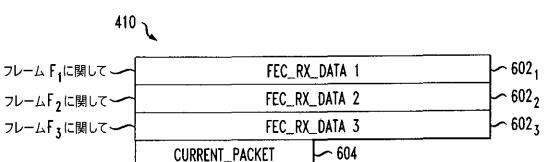

【図6】図4に示した受信機でのパケット・バッファの説明図である。

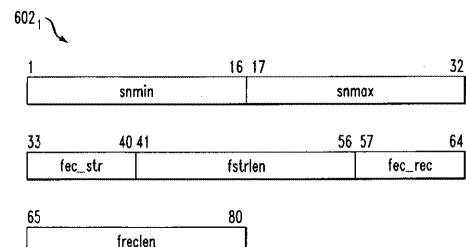

【図7】図4に示した受信機におけるFECデータ構造を含むキャッシュ・メモリの一部分の説明図である。

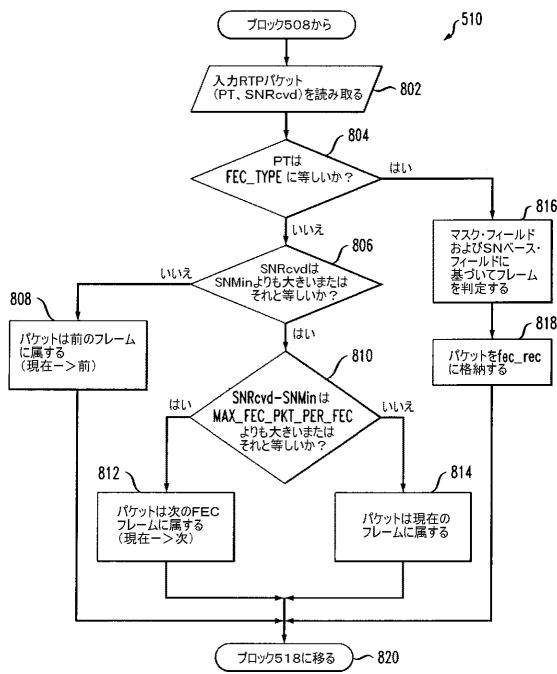

【図8】図5に示したフレーム判定ブロックのより詳細な流れ図である。

30

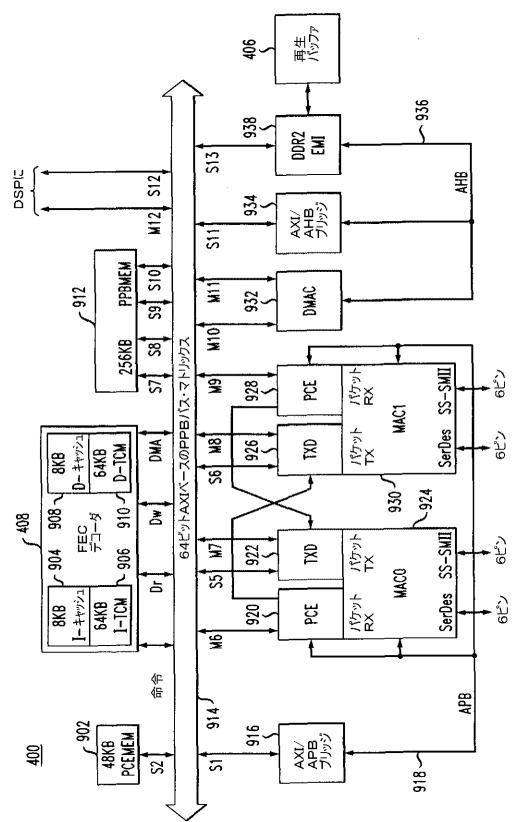

【図9】図4に示した受信機のより詳細なブロック図である。

## 【発明を実施するための形態】

## 【0016】

本明細書において「一実施形態（one embodiment）」または「一実施形態（an embodiment）」という場合、その実施形態に関して記述された具体的な特徴、構造、または特性が、本発明の少なくとも1つの実施形態に含まれ得ることを意味する。本明細書の様々な場所で「一実施形態では（in one embodiment）」という表現が現れるが、必ずしもすべてが同じ実施形態を指すものではなく、または他の実施形態を必然的に相互に排除する別個のまたは代替の実施形態でもない。同じことが「実装形態」という用語にも当てはまる。

40

## 【0017】

図4は、本発明による受信機400の一実施形態を示す。図4に示すように、受信機400は、パケット・バッファ404、再生バッファ406、FECデコーダ408、およびFECキャッシュ410を備える。受信機400では、FECデコーダ408は、各受信パケットを実質的にリアルタイムに、たとえば各パケットが到達し、パケット・バッファ404に格納された後すぐに処理する。パケットの属するフレームが不完全な場合でも、FEC処理は各パケットに対して開始される。こうした理由で、FECデコーダ408は、FECキャッシュ410に格納されるFEC処理中間結果を生成し維持する。各入力パケットを受信しFEC処理した後に、FECデコーダ408は、FECキャッシュ410に格納された中間結果を更新する。したがって、FECデコーダ408は、図1の従来技術のFECデコーダ108とは異なるが、FECデコーダ108は、メディア・フレー

50

ム内のデータ・パケットのうちの1つを除くすべてのパケットを受信するまで待ってから、FEC処理を開始する。

【0018】

FECデコーダ408は、実質的にリアルタイムで（受信すべきフレーム内で、さらなるパケットを待つことなく）受信パケットを処理するので、パケット・バッファ404は、図1の従来技術のパケット・バッファ104よりも著しく小さくてよい。パケット・バッファ404は、(i)受信パケットを再生バッファ406に転送するために、また(ii)受信パケットをFECデコーダ408に転送するために、必要とされる期間のみ受信パケットを格納する。こうした転送が完了した後に、受信パケットが占めているパケット・バッファ404内のメモリは、クリアされ、別の入力パケット用に使用されてもよい。したがって、パケット・バッファ404は、フレームがFEC処理可能と見なされるまでフレームにおけるパケットのすべてを格納する必要はない。したがって、再生バッファ406は、再生バッファ106よりも著しく小さくてよい（たとえば、約1/2～約1/10の範囲）。

10

【0019】

たとえば、一実施形態では、再生バッファ406は、約12から約24の間のパケット（これらのパケットは、12の異なる連続伝送されるフレームに属してもよい）を格納することができるようなサイズにしてもよく、FECデコーダ408は、これら12の連続伝送されるフレームについて、パケットをFEC処理するように構成される。しかし、パケット・バッファ404が扱うように設計されているパケットの数、およびFECデコーダ408が扱うように設計されているフレームの数は、パケットベースのネットワーク内でのパケット・ジッタ、FECデコーダ408の待ち時間、およびFECデコーダ408の処理遅延に基づいて変化させてもよいことを理解されたい。

20

【0020】

説明を簡潔にするために、一実施形態では、受信機400は、同時に連続伝送される3つのメディア・フレームに属するパケット上で、FECデコーダ408が動作できるようにするのに十分に小さいパケット・ジッタを有する通信システムで使用するように設計されていることを、以下に仮定する。こうした一実施形態では、FECキャッシュ410は、とりわけ、連続伝送される3つのメディア・フレーム（以下では、前のフレームF<sub>1</sub>、現在のフレームF<sub>2</sub>、および次のフレームF<sub>3</sub>と呼ぶ）についての中間の数学的結果（たとえば、XOR論理演算結果）を格納するための3つの記憶場所fec스트<sub>1</sub>、fec스트<sub>2</sub>、およびfec스트<sub>3</sub>（図4には図示せず）と、現在の受信パケットを格納するための1つの記憶場所current\_packetとを含む。FECフレームによって保護されるパケットの数は、当業者に知られている技法に従って、受信機400と送信機（図示せず）の間で事前に決定されるか取り決められることを、以下でさらに仮定する。

30

【0021】

図5には、受信機400の動作が示してある。ロック502で動作が始まる。ロック504で、記憶場所fec스트<sub>1</sub>、fec스트<sub>2</sub>、およびfec스트<sub>3</sub>がクリアされる（たとえば、ゼロにセットされる）。ロック506で、受信パケット402が、パケット・バッファ404に格納される。ロック508で、受信パケット402は、パケット・バッファ404から、FECキャッシュ410内の記憶場所current\_packetおよび再生バッファ406に転送され、受信パケット402が占めているパケット・バッファ404内の記憶場所を他のパケット用に解放する。ロック510で、FECデコーダ408は、パケット402のヘッダ情報を読み取り、パケット402がどちらのメディア・フレーム（たとえば、前のフレームF<sub>1</sub>）に属しているのか判定する。

40

【0022】

ロック512で、FECデコーダ408は、パケット402の属するメディア・フレーム（たとえば、前のフレームF<sub>1</sub>）において、パケット402が、受信機400が受信

50

した第1のパケットであるかどうか判定する。そうである場合、ブロック514で、FECデコーダは、パケット402の属するメディア・フレームに対応する記憶場所(fec\_str<sub>1</sub>、fec\_str<sub>2</sub>、またはfec\_str<sub>3</sub>)にパケット402を格納し、動作はブロック506に戻って、別の受信パケットを処理する。パケット402の属するメディア・フレーム(たとえば、前のフレームF<sub>1</sub>)において、パケット402が、受信機400が受信した第1のパケットではない場合、ブロック516で、FECデコーダ408は、パケット402のデータ部分と、このパケットの属するメディア・フレームに対応する記憶場所(たとえば、fec\_str<sub>1</sub>)のコンテンツとの間で数学演算(たとえば、XOR論理演算)を実行する。次いで、数学演算の結果は、同じ記憶場所(たとえば、fec\_str<sub>1</sub>)に格納され、それにより、この記憶場所の前のコンテンツを置き換える。

10

#### 【0023】

ブロック518で、FECデコーダは、パケット402の属するメディア・フレームがFEC復号化可能かどうか判定する(たとえば、このメディア・フレームについて、FECパケットおよび1つのデータ・パケットを除くすべてのデータ・パケットを受信したとき)。(図8を参照しながら、フレーム判定ブロック518を、以下でより詳細に説明する。)パケット402の属するフレームがFEC復号化可能でない場合、動作はブロック506に戻って、別の受信パケットを処理する。

#### 【0024】

メディア・フレームがFEC復号化可能である場合、ブロック520で、FECデコーダ408は、パケット402の属するメディア・フレーム(たとえば、前のフレームF<sub>1</sub>)に対応する記憶場所(たとえば、fec\_str<sub>1</sub>)に格納されている数学演算結果を使用して、米国特許第6,141,788号およびインターネット標準化過程プロトコル番号RFC-2733に記載されている技法など、よく知られた技法に従って、欠落パケットを再構成する。最後に、ブロック522で、FECデコーダ408は、回復されたパケットを再生バッファ406内に格納し、次の入力パケットのために記憶場所(たとえば、fec\_str<sub>1</sub>)がクリアされる。

20

#### 【0025】

図6は、FECキャッシュ410の説明図である。一実施形態では、FECキャッシュ410は、3つのデータ構造(または、定義されたメモリ部分)602<sub>1</sub>、602<sub>2</sub>、および602<sub>3</sub>(それぞれ、FEC\_RX\_DATA1、FEC\_RX\_DATA2、およびFEC\_RX\_DATA3とされる)、ならびに現在の受信パケットを格納するためのcurrent\_packetの記憶場所604を含む。データ構造(または、定義されたメモリ部分)602<sub>1</sub>、602<sub>2</sub>、および602<sub>3</sub>において、FECデコーダ408は、それぞれメディア・フレームF<sub>1</sub>、F<sub>2</sub>、およびF<sub>3</sub>をFEC復号化するのに有用な情報を格納する。

30

#### 【0026】

一実施形態では、データ構造602<sub>1</sub>、602<sub>2</sub>、および602<sub>3</sub>は、以下のように定義される。

```

typedef struct FEC_RX_DATA

{

uint16_t snmin;

uint16_t snmax;

uint8_t fec_str [MAX RTP_PACKET_SIZE];

uint16_t fstrlen;

uint8_t fec_rec [MAX RTP_PACKET_SIZE];

uint16_t freclen;

struct FEC_RX_DATA * prev;

struct FEC_RX_DATA * next;

} FEC_RX_DATA_t;

```

40

50

ここで、データ・フィールドは以下のように定義される。

【0027】

【表1】

|          |                                                                                                                                                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Snmin    | 現在のF <sub>2</sub> 内のRTPメディア・パケットの最小シーケンス番号                                                                                                                          |

| Snmax    | 現在のフレームF <sub>2</sub> 内のRTPメディア・パケットの最大シーケンス番号                                                                                                                      |

| fec_str  | 現在のフレームF <sub>2</sub> に属する受信されたRTPメディア・パケットへのXOR論理演算の現在の結果                                                                                                          |

| Fstrlen  | 現在のフレームF <sub>2</sub> に属するRTPメディア・パケットのペイロード長<br><br>一実態形態では、受信パケットのペイロード長は、XOR形式で格納してもよい(たとえば、パケット1のペイロード長が9バイトで、パケット2のペイロード長が8バイトである場合、fstrlen = 8 XOR 9 = 1である。) |

| fec_rec  | 現在のフレームF <sub>2</sub> に属する受信FECパケット                                                                                                                                 |

| Frecrlen | FECパケット長                                                                                                                                                            |

| Prev     | 前のフレームF <sub>1</sub> のデータ構造に対するポインタ                                                                                                                                 |

| Next     | 次のフレームF <sub>3</sub> のデータ構造に対するポインタ                                                                                                                                 |

10

20

【0028】

説明するために、図7には、データ構造602<sub>1</sub>が図示してある。

【0029】

図8は、図5のフレーム判定ブロック510をより詳細に示す流れ図であり、ここで、FECデコーダ408は、受信パケット402がどのメディア・フレーム(たとえば、前のフレームF<sub>1</sub>)に属するのか判定する。

【0030】

ブロック802で、FECデコーダ408は、図4に示したパケット・バッファ404内に格納されている受信パケット402の、ペイロード・タイプ記述子PTおよびシーケンス番号SNRcvdを読み取る。ブロック804で、FECデコーダ408は、受信パケット402がFECパケットである(すなわち、ペイロード・タイプ記述子PTが所定の値FEC\_TYPEに等しい)かどうか検査する。受信パケット402がFECパケットでない場合、ブロック806で動作が続く。ブロック806で、FECデコーダ408は、シーケンス番号SNRcvdが、現在のフレームF<sub>2</sub>内のメディア・パケットの最小シーケンス番号snminよりも大きい、またはそれと等しいかを検査する。そうでない場合、ブロック808で、FECデコーダ408は、受信パケット402を前のフレームF<sub>1</sub>に属するものと識別し、ポインタが、前のフレームF<sub>1</sub>に関係するFEC復号化情報を格納するための定義された記憶場所であるデータ構造602<sub>1</sub>(FEC\_RX\_DATA1)にセットされる。ブロックIiで動作が続き、ここで動作は、図5のブロック516に戻る。ブロック516で、FECデコーダ408は、ポインタを使用して、パケット402のデータ部分に数学演算を実行する際に使用される記憶場所(たとえば、fec\_sctr<sub>1</sub>)を有するデータ構造(たとえば、FEC\_RX\_DATA1)を識別する。

30

40

【0031】

しかし、ブロック806で、シーケンス番号SNRcvdが、現在のフレームF<sub>2</sub>内のメディア・パケットの最小シーケンス番号snminよりも大きい、またはそれと等しいとFECデコーダ408が判定する場合、動作はブロック810に進む。FECデコーダ408は、受信パケットのシーケンス番号SNRcvdと、現在のフレームF<sub>2</sub>内のRTTメディア・パケットの最小シーケンス番号snminとの差が、FECパケットによって保護することができるパケットの所定の最大数MAX\_FEC\_PKT\_PER\_FECよりも大きいまたはそれと等しいかどうか検査する。たとえば、MPEG RTPメディア・フレームでは、FECパケットによって保護することができるパケットの、所定の

50

最大数MAX\_FEC\_PKT\_PER\_FECは24である。

【0032】

受信パケットのシーケンス番号SNRcvdと、現在のフレームF<sub>2</sub>内の RTP メディア・パケットの最小シーケンス番号snminとの差が、所定の最大数MAX\_FEC\_PKT\_PER\_FECよりも大きくなくまたそれと等しくもない（すなわちそれ未満の）場合、ブロック814で、FECデコーダ408は、受信パケット402を現在のフレームF<sub>2</sub>に属するものと識別する。具体的には、ポインタがデータ構造602<sub>2</sub>（FEC\_RX\_DATA2）にセットされ、FEC復号化情報を格納するための定義された記憶場所は、現在のフレームF<sub>2</sub>に関係する。ブロックI<sub>i</sub>で動作が続き、ここで動作は、図5のブロック516に戻る。ブロック516で、FECデコーダ408は、ポインタを使用して、データ・パケット402のデータ部分に数学演算を実行する際に使用される記憶場所（たとえば、fec\_s tr<sub>2</sub>）を有するデータ構造（たとえば、FEC\_RX\_DATA2）を識別する。

10

【0033】

ブロック810に戻ると、受信パケットのシーケンス番号SNRcvdと、現在のフレームF<sub>2</sub>内の RTP メディア・パケットの最小シーケンス番号snminとの差が、所定の最大数MAX\_FEC\_PKT\_PER\_FECよりも大きいまたはそれと等しい（すなわち、それ以上である）とFECデコーダ408が判定する場合、ブロック812で動作が続く。FECデコーダ408は、受信パケット402を次のフレームF<sub>3</sub>に属するものと識別する。具体的には、ポインタがデータ構造602<sub>3</sub>（FEC\_RX\_DATA3）にセットされ、FEC復号化情報を格納するための定義された記憶場所は、次のフレームF<sub>3</sub>に関係する。ブロックI<sub>i</sub>で動作が続き、ここで動作は、図5のブロック516に戻る。ブロック516で、FECデコーダ408は、ポインタを使用して、パケット402のデータ部分に数学演算を実行する際に使用される記憶場所（たとえば、fec\_s tr<sub>3</sub>）を有するデータ構造（たとえば、FEC\_RX\_DATA3）を識別する。

20

【0034】

ブロック804で、受信パケット402がFECパケットである（すなわち、ペイロード・タイプ記述子PTが所定の値FEC\_TYPEに等しい）とFECデコーダ408が判定する場合、ブロック816で動作が続く。ブロック816で、パケット402のマスク・フィールドおよびsnベース・フィールドを使用して、パケット402が、どのフレーム（たとえば、前のフレームF<sub>1</sub>、現在のフレームF<sub>2</sub>、または次のフレームF<sub>3</sub>）に属するのかを判定する。次いで、ブロック818で、FECキャッシュ410内の適切なデータ構造（FEC\_RX\_DATA1、FEC\_RX\_DATA2、またはFEC\_RX\_DATA3）内のfec\_rec記憶場所にパケット402が格納され、ブロック820で、図5のブロック518に動作が戻る。

30

【0035】

図9は、図4に示した受信機400のより詳細なブロック図である。FECデコーダ408は、英国ケンブリッジにあるARM Holdings plcから入手可能なコア設計に基づく、ARM1176J-Sプロセッサなどの縮小命令セットコンピューティング(RISC)プロセッサとして実装されることが好ましい。RISCプロセッサは、少なくとも250MHzの速度で動作することが好ましい。

40

【0036】

パケット・バッファ404およびFECキャッシュ410は、RISCプロセッサ内の64KBのデータ密結合メモリ(D-TCM)910内に実装されることが好ましい。RISCプロセッサはまた、8KBのデータ・キャッシュ(D-キャッシュ)、8KBの命令キャッシュ(I-キャッシュ)、および64KBの命令密結合メモリ(I-TCM)を備えてよい。

【0037】

図9に示すように、再生バッファ406およびFECデコーダ408は、64ビットのアドバンスト・エクステンシブル・インターフェース(AXI)ベースのバス・マトリック

50

ス914を介して接続されている。再生バッファ406は、(i)データ転送速度が毎秒5億3300万回であり、(ii)「DDR2 SDRAM Specification」と題するJEDDEC規格番号JESD79-2Eに準拠し、(iii)「x16」構成で実装される(すなわち、DDR2-533 x16メモリ)、外部のダブル・データ・レート(DDR)シンクロナス・ダイナミック・ランダム・アクセス・メモリ(SDRAM)であることが好ましい。再生バッファ406は、DDR2外部メモリ・インターフェース(EMI)938を介して、バス・マトリックス914に接続される。

#### 【0038】

受信機400はまた、FECデコーダ408が使用するための、256KBの汎用SRAMメモリ(「PPBMEM」)912を備える。

10

#### 【0039】

受信機400はまた、イーサネットをサポートするための、媒体アクセス制御装置(MAC)924、930を備える。MAC924、930は、パケット分類エンジン(PCI)コプロセッサ920、928および送信MAC DMA(TXD)コプロセッサを介して、バス・マトリックス914に接続される。PCIコプロセッサ920、928は、L2/L3/L4のIPおよびUDPのパケット分類、ならびにMAC924、930と受信パケット用のパケット・バッファ404との間での直接メモリアクセス(DMA)のサポートを実現する。TXDコプロセッサ922、926は、MAC924、930と送信パケット用の送信メモリ(図示せず)との間でのDMAのサポートを実現する。48KBの汎用SRAMメモリ902も、PCIコプロセッサ920、928用に設けられて、たとえば、インターネット・プロトコル・バージョン6(IPv6)をサポートするための表を格納する。

20

#### 【0040】

受信機400はまた、(外部メモリ・インターフェース938を介して)再生バッファ406に対してDMAをサポートするDMA制御装置932を備える。

#### 【0041】

FECデコーダ408はまた、(i)AXI/APBブリッジ916を介して接続されたアドバンスト・ペリフェラル・バス(APB)918を介してMAC924、930およびPCIコプロセッサ920、928と通信し、また(ii)AXI/AHBブリッジ934を介して接続されたアドバンスト・ハイパフォーマンス・バス(AHB)936を介してDMA制御装置932およびDDR2外部メモリ・インターフェース938と通信することが好ましい。

30

#### 【0042】

1つまたは複数のデジタル信号プロセッサ(DSP)(図示せず)もまた、バス・マトリックス914に接続して、再生バッファ406内に格納されたメディア・パケットを復号化してもよい。

#### 【0043】

このように、複数のデータ・パケットおよび誤り訂正パケットを有するメディア・フレームを受信するための、新規で革新的なシステムおよび方法を説明してきた。図4に示す前述の受信機400において、FECデコーダ408は、対応するメディア・フレーム内に残っているパケットのすべてまたはほとんどを受信するまで遅延することなく、ただちに各受信パケットに数学演算(たとえば、XOR論理演算)を実行することに留意してもよい。対照的に、図1に示す従来の受信機100においては、FECデコーダ108は、バッファリングされたフレームがFEC復号化可能であると判定されるまで(たとえば、このフレームにおけるFECパケットおよび1つのデータ・パケットを除くすべてのデータ・パケットが受信されるまで)、いかなる数学演算の実行をも遅延する。したがって、FECデコーダ408は、従来のFECデコーダ108よりも、待ち時間が著しく少ない。さらに、FECデコーダ408は、各受信パケットにただちに数学演算を実行するので、パケット・バッファ404が、各フレームのほとんどすべてのパケットを格納することができる必要はない。その結果、パケット・バッファ404は、図1のパケット・バッフ

40

50

ア 1 0 4 よりも、サイズをはるかに小さくすることができる。

【 0 0 4 4 】

本発明は、(A S I C または F P G A などの) 単一の集積回路、マルチチップ・モジュール、單一カード、またはマルチカード回路パックのような実現可能な実装形態を含め、オールデジタル、オールアナログ、またはアナログ回路とデジタル回路両方をベースにするプロセスのハイブリッドとして実施してもよい。当業者には明らかになるように、回路要素の様々な機能をも、ソフトウェア・プログラム内の処理ブロックとして実装してもよい。このようなソフトウェアは、たとえば、デジタル信号プロセッサ、マイクロコントローラ、または汎用コンピュータで利用してもよい。

【 0 0 4 5 】

本発明の本質を説明するために説明し図示してきた各部品の詳細、材料、および構成には、以下の特許請求の範囲に記載された本発明の範囲を逸脱することなく、当業者によって様々な変更を加えてよいことがさらに理解されよう。

【 0 0 4 6 】

したがって、本発明は、X O R 論理演算を使用する誤り訂正に関するこれまで述べてきたが、本発明は、それに限定されるものではなく、他の論理演算(たとえば、否定排他的論理和( N X O R )論理演算)を使用してもよい。さらに、本発明を、論理演算以外の数学演算に基づく他の誤り訂正( E C )アルゴリズムを使用して実施してもよいのは、このような E C アルゴリズムにより、遅延することなく、たとえば、E C 処理が開始される前に、フレーム内のすべてのまたは実質的にすべてのパケットが存在する必要もなく、F E C 処理を各受信パケットについて行うことができる場合である。

【 0 0 4 7 】

さらに、本発明は、特定の長さおよび量に関してこれまで述べてきたが、本発明は、それに限定されるものではなく、他の長さおよび量を使用してもよい。たとえば、F E C デコーダ 4 0 8 およびパケット・バッファ 4 0 4 が扱うように設計されているフレームの数、ならびにF E C キャッシュ 4 1 0 内の記憶場所の数は、パケットベースのネットワーク内のパケット・ジッタ、および/またはF E C デコーダ 4 0 8 の待ち時間に基づいて増減させてよい。たとえば、本発明の一実施形態では、前述の3フレーム・パケット・バッファではなく、2フレーム・パケット・バッファを利用してよい。このような実施形態では、前述の3つではなく、2つのデータ構造 6 0 2<sub>1</sub>、6 0 2<sub>2</sub> のみがF E C キャッシュ 4 1 0 内で必要となる。

【 0 0 4 8 】

他の実施形態では、ネットワークのパケット・ジッタが非常に小さい場合、1フレーム・パケット・バッファを利用してもよく、F E C キャッシュ 4 1 0 は、単一のデータ構造 6 0 2<sub>1</sub> を含んでもよく、またそれから構成されてもよい。一方で、パケット・ジッタが大きい場合、F E C デコーダ 4 0 8 およびパケット・バッファ 4 0 4 は、4つ(以上)のフレームを扱うように設計してもよく、対応する数のデータ構造がF E C キャッシュ 4 1 0 内に必要となるはずである。たとえば、パケット・ジッタが、前述の受信機 1 0 0 の場合と同様に大きい場合(パケット・バッファ 1 0 4 が12フレームを格納することができるよう設計された場合)、F E C デコーダ 4 0 8 およびパケット・バッファ 4 0 4 もまた、F E C キャッシュ 4 1 0 内の12のデータ構造を使用する場合には、12フレームを扱うように設計してもよいことが予想される。

【 0 0 4 9 】

本明細書で説明した例示的な方法の各ステップは、必ずしも説明した順序で実行する必要はなく、このような方法のステップの順序は、単に例示的なものと理解すべきであることも理解されたい。同様に、本発明の様々な実施形態に合致する方法においては、このような方法に追加のステップを含んでもよく、また何らかのステップを割愛してもよく、または組み合わせてもよい。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(74)代理人 100128657

弁理士 三山 勝巳

(74)代理人 100160967

弁理士 濱 口 岳久

(72)発明者 アチュル キサンラオ ヘダオー

インド国 5 6 0 0 1 7 カーナタカ ステート, バンガロア, ムルジエシュバルヤ, ケー アール ガーデン, アショク アヴェニュー 93, ジェーヴァナデ マグナス, エフエフ3

(72)発明者 ラエシュ カシナス ライカー

インド国 5 6 0 1 0 3, カーナタカ ステート, バンガロア, ベランジュル, グリーングレン レイアウト, マーゴサ アヴェニュー, アップル プロッサム, アパートメント ナンバー 208

F ターム(参考) 5K014 AA01 BA05 EA01