(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4809596号

(P4809596)

(45) 発行日 平成23年11月9日(2011.11.9)

(24) 登録日 平成23年8月26日(2011.8.26)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/3205 | (2006.01) | HO1L 21/88 | K    |

| HO1L 23/52   | (2006.01) | HO1L 21/88 | R    |

| HO1L 21/768  | (2006.01) | HO1L 21/90 | Q    |

| HO1L 21/28   | (2006.01) | HO1L 21/90 | C    |

| HO1L 21/285  | (2006.01) | HO1L 21/28 | 301R |

請求項の数 17 (全 40 頁) 最終頁に続く

(21) 出願番号 特願2004-228438 (P2004-228438)

(22) 出願日 平成16年8月4日 (2004.8.4)

(65) 公開番号 特開2005-123576 (P2005-123576A)

(43) 公開日 平成17年5月12日 (2005.5.12)

審査請求日 平成19年7月25日 (2007.7.25)

(31) 優先権主張番号 特願2003-286278 (P2003-286278)

(32) 優先日 平成15年8月4日 (2003.8.4)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2003-329145 (P2003-329145)

(32) 優先日 平成15年9月19日 (2003.9.19)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 秋元 健吾

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 藤井 厳

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山口 哲司

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 ▲辻▼ 弘輔

最終頁に続く

(54) 【発明の名称】半導体装置及びその作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体領域と、前記半導体領域表面に形成されたコンタクトホールを有する絶縁膜と、前記コンタクトホールを介して前記半導体領域に接する導電層を有し、

前記絶縁膜は、塗布法を用いて形成され、シリコンと酸素との結合で骨格構造が構成される絶縁膜であり、

前記絶縁膜及び前記導電層の間に、窒素化合物で形成される層を有し、

前記導電層は、窒素元素の含有量が7atomm以上44atomm未満であり、前記導電層の抵抗率は100μcm以上250μcm未満であり、且つ前記半導体領域と前記導電層とのコンタクト抵抗が1000以上3000未満であることを特徴とする半導体装置。

10

## 【請求項2】

半導体領域と、前記半導体領域表面に形成されたコンタクトホールを有する絶縁膜と、前記コンタクトホールを介して前記半導体領域に接続する導電層を有し、

前記絶縁膜は、塗布法を用いて形成され、シリコンと酸素との結合で骨格構造が構成される絶縁膜であり、

前記絶縁膜及び前記導電層の間に、窒素化合物で形成される層を有し、

前記導電層は、窒素元素の含有量が7atomm以上44atomm未満であり、前記導電層の抵抗率は、100μcm以上250μcm未満であり、且つ前記半導体領域と前記導電層との接触抵抗率が7.1×10<sup>-5</sup>·cm<sup>2</sup>以上2.1×10<sup>-</sup>

20

<sup>4</sup> · cm<sup>2</sup> 未満であることを特徴とする半導体装置。

【請求項 3】

請求項 1 又は請求項 2 において、

前記導電層は、窒素元素を含有するチタン、モリブデン、タンゲステン、又はタンタルであることを特徴とする半導体装置。

【請求項 4】

請求項 1 又は請求項 2 において、

前記導電層は、流量比が 9 : 1 ~ 4 : 6 の希ガスと窒素とをスパッタリングガスとし、チタンをターゲットとしてスパッタリング法により形成されていることを特徴とする半導体装置。 10

【請求項 5】

請求項 1 乃至請求項 4 のいずれか一項において、

前記導電層は、膜厚方向に対して窒素の濃度勾配を有することを特徴とする半導体装置。 15

【請求項 6】

請求項 5 において、前記濃度勾配は、前記半導体領域側において前記窒素の濃度が低いことを特徴とする半導体装置。

【請求項 7】

請求項 1 乃至請求項 6 のいずれか一項において、前記導電層は、窒素元素の濃度の異なる導電層が積層されて構成されることを特徴とする半導体装置。 20

【請求項 8】

請求項 1 乃至 7 のいずれか一項において、前記窒素化合物で形成される層は、窒化チタン、窒化モリブデン、窒化タンゲステン、又は窒化タンタルであることを特徴とする半導体装置。

【請求項 9】

請求項 1 乃至 請求項 8 のいずれか一項において、

前記導電層上に、アルミニウム、タンゲステン、銅、金、銀から選ばれた元素、またはこれらの元素を主成分とする合金材料で形成される導電層と、チタン、モリブデン、タンゲステン、タンタルから選ばれた元素、又はこれらの元素で形成される化合物で形成される導電層とが積層して形成されていることを特徴とする半導体装置。 30

【請求項 10】

請求項 1 乃至 請求項 9 のいずれか一項において、前記絶縁膜は、平坦性を有することを特徴とする半導体装置。

【請求項 11】

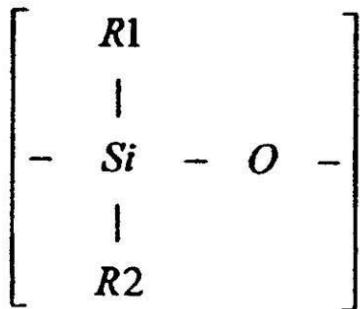

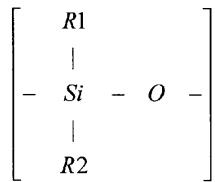

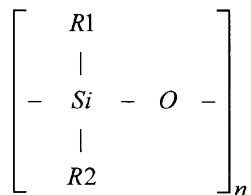

請求項 1 乃至 請求項 10 のいずれか一項において、前記絶縁膜は、下記構造式(1)で示される繰り返し単位を有することを特徴とする半導体装置。

【化 1】

(式中、R1 及び R2 はそれぞれ独立して、水素原子、ハロゲン、アルキル基、又はフェニル基、を示す。)

【請求項 12】

10

20

30

40

50

請求項 1 乃至 請求項 1\_1 のいずれか一項において、

前記絶縁膜はスピンコート法により形成されていることを特徴とする半導体装置。

**【請求項 1\_3】**

請求項 1 乃至 請求項 1\_2 のいずれか一項において、前記絶縁膜は、シロキサンポリマーを用いて形成することを特徴とする半導体装置。

**【請求項 1\_4】**

半導体領域上にシロキサンポリマーを含有する塗布材料を塗布し焼成して、シリコンと酸素との結合で骨格構造が構成されている絶縁膜を形成し、

前記絶縁膜上に、窒素化合物で形成される導電膜を成膜し、

前記窒素化合物で形成される導電膜及び前記絶縁膜の一部をエッティングして、前記半導体領域の一部を露出し。 10

前記露出された半導体領域及び前記窒素化合物で形成される導電膜上に、流量比が 9 : 1 ~ 4 : 6 の希ガスと窒素とをスパッタリングガスとしてスパッタリング法により窒素を含む導電膜を前記絶縁膜に接して形成し、

前記窒素を含む導電膜の一部をエッティングして配線を形成し、

前記窒素を含む導電膜は、窒素元素の含有量が 7 atomic % 以上 44 atomic % 未満であり、前記窒素を含む導電膜の抵抗率は 100 μ cm 以上 250 μ cm 未満であり、且つ前記半導体領域と前記窒素を含む導電膜とのコンタクト抵抗が 1000 以上 3000 未満であることを特徴とする半導体装置の作製方法。 20

**【請求項 1\_5】**

半導体領域上にシロキサンポリマーを含有する塗布材料を塗布し焼成して、シリコンと酸素との結合で骨格構造が構成されている絶縁膜を形成し、

前記絶縁膜上に、窒素化合物で形成される導電膜を成膜し、

前記窒素化合物で形成される導電膜及び前記絶縁膜の一部をエッティングして、前記半導体領域の一部を露出し、

前記露出された半導体領域及び前記窒素化合物で形成される導電膜上に、流量比が 9 : 1 ~ 4 : 6 の希ガスと窒素とをスパッタリングガスとしてスパッタリング法により窒素を含む導電膜を前記絶縁膜に接して形成し、

前記窒素を含む導電膜の一部をエッティングして配線を形成し、

前記窒素を含む導電膜は、窒素元素の含有量が 7 atomic % 以上 44 atomic % 未満であり、前記窒素を含む導電膜の抵抗率は 100 μ cm 以上 250 μ cm 未満であり、且つ前記半導体領域と前記窒素を含む導電膜との接触抵抗率が  $7 \cdot 1 \times 10^{-5} \cdot \text{cm}^2$  以上  $2 \cdot 1 \times 10^{-4} \cdot \text{cm}^2$  未満であることを特徴とする半導体装置の作製方法。 30

**【請求項 1\_6】**

請求項 1\_4 又は請求項 1\_5において、

前記窒素を含む導電膜上に当該窒素を含む導電膜より低抵抗材料で形成される第 1 の導電膜及び前記第 1 の導電膜への元素の拡散を抑制する第 2 の導電膜を成膜したのち、前記窒素を含む導電膜、前記第 1 の導電膜、及び前記第 2 の導電膜の一部をエッティングして配線を形成することを特徴とする半導体装置の作製方法。 40

**【請求項 1\_7】**

請求項 1\_6において、

前記窒素を含む導電膜上に、当該窒素を含む導電膜への元素の拡散を抑制する第 3 の導電膜を形成した後、前記第 1 の導電膜及び前記第 2 の導電膜を成膜し、前記窒素を含む導電膜、前記第 3 の導電膜、前記第 1 の導電膜、及び前記第 2 の導電膜の一部をエッティングして配線を形成することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は半導体素子が形成される配線基板、またその半導体素子で構成された回路を有

50

する半導体装置およびそれらの作製方法に関する。また、液晶表示パネルに代表される電気光学装置や有機発光素子を有する発光表示装置を部品として搭載した電子機器に関する。

【背景技術】

【0002】

近年、半導体素子の一つとして絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に画像表示装置のスイッチング素子として開発が急がれている。

【0003】

10

また、画像表示装置において、高品位な画像を得るために、画素電極をマトリクス状に配置し、画素電極の各々に接続するスイッチング素子としてTFTを用いたアクティブマトリクス型液晶表示装置や、アクティブマトリクス型発光装置が注目を集めている。

【0004】

このようなアクティブマトリクス型の表示装置の用途は広がっており、画面サイズの大面積化とともに高精細化や高開口率化や高信頼性の要求が高まっている。

【0005】

液晶表示装置に搭載される液晶モジュールには、機能ブロックごとに画像表示を行う画素部や、CMOS回路を基本としたシフトレジスタ回路、レベルシフタ回路、バッファ回路、サンプリング回路などの画素部を制御するための駆動回路が一枚の基板上に形成される。

20

【0006】

また、液晶モジュールの画素部には、数十から数百万個の各画素にTFT（画素TFT）が配置され、その画素TFTのそれぞれには画素電極が設けられている。液晶を挟んだ対向基板側には対向電極が設けられており、液晶を誘電体とした一種のコンデンサを形成している。そして、各画素に印加する電圧をTFTのスイッチング機能により制御して、このコンデンサへの電荷を制御することで液晶を駆動し、透過光量を制御して画像を表示する仕組みになっている。

【0007】

30

液晶表示装置において、凹凸を有している層間絶縁膜上に画素電極を形成した場合、層間絶縁膜の凹凸に沿って画素電極表面にも凹凸が形成されてしまう。この凹凸部が液晶の配向不良を引き起こす恐れがあった。

【0008】

一方、自発光型の発光素子としてEL素子を有した発光装置の研究が活発化している。この発光装置は有機ELディスプレイ、又は有機発光ダイオードとも呼ばれている。これらの発光装置は、動画表示に適した速い応答速度、低電圧、低消費電力駆動などの特徴を有しているため、新世代の携帯電話や携帯情報端末（PDA）をはじめ、次世代ディスプレイとして大きく注目されている。

【0009】

また、発光素子及びそれで構成される発光装置においても、同様に、凹凸を有している層間絶縁膜上に陽極（または陰極）を形成した場合、発光物質を含む層が薄いため、陽極と陰極との間でショートが生じる恐れがあった。

40

【0010】

このように、平坦化のために設ける層間絶縁膜としては、絶縁性が高く、且つ、平坦化率の高いものが要求されている。こうした層間絶縁膜の形成方法としては、CVD法や蒸着法よりもスピンドルコート法で代表される塗布法を用いることが好ましい（特許文献1参照。）。

【0011】

塗布法によって形成される層間絶縁膜の材料としては、シリコン（Si）と酸素（O）との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料が挙げられる。また

50

、置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料が挙げられる。これらの原料の代表例としては、シロキサン系ポリマーがある。

【特許文献1】特開2000-243834号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

しかしながら、塗布法を用いて形成するシリコン(Si)と酸素(O)との結合で骨格構造が構成される層間絶縁膜にコンタクトホールを開口し、配線を形成する場合、層間絶縁層に接してチタンのような金属元素膜を成膜すると、この膜がはがれるという問題点があつた。

10

【0013】

シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜に、チタン窒化物のような窒素化合物で形成される膜を成膜したのち金属元素膜を成膜すると、上記のような膜はがれの問題は解決するが、TFTの半導体領域とのコンタクト部での抵抗が高まりオーミックコンタクトができないという問題があつた。

【0014】

本発明では、シリコン(Si)と酸素(O)との結合で骨格構造が構成され平坦性を有する絶縁膜と、密着性が高く、かつ低抵抗を有する配線基板の構造及びその作製方法を提供することを課題とする。

【課題を解決するための手段】

20

【0015】

本発明の一は、半導体領域と、前記半導体領域表面に形成されたコンタクトホールを有する絶縁膜と、前記コンタクトホールを介して前記半導体領域に接する導電層とを有し、前記絶縁膜は、シリコンと酸素との結合で骨格構造が構成される絶縁膜であり、前記導電層は、窒素元素の組成比が7atomic%以上44atomic%未満であることを特徴とする配線基板である。

【0016】

また、本発明の一は、半導体領域と、前記半導体領域表面に形成されたコンタクトホールを有する絶縁膜と、前記コンタクトホールを介して前記半導体領域に接する導電層を有し、前記絶縁膜は、シリコンと酸素との結合で骨格構造が構成される絶縁膜であり、前記導電層の抵抗率は $100\mu\text{cm}$ 以上 $250\mu\text{cm}$ 未満であり、且つ前記半導体領域と前記導電層とのコンタクト抵抗が $1000$ 以上 $3000$ 未満であることを特徴とする配線基板である。

30

【0017】

また、本発明の一は、半導体層と、前記半導体表面に形成されたコンタクトホールを有する絶縁膜と、前記コンタクトホールを介して前記半導体領域に接続する導電層を有し、前記絶縁膜は、シリコンと酸素との結合で骨格構造が構成される絶縁膜であり、前記導電層の抵抗率は、 $100\mu\text{cm}$ 以上 $250\mu\text{cm}$ 未満であり、且つ前記半導体領域と前記導電層との接触抵抗率が $7 \cdot 1 \times 10^{-5} \cdot \text{cm}^2$ 以上 $2 \cdot 1 \times 10^{-4} \cdot \text{cm}^2$ 未満の窒素元素を含む導電膜が形成されていることを特徴とする配線基板である。

40

【0018】

また、本発明の一は、シリコンと酸素との結合で骨格構造が構成されている絶縁膜と密着性を有し、且つ半導体領域とオーミックコンタクトする濃度の窒素元素を含む導電膜が、前記絶縁膜及び半導体領域に接して形成されていることを特徴とする配線基板である。

【0019】

また、本発明の一は、シリコンと酸素との結合で骨格構造が構成されている絶縁膜と密着性を有する濃度の窒素元素を含む導電膜が、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜及び半導体領域に接して形成されていることを特徴とする配線基板である。

50

## 【0020】

また、本発明の一は、シリコンと酸素との結合で骨格構造が構成されている絶縁膜及び半導体領域表面に、窒素元素を含む導電層が接して形成され、前記窒素元素を含む導電層は、流量比が9:1~4:6の希ガスと窒素とをスパッタリングガスとし、チタンをターゲットとしてスパッタリング法により形成していることを特徴とする配線基板である。

## 【0021】

なお、前記窒素元素は、膜厚方向に対して濃度勾配を有してもよい。このとき、前記濃度勾配は、半導体領域付近において低いことが好ましい。

## 【0022】

また、前記窒素を含む導電層は、窒素元素の濃度の異なる導電層で積層されていてもよい。

## 【0023】

前記導電層は、チタン、モリブデン、タンゲステン、又はタンタルである。

## 【0024】

また、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜及び前記窒素元素を含む導電層の間に、窒素化合物で形成される層が形成されていても良い。前記窒素化合物で形成される層は、窒化チタン、窒化モリブデン、窒化タンゲステン、又は窒化タンタルである。

## 【0025】

また、前記窒素元素を含む導電層上に、低抵抗率を有する導電膜及びバリア性を有する導電層が積層されていてもよい。低抵抗を有する導電層としては、アルミニウム、タンゲステン、銅、金、銀から選ばれた元素、またはこれらの元素を主成分とする合金材料で形成される導電膜であり、前記バリア性を有する導電層は、チタン、モリブデン、タンゲステン、タンタルから選ばれた元素、又はこれらの元素で形成される化合物で形成される導電層が挙げられる。

## 【0026】

さらに、前記窒素元素を含む導電層上に、第一のバリア性を有する導電層、低抵抗率を有する導電層及び第2のバリア性を有する導電層が積層されててもよい。第一のバリア性を有する導電層は、チタン、モリブデン、タンゲステン、タンタルから選ばれた元素、又はこれらの元素で形成される化合物で形成される導電層であり、前記低抵抗を有する導電層は、アルミニウム、タンゲステン、銅、金、銀から選ばれた元素、またはこれらの元素を主成分とする合金材料で形成される導電層であり、前記第2のバリア性を有する導電層は、チタン、モリブデン、タンゲステン、タンタルから選ばれた元素、又はこれらの元素で形成される化合物で形成される導電層が挙げられる。

## 【0027】

また、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜は、平坦性を有する。ここで、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜は、下記構造式(1)で示される繰り返し単位を有することを特徴とする配線基板。

## 【化1】

(式中、R1及びR2はそれぞれ独立して、水素原子、ハロゲン、アルキル基、又はフェニル基、を示す。)

## 【0028】

また、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜は塗布法により

10

20

30

40

50

形成されている。

【0029】

また、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜は、シロキサンポリマーを用いて形成されている。

【0030】

また、本発明の一は、半導体領域上にシロキサンポリマーを含有する塗布材料を塗布し焼成して、シリコンと酸素との結合で骨格構造が構成されている絶縁膜を形成し、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜の一部をエッティングして、前記半導体領域の一部を露出し、前記露出された半導体領域及び前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜上に、流量比が9：1～4：6の希ガスと窒素とをスパッタリングガスとしてスパッタリング法により窒素を含む導電膜を形成し、前記窒素を含む導電膜の一部をエッティングして配線を形成することを特徴とする配線基板の作製方法である。10

【0031】

また、本発明の一は、半導体領域上にシロキサンポリマーを含有する塗布材料を塗布し焼成して、シリコンと酸素との結合で骨格構造が構成されている絶縁膜を形成し、前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜上に、窒素化合物で形成される導電膜を成膜し、前記窒素化合物及び前記シリコンと酸素との結合で骨格構造が構成されている絶縁膜の一部をエッティングして、前記半導体領域の一部を露出し、前記露出された半導体領域及び前記窒素化合物で形成される導電膜上に、流量比が9：1～4：6の希ガスと窒素とをスパッタリングガスとしてスパッタリング法により窒素を含む導電膜を形成し、前記窒素を含む導電膜の一部をエッティングして配線を形成することを特徴とする配線基板の作製方法である。20

【0032】

なお、前記窒素を含む導電膜上に低抵抗材料で形成される導電膜及び第1のバリア性を有する導電膜を成膜したのち、前記窒素を含む導電膜、前記低抵抗で形成される導電膜、及び前記第1のバリア性を有する導電膜の一部をエッティングして配線を形成してもよい。

【0033】

また、前記窒素を含む導電膜上に、第2のバリア性を有する導電膜を形成した後、前記低抵抗材料で形成される導電膜及び前記第1のバリア性を有する導電膜を成膜し、前記窒素を含む導電膜、第2のバリア性を有する導電膜、前記低抵抗で形成される導電膜、及び前記第1のバリア性を有する導電膜の一部をエッティングして配線を形成してもよい。30

【0034】

また、本発明の一は、上記配線基板を有する半導体装置である。半導体装置の代表例としては、液晶表示パネルに代表される電気光学装置や有機発光素子を有する発光表示装置、またそれらを部品として搭載した電子機器、IC(Integrated Circuit)、LSI(Large scale Integration)等が挙げられる。

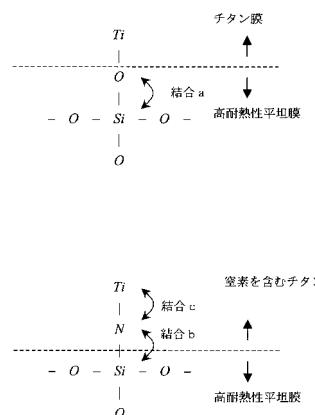

【0035】

図15(A)に、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜に、金属元素膜、例えばチタン膜を成膜した場合の、絶縁膜とチタン膜との結合の一部分のモデル図の一つを示す。図15(A)に示すように、シリコンと酸素の結合の延長上にチタンが結合される。この場合、シリコンと結合している酸素と、チタンの結合力(結合a)は弱いため、密着性が低い。40

【0036】

一方、図15(B)に、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜に、窒素元素を含む金属元素膜、例えば窒素を含むチタン膜を成膜した場合の、絶縁膜と導電膜との結合の一部分のモデル図の一つを示す。図15(B)に示すように、シリコンと窒素が結合し、この結合の延長上にチタンが結合される。シリコンと結合している窒素と、チタンの結合力(結合b)、及び窒素とチタンの結合力(結合c)は強いため、密着性が高くなる。50

**【発明の効果】****【0037】**

シリコン及び酸素を含み、平坦性を有する絶縁膜上に7～44 atomic%の窒素元素を含む導電膜を配線として形成することにより、配線とコントラクト部と接触抵抗を高めずとも絶縁膜と配線との密着性を向上させることができが可能な配線基板を作製することができる。よって、歩留まり高く半導体装置を形成することが可能である。

**【発明を実施するための最良の形態】****【0038】**

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて、本発明は本実施形態の記載内容に限定して解釈されるものではない。例えば、配線と接触する部材として半導体薄膜を例に挙げて述べているが、これは、半導体薄膜に限らない。この代わりに、半導体基板を用いることも可能である。また、半導体素子として、薄膜トランジスタ(TFT)を用いて説明するが、特に限定はされない。例えば、MOSトランジスタ、有機トランジスタ、ダイオード等の半導体素子を同様に用いても良い。

10

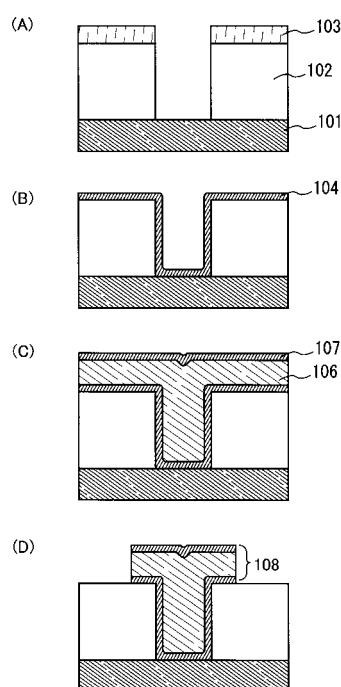

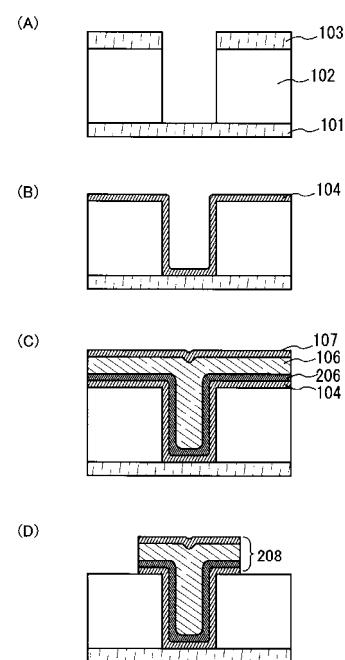

**【0039】****(第1実施形態)****【0040】**

図1は、本発明の第1実施形態の主要工程を示す断面図である。図1(A)に示すように、基板(図示しない。)上に形成された半導体薄膜101上にシリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜102を形成する。シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜の形成方法として塗布法を用いる。

20

**【0041】**

なお、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜は、塗布法で形成するため、平坦性が高い。また、有機樹脂で形成される絶縁膜よりも耐熱性が高い。このため、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜を高耐熱性平坦化膜と呼ぶ。

**【0042】**

この塗布法による絶縁膜の形成方法は、まず、シリコン(Si)と酸素(O)との結合を有する低分子成分(前駆体)を溶媒に溶解させたワニスと呼ばれる液状原料を基板上にスピンドルコート法などにより塗布する。その後、ワニスを基板とともに加熱して溶媒の揮発(蒸発)と、低分子成分の架橋反応とを進行させることによって、薄膜としての絶縁膜を得ることができる。また、膜厚は、スピンドル回転数、回転時間、ワニスの濃度および粘度によって制御する。

30

**【0043】**

絶縁膜の材料としては、シリコン(Si)と酸素(O)との結合で骨格構造が構成され、置換基に少なくとも水素を含む材料が用いられる。または置換基にフッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いる。代表的には、下式2に示されるシロキサン系ポリマーを用いる。

40

**【0044】**

## 【化2】

(R1、R2は、-H、-CH<sub>3</sub>、-CH<sub>2</sub>、-C<sub>6</sub>H<sub>5</sub>など)

10

## 【0045】

シリコサンの構造により、例えば、シリカガラス、アルキルシリコサンポリマー、アルキルシルセスキオキサンポリマー、水素化シルセスキオキサンポリマー、水素化アルキルシリセスキオキサンポリマーなどに分類することができる。

## 【0046】

また、絶縁膜の材料としてSi-N結合を有するポリマー（ポリシラザン）を含む液状原料を用いてもよい。

## 【0047】

次に、この絶縁膜（高耐熱性平坦化膜）102上にフォトレジスト膜を塗布し、露光及び現像により所望の形状のフォトレジストマスク103を形成して、絶縁膜102の一部をエッティングしてコンタクトホールを形成する。

20

## 【0048】

次に、図1(B)に示すように、露出された半導体薄膜及び絶縁膜（高耐熱性平坦化膜）102上に第1の導電膜104を形成する。第1の導電膜としては、シリコン(Si)と酸素(O)との結合で骨格構造が構成されている絶縁膜（高耐熱性平坦化膜）と密着性を有する濃度の窒素元素を含むチタン薄膜で形成することができる。このときの膜厚は、5~100nmとする。このときの作製方法は、希ガスと窒素との流量比を9:1~4:6とするスパッタリング法、またはCVD法等を用いて形成する。

## 【0049】

なお、希ガスと窒素は、スパッタリング法又はCVD法における原料用のガスである。

30

## 【0050】

第1の導電膜に7~44 atomic%窒素が含まれていることにより、半導体薄膜と第1の導電膜との接触抵抗を下げたまま、シリコンと酸素で骨格構造が構成される絶縁膜（高耐熱性平坦化膜）と第1の導電膜との密着性を向上させることができる。また、第1の導電膜として、窒素元素を含むモリブデン(Mo)、タンクステン(W)、タンタル(Ta)薄膜等を用いることができる。

## 【0051】

なお、第1の導電膜は、膜厚方向に対して窒素の濃度勾配を有しても良い。この場合、半導体薄膜側の窒素濃度が低い方が好ましい。また、第1の導電膜は、窒素元素の濃度の異なる導電膜を積層してもよい。さらには、積層構造で濃度勾配を有しても良い。

40

## 【0052】

次に、図1(C)に示すように、第1の導電膜上に第2の導電膜106及び第3の導電膜107をスパッタリング法等の公知の手法により形成する。第2の導電膜としては、低抵抗を有する材料で形成されており、代表的にはアルミニウム(Al)、銅(Cu)、タンクステン(W)、銅(Cu)、金(Ag)、銀(Ag)から選ばれた元素、またはこれらの元素を主成分とする合金材料で形成することが可能である。また、第2の導電膜の膜厚は、200~800nmである。

## 【0053】

また、第3の導電膜としては、スパッタリング法、CVD法等の公知の手法により、第2の導電膜表面に後に形成される導電膜からの元素拡散を抑制するバリア膜であって、チ

50

タン( Ti )、モリブデン( Mo )、タングステン( W )、タンタル( Ta )から選ばれた元素、又はこれらの元素で形成される化合物等で形成することができる。第3の導電膜の膜厚は、5~100 nmである。

#### 【 0 0 5 4 】

代表的な、配線の積層構造としては、窒素元素を含むチタン＼アルミニウム－シリコン合金＼チタン、窒素元素を含むタンタル＼銅＼タンタル、窒素元素を含むタングステン＼銅＼タングステン、窒素元素を含むモリブデン＼アルミニウム－ネオジウム合金＼タンタルが挙げられる。

#### 【 0 0 5 5 】

このときの積層構造は、半導体薄膜側から積層される順に膜の種類を列挙している。

10

#### 【 0 0 5 6 】

なお、配線の積層構造、すなわち第1の導電膜、第2の導電膜、及び第3の導電膜の組み合わせは、上記以外にも任意に選択することができる。

#### 【 0 0 5 7 】

次に、図1( D )に示すように、第3の導電膜上にフォトレジストを塗布し、露光及び現像を行って所望の形状のフォトレジストマスク( 図示しない。 )を形成する。この後、第3の導電膜、第2の導電膜、第1の導電膜を順次エッチングして、配線108を形成する。

#### 【 0 0 5 8 】

上記の配線構造は、半導体薄膜と7~44 atomic%の窒素元素を含む導電膜が接しており、これらの接触抵抗が低い。また、シリコン( Si )と酸素( O )との結合で骨格構造が構成される絶縁膜( 高耐熱性平坦化膜 )と、窒素元素を含む導電膜とが接しているためこれらの密着性が高く、膜はがれが生じにくい。このため、歩留まり高く半導体装置を作製することができる。

20

#### 【 0 0 5 9 】

( 第2実施形態 )

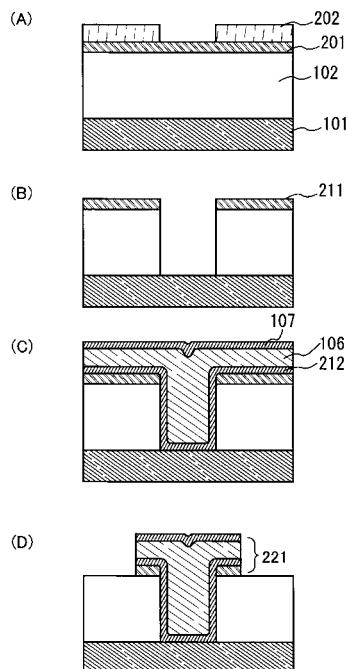

#### 【 0 0 6 0 】

本実施形態では、第1実施形態とは異なる構造の配線を形成する工程を述べる。本実施形態では、第1実施形態で示す配線構造において、第1の窒素元素を含む導電膜と第2の導電膜との間に、バリア膜を有する構造を、図2を用いて示す。

30

#### 【 0 0 6 1 】

図2( A )に示すように、第1実施形態と同様に、半導体薄膜101上にシリコン( Si )と酸素( O )との結合で骨格構造が構成される絶縁膜( 高耐熱性平坦化膜 )102を形成し、その絶縁膜102上にフォトレジスト膜を塗布し、露光及び現像により所望の形状のフォトレジストマスク103を形成して、絶縁膜102の一部をエッチングしてコントакトホールを形成する。

#### 【 0 0 6 2 】

次に、図2( B )に示すように、露出された半導体薄膜及び絶縁膜( 高耐熱性平坦化膜 )102上に第1の導電膜104を形成する。第1の導電膜としては、第1実施形態と同様の作製方法により、シリコン( Si )と酸素( O )との結合で骨格構造が構成されている絶縁膜( 高耐熱性平坦化膜 )と密着性を有する濃度、即ち7~44 atomic%の窒素元素を含むチタン薄膜、モリブデン( Mo )、タングステン( W )、又はタンタル( Ta )で形成することができる。このように、第1の導電膜に窒素が含まれていることにより、半導体薄膜と第1の導電膜との接触抵抗を下げたまま、シロキサンで形成される絶縁膜( 高耐熱性平坦化膜 )と第1の導電膜との密着性を向上させることができる。

40

#### 【 0 0 6 3 】

次に、図2( C )に示すように、第1の導電膜上104にバリア膜206をスパッタリング法やCVD法等の公知の手法により形成する。バリア膜としては、導電性を有し、次に形成される第2の導電膜から第1の導電膜、又は半導体薄膜へ元素が拡散するのを抑制する膜である。これは、チタン( Ti )、モリブデン( Mo )、タングステン( W )、タ

50

ンタル (Ta) から選ばれた元素、又はこれらの元素で形成される化合物で形成することができる。バリア膜の膜厚は、5 ~ 100 nmである。

#### 【0064】

次に、バリア膜206上に、第2の導電膜106及び第3の導電膜107を順次形成する。第2の導電膜及び第3の導電膜は、第1実施形態と同様の材料で形成することができる。

#### 【0065】

本実施形態において、代表的な配線の積層構造としては、窒素元素を含むチタン＼窒化チタン＼アルミニウム－シリコン合金＼チタン、窒素元素を含むタンタル＼窒化タンタル＼銅＼タンタル、窒素元素を含むタングステン＼窒化タングステン＼銅＼タングステン、窒素元素を含むモリブデン＼窒化モリブデン＼アルミニウム－ネオジウム合金＼タンタル等が挙げられる。10

#### 【0066】

このときの積層構造は、半導体薄膜側から積層される順に膜の種類を列挙している。

#### 【0067】

なお、配線の積層構造、すなわち第1の導電膜、バリア膜、第2の導電膜、及び第3の導電膜の組み合わせは、上記以外にも任意に選択することができる。

#### 【0068】

次に、図2(D)に示すように、第3の導電膜上にフォトレジストを塗布し、露光及び現像を行って所望の形状のフォトレジストマスク(図示しない。)を形成する。この後、20

第3の導電膜、第2の導電膜、バリア膜、及び第1の導電膜を順次エッチングして、配線208を形成する。

#### 【0069】

上記の配線構造は、半導体薄膜と7~44 atomic%の窒素元素を含む導電膜が接しており、これらの接触抵抗が低い。また、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜(高耐熱性平坦化膜)と、窒素元素を含む導電膜とが接しているためこれら密着性が高く、膜はがれが生じにくい。さらに、第1の導電膜と第2の導電膜の間にバリア膜が形成されているため、第2の導電膜から第1の導電膜、又は半導体薄膜へ元素が拡散するのを抑制することができ、ヒロック等の突起物の形成を抑制することができる。30

#### 【0070】

(第3実施形態)

#### 【0071】

本実施形態では、第1実施形態及び第2実施形態とは異なる構造の配線を形成する工程を述べる。

#### 【0072】

図3(A)に示すように、第1実施形態と同様に、半導体薄膜101上にシリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜(高耐熱性平坦化膜)102を形成し、その上に窒素化合物で形成される膜201を形成する。窒素化合物で形成される膜としては、窒化チタン(TiN)、窒化モリブデン(MoNx)、窒化タングステン(WNx)、窒化タンタル(TaNx)等で形成することができる。次に、窒素化合物で形成される膜上にフォトレジストを塗布し、露光及び現像を行って、所望の形状を有するフォトレジストマスク202を形成する。40

#### 【0073】

次に、図3(B)に示すように、フォトレジストマスク202を用いて窒素化合物で形成される膜201及び絶縁膜(高耐熱性平坦化膜)102をエッチングしてコンタクトホールを形成する。

#### 【0074】

この後、図3(C)に示すように、窒素化合物で形成される膜201及び露出された半導体薄膜表面に第1の導電膜212、第2の導電膜106、第3の導電膜107を順次形50

成する。第1の導電膜としては、シリコン(Si)と酸素(O)との結合で骨格構造が構成されている絶縁膜(高耐熱性平坦化膜)と密着性を有する濃度、即ち、7~44 atomic %の窒素元素含むチタン(Ti)、モリブデン(Mo)、タングステン(W)、又はタンタル(Ta)薄膜で形成することができる。第2の導電膜及び第3の導電膜としては、第1実施形態で示される材料で形成することができる。

## 【0075】

次に、図3(D)に示すように、第1実施形態と同様にフォトマスク(図示しない。)を形成して第3の導電膜、第2の導電膜、第1の導電膜、窒素化合物で形成される膜を、所望の形状に順次エッチングして配線221を形成する。

## 【0076】

なお、配線の積層構造、すなわち窒素化合物で形成される膜、第1の導電膜、第2の導電膜、及び第3の導電膜の組み合わせは、任意に選択することができる。

## 【0077】

なお、本実施形態において、窒素を含む導電膜と低抵抗の導電膜との間に、第2実施形態で示されるような、導電性を有し、かつ第2の導電膜から第1の導電膜、又は半導体薄膜へ元素が拡散するのを抑制するバリア膜、代表的には、チタン(Ti)、モリブデン(Mo)、タングステン(W)、タンタル(Ta)から選ばれた元素、又はこれらの元素で形成される化合物で形成される膜を形成しても良い。

## 【0078】

上記の配線構造は、半導体薄膜と7~44 atomic%の窒素元素を含む導電膜が接しており、これらの接触抵抗が低い。また、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜(高耐熱性平坦化膜)と、窒素元素を含む導電膜および窒素化合物で形成される膜とが接しているためこれらの密着性が高く、膜はがれが生じにくい。このため、歩留まり高く半導体装置を作製することができる。

## 【実施例1】

## 【0079】

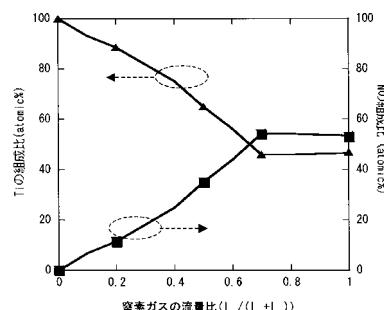

本実施例では、本発明を適応して形成した窒素元素を含む導電膜の組成比、抵抗率及びコンタクト抵抗値について述べる。ここでは、窒素元素を含む導電膜の代表例として、窒素元素を含むチタン膜を挙げる。

## 【0080】

表1及び図16は、ターゲットをチタンとして、アルゴン及び窒素雰囲気でスパッタリングして形成した窒素元素を含むチタン膜の各元素の組成比をラザフォード後方散乱法(RBS)にて測定した結果を示すものである。

## 【表1】

| ArガスとN <sub>2</sub> ガスの流量(sccm) | 窒素ガスの流量比 N <sub>2</sub> /(Ar+N <sub>2</sub> ) | 膜中のTiの組成比 (atomic%) | 膜中のNの組成比 (atomic%) |

|---------------------------------|-----------------------------------------------|---------------------|--------------------|

| Ar/N <sub>2</sub> =20/0         | 0                                             | 100                 | 0                  |

| Ar/N <sub>2</sub> =45/5         | 0.1                                           | 93                  | 7                  |

| Ar/N <sub>2</sub> =40/10        | 0.2                                           | 88.5                | 11.5               |

| Ar/N <sub>2</sub> =30/20        | 0.4                                           | 75                  | 25                 |

| Ar/N <sub>2</sub> =25/25        | 0.5                                           | 65                  | 35                 |

| Ar/N <sub>2</sub> =20/30        | 0.6                                           | 56                  | 44                 |

| Ar/N <sub>2</sub> =15/35        | 0.7                                           | 46                  | 54                 |

| Ar/N <sub>2</sub> =10/40        | 0.8                                           | 46                  | 54                 |

| Ar/N <sub>2</sub> =0/50         | 1                                             | 47                  | 53                 |

## 【0081】

チャンバー内のガスに対する窒素ガスの流量比(1<sub>N<sub>2</sub></sub> / (1<sub>N<sub>2</sub></sub> + 1<sub>Ar</sub>))が0.1から0.6、すなわちアルゴンガスと窒素ガスの流量比が9:1~4:6においては、窒素ガス

10

20

30

40

50

の流量が増えるにつれ膜中の窒素元素の組成比が増加する。しかし、窒素ガスの流量比が0.7、すなわちアルゴンガスと窒素ガスの流量比が3:7以上では、膜中のチタン元素に対する窒素元素の組成比が一定となる。このときの窒素元素の組成比は、窒化チタン(チャンバー内のガスを窒素のみとしてスパッタリングし、形成したもの)とほぼ同様である。

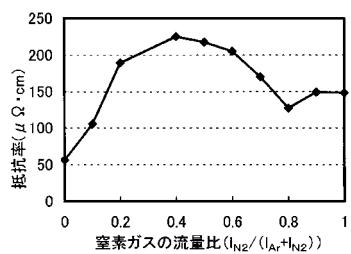

#### 【0082】

次に、表1に示す窒素元素を含む導電膜と同様条件で形成した膜、それぞれの抵抗率を表2及び図17に示す。アルゴンと窒素ガス中の窒素ガスの流量比( $l_{N_2} / (l_{N_2} + l_{Ar})$ )が0.1の条件で作製した導電膜、即ちチタン元素と窒素元素の組成比がそれぞれ93 atomic%、7 atomic%の膜では、抵抗率が $105 \mu\Omega\text{cm}$ であり、アルゴンと窒素ガス中の窒素ガスの流量比( $l_{N_2} / (l_{N_2} + l_{Ar})$ )が0.4、すなわちアルゴンガスと窒素ガスの流量比が6:4の条件で作製した導電膜、即ちチタン元素と窒素元素の組成比がそれぞれ75 atomic%、25 atomic%の膜では、抵抗率が $225 \mu\Omega\text{cm}$ である。

#### 【表2】

| 窒素ガスの<br>流量比<br>$N_2/(Ar+N_2)$ | 抵抗率<br>( $\mu\Omega\text{cm}$ ) |

|--------------------------------|---------------------------------|

| 0                              | 57                              |

| 0.1                            | 106                             |

| 0.2                            | 189                             |

| 0.4                            | 225                             |

| 0.5                            | 218                             |

| 0.6                            | 205                             |

| 0.7                            | 170                             |

| 0.8                            | 127                             |

| 0.9                            | 149                             |

| 1                              | 148                             |

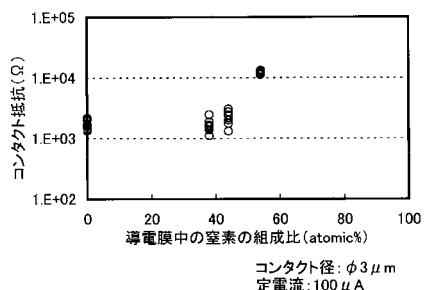

#### 【0083】

次に、表1及び表2で示される窒素を含む導電膜を有する配線と半導体領域とのコンタクト抵抗値を測定した結果を表3及び図18に示す。なお、このときの配線構造は、半導体領域\ (窒素元素を含む)チタン\アルミニウムシリコン合金\チタンとなっている。

#### 【表3】

| 膜中のNの<br>組成比<br>(atomic%) | 平均抵抗<br>( $\Omega$ ) |

|---------------------------|----------------------|

| 0                         | 1714                 |

| 38                        | 1646                 |

| 44                        | 2223                 |

| 54                        | 11848                |

| 54.1                      | 12601                |

#### 【0084】

測定試料としては、アルゴンガスのみを用いて形成したチタン膜、チャンバー内のガスに対する窒素ガスの流量比( $l_{N_2} / (l_{N_2} + l_{Ar})$ )が0.5、即ちアルゴンガスと窒素ガスの流量比が5:5の条件で作製した導電膜、即ちチタン元素と窒素元素それぞれの組成比が65 atomic%と35 atomic%の膜、同様の比が0.6の条件で作製した導電膜、即ちチタン元素と窒素元素それぞれの組成比が56 atomic%と44 atomic%の膜、同様の比が0.

10

20

30

40

50

7の条件で作製した導電膜、即ちチタン元素と窒素元素それぞれの組成比が4.6 atomic%と5.4 atomic%の膜の4種類を用いる。

#### 【0085】

なお、コンタクト抵抗の測定方法には、ケルビンパターン測定法を用いる。これは、コンタクトホールを中心として、電流端子と電圧測定端子が対向して配置され、半導体領域と導電膜との間に電流Iを流し、電圧測定端子間の電圧差Vを測定し、この結果からコンタクト抵抗を求めるものである（伊藤隆司、石川元、中村宏昭著「電子材料シリーズ VLSIの薄膜技術」、第3刷、丸善株式会社、平成4年10月10日、p.205-206参照）。

#### 【0086】

膜中のチタン元素と窒素元素の組成比が6.5 atomic%、3.5 atomic%の膜、及びそれよりも窒素元素の組成比が低い膜では、チタン膜と同様のコンタクト抵抗値であって、半導体領域と十分なコンタクトを取ることができる。一方、膜中のチタン元素と窒素元素の組成比が、それぞれ4.6 atomic%、5.4 atomic%では、コンタクト抵抗値が高くなっている。このため、半導体領域との十分なコンタクトが取れない。

#### 【0087】

以上の結果から、膜中の窒素元素の組成比が7 atomic%以上4.4 atomic%未満の導電膜は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜と密着性がよく、且つ半導体領域と十分なコンタクトをとれる導電膜である。

#### 【0088】

また、抵抗率が100 μ cm以上250 μ cm未満、好ましくは105 μ cm以上225 μ cm未満で、且つコンタクト抵抗が1000 以上3000 未満、好ましくは1645 以上2223 未満の窒素元素を含む導電膜は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜と密着性がよく、且つ半導体領域と十分なコンタクトをとれる導電膜である。

#### 【0089】

さらには、窒素元素の組成比が7 atomic%以上4.4 atomic%未満であって、抵抗率が100 μ cm以上250 μ cm未満、好ましくは105 μ cm以上225 μ cm未満で、コンタクト抵抗が1000 以上3000 未満、好ましくは1645 以上2223 未満の窒素元素を含む導電膜は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜と密着性がよく、且つ半導体領域と十分なコンタクトをとれる導電膜である。

#### 【0090】

本実施例のような導電膜を用いることで、配線とコンタクト部と接触抵抗を高めずとも絶縁膜と配線との密着性を向上させることができ可能な配線基板を作製することができる。よって、歩留まり高く半導体装置を形成することが可能である。

#### 【実施例2】

#### 【0091】

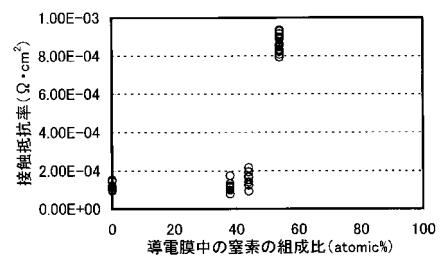

本実施例では、実施例1で示された窒素元素を含む導電膜の接触抵抗率(比接触抵抗)を示す。比接触抵抗とは、コンタクト抵抗と面積の積で求められる。

#### 【0092】

実施例1で示したコンタクト抵抗を元に、各導電膜の接触抵抗率(比接触抵抗)を表4及び図19に示す。なお、実施例1において、コンタクト抵抗を測定したコンタクトホールは、直径3 μ mである。

10

20

30

40

【表4】

| 膜中のNの組成比<br>(atomic%) | 平均接触抵抗率<br>( $\Omega \cdot \text{cm}^2$ ) |

|-----------------------|-------------------------------------------|

| 0                     | 1.2E-04                                   |

| 38                    | 1.2E-04                                   |

| 44                    | 1.6E-04                                   |

| 54                    | 8.4E-04                                   |

| 54.1                  | 8.9E-04                                   |

10

## 【0093】

以上の結果から、膜中の窒素元素の組成比が7 atomic%以上44 atomic%未満の導電膜は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜と密着性がよく、且つ半導体領域と十分なコンタクトをとれる導電膜である。

## 【0094】

また、抵抗率が $100 \mu \text{ cm}$ 以上 $250 \mu \text{ cm}$ 未満、好ましくは $105 \mu \text{ cm}$ 以上 $225 \mu \text{ cm}$ 未満で、且つ接触抵抗率(比接触抵抗)が $7.1 \times 10^{-5} \cdot \text{cm}^2$ 以上 $2.1 \times 10^{-4} \cdot \text{cm}^2$ 未満、好ましくは $1.2 \times 10^{-4} \cdot \text{cm}^2$ 以上 $1.6 \times 10^{-4} \cdot \text{cm}^2$ の窒素元素を含む導電膜は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜と密着性がよく、且つ半導体領域と十分なコンタクトをとれる導電膜である。

20

## 【0095】

さらには、窒素元素の組成比が7 atomic%以上44 atomic%未満であって、抵抗率が $100 \mu \text{ cm}$ 以上 $250 \mu \text{ cm}$ 未満、好ましくは $105 \mu \text{ cm}$ 以上 $225 \mu \text{ cm}$ 未満で、接触抵抗率(比接触抵抗)が $7.1 \times 10^{-5} \cdot \text{cm}^2$ 以上 $2.1 \times 10^{-4} \cdot \text{cm}^2$ 未満、好ましくは $1.2 \times 10^{-4} \cdot \text{cm}^2$ 以上 $1.6 \times 10^{-4} \cdot \text{cm}^2$ 未満の窒素元素を含む導電膜は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される絶縁膜と密着性がよく、且つ半導体領域と十分なコンタクトをとれる導電膜である。

## 【0096】

30

本実施例のような導電膜を用いることで、配線とコンタクト部と接触抵抗を高めずとも絶縁膜と配線との密着性を向上させることができ可能な配線基板を作製することができる。よって、歩留まり高く半導体装置を形成することが可能である。

## 【実施例3】

## 【0097】

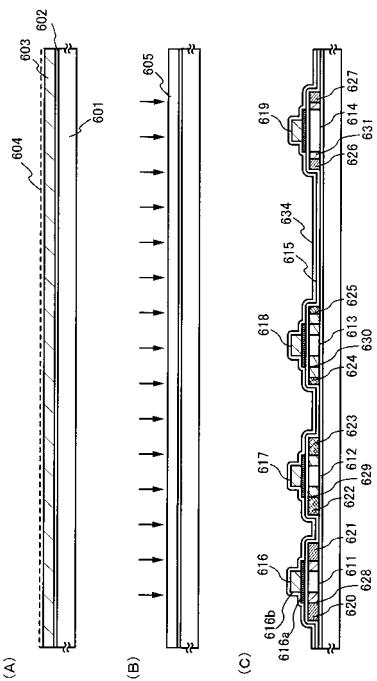

本実施例では、本発明を用いて形成された半導体素子及び該半導体素子を有するアクティブマトリクス基板の作製工程を、図4、図5を用いて説明する。なお、本実施例において、半導体素子の代表例として、薄膜トランジスタを用いるが、この他、有機薄膜トランジスタ、薄膜ダイオード、光電変換素子、抵抗等も半導体素子として用いることができる。

40

## 【0098】

図4(A)に示すように、ガラス基板(第1の基板601)上に下地絶縁膜602を形成する。本実施例では、下地絶縁膜を2層構造とし、SiH<sub>4</sub>、NH<sub>3</sub>、及びN<sub>2</sub>Oを反応ガスとして成膜される第1の酸化窒化シリコン膜を50~100 nm、SiH<sub>4</sub>、及びN<sub>2</sub>Oを反応ガスとして成膜される第2の酸化窒化シリコン膜を100~150 nmの厚さに積層形成する。なお、この下地絶縁膜を2層構造とせず、一層構造としてもよい。また、ガラス基板の代わりに、石英、金属、プラスチック等を用いることもできる。

## 【0099】

次に、下地絶縁膜上に、プラズマCVD法や減圧CVD法、或いはスパッタリング法等の公知の手法により非晶質シリコン膜603(膜厚54 nm)を積層形成する。

50

## 【0100】

次に特開平8-78329号公報に記載の公知技術によって非晶質シリコン膜603を結晶化する。同公報記載の技術は、非晶質シリコン膜に対して結晶化を助長する金属元素を選択的に添加し、加熱処理を行うことで添加領域を起点として広がる結晶構造を有する半導体膜を形成するものである。

## 【0101】

ここでは、加熱処理を行い、結晶化を行う。この場合、結晶化は半導体の結晶化を助長する金属元素が接した半導体膜の部分でシリサイドが形成され、それを核として結晶化が進行する。脱水素化のための熱処理(450、1時間)の後、結晶化のための熱処理(550～650で4～24時間)を行う。

10

## 【0102】

この後、結晶性シリコン膜中から金属元素のゲッタリングを行い、結晶性シリコン膜中の金属元素を除去又は濃度を低減する。ゲッタリングの手法としては、結晶シリコン膜の一部にリン又は希ガス(代表的にはアルゴン)などを添加してゲッタリングサイトを形成した後、熱処理を行って金属元素を移動させる方法、若しくはリン又は希ガスなどを含有した非晶質シリコン膜又は結晶質シリコン膜を酸化膜を介して積層し、ゲッタリングサイトとして熱処理を行って金属元素をゲッタリングサイトに移動させる方法を用いれば良い。ゲッタリング後の結晶性シリコン膜の不純物金属元素濃度を $1 \times 10^{17} / \text{cm}^3$ 以下(SIMS(二次イオン質量分析法)の測定限界以下)とすることが好ましく、より好ましくはICP-MS(誘導結合高周波プラズマ分光質量分析法)により $5 \times 10^{16} / \text{cm}^3$ 以下とすることである。

20

## 【0103】

次いで、結晶化率(膜の全体積における結晶成分の割合)を高め、結晶粒内に残される欠陥を補修するために、結晶性シリコン膜605に対してレーザ光を照射することが好ましい。(図4(B))。

## 【0104】

次に、結晶性シリコン膜を用い、公知の手法によりTFTを形成する。図4(C)にその図を示す。結晶質シリコン膜を所望の形状にエッチングし、活性領域611～614を形成する。次に、シリコン膜の表面をフッ酸を含むエッチャントで洗浄した後、ゲート絶縁膜615となるシリコンを主成分とする絶縁膜を形成する。

30

## 【0105】

なお、結晶性半導体膜のほかに、微結晶半導体膜を用いて半導体領域を形成することができる。

## 【0106】

微結晶半導体膜とは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、0.5～20nmの結晶粒を含んでいる。

## 【0107】

微結晶半導体膜は、珪化物気体をグロー放電分解(プラズマCVD)して形成する。珪化物気体としては、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などを用いる。また、この珪化物気体をH<sub>2</sub>、又は、H<sub>2</sub>とHe、Ar、Kr、Neから選ばれた一種または複数種の希ガス元素で希釈しても良い。希釈率は2～1000倍の範囲であることが好ましい。このときの、圧力は概略0.1Pa～133Paの範囲であり、電源周波数は1MHz～120MHz、好ましくは13MHz～60MHzとする。基板加熱温度は300以下でよく、好ましくは100～250である。膜中の不純物元素として、酸素、窒素、炭素などの大気成分の不純物は $1 \times 10^{20} \text{ cm}^{-2}$ 以下とすることが望ましく、特に、酸素濃度は $5 \times 10^{19} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{19} / \text{cm}^3$ 以下とする。

40

## 【0108】

また、ゲート絶縁膜として、窒化珪素膜を用いることにより、半導体薄膜及びゲート絶

50

縁膜界面を、後に形成される第1の導電膜又は第2の導電膜を形成する際に生じるスパッタ衝撃から、守ることが可能である。

#### 【0109】

次いで、ゲート絶縁膜表面を洗浄した後、ゲート電極616～619を形成する。本実施例では、ゲート電極は積層構造をしており、ゲート絶縁膜に接する第1導電膜616a及び該第1導電膜に接する第2導電膜616bからなる。第1導電膜は窒化タンタル膜からなり、第2の導電膜は、タングステン膜からなる。ただし、ゲート電極の材料は、これに限られるものではなく、いずれもタンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジム(Nd)から選ばれた元素、またはこれらの元素を主成分とする合金材料若しくは化合物材料で形成してもよい。また、銀銅パラジウム合金(AgPdCu合金)を用いてもよい。さらに、本実施例では、ゲート電極を積層構造としたが、これに限られるものではなく単層構造でもさらに多くの積層構造でもよい。10

#### 【0110】

なお、ゲート絶縁膜に接する第1導電膜616aを形成する前にPECVD法により、N型を呈するシリコン膜を形成しても良い。この場合、後に形成される第1の導電膜及び第2の導電膜を形成する際に生じるスパッタ衝撃からゲート絶縁膜を守ることが可能である。なお、このN型を呈するシリコン膜は、ゲート電極として用いる。

#### 【0111】

次に、半導体にn型を付与する不純物元素(P、As等)及びP型を付与する不純物元素(B等)、ここではリン及びボロンを適宜添加して、nチャネル型TFT及びpチャネル型TFTのソース領域及びドレイン領域620～627、及びLDD領域(Light doped drain領域)628～631を形成する。LDD領域628～630の一部は、各ゲート電極に覆われているが、LDD領域631では、各ゲート電極に覆われていない。なお、ゲート電極及びLDD領域の形成工程に関しては、特開2001-345453号公報に開示された工程を適応すればよい。20

#### 【0112】

次に、添加した不純物元素を活性化するために加熱処理、強光の照射、またはレーザ光の照射を行う。この工程は、活性化と同時にゲート絶縁膜へのプラズマダメージやゲート絶縁膜と半導体膜との界面へのプラズマダメージを回復することができる。この後、ゲート電極及びゲート絶縁膜上に第2絶縁膜634を形成する。第2の絶縁膜としては、水素を含有する酸化窒化珪素膜または窒化酸化珪素膜を形成する。30

#### 【0113】

次に、図5に示すように第2絶縁膜634上に第1の層間絶縁膜635を形成する。第1の層間絶縁膜としては、シロキサン系ポリマーを全面塗布した後、50～200、1～10分間の熱処理によって乾燥させた後、さらに200～450、好ましくは300～450、0.1～1.2時間、好ましくは1～1.2時間の焼成処理を行う。この焼成により、1μm厚のシリコン(Si)と酸素(O)との結合で骨格構造が構成される第1の層間絶縁膜(高耐熱性平坦化膜)を全面に成膜する。この工程は、シロキサン系ポリマーの焼成を行うと共に、第2の絶縁膜634中の水素によって、半導体領域を水素化することが可能であるため、工程数を削減でき、プロセスを簡略化することが可能である。40

#### 【0114】

塗布法により形成して第1の層間絶縁膜の平坦性を高めたことにより、ゲート電極や半導体層に起因する凹凸部をなくし、液晶の配向不良を防止することができる。また、後のコンタクトホール形成のために第1の層間絶縁膜の膜厚を薄くすることが好ましい。

#### 【0115】

また、第1の層間絶縁膜として、CVD法等の公知の手法により形成される無機絶縁膜又は有機材料樹脂を用いることができる。なお、有機樹脂を用いる場合は、感光性樹脂及び非感光性樹脂を用いることができる。感光性有機樹脂を用いた場合、フォトリソフライ工程による露光処理を行い、感光性有機樹脂をエッチングすると曲率を有する第1の開50

口部を形成することができる。このように曲率を有する開口部を形成することは、後に形成する電極の被覆率（カバレッジ）が高くなるという効果がある。

#### 【0116】

この後、第1の層間絶縁膜635を覆うように、CVD法により窒化酸化珪素膜又は酸化窒化珪素膜を形成しても良い。この膜は、後に形成される導電膜をエッチングするときに、エッチングストッパーとして働き、層間絶縁膜のオーバーエッチングを防止することができる。さらにこの上に、スパッタリング法により窒化珪素膜を形成してもよい。この窒化珪素膜は、アルカリ金属イオンの移動を抑制する働きがあるため、後に形成される画素電極からのリチウム元素、ナトリウム等の金属イオンが半導体薄膜へ移動するのを抑制することができる。

10

#### 【0117】

次に、第1の層間絶縁膜のパターニング及びエッチングを行い、第1の開口部を形成する。このエッチング工程で用いるエッチング用ガスに限定はないが、ここではCF<sub>4</sub>、O<sub>2</sub>、He、Arを用いることが適している。CF<sub>4</sub>の流量を380 sccm、O<sub>2</sub>の流量を290 sccm、Heの流量を500 sccm、Arの流量を500 sccm、RFパワーを3000 W、圧力を25 Paとし、ドライエッチングを行う。なお、半導体領域上に残渣を残すことなくエッチングするためには、10～20%程度の割合でエッチング時間を増加させると良い。1回のエッチングでテーパー形状としてもよいし、複数のエッチングによってテーパー形状にしてもよい。ここでは、さらにCF<sub>4</sub>、O<sub>2</sub>、Heを用いて、CF<sub>4</sub>の流量を550 sccm、O<sub>2</sub>の流量を450 sccm、Heの流量を350 sccm、RFパワーを3000 W、圧力を25 Paとし、2回目のドライエッチングを行ってテーパー形状とする。

20

#### 【0118】

次に、第1の開口部を形成した後、第1の開口部に金属膜を積層し、フォトリソグラフィ工程の後、金属膜をエッチングしてソース電極及びドレイン電極637～643を形成する。本実施例では、ターゲットをチタンとし、窒素とアルゴンの流量を1：1としてスパッタリング法により100 nm厚の窒素元素を含むチタン膜を形成する。上記のような窒素元素を含むチタン膜を、シリコン(Si)と酸素(O)との結合で骨格構造が構成される層間絶縁膜上に形成すると、膜はがれしにくく、且つ半導体領域と低抵抗を有する配線を形成することができる。

30

#### 【0119】

このとき、チタン膜中の窒素元素の組成比は7 atomic%以上44 atomic%未満である。

#### 【0120】

つぎに、窒素元素を含むチタン膜上に、チタンーアルミニウム合金膜\チタン膜(Al-Si\Ti)をそれぞれ350\100 nmに積層したのち、所望の形状にパターニング及びエッチングして3層で形成されるソース電極ドレイン電極637～643を形成する。その後、第1の電極644を形成する。

#### 【0121】

なお、本実施例では、電極641を形成した後に第1の電極644を形成しているが、この構造に限られない。例えば、第1の電極となる導電膜を成膜し、第1の電極となるよう所望の形状にエッチングし、その後、コンタクトホールを開口し、次に配線となる導電膜を成膜した後、所望の形状にエッチングして配線を形成しても良い。この場合、配線と第1の層間絶縁膜との間に第1の電極が形成される。

40

#### 【0122】

さらには、第1の層間絶縁膜670上に配線を形成し、この上に別途層間絶縁膜を形成し、この層間絶縁膜の一部をエッチングしてコンタクトホールを形成した後、このコンタクトホールを介して配線と接続する第1の電極を形成してもよい。この場合、配線が形成される層と第1の電極との間には、層間絶縁膜が形成されている。

#### 【0123】

以上の様にして、nチャネル型TFT640、643及びpチャネル型641、642

50

を作製することができる。

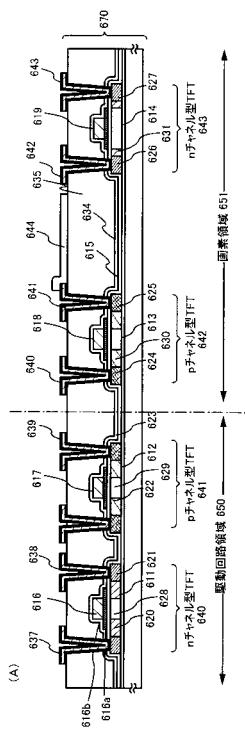

**【0124】**

また、nチャネル型TFT640とpチャネル型TFT641をCMOS回路として駆動回路650に用い、pチャネル型TFT642、nチャネル型643を画素領域651に用いることにより、駆動回路と画素領域を同一基板上に形成したアクティブマトリクス基板670を得ることができる。

**【0125】**

なお、本実施例では、ソース電極及びドレイン電極の作製工程として、第1実施形態の作製工程を用いたが、第2実施形態又は第3実施形態の作製工程を適応することができる。

10

**【0126】**

次に、アクティブマトリクス基板上に発光素子を形成して表示装置を作製する工程を示す。

**【0127】**

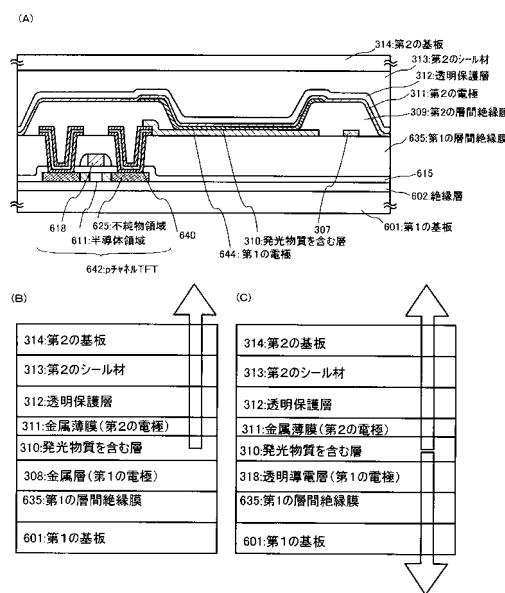

図6(A)は、図5のアクティブマトリクス基板において、画素領域651に形成されるpチャネル型TFT642とその配線625に接続される第1の電極6441の部分を拡大した図である。図6(A)において、図4および図5と同様の部分は、同じ符号を用いて詳細な説明を省略する。

**【0128】**

601は第1の基板、601、602は絶縁層、642はTFT、635は第2の層間絶縁膜、644が第1の電極、309は第3の層間絶縁膜、310は発光物質を含む層、311は第2の電極、312は透明保護層、313は第2のシール材、314は第2の基板である。

20

**【0129】**

第1の基板601上に設けられたTFT642(pチャネル型TFT)は、発光する発光物質を含む層310に流れる電流を制御する素子であり、625はドレイン領域(またはソース領域)である。また、640は第1の電極とドレイン領域(またはソース領域)とを接続するドレイン電極(またはソース電極)である。また、ドレイン電極640と同じ工程で電源供給線やソース配線などの配線307も同時に形成される。ここでは第1電極とドレイン電極とを別々に形成する例を示したが、同一としてもよい。第1の基板601上には下地絶縁膜(ここでは、下層を窒化絶縁膜、上層を酸化絶縁膜)となる絶縁層602がプラズマCVD法で形成されており、ゲート電極618と活性層との間には、ゲート絶縁膜615が設けられている。

30

**【0130】**

また、644は、第1の電極、即ち、発光素子の陽極(或いは陰極)である。第1の電極644の材料としては、Ti、TiN、TiSi<sub>x</sub>N<sub>y</sub>、Ni、W、WSi<sub>x</sub>、WN<sub>x</sub>、WSi<sub>x</sub>N<sub>y</sub>、NbN、Mo、Cr、Pt、Zn、Sn、In、またはMoから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料を主成分とする膜またはそれらの積層膜を総膜厚100nm~800nmの範囲で用いればよい。ここでは、第1の電極644として窒化チタン膜を用いる。窒化チタン膜を第1の電極644として用いる場合、表面に紫外線照射や塩素ガスを用いたプラズマ処理を行って仕事関数を増大させることが好ましい。

40

**【0131】**

また、第1の電極644の端部(および配線307)を覆う第2の層間絶縁膜309(バンク、隔壁、障壁、土手などと呼ばれる)を有している。絶縁物309としては、無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコンなど)、感光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、レジストまたはベンゾシクロブテン)、またはこれらの積層などを用いることができる。さらには、第1実施形態で示した、シロキサン系ポリマーを全面塗布し焼成したシリコン(Si)と酸素(O)との結合で骨格構造が構成される膜(高耐熱性平坦化膜)で形成することもできる。こ

50

こでは室化シリコン膜で覆われた感光性の有機樹脂を用いる。例えば、有機樹脂の材料としてポジ型の感光性アクリルを用いた場合、絶縁物の上端部のみに曲率半径を有する曲面を持たせることが好ましい。また、絶縁物として、感光性の光によってエッチャントに不溶解性となるネガ型、或いは光によってエッチャントに溶解性となるポジ型のいずれも使用することができます。

#### 【0132】

なお、第1の層間絶縁膜635と第2の層間絶縁膜309との組み合わせは、無機材料 - 無機材料、有機材料 - 無機材料、無機材料 - 有機材料、有機材料 - 有機材料等の組み合わせを適宜適応することができる。

#### 【0133】

発光物質を含む層310は、蒸着法または塗布法を用いて形成する。なお、信頼性を向上させるため、発光物質を含む層310の形成前に真空加熱を行って脱気を行うことが好ましい。例えば、蒸着法を用いる場合、真空中度が $5 \times 10^{-3}$  Torr (0.665 Pa) 以下、好ましくは $10^{-4} \sim 10^{-6}$  Paまで真空排気された成膜室で蒸着を行う。蒸着の際、予め、抵抗加熱により有機化合物は気化されており、蒸着時にシャッターが開くことにより基板の方向へ飛散する。気化された有機化合物は、上方に飛散し、メタルマスクに設けられた開口部を通じて基板に蒸着される。

#### 【0134】

発光物質を含む層310の材料としては、低分子系、高分子系、もしくはオリゴマーやデンドリマーに代表される、中分子系の公知の有機化合物を用いることができる。また、一重項励起により発光(蛍光)する発光材料(シングレット化合物)、または三重項励起により発光(リン光)する発光材料(トリプレット化合物)を用いることができる。代表例としては、例えば、Alq<sub>3</sub>、部分的に赤色発光色素であるナイルレッドをドープしたAlq<sub>3</sub>、Alq<sub>3</sub>、p-EtTAZ、TPD(芳香族ジアミン)を蒸着法により順次積層することで白色を得ることができる。

#### 【0135】

発光物質を含む層は、少なくなくとも発光層を有し、発光層と陽極との間に正孔注入層、又は正孔輸送層を設けても良い。また、発光層と陰極の間に、電子注入層、又は電子輸送層を設けてもよい。各層の代表的な材料を以下に示す。

#### 【0136】

正孔注入層を形成する正孔注入材料としては、有機化合物であればポルフィリン系の化合物が有効であり、フタロシアニン(以下、H<sub>2</sub>-Pcと示す)、銅フタロシアニン(以下、Cu-Pcと示す)等を用いることができる。導電性高分子化合物に化学ドーピングを施した材料もあり、ポリスチレンスルホン酸(以下、PSSと示す)をドープしたポリエチレンジオキシチオフェン(以下、PEDOTと示す)や、ポリアニリン、ポリビニルカルバゾール(以下、PVKと示す)などが挙げられる。また、五酸化バナジウムのような無機半導体の薄膜や、酸化アルミニウム、酸化モリブデンなどの無機絶縁体の超薄膜も有効である。

#### 【0137】

正孔輸送層を形成する正孔輸送材料としては、芳香族アミン系(すなわち、ベンゼン環 -窒素の結合を有するもの)の化合物が好適である。広く用いられている材料として、例えば、N,N'-ビス(3-メチルフェニル)-N,N'-ジフェニル-1,1'-ビフェニル-4,4'-ジアミン(略称:TPD)や、その誘導体である4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル(略称:-NPD)などがある。また、4,4',4''-トリス(N,N-ジフェニル-アミノ)-トリフェニルアミン(略称:TDATA)や、4,4',4''-トリス[N-(3-メチルフェニル)-N-フェニル-アミノ]-トリフェニルアミン(略称:MTDATA)などのスターバースト型芳香族アミン化合物が挙げられる。

#### 【0138】

発光層を形成する発光材料としては、具体的には、トリス(8-キノリノラト)アルミ

10

20

30

40

50

ニウム(以下、Al<sub>3</sub>と示す)、トリス(4-メチル-8-キノリノラト)アルミニウム(以下、Al<sub>1</sub>m<sub>3</sub>と示す)、ビス(10-ヒドロキシベンゾ[*h*]-キノリナト)ベリリウム(以下、BeB<sub>2</sub>と示す)、ビス(2-メチル-8-キノリノラト)- (4-ヒドロキシ-ビフェニリル)-アルミニウム(以下、Al<sub>1</sub><sub>1</sub>と示す)、ビス[2-(2-ヒドロキシフェニル)-ベンゾオキサゾラト]亜鉛(以下、Zn(BOX)<sub>2</sub>と示す)、ビス[2-(2-ヒドロキシフェニル)-ベンゾチアゾラト]亜鉛(以下、Zn(BTZ)<sub>2</sub>と示す)などの金属錯体の他、各種蛍光色素が有効である。また、三重項発光材料も可能であり、白金ないしはイリジウムを中心金属とする錯体が主体である。三重項発光材料としては、トリス(2-フェニルピリジン)イリジウム(以下、Ir(ppy)<sub>3</sub>と示す)、2,3,7,8,12,13,17,18-オクタエチル-21H,23H-ポルフィリン-白金(以下、PtOEPと示す)などが知られている。

10

#### 【0139】

電子輸送層を形成する電子輸送材料としては、トリス(8-キノリノラト)アルミニウム(略称: Al<sub>3</sub>)、トリス(4-メチル-8-キノリノラト)アルミニウム(略称: Al<sub>1</sub>m<sub>3</sub>)、ビス(10-ヒドロキシベンゾ[*h*]-キノリナト)ベリリウム(略称: BeB<sub>2</sub>)、ビス(2-メチル-8-キノリノラト)- (4-ヒドロキシ-ビフェニリル)-アルミニウム(略称: Al<sub>1</sub><sub>1</sub>)、ビス[2-(2-ヒドロキシフェニル)-ベンゾオキサゾラト]亜鉛(略称: Zn(BOX)<sub>2</sub>)、ビス[2-(2-ヒドロキシフェニル)-ベンゾチアゾラト]亜鉛(略称: Zn(BTZ)<sub>2</sub>)などの金属錯体が挙げられる。さらに、金属錯体以外にも、2-(4-ビフェニリル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール(略称: PBD)、1,3-ビス[5-(p-tert-ブチルフェニル)-1,3,4-オキサジアゾール-2-イル]ベンゼン(略称: OXD-7)などのオキサジアゾール誘導体、3-(4-tert-ブチルフェニル)-4-フェニル-5-(4-ビフェニリル)-1,2,4-トリアゾール(略称: TAZ)、3-(4-tert-ブチルフェニル)-4-(4-エチルフェニル)-5-(4-ビフェニリル)-1,2,4-トリアゾール(略称: p-EtTAZ)などのトリアゾール誘導体、2,2',2"- (1,3,5-ベンゼントリイル)トリス[1-フェニル-1H-ベンズイミダゾール](略称: TPBI)のようなイミダゾール誘導体、バソフェナントロリン(略称: BPhen)、バソキュプロイン(略称: BCP)などのフェナントロリン誘導体を用いることができる。

20

#### 【0140】

電子注入層に用いることができる電子注入材料としては、上述した電子輸送材料を用いることができる。その他に、LiF、CsFなどのアルカリ金属ハロゲン化物や、CaF<sub>2</sub>のようなアルカリ土類ハロゲン化物、Li<sub>2</sub>Oなどのアルカリ金属酸化物のような絶縁体の超薄膜がよく用いられる。また、リチウムアセチルアセトネート(略称: Li(acac)<sub>2</sub>)や8-キノリノラト-リチウム(略称: Liq)などのアルカリ金属錯体も有効である。

#### 【0141】

また、311は、導電膜からなる第2の電極、即ち、有機発光素子の陰極(或いは陽極)である。第2の電極311の材料としては、MgAg、MgIn、AlLi、CaF<sub>2</sub>、CaNなどの合金、または周期表の1族もしくは2族に属する元素とアルミニウムとを共蒸着法により形成した透光性を有する膜を用いる。また、遮光性を有する導電膜、代表例としては、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、およびこれらを含む合金(Mg:Ag、Al:Liなど)、YbやEr等の希土類金属元素、アルミニウムを用いて形成する。これらの導電膜は、発光素子の構造によって適宜採用すればよい。ここでは、第2の電極を通過させて発光させる上面出射型であるので、1nm~10nmのアルミニウム膜、もしくはLiを微量に含むアルミニウム膜を用いる。第2の電極311としてAl膜を用いる構成とすると、発光物質を含む層310と接する材料を酸化物以外の材料で形成することが可能となり、発光装置の信頼性を向上させることができる。また、1nm~10nmのアルミニウム膜を形成する前に陰極バッファ

30

10

20

30

40

50

層として  $\text{CaF}_2$ 、 $\text{MgF}_2$ 、または  $\text{BaF}_2$  からなる透光性を有する層（膜厚 1 nm ~ 5 nm）を形成してもよい。

#### 【0142】

また、陰極の低抵抗化を図るため、発光領域とならない領域の第2の電極 311 上に補助電極を設けてもよい。また、陰極形成の際には蒸着による抵抗加熱法を用い、蒸着マスクを用いて選択的に形成すればよい。

#### 【0143】

発光素子の構造は、種々の発光素子構造、例えば、陽極 / 正孔注入層 / 発光層 / 電子輸送層 / 陰極、陽極 / 正孔注入層 / 正孔輸送層 / 発光層 / 電子輸送層 / 電子注入層 / 陰極、陽極 / 正孔注入層 / 正孔輸送層 / 発光層 / 正孔プロッキング層 / 電子輸送層 / 陰極、陽極 / 正孔注入層 / 正孔輸送層 / 発光層 / 正孔プロッキング層 / 電子輸送層 / 電子注入層 / 陰極等を適宜採用することができる。なお、発光領域の配置、即ち第1の電極の配置としてはストライプ配列、デルタ配列、モザイク配列などを挙げることができる。10

#### 【0144】

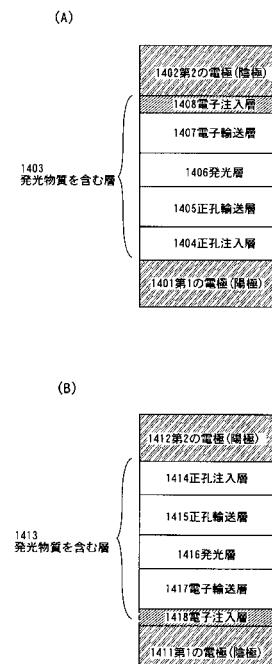

また、本実施例ではアクティブマトリクス基板において、画素領域 651 に形成される p チャネル型 TFT 642 とその配線 625 に接続される第1の電極が陽極である構造の発光素子を示している。図 14 (A) にその断面構造を示す。

#### 【0145】

図 14 (A) においては、発光物質を含む層 1403 は、第1の電極（陽極）1401 上に、正孔注入層 1404、正孔輸送層 1405、発光層 1406、電子輸送層 1407、電子注入層 1408 が積層されており、電子注入層 1408 に接して第2の電極（陰極）1402 が設けられている。第1の陽極は、アクティブマトリクス基板上に形成された p チャネル型 TFT の配線に接続している。20

#### 【0146】

一方、順積み型発光素子の代わりに、第1の電極が n チャネル型 TFT の配線に接続される発光素子を用いることもできる。

#### 【0147】

図 14 (B) においては、発光物質を含む層 1413 は、第1の電極（陰極）1411 上に、電子注入層 1418、電子輸送層 1417、発光層 1416、正孔輸送層 1415、正孔注入層 1414 が積層されており、正孔注入層 1414 に接して第2の電極（陽極）1412 が設けられている。第1の電極（陰極）は、アクティブマトリクス基板上に形成された n チャネル型 TFT の配線と接続している。この構造の発光素子を形成する場合、画素部における TFT は、すべて n 型となるため、ドーピングの工程数を削減することができる。また、マスク数も削減することができるので、歩留まりを向上させることができる。さらには、TFT の半導体領域を非晶質半導体膜で形成することもできる。非晶質半導体膜で形成された TFT を用いることによって、TFT のばらつきを抑えることができる。30

#### 【0148】

また、312 は蒸着法により形成する透明保護層であり、金属薄膜からなる第2の電極 311 を保護する。さらに透明保護層 312 を第2のシール材 313 で覆う。第2の電極 311 は極薄い金属膜であるため、酸素に触れれば容易に酸化などが発生しやすく、シール材に含まれる溶剤などと反応して変質する恐れがある。このような金属薄膜からなる第2の電極 311 を透明保護層 312、例えば  $\text{CaF}_2$ 、 $\text{MgF}_2$ 、または  $\text{BaF}_2$  で覆うことによって、第2の電極 311 と第2のシール材 313 に含まれる溶剤などの成分とが反応することを防ぐとともに、乾燥剤を使うことなく、酸素や水分を効果的にプロックする。また、 $\text{CaF}_2$ 、 $\text{MgF}_2$ 、 $\text{BaF}_2$  は、蒸着法で形成することが可能であり、連続的に陰極と透明な保護層とを蒸着法で形成することによって、不純物の混入や電極表面が大気に触れることを防ぐことができる。加えて、蒸着法を用いれば、発光物質を含む層へダメージをほとんど与えない条件で透明保護層 312 を形成することができる。また、第2の電極 311 の上下に  $\text{CaF}_2$ 、 $\text{MgF}_2$ 、または  $\text{BaF}_2$  からなる透光性を有する層を設けて挟むことによって4050

、さらに第2の電極311を保護してもよい。

#### 【0149】

また、第1の電極として材料自身に酸素原子のない金属（仕事関数の大きい材料）、例えば窒化チタン膜を用い、第2の電極として材料自身に酸素原子のない金属（仕事関数の小さい材料）、例えばアルミニウム薄膜を用い、さらにCaF<sub>2</sub>、MgF<sub>2</sub>、BaF<sub>2</sub>で覆うことによって、第1の電極と第2の電極との間の領域を限りなくゼロに近い無酸素状態を維持できる。

#### 【0150】

また、第2のシール材313は、第2の基板314と第1の基板300とを貼り合せて10いる。第2のシール材313としては、透光性を有している材料であれば特に限定されず、代表的には紫外線硬化または熱硬化のエポキシ樹脂を用いればよい。ここでは屈折率1.50、粘度500cps、ショアD硬度90、テンシル強度3000psi、Tg点150、体積抵抗 $1 \times 10^{15} \text{ cm}$ 、耐電圧450V/milである高耐熱のUVエポキシ樹脂（エレクトロライト社製：2500Clear）を用いる。また、第2のシール材313を一对の基板間に充填することによって、全体の透過率を向上させることができる。

#### 【0151】

また、図6(B)には、発光領域における積層構造を簡略化したものを示す。図6(B)に示す矢印の方向（発光物質を含む層310から第2の電極311方向；上方）に発光が放出される。20

#### 【0152】

下方に発光し、かつpチャネル型TFTが第1の電極に接続される発光素子としては、第1の電極（陽極）材料として、透明性を有し、且つ、仕事関数の大きい導電膜（ITO（酸化インジウム酸化スズ合金）、酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub> ZnO）、酸化亜鉛（ZnO）、酸化珪素を含む酸化インジウムスズ等）を用いる。一方、第2の電極（陰極）には、遮光性を有する導電膜、代表例としては、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、およびこれらを含む合金（Mg：Ag、Al：Liなど）、YbやEr等の希土類金属元素、アルミニウムを用いて形成する。

#### 【0153】

下方に発光し、かつnチャネル型TFTが第1の電極に接続される発光素子としては、第1の電極（陰極）に、MgAg、MgIn、AlLi、CaF<sub>2</sub>、CaNなどの合金、または周期表の1族もしくは2族に属する元素とアルミニウムとを共蒸着法により形成した透光性を有する膜を用いる。一方、第2の電極（陽極）には、TiN、ZrN、Ti、W、Ni、Pt、Cr、Al等の単層膜の他、窒化チタンとアルミニウムを主成分とする膜との積層、窒化チタン膜とアルミニウムを主成分とする膜と窒化チタン膜との三層構造等を用いることができる。30

#### 【0154】

また、金属層からなる第1の電極308に代えて、図6(C)に示すように透明導電膜からなる第1の電極318を用いた場合、上面と下面の両方に発光を放出することができる。透明導電膜としては、ITO（酸化インジウム酸化スズ合金）、酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub> ZnO）、酸化亜鉛（ZnO）、酸化ケイ素を含む酸化インジウムスズ等を用いればよい。40

#### 【0155】

また、下方（発光物質を含む層310から第1の電極310方向）のみに発光を放する発光装置としてもよい。

#### 【0156】

上方に発光し、かつpチャネル型TFTが第1の電極に接続される発光素子は、第1の電極（陽極）材料として、アルミニウム-シリコン合金、窒化タンタル、タンタル、チタン、タングステン、窒素を含むチタン等で形成される反射性を有する導電膜上に、仕事関数の大きい導電膜（ITO（酸化インジウム酸化スズ合金）、酸化インジウム酸化亜鉛合50

金 ( $In_2O_3$   $ZnO$ )、酸化亜鉛 ( $ZnO$ )、酸化珪素を含む酸化インジウムスズ等) を用いる。一方、第2の電極(陰極)には、1 nm ~ 10 nmのアルミニウム膜、もしくはLiを微量に含むアルミニウム膜を用いる。この場合、膜厚が薄いため、上方に光が出射される。

#### 【0157】

上方に発光し、かつnチャネル型TFTが第1の電極に接続される発光素子は、第1の電極(陰極)に、アルミニウム・シリコン合金、窒化タンタル、タンタル、チタン、タングステン、窒素を含むチタン等で形成される反射性を有する導電膜を用いる。一方、第2の電極(陽極)には、透明性を有し、且つ、仕事関数の大きい導電膜(I TO(酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金( $In_2O_3$   $ZnO$ )、酸化亜鉛( $ZnO$ )、酸化珪素を含む酸化インジウムスズ等)を用いる。10

#### 【0158】

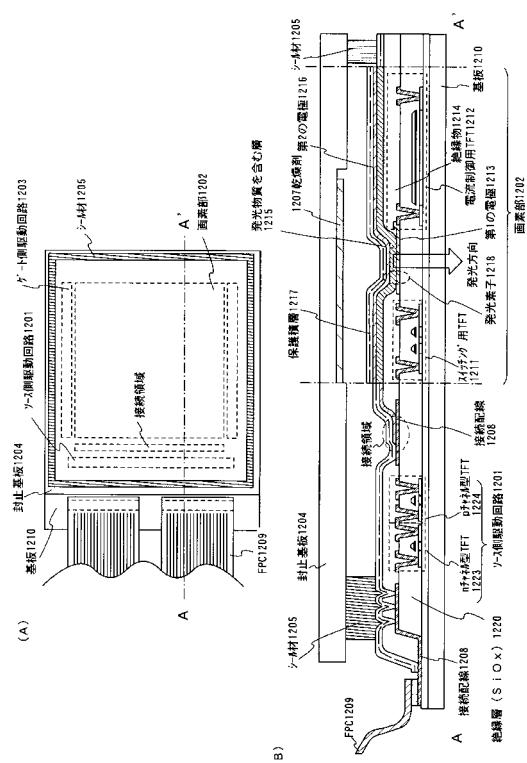

次に、下面出射構造の発光装置の一例を図7に示す。

#### 【0159】

図7(A)は、発光装置を示す上面図、図7(B)は図7(A)をA-A'で切断した断面図である。点線で示された1201はソース信号線駆動回路、1202は画素部、1203はゲート信号線駆動回路である。また、1204は封止基板、1205は密閉空間の間隔を保持するためのギャップ材が含有されているシール材であり、シール材1205で囲まれた内側は、不活性気体(代表的には窒素)で充填されている。シール材1205で囲まれた内側の空間は乾燥剤1207によって微量な水分が除去され、十分乾燥している。20

#### 【0160】

なお、1208はソース信号線駆動回路1201及びゲート信号線駆動回路1203に入力される信号を伝送するための配線であり、外部入力端子となるFPC(フレキシブルプリントサーキット)1209からビデオ信号やクロック信号を受け取る。

#### 【0161】

次に、断面構造について図7(B)を用いて説明する。基板1210上には駆動回路及び画素部が形成されているが、ここでは、駆動回路としてソース信号線駆動回路1201と画素部1202が示されている。なお、ソース信号線駆動回路1201はnチャネル型TFT1223とpチャネル型TFT1224とを組み合わせたCMOS回路が形成される。30

#### 【0162】

また、画素部1202はスイッチング用TFT1211と、駆動用TFT1212とそのドレインに電気的に接続された透明な導電膜からなる第1の電極(陽極)1213を含む複数の画素により形成される。

#### 【0163】

また、これらのTFT1211、1212、1223、1224の層間絶縁膜1220としては、シリコン系ポリマーを用いて塗布法で形成された絶縁膜(シリコン(Si)と酸素(O)との結合で骨格構造が構成される膜)である。

#### 【0164】

ここでは第1の電極1213が接続電極と一部重なるように形成され、第1の電極1213はTFTのドレイン領域と接続電極を介して電気的に接続している構成となっている。第1の電極1213は透明性を有し、且つ、仕事関数の大きい導電膜(I TO(酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金( $In_2O_3$   $ZnO$ )、酸化亜鉛( $ZnO$ )、酸化珪素を含む酸化インジウムスズ等)を用いることが望ましい。40

#### 【0165】

酸化珪素を含む酸化インジウムスズは、ベークを行ってもITOのように結晶化せず、アモルファス状態のままである。従って、酸化珪素を含む酸化インジウムスズは、ITOよりも平坦性が高く、発光物質を含む層が薄くとも陰極とのショートが生じにくく、発光素子の陽極として適している。また、屈折率が約1.46前後である酸化珪素を含ませる50

ことによって陽極となる酸化珪素を含む酸化インジウムスズの屈折率を変化させている。

**【0166】**

また、第1の電極（陽極）1213の両端には絶縁物（バンク、隔壁、障壁、土手などと呼ばれる）1214が形成される。カバレッジを良好なものとするため、絶縁物1214の上端部または下端部に曲率を有する曲面が形成されるようとする。また、絶縁物1214を窒化アルミニウム膜、窒化酸化アルミニウム膜、炭素を主成分とする薄膜、または窒化珪素膜からなる保護膜で覆ってもよい。

**【0167】**

また、第1の電極（陽極）1213上には、有機化合物材料の蒸着を行い、発光物質を含む層1215を選択的に形成する。

10

**【0168】**

また、有機化合物材料の蒸着を行う前に、基板に含まれるガスを除去するために減圧雰囲気や不活性雰囲気で200～300の加熱処理を行うことが望ましい。

**【0169】**

本実施例では、発光物質を含む層1215の成膜を蒸着装置で行い、均一な膜厚を得る。さらに、発光物質を含む層1215上には第2の電極（陰極）1216が形成される。陰極としては、仕事関数の小さい材料（Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、またはCaN）を用いればよい。こうして、第1の電極（陽極）1213、発光物質を含む層1215、及び第2の電極（陰極）1216からなる発光素子1218が形成される。発光素子1218は、図4中に示した矢印方向に発光する。ここでは発光素子1218はR、G、或いはBの単色発光が得られる発光素子の一つであり、R、G、Bの発光が得られる発光物質を含む層をそれぞれ選択的に形成した3つの発光素子でフルカラーとする。

20

**【0170】**

また、発光物質を含む層を白色発光とし、カラーフィルターを別途設けることでフルカラー表示しても良い。あるいは、発光物質を含む層を青色発光とし、色変換層などを別途設けることによってフルカラー表示してもよい。

**【0171】**

また、発光素子1218を封止するために保護積層1217を形成する。保護積層は、第1の無機絶縁膜と、応力緩和膜である第2の無機絶縁膜との積層からなっている。

30

**【0172】**

また、発光素子1218を封止するために不活性気体雰囲気下でシール材1205により封止基板1204を貼り合わせる。封止基板1204には予めサンドブラスト法などによって形成した凹部が形成されており、その凹部に乾燥剤1207を貼り付けている。なお、シール材1205としてはエポキシ系樹脂を用いるのが好ましい。また、シール材1205はできるだけ水分や酸素を透過しない材料であることが望ましい。

**【0173】**

また、本実施例では凹部を有する封止基板1204を構成する材料として金属基板、ガラス基板や石英基板の他、FRP（Fiberglass-Reinforced Plastics）、PVF（ポリビニルフロライド）、マイラー、ポリエステルまたはアクリル等からなるプラスチック基板を用いることができる。また、内側に乾燥剤を貼りつけた金属缶で封止することも可能である。

40

**【0174】**

また、発光素子の信頼性を向上させるために、蒸着を行う前に減圧雰囲気または不活性雰囲気で200、好ましくは300以上の加熱処理を行うことが望ましく、層間絶縁膜および隔壁にシリコン系ポリマーを用いた平坦絶縁膜（シリコン（Si）と酸素（O）との結合で骨格構造が構成される平坦絶縁膜）とした場合には、約450まで加熱することができる。本実施例では230、1時間の熱処理により基板の脱ガスおよび脱水処理を行い、信頼性を向上させている。

**【0175】**

50

また、本発明の発光装置において、画面表示の駆動方法は特に限定されず、例えば、点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、発光装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

#### 【0176】

さらに、ビデオ信号がデジタルの発光装置において、画素に入力されるビデオ信号が定電圧（C V）のものと、定電流（C C）のものとがある。ビデオ信号が定電圧のもの（C V）には、発光素子に印加される電圧が一定のもの（C V C V）と、発光素子に印加される電流が一定のもの（C V C C）とがある。また、ビデオ信号が定電流のもの（C C）には、発光素子に印加される電圧が一定のもの（C C C V）と、発光素子に印加される電流が一定のもの（C C C C）とがある。

#### 【実施例4】

#### 【0177】

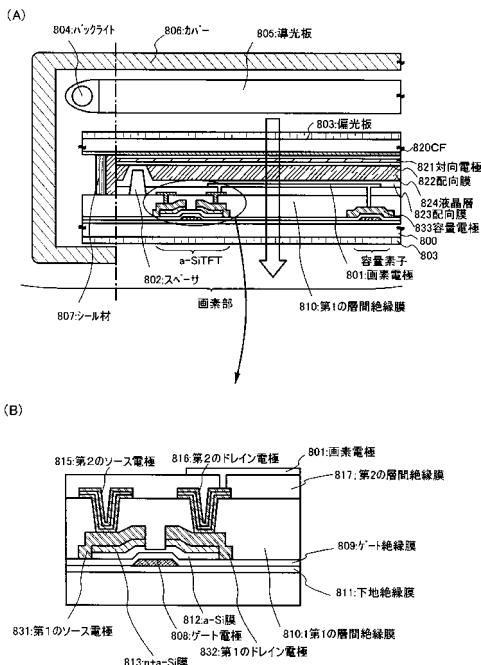

本実施例では、アモルファスシリコンを活性層とする逆スタガ型 TFT をスイッチング素子としたアクティブマトリクス型の液晶表示装置の例を、図 8 に示す。

#### 【0178】

なお、図 8 (A) は液晶表示装置のモジュールの断面図であり、図 8 (B) は、液晶表示装置の画素部に設けられる画素 TFT の拡大図である。以下、図 8 (A) 及び図 8 (B) を参照しながら説明する。

#### 【0179】

最初に、透光性有する基板 800 を用いてアクティブマトリクス基板を作製する。基板サイズとしては、 $600\text{mm} \times 720\text{mm}$ 、 $680\text{mm} \times 880\text{mm}$ 、 $1000\text{mm} \times 1200\text{mm}$ 、 $1100\text{mm} \times 1250\text{mm}$ 、 $1150\text{mm} \times 1300\text{mm}$ 、 $1500\text{mm} \times 1800\text{mm}$ 、 $1800\text{mm} \times 2000\text{mm}$ 、 $2000\text{mm} \times 2100\text{mm}$ 、 $2200\text{mm} \times 2600\text{mm}$ 、または $2600\text{mm} \times 3100\text{mm}$ のような大面積基板を用い、製造コストを削減することが好ましい。用いることのできる基板として、コーニング社の #7059 ガラスや #1737 ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板を用いることができる。更に他の基板として、石英基板、プラスチック基板などの透光性基板を用いることもできる。

#### 【0180】

まず、スパッタ法を用いて絶縁表面を有する基板 800 上に導電層を基板全面に形成した後、第 1 のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッティングにより不要な部分を除去して配線及び電極（ゲート電極 808、容量配線、及び端子など）を形成する。なお、必要があれば、基板 800 上に下地絶縁膜 811 を形成する。

#### 【0181】

上記の配線及び電極の材料としては、Ti、Ta、W、Mo、Cr、Nd から選ばれた元素、前記元素を成分とする合金、または前記元素を成分とする窒化物で形成する。さらに、Ti、Ta、W、Mo、Cr、Nd から選ばれた元素、前記元素を成分とする合金、または前記元素を成分とする窒化物から複数選択し、それを積層することもできる。

#### 【0182】

また、画面サイズが大画面化するとそれぞれの配線の長さが増加して、配線抵抗が高くなる問題が発生し、消費電力の増大を引き起こす。よって、配線抵抗を下げ、低消費電力を実現するために、上記の配線及び電極の材料としては、Cu、Al、Ag、Au、Cr、Fe、Ni、Pt またはこれらの合金を用いることもできる。また、Ag、Au、Cu、または Pt などの金属からなる超微粒子（粒径 5 ~ 10 nm）を凝集させずに高濃度で分散した独立分散超微粒子分散液を用い、インクジェット法で上記の配線及び電極を形成してもよい。

#### 【0183】

次に、PCVD 法によりゲート絶縁膜 809 を全面に成膜する。ゲート絶縁膜は窒化シ

10

20

30

40

50

リコン膜と酸化シリコン膜の積層を用い、膜厚を 50 ~ 200 nm とし、好ましくは 150 nm の厚さで形成する。尚、ゲート絶縁膜は積層に限定されるものではなく酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、酸化タンタル膜などの絶縁膜を用いることもできる。

#### 【 0184 】

次に、ゲート絶縁膜上に、50 ~ 200 nm 好ましくは 100 ~ 150 nm の膜厚で第 1 の非晶質半導体膜を、プラズマ CVD 法やスパッタ法などの公知の方法で全面に成膜する。代表的には非晶質シリコン (a-Si) 膜を 100 nm の膜厚で成膜する。なお、大面积基板に成膜する際、チャンバーも大型化するためチャンバー内を真空にすると処理時間がかかり、成膜ガスも大量に必要となるため、大気圧で線状のプラズマ CVD 装置を用いて非晶質シリコン (a-Si) 膜の成膜を行ってさらなる低コスト化を図ってもよい。10

#### 【 0185 】

次に、一導電型 (n 型または p 型) の不純物元素を含有する第 2 の非晶質半導体膜を 20 ~ 80 nm の厚さで成膜する。一導電型 (n 型または p 型) を付与する不純物元素を含む第 2 の非晶質半導体膜は、プラズマ CVD 法やスパッタ法などの公知の方法で全面に成膜する。本実施例ではリンが添加されたシリコンターゲットを用いて n 型の不純物元素を含有する第 2 の非晶質半導体膜を成膜する。

#### 【 0186 】

次に、第 2 のフォトリソグラフィー工程によりレジストマスクを形成し、エッチングにより不要な部分を除去して島状の第 1 の非晶質半導体膜 (a-Si 膜) 812、および島状の第 2 の非晶質半導体膜 (n<sup>+</sup>-Si 膜) 813 を形成する。この際のエッチング方法としてウエットエッチングまたはドライエッチングを用いる。20

#### 【 0187 】

次に、島状の第 1 の非晶質半導体膜及び第 2 の非晶質半導体膜を覆う導電層をスパッタ法で形成した後、第 3 のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して配線及び電極 (ソース配線、ドレイン電極、保持容量電極など) を形成する。上記の配線及び電極の材料としては、Al、Ti、Ta、W、Mo、Cr、Nd、Cu、Ag、Au、Cr、Fe、Ni、Pt から選ばれた元素、または前記元素を成分とする合金で形成する。また、Ag、Au、Cu、またはPd などの金属からなる超微粒子 (粒径 5 ~ 10 nm) を凝集させずに高濃度で分散した独立分散超微粒子分散液を用い、インクジェット法で上記の配線及び電極を形成してもよい。インクジェット法で上記の配線及び電極を形成すれば、フォトリソグラフィー工程が不要となり、さらなる低コスト化が実現できる。30

#### 【 0188 】

次に、第 4 のフォトリソグラフィー工程によりレジストマスクを形成し、エッチングにより不要な部分を除去してソース配線 831、ドレイン電極 832、容量電極 833 を形成する。この際のエッチング方法としてウエットエッチングまたはドライエッチングを用いる。この段階でゲート絶縁膜と同一材料からなる絶縁膜を誘電体とする容量素子が形成される。そして、第 1 のソース配線、第 1 のドレイン電極をマスクとして自己整合的に第 2 の非晶質半導体膜の一部を除去し、さらに第 1 の非晶質半導体膜の一部を薄膜化することでチャネルエッチ型の TFT を形成することができる。薄膜化された領域は TFT のチャネル形成領域となる。40

#### 【 0189 】

なお、本実施例では TFT 構造は特に限定されず、チャネルストッパー型の TFT、トップゲート型の TFT、或いは順スタガ型の TFT としてもよい。

#### 【 0190 】

次に、基板上にシロキサン系ポリマーを塗布し焼成して、1 μm 厚の第 1 の層間絶縁膜 (シリコン (Si) と酸素 (O) との結合で骨格構造が構成される膜) 810 を形成する。

#### 【 0191 】

10

20

30

40

50

次に、第5のフォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングにより第1の層間絶縁膜の一部をエッチング非晶質半導体膜の一部を露出して、コンタクトホールを形成する。この後、第1実施形態のように、金属膜を積層し、フォトリソグラフィ工程の後、金属膜をエッチングして窒素元素を含むチタン膜＼チタンーアルミニウム合金膜＼チタン膜で形成される第2のソース電極815、第2のドレイン電極816を形成する。この際のエッチング方法としてウェットエッチングまたはドライエッチングを用いる。

#### 【0192】

次に、第1の層間絶縁膜と同様の材料で第2の層間絶縁膜を形成し、第6のフォトリソグラフィー工程を行い、レジストマスクを形成して、その後ドライエッチング工程により、第2のドレイン電極や容量電極633に達するコンタクトホールを形成する。また、同時にゲート配線と端子部を電気的に接続するためのコンタクトホール(図示しない)を端子部分に形成し、ゲート配線と端子部を電気的に接続する金属配線(図示しない)を形成してもよい。また、同時に第2のソース電極に達するコンタクトホール(図示しない)を形成し、第2のソース電極から引き出すための金属配線を形成してもよい。これらの金属配線を形成した後にITO等の画素電極を形成してもよいし、ITO等の画素電極を形成した後にこれらの金属配線を形成してもよい。

#### 【0193】

次に、ITO(酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金(I<sub>n</sub><sub>2</sub>O<sub>3</sub>＼ZnO)、酸化亜鉛(ZnO)等の透明電極膜を110nmの厚さで成膜する。その後、第7のフォトリソグラフィー工程とエッチング工程を行うことにより、画素電極801を形成する。

#### 【0194】

以上、画素部においては、6回のフォトリソグラフィー工程により、ソース配線と、逆スタガ型の画素部のTFT及び容量素子と、端子部で構成されたアクティブマトリクス基板を作製することができる。塗布法により形成して第1及び第2の層間絶縁膜の平坦性を高めたことにより、ゲート電極や半導体層に起因する凹凸部をなくし、液晶の配向不良を防止することができる。

#### 【0195】

次いで、アクティブマトリクス基板上に配向膜823を形成しラビング処理を行う。なお、本実施例では配向膜823を形成する前に、アクリル樹脂膜等の有機樹脂膜をパテニングすることによって基板間隔を保持するための柱状のスペーサ802を所望の位置に形成した。また、柱状のスペーサに代えて、球状のスペーサを基板全面に散布してもよい。

#### 【0196】

次いで、対向基板を用意する。この対向基板には、着色層、遮光層が各画素に対応して配置されたカラーフィルタ820が設けられている。また、このカラーフィルタと遮光層とを覆う平坦化膜を設けている。次いで、平坦化膜上に透明導電膜からなる対向電極821を画素部と重なる位置に形成し、対向基板の全面に配向膜822を形成し、ラビング処理を施す。

#### 【0197】

そして、実施の形態1に従って、アクティブマトリクス基板の画素部を囲むようにシール材を描画した後、減圧下でシール材に囲まれた領域にインクジェット法で液晶を吐出する。次いで、大気にふれることなく、減圧下でアクティブマトリクス基板と対向基板とをシール材807で貼り合わせる。シール材807にはフィラー(図示しない)が混入されていて、このフィラーと柱状スペーサ802によって均一な間隔を持って2枚の基板が貼り合わせられる。インクジェット法で液晶を吐出する方法を用いることによって作製プロセスで使用する液晶の量を削減することができ、特に、大面積基板を用いる場合に大幅なコスト低減を実現することができる。

#### 【0198】

10

20

30

40

50

このようにしてアクティブマトリクス型液晶表示装置が完成する。そして、必要があれば、アクティブマトリクス基板または対向基板を所望の形状に分断する。さらに、公知の技術を用いて偏光板 803 等の光学フィルムを適宜設ける。そして、公知の技術を用いて FPC を貼りつける。

#### 【0199】

以上の工程によって得られた液晶モジュールに、バックライト 804、導光板 805 を設け、カバー 806 で覆えば、図 8 にその断面図の一部を示したようなアクティブマトリクス型液晶表示装置（透過型）が完成する。なお、カバーと液晶モジュールは接着剤や有機樹脂を用いて固定する。また、透過型であるので偏光板 803 は、アクティブマトリクス基板と対向基板の両方に貼り付ける。

10

#### 【0200】

また、本実施例は透過型の例を示したが、特に限定されず、反射型や半透過型の液晶表示装置も作製することができる。反射型の液晶表示装置を得る場合は、画素電極として光反射率の高い金属膜、代表的にはアルミニウムまたは銀を主成分とする材料膜、またはそれらの積層膜等を用いればよい。

#### 【0201】

また、本実施例は、第 2 実施形態又は第 3 実施形態と自由に組み合わせることができる。

#### 【実施例 5】

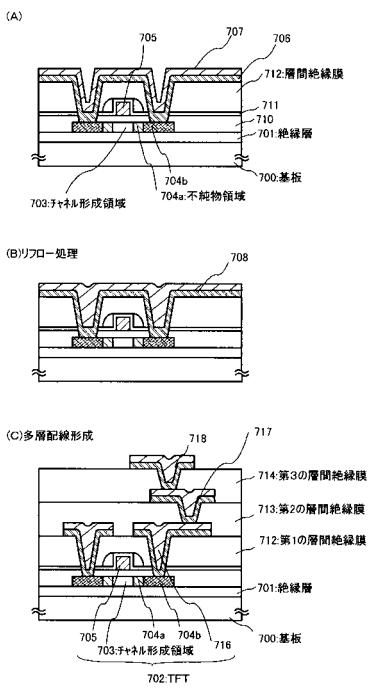

#### 【0202】

本実施例では、ゲート絶縁膜をシロキサン系ポリマーを用いて形成したシリコン（Si）と酸素（O）との結合で骨格構造が構成される膜で層間絶縁膜を形成し、多層配線を設けた例を図 9 に示す。

20

#### 【0203】

まず、基板 700 上に下地絶縁膜 701 となる無機絶縁膜を P C V D 法などによって形成する。次いで結晶構造を有する半導体膜を形成し、パターニングを行う。

#### 【0204】

次いで、シロキサン系ポリマーを用いたシリコン（Si）と酸素（O）との結合で骨格構造が構成される膜で平坦なゲート絶縁膜 710 を形成する。

#### 【0205】

次いで、ゲート電極 705 を形成し、ゲート電極をマスクとして半導体膜に n 型または p 型を付与する不純物元素のドーピングを行って低濃度不純物領域 704a を形成する。次いで、後にエッティングストッパー膜となる窒化珪素膜 711 を P C V D 法で形成する。次いで、水素化処理または活性化処理を行う。次いで、シロキサン系ポリマーを用いてシリコン（Si）と酸素（O）との結合で骨格構造が構成される膜の成膜を行った後、エッチバックを行ってサイドウォールを形成する。

30

#### 【0206】

次いで、ゲート電極およびサイドウォールをマスクとしてドーピングを行い、高濃度不純物領域 704b を形成する。次いで、層間絶縁膜 712 となるシロキサン系ポリマーを用いたシリコン（Si）と酸素（O）との結合で骨格構造が構成される膜を約 1 μm の膜厚で形成する。

40

#### 【0207】

次いでコンタクトホールを形成する。次に、窒素元素を含む導電膜 706 を成膜する。ここでは、窒素元素を含むチタン膜を成膜する。次いで、リフローが可能な金属材料膜 707 を成膜する。ここではアルミニウムを主成分とする AlGe 膜を形成する。（図 9 (A)）

#### 【0208】

次いで、350 ~ 400 の熱処理を行って金属材料膜をリフローさせて凹凸を緩和する。ここで、凹凸が緩和された金属膜 708 が形成される。（図 9 (B)）

#### 【0209】

ゲート絶縁膜 710 及び層間絶縁膜 712 は、シロキサン系ポリマーを用いたシリコン

50

(S i) と酸素 (O) との結合で骨格構造が構成される膜からなるため耐熱温度が高く、このリフロー処理の温度に十分耐えることができる。

#### 【0210】

次いで、金属材料膜をパターニングして配線および電極 716 を形成する。この段階で TFT が完成する。その後、層間絶縁膜の形成と、コンタクトホールの形成と、金属材料膜の形成と、リフロー処理とパターニング処理とを同様に繰り返して、第 2 配線 717、第 3 配線 718 を形成する。(図 9 (C))。

#### 【0211】

このように多層配線を可能とすることで、さらなる素子の高集積化が可能である。なお、本実施例では、配線の作製工程として、第 1 実施形態の作製工程を用いたが、第 2 実施形態又は第 3 実施形態の作製工程を適応することができる。10

#### 【実施例 6】

#### 【0212】

本実施例では、本発明を用いて、半導体基板を用いて半導体素子を作製する工程を、図 10 を用いて説明する。なお、前記半導体基板は、単結晶シリコン基板または化合物半導体基板であり、代表的には、N 型または P 型の単結晶シリコン基板、GaAs 基板、InP 基板、GaN 基板、SiC 基板、サファイア基板、又は ZnSe 基板である。

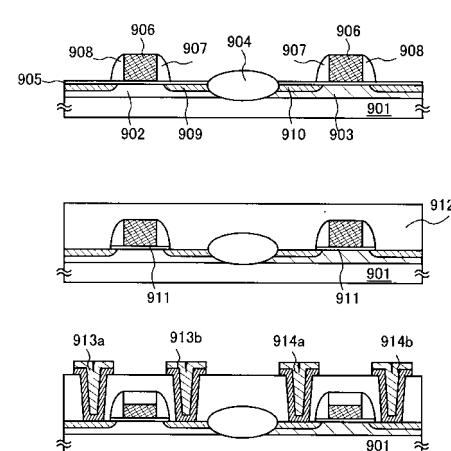

#### 【0213】

図 10 (A) に示すように、例えば単結晶シリコンからなる p 型の半導体基板 901 を用意し、その半導体基板に p 型のウエル 902 と n 型のウエル 903 を形成した後、半導体基板 901 の表面の選択的な領域を熱酸化して LOCOS (Local Oxidation of Silicon) 構造の酸化シリコン膜からなる阻止分離用のフィールド絶縁膜 904 を形成する。20

#### 【0214】

次に、半導体基板 901 の表面を熱酸化して 50 nm 程度以下の薄膜の酸化シリコン膜 (ゲート絶縁膜) 905 を形成し、この酸化シリコン膜 905 の上に、CVD 法を用いて 300 nm 程度の膜厚の多結晶シリコン膜を堆積する。

#### 【0215】

次に、半導体基板 901 の上に、レジストを塗布した後、フォトマスクを用いて露光及び現像を行ってゲート電極形状のレジストマスクを形成する。

#### 【0216】

次に、レジストマスクを用いて、ドライエッティングにより多結晶シリコン膜をエッティングしてゲート電極 306 を形成する。なお、多結晶シリコン膜は、ゲート絶縁膜の酸化シリコン膜よりもエッティングレートが高いため、選択的に多結晶シリコン膜のみをエッティングすることができる。

#### 【0217】

次に、半導体基板 901 上に CVD 法により酸化シリコン膜を堆積した後、この酸化シリコン膜を RIE 法、ECR 法によりエッティングして酸化シリコン膜で形成されるサイドウォール 907、908 を形成する。

#### 【0218】

次に、半導体基板 901 の上の p 型ウエル 902 に、例えばリンなどの n 型の不純物元素をイオン注入してソース及びドレインとなる n 型半導体領域 909 を形成する。また、半導体基板 1 の n 型ウエル 3 に、例えばホウ素などの p 型の不純物をイオン注入して、ソース及びドレインとなる p 型の半導体領域 910 を形成する。40

#### 【0219】

次に、図 9 (B) に示すように、ソース及びドレインとなる n 型の半導体領域 909 及び p 型の半導体領域 910 の上に形成されている酸化シリコン膜 905 を除去し、ゲート絶縁膜 911 を形成する。

#### 【0220】

次に、半導体基板 901 上にシリコサン系ポリマーを塗布し、焼成してシリコン (Si) と酸素 (O) との結合で骨格構造が構成される層間絶縁層 912 を形成する。50

**【0221】**

次に、図10(C)に示すように、レジストを塗布した後、フォトマスクを用いて露光及び現像を行ってコンタクトホール形状のレジストマスクを形成し、これをマスクとして層間絶縁膜をエッチングする。

**【0222】**

次に、第1実施形態で示される配線形成工程により、金属膜をエッチングして窒素元素を含むチタン膜＼チタン－アルミニウム合金膜＼チタン膜で形成される各素子のソース電極及びドレイン電極913a、913b、914a、914bを形成する。なお、本実施例では、ソース電極及びドレイン電極の作製工程として、第1実施形態の作製工程を用いたが、第2実施形態2又は第3実施形態の作製工程を適応することができる。

10

**【0223】**

以上の工程により、MOSFETを作製することができる。本実施の形態により作製されるMOSFETは、層間絶縁膜にシリコーン系ポリマーを用いたシリコン(Si)と酸素(O)との結合で骨格構造が構成される膜を用いたため耐熱温度が高く、高温処理をすることが可能となる。また、層間絶縁膜と、窒素元素を含む導電膜とが接しているためこれらの密着性が高く、膜はがれが生じにくい。このため、歩留まり高く半導体装置を作製することができる。

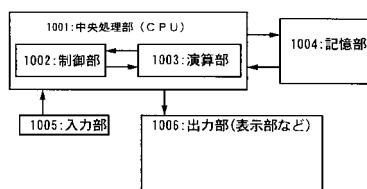

**【実施例7】****【0224】**

ここでは、絶縁表面を有する基板(代表的にはガラス基板、プラスチック基板)上に上記最良の形態や実施例4で得られるTFTおよび回路を用い、CPUやメモリーを形成する例を図11を用いて説明する。

20

**【0225】**

1001は中央処理部(CPUとも呼ばれる)、1002は制御部、1003は演算部、1004は記憶部(メモリーとも呼ばれる)、1005は入力部、1006は出力部(表示部など)である。

**【0226】**

演算部1003と制御部1002とを合わせたものが、中央処理部1001であり、演算部1003は、加算、減算の算術演算やAND、OR、NOTなどの論理演算を行う算術論理演算部(arithmetic logic unit, ALU)、演算のデータや結果を一時格納する種々のレジスタ、入力される1の個数を数え上げるカウンタなどから成り立っている。演算部1003を構成する回路、例えば、AND回路、OR回路、NOT回路、バッファ回路、またはレジスタ回路などはTFTで構成することができ、高い電界効果移動度を得るために、連続発振型のレーザー光を用いて結晶化を行った半導体膜をTFTの活性層として作製すればよい。アモルファスシリコン膜に連続発振型のレーザー光を照射してポリシリコン膜を得る方法を用いてもよいし、アモルファスシリコン膜を加熱してポリシリコン膜を得た後に連続発振型のレーザー光を照射してポリシリコン膜を得る方法を用いてもよいし、アモルファスシリコン膜に触媒となる金属元素を添加した後、加熱してポリシリコン膜を得た後に連続発振型のレーザー光を照射してポリシリコン膜を得る方法を用いてもよい。本実施例において、演算部1003を構成するTFTのチャネル長方向とレーザービームの走査方向とを揃える。また、ドーピングの際、演算部1003を構成するTFTのチャネル長方向と基板の傾け方向とを合わせる。

30

**【0227】**

また、制御部1002は記憶部1004に格納された命令を実行して、全体の動作を制御する役割を担っている。制御部1002はプログラムカウンタ、命令レジスタ、制御信号生成部からなる。また、制御部1002もTFTで構成することができ、連続発振型のレーザー光を用いて結晶化を行った半導体膜をTFTの活性層として作製すればよい。本実施例において、制御部1002を構成するTFTのチャネル長方向とレーザービームの走査方向とを揃える。また、ドーピングの際、制御部1002を構成するTFTのチャネル長方向と基板の傾け方向とを合わせる。

40

50

**【0228】**

また、記憶部1004は、計算を行うためのデータと命令を格納する場所であり、CPUで頻繁に実行されるデータやプログラムが格納されている。記憶部1004は、主メモリ、アドレスレジスタ、データレジスタからなる。さらに主メモリに加えてキャッシュメモリを用いてもよい。これらのメモリは、SRAM、DRAM、フラッシュメモリなどで形成すればよい。また、記憶部1004も TFTで構成する場合には、連続発振型のレーザー光を用いて結晶化を行った半導体膜をTFTの活性層として作製することができる。本実施例において、記憶部1004を構成するTFTのチャネル長方向とレーザービームの走査方向とを揃えることが好ましい。

**【0229】**

また、入力部1005は外部からデータやプログラムを取り込む装置である。また、出力部1006は結果を表示するための装置、代表的には表示装置である。

**【0230】**

TFTのチャネル長方向とレーザービームの走査方向を揃えることによってバラツキの少ないCPUを絶縁基板上に作り込むことができる。また、同一基板上にCPUと表示部とを作り込むことができる。表示部においても各画素に配置される複数のTFTのチャネル長方向とレーザービームの走査方向を揃えることが好ましい。

**【0231】**

また、回路設計や作製工程が複雑になるが、同一基板上にCPUと表示部とメモリとを作り込むこともできる。

**【0232】**

また、本実施例は、最良の形態または実施例4と自由に組み合わせることができる。

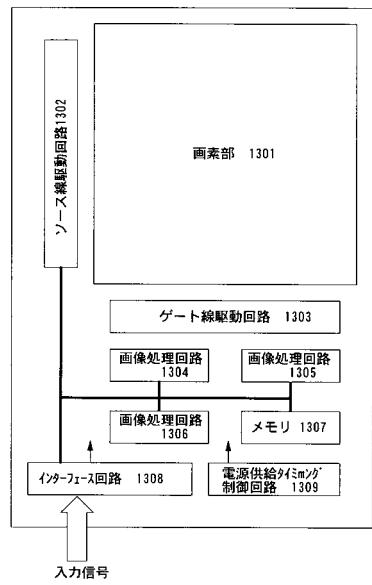

**【実施例8】****【0233】**

本実施例では、絶縁表面を有する基板上に、画素部、画素を駆動する駆動回路、及び画像処理回路とを少なくとも形成した半導体装置の構成例と、消費電力を削減する動作方法について説明する。

**【0234】**

図12に示すのはガラス基板上に形成された表示部を有するシステムの一例であって、ガラス基板上には、画素部1301、ソース線駆動回路1302、ゲート線駆動回路1303、機能の異なる3つの画像処理回路1304～1306、メモリ1307、インターフェース回路1308、電源供給タイミング制御回路1309が設けられている。本半導体装置は、液晶表示装置であっても、EL材料を用いた発光表示装置であっても構わない。

**【0235】**

図12に示したブロック図において、画素部1301は画像を表示する部分であり、ソース線駆動回路1302、及びゲート線駆動回路1303は、画素を駆動する駆動回路である。画像データはソース線駆動回路1302に入力される。また、インターフェース回路1308は外部から画像データ、あるいは画像の基となるデータを入力し、適切な内部信号に変換した後、ソース線駆動回路1302、画像処理回路1304～1306、もしくはメモリ1307に出力する。

**【0236】**

本半導体装置の機能として、3つの画像処理回路1304～1306とメモリ1307を用いた様々な画像処理を行う半導体装置を考えることができる。例えば、これらの画像処理回路の1つもしくは複数を用いることによって、画像の歪み補正、リサイズ、モザイク処理、スクロール、反転といった画像変換や、マルチウィンドウ処理、メモリ1307を用いた画像生成、及びこれらの複合処理等を考えることができる。

**【0237】**

これに対応して、様々な動作モードが考えられ、本構成の半導体装置においては、画像処理回路1304～1306が有するレジスタ及びラッチ回路に、不揮発性を有するラッ

10

20

30

40

50

チ回路を適用することが有効である。つまり、不揮発性を有するラッチ回路によって、画像処理回路 1304～1306 の論理状態が復元可能である構成が有効である。こうすることにより、画像処理回路 1304～1306 の動作状態を保持したまま電源を遮断することが可能となり、使用しない画像処理回路の電源を遮断することが可能となる。その結果、消費電力の削減が可能となる。

#### 【0238】

また、待機時においても、システムの状態を保持したままで、電源供給を止めることができるために、待機時と動作時の高速な移行と、待機時の消費電力の削減を同時に実現することが可能となる。

#### 【0239】

動作モードの切り替え制御は、電源供給タイミング制御回路 1309 によって行う。具体的には、動作モードに対応して、モードの切り替え前後に、使用しない画像処理回路に対して格納手続と復元手続を行えばよい。

#### 【0240】

なお、本実施例では、画像処理回路 1304～1306 全体を復元可能な場合を説明したが、必ずしもこれに限定されない。画像処理回路 1304～1306 を構成する一部の回路（例えば回路 C とする）の論理状態を復元可能とする構成であっても構わない。その場合、回路 C を使用する時のみに回路 C に電源を供給することが可能となり、消費電力の削減が可能となる。

#### 【0241】

なお、不揮発性を有するラッチ回路を、インターフェース回路、あるいはソース線駆動回路、ゲート線駆動回路に対して適用することも可能である。その結果、それぞれの論理回路が動作しない時には、その論理回路の電源を遮断することで消費電力を削減することが可能となる。

#### 【0242】

本実施例における様々な回路（画素部 1301、ソース線駆動回路 1302、ゲート線駆動回路 1303、機能の異なる 3 つの画像処理回路 1304～1306、メモリ 1307、インターフェース回路 1308、電源供給タイミング制御回路 1309）は、実施例 4 に従って得られる高速動作可能な TFT で作製することができる。

#### 【0243】

なお、本実施例は、最良の形態、実施例 1 乃至 4 のいずれの構成とも自由に組み合わせることが可能である。

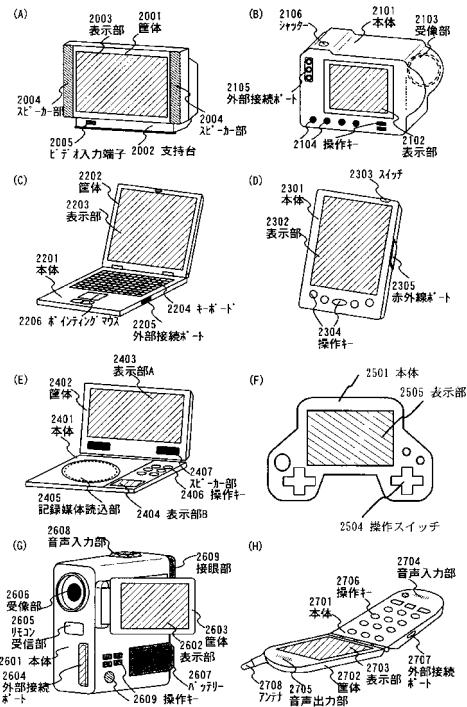

#### 【実施例 9】

#### 【0244】

本発明を実施して得た半導体素子を組み込むことによって様々な電子機器を作製することができる。電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDigital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。それらの電子機器の具体例を図 9 に示す。

#### 【0245】

図 13 (A) はテレビであり、筐体 2001、支持台 2002、表示部 2003、スピーカー部 2004、ビデオ入力端子 2005 等を含む。本発明は表示部 2003 に適用することができる。なお、パソコン用、TV 放送受信用、広告表示用などの全ての情報表示用のテレビが含まれる。

#### 【0246】

図 13 (B) はデジタルカメラであり、本体 2101、表示部 2102、受像部 2103、操作キー 2104、外部接続ポート 2105、シャッター 2106 等を含む。本発明

10

20

30

40

50

は、表示部 2102 に適用することができる。

**【0247】**

図 13 (C) はノート型パーソナルコンピュータであり、本体 2201、筐体 2202、表示部 2203、キーボード 2204、外部接続ポート 2205、ポインティングマウス 2206 等を含む。本発明は、表示部 2203 に適用することができる。

**【0248】**

図 13 (D) はモバイルコンピュータであり、本体 2301、表示部 2302、スイッチ 2303、操作キー 2304、赤外線ポート 2305 等を含む。本発明は、表示部 2302 に適用することができる。

**【0249】**

図 13 (E) は記録媒体を備えた携帯型の画像再生装置（具体的には DVD 再生装置）であり、本体 2401、筐体 2402、表示部 A 2403、表示部 B 2404、記録媒体（DVD 等）読み込み部 2405、操作キー 2406、スピーカー部 2407 等を含む。表示部 A 2403 は主として画像情報を表示し、表示部 B 2404 は主として文字情報を表示するが、本発明は表示部 A、B 2403、2404 に適用することができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

**【0250】**

図 13 (F) はゲーム機器であり、本体 2501、表示部 2505、操作スイッチ 2504 等を含む。

**【0251】**

図 13 (G) はビデオカメラであり、本体 2601、表示部 2602、筐体 2603、外部接続ポート 2604、リモコン受信部 2605、受像部 2606、バッテリー 2607、音声入力部 2608、操作キー 2609 等を含む。本発明は、表示部 2602 に適用することができる。

**【0252】**

図 13 (H) は携帯電話であり、本体 2701、筐体 2702、表示部 2703、音声入力部 2704、音声出力部 2705、操作キー 2706、外部接続ポート 2707、アンテナ 2708 等を含む。本発明は、表示部 2703 に適用することができる。なお、表示部 2703 は黒色の背景に白色の文字を表示することで携帯電話の消費電流を抑えることができる。

**【0253】**

以上の様に、本発明を実施して得た表示装置は、あらゆる電子機器の表示部として用いても良い。なお、本実施の形態の電子機器には、最良の形態、実施例 1 乃至 7 のいずれの構成を用いて作製された半導体装置を用いても良い。

**【図面の簡単な説明】**

**【0254】**

【図 1】本発明に係る配線の作製工程を説明する断面図。

【図 2】本発明に係る配線の作製工程を説明する断面図。

【図 3】本発明に係る配線の作製工程を説明する断面図。

【図 4】本発明に係るアクティブマトリクス基板の作製工程を説明する断面図

【図 5】本発明に係るアクティブマトリクス基板の作製工程を説明する斜視図。

【図 6】本発明に係る発光装置の発光領域の構造を説明する斜視図。

【図 7】本発明に係る発光装置の構造を説明する断面図

【図 8】本発明に係る液晶表示装置の構造を説明する斜視図。

【図 9】本発明に係る多層配線の作製工程を説明する断面図。

【図 10】本発明に係る半導体装置の作製工程を説明する斜視図。

【図 11】CPU のブロック図を示す図。

【図 12】表示部を有するシステムブロック図を示す図。

【図 13】電子機器の一例を示す図。

【図 14】発光素子の断面構造を示す図。

10

20

30

40

50

【図15】絶縁膜と配線との結合を示すモデル図。

【図16】窒素を含む導電膜の組成比を示す図。

【図17】窒素を含む導電膜の導電率を示す図。

【図18】窒素を含む導電膜のコンタクト抵抗値を示す図。

【図19】窒素を含む導電膜の接触抵抗率を示す図。

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【 四 6 】

【図7】

〔 図 8 〕

【 図 9 】

【 図 1 0 】

【図 1-1】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

コンタクト径:  $\phi 3 \mu m$

定電流:  $100 \mu A$

---

フロントページの続き

| (51)Int.Cl.             | F I               |

|-------------------------|-------------------|

| H 01 L 21/312 (2006.01) | H 01 L 21/285 S   |

| H 01 L 29/786 (2006.01) | H 01 L 21/312 C   |

| H 01 L 51/50 (2006.01)  | H 01 L 29/78 612C |

|                         | H 01 L 29/78 619A |

|                         | H 01 L 29/78 616V |

|                         | H 05 B 33/14 A    |

(56)参考文献 特開2003-179232(JP,A)

特開平07-326618(JP,A)

特開平10-084041(JP,A)

特開2001-102382(JP,A)

特開2001-176875(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |               |

|--------|---------------|

| H 01 L | 2 1 / 3 2 0 5 |

| H 01 L | 2 1 / 3 2 1 3 |

| H 01 L | 2 1 / 7 6 8   |

| H 01 L | 2 1 / 2 8     |

| H 01 L | 2 1 / 2 8 5   |

| H 01 L | 2 1 / 3 1 2   |

| H 01 L | 2 3 / 5 2     |

| H 01 L | 2 9 / 7 8 6   |

| H 01 L | 2 1 / 3 3 6   |

| H 01 L | 5 1 / 5 0     |