(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2022-142782

(P2022-142782A)

(43)公開日 令和4年9月30日(2022.9.30)

(51)国際特許分類

H 01 L 33/38 (2010.01)

H 01 L 33/30 (2010.01)

F I

H 01 L 33/38

H 01 L 33/30

テーマコード(参考)

5 F 2 4 1

審査請求 未請求 請求項の数 10 O L (全22頁)

(21)出願番号 特願2022-40869(P2022-40869)

(22)出願日 令和4年3月16日(2022.3.16)

(31)優先権主張番号 17/203293

(32)優先日 令和3年3月16日(2021.3.16)

(33)優先権主張国・地域又は機関

米国(US)

(71)出願人 598061302

晶元光電股 ふん 有限公司

Epistar Corporation

台灣新竹科學工業園區新竹市東區力行路

21號

21, Li-hsin Rd., Science-based Industrial Park, Hsinchu 300, TAIWAN

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(74)代理人 100135079

弁理士 宮崎 修

最終頁に続く

(54)【発明の名称】 半導体素子、該半導体素子を含む半導体装置及び表示パネル

## (57)【要約】

10

【課題】本開示は、半導体素子、それを含む半導体装置及び表示パネルを提供する。

【解決手段】半導体素子は、表面を有する第一半導体層であって、該表面は第一部分及び第二部分を含む、第一半導体層；前記第一部分上に位置し、かつAlGaInAs、InGaAsP、AlGaAsP又はAlGaInPを含むアクティブ領域；前記第二部分上に位置し、前記第一半導体層と同じ又は異なる導電型を有し、かつ酸素(O)元素及び第五金属元素を含む接触層；及び、前記接触層上に位置する第一金属元素含有構造を含む。前記接触層は前記第一金属元素含有構造及び前記第一半導体層に直接接觸する。

【選択図】図 1

10

**【特許請求の範囲】****【請求項 1】**

半導体素子であって、

表面を有する第一半導体層であって、該表面は第一部分及び第二部分を含む、第一半導体層；

前記第一部分上に位置し、かつAlGaInAs、InGaAsP、AlGaAsP又はAlGaInPを含むアクティブ領域；

前記第二部分上に位置し、前記第一半導体層と同じ又は異なる導電型を有し、かつ酸素(O)元素及び第五金属元素を含む接触層；及び

前記接触層上に位置する第一金属元素含有構造を含み、

前記接触層は前記第一金属元素含有構造及び前記第一半導体層に直接接觸する、半導体素子。

**【請求項 2】**

請求項1に記載の半導体素子であって、

前記第一金属元素含有構造は前記第一半導体層に直接接觸せず、前記第一金属元素含有構造は前記接触層によって前記第一半導体層に電気接続される、半導体素子。

**【請求項 3】**

請求項1に記載の半導体素子であって、

前記第一半導体層の下に位置する接合構造をさらに含む、半導体素子。

**【請求項 4】**

請求項1に記載の半導体素子であって、

前記接触層には1種類のみの金属元素が含まれる、半導体素子。

**【請求項 5】**

請求項1に記載の半導体素子であって、

前記第一半導体層はリン化物又はヒ化物を含む、半導体素子。

**【請求項 6】**

半導体素子の製造方法であって、

成長基板を提供し；

前記成長基板上に半導体スタック層を形成し、前記半導体スタック層は第一半導体層及びアクティブ領域を含み；

前記半導体スタック層を接合基板に接合し；

前記成長基板を除去し；

一部の前記半導体スタック層を除去して前記第一半導体層を露出させ；

前記第一半導体層上に接触層を形成し、前記接触層は、前記第一半導体層と同じ又は異なる導電型を有し、かつ酸素(O)元素及び第五金属元素を含み；及び

前記接触層上に第一金属元素含有構造を形成するステップを含む、半導体素子の製造方法。

**【請求項 7】**

請求項6に記載の半導体素子の製造方法であって、

前記第一半導体層と前記接合基板との間に接合構造を形成するステップをさらに含む、半導体素子の製造方法。

**【請求項 8】**

請求項7に記載の半導体素子の製造方法であって、

前記接合構造は熱硬化性ポリマーを含む、半導体素子の製造方法。

**【請求項 9】**

請求項8に記載の半導体素子の製造方法であって、

前記接合構造を形成するステップは、

第一温度で加熱を行う加熱ステップを含み、

前記熱硬化性ポリマーは熱分解温度を有し、前記第一温度は前記熱分解温度よりも小さく、又は、前記第一温度と前記該熱分解温度との差は50°C以下である、導体素子の製

10

20

30

40

50

造方法。

【請求項 10】

請求項 6 に記載の半導体素子の製造方法であって、

前記第一金属元素含有構造は合金を含む、導体素子の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、半導体素子に関し、特に、半導体発光素子、例えば、発光ダイオード(Light emitting diode、LED)などに関する。また、本開示は、半導体素子の製造方法、半導体素子を含む半導体装置及び表示パネルにも関する。

10

【背景技術】

【0002】

半導体素子が各種の製品に広く使用されており、また、様々な半導体素子関連材料の研究開発も進行中である。例を挙げて言えば、3族及び5族元素を含むIII-V族化合物半導体材料は、各種の半導体素子、例えば、発光ダイオード、レーザーダイオード(Laser diode、LD)、光電検出器(Opoelectronic detector)、太陽電池(Solar cell)、あるいは、パワー素子(Power device)、例えば、スイッチ素子(Switch)又は整流器(Rectifier)の製造に広く適用することができる。近年、これらの半導体素子は照明、医療、ディスプレイ、通信、センシングシステムなどの分野で広く使用されている。そのうち、発光ダイオードは、エネルギー消費量が少なく、かつ耐用年数が長いため、様々な分野で広く応用されている。

20

【発明の概要】

【発明が解決しようとする課題】

【0003】

本開示の目的は、半導体素子の製造方法、半導体素子を含む半導体装置及び表示パネルを提供することにある。

【課題を解決するための手段】

【0004】

本開示によれば、半導体素子が提供され、該半導体素子は第一半導体層、アクティブ領域、接触層、及び第一金属元素含有構造(first metal element-containing structure)を含む。第一半導体層は表面を有する。該表面は第一部分及び第二部分を含む。アクティブ領域は第一部分上に位置し、かつAlGaInAs、InGaAsP、AlGaAsP又はAlGalnPを含む。接触層は第二部分上に位置し、かつ酸素(O)元素及び第五金属元素を含む。第一金属元素含有構造はp型又はn型層上に位置する。そのうち、接触層は第一金属元素含有構造及び第一半導体層に直接接觸する。

30

【0005】

本開示の一実施例において、上述の第一金属元素含有構造は第一半導体層に直接接觸せず、かつ第一金属元素含有構造は接触層によって第一半導体層に電気接続される。

【0006】

本開示の一実施例において、第一半導体層の下に位置する接合構造をさらに含む。

40

【0007】

本開示の一実施例において、接触層には1種類のみの金属元素が含まれる。

【0008】

本開示の一実施例において、第一半導体構造はリン化物又はヒ化物を含む。

【0009】

本開示によれば、半導体素子の製造方法が提供され、該製造方法以下のステップを含み、即ち、成長基板を提供し；成長基板上に半導体スタック層を形成し、上述の半導体スタック層は第一半導体層及びアクティブ領域を含み；半導体スタック層を接合基板に接合し；成長基板を除去し；一部の半導体スタック層を除去して第一半導体層を露出させ；第一半導体層上に接触層を形成し、上述の接触層は酸素(O)元素及び第五金属元素を含み；及

50

び、接触層上に第一金属元素含有構造を形成するステップである。

【0010】

本開示の一実施例において、第一半導体層と接合基板との間に形成される接合構造をさらに含む。

【0011】

本開示の一実施例において、接合構造は熱硬化性ポリマーを含む。

【0012】

本開示の一実施例において、接触層上に第一金属元素含有構造を形成するステップは、第一温度で加熱を行う加熱ステップを含み、そのうち、熱硬化性ポリマーは熱分解温度を有し、第一温度は熱分解温度よりも小さく（低く）、又は、第一温度と熱分解温度との差は50°C以下である。10

【0013】

本開示の一実施例において、第一金属元素含有構造は合金を含む。

【図面の簡単な説明】

【0014】

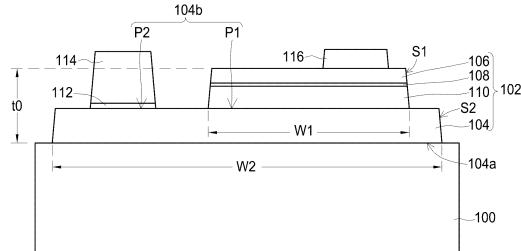

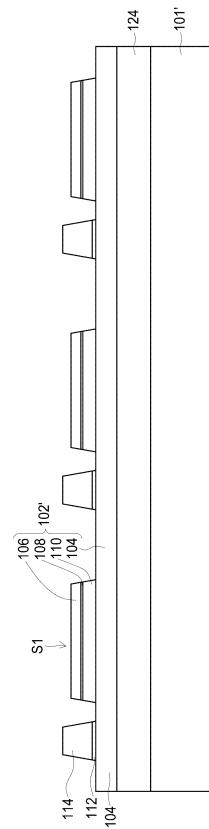

【図1】本開示の一実施例における半導体素子の断面構造を示す図である。

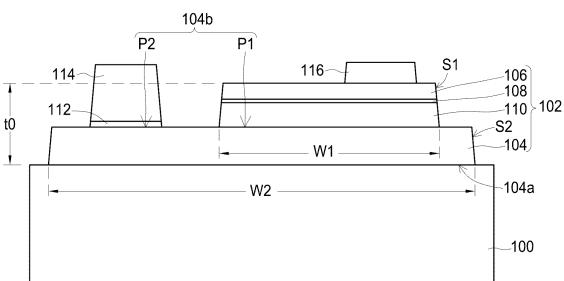

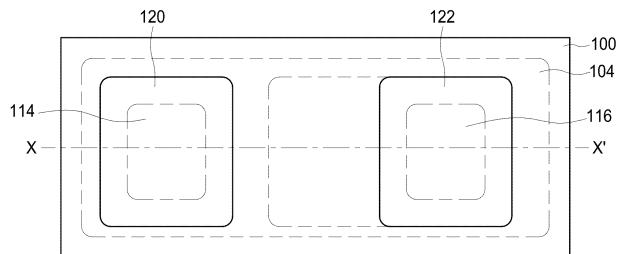

【図2A】本開示の一実施例における半導体素子の上面図である。

【図2B】図2Aに示す半導体素子のX-X'線に沿った断面構造を示す図である。

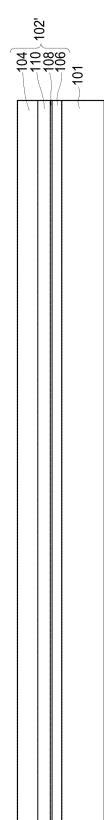

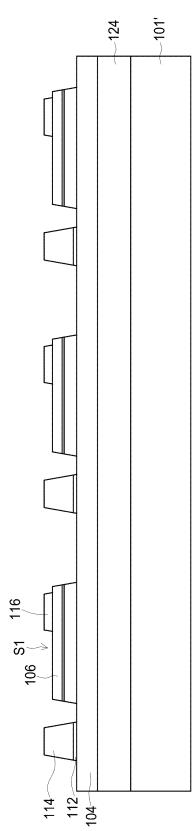

【図3A】本開示の一実施例における半導体素子の製造方法を示す図である。

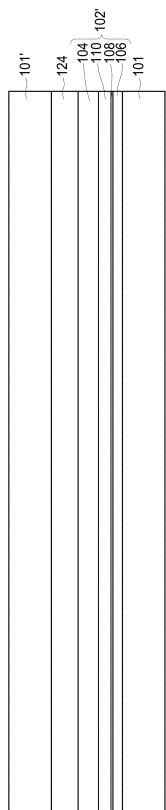

【図3B】本開示の一実施例における半導体素子の製造方法を示す図である。20

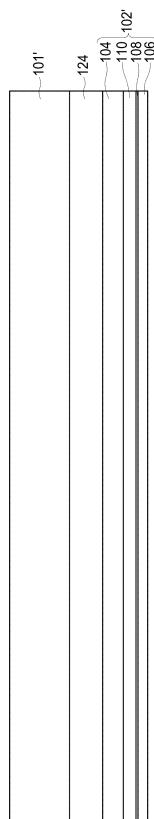

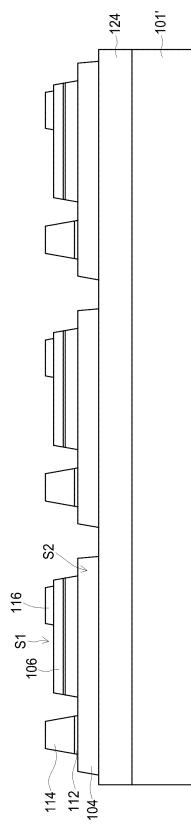

【図3C】本開示の一実施例における半導体素子の製造方法を示す図である。

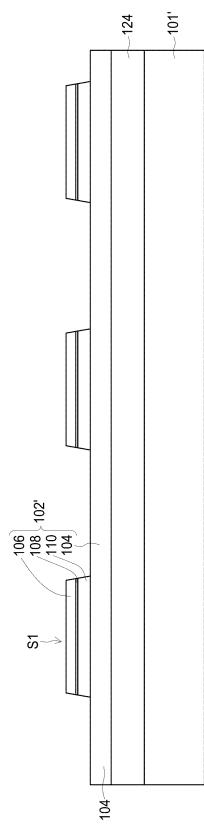

【図3D】本開示の一実施例における半導体素子の製造方法を示す図である。

【図3E】本開示の一実施例における半導体素子の製造方法を示す図である。

【図3F】本開示の一実施例における半導体素子の製造方法を示す図である。

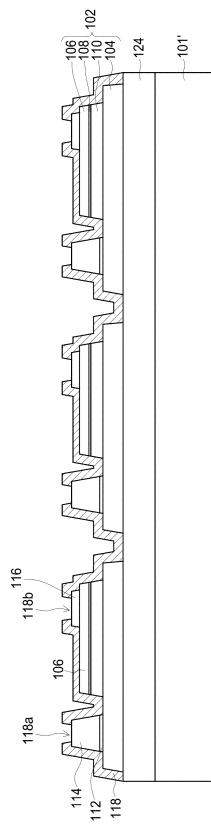

【図3G】本開示の一実施例における半導体素子の製造方法を示す図である。

【図3H】本開示の一実施例における半導体素子の製造方法を示す図である。

【図3I】本開示の一実施例における半導体素子の製造方法を示す図である。

【図3J】本開示の一実施例における半導体素子の製造方法を示す図である。

【図3K】本開示の一実施例における半導体素子の断面構造を示す図である。

【図3L】本開示の一実施例における半導体素子の断面構造を示す図である。30

【図3M】本開示の一実施例における半導体素子の断面構造を示す図である。

【図4A】本開示の一実施例における半導体装置の断面構造を示す図である。

【図4B】本開示の一実施例における半導体装置の断面構造を示す図である。

【図5A】本開示の一実施例における表示パネルの上面図である。

【図5B】本開示の一実施例における表示パネルの一部の断面構造を示す図である。

【図5C】本開示の一実施例における表示パネルの一部の断面構造を示す図である。

【図5D】本開示の一実施例における表示パネルの一部の断面構造を示す図である。

【図5E】本開示の一実施例における表示パネルの一部の断面構造を示す図である。

【発明を実施するための形態】

【0015】

本開示の上述した及び他の技術的内容、特徴、機能及び効果は、添付した図面に基づく次のような好適な実施例の詳細な説明により明確になる。なお、以下の実施例に言及される方向についての用語、例えば、上、下、左、右、前又は後などは、添付した図面の方向に過ぎない。よって、使用される方向の用語は、本開示を説明するためだけのものであり、本開示を限定するためのものではない。40

【0016】

本開示において、特段の説明がない限り、一般式 $\text{In}_x\text{Ga}_1-x\text{P}$ が $\text{In}_{x_0}\text{Ga}_{1-x_0}\text{P}$ を表し、そのうち、 $0 < x_0 < 1$ であり；一般式 $\text{Al}_x\text{In}_1-x\text{P}$ が $\text{Al}_{x_1}\text{In}_{1-x_1}\text{P}$ を表し、そのうち、 $0 < x_1 < 1$ であり；一般式 $\text{Al}_x\text{Ga}_y\text{In}_z\text{P}$ が $\text{Al}_{x_2}\text{Ga}_{x_3}\text{In}_{1-x_2-x_3}\text{P}$ を表し、そのうち、 $0 < x_2 < 1$ 、かつ $0 < x_3 < 1$ であり；一般式 $\text{In}_x\text{Ga}_y\text{As}_z\text{P}$ が $\text{In}_{x_4}\text{Ga}_{1-x_4}\text{As}_{x_5}\text{P}_{1-x_5}$ を表し、そのうち、 $0 < x_4 < 1$ 50

1、かつ0  $x$  5 1であり；一般式AlGaNAsが $Al_{x_6}Ga_{x_7}In_{1-x_6-x_7}As$ を表し、そのうち、0  $x$  6 1、かつ0  $x$  7 1であり；一般式InGaAsが $In_{x_8}Ga_{1-x_8}As$ を表し、そのうち、0  $x$  8 1であり；一般式AlGaAsが $Al_{x_9}Ga_{1-x_9}As$ を表し、そのうち、0  $x$  9 1であり；一般式InGaNが $In_{x_{10}}Ga_{1-x_{10}}N$ を表し、そのうち、0  $x$  10 1であり；一般式AlGaNが $Al_{x_{11}}Ga_{1-x_{11}}N$ を表し、そのうち、0  $x$  11 1であり；一般式AlGaAsPが $Al_{x_{12}}Ga_{1-x_{12}}As_{x_{13}}P_{1-x_{13}}$ を表し、そのうち、0  $x$  12 1、かつ0  $x$  13 1であり；一般式InGaAsNが $In_{x_{14}}Ga_{1-x_{14}}As_{x_{15}}N_{1-x_{15}}$ を表し、そのうち、0  $x$  14 1、かつ0  $x$  15 1であり；一般式AlInGaNが $Al_{x_{16}}In_{x_{17}}Ga_{1-x_{16}-x_{17}}N$ を表し、そのうち、0  $x$  16 1、かつ0  $x$  17 1である。なお、異なる目的に従って各元素の含有量を調整することができ、例えば、エネルギーギャップの大きさを調整し得るが、これに限定されず、あるいは、半導体素子が発光素子であるときに、発光素子のピーク波長(peak wavelength)又は主波長(domain wavelength)を調整しても良い。

10

#### 【0017】

本開示の半導体素子は例えば光電素子、例えば、発光素子(例えば、発光ダイオード(light-emitting diode)又はレーザーダイオード(laser diode))、吸光素子(例えば、光電ダイオード(photo-detector)又は太陽電池(solar cell))であり、あるいは、非光電素子(non-optoelectric device)であっても良い。本開示の半導体素子に含まれる各層の組成(成分)及び/又はドーパント(dopant)は任意の適切な方式、例えば、二次イオン質量分析計(secondary ion mass spectrometer、SIMS)、エネルギー分散型X線分光法(Energy-dispersive X-ray spectroscopy、EDX)、X線光電子分光法(X-ray photoelectron spectroscopy、XPS)又は紫外線電子分光法(Ultra violet Photoelectron Spectroscopy、UPS)により分析することで得ることができる。各層の厚さなどのサイズも任意の適切な方式、例えば、透過型電子顕微鏡法(transmission electron microscopy、TEM)、走査型電子顕微鏡(scanning electron microscope、SEM)又は走査型透過電子顕微鏡(scanning transmission electron microscope、STEM)により分析することで得ることができる。

20

#### 【0018】

当業者が理解すべきは、以下に説明される各実施例をもとに他の構成要素を追加しても良いということである。例を挙げて言えば、特段の説明がない限り、「第一層(又は構造)が第二層(又は構造)上に位置する」のような説明は、第一層(又は構造)が第二層(又は構造)に直接接触する実施例を含んでも良く、又は、第一層(又は構造)と第二層(又は構造)との間に他の構造があつて両者が互いに直接接触しない実施例を含んでも良い。また、理解すべきは、各層(又は構造)の上下の位置関係などは異なる方向で観察することによって変わることがあるということである。

30

#### 【0019】

また、本開示では、層又は構造が「実質的にMからなる」のような記載は、この層又は構造の主な成分がMであることを表すが、この層又は構造がドーパント又は避けられない不純物(impurities)を含むことを排除しない。

#### 【0020】

図1は本開示の一実施例における半導体素子10の断面構造を示す図である。図1に示すように、半導体素子10はベース100及びベース100上に位置する半導体構造102を含む。半導体構造102はエピタキシャル構造であり、かつ第一半導体層104、第二半導体層106、及び第一半導体層104と第二半導体層106との間に位置するアクティブ領域108を含んでも良い。一実施例において、半導体構造102はさらに、アクティブ領域108と第一半導体層104との間に位置する第三半導体層110を含む。 $p$ 型又は $n$ 型層(接触層)112は第一半導体層104上に位置する。図1に示すように、半導体構造102上に第一金属元素含有構造114及び第二金属元素含有構造116が設置されている。具体的に言えば、第一半導体層104はベース100に面する第一表面104a、並びに第一金属元素含有構造114及び第二金属元素含有構造116に面する第二表面104bを有する。第二表面104bは第一部分P1及び第二部分P2を含む。

40

50

## 【 0 0 2 1 】

一実施例において、第二半導体層106、アクティブ領域108及び第三半導体層110は第一部分P1に位置するが、第二部分P2上に位置しない。p型又はn型層112は第二部分P2に位置するが、第一部分P1上に位置せず、第一金属元素含有構造114はこのp型又はn型層112上に位置する。具体的に言えば、このp型又はn型層112は第一金属元素含有構造114と第一半導体層104との間に位置し、かつ第一金属元素含有構造114及び第一半導体層104に直接接触する。一実施例では、第一半導体層104上において、第二半導体層106、アクティブ領域108及び第三半導体層110は第一メサ構造(mesa structure)S1を形成し、第一半導体層104は第二メサ構造S2を形成する。図1に示すように、第一メサ構造S1は第一幅W1を有し、かつ第二メサ構造S2は第一幅W1よりも大きい第二幅W2を有する。第一幅W1は第一メサ構造S1の最大幅であり、第二幅W2は第二メサ構造S2の最大幅である。断面において、第一メサ構造S1及び第二メサ構造S2はそれぞれ台形状又は矩形状を有する。

## 【 0 0 2 2 】

一実施例では、断面において、第一メサ構造S1の側表面は第二メサ構造S2の側表面とはアライメントしない(同一平面上にない)。一実施例において、第一メサ構造S1及び第二メサ構造S2は上面図においてそれぞれ角丸矩形状(rounded rectangular shape)を有し、これにより、尖端放電(point discharge)を減少させ、安定性を改善することができる。一実施例において、上面視で、半導体素子10は $150\mu m$ よりも小さく又は $100\mu m$ よりも小さい長さ、及び $150\mu m$ よりも小さく又は $100\mu m$ よりも小さい幅を有する。半導体素子10の長さと幅の比は0.3乃至1の範囲内にあっても良い。

## 【 0 0 2 3 】

ベース100は導電又は絶縁材料を含んでも良い。導電材料はGaAs、InP、SiC、GaP、ZnO、GaN、AlN、Ge、Siなどを含み、絶縁材料はサファイア(Sapphire)などを含む。一実施例において、ベース100は成長基板であり、即ち、半導体構造102は例えば、金属有機化学蒸着法(metal organic chemical vapor deposition、MOCVD)によりエピタキシャル方式でベース100上に形成することができる。一実施例において、ベース100は成長基板ではなく、接合基板であり、かつ接合構造124により半導体構造102に接続され得る(図2Bに示すように)。一実施例において、半導体素子10はベース100を有しなくても良い。半導体構造102の総厚さt0は $10\mu m$ 以下であっても良い。総厚さt0と半導体素子10の長さ又は幅の比は0.5以下であっても良く、例えば、0.3よりも小さく又は0.1よりも小さく、これにより、製造プロセスにおける半導体素子10の構造安定性を確保することができる。

## 【 0 0 2 4 】

一実施例において、第一半導体層104は第一ドーパントを含み、第二半導体層106は第二ドーパントを含み、これにより、第一半導体層104及び第二半導体層106は異なる導電型を有するようになる。例を挙げて言えば、第一半導体層104はn型であり、第二半導体層106はp型であり、あるいは、第一半導体層104はp型であり、第二半導体層106はn型である。一実施例において、第一ドーパント及び第二ドーパントはそれぞれ周期表における第II族、第IV族又は第VI族の元素を含んでも良い。例を挙げて言えば、第一ドーパント及び第二ドーパントはそれぞれC、Zn、Si、Ge、Sn、Se、Mg又はTeを含み得る。第一半導体層104及び第二半導体層106はそれぞれ電子及び正孔、あるいは、正孔及び電子を提供する。一実施例において、第三半導体層110は第一半導体層104と同じ導電型を有する。一実施例において、第一半導体層104、第二半導体層106、アクティブ領域108及び第三半導体層110はそれぞれIII-V族半導体材料を含む。一実施例において、上述のIII-V族半導体材料はAl、Ga、As、P、N又はIn元素を含む。具体的に言えば、一実施例において、上述のIII-V族半導体材料は二元化合物半導体(例えば、GaAs、GaP又はGaN)、三元化合物半導体(例えば、InGaAs、AlGaAs、InGaP、AlInP、InGaN又はAlGaN)、又は四元化合物半導体(例えば、AlGaInAs、AlGaInP、AlInGaN、InGaAsP、InGaAsN又はAlGaAsP)であっても良い。一実施例において、アクティブ領域1

10

20

30

40

50

08は実質的に三元化合物半導体(例えば、InGaAs、AlGaAs、InGaP、AlInP、InGaN又はAlGaN)又は四元化合物半導体(例えば、AlGaInAs、AlGaInP、AlInGaN、InGaAsP、InGaAsN又はAlGaAsP)からなる。幾つかの実施例において、第一半導体層104、第二半導体層106、アクティブ領域108及び第三半導体層110はN元素を含まない。幾つかの実施例において、第一半導体層104、第二半導体層106、アクティブ領域108及び第三半導体層110はそれぞれリン化物(phosphide compound)又はヒ化物(arsenide compound)を含む。

#### 【0025】

一実施例によれば、半導体素子10が発光素子であり、半導体素子10がワーキングするときに、アクティブ領域108は光線(光束)を発することができる。この光線は可視光又は不可視光を含む。半導体素子10が発するピーク波長(peak wavelength)はアクティブ領域108の材料組成(成分)に依存する。アクティブ領域108の材料は三元化合物半導体(例えば、InGaN、InGaAs、AlGaN、AlGaAs又はInGaP)又は四元化合物半導体(例えば、InGaAsP、AlGaInAs又はAlGaInP)を含んでも良い。幾つかの実施例において、半導体素子10は、ピーク波長が400nm乃至490nmの青色光又は深(濃)青色光、ピーク波長が490nm乃至550nmの緑色光、ピーク波長が250nm乃至400nmの紫外線、ピーク波長が610nm乃至700nmの赤色光、ピーク波長が530nm乃至600nmの黄色光、又はピーク波長が700乃至1700nmの赤外線を発することができる。

#### 【0026】

第一金属元素含有構造114及び第二金属元素含有構造116はそれぞれ単層又は多層であっても良い。第一金属元素含有構造114及び第二金属元素含有構造116は何れも接触部とすることができます。幾つかの実施例によれば、第一金属元素含有構造114及び第二金属元素含有構造116は外部電源(図示せず)と直接電気接続することができ、あるいは、他の構造(例えば、後述の第一電極パッド120及び第二電極パッド122)により外部電源(図示せず)と電気接続されても良い。断面において、第一金属元素含有構造114及び第二金属元素含有構造116はそれぞれ台形状又は矩形状を有しても良い。一実施例において、第一金属元素含有構造114は第一金属元素M1を含み、第二金属元素含有構造116は第二金属元素M2を含む。第一金属元素M1及び第二金属元素M2は同じであっても良く、異なっても良い。一実施例において、第一金属元素含有構造114はBeを含まない(void of Be)。

#### 【0027】

一実施例において、第一金属元素含有構造114はさらに、第一金属元素M1とは異なる第三金属元素M3を含む。一実施例において、第一金属元素含有構造114は第一金属元素M1及び第三金属元素M3の合金を含む。一実施例において、第一金属元素含有構造114は第一層及び第二層(図示せず)を含んでも良く、第一層はp型又はn型層112に直接接触し、第二層は第一層上に位置する。一実施例において、第一層は第一金属元素M1を含み、第二層は第三金属元素M3を含む。一実施例において、第二金属元素含有構造116はさらに、第二金属元素M2とは異なる第四金属元素M4を含んでも良い。一実施例において、第二金属元素含有構造116は第二金属元素M2及び第四金属元素M4の合金を含む。一実施例において、第二金属元素含有構造116は第三層及び第四層を含んでも良く、第三層は第二半導体層106に直接接触し、第四層は第三層上に位置する。一実施例において、第三層は第二金属元素M2を含み、第四層は第四金属元素M4を含む。一実施例において、第三金属元素M3及び第四金属元素M4は同じであっても良い。一実施例において、第一金属元素M1、第二金属元素M2、第三金属元素M3及び第四金属元素M4はそれぞれTi、Ni、Al、Zn、Ge、Mo、W、V、Ga、Au又はAgから選択され得る。

#### 【0028】

一実施例において、第一金属元素含有構造114は第一半導体層104に直接接触しない。第一金属元素含有構造114はp型又はn型層112により第一半導体層104に電気接続される。一実施例において、p型又はn型層112の材料は垂直方向上で第一接触抵抗率(contact resistivity)を有し、水平方向上で第二接触抵抗率を有する。第二接触抵抗率は

10

20

30

40

50

第一接触抵抗率よりも大きくても良く、これにより、電流は主に垂直方向に沿ってp型又はn型層112を通過し、p型又はn型層112は第一金属元素含有構造114及び第一半導体層104に電気接続される。幾つかの実施例において、第一接触抵抗率及び第二接触抵抗率は例えば $\cdot \text{cm}^2$ を単位として測定することができる。幾つかの実施例において、p型又はn型層112が第一半導体層104とは異なる又はそれと同じ導電型を有するときに、p型又はn型層112はトンネリング層とされ得る。幾つかの実施例において、p型又はn型層112が第一半導体層104と同じ導電型を有するときに、p型又はn型層112はさらに、第一半導体層104と第一金属元素含有構造114との間のエネルギー・バリア(energy barrier)(例えば、ショットキーバリア(Schottky barrier))を減少させることができる。一実施例において、p型又はn型層112はアクティブ領域108と垂直方向上でオーバーラップしない。一実施例において、第一半導体層104は $1 \times 10^{19}/\text{cm}^3$ 以上のドーパント濃度を有し、これにより、第一半導体層104と第一金属元素含有構造114との間の接触抵抗を低減することができる。

10

20

30

40

### 【0029】

第一半導体層104の材料は伝導帯(conduction band)及び価電子帯(valence band)を有し、そのうち、伝導帯の底縁(bottom edge)はEcで表し、価電子帯の上縁(top edge)はEvで表する。p型又はn型層112の材料は第一仕事関数(work function)WF1を有し、第一金属元素M1は第二仕事関数WF2を有する。幾つかの実施例において、第一半導体層104の導電型がn型であるときに、第一仕事関数WF1は $WF1 = (Ec + Ev)/2$ を満足する。幾つかの実施例において、第一半導体層104の導電型がp型であるときに、第一仕事関数WF1は $WF1 = (Ec + Ev)/2$ を満足する。幾つかの実施例において、p型又はn型層112の導電型がn型であるときに、第二仕事関数WF2は第一仕事関数WF1よりも大きい。幾つかの実施例において、p型又はn型層112の導電型がp型であるときに、第一仕事関数WF1は第二仕事関数WF2よりも大きい。幾つかの実施例において、上述の関係を満たす第一半導体層104、p型又はn型層112及び第一金属元素含有構造114の材料を採用することで、p型又はn型層112と第一金属元素含有構造114との間の接触抵抗率(contact resistivity)をさらに改善することができる。一実施例において、p型又はn型層112の材料は第一半導体層104の材料のバンドギャップよりも大きいバンドギャップ(bandgap)を有し、これにより、p型又はn型層112がアクティブ領域108から発する光を吸収するのを避けることができる。一実施例において、p型又はn型層112の材料は酸素(O)元素及び第五金属元素M5を含む。一実施例において、第五金属元素M5は第一金属元素M1又は第三金属元素M3と同じであり、これにより、p型又はn型層112と第一金属元素含有構造114との間の付着をさらに改善することができ、また、半導体素子10の熱安定性(thermal stability)を向上させることもできる。一実施例において、第五金属元素M5はIn、Ti、Al、Zn、Ni、Ga、Mo、V、W又はNbである。

30

40

50

### 【0030】

p型又はn型層112に含まれる金属元素について、p型又はn型層112には1種類のみの金属元素が含まれても良い。このような金属元素はIn、Ti、Al、Zn、Ni、Ga、Mo、V、W又はNbを含んでも良い。幾つかの実施例において、p型又はn型層112は2種類又は2種類以上の金属元素を含む。例を挙げて言えば、一実施例において、p型又はn型層112はさらに、第五金属元素M5とは異なる第六金属元素M6を含んでも良い。第五金属元素M5及び第六金属元素M6はそれぞれIn、Ti、Al、Zn、Ni、Ga、Mo、V、W又はNbであり得る。一実施例において、p型又はn型層112はさらに5族元素(例えば、N、P又はAs)を含む。具体的に言えば、一実施例において、p型又はn型層112は酸素元素及び第五金属元素M5により形成される第一金属酸化物(metal oxide compound)を含んでも良い。一実施例において、p型又はn型層112はさらに、酸素元素及び第六金属元素M6により形成される第二金属酸化物を含み得る。一実施例において、p型又はn型層112はさらに、酸素元素及び5族元素により形成される第三金属酸化物を含んでも良い。例を挙げて言えば、第一金属酸化物又は第二金属酸化物はn型(例えば、 $\text{TiO}_x$ 、 $\text{InO}_x$ 、 $\text{MoO}_x$ 、 $\text{VO}_x$ 、 $\text{WO}_x$ 、 $\text{GaO}_x$ 、又は $\text{NbO}_x$ )又はp型(例えば、 $\text{NiO}_x$ )であり得る。第三金属酸化物

はPO<sub>x</sub>、NO<sub>x</sub>又はAsO<sub>x</sub>であっても良い。一実施例において、p型又はn型層112は0nmよりも大きくかつ20nm以下の厚さを有する。例を挙げて言えば、p型又はn型層112の厚さは0.5nm乃至15nmの範囲内にあっても良く、例えば、1nm、2nm、3nm、4nm、5nm、6nm、7nm、8nm、9nm、10nm、11nm、12nm、13nm又は14nmである。幾つかの実施例において、p型又はn型層112の厚さが5nm以下のときに、第一金属元素含有構造114と第一半導体層104との間の接触抵抗率はトンネリング効果(tunneling effect)により改善することができる。

#### 【0031】

幾つかの実施例において、第一半導体層104がリン化物又はヒ化物を含むときに、p型又はn型層112の存在は、第一半導体層104が第一金属元素含有構造114に直接接觸することが原因で界面化合物(interfacial compound)を形成するのを避けることができる。例を挙げて言えば、第一金属元素含有構造114がAuを含み、第一半導体層104がリン化物(例えば、GaP)であるときに、上述の界面化合物はAu<sub>2</sub>P<sub>3</sub>であり得る。それは、バンドギャップエネルギー(bandgap energy)がアクティブ領域108の材料のバンドギャップエネルギーよりも小さいため、アクティブ領域108から発する光を吸収することができる。

10

#### 【0032】

図2Aは本開示の一実施例における半導体素子20の上面図である。図2Bは図2Aに示す半導体素子20のX-X'線に沿った断面構造を示す図である。図示をより明確にするために、図2Aでは説明に必要なコンポーネントのみ(図中で符号が付いているように)が示されている。

20

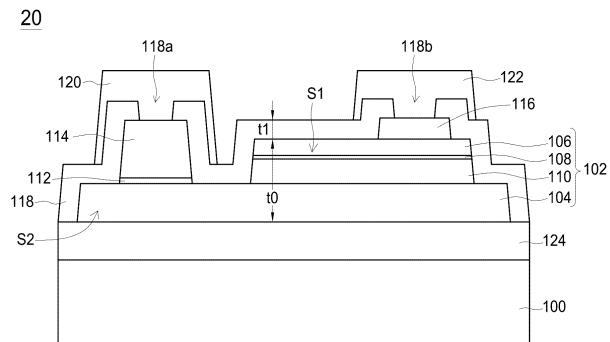

#### 【0033】

半導体素子20と半導体素子10との間の相違点は、半導体素子20はさらに、半導体構造102上に位置する絶縁構造118、第一金属元素含有構造114に接続される第一電極パッド120、第二金属元素含有構造116に接続される第二電極パッド122、及び第一半導体層104の下に位置する接合構造124を含むことにある。一実施例において、絶縁構造118はほぼ共形で半導体構造102、第一金属元素含有構造114、及び第二金属元素含有構造116を覆う。図2Bに示すように、絶縁構造118は第一開口118a及び第二開口118bを有する。第一金属元素含有構造114は第一開口118aにより第一電極パッド120に直接接觸し、第二金属元素含有構造116は第二開口118bにより第二電極パッド122に直接接觸する。

30

#### 【0034】

第一電極パッド120及び第二電極パッド122は外部電源(図示せず)に電気接続するために用いられ、かつ緩衝(バッファ)として例えばワイヤ接合(wire-bonding)やはんだ接合(solder bonding)などの製造プロセスにおいて生じた応力(stress)を吸収するために用いられる。第一電極パッド120の上表面及び第二電極パッド122の上表面は実質的に同一水平面に位置しても良い(約±1μmの誤差(tolerance)を有しても良い)。一実施例において、第一電極パッド120は絶縁構造118の一部を覆い、かつ第一開口118aに充填され、第二電極パッド122は絶縁構造118の一部を覆い、かつ第二開口118bに充填される。幾つかの実施例において、第一メサ構造S1、絶縁構造118及び第一電極パッド122は垂直方向上でオーバーラップしても良い。第一電極パッド120及び第二電極パッド122はそれぞれ単層又は多層であっても良い。一実施例において、第一電極パッド120及び第二電極パッド122の材料はNi、Ti、Pt、Pd、Ag、Au、Al、Sn又はCuを含み、又は、これらの元素を含む合金であり得る。

40

#### 【0035】

絶縁構造118は半導体構造102を湿気又は汚染から保護することができ、かつ半導体素子20の信頼性(reliability)を改善することができる。一実施例において、絶縁構造118は誘電材料、例えば、酸化物(例えば、SiO<sub>2</sub>)又は窒化物(例えば、SiN<sub>x</sub>)を含む。一実施例において、絶縁構造118は反射構造、例えば、交互にスタックされる、異なる屈折率を有する2種類以上の半導体材料により形成される分布プラグ反射鏡(distribute

50

d Bragg reflector、DBR)を含み得る。一実施例において、絶縁構造118は厚さt1を有し、厚さt1は半導体構造102の総厚さt0の15%より小さく又は10%よりも小さくても良い。

#### 【0036】

接合構造124は電気絶縁(electrically-insulative)構造であっても良い。一実施例において、接合構造124は熱硬化性ポリマー(thermosetting polymer)を含む主層(main layer)(図示せず)を有する。一実施例において、このような熱硬化性ポリマーはpolyimide、epoxy resin、polyester、polyurethane、benzocyclobutene(BCB)又はその組み合わせを含み得る。一実施例において、接合構造124はさらに、主層と第一半導体層104との間、あるいは、主層とベース100との間に位置する輔助層(auxiliary layer)(図示せず)を有し、これにより、両者間の付着をさらに改善することができる。輔助層の材料は主層の材料とは異なっても良い。一実施例において、輔助層の材料は酸化物(例えば、 $\text{SiO}_2$ )又は窒化物(例えば、 $\text{SiN}_x$ )を含む。なお、他の各層又は構造の位置、相対関係及び材料成分などの内容及び構造の変化例について、前の実施例で詳細に説明したので、ここではその詳しい説明を省略する。

10

#### 【0037】

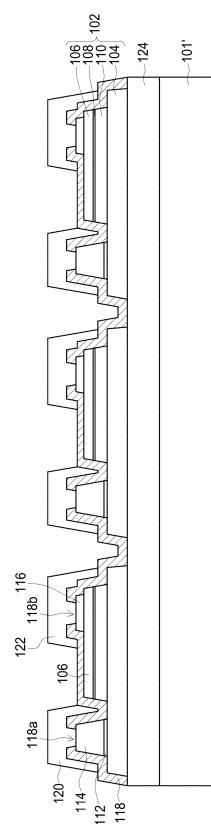

図3A乃至図3Jは本開示の一実施例における半導体素子30Aの製造方法を示す図である。理解すべきは、製造プロセスにおいて複数の半導体素子を形成し得るが、便宜のため、以下、主に单一半導体素子の製造プロセスにおける構造の変化に基づいて説明を行うということである。

20

#### 【0038】

図3Aに示すように、まず、成長基板101を提供する。成長基板101上に半導体スタック層102'を形成する。半導体スタック層102'は第一半導体層104、第二半導体層106、及び第一半導体層104と第二半導体層106との間に位置するアクティブ領域108を含む。第一半導体層104とアクティブ領域108との間に第三半導体層110が形成されている。

#### 【0039】

その後、図3B及び図3Cに示すように、接合構造124により半導体スタック層102'を接合基板101'に接合し、そして、成長基板101を除去する。

30

#### 【0040】

続いて、図3Dに示すように、図3Cに示す構造を反転し、かつ一部の半導体スタック層102'を除去することで、一部の第一半導体層104を露出させ、そして、第一半導体層104上に第一メサ構造S1を形成する。

#### 【0041】

その後、図3Eに示すように、第一半導体層104の露出した部分にp型又はn型層112を形成し、そして、このp型又はn型層112上に第一金属元素含有構造114を形成する。一実施例において、p型又はn型層112は薄膜堆積(film deposition)方式、例えば、原子層堆積 atomic layer deposition、ALD)又は電子ビーム蒸着(e-gun evaporation)により形成され得る。

40

#### 【0042】

一実施例において、第一金属元素含有構造114の形成はp型又はn型層112上に第一金属元素M1を含む構造を形成し、また、第一温度で加熱を行う第一加熱ステップを含む。一実施例において、加熱ステップは合金製造プロセスであっても良く、例えば、第一金属元素M1及び他の金属元素(例えば、前述の第三金属元素M3)を含む合金を形成するための製造プロセスである。第一温度は設備(例えば、ボイラーパイプ(furnace))が第一加熱ステップに対して提供する環境温度であっても良い。一実施例において、第一温度は接合構造124に含まれる熱硬化性ポリマーの熱分解温度よりも小さくても良く、又は、第一温度と前述の熱分解温度との差は50°C以下又は30°C以下であっても良く、これにより、製造プロセスの安定性(process stability)を確保することができる。前述の熱分解温度は前述の熱硬化性ポリマーの1時間内の重量損失(weight loss)が1%を超えたときの

50

温度であっても良い。

#### 【 0 0 4 3 】

図3F及び図3Gに示すように、さらに、第一メサ構造S1上に第二金属元素含有構造116を形成し、また、一部の第一半導体層を除去することで第二メサ構造S2を形成する。第二金属元素含有構造116の形成は、第二半導体層106上に第二金属元素M2を含む構造を形成し、また、第二温度で加熱を行う第二加熱ステップを含んでも良い。第二温度は設備(例えば、ボイラーパイプ)が第二加熱ステップに対して提供する環境温度であっても良い。一実施例において、第一温度と第二温度との差は50°Cよりも小さく又は30°Cよりも小さくても良い。一実施例において、第一温度及び第二温度はそれぞれ500°Cよりも小さく又は400°Cよりも小さくても良い。一実施例において、第一温度及び第二温度はそれぞれ200°C以上又は300°C以上であっても良い。

10

#### 【 0 0 4 4 】

図3Hに示すように、続いて、第一メサ構造S1、第二メサ構造S2、第一金属元素含有構造114及び第二金属元素含有構造116上に共形で絶縁構造118を形成する。第一メサ構造S1及び第二メサ構造S2の側壁はすべて絶縁構造118により覆われ、これにより、半導体構造102を完全に保護することができる。一部の絶縁構造118を除去することで第一開口118a及び第二開口118bを形成する。

#### 【 0 0 4 5 】

続いて、図3Iに示すように、第一金属元素含有構造114上に第一電極パッド120を形成し、また、第二金属元素含有構造116上に第二電極パッド122を形成する。

20

#### 【 0 0 4 6 】

図3Iに示す構造はさらに、切断方法、例えば、レーザー切断(laser cutting)により複数の半導体素子30Aに分離することができる。図3Jには各半導体素子30Aの構造が示されている。

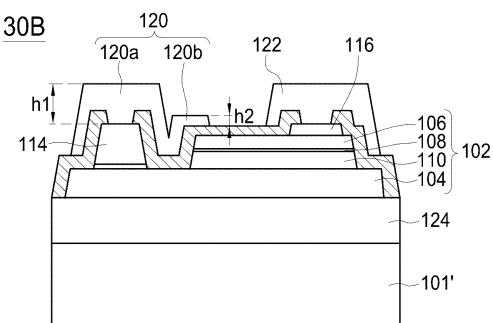

#### 【 0 0 4 7 】

図3Kは本開示の一実施例における半導体素子30Bの断面構造を示す図である。図3Kに示すように、一実施例において、第一電極パッド120は一部の第一メサ構造S1上に形成することもでき、これにより、半導体素子の構造強度を改善することができる。一実施例において、第一電極パッド120は変化ありの厚さを有しても良く、又は、第一電極パッド120は非平坦(non-planar)の上表面を有しても良い。図3Kに示すように、第一電極パッド120は第一部120a及び第二部120bを含んでも良く、第一部120aは第一金属元素含有構造114上に位置し、かつ第一厚さh1を有し、第二部120bは第一メサ構造S1上に位置し、かつ第二厚さh2を有し、第二厚さh2は第一厚さh1よりも小さくても良い。

30

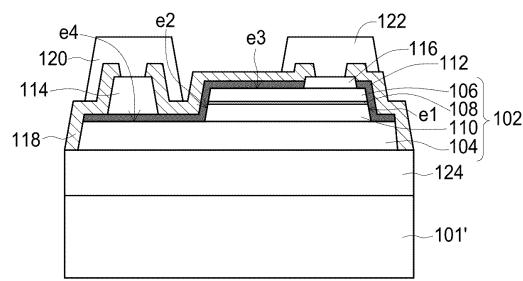

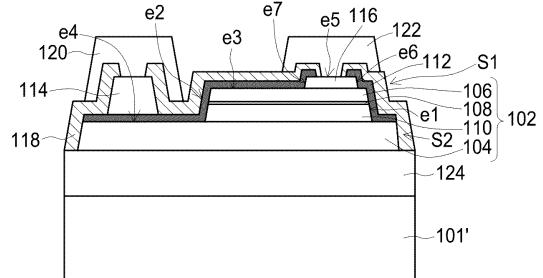

#### 【 0 0 4 8 】

図3Lは本開示の一実施例における半導体素子30Cの断面構造を示す図である。図3Lに示すように、p型又はn型層112はほぼ共形で半導体構造102の上表面に形成される。一実施例において、p型又はn型層112は第一金属元素含有構造114、第二金属元素含有構造116及び絶縁構造118に直接接触する。具体的に言えば、図3Lに示すように、p型又はn型層112は第一メサ構造S1の第一側表面e1、第二側表面e2及び上表面e3、並びに第二メサ構造S2の上表面e4を覆い、かつそれらに直接接触する。一実施例において、p型又はn型層112は第一半導体層104の側壁を覆わない。p型又はn型層112は第二金属元素含有構造116に直接接触し、かつ第二金属元素含有構造116と垂直方向上でオーバーラップしなくても良い。一実施例において、水平方向に比べて、p型又はn型層112は垂直方向上で比較的低い接触抵抗率を有するので、半導体素子30Cがワーキングするときに、第二金属元素含有構造116と第一金属元素含有構造114との間、あるいは、第二金属元素含有構造116と第一半導体層104との間に電流経路(current path)を形成することができない。図3Mは本開示の一実施例における半導体素子30Dの断面を示す図である。図3Mに示すように、p型又はn型層112はさらに、第二金属元素含有構造116の上表面e5の一部、第三側表面e6及び第四側表面e7を覆っても良く、これにより、第二電極パッ

40

50

ド122は第二金属元素含有構造116においてp型又はn型層112により覆われない上表面e5の部分に直接接触し得る。図3Mに示す構造を形成するために、製造プロセスにおいて、先に第一メサ構造S1上に第二金属元素含有構造116を形成し、その後、第一メサ構造S1及び第二金属元素含有構造116の一部上に位置するp型又はn型層112を形成し、それから、p型又はn型層112上に第一金属元素含有構造114を形成する。

#### 【0049】

なお、他の各層又は構造の位置、相対関係及び材料成分などの内容及び構造の変化例について、前の実施例で詳細に説明したので、ここではその詳しい説明を省略する。

#### 【0050】

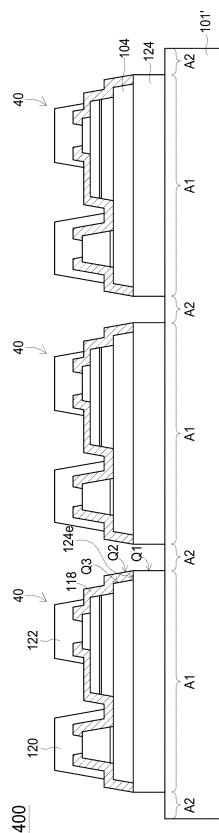

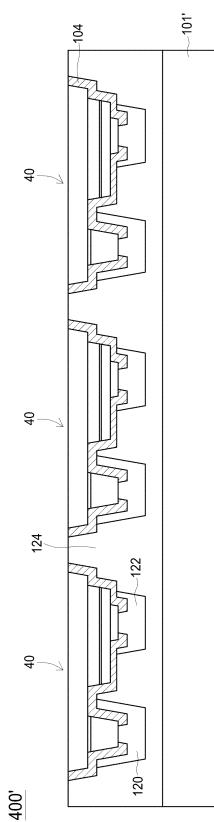

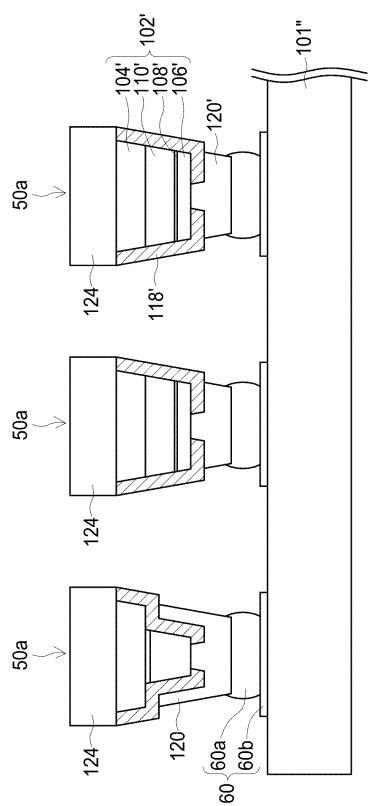

図4Aは本開示の一実施例における半導体装置400の断面構造を示す図である。図4Bは本開示の一実施例における半導体装置400'の断面構造を示す図である。 10

#### 【0051】

図4A及び図4Bに示すように、半導体装置400又は半導体装置400'は複数の半導体素子40を含む。図4Aにおける各半導体素子40の構造は前述の半導体素子30Aの構造と類似している。具体的に言えば、半導体素子40は本開示の任意の1つの実施例に記載の半導体素子(例えば、半導体素子10、20、30B、30C又は30D)であっても良い。

#### 【0052】

図4A及び図4Bでは、半導体素子40は成長基板101を有しない。図4Aに示すように、複数の半導体素子40は接合基板101'上に配置される。一実施例において、接合基板101'は第一領域A1及び第二領域A2を含み、第一領域A1は接合構造124により覆われ、第二領域A2は接合構造124により覆われない。具体的に言えば、第一領域A1及び半導体素子40は垂直方向上でオーバーラップしている。即ち、図4Aでは、接合構造124は接合基板101'上に連続して分布しているのではない。図4Aでは、接合構造124は上縁(upper edge)124e及び側壁Q1を有し、絶縁構造118は上縁を覆うが、側壁Q1を覆わない。一実施例において、絶縁構造118は側壁Q1と垂直方向上でオーバーラップする側壁Q2を有する。側壁Q1及び第一半導体層104の側壁Q3は垂直方向上でオーバーラップしない。一実施例では、接合構造124において上縁に近い上表面は絶縁構造118により覆われない。一実施例において、接合構造124は第一半導体層104の幅以下の幅を有する。 20

#### 【0053】

図4Bはもう1つの配置方式を示しており、そのうち、複数の半導体素子40は接合構造124に埋め込まれている。そのうち、接合構造124は接合基板101'上に連続して分布しており、かつ複数の半導体素子40に直接接触する。幾つかの実施例において、接合構造124は半導体素子40を所定位置に固定することに有利であり、輸送プロセスでは半導体素子40内の半導体構造102を守ることができる。 30

#### 【0054】

一実施例において、半導体素子40と接合基板101'との間にブルーテープ(blue tape)、サーマルリリースシート又はテープ(thermal release sheet or tape)、あるいは(UV)ライトリリーステープ(light release tape)(例えば、polyethylene terephthalate、PET))を設置しても良い。具体的に言えば、ブルーテープ、サーマルリリースシート又はテープ、あるいは(UV)ライトリリーステープは接合構造124と接合基板101'との間に設置しても良く、あるいは、半導体素子40の第一電極パッド120及び第二電極パッド122に直接接触して覆っても良い。 40

#### 【0055】

なお、他の各層又は構造の位置、相対関係及び材料組成など内容及び構造の変化例について、前の実施例で詳細に説明したので、ここではその詳しい説明を省略する。

#### 【0056】

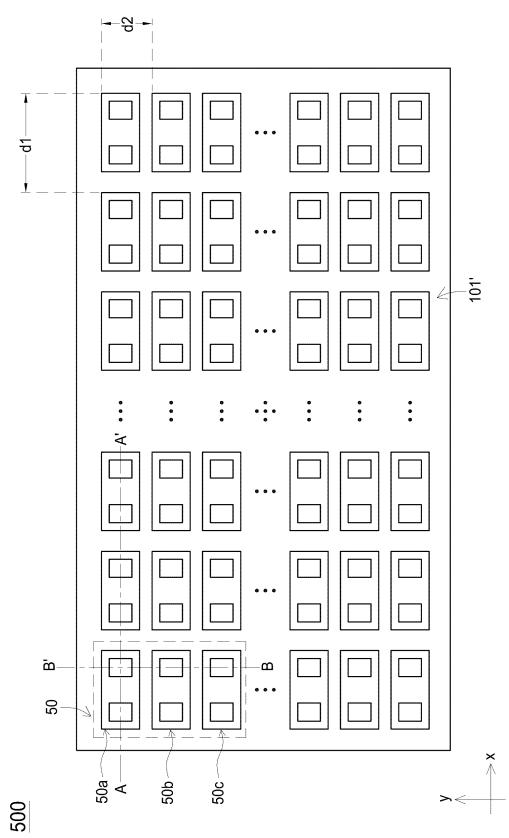

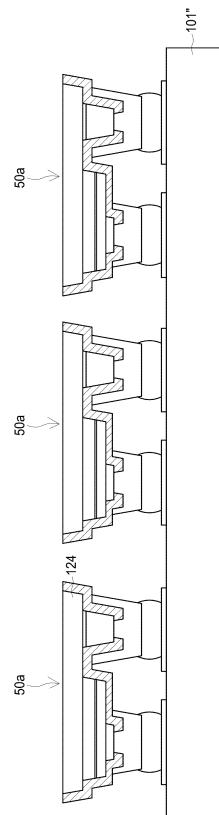

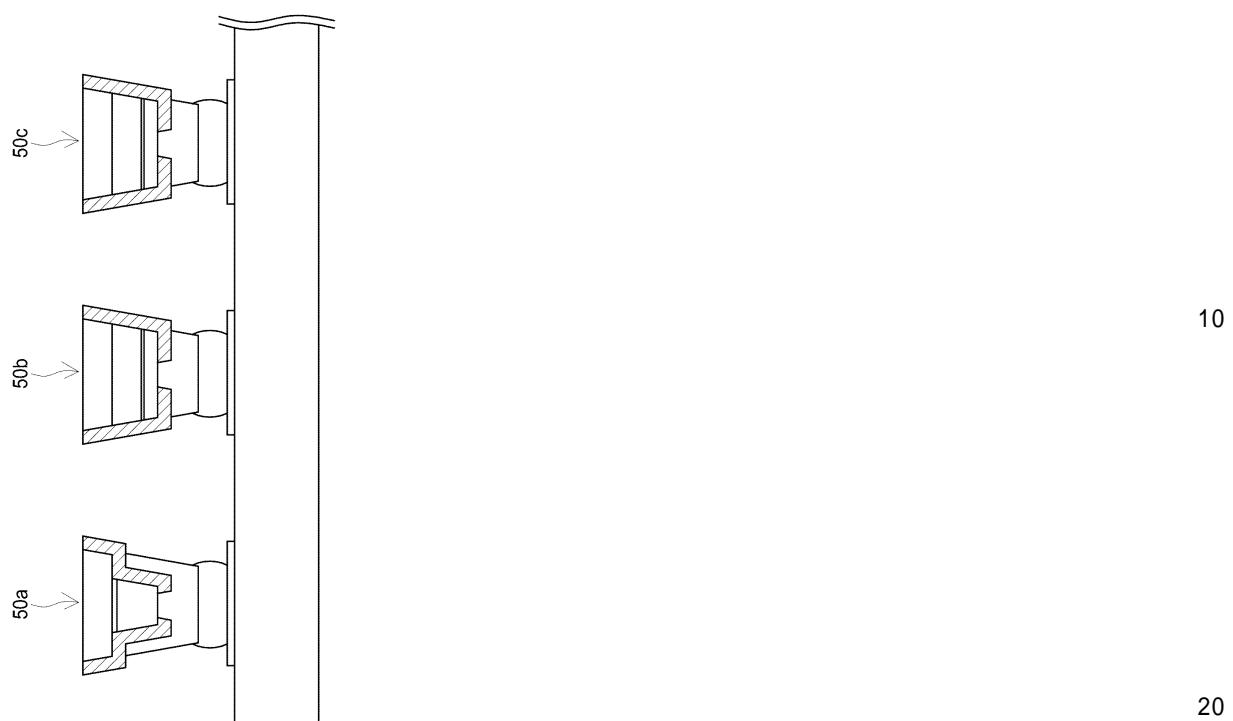

図5Aは本開示の一実施例における表示パネル500の上面図である。図5B及び図5Cは本開示の一実施例における表示パネル500の一部の断面構造を示す図である。具体的に言えば、図5Bは図5AのA-A'線に沿った断面を示す図であり、図5Cは図5AのB-B'線に沿った断面を示す図である。 50

### 【 0 0 5 7 】

一実施例において、表示パネル500はキャリア基板101”及びキャリア基板101”上に位置する複数の画素ユニット50を含む。複数の画素ユニット50は行方向(row direction)x及び列方向(column direction)yに沿って配列される。複数の画素ユニット50はトランスファー(transfer)方法によりキャリア基板101”上に形成することができる。キャリア基板101”はガラス、プラスチック(plastic)、シリコン基板(silicon substrate)又はプリント回路板(printed circuit board、PCB)であり得る。各画素ユニット50は複数の半導体素子を含む。一実施例において、各画素ユニット50は3つの半導体素子、即ち、半導体素子50a、半導体素子50b及び半導体素子50cを含む。具体的に言えば、この実施例では、半導体素子50a、半導体素子50b及び半導体素子50cは行方向x上で第一間隔d1を空けて設置され、列方向y上で第二間隔d2を空けて設置される。10 一実施例において、第一間隔d1は100 μm以下であり、第二間隔d2は50 μm以下である。半導体素子50a、半導体素子50b及び半導体素子50cはそれぞれ異なる波長範囲の光を発することができる。例を挙げて言えば、半導体素子50a、半導体素子50b及び半導体素子50cはそれぞれ赤色光、緑色光及び青色光を発し得る。さらに、キャリア基板101”上に駆動回路(driving circuit)及び制御ユニット(control unit)(図示せず)を設けることで、画素ユニット50を駆動し、画素ユニット50の発光時間を制御することもできる。

### 【 0 0 5 8 】

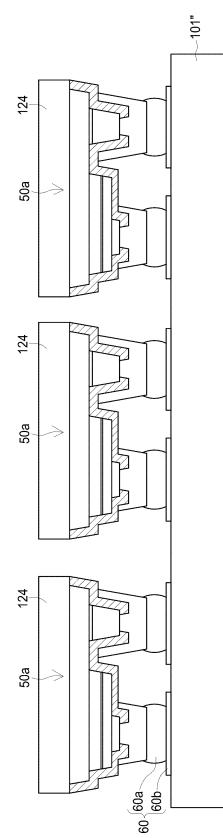

図5B及び図5Cに示すように、各半導体素子50a、半導体素子50b及び半導体素子50cは接触構造60によりキャリア基板101”に電気接続される。接触構造60は接続層(connection layer)60a及び回路電極(circuit electrode)60bを含む。一実施例において、半導体素子50aは本開示の任意の1つの実施例に記載の半導体素子(例えば、半導体素子10、20、30A、30B、30C又は30D)であっても良く、半導体素子50b及び半導体素子50cは半導体素子50aとは異なる構造を有しても良い。20

### 【 0 0 5 9 】

図5Cに示すように、各半導体素子50b及び半導体素子50cは半導体スタック層102’、絶縁構造118及び電極パッド120を含む。半導体スタック層102’は第一半導体層104’、第二半導体層106’、第一半導体層104’と第二半導体層106’との間に位置するアクティブ領域108’、及び第一半導体層104’とアクティブ領域108’との間に位置する第三半導体層110’を有する。絶縁構造118は半導体スタック層102’の側壁及び一部の表面を覆う。電極パッド120’は半導体スタック層102’に電気接続される。幾つかの実施例において、アクティブ領域108’は電極パッド120’とオーバーラップし、電極パッド120はアクティブ領域108とオーバーラップしても良く、又は、オーバーラップしてなくても良い(図示せず)。30 一実施例において、アクティブ領域108’の材料はアクティブ領域108の材料とは異なる。例を挙げて言えば、アクティブ領域108’はN元素を含み、アクティブ領域108はAs元素又はP元素を含む。一実施例において、さらに、第二半導体層106’と電極パッド120’との間に導電層(図示せず)を設置しても良い。この導電層は導電酸化物、例えば、ITOを含んでも良い。

### 【 0 0 6 0 】

図5D及び図5Eは本開示のもう1つの実施例における表示パネル500の一部の断面構造を示す図である。具体的に言えば、図5Dは図5AのA-A’線に沿った断面図を示しており、図5Eは図5AのB-B’線に沿った断面図を示している。一実施例において、半導体素子50a、半導体素子50b及び半導体素子50cは接合構造124を有せず、これにより、各半導体素子の厚さをさらに減少させることができる。40

### 【 0 0 6 1 】

なお、他の各層又は構造の位置、相対関係及び材料成分などの内容及び構造の変化例について、前の実施例で詳細に説明したので、ここではその詳しい説明を省略する。

### 【 0 0 6 2 】

上述によれば、本開示では半導体素子、半導体素子の製造方法、半導体装置又は表示パ50

ネルが提供される。本開示により提供される半導体素子は、光電特性、例えば、接触抵抗(contact resistance)及びプロセス安定性(process stability)の面において向上している。具体的に言えば、本開示による半導体素子又は半導体装置は様々な分野、例えば、照明、医療、表示、通信、センシング、電源システムなどの分野における製品、例えば、灯具、モニター、携帯電話、タブレットパソコン、自動車用計器盤、テレビ、コンピューター、ウェアラブルデバイス(時計、プレスレット、ネックレスなど)、交通標識、屋外ディスプレイデバイス、医療デバイスなどに適用することができる。

#### 【0063】

本開示は、前述した好適な実施例に基づいて以上のように説明されたが、前述した好適な実施例は、本開示を限定するためのものでなく、当業者は、本開示の精神と範囲を離脱しない限り、本開示に対して些細な変更と潤色を行うことができるので、本開示の保護範囲は、添付した特許請求の範囲に定まったものを基準とする。また、本開示の何れの実施例又は特許請求の範囲は、本開示に開示された全ての目的又は利点又は特徴を達成する必要がない。例えば、一実施例で開示された特定の構成要素の関連パラメータや特定の構成要素と他の構成要素との接続関係は他の実施例に適用することができ、かつそのすべては本開示の保護範囲に属する。また、要約の一部及び発明の名称は、文献の検索を助けるためのみのものであり、本開示の権利範囲を限定するものではない。また、本明細書又は特許請求の範囲に言及されている「第一」、「第二」などの用語は、要素に名前を付け、又は、異なる実施例又は範囲を区別するためのもののみであり、要素の数量上の上限又は下限を限定するためのものでない。

10

20

30

40

50

#### 【符号の説明】

#### 【0064】

10、20、30A、30B、30C、30D、40、50a、50b、50c：半導体素子

100：ベース

101：成長基板(growth substrate)

101'：接合基板(bonding substrate)

101"：キャリア基板(carrier substrate)

102：半導体構造

102'：半導体スタック層

104：第一半導体層

104a：第一表面

104b：第二表面

106：第二半導体層

108：アクティブ領域(active region)

110：第三半導体層

112：p型又はn型層(接触層)

114：第一金属元素含有構造

116：第二金属元素含有構造

118：絶縁構造

118a：第一開口

118b：第二開口

120：第一電極パッド

120'：電極パッド(electrode pad)

120a：第一部

120b：第二部

122：第二電極パッド

124：接合構造

124e：上縁

400、400'：半導体装置

50：画素ユニット

60 : 接触構造

60a : 接続層

60b : 回路電極

500 : 表示パネル

A1 : 第一領域

A2 : 第二領域

d1 : 第一間隔

d2 : 第二間隔

e1 : 第一侧表面

e2 : 第二侧表面

e3、e4、e5 : 上表面

e6 : 第三侧表面

e7 : 第四侧表面

h1 : 第一厚さ

h2 : 第二厚さ

P1 : 第一部分

P2 : 第二部分

Q1、Q2、Q3 : 側壁

S1 : 第一メサ構造 (first mesa structure)

S2 : 第二メサ構造 (second mesa structure)

10

## 【図面】

【図1】

10

【図2A】

20

30

40

50

【図2B】

【図3A】

20

20

30

40

【図3B】

【図3C】

50

【図3D】

【図3E】

10

20

30

40

50

【図3F】

【図3G】

【図3H】

【図3I】

10

20

30

【図3J】

【図3K】

40

50

【図3L】

30C

【図3M】

30D

10

【図4A】

【図4B】

20

30

40

50

【図 5 A】

【図 5 B】

10

20

30

40

【図 5 C】

【図 5 D】

50

【図5E】

40

50

---

フロントページの続き

(72)発明者 シエ , ミン - シュン

台湾 シンチュ シティ , サイエンス - ベースド インダストリアル パーク , リ - シン ロード 21

(72)発明者 リー , ユ - ツ

台湾 シンチュ シティ , サイエンス - ベースド インダストリアル パーク , リ - シン ロード 21

(72)発明者 シュエ , ウェイ - ジエン

台湾 シンチュ シティ , サイエンス - ベースド インダストリアル パーク , リ - シン ロード 21

F ターム (参考) 5F241 AA31 CA04 CA36 CA37 CA39 CA40 CA65 CA76 CA85 CA86

CA87 CA92 CB11 CB36 FF01