(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7206130号**

**(P7206130)**

(45)発行日 令和5年1月17日(2023.1.17)

(24)登録日 令和5年1月6日(2023.1.6)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 13/38 (2006.01) | F I | G 0 6 F | 13/38 | 3 2 0 A |

| G 0 6 F | 3/08 (2006.01)  |     | G 0 6 F | 3/08  | H       |

| G 0 6 F | 13/10 (2006.01) |     | G 0 6 F | 13/10 | 3 1 0 E |

|         |                 |     | G 0 6 F | 13/38 | 3 5 0   |

請求項の数 14 (全15頁)

(21)出願番号 特願2019-34566(P2019-34566)

(22)出願日 平成31年2月27日(2019.2.27)

(65)公開番号 特開2019-160307(P2019-160307

A)

(43)公開日 令和1年9月19日(2019.9.19)

審査請求日 令和4年1月28日(2022.1.28)

(31)優先権主張番号 62/641,246

(32)優先日 平成30年3月9日(2018.3.9)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 16/020,923

(32)優先日 平成30年6月27日(2018.6.27)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路12

9

129, Samsung-ro, Yeo

ngtong-gu, Suwon-si

, Gyeonggi-do, Repub

lic of Korea

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(74)代理人 100091214

最終頁に続く

(54)【発明の名称】 適応型インターフェイスストレージ装置

**(57)【特許請求の範囲】****【請求項1】**

第1コネクターと、

前記第1コネクターに接続された第1回路と、

前記第1回路に接続された第2回路と、

前記第2回路に接続された第2コネクターと、

を含み、

前記第1回路は、第1エンドポイントおよび第2エンドポイントを含み、

前記第2回路は、第1マルチプレクサーであって、

第1マルチプレクサーチャンネルであり、

前記第2コネクターに接続された、第1マルチプレクサーチャンネル共通ポートと、

前記第1エンドポイントに接続された、第1マルチプレクサーチャンネル第1選択可能ポートと、

接続されていない、第1マルチプレクサーチャンネル第2選択可能ポートと、

を有する、第1マルチプレクサーチャンネルと、

第2マルチプレクサーチャンネルであり、

前記第2コネクターに接続された、第2マルチプレクサーチャンネル共通ポートと、

前記第1エンドポイントに接続された、第2マルチプレクサーチャンネル第1選択可能ポートと、

前記第2エンドポイントに接続された第2マルチプレクサーチャンネル第2選択可能

10

20

ポートと、

を有する、第2マルチプレクサーチャンネルと、

を含む、装置であって、

前記装置は、第1状態または第2状態で動作するように構成されており、

前記第1状態では、前記第1マルチプレクサーチャンネル第1選択可能ポートが選択され、かつ、前記第2マルチプレクサーチャンネル第1選択可能ポートが選択されており、

前記第2状態では、前記第1マルチプレクサーチャンネル第1選択可能ポートが選択され、かつ、前記第2マルチプレクサーチャンネル第2選択可能ポートが選択されており、

前記装置は、

前記第1状態において、前記第2コネクターで、第1プロトコルに従って第1インターフェイスを提供し、かつ、

前記第2状態において、前記第2コネクターで、前記第1プロトコルとは異なる第2プロトコルに従って、第2インターフェイスを提供する、

ように構成されている、

装置。

#### 【請求項2】

前記第1プロトコルは、NVMeである、

請求項1に記載の装置。

#### 【請求項3】

前記第2プロトコルは、NVMeoF(NVMe over Fabrics)である、

請求項2に記載の装置。

#### 【請求項4】

前記装置は、さらに、前記第2状態において、前記第2コネクターで、第1制御ブレインインターフェイスを提供するように構成されている、

請求項1に記載の装置。

#### 【請求項5】

前記第1エンドポイントは、4レーンエンドポイントであり、

前記第2エンドポイントは、4レーンエンドポイントであり、かつ、

前記第1マルチプレクサーチャンネル共通ポートおよび前記第2マルチプレクサーチャンネル共通ポートは、合わせて、2つの入力レーンおよび2つの出力レーンを有する、

請求項1に記載の装置。

#### 【請求項6】

前記第1回路は、プログラマブル適応可能回路であり、構成ポートを有し、かつ、システム開始の時に、前記構成ポートを通じてビットファイルをロードするように構成されている、

請求項1に記載の装置。

#### 【請求項7】

前記装置は、さらに、

第1ビットファイルメモリと、

第2ビットファイルメモリと、

第2マルチプレクサーと、

を含み、

前記第2マルチプレクサーは、

前記構成ポートに接続された第2マルチプレクサー共通ポートと、

前記第1ビットファイルメモリに接続された第2マルチプレクサーの第1選択可能ポートと、

前記第2ビットファイルメモリに接続された第2マルチプレクサーの第2選択可能ポートと、

前記第2ビットファイルメモリに接続された第2マルチプレクサーの第2選択可能ポートと、

を有する、

請求項6に記載の装置。

10

20

30

40

50

**【請求項 8】**

前記第1状態では、前記第2マルチプレクサーの第1選択可能ポートが選択され、かつ、前記第2状態では、前記第2マルチプレクサーの第2選択可能ポートが選択される、請求項7に記載の装置。

**【請求項 9】**

前記第2コネクターは、U . 2コネクターである、

請求項1に記載の装置。

**【請求項 10】**

前記装置は、さらに、

前記第1状態と前記第2状態との間を選択するための信号を受信するように構成されて

いる状態制御入力、

を含む、請求項1に記載の装置。

**【請求項 11】**

前記第2コネクターは、E 6ピンを有するU . 2コネクターであり、かつ、

前記状態制御入力は、前記E 6ピンである、

請求項10に記載の装置。

**【請求項 12】**

前記装置は、

前記第1状態では、前記第2コネクターで、装置側N V M eストレージインターフェイスを提供し、かつ、

前記第2状態では、前記第2コネクターで、装置側N V M e o Fストレージインターフェイスを提供する、

のように構成されている、

請求項1に記載の装置。

**【請求項 13】**

シャーシと、

請求項1乃至12いずれか一項に記載の装置と、

を含む、システム。

**【請求項 14】**

前記装置は、さらに、前記第1状態と前記第2状態との間を選択するための信号を受信するように構成されている状態制御入力を含み、かつ、

前記シャーシは、前記第1状態を選択する信号を前記状態制御入力へ供給するようにハードウェア処理されている、

請求項13に記載のシステム。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は永久ストレージに関する。さらに詳細には、構成可能なストレージインターフェイスを有するストレージ装置に関する。

**【背景技術】****【0 0 0 2】**

永久ストレージ装置は、多様なアプリケーションで使用されることができ、多様なインターフェイスと共に動作される。幾つかのアプリケーションで、多数の異なるインターフェイスが使用されるシステムにおいて異なるストレージインターフェイスをサポートするストレージ装置の在庫を維持することは不都合な可能性がある。

**【0 0 0 3】**

従って、異なるストレージインターフェイスで動作することができるストレージ装置が必要である。

**【先行技術文献】****【特許文献】**

10

20

30

40

50

**【0004】**

【文献】米国特許第9,767,856号公報

米国特許第9,798,636号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

本発明の目的は、異なるストレージインターフェイスで動作することができるストレージ装置を提供することである。

**【課題を解決するための手段】****【0006】**

本発明の実施形態によれば、後端ストレージインターフェイスコネクターと、後端ストレージインターフェイスコネクターと連結される適応可能(adaptive)回路と、適応可能回路と連結される第1ルーティング回路と、第1マルチプレクサーと連結される前端ストレージインターフェイスコネクターと、を含み、第1状態又は第2状態で動作し、第1状態において前端ストレージインターフェイスコネクターで第1ストレージプロトコルに従って第1装置側ストレージインターフェイスを提供し、第2状態において前端ストレージインターフェイスコネクターで第1ストレージプロトコルとは異なる第2ストレージプロトコルに従って第2装置側ストレージインターフェイスを提供する、ように構成される適応型インターフェイスストレージ装置が提供される。

**【0007】**

一実施形態で、適応型インターフェイスストレージ装置は、第1PCIe(Peripheral Component Interconnect express)エンドポイント(end point)及び第2PCIeエンドポイントを含み、第1ルーティング回路は、前端ストレージインターフェイスコネクターと連結される第1マルチプレクサーチャンネル共通ポートを有する第1マルチプレクサーチャンネル、及び前端ストレージインターフェイスコネクターと連結される第2マルチプレクサーチャンネル共通ポート、第1PCIeエンドポイントと連結される第1選択可能(selectable)ポート、及び第2PCIeエンドポイントと連結される第2選択可能ポートを有する第2マルチプレクサーを含む第1マルチプレクサーである。

**【0008】**

一実施形態で、第1マルチプレクサーチャンネルは、第1PCIeエンドポイントと連結される第3選択可能ポートを有する。

**【0009】**

一実施形態で、第1マルチプレクサーチャンネルは、連結されない状態である第4選択可能ポートを有し、第1状態において第3選択可能ポートが選択され、第2状態において3選択可能ポートが選択される。

**【0010】**

一実施形態で、第1ストレージプロトコルは、NVMeである。

**【0011】**

一実施形態で、適応可能回路は、前端ストレージインターフェイスコネクターの第1複数のコンダクターに連結され、第2状態で適応可能回路は、第1複数のコンダクターでイーサーネットインターフェイスを提供するように構成される。

**【0012】**

一実施形態で、第2ストレージプロトコルは、イーサーネットインターフェイス上のNVMeoF(NVMe over Fabrics)である。

**【0013】**

一実施形態では、第1状態において、第1選択可能ポートが選択される。

**【0014】**

一実施形態では、第2状態において、第2選択可能ポートが選択される。

**【0015】**

10

20

30

40

50

一実施形態では、第2状態において、前端ストレージインターフェイスコネクターでPCIe制御プレーン(plane)を提供するようにさらに構成される。

**【0016】**

一実施形態で、第1PCIエンドポイントは、4レーンPCIeエンドポイントであり、第2PCIeエンドポイントは、4レーンエンドポイントであり、第2マルチプレクサーチャンネル共通ポートは、2つの入力レーンと2つの出力レーンを有する。

**【0017】**

一実施形態で、適応可能回路は、構成ポートを有しシステム開始の時に、構成ポートを通じてビットファイルをロードするように構成されるプログラマブル(programmable)適応可能回路である。

10

**【0018】**

一実施形態で、第1ルーティング回路は、第1マルチプレクサーであり、適応型インターフェイスストレージ装置は、第1ビットファイルメモリと、第2ビットファイルメモリと、構成ポートと連結される第2マルチプレクサー共通ポート、第1ビットファイルメモリと連結される第1選択可能ポート、及び第2ビットファイルメモリと連結される第2選択可能ポートを有する第2マルチプレクサーと、を含む。

**【0019】**

一実施形態では、第1状態で第1選択可能ポートが選択され、第2状態で第2選択可能ポートが選択される。

**【0020】**

一実施形態で、前端ストレージインターフェイスコネクターは、U.2コネクターである。

20

**【0021】**

一実施形態で、適応型インターフェイスストレージ装置は、第1状態及び第2状態の間で選択するための信号を受信するように構成される状態制御入力を含む。

**【0022】**

一実施形態で、前端ストレージインターフェイスコネクターは、E6ピンを有するU.2コネクターであり、状態制御入力は、E6ピンである。

**【0023】**

本発明の実施形態によれば、前端ストレージインターフェイスコネクターと、永久ストレージと、を含む適応型インターフェイスストレージ装置が提供され、適応型インターフェイスストレージ装置は、第1状態又は第2状態で動作し、適応型インターフェイスストレージ装置は、第1状態において前端ストレージインターフェイスコネクターで第1装置側NvMeストレージインターフェイスを提供し、第2状態において前端ストレージインターフェイスコネクターで第2装置側NvMeoFストレージインターフェイスを提供するように構成される。

30

**【0024】**

本発明の異なる実施形態の場合に、ストレージシステムは、シャーシと、後端ストレージインターフェイスコネクター、後端ストレージインターフェイスコネクターと連結される適応可能回路、及び適応可能回路と連結される第1ルーティング回路を含む適応型インターフェイスストレージ装置と、を含み、適応型インターフェイスストレージ装置は、第1状態又は第2状態で動作し、第1状態において前端ストレージインターフェイスコネクターで第1ストレージプロトコルに従って第1装置側ストレージインターフェイスを提供し、第2状態において前端ストレージインターフェイスコネクターで第1ストレージプロトコルと異なる第2ストレージプロトコルに従って第2装置側ストレージインターフェイスを提供するように構成される。

40

**【0025】**

一実施形態で、適応型インターフェイスストレージ装置は、第1状態と第2状態との間で選択するための信号を受信するように構成される状態制御入力をさらに含み、シャーシは状態制御入力で第1状態を選択するための信号を供給するためにハードウェア処理(hardw

50

`a r d - w i r e d`) される。

【発明の効果】

【0026】

外部ハードウェア前端マルチプレクサーを使用することは、適応可能回路を構成することが PCIe リンクのトレーニングのための PCIe 標準によって割り当てられた時間より長い時間を消耗する場合に発生し得る問題を回避することができる。

【図面の簡単な説明】

【0027】

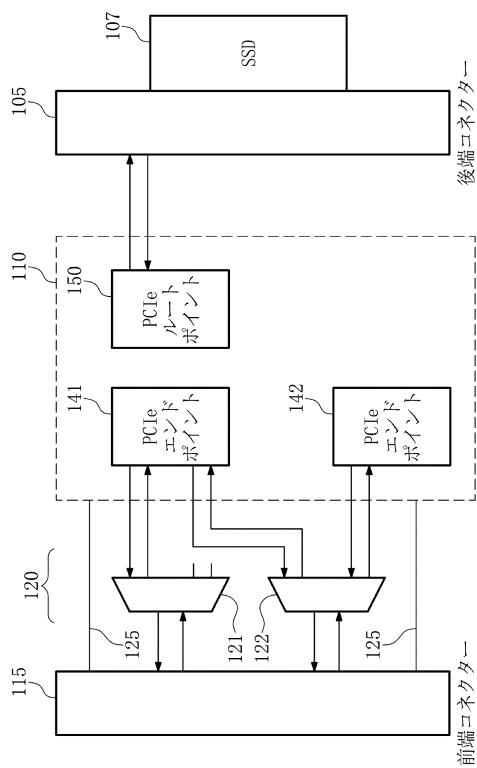

【図1】本発明の実施形態に係る適応型インターフェイスストレージ装置のブロック図である。 10

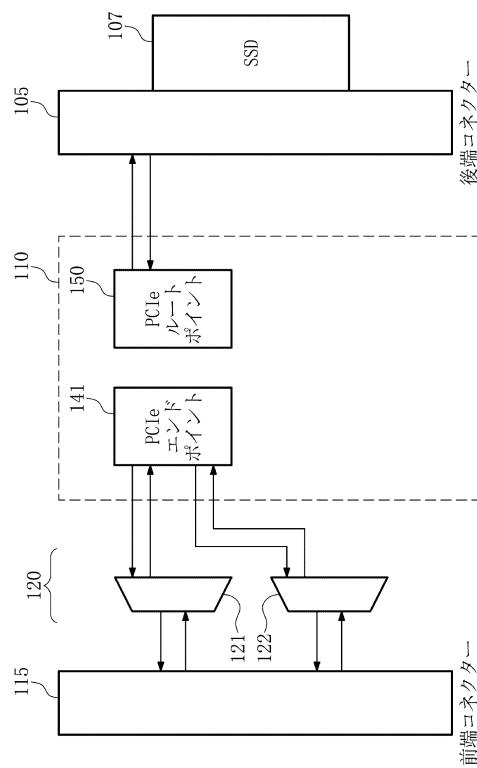

【図2A】本発明の実施形態に係る適応型インターフェイスストレージ装置のブロック図である。

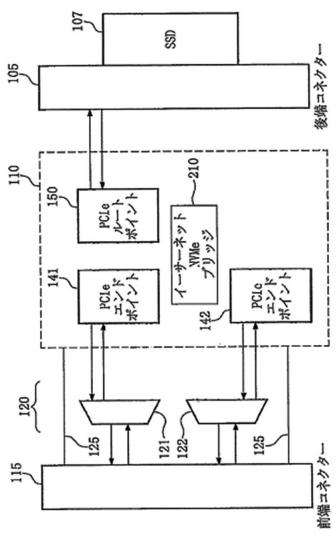

【図2B】本発明の実施形態に係る適応型インターフェイスストレージ装置のブロック図である。

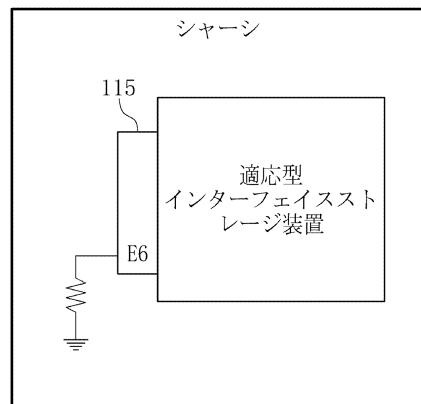

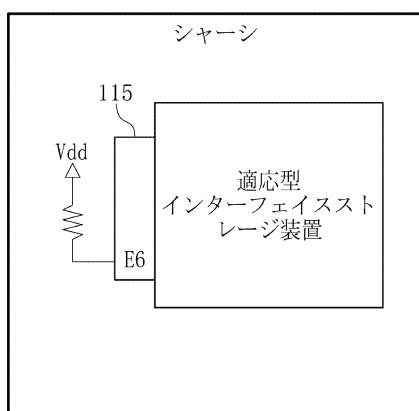

【図3A】本発明の実施形態に係る適応型インターフェイスストレージ装置を含むシャーシのブロック図である。

【図3B】本発明の実施形態に係る適応型インターフェイスストレージ装置を含むシャーシのブロック図である。

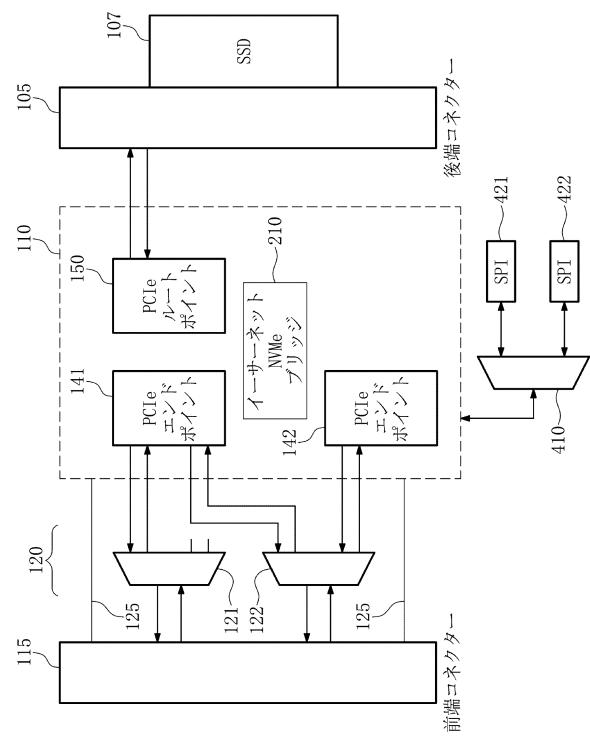

【図4】本発明の実施形態に係る適応型インターフェイスストレージ装置のブロック図である。 20

【発明を実施するための形態】

【0028】

添付された図面と関連して、以下で説明される詳細な説明は、本発明によって提供される適応型インターフェイスストレージ装置の例示的な実施形態の説明として意図されており、本発明が構成されるか、或いは使用されることができる唯一の形態を示すことを意図するものではない。説明は、図示された実施形態と関連して本発明の特徴を説明する。しかし、同一又は同等な機能及び構造が、発明の範囲内に含まれるように意図された異なる実施形態によって達成されることができる。本明細書で言及されるように、同一な構成要素番号は、同一な構成要素又は特徴を示すことが意図されている。

【0029】 30

図1を参照すると、幾つかの実施形態で、適応型インターフェイスストレージ装置 (`a d a p t i v e i n t e r f a c e s t o r a g e d e v i c e`) は、後端ストレージインターフェイスコネクター 105、適応可能 (`a d a p t a b l e`) 回路 110、前端ストレージインターフェイスコネクター 115、及び、前端ストレージインターフェイスコネクター 115 と適応可能回路 110との間に連結された前端マルチプレクサー 120、を含む。このような構成要素は、後端ストレージインターフェイスコネクター 105 を通じて固定インターフェイスストレージ装置 107 (例えば、`N V M e ( n o n v o l a t i l e m e m o r y e x p r e s s )`、`S S D ( S o l i d S t a t e D r i v e )` 等) に連結されるアダプターモジュールとして動作し、ホストシャーシに 1 つ以上のストレージインターフェイスをサポートするストレージディバイスとして動作する。前端マルチプレクサーは、一般的に、信号を複数の利用可能である経路の中で 1 つにルーティングするための任意の適切な回路であるルーティング又はスイッチング回路の例示である。2 つ以上の経路が利用可能である場合、`P C I e ( P e r i p h e r a l C o m p o n e n t I n t e r c o n n e c t e x p r e s s )` スイッチのようなルーティング構成要素が使用される。一例として、ルーティングは、単なる 2 つの構成要素の間に存在し得る。

【0030】 40

幾つかの実施形態で、適応型インターフェイスストレージ装置は (i) 3.5 インチハードドライブフォームファクタ (又は “`L F F ( L a r g e F r o m F a c t o r )`” 標準、又は (ii) 2.5 インチハードドライブフォームファクタ (又は `S F F ( S m a l`

1 Form Factor) )、又は( i i i )例えば、FH - FL カードアウトライン(Full - Height, Full Length card outline)のような標準PCIeカードフォームファクタ、又はFH - HL アウトライン(Full - Height, Half Length outline)に従っている。

#### 【0031】

本明細書で使用される、“ストレージインターフェイス”は、( i )ストレージ装置(例えば、ハードドライブ又はSSDのような永久ストレージ装置)、及び、( i i )ストレージ装置に連結されるマザーボード又はプロセッサのようなホストとの間のインターフェイスである。幾つかの実施形態で、ホストは、電力及び機械的なサポート(マウンティング及び冷却)を提供し、ストレージ装置に連結され、他のホスト(例えば、サーバー)とストレージ装置との間の連結を提供するシャーシである。これと関連して、永久ストレージ装置とホストとの間のストレージインターフェイスで、ホストは、ストレージ装置に対する“ホスト側ストレージインターフェイス”、例えば、ホスト側N V M eストレージインターフェイスを提供し(例えば、ホストは命令(例えば、読み出し又は書き込み命令)をN V M eインターフェイスを通じてストレージ装置に伝送し)、ストレージ装置は、“装置側ストレージ装置インターフェイス”、例えば装置側N V M eストレージ装置インターフェイスをホストに提供する。他の例示として、ストレージインターフェイスは“N V M e o F ( N V M e over Fabrics)”である。

#### 【0032】

適応可能回路110は、F P G A ( F i e l d P r o g r a m m a b l e G a t e A r r a y )のようなプログラマブル( p r o g r a m m a b l e )論理回路である。図1の実施形態は、適応可能回路110と前端ストレージインターフェイスコネクター115との間の1つ以上の連結(“イーサーネット連結”と称される)125を形成する1つ以上のコンダクターのセットをさらに含むことができ、適応可能回路110は、動作の幾つかのモード(又は“状態”)で、1つ以上のイーサーネットインターフェイス(例えば、図示されたように2つのイーサーネットインターフェイス)をイーサーネット連結125で提供するように構成される。前端ストレージインターフェイスコネクター115はU . 2コネクターであり、U . 2コネクターのS A Sポート0及びS A Sポート1ピンは、イーサーネット連結のために使用することができる。

#### 【0033】

図1の適応型インターフェイスストレージ装置は、2つの状態、第1状態及び第2状態で動作するように構成される；第1状態において、適応型インターフェイスストレージ装置は、前端ストレージインターフェイスコネクターで第1ストレージプロトコル(例えば、“N V M e ”)に従って装置側ストレージインターフェイスを提供するように構成され、第2状態において、適応型インターフェイスストレージ装置は、前端ストレージインターフェイスコネクター115で第2ストレージプロトコル(例えば、“N V M e over F a b r i c s ”)に従って装置側ストレージインターフェイスを提供するように構成されている。

#### 【0034】

前端マルチブレクサー120は、2つの異なる装置側ストレージインターフェイスをサポートするために、第1状態及び第2状態で異なるように構成される。前端マルチブレクサー120は、図1に示されるように、第1マルチブレクサーチャンネル121と第2マルチブレクサーチャンネル122とを含む。第1マルチブレクサーチャンネル121及び第2マルチブレクサーチャンネル122の各々は、以下でさらに詳細に論議されるように制御される。幾つかの実施形態で、前端マルチブレクサー120、例えばクワッド1 : 2 - 2 : 1マルチブレクサーは、“T e x a s I n s t r u m e n t s ”から購入可能なモデル“S N 6 5 L V C P 1 1 4 ”集積回路のような信号コンディショニングを含む線形リドライバー( r e d r i v e r )で具現される。

#### 【0035】

本明細書で使用されるように、マルチブレクサーは、1つの共通ポート、2つ以上の選

10

20

30

40

50

択可能 (selectable) ポート、及び選択入力を有する装置である。動作の時、選択入力で受信された選択信号に応じて、マルチブレクサーは、共通ポートと選択可能ポートとの内で 1 つのポート（“選択されたポート”と称される）を連結する（即ち、それらの間で内部接続を作る）。各ポートは、1 つのレーン幅又は様々なレーンの幅である。ポートの全てのレーンは、入力レーン又は出力レーンであり、ポートは、入力レーン及び出力レーンの組み合わせを含む。（出力レーンを有しない）共通入力ポート及び複数の選択可能出力レーンを含むマルチブレクサーは、デマルチブレクサー (de-multiplexer) と称されることもある。様々なレーン幅を有する共通ポートを有するマルチブレクサーは（“マルチブレクサーチャンネル”と称される）、複数のマルチブレクサーと同等であり、各マルチブレクサーチャンネルはさらに少ないレーンを有し（これによってマルチブレクサーチャンネルの総レーン数がマルチブレクサーのレーン数と同一である）、共有された選択入力連結を有する（即ち、各々が同一な選択信号ソースに連結された選択入力を有する）。幾つかの実施形態で、複数のマルチブレクサーチャンネルが、单一集積回路（“Texas Instruments”から購入可能なモデル“SN65LVCPI14”集積回路など）に含まれてよい。このような集積回路は、例として 4 つの独立なチャネル（各々が 1 つのレーン幅）を含み、各々が別の独立な選択入力を有するので、集積回路は、4 つの選択入力を有する。

#### 【0036】

このように、“Texas Instruments”で購入することができるモデル“SN65LVCPI114”のような信号コンディショニングを有する線形リドライバーであるクワッド 1 : 2 - 2 : 1 マルチブレクサーが採用される場合には、単一マルチブレクサー（例えば、前端マルチブレクサー 120）、又は 2 つのマルチブレクサーチャンネル（第 1 マルチブレクサーチャンネル 121 及び第 2 マルチブレクサーチャンネル 122）、又は 8 個のマルチブレクサーチャンネルとして称され、各々は、1 つのレーン幅を有する（共に 4 つの入力レーン及び 4 つの出力レーン提供する）。

#### 【0037】

適応可能回路 110 は、以下で、さらに具体的に説明されるように、前端ストレージインターフェイスコネクター 115 で、装置側ストレージインターフェイス又は制御ブレインインターフェイスの具現の一部を形成する、第 1 PCIe エンドポイント 141 及び第 2 PCIe エンドポイント 142 を含む。後端ストレージインターフェイスコネクター 105 で、後端ストレージインターフェイスコネクター 105 と連結される固定インターフェイスストレージ装置 107 にホスト側ストレージインターフェイスを具現するための 1 つ以上の PCIe ルートポート（又は、ルートコンプレックス）150 も含む。

#### 【0038】

図 2 A を参照すると、幾つかの実施形態では、適応型インターフェイスストレージ装置が第 1 状態で動作する時、第 1 マルチブレクサーチャンネルの第 1 選択可能ポートが選択され、第 2 マルチブレクサーチャンネルの第 1 選択可能ポートが選択される。図 2 A では、異なる環境（例えば、適応型インターフェイスストレージ装置が第 2 状態で動作する時）でこれらの連結を生成するコンダクターが存在するにも拘らず、このような構成は、容易な理解のために、第 1 マルチブレクサーチャンネルの第 2 選択可能ポート及び第 2 マルチブレクサーチャンネルの第 2 選択可能ポートで終わるラインを図面から省略することによって図示されている。第 2 PCIe エンドポイント 142 は、（（以下でさらに具体的に説明されるように）適応可能回路 110 のプログラミングの結果として）存在しないか、或いは（選択されない第 2 マルチブレクサーチャンネルの第 2 選択可能であるポートの結果として）存在するが、使用されないことがある。同様に、適応可能インターフェイスストレージ装置が（適応可能回路 110 のプログラミングの結果として）第 1 状態で動作する時、イーサーネット連結 125 は、動作可能である；容易な理解のために、イーサーネット連結によって採用されるコンダクターが（例えば、適応型インターフェイスストレージ装置が第 2 状態で動作する時）存在するにも拘らず、イーサーネット連結 125 を示す（例えば、図 1 で）ラインを図 2 A から省略することによって図示されている。

10

20

30

40

50

### 【 0 0 3 9 】

第1状態において、前端ストレージインターフェイスコネクター115に存在する装置側ストレージインターフェイスは、NVMeである。適応型インターフェイスストレージ装置は、ホスト（例えば、以下でさらに具体的に説明されるように、適応型インターフェイスストレージ装置を収容するシャーシに連結されたホスト）からNVMe命令を受信し、その命令は、前端マルチブレクサー120、適応可能回路110、及び後端ストレージインターフェイスコネクター105を通じて、固定インターフェイスストレージ装置107に伝送される。固定インターフェイスストレージ装置107は、各命令を処理し、適応型インターフェイスストレージ装置が、適応可能回路110、前端マルチブレクサー120、及び前端ストレージインターフェイスコネクター115を通じて、ホストに伝達する命令応答を、受信された各命令に応答して伝送する。適応可能インターフェイスストレージ装置は、 $1 \times 4$  NVMe装置側ストレージインターフェイスをホストに提供する。第1PCIeエンドポイント141は、 $1 \times 4$  PCIeエンドポイントである； $1 \times 4$  NVMe装置側ストレージインターフェイスの4つのレーンの中で2つ（例えば、第1番目の2つのレーン、レーン“0”及び“1”）は、第1マルチブレクサーチャンネル121を通じて第1PCIeエンドポイント141に連結され、4つのレーンの中で他の2つ（例えば、第3及び第4レーン、レーン“2”及び“3”）は、第2マルチブレクサーチャンネル122を通じて第1PCIeエンドポイント141と連結されている。10

### 【 0 0 4 0 】

図2Bを参照すると、幾つかの実施形態で、適応型インターフェイスストレージ装置は、第2状態で動作する時、第1マルチブレクサーチャンネルの第1選択可能ポートが選択され、第2マルチブレクサーチャンネルの第2選択可能ポートが選択される。図2Bで、（例えば、適応型インターフェイスストレージ装置が第1状態で動作する時）他の環境でこのような連結を生成するコンダクターが存在するにも拘らず、容易な理解のために、この構成は、第1マルチブレクサーチャンネルの第2選択可能ポート及び第2マルチブレクサーチャンネルの第1選択可能ポートで終わるラインを図面から省略することによって図示されている。20

### 【 0 0 4 1 】

第2状態において、前端ストレージインターフェイスコネクター115で提供された装置側ストレージインターフェイスは、1つ以上のイーサーネット連結125上の“NVMe over Fabrics”である。適応型インターフェイスストレージ装置は、イーサーネット連結125を通じて“NVMe over Fabrics”命令を受信し、その命令は、適応可能回路110及び後端ストレージインターフェイスコネクター105を通じて、固定インターフェイスストレージ装置107に伝達される。適応可能回路110は、前端ストレージインターフェイスコネクター115で採用される“NVMe over Fabrics”ストレージプロトコルと後端ストレージインターフェイスコネクター105で採用されるNVMeストレージプロトコルとの間の変換のためのイーサーネット-NVMeブリッジ210を含む。30

### 【 0 0 4 2 】

適応型インターフェイスストレージ装置が第1状態で動作する時のように、適応型インターフェイスストレージ装置が第2状態で動作する時、固定インターフェイスストレージ装置107は、ストレージ装置107が受信した各命令を処理して、各々の受信された命令に対して後端ストレージインターフェイスコネクター105を通じて適応型インターフェイスストレージ装置が適応可能回路110及び前端ストレージインターフェイスコネクター115を通じて戻して伝送する命令応答を伝送する。適応型インターフェイスストレージ装置は、“NVMe over Fabrics”装置側ストレージインターフェイスをホストに提供する。40

### 【 0 0 4 3 】

適応型インターフェイスストレージ装置が第2状態で動作する時、第1PCIeエンドポイント141は、 $1 \times 4$  PCIeエンドポイントであり、第2PCIeエンドポイント50

142も $1 \times 4$ PCIeエンドポイントである；第1PCIeエンドポイント141及び第2PCIeエンドポイント142が、共に第1前端ストレージインターフェイスコネクター115で第1マルチブレクサーチャンネル121及び第2マルチブレクサーチャンネル122を通じて制御プレーン動作のための $2 \times 2$ PCIeリンクを提供する。このような制御プレーン動作は、例として、固定インターフェイスストレージ装置107の消去コードをアップデートするか、或いは適応型インターフェイスストレージ装置でファームウェアをアップグレードすることを含む。

#### 【0044】

図2A及び図2Bから分かるように、第1マルチブレクサーチャンネル121の状態は、適応型インターフェイスストレージ装置の第1状態及び適応型インターフェイスストレージ装置の第2状態で同一である（そして、第1マルチブレクサーチャンネル121の第2選択可能ポートは“連結されない”、即ち、他のどの構成要素とも連結されない）。第2マルチブレクサーチャンネル122を通じて連結されたPCIeレーンに遅延等化（delay equalization）を提供するためのシステムに含まれる。適応型インターフェイスストレージ装置が第1状態で動作する時及び適応型ストレージ装置が第2状態で動作する時、全ての適応型インターフェイスストレージ装置は、ホスト側“ $1 \times 4$ NVMe”ストレージインターフェイスを固定インターフェイスストレージ装置107に提供し、以後、装置側“ $1 \times 4$ NVMe”ストレージインターフェイスを適応型インターフェイスストレージ装置に提供する。

#### 【0045】

図3A及び図3Bを参照すると、幾つかの実施形態で、以上言及されたように、適応型インターフェイスストレージ装置が、シャーシに設置されている。適応型インターフェイスストレージ装置は、第1状態及び第2状態の間で選択するための信号を受信するピン（例えば、前端ストレージインターフェイスコネクター115がU.2コネクターである場合、U.2コネクターの“E6”ピン）を有する。シャーシは、第1状態で動作する適応型インターフェイスストレージ装置に信号するための接地電圧（図3Aのように）、又は第2状態で動作する適応型インターフェイスストレージ装置に信号するための“Vdd”（図3Bのように）にピンを連結する配線（wiring）を有する。以下でさらに具体的に説明されるように、適応型インターフェイスストレージ装置の回路は、適応型インターフェイスストレージ装置が信号（例えば、“E6”ピンで受信された信号）により、前端マルチブレクサー120をセッティングすることによって、及び適応可能回路110をプログラミングすることによって識別された状態で動作するように惹起する。

#### 【0046】

図4を参照すると、幾つかの実施形態で、（適応可能回路110の構成ポート（例えば、適応可能回路110のSPI（Serial Peripheral Interface）構成ポート）を通じて）開始される時、適応可能回路110によってロードされたビットファイルは、適応型インターフェイスストレージ装置が動作中である時の状態に基づいて選択される。例として、適応型インターフェイスストレージ装置が第1状態において動作する時、ビットファイルマルチブレクサー410は適応可能回路110の構成ポートを第1状態で動作するための適応可能回路110を構成するためのビットファイルを格納する第1メモリ421（例えば、SPIフラッシュメモリ）と連結させ、第2状態において、ビットファイルマルチブレクサー410は、適応可能回路110の構成ポートを第2状態で動作するための適応可能回路110を構成するためのビットファイルを格納する第2メモリ422（例えば、SPIフラッシュメモリ）と連結させる。これによって、メモリ421は、第1状態のためのビットファイルのみを格納し、メモリ422は第2状態のためのビットファイルのみを格納することができる。第1メモリ421及び第2メモリ422の各々のビットファイルの1つは、PCIe部分を含み、PCIe部分は、適応可能回路110に読み出し、先ず具現され、PCIeエンドポイント141と142、及びルートポイント150が、PCIeリンクトレーニングに正確な時間に参与するように構成されるように引き起こす。適応可能回路110の残りは、PCIeリンクトレーニングが

10

20

30

40

50

発生する間又はPCIeリンクトレーニングが成功的に完了された後、もしくは、PCIeトレーニングの間及びPCIeトレーニングの後で、全てに構成される。(前端マルチプレクサー120によって生成される連結を適応可能回路110にプログラミングする代わりに)外部ハードウェア前端マルチプレクサー120を使用することは、適応可能回路110を構成することがPCIeリンクのトレーニングのためのPCIe標準によって割り当てられた時間より長い時間を消耗する場合に発生し得る問題を回避することができる。

#### 【0047】

たとえ、ここでは、“第1”、“第2”、“第3”等の用語が、多様な要素、成分、領域、層、及び／又はセクションを説明するために使用されていても、このような要素、成分、領域、層、及び／又はセクションは、このような用語によって限定されないことが理解されるべきである。このような用語は、他の要素、成分、領域、層、又はセクションから1つの要素、構成、領域、層又はセクションを区別するために使用される。従って、後述する第1構成要素、成分、領域、層、又はセクションは、本発明の思想及び範囲を逸脱することなく、第2構成要素、成分、領域、層、又はセクションを指称することができる。

#### 【0048】

1つの要素又は図面で図示された他の構成要素又は特徴との特徴的な関係を説明することを容易にするために“下の”、“下”、“低い”、“特定部分の下”、“上に”、“上部”と同一の、空間的であり、相対的な用語が、ここにおいて使用され得る。空間的であり、相対的な用語は、図面で示された方向に加えて、使用又は動作で装置の他の方向を含むように意図されることが理解されるべきである。例えば、仮に、図面の装置を裏返したら、他の構成要素又は特徴の“下”又は“下の”又は“特定部分の下”として説明された構成要素は、他の構成要素又は特徴の“上に”合わせられるようになる。従って、“下の”又は“特定部分の下”的例示的な用語は、上又は下方向の全てを含むことができる。装置は、異なって合わせられ(例えば、90°又は他の方向に回転されること)、そして、空間的であり相対的な技術語は、それに従って解釈されなければならない。また、2層の“間に”と指称される時、2層の間に1つの層のみがあるか、又は、1つ以上の間の層が存在することも、また理解されるべきである。

#### 【0049】

本明細書で使用された用語は、単に特定の実施形態を説明するためのものであり、本発明を限定しようとする意図するものではない。本明細書で使用されるように、“大体”、“約”の用語、及びこれらと同様な用語は、近似する用語として使用され、程度の用語としては、使用されなく、本発明の当業者によって識別される測定され又は計算された値の固有な変動を考慮するように意図されている。

#### 【0050】

本明細書で使用されるように、文脈上で明確に異なるように指示されない限り、単数形態は、本発明の概念の説明及び付加された請求項に使用される時、複数の形態を含むものと意図されている。そして、“含む”又は“含み、限定されない”の用語が本明細書に使用される場合は、記述された特徴、領域、数字、段階、動作、構成、及び／又は部品の存在を明記することであり、これらの1つ又はそれ以上の他の特徴、数字、段階、動作、構成、部品、及び／又は、グループの存在又は付加を排除しないものと、さらに理解されなければならない。本明細書で使用されるように、“及び／又は”的用語は、1つ以上の関連した羅列されたアイテムの任意の、及び、全ての組み合わせを含む。“少なくとも1つ”的な表現は、要素の全体リストを修正し、そしてリストの個別要素を修正しない。また、“することができる”的の使用は、本発明の実施形態を説明する時、“本発明の1つ以上の実施形態”を称する。また、“例示的な”的の用語は、例示又は実施形態を指称するように意図されている。本明細書で使用されたように、“使用する”、“使う”、及び“使用された”的の用語は、“利用する”、“利用している”、そして“利用された”的の用語の同意語であると各々看做され得る。

#### 【0051】

構成要素又はレイヤーが他の構成要素又はレイヤーと“上有る”、“連結される”、“結合

10

20

30

40

50

される”、又は“隣接する”と言及される時は、他の構成要素又はレイヤー上に直接的にあるか、連結させるか、或いは結合されるか、或いは隣接することができ、もしくは、1つ以上の間に位置する構成要素又はレイヤーが存在することができる。反面、構成要素が他の構成要素又はレイヤーに“直接的に上にある”、“直接的に連結される”、“直接的に結合される”、又は“直ぐ隣接する”と言及される時は、間に位置する構成要素又はレイヤーが存在しない。

#### 【0052】

本明細書で羅列された任意の数の範囲は、羅列された範囲内に含まれる同一な数の正確性の全ての下位範囲を含むように意図されている。例として、“1.0で10.0”的範囲は羅列された最小値1.0と羅列された最大値10.0との間の(そして含まれた)全ての下位範囲を含むするように、即ち、例として、2.4で7.6のように、1.0と同一であるか、又は、大きい最小値及び10.0と同一であるか、もしくは、小さい最小値を有する下位グループを含むように意図されている。本明細書で羅列された任意の最大数の制限は、ここに含まれる全てのさらに低い数の制限を含むように意図され、本明細書で羅列された任意の最小数の制限は、ここに含まれた全てのさらに高い数の制限を含むするように意図される。10

#### 【0053】

本明細書では、適応型インターフェイスストレージ装置の例示的な実施形態が具体的に説明され図示されたが、多くの修正と変形が当業者にとっては明確である。従って、本開示の原理に従って説明される適応型インターフェイスストレージ装置について、本明細書で具体的に説明されること以外の実施形態が具現できることが理解されるべきである。20

#### 【符号の説明】

#### 【0054】

- 105 後端ストレージインターフェイスコネクター

- 107 固定インターフェイスストレージ装置

- 110 適応可能回路

- 115 前端ストレージインターフェイスコネクター

- 120 前端マルチプレクサー

- 121 第1マルチプレクサーチャンネル

- 122 第2マルチプレクサーチャンネル

- 125 イーサーネット連結

- 141 第1PCIeエンドポイント

- 142 第2PCIeエンドポイント

- 150 PCIeルートポイント

- 210 イーサーネットNVMeブリッジ

304050

【図面】

【図 1】

【図 2 A】

10

20

【図 2 B】

【図 3 A】

30

40

50

【図 3 B】

【図 4】

10

20

30

40

50

---

フロントページの続き

弁理士 大貫 進介

(72)発明者 スティーブン ジー . フィッシャー

アメリカ合衆国 カリフォルニア州 94041 マウンテンビュー 263 ヴィラストリートアパート 1600

(72)発明者 ソムポン ポール オラリグ

アメリカ合衆国 カリフォルニア州 94566 プレザントン パセオグラナダ 3050

審査官 打出 義尚

(56)参考文献 特表2015-528608 (JP, A)

米国特許出願公開第2017/0185554 (US, A1)

特開2018-018514 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 06 F 13 / 38

G 06 F 3 / 08

G 06 F 13 / 10