(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-170346

(P2011-170346A)

(43) 公開日 平成23年9月1日(2011.9.1)

| (51) Int.Cl.                 | F 1         | テーマコード (参考) |

|------------------------------|-------------|-------------|

| <b>G09G 3/36 (2006.01)</b>   | G09G 3/36   | 2H092       |

| <b>H01L 29/786 (2006.01)</b> | H01L 29/78  | 618B        |

| <b>H01L 21/336 (2006.01)</b> | H01L 29/78  | 616V        |

| <b>G02F 1/1368 (2006.01)</b> | H01L 29/78  | 618Z        |

| <b>G02F 1/133 (2006.01)</b>  | G02F 1/1368 | 5C006       |

|                              |             | 5C080       |

審査請求 未請求 請求項の数 18 O L (全 48 頁) 最終頁に続く

|              |                            |            |                                                                                                                |

|--------------|----------------------------|------------|----------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2011-11906 (P2011-11906) | (71) 出願人   | 000153878                                                                                                      |

| (22) 出願日     | 平成23年1月24日 (2011.1.24)     |            | 株式会社半導体エネルギー研究所                                                                                                |

| (31) 優先権主張番号 | 特願2010-12664 (P2010-12664) |            | 神奈川県厚木市長谷398番地                                                                                                 |

| (32) 優先日     | 平成22年1月24日 (2010.1.24)     | (72) 発明者   | 山崎 舜平                                                                                                          |

| (33) 優先権主張国  | 日本国 (JP)                   |            | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内                                                                                |

|              |                            | F ターム (参考) | 2H092 GA59 JA24 JA28 JA31 JA32 JA34 JA37 JA41 JB13 JB22 JB31 KA08 KA12 KA18 MA05 MA13 NA01 NA26 PA02 PA06 QA07 |

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】表示装置の消費電力を低減すること及び表示の劣化（表示品質の低下）を抑制することを課題の一とする。また、本発明の一態様は、温度などの外部因子に対する表示の劣化（表示品質の低下）が抑制された液晶表示装置を提供することを課題の一とする。

【解決手段】表示装置の駆動回路部に、選択されたピクセルに逐次画像信号を書き込んで画像を画面に表示すると共に、同一画像を画面に表示する場合には、画像信号を書き込む動作を停止させ、トランジスタをオフ状態として画面に書き込まれた画像をそのまま保持させておく機能を設ける。このような機能をオフ電流を、室温にてチャネル幅 1  $\mu$ m当たり 10 zA /  $\mu$ m未満、85 °C にて 100 zA /  $\mu$ m未満と極めて低いレベルにまで低減されたトランジスタによって実現する。

【選択図】図4

## 【特許請求の範囲】

## 【請求項 1】

酸化物半導体層がゲート絶縁層を介してゲート電極と重畳するように設けられたトランジスタと、前記トランジスタのソース側又はドレイン側に接続された液晶を駆動する画素電極と、前記画素電極と対向するように設けられた対向電極と、前記画素電極と前記対向電極との間に設けられた液晶層と、を有するユニットを一又は複数有するピクセルがマトリクス状に配置された画素部と、前記画素部を駆動して画面に画像を表示する駆動回路部とを有する表示パネルを備え、

前記駆動回路部は、選択されたピクセルに逐次画像信号を書き込んで画像を画面に表示すると共に、同一画像を画面に表示する場合には、画像信号を書き込む動作を停止させると共に前記トランジスタをオフ状態として画面に書き込まれた画像をそのまま保持させておく機能を有することを特徴とする表示装置。10

## 【請求項 2】

酸化物半導体層がゲート絶縁層を介してゲート電極と重畳するように設けられたトランジスタと、前記トランジスタのソース側又はドレイン側に接続された液晶を駆動する画素電極と、前記画素電極と対向するように設けられた対向電極と、前記画素電極と前記対向電極との間に設けられた液晶層と、を有するユニットを一又は複数有するピクセルがマトリクス状に配置された画素部と、前記画素部を駆動して画面に画像を表示する駆動回路部とを有する表示パネルを備え、

前記駆動回路部は、選択されたピクセルに逐次画像信号を書き込んで画像を画面に表示する書き動作を行なう動作モードと、同一画像を画面に表示する場合には、画像信号を書き込む動作を停止させ画面に書き込まれた画像をそのまま保持させておく動作モードとを選択する機能を有することを特徴とする表示装置。20

## 【請求項 3】

請求項 1 又は 2 において、同一画像を画面に表示する場合において、1 秒より長い間隔で、選択されたピクセルに、当該同一画像の信号を逐次、書き込む機能を有することを特徴とする表示装置。

## 【請求項 4】

請求項 1 乃至 3 のいずれか一項において、前記同一画像の表示は、文字、図形、記号、写真、模様、若しくは絵画、若しくはこれらの結合、又はこれらと色彩の結合を含む静止画像であることを特徴とする表示装置。30

## 【請求項 5】

請求項 1 乃至 4 のいずれか一項において、前記表示パネルを照明する照明手段を有し、該照明手段の光源が発光ダイオード、又は有機エレクトロルミネッセンス素子であることを特徴とする表示装置。

## 【請求項 6】

請求項 1 乃至 5 のいずれか一項において、前記画素電極と液晶層の間、前記対向電極と前記液晶層の間に設けられた配向膜を有し、該配向膜は、光配向法またはラビング法で配向処理されていることを特徴とする表示装置。

## 【請求項 7】

請求項 1 乃至 6 のいずれか一項において、前記液晶層の方式が、TN 方式、VA 方式、MVA 方式、IPS 方式、CPA 方式、PVA 方式のいずれかであることを特徴とする表示装置。40

## 【請求項 8】

請求項 1 乃至 7 のいずれか一項において、前記液晶層の液晶相が、ネマチック相、スマチック相、コレステリック相、ブルー相のいずれかであることを特徴とする表示装置。

## 【請求項 9】

請求項 1 乃至 8 のいずれか一項において、前記ゲート電極は、前記ゲート絶縁層を介して、前記酸化物半導体層の上方又は下方に配置されていることを特徴とする表示装置。50

**【請求項 1 0】**

請求項 1 乃至 9 のいずれか一項において、前記トランジスタのソース電極及びドレイン電極は、金属窒化物であることを特徴とする表示装置。

**【請求項 1 1】**

請求項 1 乃至 9 のいずれか一項において、前記トランジスタのソース電極及びドレイン電極は、窒化タングステン、窒化チタン、又は窒化モリブデンであることを特徴とする表示装置。

**【請求項 1 2】**

請求項 1 乃至 1 1 のいずれか一項において、前記トランジスタは、オン状態において電界効果移動度が、 $5 \text{ cm}^2 / \text{V sec}$  以上であることを特徴とする表示装置。

10

**【請求項 1 3】**

請求項 1 乃至 1 1 のいずれか一項において、前記トランジスタは、オン状態において電界効果移動度が、 $10 \text{ cm}^2 / \text{V sec}$  以上  $150 \text{ cm}^2 / \text{V sec}$  以下であることを特徴とする表示装置。

**【請求項 1 4】**

請求項 1 乃至 1 3 のいずれか一項において、前記液晶を駆動する電圧範囲において、前記トランジスタのオフ電流が室温にて  $10 \text{ zA} / \mu\text{m}$  未満、 $85^\circ\text{C}$  にて  $100 \text{ zA} / \mu\text{m}$  未満であることを特徴とする表示装置。

20

**【請求項 1 5】**

請求項 1 乃至 1 4 のいずれか一項において、前記駆動回路部は、前記トランジスタのゲート電極に信号を送るゲート線側駆動回路を有し、該ゲート線側駆動回路が前記画素部と同一基板上に形成されていることを特徴とする表示装置。

**【請求項 1 6】**

請求項 1 乃至 1 5 のいずれか一項において、前記駆動回路部は、前記トランジスタのソース電極又はドレイン電極に信号を送る信号線側駆動回路を有し、該信号線側駆動回路が前記画素部と同一基板上に形成されていることを特徴とする表示装置。

30

**【請求項 1 7】**

請求項 1 乃至 1 6 のいずれか一項において、前記酸化物半導体層は真性又は実質的に真性な半導体であって、該酸化物半導体層に前記トランジスタのチャネル形成領域が形成されることを特徴とする表示装置。

**【請求項 1 8】**

請求項 1 乃至 1 7 のいずれか一項において、前記液晶を駆動する画素電極と接続され、かつ液晶層と並列に設けられた保持容量を有することを特徴とする表示装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明の一形態は、酸化物半導体を用いた電界効果型トランジスタにより構成される表示装置に関する。

**【背景技術】****【0 0 0 2】**

液晶表示装置は、テレビ受像機などの大型表示装置から携帯電話などの小型表示装置に至るまで普及している。そのため、液晶表示装置の開発としては、低コスト化又は高付加価値化を目的とした開発が行われている。特に近年では、地球環境への関心が高まり、低消費電力型の液晶表示装置の開発が注目されている。

40

**【0 0 0 3】**

その一例として、明るさ、コントラストなどの基本的な表示品位を満たした上で十分な低消費電力化を図るための方法として、走査期間と、該走査期間よりも長い非走査期間を設定する表示装置の駆動方法が開示されている（特許文献 1 参照）。具体的には、全ての走査線及びデータ信号線を非選択状態とする休止期間に、全データ信号線を電気的にデータ信号ドライバから切り離してハイインピーダンス状態とする表示装置の駆動方法である。

50

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001-312253号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

例えば液晶表示装置における画素は、画像信号の入力を制御するトランジスタと、入力される画像信号に応じた電圧が印加される液晶素子と、該液晶素子に印加される電圧を保持する保持容量とを有している。液晶素子は印加される電圧に応じて配向が変化する液晶材料を有し、当該液晶材料の配向を制御することによって各画素の表示が制御される。

10

【0006】

特許文献1で開示される液晶表示装置では、休止期間において、画素部に含まれる各画素に対して画像信号が入力されない。すなわち、各画素内に画像信号を保持したまま、画像信号の入力を制御するトランジスタがオフ状態を維持する期間が長期化する。そのため、当該トランジスタを介した画像信号のリークが各画素の表示に対して与える影響が顕在化する。具体的には、液晶素子に印加される電圧が低下し、当該液晶素子を有する画素の表示の劣化（変化）が顕在化する。

20

【0007】

さらに当該トランジスタを介した画像信号のリークは、トランジスタの動作温度によって変動する。具体的には、動作温度の上昇に伴い、トランジスタを介した画像信号のリークが増加する。そのため、特許文献1で開示される液晶表示装置は、環境の変動が大きい屋外などにおいて使用した際に、表示品質を一定に保つことが困難である。

20

【0008】

そこで、本発明の一態様は、液晶表示装置の消費電力を低減すること及び表示の劣化（表示品質の低下）を抑制することを課題の一とする。また、本発明の一態様は、温度などの外部因子に対する表示の劣化（表示品質の低下）が抑制された液晶表示装置を提供することを課題の一とする。

30

【課題を解決するための手段】

【0009】

本発明の一形態は、各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用することで上記課題解決せんとするものである。なお、当該酸化物半導体層は、電子供与体（ドナー）となる不純物（水素又は水など）を極力に除去することにより高純度化された酸化物半導体層であることが好ましい。当該酸化物半導体層をチャネル形成領域に用いたトランジスタは、オフ電流を、室温にてチャネル幅  $1 \mu m$  当たり  $10 zA / \mu m$  未満、  $85$  にて  $100 zA / \mu m$  未満と極めて低いレベルにまで低減させることを可能とするからである。

30

【0010】

当該酸化物半導体層は、  $2.0 eV$  以上、好ましくは  $2.5 eV$  以上、より好ましくは  $3.0 eV$  以上のバンドギャップを有する。加えて、当該酸化物半導体層は、高純度化されることで、導電型が限りなく真性型に近づく。そのため、当該酸化物半導体層では、熱励起に起因するキャリアの発生を抑制することができる。その結果、当該酸化物半導体層によってチャネル形成領域が構成されたトランジスタの動作温度の上昇に伴うオフ電流の増加を低減することができる。

40

【0011】

酸化物半導体を用いたトランジスタの一態様としては、上記のような酸化物半導体層の他に、ソース電極及びドレン電極の一部を金属窒化物で形成したものを用いる。トランジスタのゲート電極は、絶縁層を介して酸化物半導体層の下側（基板側）又は上側（基板側とは反対側）若しくは両側に設けられていれば良い。また、トランジスタの特性としてオフ状態の特性ばかりでなく、オン状態の特性として、電界効果移動度の最大値が  $5 cm^2$

50

/ V sec 以上、好ましくは 10 cm<sup>2</sup> / V sec ~ 150 cm<sup>2</sup> / V sec のものを用いる。トランジスタの動作を高速化することで、画素を高密度化したときにも、高速で書き込み動作等ができるようになるためである。

【0012】

本発明の一形態は、酸化物半導体層がゲート絶縁層を介してゲート電極と重畳するように設けられたトランジスタと、トランジスタのソース側又はドレイン側に接続された液晶を駆動する画素電極と、画素電極と対向するように設けられた対向電極と、画素電極と対向電極との間に設けられた液晶層とを有するユニットを一又は複数有するピクセルがマトリクス状に配置された画素部と、画素部を駆動して画面に画像を表示する駆動回路部とを有する表示パネルを備えた表示装置である。そして駆動回路部に、選択されたピクセルに逐次画像信号を書き込んで画像を画面に表示すると共に、同一画像を画面に表示する場合には、画像信号を書き込む動作を停止させ、トランジスタをオフ状態として画面に書き込まれた画像をそのまま保持させておく機能を設ける。このような機能は、上記トランジスタを用いることにより実現される。

【0013】

本発明の一形態は、酸化物半導体層がゲート絶縁層を介してゲート電極と重畳するように設けられたトランジスタと、トランジスタのソース側又はドレイン側に接続された液晶を駆動する画素電極と、画素電極と対向するように設けられた対向電極と、画素電極と対向電極との間に設けられた液晶層とを有するユニットを一又は複数有するピクセルがマトリクス状に配置された画素部と、画素部を駆動して画面に画像を表示する駆動回路部とを有する表示パネルを備えた表示装置である。駆動回路部は、選択されたピクセルに逐次画像信号を書き込んで画像を画面に表示する書き動作を行なう動作モードと、同一画像を画面に表示する場合には、画像信号を書き込む動作を停止させ画面に書き込まれた画像をそのまま保持させておく動作モードとを選択する機能を設ける。このような機能は、上記トランジスタを用いることにより実現される。

【発明の効果】

【0014】

本発明の一態様の液晶表示装置は、各画素に設けられるトランジスタとして、チャネル形成領域が酸化物半導体層によって構成されるトランジスタを適用する。当該酸化物半導体層を高純度化することで、当該トランジスタの室温におけるオフ電流値をチャネル幅 1 μm 当たり 10 zA / μm 未満、 85 °C にて 100 zA / μm 未満とすることが可能である。そのため、当該トランジスタを介した画像信号のリークを低減することができる。すなわち、当該トランジスタを有する画素への画像信号の書き込み頻度を低減した場合における表示の劣化（変化）を抑制することができる。その結果、当該液晶表示装置の消費電力を低減すること及び表示の劣化（表示品質の低下）を抑制することが可能になる。

【0015】

また、オフ電流が極めて低いトランジスタを用いた画素は、一定の状態（画像信号が書き込まれた状態）を保持することができる。その場合に、当該トランジスタは、動作温度の上昇に伴うオフ電流値の増加が著しく小さいため、温度などの外部因子が当該画素における画像信号のリークに与える影響を低減することができる。つまり、当該液晶表示装置は、環境の変動が大きい屋外などにおいて、画像信号が書き込まれた状態を保持して静止画を表示した場合においても、表示の劣化（表示品質の低下）を抑制することができる。

【図面の簡単な説明】

【0016】

【図1】実施の形態1に係る液晶表示装置の各構成を説明するブロック図。

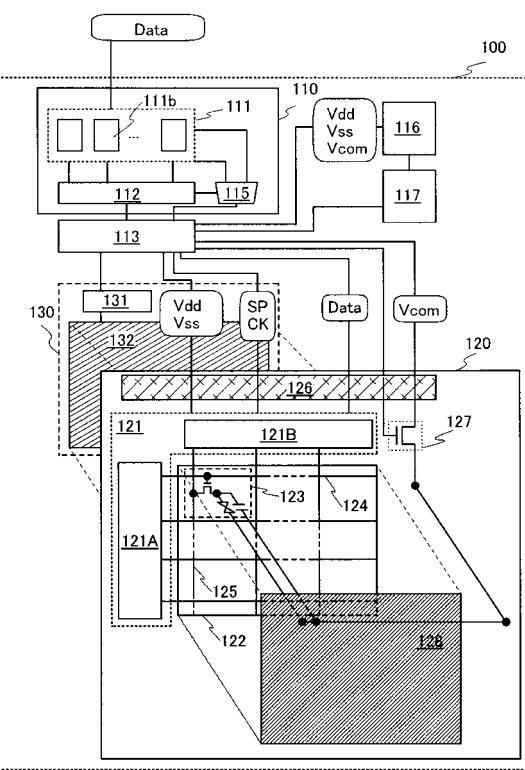

【図2】実施の形態1に係る液晶表示装置の各構成を説明するブロック図。

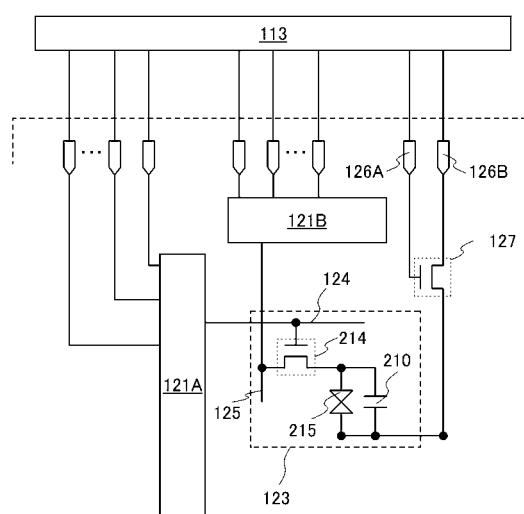

【図3】実施の形態1に係る液晶表示装置の駆動回路と画素の構成を説明する図。

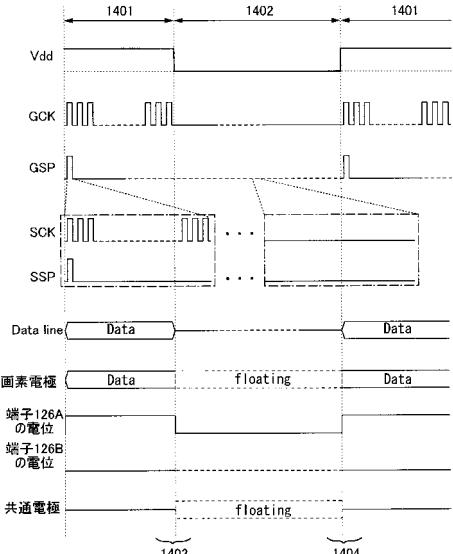

【図4】実施の形態1に係る液晶表示装置の動作を説明するタイミングチャート。

【図5】実施の形態1に係る液晶表示装置の表示制御回路の動作を説明するタイミングチ

10

20

30

40

50

ヤート。

【図6】動画を表示する期間と静止画を表示する期間における画像信号の書き込み頻度を模式的に示す図。

【図7】実施の形態2に係るテレビ受像機の構成を説明する図。

【図8】実施の形態2に係るモニターの構成を説明する図。

【図9】液晶表示装置のバックライト構成例を説明する図。

【図10】液晶表示装置のバックライト構成例を説明する図。

【図11】液晶表示装置に適用できるトランジスタの一例を説明する図

【図12】酸化物半導体層を含むトランジスタ及びその作製方法の一例を説明する図。

【図13】酸化物半導体によって作製されたトランジスタのVg - Id特性の一例を示すグラフ。

【図14】酸化物半導体によって作製されたトランジスタのVg - Id特性の内、オフ状態の特性を説明するためのグラフ。

【図15】ソース - ドレイン電圧Vとオフ電流Iとの関係を表すグラフ。

【図16】本発明に係る電子書籍の一例を説明する図。

【図17】本発明に係るコンピュータの一例を説明する図。

【図18】液晶表示装置の画素の一例を示す平面図。

【図19】液晶表示装置の画素の一例を示す断面図。

【発明を実施するための形態】

【0017】

発明の実施の形態について図面を用いて以下に説明する。但し、本明細書で開示される発明は以下の説明に限定されず、その発明の趣旨及びその範囲から逸脱することなくその形態及び詳細をさまざまに変更し得ることは当業者であれば容易に理解される。したがって、本明細書で開示される発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0018】

実施の形態において図面を参照して説明をする場合には、同じ構成要素を指す符号を異なる図面間で共通して用いる場合がある。なお、図面において示す構成要素、すなわち層や領域等の厚さ幅、相対的な位置関係等は、実施の形態において説明する上で明確性のため誇張して示される場合がある。

【0019】

(実施の形態1)

本実施の形態では、本発明の液晶表示装置、及び低消費電力化を図れる液晶表示装置の駆動方法の一形態を、図1乃至図6を用いて説明する。

【0020】

本実施の形態で例示する液晶表示装置100の各構成を、図1のプロック図に示す。液晶表示装置100は、画像処理回路110、電源116、表示制御回路113、表示パネル120を有する。透過型液晶表示装置、又は半透過型液晶表示装置の場合、さらに光源としてバックライト部130を設ける。

【0021】

液晶表示装置100は、接続された外部機器から画像信号(画像信号Data)が供給されている。なお、電源電位(高電源電位Vdd、低電源電位Vss、及び共通電位Vcom)は液晶表示装置の電源116をオン状態として電力供給を開始することによって供給され、制御信号(スタートパルスSP、及びクロック信号CK)は表示制御回路113によって供給される。

【0022】

なお高電源電位Vddとは、基準電位より高い電位のことであり、低電源電位Vssとは基準電位以下の電位のことをいう。なお高電源電位Vdd及び低電源電位Vssともに、トランジスタが動作できる程度の電位であることが望ましい。なお高電源電位Vdd及び低電源電位Vssを併せて、電源電圧と呼ぶこともある。

10

20

30

40

50

## 【0023】

共通電位  $V_{com}$  は、画素電極に供給される画像信号の電位に対して基準となる固定電位であればよく、一例としてはグラウンド電位であってもよい。

## 【0024】

画像信号  $Data$  は、ドット反転駆動、ソースライン反転駆動、ゲートライン反転駆動、フレーム反転駆動等に応じて適宜反転させて液晶表示装置 100 に供給される構成とすればよい。また、画像信号がアナログの信号の場合には、A/D コンバータ等を介してデジタルの信号に変換して、液晶表示装置 100 に供給する構成とすればよい。

## 【0025】

本実施の形態では、共通電極 128 及び容量素子 210 の一方の電極には、電源 116 より表示制御回路 113 を介して固定電位である共通電位  $V_{com}$  が与えられている。

10

## 【0026】

表示制御回路 113 は、表示パネル 120 に表示パネル画像信号 ( $Data$ )、並びに制御信号（具体的にはスタートパルス  $SP$ 、及びクロック信号  $CK$  等の制御信号の供給または停止の切り替えを制御するための信号）、電源電位（高電源電位  $V_{dd}$ 、低電源電位  $V_{ss}$ 、及び共通電位  $V_{com}$ ）を供給する回路である。

## 【0027】

画像処理回路 110 は、入力される画像信号（画像信号  $Data$ ）を解析、演算、乃至加工し、処理した画像信号を制御信号と共に表示制御回路 113 に出力する。

20

## 【0028】

具体的には画像処理回路 110 は、入力される画像信号  $Data$  を解析し動画であるか静止画であるかを判断し、判断結果を含む制御信号を表示制御回路 113 に出力する。また、画像処理回路 110 は、動画または静止画を含む画像信号  $Data$  から 1 フレームの静止画を切り出し、静止画であることを意味する制御信号と共に表示制御回路 113 に出力する。また、画像処理回路 110 は、入力される画像信号  $Data$  を上述の制御信号と共に表示制御回路 113 に出力する。なお、上述した機能は画像処理回路 110 が有する機能の一例であり、表示装置の用途に応じて種々の画像処理機能を選択して適用すればよい。

## 【0029】

なお、デジタル信号に変換された画像信号は演算（例えば画像信号の差分を検出する等）が容易であるため、入力される画像信号（画像信号  $Data$ ）がアナログの信号の場合には、A/D コンバータ等を画像処理回路 110 に設ける。

30

## 【0030】

表示パネル 120 は液晶素子 215 を一対の基板（第 1 の基板と第 2 の基板）間に挟持する構成を有し、第 1 の基板には駆動回路部 121、画素部 122 が設けられている。また、第 2 の基板には共通接続部（コモンコンタクトともいう）、及び共通電極 128（コモン電極、または対向電極ともいう）が設けられている。なお、共通接続部は第 1 の基板と第 2 の基板とを電気的に接続するものであって、共通接続部は第 1 の基板上に設けられていてもよい。

40

## 【0031】

画素部 122 には、複数のゲート線 124（走査線）、及びソース線 125（信号線）が設けられており、複数の画素 123 がゲート線 124 及びソース線 125 に環囲されてマトリクス状に設けられている。なお、本実施の形態で例示する表示パネルにおいては、ゲート線 124 はゲート線側駆動回路 121A から延在し、ソース線 125 はソース線側駆動回路 121B から延在している。

## 【0032】

また、画素 123 はスイッチング素子としてトランジスタ 214、該トランジスタ 214 に接続された容量素子 210、及び液晶素子 215 を有する。

## 【0033】

液晶素子 215 は、液晶の光学的変調作用によって光の透過又は非透過を制御する素子で

50

ある。液晶の光学的変調作用は、液晶にかかる電界によって制御される。液晶にかかる電界方向は液晶材料、駆動方法、及び電極構造によって異なり、適宜選択することができる。例えば、液晶の厚さ方向（いわゆる縦方向）に電界をかける駆動方法を用いる場合は液晶を挟持するように第1の基板に画素電極を、第2の基板に共通電極をそれぞれ設ける構造とすればよい。また、液晶に基板面内方向（いわゆる横電界）に電界をかける駆動方法を用いる場合は、液晶に対して同一面に、画素電極と共通電極を設ける構造とすればよい。また画素電極及び共通電極は、多様な開口パターンを有する形状としてもよい。本実施の形態においては光学的変調作用によって光の透過又は非透過を制御する素子であれば、液晶材料、駆動方法、及び電極構造は特に限定されない。

## 【0034】

10

トランジスタ214は、画素部122に設けられた複数のゲート線124のうちの一つとゲート電極が接続され、ソース電極またはドレイン電極の一方が複数のソース線125のうちの一つと接続され、ソース電極またはドレイン電極の他方が容量素子210の一方の電極、及び液晶素子215の一方の電極（画素電極）と接続される。

## 【0035】

トランジスタ214は、オフ電流が低減されたトランジスタを用いることが好ましい。トランジスタ214がオフ状態のとき、オフ電流が低減されたトランジスタ214に接続された液晶素子215、及び容量素子210に蓄えられた電荷は、トランジスタ214を介して漏れ難く、トランジスタ214がオフ状態になる前に書き込まれた状態を、次に信号が書き込まれるまで安定して保持できる。従って、オフ電流が低減されたトランジスタ214に接続された容量素子210を用いることなく、画素123を構成することもできる。

20

## 【0036】

このような構成とすることで、容量素子210は液晶素子215に加える電圧を保持することができる。また、容量素子210の電極は、別途設けた容量線に接続する構成としてもよい。

## 【0037】

駆動回路部121は、ゲート線側駆動回路121A、ソース線側駆動回路121Bを有する。ゲート線側駆動回路121A、ソース線側駆動回路121Bは、複数の画素を有する画素部122を駆動するための駆動回路であり、シフトレジスタ回路（シフトレジスタともいう）を有する。

30

## 【0038】

なお、ゲート線側駆動回路121A、及びソース線側駆動回路121Bは、画素部122と同じ基板に形成されるものでもよいし、別の基板に形成されるものであってもよい。

## 【0039】

なお駆動回路部121には、表示制御回路113によって制御された高電源電位Vdd、低電源電位Vss、スタートパルスSP、クロック信号CK、画像信号Dataが供給される。

## 【0040】

40

端子部126は、表示制御回路113が出力する所定の信号（高電源電位Vdd、低電源電位Vss、スタートパルスSP、クロック信号CK、画像信号Data、共通電位Vcom等）等を駆動回路部121に供給する入力端子である。

## 【0041】

共通電極128は、表示制御回路113に制御された共通電位Vcomを与える共通電位線と、共通接続部において電気的に接続する。

## 【0042】

共通接続部の具体的な一例としては、絶縁性球体に金属薄膜が被覆された導電粒子を間に介することにより共通電極128と共通電位線との電気的な接続を図ることができる。なお、共通接続部は、表示パネル120内に複数箇所設けられる構成としてもよい。

## 【0043】

50

また、液晶表示装置は、測光回路を有していてもよい。測光回路を設けた液晶表示装置は当該液晶表示装置がおかれている環境の明るさを検知できる。その結果、測光回路が接続された表示制御回路 113 は、測光回路から入力される信号に応じて、バックライト、サイドライト等の光源の駆動方法を制御することができる。

【0044】

バックライト部 130 はバックライト制御回路 131、及びバックライト 132 を有する。バックライト 132 は、液晶表示装置 100 の用途に応じて選択して組み合わせればよく、液晶表示装置 100 は照明する照明手段を有し、該照明手段の光源として発光ダイオード (LED) などを用いることができる。バックライト 132 には例えば白色の発光素子 (例えば LED) を配置することができる。バックライト制御回路 131 には、表示制御回路 113 からバックライトを制御するバックライト信号、及び電源電位が供給される。

10

【0045】

なお、カラー表示を行う場合は、カラーフィルタを用いることで表示が可能である。また、他の光学フィルム (偏光フィルム、位相差フィルム、反射防止フィルムなど) も用いることができる。透過型液晶表示装置、又は半透過型液晶表示装置の場合に用いられるバックライト等の光源は、液晶表示装置 100 の用途に応じて用いればよく、冷陰極管や発光ダイオード (LED) などを用いることができる。また複数の LED 光源、または複数のエレクトロルミネセンス (EL) 光源などを用いて面光源を構成してもよい。面光源として、3 種類以上の LED を用いてもよいし、白色発光の LED を用いてもよい。なお、バックライトに RGB の発光ダイオード等を配置し、時分割によりカラー表示する継時加法混色法 (フィールドシーケンシャル法) を採用するときには、カラーフィルタを設けない。

20

【0046】

次に、図 1 に例示した液晶表示装置の駆動方法について、図 2 乃至図 6 を用いて説明する。本実施の形態で説明する液晶表示装置の駆動方法は、表示する画像の特性に応じて、表示パネルの書き換え頻度 (または周波数) を変える表示方法である。具体的には、連続するフレームの画像信号が異なる画像 (動画) を表示する場合は、フレーム毎に画像信号が書き込まれる表示モードを用いる。一方、連続するフレームの画像信号が同一な画像 (静止画) を表示する場合は、同一な画像を表示し続ける期間に新たに画像信号は書き込まれないか、書き込む頻度を極めてすくなくし、さらに液晶素子に電圧を印加する画素電極及び共通電極の電位を浮遊状態 (フローティング) にして液晶素子にかかる電圧を保持し、新たに電位を供給することなく静止画の表示を行う表示モードを用いる。

30

【0047】

なお、液晶表示装置は動画と静止画を組み合わせて画面に表示する。動画は、複数のフレームに時分割した複数の異なる画像を高速に切り替えることで人間の目に動く画像として認識される画像をいう。具体的には、1 秒間に 60 回 (60 フレーム) 以上画像を切り替えることで、人間の目にはちらつきが少なく動画と認識されるものとなる。一方、静止画は、動画及び部分動画と異なり、複数のフレーム期間に時分割した複数の画像を高速に切り替えて動作させていても、連続するフレーム期間、例えば  $n$  フレーム目と、 $(n + 1)$  フレーム目とで変化しない画像のことをいう。

40

【0048】

本発明に係る液晶表示装置は、画像が動く動画表示の時と画像が静止している静止画表示の時とにおいて、それぞれ動画表示モード、静止画表示モードという異なる表示モードを用いることができる。なお本明細書では、静止画表示モードの時に表示される画像を静止画像ともよぶ。

【0049】

次に、本実施の形態の液晶表示装置 100 の各構成を、図 2 のブロック図を用いて説明する。液晶表示装置 100 は、画素において光の透過、非透過を利用して表示を行う透過型液晶表示装置、又は半透過型液晶表示装置の例であり、画像処理回路 110、電源 116

50

、表示パネル 120、及びバックライト部 130 を有する。なお、反射型液晶表示装置の場合は、光源として外光を用いるため、バックライト部 130 を省略することができる。

#### 【0050】

液晶表示装置 100 は、接続された外部機器から画像信号（画像信号 Data）が供給されている。なお、電源電位（高電源電位 Vdd、低電源電位 Vss、及び共通電位 Vcom）は液晶表示装置の電源 116 をオン状態として電力供給を開始することによって供給され、制御信号（スタートパルス SP、及びクロック信号 CK）は表示制御回路 113 によって供給される。

#### 【0051】

次に、画像処理回路 110 の構成、及び画像処理回路 110 が信号を処理する手順について、図 2 に一例を示して説明する。なお、図 2 に示す画像処理回路 110 は、本実施の形態の一態様であり、本実施の形態はこの構成に限定されない。

10

#### 【0052】

図 2 に例示する画像処理回路 110 は、連続して入力される画像信号を解析し、動画と静止画を判別する。また、入力される画像信号（画像信号 Data）が動画から静止画に移行する際に、静止画を切り出し、静止画であることを意味する制御信号と共に表示制御回路 113 に出力する。また、入力される画像信号（画像信号 Data）が静止画から動画に移行する際に、動画を含む画像信号を、動画であることを意味する制御信号と共に表示制御回路 113 に出力する。

20

#### 【0053】

画像処理回路 110 は、記憶回路 111、比較回路 112、及び選択回路 115 を有する。画像処理回路 110 は、入力されたデジタル画像信号 Data から表示パネル画像信号とバックライト信号を生成する。表示パネル画像信号は、表示パネル 120 を制御する画像信号であり、バックライト信号はバックライト部 130 を制御する信号である。

#### 【0054】

記憶回路 111 は、複数のフレームに関する画像信号を記憶するための複数のフレームメモリを有する。記憶回路 111 が有するフレームメモリの数は特に限定されるものではなく、複数のフレームに関する画像信号を記憶できる素子であればよい。なおフレームメモリは、例えばDRAM (Dynamic Random Access Memory)、SRAM (Static Random Access Memory) 等の記憶素子を用いて構成すればよい。

30

#### 【0055】

なおフレームメモリは、フレーム期間毎に画像信号を記憶する構成であればよく、フレームメモリの数について特に限定されるものではない。またフレームメモリの画像信号は、比較回路 112 及び表示制御回路 113 により選択的に読み出されるものである。なお図中のフレームメモリ 111b は、1 フレーム分のメモリ領域を概念的に図示するものである。

#### 【0056】

比較回路 112 は、記憶回路 111 に記憶された連続するフレーム期間の画像信号を選択的に読み出して、当該画像信号の連続するフレーム間での比較を画素毎に行い、差分を検出するための回路である。

40

#### 【0057】

なお、本実施の形態では連続するフレーム間の画像信号の差分の有無により、表示制御回路 113 及び選択回路 115 の動作を決定する。当該比較回路 112 がフレーム間のいずれかの画素で差分を検出した場合（差分「有」の場合）、比較回路 112 は画像信号が静止画ではないと判断し、差分を検出した連続するフレーム期間を動画であると判断する。

#### 【0058】

一方、比較回路 112 での画像信号の比較により、全ての画素で差分が検出されない場合（差分「無」の場合）、当該差分を検出しなかった連続するフレーム期間は、静止画であると判断する。すなわち比較回路 112 は、連続するフレーム期間の画像信号の差分の有

50

無を検出することによって、動画を表示するための画像信号であるか、または静止画を表示するための画像信号であるかの判断をするものである。

【0059】

なお、当該比較により「差分が有る」と検出される基準は、差分の大きさが一定のレベルを超えたときに、差分有りとして検出したと判断されるように設定してもよい。なお比較回路112の検出する差分は、差分の絶対値によって判断をする設定とすればよい。

【0060】

また、本実施の形態においては、液晶表示装置100内部に設けられた比較回路112が連続するフレーム期間の画像信号の差分を検出することにより当該画像が動画又は静止画のいずれであるかの判断を行う構成について示したが、外部から動画であるか静止画であるかを示す信号を供給する構成としてもよい。

10

【0061】

選択回路115は、例えばトランジスタで形成される複数のスイッチを設ける構成とする。比較回路112が連続するフレーム間に差分を検出した場合、すなわち画像が動画の際、記憶回路111内のフレームメモリから動画の画像信号を選択して表示制御回路113に出力する。

20

【0062】

なお選択回路115は、比較回路112が連続するフレーム間に差分を検出しない場合、すなわち画像が静止画の際、記憶回路111内のフレームメモリから表示制御回路113に画像信号を出力しない。画像信号をフレームメモリより表示制御回路113に出力しない構成とすることにより、液晶表示装置の消費電力を削減できる。

20

【0063】

なお、本実施の形態の液晶表示装置において、比較回路112が画像を静止画と判断しておこなう動作が静止画表示モード、比較回路112が画像を動画と判断しておこなう動作が動画表示モードとなる。

30

【0064】

表示制御回路113は、表示パネル120に選択回路115で選択された画像信号、並びに制御信号（具体的にはスタートパルスS P、及びクロック信号C K等の制御信号の供給または停止の切り替えを制御するための信号）、電源電位（高電源電位V d d、低電源電位V s s、及び共通電位V c o m）を供給し、バックライト部130にバックライト制御信号（具体的にはバックライト制御回路131がバックライトの点灯、及び消灯を制御するための信号）を供給する回路である。

30

【0065】

なお、本実施の形態で例示される画像処理回路は、表示モード切り替え機能を有していてもよい。表示モード切り替え機能は、当該液晶表示装置の利用者が手動または外部接続機器を用いて当該液晶表示装置の動作モードを選択することで動画表示モードまたは静止画表示モードを切り替える機能である。

40

【0066】

選択回路115は表示モード切り替え回路から入力される信号に応じて、画像信号を表示制御回路113に出力することもできる。

40

【0067】

例えば、静止画表示モードで動作している際に、表示モード切り替え回路から選択回路115にモード切り替え信号が入力された場合、比較回路112が連続するフレーム期間での画像信号の差分を検出していない場合であっても、選択回路115は入力される画像信号を順次表示制御回路113に出力するモード、すなわち動画表示モードを実行できる。また、動画表示モードで動作している際に、表示モード切り替え回路から選択回路115にモード切り替え信号が入力された場合、比較回路112が連続するフレーム期間での画像信号の差分を検出している場合であっても、選択回路115は選択した1フレームの画像信号の信号のみを出力するモード、すなわち静止画表示モードを実行できる。その結果、本実施の形態の液晶表示装置には、動画中の1フレームが静止画として表示される。

50

## 【0068】

また、液晶表示装置が測光回路を有している場合、測光回路が検知する環境の明るさにより、液晶表示装置が薄暗い環境で使用されていることが判明すると表示制御回路113はバックライト132の光の強度を高めるように制御して表示画面の良好な視認性を確保し、反対に液晶表示装置が極めて明るい外光下（例えば屋外の直射日光下）で利用されていることが判明すると、表示制御回路113はバックライト132の光の強度を抑えるように制御しバックライト132が消費する電力を低下させる。

## 【0069】

本実施の形態では、表示パネル120は画素部122の他に、スイッチング素子127を有する。本実施の形態では、表示パネル120は第1の基板と、第2の基板を有し、第1の基板には駆動回路部121、画素部122、及びスイッチング素子127が設けられている。

10

## 【0070】

また、画素123はスイッチング素子としてトランジスタ214、該トランジスタ214に接続された容量素子210、及び液晶素子215を有する（図3参照。）。

## 【0071】

トランジスタ214は、オフ電流が低減されたトランジスタを用いることが好ましい。トランジスタ214がオフ状態のとき、オフ電流が低減されたトランジスタ214に接続された液晶素子215、及び容量素子210に蓄えられた電荷は、トランジスタ214を介して漏れ難く、トランジスタ214がオフ状態になる前に書き込まれた状態を長時間に渡って保持できる。

20

## 【0072】

本実施の形態では、液晶は、第1の基板に設けられた画素電極と対向する第2の基板に設けられた共通電極によって形成された縦方向の電界によって制御される。

## 【0073】

液晶素子に適用する液晶の一例としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子分散型液晶（PDL C）、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、バナナ型液晶などを挙げることができる。

30

## 【0074】

また液晶の駆動方法の一例としては、TN（Twisted Nematic）モード、STN（Super Twisted Nematic）モード、OCB（Optically Compensated Birefringence）モード、ECB（Electrically Controlled Birefringence）モード、FLC（Ferroelectric Liquid Crystal）モード、AFLC（AntiFerroelectric Liquid Crystal）モード、PDLC（Polymer Dispersed Liquid Crystal）モード、PNLC（Polymer Network Liquid Crystal）モード、ゲストホストモードなどがある。

## 【0075】

スイッチング素子127は、表示制御回路113が出力する制御信号に応じて、共通電位Vcomを共通電極128に供給する。スイッチング素子127としては、トランジスタを用いることができる。トランジスタのゲート電極及びソース電極またはドレイン電極の一方を表示制御回路113に接続し、ソース電極またはドレイン電極の一方には、端子部126を介して表示制御回路113から共通電位Vcomが供給されるようにし、他方を共通電極128に接続すればよい。なお、スイッチング素子127は駆動回路部121、及び画素部122と同じ基板に形成されるものでもよいし、別の基板に形成されるものであってもよい。

40

## 【0076】

スイッチング素子127としてオフ電流が低減されたトランジスタを用いることにより、

50

液晶素子 215 の両端子に加わる電圧が経時的に低下する現象を抑制できる。

【0077】

共通接続部は、スイッチング素子 127 のソース電極またはドレイン電極と接続された端子と、共通電極 128 を電気的に接続する。

【0078】

スイッチング素子の一様であるトランジスタを用いるスイッチング素子 127 のソース電極またはドレイン電極の一方は、共通接続部を介して端子 126B に接続され、スイッチング素子 127 のソース電極またはドレイン電極の他方は、トランジスタ 214 と接続されていない容量素子 210 の他方の電極、及び液晶素子 215 の他方の電極と接続される。また、スイッチング素子 127 のゲート電極は端子 126A に接続される。

10

【0079】

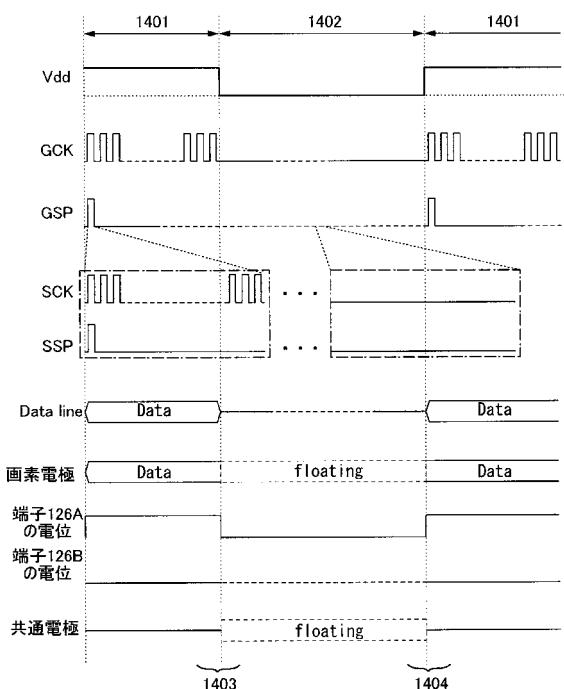

次に、画素に供給する信号の様子を、図 3 に示す液晶表示装置の等価回路図、及び図 4 に示すタイミングチャートを用いて説明する。

【0080】

図 4 に、表示制御回路 113 がゲート線側駆動回路 121A に供給するクロック信号 GCK、及びスタートパルス GSP を示す。また、表示制御回路 113 がソース線側駆動回路 121B に供給するクロック信号 SCK、及びスタートパルス SSP を示す。なお、クロック信号の出力のタイミングを説明するために、図 4 ではクロック信号の波形を単純な矩形波で示す。

20

【0081】

また図 4 に、高電源電位 Vdd、ソース線 125 の電位 (Data line の電位)、画素電極の電位、端子 126A の電位、端子 126B の電位、並びに共通電極の電位を示す。

【0082】

図 4 において期間 1401 は、動画を表示するための画像信号を書き込む期間に相当する。期間 1401 では画像信号、共通電位が画素部 122 の各画素、共通電極に供給されるように動作する。

【0083】

また、期間 1402 は、静止画を表示する期間に相当する。期間 1402 では、画素部 122 の各画素への画像信号、共通電極への共通電位を停止することとなる。なお図 4 に示す期間 1402 では、駆動回路部の動作を停止するよう各信号を供給する構成について示したが、期間 1402 の長さ及びリフレッシュレートによって、定期的に画像信号を書き込むことで静止画の画像の劣化を防ぐ構成とすることが好ましい。

30

【0084】

まず、期間 1401 におけるタイミングチャートを説明する。期間 1401 では、クロック信号 GCK として、常時クロック信号が供給され、スタートパルス GSP として、垂直同期周波数に応じたパルスが供給される。また、期間 1401 では、クロック信号 SCK として、常時クロック信号が供給され、スタートパルス SSP として、1 ゲート選択期間に応じたパルスが供給される。

40

【0085】

また、各行の画素に画像信号 Data がソース線 125 を介して供給され、ゲート線 124 の電位に応じて画素電極にソース線 125 の電位が供給される。

【0086】

また、表示制御回路 113 がスイッチング素子 127 の端子 126A にスイッチング素子 127 を導通状態とする電位を供給し、端子 126B を介して共通電極に共通電位を供給する。

【0087】

一方、期間 1402 は、静止画を表示する期間である。次に、期間 1402 におけるタイミングチャートを説明する。期間 1402 では、クロック信号 GCK、スタートパルス GSP、クロック信号 SCK、及びスタートパルス SSP は共に停止する。また、期間 14

50

02において、ソース線125に供給していた画像信号Dataは停止する。クロック信号GCK及びスタートパルスGSPが共に停止する期間1402では、トランジスタ214が非導通状態となり画素電極の電位が浮遊状態となる。

【0088】

また、表示制御回路113がスイッチング素子127の端子126Aにスイッチング素子127を非導通状態とする電位を供給し、共通電極の電位を浮遊状態にする。

【0089】

期間1402では、液晶素子215の両端子の電極、即ち画素電極及び共通電極の電位を浮遊状態にして、新たに電位を供給することなく、静止画の表示を行うことができる。

【0090】

また、ゲート線側駆動回路121A、及びソース線側駆動回路121Bに供給するクロック信号、及びスタートパルスを停止することにより低消費電力化を図ることができる。

【0091】

特に、トランジスタ214及びスイッチング素子127にオフ電流が低減されたトランジスタを用いることにより、液晶素子215の両端子に加わる電圧が経時的に低下する現象を抑制できる。

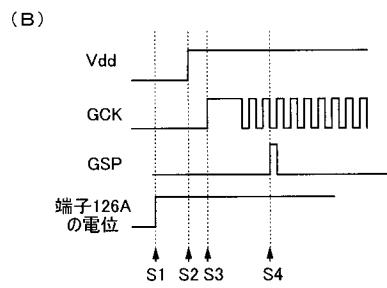

【0092】

次に、動画から静止画に切り替わる期間(図4中の期間1403)、及び静止画から動画に切り替わる期間(図4中の期間1404)における表示制御回路の動作を、図5(A)、(B)を用いて説明する。図5(A)、(B)は表示制御回路が出力する、高電源電位Vdd、クロック信号(ここではGCK)、スタートパルス信号(ここではGSP)、及び端子126Aの電位を示す。

【0093】

動画から静止画に切り替わる期間1403の表示制御回路の動作を図5(A)に示す。表示制御回路は、スタートパルスGSPを停止する(図5(A)のE1、第1のステップ)。パルス出力がシフトレジスタの最終段まで達した後に、複数のクロック信号GCKを停止する(図5(A)のE2、第2のステップ)。次いで、電源電圧を高電源電位Vddから低電源電位Vssにする(図5(A)のE3、第3のステップ)。次いで、端子126Aの電位を、スイッチング素子127が非導通状態となる電位にする(図5(A)のE4、第4のステップ)。

【0094】

以上の手順をもって、駆動回路部121の誤動作を引き起こすことなく、駆動回路部121に供給する信号を停止できる。動画から静止画に切り替わる際の誤動作はノイズを生じ、ノイズは静止画として保持されるため、誤動作が少ない表示制御回路を搭載した液晶表示装置は画像の劣化が少ない静止画を表示できる。

【0095】

次に静止画から動画に切り替わる期間1404の表示制御回路の動作を図5(B)に示す。表示制御回路は、端子126Aの電位をスイッチング素子127が導通状態となる電位にする(図5(B)のS1、第1のステップ)。次いで、電源電圧を低電源電位Vssから高電源電位Vddにする(図5(B)のS2、第2のステップ)。次いで、クロック信号GCKとして先にハイの電位を与えた後、複数のクロック信号GCKを供給する(図5(B)のS3、第3のステップ)。次いでスタートパルス信号GSPを供給する(図5(B)のS4、第4のステップ)。

【0096】

以上の手順をもって、駆動回路部121の誤動作を引き起こすことなく駆動回路部121に駆動信号の供給を再開できる。各配線の電位を適宜順番に動画表示時に戻すことで、誤動作なく駆動回路部の駆動を行うことができる。

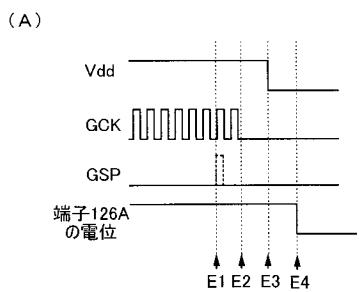

【0097】

また、図6に、動画を表示する期間601及び静止画を表示する期間602における、画像信号の書き込み頻度を模式的に示す。図6中、「W」は画像信号の書き込み期間である

10

20

30

40

50

ことをあらわし、「H」は画像信号を保持する期間であることを示している。また、図6中、期間603は1フレーム期間を表したものであるが、別の期間であってもよい。

【0098】

このように、本実施の形態の液晶表示装置の構成において、期間602で表示される静止画の画像信号は期間604に書き込まれ、期間604で書き込まれた画像信号は、期間602の他の期間で保持される。

【0099】

本実施の形態に例示した液晶表示装置は、静止画を表示する期間において画像信号の書き込み頻度を低減できる。その結果、静止画を表示する際の低消費電力化を図ることができる。

10

【0100】

また、同一の画像を複数回書き換えて静止画を表示する場合、画像の切り替わりが視認できると、人間は目に疲労を感じることもあり得る。本実施の形態の液晶表示装置は、画像信号の書き込み頻度が削減されているため、目の疲労を減らすといった効果もある。

【0101】

特に、本実施の形態の液晶表示装置は、オフ電流が低減されたトランジスタを各画素、並びに共通電極のスイッチング素子に適用することにより、保持容量で電圧を保持できる期間（時間）を長く取ることができる。その結果、画像信号の書き込み頻度を画期的に低減することが可能になり、静止画を表示する際の低消費電力化、及び目の疲労の低減に、顕著な効果を有する。

20

【0102】

（実施の形態2）

本実施の形態においては、上記実施の形態1で説明した液晶表示装置を具備する電子機器の例について説明する。

【0103】

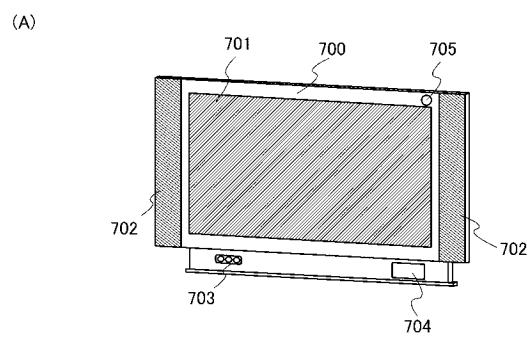

図7（A）には、電子機器であるテレビ受像機の外観図について示したものである。図7（A）では、上記実施の形態1で述べた表示パネルを用いて作製された表示モジュール701が納められた筐体700に、スピーカ702、操作キー703、外部接続端子704、照度センサ705などを有する構成について示している。

30

【0104】

図7（A）に示すテレビ受像機は、動画の他、文字情報または静止画表示を行うことができる。また、表示部の一部の領域のみを動画表示とし、その他の領域を静止画表示とすることもできる。なお静止画の表示は、文字、図形、記号、写真、模様若しくは絵画若しくはこれらの結合又はこれらと色彩の結合を含むものである。

【0105】

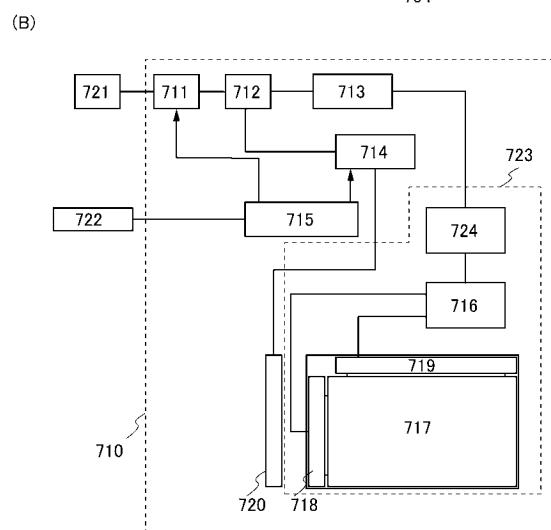

図7（B）には、テレビ受像機の主要な構成についてのブロック図を示す。図7（B）に示すテレビ受像機710は、チューナ711、デジタル復調回路712、映像信号処理回路713、音声信号処理回路714、表示調節回路715、表示制御回路716、表示パネル717、ゲート線側駆動回路718、ソース線側駆動回路719、スピーカ720、画像処理回路724を有する。

40

【0106】

チューナ711はアンテナ721より映像信号と音声信号を受信する。デジタル復調回路712は、チューナ711からの信号を、デジタル信号の映像信号と音声信号に復調する回路である。映像信号処理回路713は、デジタル信号の映像信号を赤、緑、青の各色に対応した色信号に変換する等の処理を行うための回路である。音声信号処理回路714は、デジタル信号の音声信号を、スピーカ720で音声として出力するための信号に変換する等の処理を行うための回路である。表示調節回路715は受信局（受信周波数）及び音量の制御情報を外部入力部722から受け、チューナ711又は音声信号処理回路714に信号を送信するための回路である。

【0107】

50

また、表示制御回路 716、表示パネル 717、ゲート線側駆動回路 718、ソース線側駆動回路 719、画像処理回路 724 は、それぞれ上記実施の形態 1 で説明した表示制御回路 113、表示パネル 120、ソース線側駆動回路 121B、ゲート線側駆動回路 121A、画像処理回路 110 に相当する。すなわち、点線部 723 が、上記実施の形態 1 で述べた液晶表示装置 100 に相当する構成となる。なお、表示制御回路 716 及び画像処理回路 724 の機能は、上述の映像信号処理回路 713 で兼ねる構成であってもよい。そのため、画像信号の書き換え回数を削減する構成とすることができますため、書き換えによるちらつきを緩和させ、目の疲労を減らすといった効果もある。

#### 【0108】

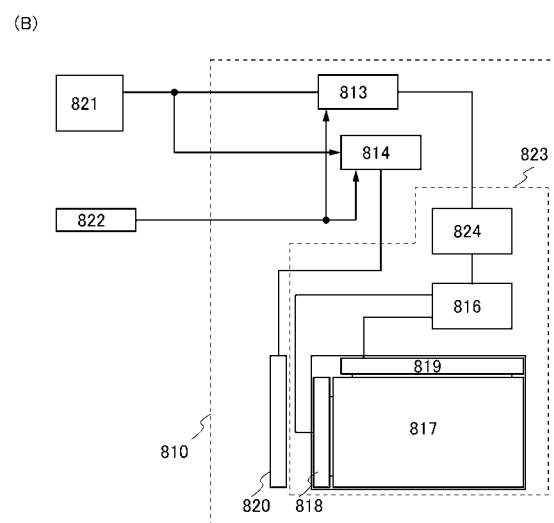

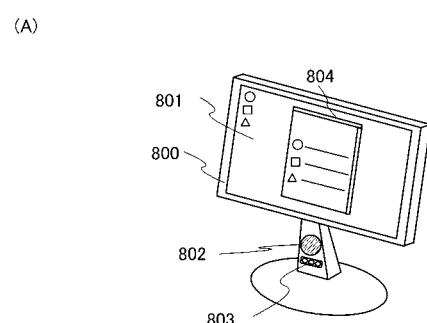

次いで図 8 (A) には、電子機器である電子計算機 (パーソナルコンピュータ) 用途のモニター (PC モニターともいう) の外観図について示したものである。図 8 (A) では、上記実施の形態 1 で述べた表示パネルを用いて作製された表示モジュール 801 が納められた筐体 800 に、スピーカ 802、外部接続端子 803 などを有する構成について示している。なお図 8 (A) には、PC モニターであることを理解するために、ウインドウ型表示部 804 を示している。

10

#### 【0109】

なお、図 8 (A) では、いわゆるデスクトップ型の PC モニターの構成について示しているが、他にもノート型パーソナルコンピュータ用途の PC モニターであってもよい。なお PC モニターの表示は、動画の他、文字、図形、記号、写真、模様若しくは絵画若しくはこれらの結合又はこれらと色彩の結合を含む静止画を含むものである。

20

#### 【0110】

図 8 (B) には、PC モニターの主要な構成についてのブロック図を示す。図 8 (B) に示す PC モニター 810 は、映像信号処理回路 813、音声信号処理回路 814、表示制御回路 816、表示パネル 817、ゲート線側駆動回路 818、ソース線側駆動回路 819、スピーカ 820、画像処理回路 824 を有する。

30

#### 【0111】

映像信号処理回路 813 は、CPU 等の外部演算回路 821 からの映像信号を赤、緑、青の各色に対応した色信号に変換する等の処理を行うための回路である。音声信号処理回路 814 は、CPU 等の外部演算回路 821 からの音声信号を、スピーカ 820 で音声として出力するための信号に変換する等の処理を行うための回路である。また映像信号処理回路 813 及び音声信号処理回路 814 は、キーボード等の外部操作手段 822 による操作に応じて、出力する信号を可変する。

30

#### 【0112】

また、表示制御回路 816、表示パネル 817、ゲート線側駆動回路 818、ソース線側駆動回路 819、画像処理回路 824 は、それぞれ上記実施の形態 1 で説明した表示制御回路 113、表示パネル 120、ソース線側駆動回路 121B、ゲート線側駆動回路 121A、画像処理回路 110 に相当する。すなわち、点線部 823 が、上記実施の形態 1 で述べた液晶表示装置 100 に相当する構成となる。なお、表示制御回路 816 及び画像処理回路 824 の機能は、上述の映像信号処理回路 813 で兼ねる構成であってもよい。そのため、画像信号の書き換え回数を削減する構成とすることができますため、書き換えによるちらつきを緩和させ、目の疲労を減らすといった効果もある。

40

#### 【0113】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0114】

##### (実施の形態 3)

本実施の形態では、本明細書に開示する液晶表示装置に用いることのできるバックライト (バックライト部、バックライトユニット) の構成の例について図 9 及び図 10 を用いて説明する。

#### 【0115】

50

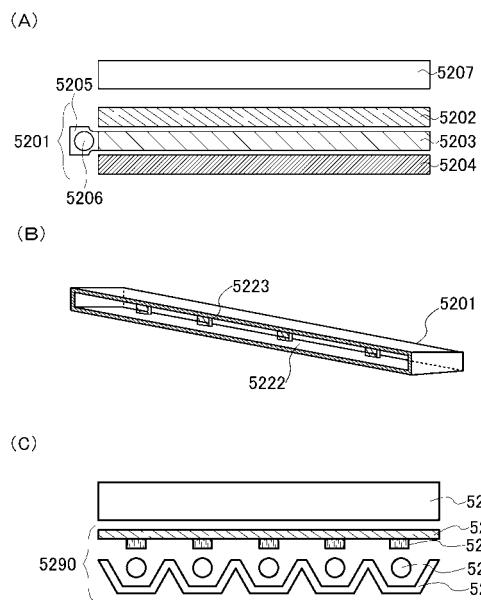

図9(A)は、エッジライト方式と呼ばれるバックライト部5201と、表示パネル5207とを有している液晶表示装置の一例を示す。エッジライト式とは、バックライト部の端部に光源を配置し、その光源の光を発光面全体から放射する方式である。

【0116】

バックライト部5201は、拡散板5202(拡散シートともいう)、導光板5203、反射板5204、ランプリフレクタ5205及び光源5206によって構成される。なおバックライト部5201は他にも輝度向上フィルム等を設ける構成としてもよい。

【0117】

光源5206は必要に応じて発光する機能を有している。例えば、光源5206としては冷陰極管(CCFL: Cold Cathode Fluorescent Lamp)、発光ダイオード、又はEL素子などが用いられる。

【0118】

図9(B)は、エッジライト式のバックライト部の詳細な構成を示す図である。なお、拡散板、導光板及び反射板などはその説明を省略する。

【0119】

図9(B)に示すバックライト部5201は、光源として発光ダイオード(LED)5223を用いた構成である。例えば、白色に発する発光ダイオード(LED)5223は所定の間隔に配置される。そして、発光ダイオード(LED)5223からの光を効率よく反射させるため、ランプリフレクタ5222が設けられている。なおフィールドシーケンシャル方式と組み合わせて表示を行う場合には、光源として各色RGBの発光ダイオード(LED)を用いる構成としてもよい。

【0120】

図9(C)は、直下型と呼ばれるバックライト部と、液晶パネルとを有する液晶表示装置の一例を示す。直下型とは、発光面の直下に光源を配置することで、その光源の光を発光面全体から放射する方式である。

【0121】

バックライト部5290は、拡散板5291、遮光部5292、ランプリフレクタ5293、光源5294及び液晶パネル5295によって構成される。

【0122】

光源5294は、必要に応じて発光する機能を有している。例えば、光源5294としては、冷陰極管、発光ダイオード、又は発光素子であるEL素子(例えば有機エレクトロルミネッセンス素子)などが用いられる。

【0123】

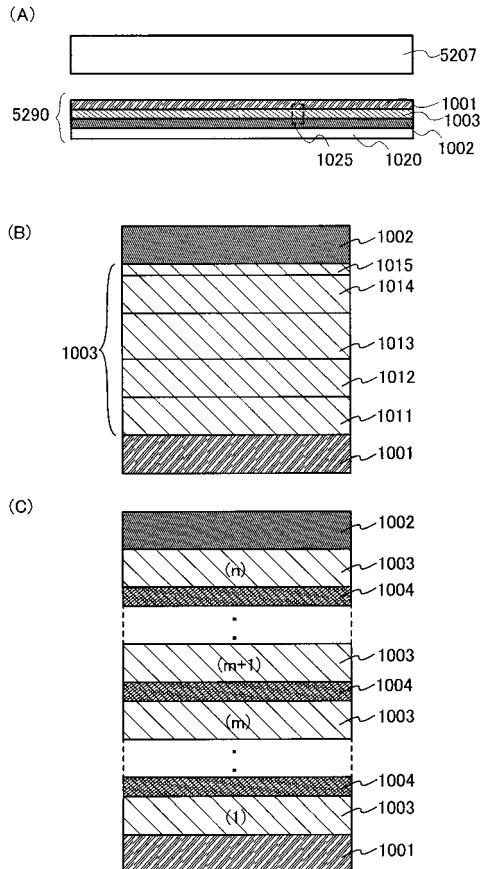

なお、直下型と呼ばれるバックライト部において、光源に発光素子であるEL素子を用いることによりバックライト部の薄型化をはかることができる。EL素子を用いたバックライト部の一例を図10(A)に示す。

【0124】

図10(A)で示すバックライト部5290は、基板1020上に設けられたEL素子1025を含む。EL素子1025は、一対の電極(陽極1001、陰極1002)間に発光領域を含むEL層1003が挟まれた構造を有する。なお、EL素子1025を覆うように基板やフィルム、保護膜などを設け、EL素子1025を封止する構成としてもよい。

【0125】

本実施の形態では、陽極1001を通過してEL層1003からの光を表示パネルに照射する構成であるので、陽極1001として光を透過する材料、例えば酸化インジウムスズ(ITO)等の材料を用いて構成すればよい。また陰極1002としては光を反射する材料、例えばアルミニウム膜等の材料を用いて構成すればよい。陽極1001および陰極1002のうち、少なくとも一方が透光性を有すればよい。

【0126】

図10(A)のEL素子1025の素子構造の例を図10(B)(C)に示す。

10

20

30

40

50

## 【0127】

EL層1003は、少なくとも発光層1013を含んで形成されればよく、発光層1013以外の機能層を含む積層構造であっても良い。発光層1013以外の機能層としては、正孔注入性の高い物質、正孔輸送性の高い物質、電子輸送性の高い物質、電子注入性の高い物質、バイポーラ性（電子及び正孔の輸送性の高い物質）の物質等を含む層を用いることができる。具体的には、正孔注入層1011、正孔輸送層1012、発光層1013、電子輸送層1014、電子注入層1015等の機能層を適宜組み合わせて用いることができる。

## 【0128】

次に、上述したEL素子1025に用いることができる材料について、具体的に説明する。

## 【0129】

陽極1001としては、仕事関数の大きい（具体的には4.0eV以上が好ましい。）金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることが好ましい。具体的には、例えば、酸化インジウム-酸化スズ（ITO：Indium Tin Oxide）、珪素若しくは酸化珪素を含有した酸化インジウム-酸化スズ、酸化インジウム-酸化亜鉛（IZO：Indium Zinc Oxide）、酸化タンゲステン及び酸化亜鉛を含有した酸化インジウム等の導電性金属酸化物が挙げられる。

## 【0130】

これらの導電性金属酸化物膜は、通常スパッタにより成膜されるが、ゾル-ゲル法などを応用して作製しても構わない。例えば、酸化インジウム-酸化亜鉛（IZO）は、酸化インジウムに対し1～20wt%の酸化亜鉛を加えたターゲットを用いてスパッタリング法により形成することができる。また、酸化タンゲステン及び酸化亜鉛を含有した酸化インジウムは、酸化インジウムに対し酸化タンゲステンを0.5～5wt%、酸化亜鉛を0.1～1wt%含有したターゲットを用いてスパッタリング法により形成することができる。

## 【0131】

この他、陽極1001に用いられる材料としては、金（Au）、白金（Pt）、ニッケル（Ni）、タンゲステン（W）、クロム（Cr）、モリブデン（Mo）、鉄（Fe）、コバルト（Co）、銅（Cu）、パラジウム（Pd）、チタン（Ti）、または金属材料の窒化物（例えば、窒化チタン等）、モリブデン酸化物、バナジウム酸化物、ルテニウム酸化物、タンゲステン酸化物、マンガン酸化物、チタン酸化物等が挙げられる。

## 【0132】

陰極1002としては、仕事関数の小さい（具体的には3.8eV以下であることが好ましい）金属、合金、電気伝導性化合物、およびこれらの混合物などを用いることができる。このような陰極材料の具体例としては、元素周期表の第1族または第2族に属する元素、すなわちリチウム（Li）やセシウム（Cs）等のアルカリ金属、およびマグネシウム（Mg）、カルシウム（Ca）、ストロンチウム（Sr）等のアルカリ土類金属、およびこれらを含む合金（MgAg、AlLi）、ユウロピウム（Eu）、イッテルビウム（Yb）等の希土類金属およびこれらを含む合金等が挙げられる。なお、アルカリ金属、アルカリ土類金属、これらを含む合金の膜は、真空蒸着法を用いて形成することができる。また、アルカリ金属またはアルカリ土類金属を含む合金はスパッタリング法により形成することも可能である。また、銀ペーストなどをインクジェット法などにより成膜することも可能である。

## 【0133】

この他、アルカリ金属化合物、アルカリ土類金属化合物、または希土類金属の化合物（例えば、フッ化リチウム（LiF）、酸化リチウム（Li<sub>x</sub>O）、フッ化セシウム（CsF）、フッ化カルシウム（CaF<sub>2</sub>）、フッ化エルビウム（ErF<sub>3</sub>）など）の薄膜と、アルミニウム等の金属膜とを積層することによって、陰極1002を形成することも可能である。

10

20

30

40

50

## 【0134】

次に、E L 層 1003 を構成する各層に用いる材料について、以下に具体例を示す。

## 【0135】

正孔注入層 1011 は、正孔注入性の高い物質を含む層である。正孔注入性の高い物質としては、例えば、モリブデン酸化物やバナジウム酸化物、ルテニウム酸化物、タンクスステン酸化物、マンガン酸化物等を用いることができる。この他、フタロシアニン（略称：H<sub>2</sub>PC）や銅フタロシアニン（CuPC）等のフタロシアニン系の化合物、4,4'-ビス[N-(4-ジフェニルアミノフェニル)-N-フェニルアミノ]ビフェニル（略称：DPA B）、N,N'-ビス[4-[ビス(3-メチルフェニル)アミノ]フェニル]-N,N'-ジフェニル-[1,1'-ビフェニル]-4,4'-ジアミン（略称：DNTPD）等の芳香族アミン化合物、或いはポリ(3,4-エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)（PEDOT/PSS）等の高分子等によっても正孔注入層 1011 を形成することができる。さらに、トリス(p-エナミン置換-アミノフェニル)アミン化合物、2,7-ジアミノ-9-フルオレニリデン化合物、トリ(p-N-エナミン置換-アミノフェニル)ベンゼン化合物、アリール基が少なくとも 1 つ置換したエテニル基が一つ又は 2 つ置換したピレン化合物、N,N'-ジ(ビフェニル-4-イル)-N,N'-ジフェニルビフェニル-4,4'-ジアミン、N,N,N',N'-テトラ(ビフェニル-4-イル)ビフェニル-4,4'-ジアミン、N,N,N',N'-テトラ(ビフェニル-4-イル)-3,3'-ジエチルビフェニル-4,4'-ジアミン、2,2'--(メチレンジ-4,1-フェニレン)ビス[4,5-ビス(4-メトキシフェニル)-2H-1,2,3-トリアゾール]、2,2'-(ビフェニル-4,4'-ジイル)ビス(4,5-ジフェニル-2H-1,2,3-トリアゾール)、2,2'-(3,3'-ジメチルビフェニル-4,4'-ジイル)ビス(4,5-ジフェニル-2H-1,2,3-トリアゾール)、ビス[4-(4,5-ジフェニル-2H-1,2,3-トリアゾール-2-イル)フェニル]（メチル）アミン等を用いて正孔注入層 1011 を形成することができる。

## 【0136】

また、正孔注入層 1011 として、有機化合物と無機化合物（好ましくは、有機化合物に対して電子受容性を示す無機化合物）とを複合してなる正孔注入性複合材料を用いることができる。正孔注入性複合材料は、有機化合物と無機化合物との間で電子の授受が行われ、キャリア密度が増大するため、正孔注入性、正孔輸送性に優れている。

## 【0137】

また、正孔注入層 1011 として正孔注入性複合材料を用いた場合、陽極 1001 とオーム接觸をすることが可能となるため、仕事関数に関わらず陽極 1001 を形成する材料を選ぶことができる。

## 【0138】

正孔注入性複合材料に用いる無機化合物としては、遷移金属の酸化物であることが好ましい。また元素周期表における第 4 族乃至第 8 族に属する金属の酸化物を挙げることができる。具体的には、酸化バナジウム、酸化ニオブ、酸化タンタル、酸化クロム、酸化モリブデン、酸化タンクスステン、酸化マンガン、酸化レニウムは電子受容性が高いため好ましい。中でも特に、酸化モリブデンは大気中で安定であり、吸湿性が低く、扱いやすいため好ましい。

## 【0139】

正孔注入性複合材料に用いる有機化合物としては、芳香族アミン化合物、カルバゾール誘導体、芳香族炭化水素、高分子化合物（オリゴマー、デンドリマー、ポリマー等）など、種々の化合物を用いることができる。なお、正孔注入性複合材料に用いる有機化合物としては、正孔輸送性の高い有機化合物であることが好ましい。具体的には、10<sup>-6</sup> cm<sup>2</sup>/Vs 以上の正孔移動度を有する物質であることが好ましい。但し、電子よりも正孔の輸送性の高い物質であれば、これら以外のものを用いてもよい。以下では、正孔注入性複合材料に用いることのできる有機化合物を具体的に列挙する。

10

20

30

40

50

## 【0140】

例えば、芳香族アミン化合物としては、N,N'-ジ(p-トリル)-N,N'-ジフェニル-p-フェニレンジアミン(略称: DTDPPA)、4,4'-ビス[N-(4-ジフェニルアミノフェニル)-N-フェニルアミノ]ビフェニル(略称: DPAB)、N,N'-ビス[4-[ビス(3-メチルフェニル)アミノ]フェニル]-N,N'-ジフェニル-[1,1'-ビフェニル]-4,4'-ジアミン(略称: DNTPD)、1,3,5-トリス[N-(4-ジフェニルアミノフェニル)-N-フェニルアミノ]ベンゼン(略称: DPAA3B)等を挙げができる。

## 【0141】

正孔注入性複合材料に用いることのできるカルバゾール誘導体としては、具体的には、3-[N-(9-フェニルカルバゾール-3-イル)-N-フェニルアミノ]-9-フェニルカルバゾール(略称: PCzPCA1)、3,6-ビス[N-(9-フェニルカルバゾール-3-イル)-N-フェニルアミノ]-9-フェニルカルバゾール(略称: PCzPCA2)、3-[N-(1-ナフチル)-N-(9-フェニルカルバゾール-3-イル)アミノ]-9-フェニルカルバゾール(略称: PCzPCN1)等を挙げができる。

## 【0142】

また、4,4'-ジ(N-カルバゾリル)ビフェニル(略称: CBP)、1,3,5-トリス[4-(N-カルバゾリル)フェニル]ベンゼン(略称: TCPB)、9-[4-(N-カルバゾリル)フェニル-10-フェニルアントラセン(略称: CzPA)、1,4-ビス[4-(N-カルバゾリル)フェニル]-2,3,5,6-テトラフェニルベンゼン等を用いることができる。

## 【0143】

また、正孔注入性複合材料に用いることのできる芳香族炭化水素としては、例えば、2-tert-ブチル-9,10-ジ(2-ナフチル)アントラセン(略称: t-BuDNA)、2-tert-ブチル-9,10-ジ(1-ナフチル)アントラセン、9,10-ビス(3,5-ジフェニルフェニル)アントラセン(略称: DPPA)、2-tert-ブチル-9,10-ビス(4-フェニルフェニル)アントラセン(略称: t-BuDBA)、9,10-ジ(2-ナフチル)アントラセン(略称: DNA)、9,10-ジフェニルアントラセン(略称: DPAnth)、2-tert-ブチルアントラセン(略称: t-BuAnth)、9,10-ビス(4-メチル-1-ナフチル)アントラセン(略称: DMNA)、2-tert-ブチル-9,10-ビス[2-(1-ナフチル)フェニル]アントラセン、9,10-ビス[2-(1-ナフチル)フェニル]アントラセン、2,3,6,7-テトラメチル-9,10-ジ(1-ナフチル)アントラセン、2,3,6,7-テトラメチル-9,10-ジ(2-ナフチル)アントラセン、9,9'-ビアントリル、10,10'-ジフェニル-9,9'-ビアントリル、10,10'-ビス(2-フェニルフェニル)-9,9'-ビアントリル、10,10'-ビス[(2,3,4,5,6-ペンタフェニル)フェニル]-9,9'-ビアントリル、アントラセン、テトラセン、ルブレン、ペリレン、2,5,8,11-テトラ(tert-ブチル)ペリレン等が挙げられる。また、この他、ペンタセン、コロネン等も用いることができる。このように、 $1 \times 10^{-6} \text{ cm}^2 / \text{Vs}$ 以上の正孔移動度を有し、炭素数14~42である芳香族炭化水素を用いることがより好ましい。

## 【0144】

なお、正孔注入性複合材料に用いることのできる芳香族炭化水素は、ビニル骨格を有していてもよい。ビニル基を有している芳香族炭化水素としては、例えば、4,4'-ビス(2,2-ジフェニルビニル)ビフェニル(略称: DPVBi)、9,10-ビス[4-(2,2-ジフェニルビニル)フェニル]アントラセン(略称: DPVPA)等が挙げられる。

## 【0145】

また、ポリ(N-ビニルカルバゾール)(略称: PVK)やポリ(4-ビニルトリフェニ

10

20

30

40

50

ルアミン) (略称: PVTPA) 等の高分子化合物を用いることもできる。

【0146】

正孔輸送層1012は、正孔輸送性の高い物質を含む層である。正孔輸送性の高い物質としては、例えば、芳香族アミン(すなわち、ベンゼン環-窒素の結合を有するもの)の化合物であることが好ましい。広く用いられている材料として、4,4'-ビス[N-(3-メチルフェニル)-N-フェニルアミノ]ビフェニル、その誘導体である4,4'-ビス[N-(1-ナフチル)-N-フェニルアミノ]ビフェニル(以下、NPBと記す)、4,4',4'''-トリス(N,N-ジフェニル-アミノ)トリフェニルアミン、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニルアミノ]トリフェニルアミンなどのスターバースト型芳香族アミン化合物が挙げられる。ここに述べた物質は、主に  $10^{-6} \text{ cm}^2 / \text{Vs}$  以上の正孔移動度を有する物質である。但し、電子よりも正孔の輸送性の高い物質であれば、これら以外のものを用いてもよい。なお、正孔輸送層1012は、単層のものだけでなく、上記物質の混合層、あるいは二層以上積層したものであってもよい。

10

【0147】

また、PMMAのような電気的に不活性な高分子化合物に、正孔輸送性材料を添加してもよい。

【0148】

また、ポリ(N-ビニルカルバゾール) (略称: PVK) やポリ(4-ビニルトリフェニルアミン) (略称: PVTPA)、ポリ[N-(4-{N'-[4-(4-ジフェニルアミノ)フェニル]フェニル-N'}-フェニルアミノ}フェニル)メタクリルアミド] (略称: PTPDMA) ポリ[N,N'-ビス(4-ブチルフェニル)-N,N'-ビス(フェニル)ベンジジン] (略称: Poly-TPD)などの高分子化合物を用いてもよく、さらに上記高分子化合物に上記正孔輸送性材料を適宜添加してもよい。さらに、トリス(p-エナミン置換-アミノフェニル)アミン化合物、2,7-ジアミノ-9-フルオレニリデン化合物、トリ(p-N-エナミン置換-アミノフェニル)ベンゼン化合物、アリール基が少なくとも1つ置換したエテニル基が一つ又は2つ置換したピレン化合物、N,N'-ジ(ビフェニル-4-イル)-N,N'-ジフェニルビフェニル-4,4'-ジアミン、N,N,N',N'-テトラ(ビフェニル-4-イル)ビフェニル-4,4'-ジアミン、N,N,N',N'-テトラ(ビフェニル-4-イル)-3,3'-ジエチルビフェニル-4,4'-ジアミン、2,2'-(メチレンジ-4,1-フェニレン)ビス[4,5-ビス(4-メトキシフェニル)-2H-1,2,3-トリアゾール]、2,2'-(ビフェニル-4,4'-ジイル)ビス(4,5-ジフェニル-2H-1,2,3-トリアゾール)、2,2'-(3,3'-ジメチルビフェニル-4,4'-ジイル)ビス(4,5-ジフェニル-2H-1,2,3-トリアゾール)、ビス[4-(4,5-ジフェニル-2H-1,2,3-トリアゾール-2-イル)フェニル] (メチル)アミン等も正孔輸送層1012に用いることができる。

20

【0149】

発光層1013は、発光性の物質を含む層であり、種々の材料を用いることができる。例えば、発光性の物質としては、蛍光を発光する蛍光性化合物や燐光を発光する燐光性化合物を用いることができる。以下に、発光層に用いることのできる有機化合物材料を説明する。ただし、EL素子1025に適用可能な材料はこれらに限定されるものではない。

30

【0150】

青色~青緑色の発光は、例えば、ペリレン、2,5,8,11-テトラ-t-ブチルペリレン(略称: TBP)、9,10-ジフェニルアントラセンなどをゲスト材料として用い、適当なホスト材料に分散させることによって得られる。また、4,4'-ビス(2,2-ジフェニルビニル)ビフェニル(略称: DPVBi)などのスチリルアリーレン誘導体や、9,10-ジ-2-ナフチルアントラセン(略称: DNA)、9,10-ビス(2-ナフチル)-2-t-ブチルアントラセン(略称: t-BuDNA)などのアントラセン誘導体から得ることができる。また、ポリ(9,9-ジオクチルフルオレン)等のポリマ

40

50

ーを用いても良い。また、青色発光のゲスト材料としては、スチリルアミン誘導体が好ましく、N,N'-ビス[4-(9H-カルバゾール-9-イル)フェニル]-N,N'-ジフェニルスチルベン-4,4'-ジアミン(略称:YGA2S)や、N,N'-ジフェニル-N,N'-ビス(9-フェニル-9H-カルバゾール-3-イル)スチルベン-4,4'-ジアミン(略称:PCA2S)などが挙げられる。特にYGA2Sは、450nm付近にピークを有しており好ましい。また、ホスト材料としては、アントラセン誘導体が好ましく、9,10-ビス(2-ナフチル)-2-t-ブチルアントラセン(略称:t-BuDNA)や、9-[4-(10-フェニル-9-アントリル)フェニル]-9H-カルバゾール(略称:CzPA)が好適である。特に、CzPAは電気化学的に安定であるため好ましい。

10

### 【0151】

青緑色～緑色の発光は、例えば、クマリン30、クマリン6などのクマリン系色素や、ビス[2-(2,4-ジフルオロフェニル)ピリジナト]ピコリナトイリジウム(略称:FIrpic)、ビス(2-フェニルピリジナト)アセチルアセトナトイリジウム(Ir(ppp)<sub>2</sub>(aacac))などをゲスト材料として用い、適当なホスト材料に分散させることによって得られる。また、上述のペリレンやTBPを5wt%以上の高濃度で適当なホスト材料に分散させることによっても得られる。また、BAlq、Zn(BTz)<sub>2</sub>、ビス(2-メチル-8-キノリノラト)クロロガリウム(Ga(mq)<sub>2</sub>C1)などの金属錯体からも得ることができる。また、ポリ(p-フェニレンビニレン)等のポリマーを用いても良い。また、青緑色～緑色の発光層のゲスト材料としては、アントラセン誘導体が効率の高い発光が得られるため好ましい。例えば、9,10-ビス{4-[N-(4-ジフェニルアミノ)フェニル-N-フェニル]アミノフェニル}-2-t-tert-ブチルアントラセン(略称:DPA BPA)を用いることにより、高効率な青緑色発光が得られる。また、2位にアミノ基が置換されたアントラセン誘導体は高効率な緑色発光が得られるため好ましく、N-(9,10-ジフェニル-2-アントリル)-N,9-ジフェニル-9H-カルバゾール-3-アミン(略称:2PCA PA)が特に長寿命であり好適である。これらのホスト材料としてはアントラセン誘導体が好ましく、先に述べたCzPAが電気化学的に安定であるため好ましい。また、緑色発光と青色発光を組み合わせ、青色から緑色の波長領域に2つのピークを持つEL素子1025を作製する場合、青色発光層のホストにCzPAのような電子輸送性のアントラセン誘導体を用い、緑色発光層のホストにNPBのようなホール輸送性の芳香族アミン化合物を用いると、青色発光層と緑色発光層との界面で発光が得られるため好ましい。すなわちこの場合、2PCA PAのような緑色発光材料のホストとしては、NPBの如き芳香族アミン化合物が好ましい。

20

30

40

### 【0152】

黄色～橙色の発光は、例えば、ルブレン、4-(ジシアノメチレン)-2-[p-(ジメチルアミノ)スチリル]-6-メチル-4H-ピラン(略称:DCM1)、4-(ジシアノメチレン)-2-メチル-6-(9-ジュロリジル)エテニル-4H-ピラン(略称:DCM2)、ビス[2-(2-チエニル)ピリジナト]アセチルアセトナトイリジウム(Ir(thp)<sub>2</sub>(aacac))、ビス(2-フェニルキノリナト)アセチルアセトナトイリジウム(Ir(pq)<sub>2</sub>(aacac))などをゲスト材料として用い、適当なホスト材料に分散させることによって得られる。特に、ゲスト材料としてルブレンのようなテトラセン誘導体が、高効率かつ化学的に安定であるため好ましい。この場合のホスト材料としては、NPBのような芳香族アミン化合物が好ましい。他のホスト材料としては、ビス(8-キノリノラト)亜鉛(II)(略称:Znq<sub>2</sub>)やビス[2-シンナモイル-8-キノリノラト]亜鉛(略称:Znsq<sub>2</sub>)などの金属錯体を用いることができる。また、ポリ(2,5-ジアルコキシ-1,4-フェニレンビニレン)等のポリマーを用いても良い。

50

### 【0153】

橙色～赤色の発光は、例えば、4-(ジシアノメチレン)-2,6-ビス[p-(ジメチルアミノ)スチリル]-4H-ピラン(略称:Bi s DCM)、4-(ジシアノメチレン

50

) - 2 , 6 - ビス [ 2 - ( ジュロリジン - 9 - イル ) エテニル ] - 4 H - ピラン ( 略称 : BisDCJ ) 、 4 - ( ジシアノメチレン ) - 2 - メチル - 6 - ( 9 - ジュロリジル ) エテニル - 4 H - ピラン ( 略称 : DCM2 ) 、 ビス [ 2 - ( 2 - チエニル ) ピリジナト ] アセチルアセトナトイリジウム ( 略称 : Ir( thp )<sub>2</sub> ( acac ) ) 、 などをゲスト材料として用い、適当なホスト材料に分散させることによって得られる。ビス ( 8 - キノリノラト ) 亜鉛 ( II ) ( 略称 : Znq<sub>2</sub> ) やビス [ 2 - シンナモイル - 8 - キノリノラト ] 亜鉛 ( 略称 : Znsq<sub>2</sub> ) などの金属錯体からも得ることができる。また、ポリ ( 3 - アルキルチオフェン ) 等のポリマーを用いても良い。赤色発光を示すゲスト材料としては、 4 - ( ジシアノメチレン ) - 2 , 6 - ビス [ p - ( ジメチルアミノ ) スチリル ] - 4 H - ピラン ( 略称 : BisDCM ) 、 4 - ( ジシアノメチレン ) - 2 , 6 - ビス [ 2 - ( ジュロリジン - 9 - イル ) エテニル ] - 4 H - ピラン ( 略称 : BisDCJ ) 、 4 - ( ジシアノメチレン ) - 2 - メチル - 6 - ( 9 - ジュロリジル ) エテニル - 4 H - ピラン ( 略称 : DCM2 ) 、 { 2 - イソプロピル - 6 - [ 2 - ( 2 , 3 , 6 , 7 - テトラヒドロ - 1 , 1 , 7 , 7 - テトラメチル - 1 H , 5 H - ベンゾ [ ij ] キノリジン - 9 - イル ) エテニル ] - 4 H - ピラン - 4 - イリデン } プロパンジニトリル ( 略称 : DCJTI ) 、 { 2 , 6 - ビス [ 2 - ( 2 , 3 , 6 , 7 - テトラヒドロ - 8 - メトキシ - 1 , 1 , 7 , 7 - テトラメチル - 1 H , 5 H - ベンゾ [ ij ] キノリジン - 9 - イル ) エテニル ] - 4 H - ピラン - 4 - イリデン } プロパンジニトリル ( 略称 : BisDCJTM ) のような 4 H - ピラン誘導体が高効率であり、好ましい。特に、 DCJTI 、 BisDCJTM は、 620 nm 付近に発光ピークを有するため好ましい。

10 20

## 【 0154 】

なお、発光層 1013 としては、上述した発光性の物質 ( ゲスト材料 ) を他の物質 ( ホスト材料 ) に分散させた構成としてもよい。発光性の高い物質を分散させるための物質としては、各種のものを用いることができ、発光性の高い物質よりも最低空軌道準位 ( LUMO 準位 ) が高く、最高被占有軌道準位 ( HOMO 準位 ) が低い物質を用いることが好ましい。

## 【 0155 】

発光性の物質を分散させるための物質としては、具体的には、トリス ( 8 - キノリノラト ) アルミニウム ( III ) ( 略称 : Alq ) 、トリス ( 4 - メチル - 8 - キノリノラト ) アルミニウム ( III ) ( 略称 : Almq<sub>3</sub> ) 、 ビス ( 10 - ヒドロキシベンゾ [ h ] キノリナト ) ベリリウム ( II ) ( 略称 : BeBq<sub>2</sub> ) 、 ビス ( 2 - メチル - 8 - キノリノラト ) ( 4 - フェニルフェノラト ) アルミニウム ( III ) ( 略称 : BALq ) 、 ビス ( 8 - キノリノラト ) 亜鉛 ( II ) ( 略称 : Znq<sub>2</sub> ) 、 ビス [ 2 - ( 2 - ベンゾオキサゾリル ) フェノラト ] 亜鉛 ( II ) ( 略称 : ZnPBO ) 、 ビス [ 2 - ( 2 - ベンゾチアゾリル ) フェノラト ] 亜鉛 ( II ) ( 略称 : ZnBTZ ) などの金属錯体、 2 - ( 4 - ビフェニリル ) - 5 - ( 4 - tert - ブチルフェニル ) - 1 , 3 , 4 - オキサジアゾール ( 略称 : PBD ) 、 1 , 3 - ビス [ 5 - ( p - tert - ブチルフェニル ) - 1 , 3 , 4 - オキサジアゾール - 2 - イル ] ベンゼン ( 略称 : OXD - 7 ) 、 3 - ( 4 - ビフェニリル ) - 4 - フェニル - 5 - ( 4 - tert - ブチルフェニル ) - 1 , 2 , 4 - トリアゾール ( 略称 : TAZ ) 、 2 , 2 ' , 2 ' ' - ( 1 , 3 , 5 - ベンゼントリイル ) トリス ( 1 - フェニル - 1 H - ベンゾイミダゾール ) ( 略称 : TPBI ) 、 バソフェナントロリン ( 略称 : BPhen ) 、 バソキュプロイン ( 略称 : BCP ) などの複素環化合物や、 9 - [ 4 - ( 10 - フェニル - 9 - アントリル ) フェニル ] - 9 H - カルバゾール ( 略称 : CZPA ) 、 3 , 6 - ジフェニル - 9 - [ 4 - ( 10 - フェニル - 9 - アントリル ) フェニル ] - 9 H - カルバゾール ( 略称 : DPCZPA ) 、 9 , 10 - ビス ( 3 , 5 - ジフェニルフェニル ) アントラセン ( 略称 : DPBA ) 、 9 , 10 - ジ ( 2 - ナフチル ) アントラセン ( 略称 : DNA ) 、 2 - tert - ブチル - 9 , 10 - ジ ( 2 - ナフチル ) アントラセン ( 略称 : t - BuDNA ) 、 9 , 9 ' - ビアントリル ( 略称 : BANT ) 、 9 , 9 ' - ( スチルベン - 3 , 3 ' - ジイル ) ジフェナントレン ( 略称 : DPNS ) 、 9 , 9 ' - ( スチルベン - 4 , 4 ' - ジイル ) ジフェナントレン ( 略称 : DPNS2 ) 、 3 , 3 ' , 3 ' - 40 40 50

’ - (ベンゼン - 1 , 3 , 5 - トリイル) トリピレン (略称: T P B 3 ) 、 9 , 1 0 - ジフェニルアントラセン (略称: D P A n t h ) 、 6 , 1 2 - ジメトキシ - 5 , 1 1 - ジフェニルクリセンなどの縮合芳香族化合物、 N , N - ジフェニル - 9 - [ 4 - ( 1 0 - フェニル - 9 - アントリル ) フェニル ] - 9 H - カルバゾール - 3 - アミン (略称: C z A 1 P A ) 、 4 - ( 1 0 - フェニル - 9 - アントリル ) トリフェニルアミン (略称: D P h P A ) 、 N , 9 - ジフェニル - N - [ 4 - ( 1 0 - フェニル - 9 - アントリル ) フェニル ] - 9 H - カルバゾール - 3 - アミン (略称: P C A P A ) 、 N , 9 - ジフェニル - N - { 4 - [ 4 - ( 1 0 - フェニル - 9 - アントリル ) フェニル ] フェニル } - 9 H - カルバゾール - 3 - アミン (略称: P C A P B A ) 、 N - ( 9 , 1 0 - ジフェニル - 2 - アントリル ) - N , 9 - ジフェニル - 9 H - カルバゾール - 3 - アミン (略称: 2 P C A P A ) 、 N P B (または - N P D ) 、 T P D 、 D F L D P B i 、 B S P B などの芳香族アミン化合物などを用いることができる。

10

## 【 0 1 5 6 】

また、発光性の物質を分散させるための物質は複数種用いることができる。例えば、結晶化を抑制するためにルブレン等の結晶化を抑制する物質をさらに添加してもよい。また、発光性の物質へのエネルギー移動をより効率良く行うために N P B 、あるいは A l q 等をさらに添加してもよい。

## 【 0 1 5 7 】

発光性の物質を他の物質に分散させた構成とすることにより、発光層 1 0 1 3 の結晶化を抑制することができる。また、発光性の物質の濃度が高いことによる濃度消光を抑制することができる。

20

## 【 0 1 5 8 】

電子輸送層 1 0 1 4 は、電子輸送性の高い物質を含む層である。電子輸送性の高い物質としては、例えば、トリス ( 8 - キノリノラト ) アルミニウム ( I I I ) (略称: A l q ) 、トリス ( 4 - メチル - 8 - キノリノラト ) アルミニウム ( I I I ) (略称: A l m q <sub>3</sub> ) 、ビス ( 1 0 - ヒドロキシベンゾ [ h ] キノリナト ) ベリリウム (略称: B e B q <sub>2</sub> ) 、ビス ( 2 - メチル - 8 - キノリノラト ) ( 4 - フェニルフェノラト ) アルミニウム (略称: B A l q ) など、キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる層である。また、この他ビス [ 2 - ( 2 - ヒドロキシフェニル ) ベンゾオキサゾラト ] 亜鉛 (略称: Z n ( B O X ) <sub>2</sub> ) 、ビス [ 2 - ( 2 - ヒドロキシフェニル ) ベンゾチアゾラト ] 亜鉛 (略称: Z n ( B T Z ) <sub>2</sub> ) などのオキサゾール系、チアゾール系配位子を有する金属錯体なども用いることができる。さらに、金属錯体以外にも、 2 - ( 4 - ピフェニリル ) - 5 - ( 4 - t e r t - プチルフェニル ) - 1 , 3 , 4 - オキサジアゾール (略称: P B D ) や、 1 , 3 - ビス [ 5 - ( p - t e r t - プチルフェニル ) - 1 , 3 , 4 - オキサジアゾール - 2 - イル ] ベンゼン (略称: O X D - 7 ) 、 3 - ( 4 - ピフェニリル ) - 4 - フェニル - 5 - ( 4 - t e r t - プチルフェニル ) - 1 , 2 , 4 - トリアゾール (略称: T A Z ) 、バソフェナントロリン (略称: B P h e n ) 、バソキュプロイン (略称: B C P ) 、ビス [ 3 - ( 1 H - ベンゾイミダゾール - 2 - イル ) フルオレン - 2 - オラト ] 亜鉛 ( I I ) 、ビス [ 3 - ( 1 H - ベンゾイミダゾール - 2 - イル ) フルオレン - 2 - オラト ] ベリリウム ( I I ) 、ビス [ 2 - ( 1 H - ベンゾイミダゾール - 2 - イル ) デベンゾ [ b , d ] フラン - 3 - オラト ] ( フェノラト ) アルミニウム ( I I I ) 、ビス [ 2 - ( ベンゾオキサゾール - 2 - イル ) - 7 , 8 - メチレンジオキシジベンゾ [ b , d ] フラン - 3 - オラト ] ( 2 - ナフトラト ) アルミニウム ( I I I ) なども用いることができる。ここに述べた物質は、主に  $10^{-6} \text{ cm}^2 / \text{V s}$  以上の電子移動度を有する物質である。なお、正孔よりも電子の輸送性の高い物質であれば、上記以外の物質を電子輸送層 1 0 1 4 として用いても構わない。また、電子輸送層 1 0 1 4 は、単層のものだけでなく、上記物質からなる層が二層以上積層したものとしてもよい。

30

## 【 0 1 5 9 】

電子注入層 1 0 1 5 は、電子注入性の高い物質を含む層である。電子注入性の高い物質としては、フッ化リチウム ( L i F ) 、フッ化セシウム ( C s F ) 、フッ化カルシウム ( C

40

10

20

30

40

50

$a F_2$  ) 等のアルカリ金属、アルカリ土類金属、またはこれらの化合物が挙げられる。また、有機化合物（好ましくは、電子輸送性を有する有機化合物）と無機化合物（好ましくは、アルカリ金属、アルカリ土類金属、希土類金属、またはそれらの化合物）とを複合してなる電子注入性複合材料を用いることもできる。電子注入性複合材料としては、例えば A 1 q 中にマグネシウム (Mg) を含有させたもの等を用いることができる。この様な構造とすることにより、陰極 1002 からの電子注入効率をより高めることができる。

#### 【 0 1 6 0 】

なお、電子注入層 1015 として、上述した電子注入性複合材料を用いた場合には、仕事関数に関わらず A 1 、 A g 、 I T O 、珪素若しくは酸化珪素を含有した I T O 等様々な導電性材料を陰極 1002 の材料として用いることができる。

10

#### 【 0 1 6 1 】

以上の層を適宜組み合わせて積層することにより、 E L 層 1003 を形成することができる。なお、発光層 1013 を 2 層以上の積層構造としても良い。発光層 1013 を 2 層以上の積層構造とし、各々の発光層に用いる発光物質の種類を変えることにより様々な発光色を得ることができる。また、発光物質として発光色の異なる複数の発光物質を用いることにより、プロードなスペクトルの発光や白色発光を得ることもできる。特に、高輝度が必要とされるバックライト用途には、発光層を積層させた構造が好適である。

#### 【 0 1 6 2 】

また、 E L 層 1003 の形成方法としては、用いる材料に応じて種々の方法（例えば、乾式法や湿式法等）適宜選択することができる。例えば、真空蒸着法、スパッタリング法、インクジェット法、スピンドル法、等を用いることができる。また、各層で異なる方法を用いて形成してもよい。

20

#### 【 0 1 6 3 】

また、本実施の形態に示す E L 素子 1025 の作製方法としては、ドライプロセス（例えば、真空蒸着法、スパッタリング法）、ウェットプロセス（例えば、インクジェット法、スピンドル法等）を問わず、種々の方法を用いて形成することができる。

#### 【 0 1 6 4 】

なお、本実施の形態に示す E L 素子 1025 の構成は、図 10 (C) に示すように一対の電極間に E L 層 1003 が複数積層された構造、所謂、積層型素子の構成であってもよい。但し、 E L 層 1003 が、例えば  $n$  ( $n$  は 2 以上の自然数) 層の積層構造を有する場合には、  $m$  ( $m$  は自然数、  $m$  は 1 以上 ( $n - 1$ ) 以下) 番目の E L 層と、 ( $m + 1$ ) 番目の E L 層との間には、それぞれ中間層 1004 が挟まれた構造を有する。

30

#### 【 0 1 6 5 】

なお、中間層 1004 とは、陽極 1001 と陰極 1002 に電圧を印加したときに、中間層 1004 に接して形成される陽極 1001 側の一方の E L 層 1003 に対して電子を注入する機能を有し、陰極 1002 側の他方の E L 層 1003 に正孔を注入する機能を有する。

#### 【 0 1 6 6 】

中間層 1004 は、上述した有機化合物と無機化合物との複合材料（正孔注入性複合材料や電子注入性複合材料）の他、金属酸化物等の材料を適宜組み合わせて形成することができる。なお、正孔注入性複合材料とその他の材料とを組み合わせて用いることがより好ましい。中間層 1004 に用いるこれらの材料は、キャリア注入性、キャリア輸送性に優れているため、 E L 素子 1025 の低電流駆動、および低電圧駆動を実現することができる。

40

#### 【 0 1 6 7 】

積層型素子の構成において、 E L 層が 2 層積層された構成を有する場合において、第 1 の E L 層から得られる発光の発光色と第 2 の E L 層から得られる発光の発光色を補色の関係にすることによって、白色発光を外部に取り出すことができる。なお、第 1 の E L 層および第 2 の E L 層のそれぞれが補色の関係にある複数の発光層を有する構成としても、白色発光が得られる。補色の関係としては、青色と黄色、あるいは青緑色と赤色などが挙げら

50

れる。青色、黄色、青緑色、赤色に発光する物質としては、例えば、先に列挙した発光物質の中から適宜選択すればよい。

【0168】

以下に、第1のEL層および第2のEL層のそれぞれが補色の関係にある複数の発光層を有し、白色発光が得られる構成の一例を示す。

【0169】

例えば、第1のEL層は、青色～青緑色の波長領域にピークを有する発光スペクトルを示す第1の発光層と、黄色～橙色の波長領域にピークを有する発光スペクトルを示す第2の発光層とを有し、第2のEL層は、青緑色～緑色の波長領域にピークを有する発光スペクトルを示す第3の発光層と、橙色～赤色の波長領域にピークを有する発光スペクトルを示す第4の発光層とを有するものとする。

10

【0170】

この場合、第1のEL層からの発光は、第1の発光層および第2の発光層の両方からの発光を合わせたものであるので、青色～青緑色の波長領域および黄色～橙色の波長領域の両方にピークを有する発光スペクトルを示す。すなわち、第1のEL層は2波長型の白色または白色に近い色の発光を呈する。

20

【0171】

また、第2のEL層からの発光は、第3の発光層および第4の発光層の両方からの発光を合わせたものであるので、青緑色～緑色の波長領域および橙色～赤色の波長領域の両方にピークを有する発光スペクトルを示す。すなわち、第2のEL層は、第1のEL層とは異なる2波長型の白色または白色に近い色の発光を呈する。

20

【0172】

したがって、第1のEL層からの発光および第2のEL層からの発光を重ね合わせることにより、青色～青緑色の波長領域、青緑色～緑色の波長領域、黄色～橙色の波長領域、橙色～赤色の波長領域をカバーする白色発光を得ることができる。

30

【0173】

なお、上述した積層型素子の構成において、積層されるEL層の間に中間層を配置することにより、電流密度を低く保ったまま、高輝度領域での長寿命素子を実現することができる。また、電極材料の抵抗による電圧降下を小さくできるので、大面積での均一発光が可能となる。

30

【0174】

なお図9(A)乃至(C)、図10(A)乃至(C)で説明するバックライト部は、輝度を調整する構成としてもよい。例えば、液晶表示装置の周りの照度に応じて輝度を調整する構成としてもよいし、表示される画像信号に応じて輝度を調整する構成としてもよい。

40

【0175】

なお、カラー表示を行う場合は、カラーフィルタを組み合わせることで表示が可能である。また、他の光学フィルム(偏光フィルム、位相差フィルム、反射防止フィルムなど)も組み合わせて用いることができる。なお、バックライトにRGBの発光ダイオード等を配置し、時分割によりカラー表示する継時加法混色法(フィールドシーケンシャル法)を採用するときには、カラーフィルタを設けない場合もある。

40

【0176】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることが可能である。

【0177】

(実施の形態4)

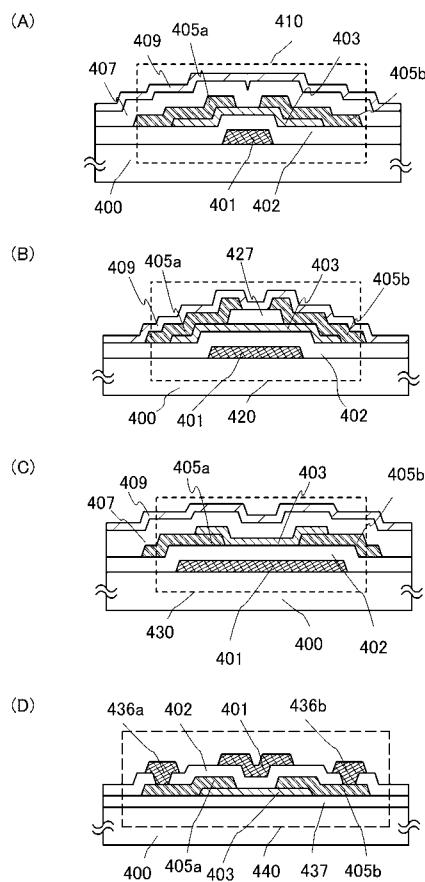

本実施の形態では、本明細書に開示する液晶表示装置に適用できるトランジスタの例を示す。本明細書に開示する液晶表示装置に適用できるトランジスタの構造は特に限定されず、例えばゲート電極が、ゲート絶縁層を介して、酸化物半導体層の上側に配置されるトップゲート構造、又はゲート電極が、ゲート絶縁層を介して、酸化物半導体層の下側に配置されるボトムゲート構造のスタガ型及びプレーナ型などを用いることができる。また、トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、二つ形成され

50

るダブルゲート構造もしくは三つ形成されるトリプルゲート構造であっても良い。また、チャネル領域の上下にゲート絶縁層を介して配置された2つのゲート電極層を有する、デュアルゲート型でもよい。なお、図11(A)乃至(D)にトランジスタの断面構造の一例を以下に示す。図11(A)乃至(D)に示すトランジスタは、半導体として酸化物半導体を用いるものである。酸化物半導体を用いることのメリットは、トランジスタのオン状態における電界効果移動度(最大値で $5\text{ cm}^2/\text{V sec}$ 以上、好ましくは $10\text{ cm}^2/\text{V sec}$ ~ $150\text{ cm}^2/\text{V sec}$ 以下)と、トランジスタのオフ状態において低いオフ電流( $1\text{ aA}/\mu\text{m}$ 未満、さらに好ましくは室温にて $10\text{ zA}/\mu\text{m}$ 未満、且つ、85にて $100\text{ zA}/\mu\text{m}$ 未満)が得られることである。

【0178】

図11(A)に示すトランジスタ410は、ボトムゲート構造のトランジスタの一つであり、逆スタガ型トランジスタともいう。

【0179】

トランジスタ410は、絶縁表面を有する基板400上に、ゲート電極層401、ゲート絶縁層402、酸化物半導体層403、ソース電極層405a、及びドレイン電極層405bを含む。また、トランジスタ410を覆い、酸化物半導体層403に積層する絶縁膜407が設けられている。絶縁膜407上にはさらに保護絶縁層409が形成されている。

【0180】

図11(B)に示すトランジスタ420は、チャネル保護型(チャネルトップ型ともいう)と呼ばれるボトムゲート構造の一つであり逆スタガ型トランジスタともいう。

【0181】

トランジスタ420は、絶縁表面を有する基板400上に、ゲート電極層401、ゲート絶縁層402、酸化物半導体層403、酸化物半導体層403のチャネル形成領域を覆うチャネル保護層として機能する絶縁層427、ソース電極層405a、及びドレイン電極層405bを含む。また、トランジスタ420を覆い、保護絶縁層409が形成されている。

【0182】

図11(C)示すトランジスタ430はボトムゲート型のトランジスタであり、絶縁表面を有する基板である基板400上に、ゲート電極層401、ゲート絶縁層402、ソース電極層405a、ドレイン電極層405b、及び酸化物半導体層403を含む。また、トランジスタ430を覆い、酸化物半導体層403に接する絶縁膜407が設けられている。絶縁膜407上にはさらに保護絶縁層409が形成されている。

【0183】

トランジスタ430においては、ゲート絶縁層402は基板400及びゲート電極層401上に接して設けられ、ゲート絶縁層402上にソース電極層405a、ドレイン電極層405bが接して設けられている。そして、ゲート絶縁層402、及びソース電極層405a、ドレイン電極層405b上に酸化物半導体層403が設けられている。

【0184】

図11(D)に示すトランジスタ440は、トップゲート構造のトランジスタの一つである。トランジスタ440は、絶縁表面を有する基板400上に、絶縁層437、酸化物半導体層403、ソース電極層405a、及びドレイン電極層405b、ゲート絶縁層402、ゲート電極層401を含み、ソース電極層405a、ドレイン電極層405bにそれぞれ配線層436a、配線層436bが接して設けられ電気的に接続している。

【0185】

本実施の形態では、上述のとおり、半導体層として酸化物半導体層403を用いる。酸化物半導体層403に用いる酸化物半導体としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O系酸化物半導体や、三元系金属酸化物であるIn-Ga-Zn-O系酸化物半導体、In-Sn-Zn-O系酸化物半導体、In-Al-Zn-O系酸化物半導体、Sn-Ga-Zn-O系酸化物半導体、Al-Ga-Zn-O系酸化物半導体、Sn-

10

20

30

40

50

A<sub>1</sub>-Zn-O系酸化物半導体や、二元系金属酸化物であるIn-Zn-O系酸化物半導体、Sn-Zn-O系酸化物半導体、A<sub>1</sub>-Zn-O系酸化物半導体、Zn-Mg-O系酸化物半導体、Sn-Mg-O系酸化物半導体、In-Mg-O系酸化物半導体や、In-O系酸化物半導体、Sn-O系酸化物半導体、Zn-O系酸化物半導体などを用いることができる。また、上記酸化物半導体にSiO<sub>2</sub>を含んでもよい。ここで、例えば、In-Ga-Zn-O系酸化物半導体とは、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物膜、という意味であり、その化学量論比はとくに問わない。また、InとGaとZn以外の元素を含んでもよい。

## 【0186】

また、酸化物半導体層403は、化学式InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0、且つ、mは整数でない)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。

## 【0187】

酸化物半導体層403を用いたトランジスタ410、420、430、440は、オフ状態における電流値(オフ電流値)を低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

## 【0188】

また、酸化物半導体層403を用いたトランジスタ410、420、430、440は、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に上記トランジスタを用いることで、色分離を抑制することができ、高画質な画像を提供することができる。また、上記トランジスタは、同一基板上に駆動回路部または画素部に作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

## 【0189】

絶縁表面を有する基板400に使用することができる基板に大きな制限はないが、バリウムホウケイ酸ガラスやアルミニウムホウケイ酸ガラスなどのガラス基板を用いる。

## 【0190】

ポトムゲート構造のトランジスタ410、420、430において、下地膜となる絶縁膜を基板とゲート電極層の間に設けてもよい。下地膜は、基板からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

## 【0191】

ゲート電極層401の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて、単層でまたは積層して形成することができる。

## 【0192】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。例えば、第1のゲート絶縁層としてプラズマCVD法により膜厚50nm以上200nm以下の窒化シリコン層(SiN<sub>y</sub>(y>0))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層(SiO<sub>x</sub>(x>0))を積層して、合計膜厚200nmのゲート絶縁層とする。

## 【0193】

ソース電極層405a、ドレイン電極層405bに用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、または上述し

10

20

30

40

50

た元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）等を用いることができる。また、A1、Cuなどの金属膜の下側又は上側の一方または双方にTi、Mo、Wなどの高融点金属膜またはそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）を積層させた構成としても良い。

【0194】

ソース電極層405a、ドレイン電極層405bに接続する配線層436a、配線層436bのような導電膜も、ソース電極層405a、ドレイン電極層405bと同様な材料を用いることができる。

【0195】

また、ソース電極層405a、ドレイン電極層405b（これと同じ層で形成される配線層を含む）となる導電膜としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）、酸化亜鉛（ZnO）、酸化インジウム酸化スズ合金（In<sub>2</sub>O<sub>3</sub>–SnO<sub>2</sub>、ITOと略記する）、酸化インジウム酸化亜鉛合金（In<sub>2</sub>O<sub>3</sub>–ZnO）またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

10

【0196】

絶縁膜407、427、437は、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの無機絶縁膜を用いることができる。

20

【0197】

また、酸化物半導体層の上方に設けられる保護絶縁層409は、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜を用いることができる。

20

【0198】

また、保護絶縁層409上にトランジスタ起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド、アクリル、ベンゾシクロブテン、等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、平坦化絶縁膜を形成してもよい。

30

【0199】

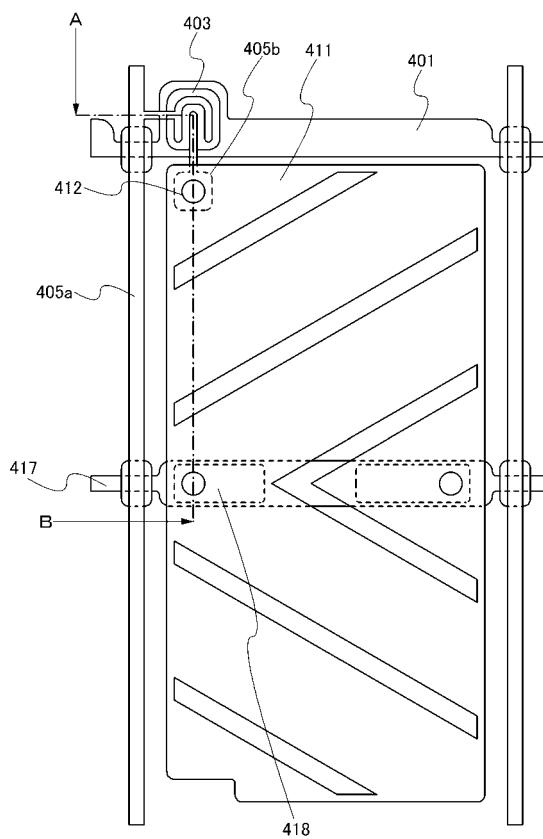

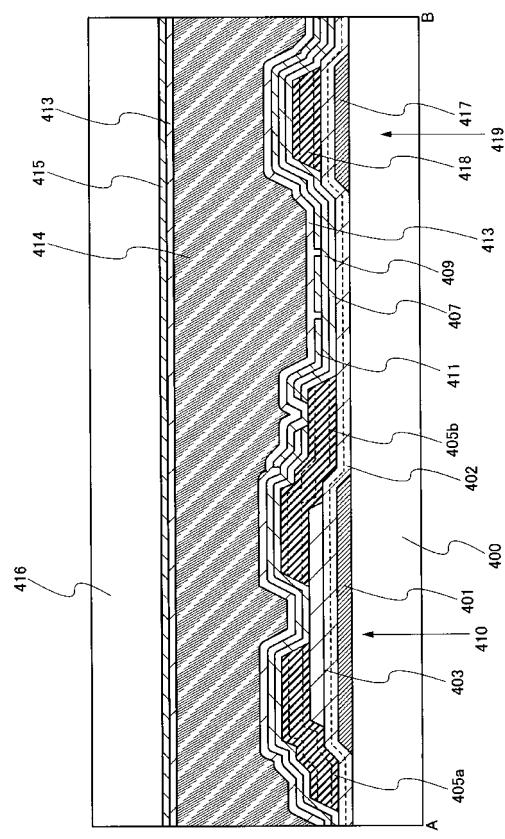

このようなトランジスタを用いた液晶表示装置の画素の一例を図18と図19に示す。図18は画素の平面図を示し、当該図中に示すA-B切断線に対応する断面図を図19に示す。なお、図18はトランジスタ410が形成された基板400の平面図を示すものであり、図19はトランジスタ410が設けられた基板400側の構成に加え、対向基板416や液晶層414が設けられている構成を示す。以下の説明では図18と図19の両方を参照して説明する。

30

【0200】

トランジスタ410の構成は図11(A)と同様であり、ゲート電極層401、ゲート絶縁層402、酸化物半導体層403を有している。画素を構成する場合、ゲート電極層401は一方向に延在するように形成されている。酸化物半導体層403はゲート絶縁層402を介してゲート電極層401と重疊するように設けられている。ソース電極層405aとドレイン電極層405bは酸化物半導体層403の上層側に設けられている（なお、ここではソース電極層405aとドレイン電極層405bという呼び方は、トランジスタ410に接続される電極として区別するために便宜的に用いている）。ソース電極層405aはゲート電極層401と交差する方向に延在している。保護絶縁層409上には画素電極411が設けられ、コンタクトホール412によってドレイン電極層405bと接続されている。画素電極411は酸化インジウムスズ、酸化亜鉛、酸化スズなどの透光性電極材料で形成されている。

40

【0201】

また、保持容量419は適宜設ければ良く、これを設ける場合には、ゲート電極層401

50

と同じ層で形成される容量配線層 417、容量電極層 418 によって形成する。容量配線層 417 と容量電極層 418 の間には、誘電体としてゲート絶縁層 402 が延在しており、これにより保持容量 419 が形成される。

【0202】

画素電極 411 にはスリットを設けることで液晶の配向を制御することができる。このような構成は、VA (Vertical Alignment) 方式において適用される。VA 方式とは、液晶パネルの液晶分子の配列を制御する方式の一種である。VA 方式は、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。なお、VA 方式の他に、TN (Twisted Nematic) 方式、MVA (Multi-domain Vertical Alignment) 方式、IPS (In-Plane Switching) 方式、CPA (Continuous Pinwheel Alignment) 方式、PVA (Patterned Vertical Alignment) 方式などを適用することもできる。10

【0203】

対向基板 416 側には対向電極 415 が設けられている。基板 400 と対向基板 416 の間には液晶層 414 が設けられている。また、液晶層 414 と接するように配向膜 413 が設けられている。配向膜 413 の配向処理は光配向法又はラビング法でなされている。液晶層 414 の液晶相は、ネマチック相、スマクチック相、コレステリック相、ブルー相などを用いることができる。

【0204】

酸化物半導体層 403 がゲート絶縁層 402 を介してゲート電極層 401 と重畳するように設けられたトランジスタ 410 と、トランジスタ 410 のソース側又はドレイン側に接続された液晶を駆動する画素電極 411 と、画素電極 411 と対向するように設けられた対向電極 415 と、画素電極 411 と対向電極 415 との間に設けられた液晶層 414 とで一つのユニットが形成される。このユニットを一又は複数用いて画素（ピクセル）を形成することができ、これをマトリクス状に配置することにより画像等を表示する表示パネルを構成することができる。20

【0205】

このように、本実施の形態において、電界効果移動度が高く、オフ電流値が低い酸化物半導体層を含むトランジスタを用いることにより、低消費電力の液晶表示装置を提供することができる。30

【0206】

（実施の形態 5）

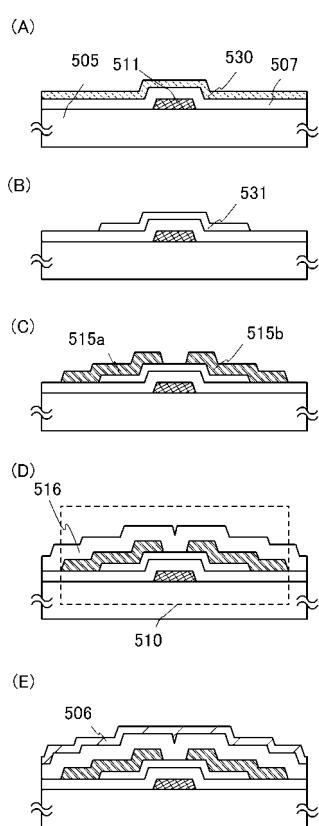

本実施の形態は、酸化物半導体層を含むトランジスタ、及び作製方法の一例を図 12 を用いて詳細に説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0207】

図 12 (A) 乃至 (E) にトランジスタの断面構造の一例を示す。図 12 (A) 乃至 (E) に示すトランジスタ 510 は、図 11 (A) に示すトランジスタ 410 と同様なボトムゲート構造の逆スタガ型トランジスタである。40

【0208】

以下、図 12 (A) 乃至 (E) を用い、基板 505 上にトランジスタ 510 を作製する工程を説明する。

【0209】

まず、絶縁表面を有する基板 505 上に導電膜を形成した後、第 1 のフォトリソグラフィ工程によりゲート電極層 511 を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0210】

10

20

30

40

50

絶縁表面を有する基板 505 は、実施の形態 4 に示した基板 400 と同様な基板を用いることができる。本実施の形態では基板 505 としてガラス基板を用いる。

【0211】

下地膜となる絶縁膜を基板 505 とゲート電極層 511との間に設けてもよい。下地膜は、基板 505 からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

【0212】

また、ゲート電極層 511 の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

10

【0213】

次いで、ゲート電極層 511 上にゲート絶縁層 507 を形成する。ゲート絶縁層 507 は、プラズマ CVD 法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。

【0214】

本実施の形態の酸化物半導体は、不純物を除去され、I型化又は実質的に I型化された酸化物半導体を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、酸化物半導体層とゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。

20

【0215】

例えば、μ 波（例えば周波数 2.45 GHz）を用いた高密度プラズマ CVD は、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

【0216】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマ CVD 法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

30

【0217】

また、ゲート絶縁層 507、酸化物半導体膜 530 に水素、水酸基及び水分がなるべく含まれないようにするために、酸化物半導体膜 530 の成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層 511 が形成された基板 505、又はゲート絶縁層 507 までが形成された基板 505 を予備加熱し、基板 505 に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、絶縁層 516 の成膜前に、ソース電極層 515a 及びドレイン電極層 515b まで形成した基板 505 にも同様に行ってよい。

40

【0218】

次いで、ゲート絶縁層 507 上に、膜厚 2 nm 以上 200 nm 以下、好ましくは 5 nm 以上 30 nm 以下の酸化物半導体膜 530 を形成する（図 12 (A) 参照）。

【0219】

なお、酸化物半導体膜 530 をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 507 の表面に付着している粉状物質（パーティクル、ごみともいう）を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に RF 電源を用いて電圧

50

を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

【0220】

酸化物半導体膜530に用いる酸化物半導体は、実施の形態4に示した酸化物半導体を用いることができる。また、上記酸化物半導体に $\text{SiO}_2$ を含んでもよい。本実施の形態では、酸化物半導体膜530として $\text{In-Ga-Zn-O}$ 系酸化物ターゲットを用いてスパッタリング法により成膜する。この段階での断面図が図12(A)に相当する。また、酸化物半導体膜530は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下においてスパッタ法により形成することができる。

【0221】

酸化物半導体膜530をスパッタリング法で作製するためのターゲットとしては、例えば、組成比として、 $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 1$  [mol数比]の金属酸化物ターゲットを用い、 $\text{In-Ga-Zn-O}$ 膜を成膜する。また、このターゲットの材料及び組成に限定されず、例えば、 $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 2$  [mol数比]の金属酸化物ターゲットを用いてもよい。

【0222】

また、金属酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とすることができます。

【0223】

酸化物半導体膜530を、成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0224】

減圧状態に保持された成膜室内に基板を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板505上に酸化物半導体膜530を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水( $\text{H}_2\text{O}$ )など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

【0225】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ごみともいう)が軽減でき、膜厚分布も均一となるために好ましい。

【0226】

次いで、酸化物半導体膜530を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0227】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体膜530の加工時に同時にを行うことができる。

【0228】

なお、ここでの酸化物半導体膜530のエッティングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。例えば、酸化物半導体膜530のウェットエッ

10

20

30

40

50

チングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液、ITO 07N(関東化学社製)などを用いることができる。

【0229】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、または400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層531を得る(図12(B)参照)。

【0230】

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0231】

例えば、第1の加熱処理として、650~700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。

【0232】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0233】

また、第1の加熱処理で酸化物半導体層を加熱した後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア(露点が-40以下、好ましくは-60以下)を導入してもよい。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N以上好ましくは7N以上(即ち、酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素ガス又はN<sub>2</sub>Oガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型(真性)化する。

【0234】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜530に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0235】

なお、第1の加熱処理は、上記以外にも、酸化物半導体膜成膜後であれば、酸化物半導体層上にソース電極層及びドレイン電極層を積層させた後、あるいは、ソース電極層及びドレイン電極層上に絶縁層を形成した後、のいずれで行っても良い。

【0236】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体

10

20

30

40

50

膜 530 に第 1 の加熱処理を行う前でも行った後に行ってもよい。

【0237】

また、酸化物半導体層を 2 回に分けて成膜し、2 回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域（非単結晶領域）、即ち、膜表面に垂直に c 軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3 nm 以上 15 nm 以下の第 1 の酸化物半導体膜を成膜し、窒素、酸素、希ガス、または乾燥空気の雰囲気下で 450 以上 850 以下、好ましくは 550 以上 750 以下の第 1 の加熱処理を行い、表面を含む領域に結晶領域（板状結晶を含む）を有する第 1 の酸化物半導体膜を形成する。そして、第 1 の酸化物半導体膜よりも厚い第 2 の酸化物半導体膜を形成し、450 以上 850 以下、好ましくは 600 以上 700 以下の第 2 の加熱処理を行い、第 1 の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第 2 の酸化物半導体膜を結晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

10

【0238】

次いで、ゲート絶縁層 507、及び酸化物半導体層 531 上に、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる導電膜を形成する。ソース電極層、及びドレイン電極層に用いる導電膜としては、実施の形態 4 に示したソース電極層 405a、ドレイン電極層 405b に用いる材料を用いることができる。

20

【0239】

第 3 のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層 515a、ドレイン電極層 515b を形成した後、レジストマスクを除去する（図 12（C）参照）。

20

【0240】

第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線や KrF レーザ光や ArF レーザ光を用いるとよい。酸化物半導体層 531 上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長 L が決定される。なお、チャネル長 L = 25 nm 未満の露光を行う場合には、数 nm ~ 数 10 nm と極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長 L を 10 nm 以上 1000 nm 以下とすることも可能であり、回路の動作速度を高速化できる。

30

【0241】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

40

【0242】

なお、導電膜のエッチングの際に、酸化物半導体層 531 がエッチングされ、分断することのないようエッチング条件を最適化することが望まれる。しかしながら、導電膜のみをエッチングし、酸化物半導体層 531 を全くエッチングしないという条件を得ることは難しく、導電膜のエッチングの際に酸化物半導体層 531 は一部のみがエッチングされ、溝部（凹部）を有する酸化物半導体層となることもある。

【0243】

本実施の形態では、導電膜として Ti 膜を用い、酸化物半導体層 531 には In-Ga-Zn-O 系酸化物半導体を用いたので、Ti 膜のエッチャントとしてアンモニア過水（3

50

1重量%過酸化水素水：28重量%アンモニア水：水=5:2:2)を用いる。

【0244】

次いで、N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理を行い、露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる絶縁層516を形成する。

【0245】

絶縁層516は、少なくとも1nm以上の膜厚とし、スパッタ法など、絶縁層516に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。絶縁層516に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化(N型化)してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁層516はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

10

【0246】

本実施の形態では、絶縁層516として膜厚200nmの酸化シリコン膜をスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化シリコン膜のスパッタ法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下において行うことができる。また、ターゲットとして酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素を含む雰囲気下でスパッタ法により酸化シリコンを形成することができる。酸化物半導体層に接して形成する絶縁層516は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

20

【0247】

酸化物半導体膜530の成膜時と同様に、絶縁層516の成膜室内の残留水分を除去するためには、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて排気した成膜室で成膜した絶縁層516に含まれる不純物の濃度を低減できる。また、絶縁層516の成膜室内の残留水分を除去するための排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。

30

【0248】

絶縁層516を、成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0249】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)が絶縁層516と接した状態で加熱される。

【0250】

以上の工程を経ることによって、酸化物半導体層に対して第1の加熱処理を行って水素、水分、水酸基又は水素化物(水素化合物ともいう)などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料の一つである酸素を供給することができる。よって、酸化物半導体層は高純度化及び電気的にI型(真性)化する。

40

【0251】

以上の工程でトランジスタ510が形成される(図12(D)参照)。

【0252】

また、絶縁層516に欠陥を多く含む酸化シリコン層を用いると、酸化シリコン層形成後の加熱処理によって酸化物半導体層中に含まれる水素、水分、水酸基又は水素化物などの不純物を拡散させ、酸化物半導体層中に含まれる該不純物をより低減させる効果を奏する

50

。

## 【0253】

絶縁層516上にさらに保護絶縁層506を形成してもよい。例えば、RFスパッタ法を用いて窒化シリコン膜を形成する。RFスパッタ法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜などを用いる。本実施の形態では、保護絶縁層506を、窒化シリコン膜を用いて形成する(図12(E)参照)。

## 【0254】

本実施の形態では、保護絶縁層506として、絶縁層516まで形成された基板505を100～400の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜する。この場合においても、絶縁層516と同様に、処理室内の残留水分を除去しつつ保護絶縁層506を成膜することが好ましい。

## 【0255】

保護絶縁層の形成後、さらに大気中、100以上200以下、1時間以上30時間以下での加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。

## 【0256】

このように、本実施の形態を用いて作製した、高純度化された酸化物半導体層を含むトランジスタは、高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に高純度化された酸化物半導体層を含むトランジスタを用いることで、色分離を抑制することができ、高画質な画像を提供することができる。また、高純度化された酸化物半導体層を含むトランジスタによって、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

## 【0257】

高純度化された酸化物半導体を用いたトランジスタの電界効果移動度を求めた結果について説明する。

## 【0258】

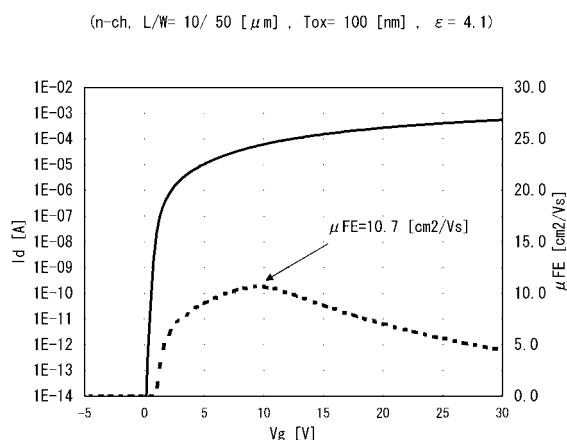

上述した本実施の形態の作製方法に従って、高純度化された酸化物半導体(膜厚50nmのIn-Ga-Zn-O系酸化物半導体膜)を用いてトランジスタ(L/W=10μm/50μm)を作製し、基板温度を室温とし、ソース-ドレイン間電圧(以下、ドレイン電圧またはVdという)を10Vとし、ソース-ゲート間電圧(以下、ゲート電圧またはVgという)を-30V～+30Vまで変化させたときのソース-ドレイン電流(以下、ドレイン電流またはIdという)の変化特性、すなわちVg-Id特性を測定した。なお、図13では、Vgを-5V～+30Vまでの範囲で示している。図13に示すように高純度化された酸化物半導体層を含むトランジスタの電界移動度の最大値は、10.7cm<sup>2</sup>/Vsecであることが確認できる。

## 【0259】

また、高純度化された酸化物半導体を含むトランジスタを用いることにより、オフ状態における電流値(オフ電流値)をより低くすることができる。よって、画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度をより少なくすることができるため、消費電力を抑制する効果を高くできる。

## 【0260】

また、高純度化された酸化物半導体を用いたトランジスタのオフ電流を求めた結果について説明する。

## 【0261】

10

20

30

40

50

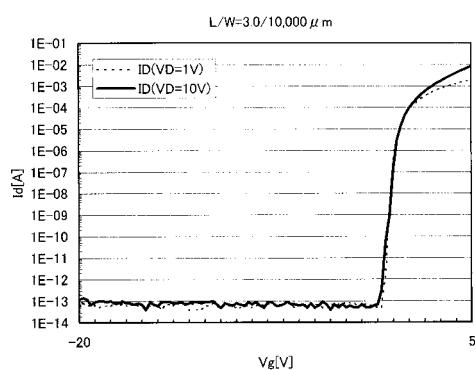

上述した本実施の形態の作製方法に従って、高純度化された酸化物半導体を用いてトランジスタを作製した。まず、高純度化された酸化物半導体を用いたトランジスタのオフ電流が十分に小さいことを考慮して、チャネル幅Wが1 cmと十分に大きいトランジスタを用意してオフ電流の測定を行った。チャネル幅Wが1 cmのトランジスタのオフ電流を測定した結果を図14に示す。図14において、横軸はゲート電圧Vg、縦軸はドレイン電流Idである。ドレイン電圧Vdが+1Vまたは+10Vの場合、ゲート電圧Vgが-5Vから-20Vの範囲では、トランジスタのオフ電流は、検出限界である $1 \times 10^{-13} A$ 以下であることがわかった。また、トランジスタのオフ電流(ここでは、単位チャネル幅(1 μm)あたりの値)は $10 aA/\mu m$ ( $1 \times 10^{-17} A/\mu m$ )以下となることがわかった。

10

#### 【0262】

次に、高純度化された酸化物半導体を用いたトランジスタのオフ電流をさらに正確に求めた結果について説明する。上述したように、高純度化された酸化物半導体を用いたトランジスタのオフ電流は、測定器の検出限界である $1 \times 10^{-13} A$ 以下であることがわかった。そこで、特性評価用素子を作製し、より正確なオフ電流の値(上記測定における測定器の検出限界以下の値)を求めた結果について説明する。

#### 【0263】

電流測定方法に用いた特性評価用素子について、以下に説明する。

#### 【0264】

特性評価用素子は、3つ並列に接続された測定系を用いる。それぞれの測定系は、容量素子、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタを有する。第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタは、本実施の形態に従って作製し、図12(D)に示したトランジスタ510と同じ構造のものを使用した。

20

#### 【0265】

一つの測定系は、第1のトランジスタのソース端子およびドレイン端子の一方と、容量素子の端子の一方と、第2のトランジスタのソース端子およびドレイン端子の一方は、電源(V2を与える電源)に接続する。また、第1のトランジスタのソース端子およびドレイン端子の他方と、第3のトランジスタのソース端子およびドレイン端子の一方と、容量素子の端子の他方と、第2のトランジスタのゲート端子とは、接続する。また、第3のトランジスタのソース端子およびドレイン端子の他方と、第4のトランジスタのソース端子およびドレイン端子の一方と、第4のトランジスタのゲート端子は、電源(V1を与える電源)に接続する。また、第2のトランジスタのソース端子およびドレイン端子の他方と、第4のトランジスタのソース端子およびドレイン端子の他方とを接続し、出力端子とする。

30

#### 【0266】

なお、第1のトランジスタのゲート端子には、第1のトランジスタのオン状態と、オフ状態を制御する電位Vext\_b2が供給され、第3のトランジスタのゲート端子には、第3のトランジスタのオン状態と、オフ状態を制御する電位Vext\_b1が供給される。また、出力端子からは電位Voutが出力される。

40

#### 【0267】

次に、上記の測定系を用いてオフ電流の測定を行う。

#### 【0268】

まず初期化期間において第1のトランジスタのソース端子とドレイン端子の間、及び第3のトランジスタのソース端子とドレイン端子の間に電位差を付与する。初期化が終了した後は、第1と第3のトランジスタのオフ電流に起因し、時間の経過と共に第2のトランジスタのゲート端子の電位が変動する。従って、時間の経過と共に、出力端子の出力電位Voutの電位も変化することとなる。こうして得られた出力電位Voutから、オフ電流を算出することができる。

#### 【0269】

50

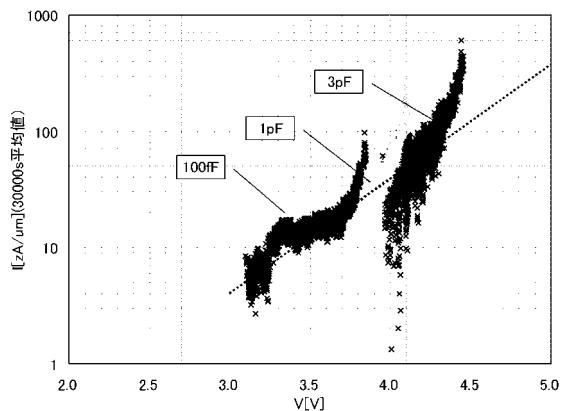

第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、及び第4のトランジスタは、それぞれチャネル長  $L = 10 \mu m$ 、チャネル幅  $W = 50 \mu m$  の、高純度化した酸化物半導体を用いたトランジスタである。また、並列された3つ測定系において、第1の測定系の容量素子の容量値を  $100 fF$  とし、第2の測定系の容量素子の容量値を  $1 pF$  とし、第3の測定系の容量素子の容量値を  $3 pF$  とした。

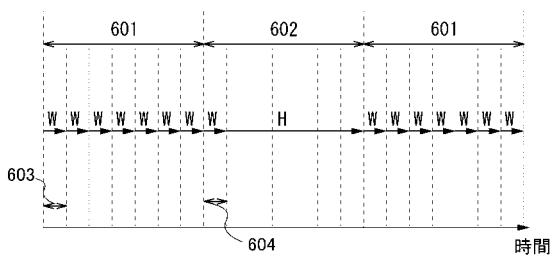

【0270】

なお、第1のトランジスタのソース端子とドレイン端子の間、及び第3のトランジスタのソース端子とドレイン端子の間に電位差を付与するために、V1とV2は適宜5V、あるいは0Vの電圧とした。また、測定は  $10 \sim 300 \text{ sec}$  ごとに行い、電位  $V_{out}$  の測定は  $100 \text{ msec}$  の期間行った。また、初期化終了後  $30000 \text{ sec}$  経過するまで測定を行った。

10

【0271】

図15には、上記電流測定によって算出されたオフ電流を示す。なお、図15は、ソース-ドレイン電圧Vと、オフ電流Iとの関係を表すものである。図15から、ソース-ドレイン電圧が4Vにおいて、オフ電流は約  $40 zA / \mu m$  であることが分かった。また、ソース-ドレイン電圧が3.1Vにおいて、オフ電流は  $10 zA / \mu m$  以下であることが分かった。なお、 $1 zA$  は  $10^{-21} A$  を表す。

20

【0272】

以上、本実施の形態により、高純度化された酸化物半導体を用いたトランジスタでは、オフ電流が十分に小さくなることが確認された。

20

【0273】

(実施の形態6)

本明細書に開示する液晶表示装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態で説明した液晶表示装置を具備する電子機器の例について説明する。

30

【0274】

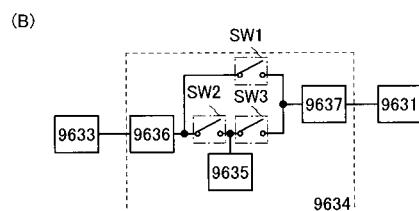

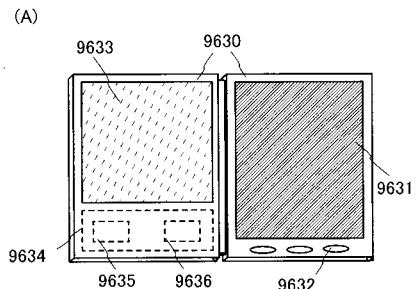

図16(A)は電子書籍(E-bookともいう)であり、筐体9630、表示部9631、操作キー9632、太陽電池9633、充放電制御回路9634を有することができる。図16(A)に示した電子書籍は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。なお、図16(A)では充放電制御回路9634の一例としてバッテリー9635、DCDCコンバータ(以下、コンバータと略記)9636を有する構成について示している。実施の形態1乃至5のいずれかで示した液晶表示装置を表示部9631に適用することにより低消費電力な電子書籍とすることができます。

40

【0275】

図16(A)に示す構成とすることにより、表示部9631として半透過型、又は反射型の液晶表示装置を用いる場合、比較的明るい状況下での使用も予想され、太陽電池9633による発電、及びバッテリー9635での充電を効率よく行うことができ、好適である。なお太陽電池9633は、筐体9630の空きスペース(表面や裏面)に適宜設けることができるため、効率的なバッテリー9635の充電を行う構成とすることができるため好適である。なおバッテリー9635としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

【0276】

また図16(A)に示す充放電制御回路9634の構成、及び動作について図16(B)にブロック図を示し説明する。図16(B)には、太陽電池9633、バッテリー963

50

5、コンバータ 9636、コンバータ 9637、スイッチ SW1 乃至 SW3、表示部 9631 について示しており、バッテリー 9635、コンバータ 9636、コンバータ 9637、スイッチ SW1 乃至 SW3 が充放電制御回路 9634 に対応する箇所となる。

【0277】

まず外光により太陽電池 9633 により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー 9635 を充電するための電圧となるようコンバータ 9636 で昇圧または降圧がなされる。そして、表示部 9631 の動作に太陽電池 9633 からの電力が用いられる際にはスイッチ SW1 をオンにし、コンバータ 9637 で表示部 9631 に必要な電圧に昇圧または降圧をすることとなる。また、表示部 9631 での表示を行わない際には、SW1 をオフにし、SW2 をオンにしてバッテリー 9635 の充電を行う構成とすればよい。

10

【0278】

次いで外光により太陽電池 9633 により発電がされない場合の動作の例について説明する。バッテリー 9635 に蓄電された電力は、スイッチ SW3 をオンにすることでコンバータ 9637 により昇圧または降圧がなされる。そして、表示部 9631 の動作にバッテリー 9635 からの電力が用いられることとなる。

【0279】

なお太陽電池 9633 については、充電手段の一例として示したが、他の手段によるバッテリー 9635 の充電を行う構成であってもよい。また他の充電手段を組み合わせて行う構成としてもよい。

20

【0280】

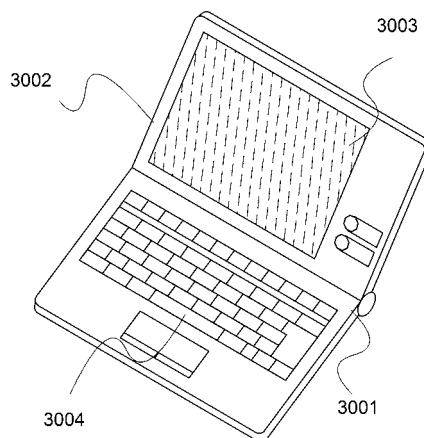

図 17 は、ノート型のパーソナルコンピュータであり、本体 3001、筐体 3002、表示部 3003、キーボード 3004 などによって構成されている。実施の形態 1 乃至 5 のいずれかで示した液晶表示装置を表示部 3003 に適用することにより、低消費電力なノート型のパーソナルコンピュータとすることができます。

【0281】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【符号の説明】

【0282】

30

|      |           |

|------|-----------|

| 100  | 液晶表示装置    |

| 110  | 画像処理回路    |

| 111  | 記憶回路      |

| 111b | フレームメモリ   |

| 112  | 比較回路      |

| 113  | 表示制御回路    |

| 115  | 選択回路      |

| 116  | 電源        |

| 120  | 表示パネル     |

| 121  | 駆動回路部     |

| 121A | ゲート線側駆動回路 |

| 121B | ソース線側駆動回路 |

| 122  | 画素部       |

| 123  | 画素        |

| 124  | ゲート線      |

| 125  | ソース線      |

| 126  | 端子部       |

| 126A | 端子        |

| 126B | 端子        |

| 127  | スイッチング素子  |

40

50

|         |            |    |

|---------|------------|----|

| 1 2 8   | 共通電極       |    |

| 1 3 0   | バックライト部    |    |

| 1 3 1   | バックライト制御回路 |    |

| 1 3 2   | バックライト     |    |

| 2 1 0   | 容量素子       |    |

| 2 1 3   | 画素         |    |

| 2 1 4   | トランジスタ     |    |

| 2 1 5   | 液晶素子       |    |

| 4 0 0   | 基板         |    |

| 4 0 1   | ゲート電極層     | 10 |

| 4 0 2   | ゲート絶縁層     |    |

| 4 0 3   | 酸化物半導体層    |    |

| 4 0 5 a | ソース電極層     |    |

| 4 0 5 b | ドレイン電極層    |    |

| 4 0 7   | 絶縁膜        |    |

| 4 0 9   | 保護絶縁層      |    |

| 4 1 0   | トランジスタ     |    |

| 4 1 1   | 画素電極       |    |

| 4 1 2   | コンタクトホール   |    |

| 4 1 3   | 配向膜        | 20 |

| 4 1 4   | 液晶層        |    |

| 4 1 5   | 対向電極       |    |

| 4 1 6   | 対向基板       |    |

| 4 1 7   | 容量配線層      |    |

| 4 1 8   | 容量電極層      |    |

| 4 1 9   | 保持容量       |    |

| 4 2 0   | トランジスタ     |    |

| 4 2 7   | 絶縁層        |    |

| 4 3 0   | トランジスタ     |    |

| 4 3 6 a | 配線層        | 30 |

| 4 3 6 b | 配線層        |    |

| 4 3 7   | 絶縁層        |    |

| 4 4 0   | トランジスタ     |    |

| 5 0 5   | 基板         |    |

| 5 0 6   | 保護絶縁層      |    |

| 5 0 7   | ゲート絶縁層     |    |

| 5 1 0   | トランジスタ     |    |

| 5 1 1   | ゲート電極層     |    |

| 5 1 5 a | ソース電極層     |    |

| 5 1 5 b | ドレイン電極層    | 40 |

| 5 1 6   | 絶縁層        |    |

| 5 3 0   | 酸化物半導体膜    |    |

| 5 3 1   | 酸化物半導体層    |    |

| 6 0 1   | 期間         |    |

| 6 0 2   | 期間         |    |

| 6 0 3   | 期間         |    |

| 6 0 4   | 期間         |    |

| 7 0 0   | 筐体         |    |

| 7 0 1   | 表示モジュール    |    |

| 7 0 2   | スピーカ       | 50 |

|         |           |    |

|---------|-----------|----|

| 7 0 3   | 操作キー      |    |

| 7 0 4   | 外部接続端子    |    |

| 7 0 5   | 照度センサ     |    |

| 7 1 0   | テレビ受像機    |    |

| 7 1 1   | チューナ      |    |

| 7 1 2   | デジタル復調回路  |    |

| 7 1 3   | 映像信号処理回路  |    |

| 7 1 4   | 音声信号処理回路  |    |

| 7 1 5   | 表示調節回路    |    |

| 7 1 6   | 表示制御回路    | 10 |

| 7 1 7   | 表示パネル     |    |

| 7 1 8   | ゲート線側駆動回路 |    |

| 7 1 9   | ソース線側駆動回路 |    |

| 7 2 0   | スピーカ      |    |

| 7 2 1   | アンテナ      |    |

| 7 2 2   | 外部入力部     |    |

| 7 2 3   | 点線部       |    |

| 7 2 4   | 画像処理回路    |    |

| 8 0 0   | 筐体        |    |

| 8 0 1   | 表示モジュール   | 20 |

| 8 0 2   | スピーカ      |    |

| 8 0 3   | 外部接続端子    |    |

| 8 0 4   | ウインドウ型表示部 |    |

| 8 1 0   | PCモニター    |    |

| 8 1 3   | 映像信号処理回路  |    |

| 8 1 4   | 音声信号処理回路  |    |

| 8 1 5   | 音声信号処理回路  |    |

| 8 1 6   | 表示制御回路    |    |

| 8 1 7   | 表示パネル     |    |

| 8 1 8   | ゲート線側駆動回路 | 30 |

| 8 1 9   | ソース線側駆動回路 |    |

| 8 2 0   | スピーカ      |    |

| 8 2 1   | 外部演算回路    |    |

| 8 2 2   | 外部操作手段    |    |

| 8 2 3   | 点線部       |    |

| 8 2 4   | 画像処理回路    |    |

| 1 0 0 1 | 陽極        |    |

| 1 0 0 2 | 陰極        |    |

| 1 0 0 3 | EL層       |    |

| 1 0 0 4 | 中間層       | 40 |

| 1 0 1 1 | 正孔注入層     |    |

| 1 0 1 2 | 正孔輸送層     |    |

| 1 0 1 3 | 発光層       |    |

| 1 0 1 4 | 電子輸送層     |    |

| 1 0 1 5 | 電子注入層     |    |

| 1 0 2 0 | 基板        |    |

| 1 0 2 5 | EL素子      |    |

| 1 4 0 1 | 期間        |    |

| 1 4 0 2 | 期間        |    |

| 1 4 0 3 | 期間        | 50 |

|         |                   |    |

|---------|-------------------|----|

| 1 4 0 4 | 期間                |    |

| 3 0 0 1 | 本体                |    |

| 3 0 0 2 | 筐体                |    |

| 3 0 0 3 | 表示部               |    |

| 3 0 0 4 | キー ボード            |    |

| 5 2 0 1 | バックライト部           |    |

| 5 2 0 2 | 拡散板               |    |

| 5 2 0 3 | 導光板               |    |

| 5 2 0 4 | 反射板               |    |

| 5 2 0 5 | ランプリフレクタ          | 10 |

| 5 2 0 6 | 光源                |    |

| 5 2 0 7 | 表示パネル             |    |

| 5 2 2 2 | ランプリフレクタ          |    |

| 5 2 2 3 | 発光ダイオード ( L E D ) |    |

| 5 2 9 0 | バックライト部           |    |

| 5 2 9 1 | 拡散板               |    |

| 5 2 9 2 | 遮光部               |    |

| 5 2 9 3 | ランプリフレクタ          |    |

| 5 2 9 4 | 光源                |    |

| 5 2 9 5 | 液晶パネル             | 20 |

| 9 6 3 0 | 筐体                |    |

| 9 6 3 1 | 表示部               |    |

| 9 6 3 2 | 操作キー              |    |

| 9 6 3 3 | 太陽電池              |    |

| 9 6 3 4 | 充放電制御回路           |    |

| 9 6 3 5 | バッテリー             |    |

| 9 6 3 6 | コンバータ             |    |

| 9 6 3 7 | コンバータ             |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

【図16】

【図17】

【図18】

【図19】

## フロントページの続き

| (51) Int.Cl.   |              | F I              |         |       |         |  | テーマコード(参考) |  |  |

|----------------|--------------|------------------|---------|-------|---------|--|------------|--|--|

| <b>G 0 9 G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G 0 2 F | 1/133 | 5 5 0   |  | 5 C 0 9 4  |  |  |

| <b>G 0 9 G</b> | <b>3/34</b>  | <b>(2006.01)</b> | G 0 9 G | 3/20  | 6 8 0 H |  | 5 F 1 1 0  |  |  |

| <b>H 0 1 L</b> | <b>51/50</b> | <b>(2006.01)</b> | G 0 9 G | 3/20  | 6 2 4 B |  |            |  |  |

| <b>G 0 9 F</b> | <b>9/30</b>  | <b>(2006.01)</b> | G 0 9 G | 3/20  | 6 1 2 U |  |            |  |  |

|                |              |                  | G 0 9 G | 3/20  | 6 2 1 K |  |            |  |  |

|                |              |                  | G 0 9 G | 3/20  | 6 6 0 U |  |            |  |  |

|                |              |                  | G 0 9 G | 3/34  | J       |  |            |  |  |

|                |              |                  | G 0 9 G | 3/20  | 6 2 2 A |  |            |  |  |

|                |              |                  | G 0 9 G | 3/20  | 6 2 3 A |  |            |  |  |

|                |              |                  | G 0 9 G | 3/20  | 6 1 1 A |  |            |  |  |

|                |              |                  | H 0 5 B | 33/14 | A       |  |            |  |  |

|                |              |                  | G 0 9 F | 9/30  | 3 3 8   |  |            |  |  |

|                |              |                  | H 0 1 L | 29/78 | 6 1 2 B |  |            |  |  |

| F ターム(参考) |      |      |      |      |      |      |      |      |      |      |                          |

|-----------|------|------|------|------|------|------|------|------|------|------|--------------------------|

| 2H193     | ZA04 | ZA05 | ZB06 | ZC03 | ZC13 | ZC15 | ZC25 | ZD23 | ZE03 | ZE40 |                          |

| ZF03      | ZF12 | ZF16 | ZF18 | ZF21 | ZF31 | ZF44 | ZG03 | ZG04 | ZG12 |      |                          |

| ZG14      | ZG15 | ZP02 | ZP03 | ZP04 | ZQ06 | ZQ14 | ZQ17 | ZQ22 | ZQ26 |      |                          |