(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5566381号

(P5566381)

(45) 発行日 平成26年8月6日(2014.8.6)

(24) 登録日 平成26年6月27日(2014.6.27)

(51) Int.Cl.

H03K 19/177 (2006.01)

H01L 21/82 (2006.01)

F 1

H03K 19/177

H01L 21/82

H01L 21/82A

P

請求項の数 22 (全 16 頁)

(21) 出願番号 特願2011-517524 (P2011-517524)

(86) (22) 出願日 平成21年7月7日 (2009.7.7)

(65) 公表番号 特表2011-528196 (P2011-528196A)

(43) 公表日 平成23年11月10日 (2011.11.10)

(86) 國際出願番号 PCT/US2009/049822

(87) 國際公開番号 WO2010/008971

(87) 國際公開日 平成22年1月21日 (2010.1.21)

審査請求日 平成24年6月18日 (2012.6.18)

(31) 優先権主張番号 12/172,247

(32) 優先日 平成20年7月13日 (2008.7.13)

(33) 優先権主張国 米国(US)

(73) 特許権者 597154922

アルテラ コーポレイション

Altera Corporation

アメリカ合衆国 95134 カリフォルニア州 サンホセ イノベーション ドライヴ 101

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】回路における周波数性能を最適化する入力／出力モジュールのための装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

回路であって、該回路は、

該回路と少なくとも1つの外部デバイスとの間で第1の信号を送るように構成可能である複数の第1の信号パッドと、

該複数の第1の信号パッド間に交互配置される複数の未使用パッドと、

複数の第1のバッファと

を備え、該複数の未使用パッドのそれぞれは、該複数の第1のバッファのうちの少なくとも1つに連結され、該複数の第1のバッファは、該複数の未使用パッドのいずれかを通して第2の信号を送ることなしに、かつ、該複数の第1の信号パッドのいずれかを通して該第2の信号を送ることなしに、該回路と少なくとも1つの外部デバイスとの間で該第2の信号を駆動するように動作可能である、回路。

## 【請求項 2】

前記複数の第1の信号パッドは、前記回路と少なくとも1つの外部デバイスとの間で高論理状態と低論理状態とを切り替えるデジタル信号を送るように構成可能である、請求項1に記載の回路。

## 【請求項 3】

前記複数の第1の信号パッドのうちの少なくとも1つは、前記複数の未使用パッドのうちの2つに隣接する、請求項1に記載の回路。

## 【請求項 4】

10

20

前記複数の第1の信号パッドは、前記回路内でグループ化される2つの差動パッドを備え、該回路は、該複数の第1の信号パッドのうちの少なくとも4つと、前記複数の未使用パッドのうちの少なくとも3つとを備える、請求項1に記載の回路。

【請求項5】

前記複数の第1の信号パッドに連結される複数の入力バッファと、

該複数の第1の信号パッドに連結される複数の出力バッファと

をさらに備える、請求項1に記載の回路。

【請求項6】

前記複数の第1のバッファは、前記回路がフリップチップパッケージ内に収納されるときに、はんだバンプを通して、前記回路と少なくとも1つの外部デバイスとの間で前記第2の信号を駆動するように構成され、前記複数の未使用パッドに連結された該複数の第1のバッファは、該回路がワイヤボンドパッケージ内に収納されるときに、該回路と少なくとも1つの外部デバイスとの間で信号を駆動するように構成されない、請求項1に記載の回路。

10

【請求項7】

前記回路は、

該回路と少なくとも1つの外部デバイスとの間で電圧信号を送るように構成可能である複数の電圧パッドであって、該電圧信号は、実質的に一定の電圧で維持される、複数の電圧パッドと、

該回路と少なくとも1つの外部デバイスとの間でデジタル信号を送るように構成可能である複数の第2の信号パッドであって、該複数の第2の信号パッドは、該複数の電圧パッド間に交互配置される、複数の第2の信号パッドと

20

をさらに備える、請求項1に記載の回路。

【請求項8】

前記回路は、集積回路であり、前記複数の第1の信号パッドおよび前記複数の未使用パッドは、該集積回路上に配置された導電性材料を含み、該複数の未使用パッドのそれぞれと、該複数の第1の信号パッドのそれぞれとは、該集積回路の表面上の接点である、請求項1に記載の回路。

【請求項9】

前記複数の第1の信号パッドは、前記回路と外部メモリデバイスとの間で、データ信号および少なくとも1つのデータストローブ信号を送るように構成される、請求項1に記載の回路。

30

【請求項10】

回路であって、該回路は、

該回路と少なくとも1つの外部デバイスとの間で第1の信号を送るように構成可能である複数の第1の信号パッドと、

少なくとも1つの外部デバイスと該回路との間で実質的に一定の電圧を送るように構成可能である複数の電圧パッドと、

複数の未使用のパッドと、

複数のバッファであって、該複数の未使用パッドのそれぞれは、該複数のバッファのうちの少なくとも1つに連結され、該複数のバッファは、該複数の未使用パッドのいずれかを通して第2の信号を送ることなしに、かつ、該複数の第1の信号パッドのいずれかを通して該第2の信号を送ることなしに、該回路と少なくとも1つの外部デバイスとの間で該第2の信号を駆動するように動作可能である、複数のバッファと

40

を備える、回路。

【請求項11】

前記複数の電圧パッドは、少なくとも1つの外部デバイスと前記回路との間で、少なくとも1つの接地電圧および少なくとも1つの供給電圧を送る、請求項10に記載の回路。

【請求項12】

供給電圧を送る前記複数の電圧パッドのうちの第1の電圧パッドは、少なくとも1つの

50

外部デバイスと前記回路との間で接地電圧を送る該複数の電圧パッドのうちの第2の電圧パッドに隣接し、前記複数の第1の信号パッドのそれぞれは、該複数の電圧パッドのうちの少なくとも2つに隣接する、請求項10に記載の回路。

【請求項13】

前記複数の電圧パッドは、第1の供給電圧パッドと、第1の接地電圧パッドと、第2の供給電圧パッドと、第2の接地電圧パッドとを備え、該第1の供給電圧パッドは、前記複数の第1の信号パッドのうちの第1の信号パッドと該第1の接地電圧パッドとに隣接し、該第1の接地電圧パッドは、該複数の第1の信号パッドのうちの第2の信号パッドに隣接し、該第2の供給電圧パッドは、該複数の第1の信号パッドのうちの該第2の信号パッドと該第2の接地電圧パッドとに隣接し、該第2の接地電圧パッドは、該複数の第1の信号パッドのうちの第3の信号パッドに隣接する、請求項10に記載の回路。

10

【請求項14】

前記複数の第1の信号パッドは、前記回路と少なくとも1つの外部デバイスとの間で高論理状態と低論理状態とを切り替えるデジタル信号を送るように構成可能である、請求項10に記載の回路。

【請求項15】

前記回路は、

該回路と少なくとも1つの外部デバイスとの間で第3の信号を送るように構成可能である複数の第2の信号パッド

をさらに備え、

前記複数の未使用パッドは、該複数の第2の信号パッド間に交互配置される、請求項10に記載の回路。

20

【請求項16】

回路であって、該回路は、

該回路と少なくとも1つの外部デバイスとの間で第1の信号を送るように構成可能である複数の第1の信号パッドと、

該回路が第1のパッケージ型内に収納されるときに、該回路と少なくとも1つの外部デバイスとの間で信号を駆動するように構成されない複数のバッファに連結される複数の未使用パッドと

を備え、該複数の未使用パッドに連結される複数のバッファは、該回路が第2のパッケージ型内に収納されるときに、該回路と少なくとも1つの外部デバイスとの間で第2の信号を駆動するように構成される、回路。

30

【請求項17】

前記第1のパッケージ型は、ワイヤボンドパッケージであり、前記第2のパッケージ型は、フリップチップパッケージであり、前記複数のバッファは、前記複数の未使用パッドのいずれかを通して第2の信号を送ることなしに、かつ、該複数の第1の信号パッドのいずれかを通して該第2の信号を送ることなしに、はんだバンプを通してフリップチップモードで、該回路と少なくとも1つの外部デバイスとの間で該第2の信号を駆動するように動作可能である、請求項16に記載の回路。

【請求項18】

前記複数の未使用パッドは、前記複数の第1の信号パッド間に交互配置され、該複数の第1の信号パッドは、可変信号を送る、請求項16に記載の回路。

40

【請求項19】

前記複数の第1の信号パッドおよび前記複数の未使用パッドは、パッドの第1の列内にあり、前記回路は、

該回路と少なくとも1つの外部デバイスとの間でデジタル信号を送るように構成可能である複数の第2の信号パッドと、

少なくとも1つの外部デバイスと該回路との間で実質的に一定の電圧を送る複数の電圧パッドであって、該複数の第2の信号パッドは、パッドの第2の列内の該複数の電圧パッド間に交互配置される、複数の電圧パッドと

50

をさらに備える、請求項 1 6 に記載の回路。

【請求項 2 0】

回路上の複数のパッドを通して送られる信号の信号対雑音比を増加させる方法であって、該方法は、

該回路上に複数の信号パッドを形成することであって、該複数の信号パッドは、該回路と少なくとも 1 つの外部デバイスとの間で第 1 の信号を送るように構成可能である、ことと、

該回路上に複数の未使用パッドを形成することであって、該複数の未使用パッドは、該複数の信号パッド間に交互配置される、ことと、

該回路上に複数のバッファを形成することであって、該複数の未使用パッドのそれぞれは、該複数のバッファのうちの少なくとも 1 つに連結され、該複数のバッファは、該複数の未使用パッドのいずれかを通して第 2 の信号を送ることなしに、かつ、該複数の信号パッドのいずれかを通して該第 2 の信号を送ることなしに、該回路と少なくとも 1 つの外部デバイスとの間で該第 2 の信号を駆動するように動作可能である、ことと

を含む、方法。

【請求項 2 1】

前記複数の信号パッドは、前記回路と少なくとも 1 つの外部デバイスとの間でデジタル信号を送るように構成可能である、請求項 2 0 に記載の方法。

【請求項 2 2】

前記複数の信号パッドのうちの少なくとも 2 つは、相互に隣接して形成され、前記複数の未使用パッドのそれぞれは、該複数の信号パッドのうちの少なくとも 2 つに隣接する、請求項 2 0 に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、電子回路に関し、より具体的には、回路における周波数性能を最適化する、入力 / 出力モジュールに関する。

【背景技術】

【0 0 0 2】

集積回路は、典型的に、集積回路と外部デバイスとの間で信号を送るためのパッドを含む。集積回路は、パッケージ内に収納することができる。

従来、集積回路ダイに対してバンプおよびトレースのレイアウトを作成するための方法が知られている（例えば、特許文献 1 を参照）。この方法は、複数の I / O パッドの第 1 の列および複数の I / O パッドの第 2 の列を有するルーティングタイルを複製するステップを含む。第 1 の列は、第 2 の列からオフセットされ、その結果、第 1 の列の複数の I / O パッドは、第 2 の列の複数の I / O パッドの間に交互配置される。

また、従来、複数の外側結合パッドおよび複数のスタッガード状内側結合パッドを有するダイを有する単段キャビティダウン (single tier cavity down) 集積回路パッケージが知られている（例えば、特許文献 2 を参照）。この集積回路パッケージでは、ダイの複数の結合パッドが、設計方法に従って、パッケージの関連付けられた複数の供給リングおよび複数の結合フィンガーに割り当てられる。1 つの形態では、少なくとも、複数の供給リングに連結されている複数の結合パッドの全てが、複数の外側結合パッドであり、複数のスタッガード状内側結合パッドは、複数の結合フィンガーに連結されている。さらに、従来、ダイの複数の結合パッドをパッケージの関連付けられた複数の供給リングおよび複数の結合フィンガーに割り当てる方法や、複数のスタッガード状結合パッドを有するダイが知られている（例えば、特許文献 2 を参照）。

また、従来、集積回路上に複数の導電性トレースをルーティングすることによって導入される電力供給電圧降下を低減するための技術や、集積回路の複数の異なる領域において受容される電力供給電圧における変動を低減するための技術が知られている（例えば、特

10

20

30

40

50

許文献 3 を参照）。電力供給電圧は、導電性トレースにわたって、集積回路内でルーティングされる。複数の導電性トレースは、複数の結合パッドに結合される。複数の結合パッドは、外部ソースからの電力供給電圧を受容する。複数のトレースのうちの別のは、高電力供給電圧  $V_{DD}$  および低電力供給電圧  $V_{SS}$  を受容する。複数の導電性トレースは、集積回路上の複数の回路要素に対して電力供給電圧をルーティングするためのより短い複数の経路を提供することによって、電力供給電圧における電圧降下を低減する。

また、従来、Stratix (R) III I/O が知られている（例えば、非特許文献 1 を参照）。この Stratix (R) III I/O は、使用の容易さおよび高速システム集積化のために特別に設計されている。それと同時に、Stratix (R) II I I / O は、内部論理性能を最大化し、システムレベルのパフォーマンスを生み出すために必要な高帯域幅を提供する。

10

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】米国特許第 6 5 9 1 4 1 0 号明細書

【特許文献 2】米国特許第 6 6 0 3 1 9 9 号明細書

【特許文献 3】米国特許第 6 9 9 8 7 1 9 号明細書

【非特許文献】

【0004】

【非特許文献 1】“Stratix III Device I/O Features”，Altera Corporation, 2008年5月, pp. 7-1 ~ 7-52

20

【発明の概要】

【課題を解決するための手段】

【0005】

本発明のいくつかの実施形態によると、回路は、回路と少なくとも 1 つの外部デバイスとの間で信号を送るように構成可能である信号パッドを有する、モジュールを含む。モジュールはまた、信号パッド間に交互配置される、未使用パッドも含む。

【0006】

本発明の他の実施形態によると、回路は、回路と少なくとも 1 つの外部デバイスとの間で可変信号を送るように構成可能である信号パッドを有する、モジュールを含む。モジュールは、少なくとも 1 つの外部デバイスと回路との間で、実質的に一定の電圧を送るように構成可能である、電圧パッドを含む。信号パッドは、電圧パッド間に交互配置される。

30

【0007】

本発明の他の実施形態によると、回路は、回路と少なくとも 1 つの外部デバイスとの間で信号を送るように構成可能である信号パッドを有する、モジュールを含む。モジュールはまた、回路が第 1 のパッケージ型内に収納されるときに、回路と少なくとも 1 つの外部デバイスとの間で信号を駆動するように構成されないバッファに連結される、未使用パッドも含む。バッファは、回路が第 2 のパッケージ型内に収納されるときに、回路と少なくとも 1 つの外部デバイスとの間で信号を駆動するように構成される。本発明は、本明細書に記載される技術を実装するための回路および方法を含む。

40

【0008】

本発明の様々な目的、特徴、および利点は、以下の発明を実施するための形態ならびに添付の図面を熟考すると明らかとなるであろう。

例えば、本発明は以下の項目を提供する。

(項目 1)

モジュールを備える回路であって、該モジュールは、

該回路と少なくとも 1 つの外部デバイスとの間で信号を送るように構成可能である複数の第 1 の信号パッドと、

該第 1 の信号パッド間に交互配置される複数の未使用パッドと

50

を備える、回路。

(項目2)

上記第1の信号パッドは、上記回路と少なくとも1つの外部デバイスとの間で高論理状態と低論理状態とを切り替えるデジタル信号を送るように構成可能である、項目1に記載の回路。

(項目3)

上記複数の第1の信号パッドのうちの少なくとも1つは、上記複数の未使用パッドのうちの2つに隣接する、項目1に記載の回路。

(項目4)

上記複数の第1の信号パッドは、上記モジュール内で共にグループ化される2つの差動パッドを備え、該モジュールは、該複数の第1の信号パッドのうちの少なくとも4つと、上記複数の未使用パッドのうちの少なくとも3つとを備える、項目1に記載の回路。

(項目5)

上記第1の信号パッドに連結される入力バッファと、

該第1の信号パッドに連結される出力バッファと

をさらに備える、項目1に記載の回路。

(項目6)

上記未使用パッドは、上記回路がフリップチップパッケージ内に収納されるときに、はんだバンプを通して、上記回路と少なくとも1つの外部デバイスとの間で信号を駆動するように構成されるバッファに連結され、該未使用パッドに連結されるバッファは、該回路がワイヤボンドパッケージ内に収納されるときに、該回路と少なくとも1つの外部デバイスとの間で信号を駆動するように構成されない、項目1に記載の回路。

(項目7)

上記モジュールはさらに、

上記回路と少なくとも1つの外部デバイスとの間で電圧信号を送るように構成可能である電圧パッドであって、該電圧信号は、実質的に一定の電圧で維持される、電圧パッドと、

該回路と少なくとも1つの外部デバイスとの間でデジタル信号を送るように構成可能である第2の信号パッドであって、該第2の信号パッドは、該電圧パッド間に交互配置される、第2の信号パッドと

を備える、項目1に記載の回路。

(項目8)

上記回路は、プログラマブル論理集積回路である、項目1に記載の回路。

(項目9)

上記第1の信号パッドは、上記回路と外部メモリデバイスとの間で、データ信号および少なくとも1つのデータストローブ信号を送るように構成される、項目1に記載の回路。

(項目10)

モジュールを備える回路であって、該モジュールは、

該回路と少なくとも1つの外部デバイスとの間で可変信号を送るように構成可能である、第1の信号パッドと、

少なくとも1つの外部デバイスと該回路との間で実質的に一定の電圧を送るように構成可能である、電圧パッドであって、該第1の信号パッドは、該電圧パッド間に交互配置される、電圧パッドと

を備える、回路。

(項目11)

上記電圧パッドは、少なくとも1つの外部デバイスと上記回路との間で、少なくとも1つの接地電圧および少なくとも1つの供給電圧を送る、項目10に記載の回路。

(項目12)

供給電圧を送る上記電圧パッドのうちの第1の電圧パッドは、少なくとも1つの外部デバイスと上記回路との間で接地電圧を送る該電圧パッドのうちの第2の電圧パッドに隣接

10

20

30

40

50

し、上記第1の信号パッドのそれぞれは、該電圧パッドのうちの少なくとも2つに隣接する、項目10記載の回路。

(項目13)

上記電圧パッドは、第1の供給電圧パッドと、第1の接地電圧パッドと、第2の供給電圧パッドと、第2の接地電圧パッドとを備え、該第1の供給電圧パッドは、上記第1の信号パッドのうちの第1の信号パッドおよび該第1の接地電圧パッドに隣接し、該第1の接地電圧パッドは、該第1の信号パッドのうちの第2の信号パッドに隣接し、該第2の供給電圧パッドは、該第1の信号パッドのうちの該第2の信号パッドおよび該第2の接地電圧パッドに隣接し、該第2の接地電圧パッドは、該第1の信号パッドのうちの第3の信号パッドに隣接する、項目10に記載の回路。

10

(項目14)

上記第1の信号パッドは、上記回路と少なくとも1つの外部デバイスとの間で高論理状態と低論理状態とを切り替えるデジタル信号を送るように構成可能である、項目10に記載の回路。

(項目15)

上記モジュールはさらに、

上記回路と少なくとも1つの外部デバイスとの間でデジタル信号を送るように構成可能である第2の信号パッドと、

該第2の信号パッド間に交互配置される未使用パッドと

を備える、項目10に記載の回路。

20

(項目16)

モジュールを備える回路であって、該モジュールは、

上記回路と少なくとも1つの外部デバイスとの間で信号を送るように構成可能である、第1の信号パッドと、

該回路が第1のパッケージ型内に収納されるときに、該回路と少なくとも1つの外部デバイスとの間で信号を駆動するように構成されないバッファに連結される未使用パッドとを備え、該未使用パッドに連結されるバッファは、該回路が第2のパッケージ型内に収納されるときに、該回路と少なくとも1つの外部デバイスとの間で信号を駆動するように構成される、回路。

(項目17)

30

上記第1のパッケージ型は、ワイヤボンドパッケージであり、上記第2のパッケージ型は、フリップチップパッケージである、項目16に記載の回路。

(項目18)

上記未使用パッドは、上記第1の信号パッド間に交互配置され、該第1の信号パッドは、可変信号を送る、項目16に記載の回路。

(項目19)

上記第1の信号パッドおよび上記未使用パッドは、パッドの第1の列内にあり、上記モジュールはさらに、

上記回路と少なくとも1つの外部デバイスとの間でデジタル信号を送るように構成可能である第2の信号パッドと、

40

少なくとも1つの外部デバイスと該回路との間で実質的に一定の電圧を送る、電圧パッドであって、該第2の信号パッドは、パッドの第2の列内の上記電圧パッド間に交互配置される、電圧パッドと

を備える、項目16に記載の回路。

(項目20)

回路上のパッドを通して送られる信号の信号対雑音比を増加させる方法であって、

該回路上に信号パッドを形成することであって、該信号パッドは、該回路と少なくとも1つの外部デバイスとの間で信号を送るように構成可能である、ことと、

該回路上に未使用パッドを形成することであって、該未使用パッドは、該未使用パッドのそれぞれが、該信号パッドのうちの少なくとも2つに隣接するように、該信号パッド間

50

に交互配置される、ことと

を含む、方法。

(項目21)

上記信号パッドは、上記回路と少なくとも1つの外部デバイスとの間でデジタル信号を送るように構成可能である、項目20に記載の方法。

(項目22)

上記信号パッドのうちの少なくとも2つは、相互に隣接して形成される、項目20に記載の方法。

【図面の簡単な説明】

【0009】

10

【図1】図1は、本発明の実施形態に係る、入力／出力（I/O）モジュールを図示する。

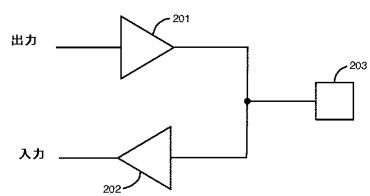

【図2A】図2Aは、本発明の実施形態に係る、集積回路上の出力バッファ、入力バッファ、およびパッドを図示する。

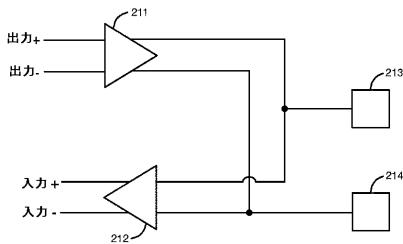

【図2B】図2Bは、本発明の実施形態に係る、集積回路上の差動出力バッファ、差動入力バッファ、およびパッドを図示する。

【図3】図3は、本発明の態様を含むことができる、フィールドプログラマブルゲートアレイ（FPGA）の簡略化部分ブロック図である。

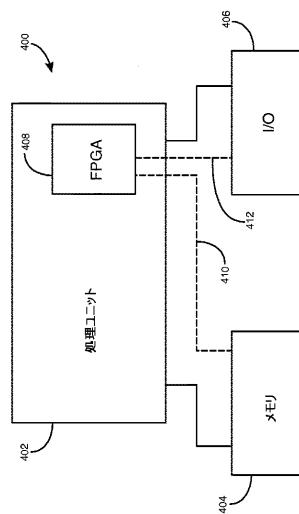

【図4】図4は、本発明の技術を具現化することができる、例示的なデジタルシステムのブロック図を示す。

【発明を実施するための形態】

【0010】

20

集積回路（IC）ダイは、パッケージの内部に配置し、回路基板上に実装することができる。信号は、ICのパッドおよびパッケージ内の導電性材料を通して、ICと回路基板との間で伝送される。パッドは、導電性材料で形成される。各パッドは、ICダイの表面上で接触を形成し、これは、ICダイへ、またはICダイから電気信号を送るために使用することができる。ICは、典型的に、多数のパッドを有する。パッドは、1つ以上の入力／出力（I/O）モジュールにグループ化されてもよい。

【0011】

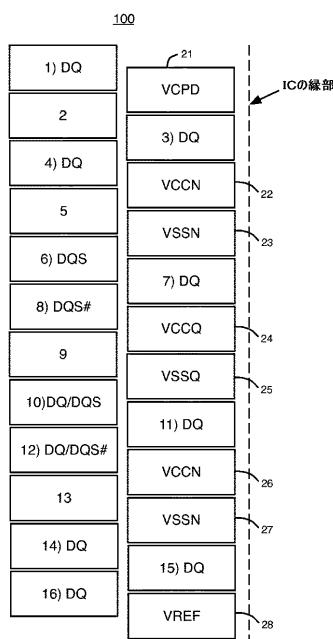

図1は、本発明の実施形態に係る、入力／出力（I/O）モジュールを図示する。図1のI/Oモジュール100は、集積回路（IC）ダイ上に24個のパッドを含む。24個のパッドは、ICへ、またはICの外へ信号を送るために使用される、ICの外部端子である。図1に示される24個のパッドは、IC上に導電性材料で形成される。図1では、パッドは、長方形で示されているが、パッドは、正方形または任意の他の所望の形状であってもよい。I/Oモジュール100の右側の点線は、ICの一方の縁部が位置することができる場所の例を図示する。I/Oモジュール100は、1～16の番号が付けられた16個のパッドと、パッドVCPD21、VCCN22、VSSN23、VCCQ24、VSSQ25、VCCN26、VSSN27、およびVREF28とを含むことができる。I/Oモジュール100内のパッドの配置は、図1に示される配置に制限されない。本発明のI/Oモジュールは、本発明の範囲および趣旨に含まれる、パッドの異なる配置ならびに配設を含むことができる。

【0012】

40

I/Oモジュール100内のパッドは、2列に配設される。第1の列は、1、2、4、5、6、8、9、10、12、13、14、および16の番号が付けられたパッドを含む。第2の列は、21、3、22、23、7、24、25、11、26、27、15、および28の番号が付けられたパッドを含む。図1には、1つのI/Oモジュール100のみが示されているが、集積回路（IC）は、いくつかのI/Oモジュール100を有することができる。例えば、ICは、ICの各縁部に隣接して、1つ以上のI/Oモジュール100を有することができる。

【0013】

I/Oモジュール100は、ワイヤボンド（WB）パッケージ、フリップチップ（FC）

50

パッケージ、または別の型式のパッケージ内に収納される、集積回路（I C）ダイ内で使用することができる。I Cがワイヤボンドパッケージ内に収納されるとき、I Cのパッドは、ワイヤボンド接続を使用して、パッケージに連結される。パッドは、典型的に、I Cの上面に接触し、ワイヤボンド接続は、パッドをI Cの下方のパッケージの導電性領域に連結する。パッケージは、I Cのパッドを基板または別のウェハもしくはチップに連結することができる。

【0014】

I Cがフリップチップパッケージ内に収納されるとき、I Cのパッドは、はんだバンプを使用して、パッケージに連結される。I Cは、I Cのパッドが下向きの状態でフリップチップパッケージ内に実装され、はんだバンプは、パッドをI Cの下のパッケージの導電性領域に接続するように、I Cの底面側に乗せられる。

10

【0015】

I C含有モジュール100がワイヤボンド（WB）パッケージ内に収納されるとき、パッド1、3、4、6、7、8、10、11、12、14、15、および16は、I Cと外部デバイスとの間で信号を送るために使用される。パッド2、5、9、および13は、I Cと外部デバイスとの間で信号を送るために使用されない。パッド2、5、9、および13は、信号を送るために使用されないため、未使用パッド2、5、9、および13は、図1に示されるパッドの左列のパッド1、4、6、8、10、12、14、および16を通して送られる信号間の遮蔽を提供する。未使用パッド2、5、9、および13は、信号パッド1、4、6、8、10、12、14、および16を通して伝送される信号間のクロストークを低減するように、信号パッド1と、4と、6と、8と、10と、12と、14と、16との間に交互配置される。結果として、未使用パッド2、5、9、および13は、パッド1、4、6、8、10、12、14、および16を通して伝送される信号の信号対雑音比を増加させる。

20

【0016】

例えば、図2A～図2Bに示されるように、出力信号は、I Oモジュール100内のパッドを通して出力（伝送器）バッファから伝送され、入力信号は、I Oモジュール100内のパッドを通して入力（受信器）バッファに伝送される。図2Aは、本発明の実施形態に係る、集積回路上の出力バッファ201、入力バッファ202、およびパッド203を図示する。出力バッファ201が、シングルエンド出力信号OUTを、パッド203を通して、集積回路の外に駆動できるようにすることができる。入力バッファ202が、集積回路の外側からパッド203で受信されたシングルエンド入力信号を駆動できるようにすることができる。図2Bは、本発明の実施形態に係る、集積回路上の差動出力バッファ211、差動入力バッファ212、およびパッド213～214を図示する。出力バッファ211が、差動出力信号OUT+/OUT-を、パッド213および214を通して、集積回路の外に駆動できるようにすることができる。入力バッファ212が、集積回路の外からパッド213および214で受信された差動入力信号IN+/IN-を駆動できるようにすることができる。

30

【0017】

I C含有モジュール100がフリップチップ（FC）パッケージ内に収納されるとき、入力信号および出力信号を、I Oモジュール100内のパッドのいずれかを通して信号を送ることなく、はんだバンプを通して、I C上の入力バッファおよび出力バッファと外部回路との間で駆動することができる。図1の1～16の番号が付けられたパッドのそれぞれは、出力バッファおよび/または入力バッファに連結される。I CがFCパッケージ内に収納されるとき、1～16の番号が付けられたパッドに連結されるバッファが、I Cと外部回路との間で信号を伝送できるようにすることができる。I Oモジュール100内のパッド1～16に連結される16個のバッファは、I CがFCパッケージ内に収納されるときに、I Oモジュール100内のパッドを通して16個の信号を送ることなく、I Cと少なくとも1つの外部デバイスとの間で16個の信号を駆動できるようにすることができる。1つのパッド当たりに1つのバッファ（各パッド1～16で）は、パッドを通して入

40

50

力信号または出力信号を送ることなく、入力信号または出力信号を駆動する。

【0018】

I/Oモジュール100は、モジュール100を含有するICを、異なる型式のパッケージで使用できるようにする。I/Oモジュール100は、集積回路内で、信号の最適な最大周波数性能を達成するように、異なる型式のパッケージの異なる入力／出力(I/O)利用率に適合することができる。例えば、IC含有I/Oモジュール100がWBパッケージ内に収納されるとき、上述されるように、図1の1～16の番号が付けられた16個のパッドのうちの12個のパッドは、ICと外部回路との間で12個の信号を送るために使用され、1～16の番号が付けられた16個のパッドの4個は、未使用である。したがって、I/Oモジュール100は、IC含有モジュール100がWBパッケージ内に収納されるときに、最大75%のI/O利用(16個のパッドのうちの12個のパッド)を提供する。

【0019】

別の実施例として、IC含有I/Oモジュール100がフリップチップ(FC)パッケージ内に収納されるとき、1～16の番号が付けられた16個のパッドに連結される16個のI/Oバッファは、ICと外部回路との間で、パッド1～16を通して16個の信号を送ることなく、はんだバンプを通して16個の信号を伝送するために使用することができる。1つのパッド当たりに1つのバッファは、16個の信号のうちの1つを伝送する。したがって、I/Oモジュール100は、IC含有モジュール100がFCパッケージ内に収納されるときに、16個のI/Oバッファに連結することができ、これは、最大100%のI/O利用(16個のパッド当たりに16個のバッファ)を提供する。

【0020】

IC含有I/Oモジュール100がワイヤボンド(WB)パッケージ内に収納されるとき、入力および／または出力データ信号を送るために、I/Oモジュール100内の8個または10個のパッドを使用することができ、データストローブ信号を送るために、I/Oモジュール100内の2個または4個のパッドを使用することができ、I/Oモジュール100内の4個のパッドは、未使用パッドである。入力および／または出力データ信号を送るために使用されるパッドは、DQパッドと称される。DQデータ信号パッドには、I/Oモジュール100内の1、3、4、7、11、14、15、および16の番号が付けられたパッドを含む。10および12の番号が付けられたパッドはまた、DQデータ信号パッドとして使用することができる。DQデータ信号パッドを通して送られるデータ信号は、典型的に、論理高状態と論理低状態との間で変化するデジタル信号である。

【0021】

未使用パッド2は、パッド1および4を通して送られる信号を遮蔽する。未使用パッド5は、パッド4および6を通して送られる信号を遮蔽する。未使用パッド9は、パッド8および10を通して送られる信号を遮蔽する。未使用パッド13は、パッド12および14を通して送られる信号を遮蔽する。

【0022】

データ出力信号は、I/Oモジュール100内のDQパッドの1つ以上を通して、IC含有モジュール100から外部メモリデバイス(例えば、メモリチップ)に伝送することができる。別の実施例として、データ入力信号は、I/Oモジュール100内のDQパッドの1つ以上を通して、外部メモリデバイスからICに伝送することができる。さらに別の実施例として、データ入力信号およびデータ出力信号は、I/Oモジュール100内のDQパッドを通して、外部メモリデバイスとICとの間で双方向に伝送することができる。

【0023】

ICがWBパッケージ内にあるときに、I/Oモジュール100内のパッド1、3、4、7、10、11、12、14、15、および16がDQデータ信号パッドとして構成される場合、I/Oモジュール100は、例えば、外部メモリデバイス(例えば、SDRAMデバイス)の×8 DQグループ化または×9 DQグループ化を支援することができる。×8 DQグループ化では、8ビットデータバイトを形成するように、8個のDQパッドを通して、8個のデータ信号が同時に伝送される。×9 DQグループ化では、9ビット

データバイトを形成するように、9個のD Qパッドを通して、9個のデータ信号が同時に伝送される。I Oモジュール100内のパッド1、3、4、7、11、14、15、および16のみがWBパッケージ内のD Qデータ信号パッドとして構成される場合、I Oモジュール100は、最大で、外部メモリデバイスの×8グループ化を支援することができる。したがって、I Oモジュール100が、パッド1、3、4、7、11、14、15、および16をD Qデータ信号パッドとして使用し、パッド10をD Q Sパッドとしての使用し、パッド12をD Q S #パッドとし使用するように構成される場合、I Oモジュール100は、最大で×8 D Qグループ化を支援することができる。

#### 【0024】

I Oモジュール100はまた、パッド1、3、4、7、11、14、15、および16の2つの×4 D Qグループ化を支援することもできる。本実施形態では、パッド1、3、4、および7は、I Cと外部メモリデバイスとの間で、第1の4ビットバイトを形成するデータ信号を送るために使用され、パッド11、14、15、および16は、I Cと外部メモリデバイスとの間で、第2の4バイトを形成するデータ信号を送るために使用される。フリップチップ(FC)パッケージでは、パッド1、3、4、7、11、14、15、16、ならびに任意にパッド10および12に連結されるバッファは、I Oモジュール100内のパッドを通してD Qデータ信号を送ることなく、D Qデータ信号を外部メモリデバイスに駆動する、または外部メモリデバイスからのD Qデータ信号を駆動することができる。

#### 【0025】

×4、×8、または×9 D Qグループ化では、データ信号は、それぞれ、I Oモジュール100内の8個または9個のD Qパッドを通して、2倍のデータ転送速度(例えば、DDR、DDR2、DDR3等)で送ることができる。2倍のデータ転送速度で動作する信号バスは、クロック信号の立ち上がりおよび立ち下りの両方でデータを転送する。代替として、データ信号は、例えば、I Oモジュール100内の8個または9個のD Qパッドを通して、4倍のデータ転送速度(例えば、QDR、QDRII等)で送ることができる。4倍のデータ転送速度は、各クロックサイクルでデータの4ビットが伝送されるように、独立したデータ読み出しピンおよびデータ書き込みピンを使用して、すなわち、2つのピンを使用する、1つのクロックサイクルでの2つの書き込みおよび2つの読み出しを使用して、クロック信号の立ち上がりおよび立ち下りの両方でデータを伝送させる、通信信号送信技術である。

#### 【0026】

×4、×8、および×9グループ化でデータ信号を送るために使用されない、1個または2個の予備のD Qパッドは、例えば、データマスク信号および/またはバイト書き込み選択信号を送るために使用することができる。データマスク信号は、データを外部メモリデバイスに書き込むための入力マスク信号である。バイト書き込み選択信号は、書き込み動作の現行部分中に外部メモリデバイスに書き込まれるデータバイトを選択するために使用される。

#### 【0027】

I C含有I Oモジュール100がワイヤボンド(WB)パッケージ内に収納されるとき、I Oモジュール100内の1個または2個のD Q Sパッドおよび1個または2個のD Q S #パッドは、I Cと外部メモリデバイス(例えば、SDRAMチップ)との間でデータストローブ信号を送るために使用することができる。フリップチップ(FC)パッケージでは、D Q SパッドおよびD Q S #パッドに連結されるバッファは、D Q SパッドまたはD Q S #パッドを通して信号を送ることなく、I C含有モジュール100と外部メモリデバイスとの間でデータストローブ信号を駆動する。D Q SパッドおよびD Q S #パッドを通して伝送されるデータストローブ信号は、D Qデータパッドを通して伝送されるデータをサンプリングするために使用される。

#### 【0028】

データストローブ信号は、典型的に、高論理状態と低論理状態とを切り替える、デジタ

10

20

30

40

50

ル信号である。差動データストローブ信号が使用される場合、差動データストローブ信号は、データストローブパッド DQS および DQS # を通して伝送される。シングルエンドデータストローブ信号が使用される場合、シングルエンドデータストローブ信号は、典型的に、データストローブパッド DQS を通して伝送される。

#### 【 0 0 2 9 】

図 1 では、1つの DQS パッドは、パッド 6 と番号が付けられ、1つの DQS # パッドは、パッド 8 と番号が付けられている。パッド 10 は、第 2 の DQS データストローブパッドとして使用することができ、パッド 12 は、第 2 の DQS # データストローブパッドとして使用することができる。したがって、パッド 10 は、データ DQ パッドまたはデータストローブ DQS パッドとして使用することができ、パッド 12 は、データ DQ パッドまたはデータストローブ DQS # パッドとして使用することができる。各 DQS パッドは、好ましくは、その特定の DQS パッドの相補データストローブ信号を送る DQS # パッドに隣接して位置する。したがって、パッド 6 および 8 は、第 1 の差動データストローブ信号 DQS および DQS # を送るために使用することができ、パッド 10 および 12 は、第 2 の差動データストローブ信号 DQS および DQS # を送るために使用することができる。

10

#### 【 0 0 3 0 】

I/O モジュール 100 はまた、電圧パッド VCPD21、VCCN22、VSSN23、VCCQ24、VSSQ25、VCCN26、VSSN27、および VREF28 も含む。第 1 の供給電圧は、外部電源から、供給電圧パッド VCPD21 を通して、I/C 上の事前駆動回路に伝送される。第 2 の供給電圧は、外部電源から、2つの供給電圧パッド VCCN22 および 26 を通して、I/C の周辺に位置する回路素子に伝送される。第 1 の接地電圧は、外部電源から、2つの VSSN パッド 23 および 27 を通して、I/C の周辺に位置する回路素子に提供される。I/C の周辺に位置する回路素子によって受容される供給電圧は、VSSN パッドでの電圧を引いた VCCN パッドでの電圧に等しい。

20

#### 【 0 0 3 1 】

第 3 の供給電圧は、外部電源から、供給電圧パッド VCCQ24 を通して、I/C のコア領域内に位置する回路素子に伝送される。第 2 の接地電圧は、外部電源から、VSSQ パッド 25 を通して、I/C のコア領域内に位置する回路素子に提供される。I/C のコア領域内に位置する回路素子によって受容される供給電圧は、VSSQ パッド 25 での電圧を引いた VCCQ パッド 24 での電圧に等しい、静穏供給電圧である。基準電圧は、VREF パッド 28 を通して、外部デバイス（例えば、外部メモリデバイス）と I/C との間で伝送される。

30

#### 【 0 0 3 2 】

パッド VCPD21、VCCN22、VSSN23、VCCQ24、VSSQ25、VCCN26、VSSN27、および VREF28 を通して伝送されるすべての信号は、論理高状態と論理低状態とを切り替えない、実質的に一定の電圧を有する。図 1 に示されるように、DQ 信号パッド 3、7、11、および 15 は、電圧パッド VCPD21 と、VCCN22 と、VSSN23 と、VCCQ24 と、VSSQ25 と、VCCN26 と、VSSN27 と、VREF28 との間に交互配置される。パッド VCPD21 と、VCCN22 と、VSSN23 と、VCCQ24 と、VSSQ25 と、VCCN26 と、VSSN27 と、VREF28 との間に DQ パッド 3、7、11、および 15 を交互配置することで、電圧パッド VCPD21、VCCN22、VSSN23、VCCQ24、VSSQ25、VCCN26、VSSN27、および VREF28 を通して伝送される信号の電圧が、回路動作中、実質的に一定のままとなるため、クロストークが低減され、DQ パッド 3、7、11、および 15 を通して伝送されるデータ信号の信号対雑音比が増加する。

40

#### 【 0 0 3 3 】

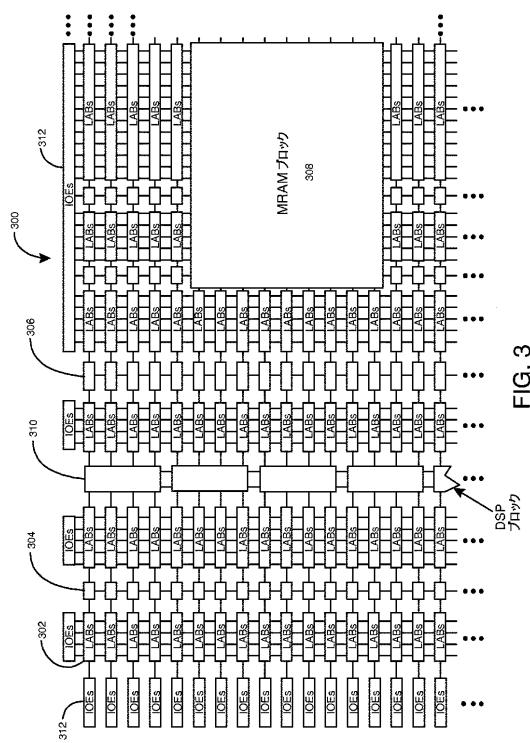

図 3 は、本発明の態様を含むことができる、フィールドプログラマブルゲートアレイ（FPGA）300 の簡略化部分ブロック図である。FPGA300 は、本発明の特徴を含むことができる、集積回路の一実施例にすぎない。本発明の実施形態は、フィールドプロ

50

グラマブルゲートアレイ (FPGA)、プログラマブル論理デバイス (PLD)、コンプレックスプログラマブル論理デバイス (CPLD)、プログラマブル論理アレイ (PLA)、および特定用途向け集積回路 (ASIC) 等の多数の種類の集積回路で使用することができることを理解されたい。

【0034】

FPGA300は、様々な長さおよび速度の列ならびに行相互接続導体のネットワークによって相互接続される、プログラマブル論理アレイブロック（またはLAB）302の2次元アレイを含む。LAB302は、複数の（例えば、10個の）論理素子（またはLE）を含む。

【0035】

LEは、ユーザー定義論理関数の効率的な実装を提供する、プログラマブル論理回路ブロックである。FPGAは、様々な組み合わせ関数および逐次関数を実装するように構成することができる、多数の論理素子を有する。論理素子は、プログラマブル相互接続構造へのアクセスを有する。プログラマブル相互接続構造は、ほぼいかなる所望の構成にも論理素子を相互接続するようにプログラムすることができる。

【0036】

FPGA300はまた、アレイ全体にわたって提供される、様々なサイズのランダムアクセスメモリ (RAM) ブロックを含む、分散メモリ構造を有する。RAMブロックは、例えば、ブロック304、ブロック306、およびブロック308を含む。これらのメモリブロックはまた、シフトレジスタおよび先入れ先出し (FIFO) バッファも含むことができる。

【0037】

FPGA300はさらに、例えば、加算機構および減算機構と共に、乗算器を実装することができる、デジタル信号処理 (DSP) ブロック310を含む。本実施例では、チップの周辺の周囲に位置する入力 / 出力素子 (IOE) 312は、多数のシングルエンド標準および差動入力 / 出力標準を支援する。IOE312は、例えば、図2A～図2Bに示されるように、集積回路のパッドに連結される、入力バッファおよび出力バッファを含む。パッドのそれぞれは、例えば、FPGAと1つ以上の外部デバイスとの間で、入力信号、出力信号、または定電圧を送るために使用することができる、FPGAダイの外部端子である。IOモジュール100内のパッドは、1つ以上のIOEに連結することができる。FPGA300は、説明のためだけに本明細書に記載され、本発明は、多くの異なる種類のPLD、FPGA、およびASICに実装できることが理解される。

【0038】

本発明はまた、いくつかの構成要素のうちの1つとしてFPGAを有するシステムに実装することもできる。図4は、本発明の技術を具現化することができる、例示的なデジタルシステム400のブロック図を示す。システム400は、プログラマされたデジタルコンピュータシステム、デジタル信号処理システム、専用デジタルスイッチングネットワーク、または他の処理システムであってもよい。さらに、そのようなシステムは、電気通信システム、自動車システム、制御システム、家庭用電化製品、個人用コンピュータ、インターネット通信およびネットワーキング等の多種多様な用途向けに設計することができる。さらに、システム400は、単一の基板上、複数の基板上、または複数の筐体内に提供することができる。

【0039】

システム400は、1つ以上のバスによって共に相互接続される、処理ユニット402と、メモリユニット404と、入力 / 出力 (I/O) ユニット406とを含む。この例示的な実施形態によると、FPGA408は、処理ユニット402内に組み込まれる。FPGA408は、図4のシステム内で、多くの異なる目的を果たすことができる。FPGA408は、例えば、その内部動作および外部動作を支援する、処理ユニット402の論理ビルディングブロックであってもよい。FPGA408は、システム動作におけるその特定の役割を実行するのに必要な論理関数を実装するようにプログラムされる。FPGA4

10

20

30

40

50

08は、具体的に、接続410を通してメモリ404に連結することができ、接続412を通してI/Oユニット406に連結することができる。

#### 【0040】

処理ユニット402は、処理または記憶に適切なシステム構成要素にデータを向けること、メモリ404内に記憶されるプログラムを実行すること、I/Oユニット406を介してデータを受信および伝送すること、または他の同様の機能を行うことができる。処理ユニット402は、中央演算処理ユニット(CPU)、マイクロプロセッサ、浮動小数点コプロセッサ、グラフィックコプロセッサ、ハードウェアコントローラ、マイクロコントローラ、コントローラとして使用するためにプログラムされたフィールドプログラマブルゲートアレイ、ネットワークコントローラ、または任意の種類のプロセッサもしくはコントローラであってもよい。さらに、多くの実施形態では、多くの場合、CPUは必要ない。

10

#### 【0041】

例えば、CPUの代わりに、1つ以上のFPGA408が、システムの論理演算を制御することができる。別の実施例として、FPGA408は、特定の計算タスクを処理するために、必要に応じて、再プログラムすることができる、再構成可能であるプロセッサとしての機能を果たす。代替として、FPGA408は、それ自体が組み込みマイクロプロセッサを含むことができる。メモリユニット404は、ランダムアクセスメモリ(RAM)、読み出し専用メモリ(ROM)、固定またはフレキシブルディスク媒体、フラッシュメモリ、テープ、もしくは任意の他の記憶手段、またはこれらの記憶手段の任意の組み合わせであってもよい。

20

#### 【0042】

本発明の例示的な実施形態の前述の説明は、図示および説明のために提示してきた。前述の説明は、包括的であること、または本発明を本明細書に開示される実施例に制限することは意図されない。場合によっては、本発明の特徴は、説明されるような他の特徴の対応する使用なく、採用することができる。本発明の範囲から逸脱することなく、上記の教示を考慮して、多くの修正、置換、および変形が可能である。

【図1】

FIG. 1

【図2 A】

FIG. 2A

【図2 B】

FIG. 2B

【図3】

FIG. 3

【図4】

FIG. 4

---

フロントページの続き

(72)発明者 リン， グー

アメリカ合衆国 カリフォルニア 95120， サンノゼ， マウンテン シャドウズ ロード 1071

(72)発明者 リン， イエン - フー

アメリカ合衆国 カリフォルニア 95129， サンノゼ， ヒッコリー ウェイ 740

(72)発明者 トラン， ステファニー

アメリカ合衆国 カリフォルニア 95120， サンノゼ， ワショー ドライブ 1227

(72)発明者 コーシュクホー， プーヤン

アメリカ合衆国 カリフォルニア 95054， サンタ クララ， クランドール サークル 4061

審査官 柳下 勝幸

(56)参考文献 特開2003-152520 (JP, A)

特開2003-229448 (JP, A)

特開2001-257313 (JP, A)

米国特許出願公開第2003/0214344 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H03K 19/177

H01L 21/82