(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-30884

(P2004-30884A)

(43) 公開日 平成16年1月29日(2004.1.29)

(51) Int.Cl.<sup>7</sup>G 11 C 11/15

H 01 L 27/105

H 01 L 43/08

F 1

G 11 C 11/15

H 01 L 43/08

H 01 L 27/10

テーマコード(参考)

5 F 08 3

16 O

Z

4 4 7

審査請求 未請求 請求項の数 10 O L (全 15 頁)

|              |                              |          |                                                                                                          |

|--------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2003-126443 (P2003-126443) | (71) 出願人 | 503003854<br>ヒューレット-パッカード テベロップメント カンパニー エル.ピー.<br>アメリカ合衆国 テキサス州 77070<br>ヒューストン 20555 ステイト<br>ハイウェイ 249 |

| (22) 出願日     | 平成15年5月1日 (2003.5.1)         | (74) 代理人 | 100087642<br>弁理士 古谷 聰                                                                                    |

| (31) 優先権主張番号 | 10/138074                    | (74) 代理人 | 100076680<br>弁理士 溝部 孝彦                                                                                   |

| (32) 優先日     | 平成14年5月1日 (2002.5.1)         | (74) 代理人 | 100121061<br>弁理士 西山 清春                                                                                   |

| (33) 優先権主張国  | 米国(US)                       |          |                                                                                                          |

(特許庁注: 以下のものは登録商標)

UNIX

最終頁に続く

(54) 【発明の名称】磁気抵抗固体記憶素子における誤りを最小限にする方法

## (57) 【要約】

## 【課題】

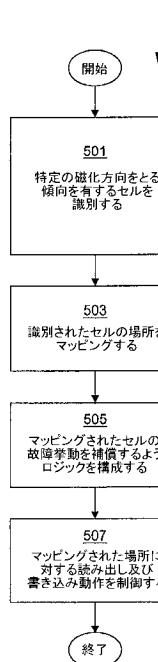

【解決手段】磁気ランダムアクセスメモリ(MRAM)素子アレイ等の磁気抵抗固体記憶素子(100)における誤りを最小限にすることを可能にする例示的な実施形態を開示する。本開示の方法は、特定の磁化方向に留まる傾向を有することを特徴とする故障挙動を有する磁気抵抗固体記憶素子内のセルを識別し(501)、該識別されたセルの場所をマッピングし(503)、該マッピングされた場所におけるセルの故障挙動を補償する(505)、という各ステップを含む。システム及びコンピュータ読み出可能媒体もまた提供される。

【選択図】 図5

**【特許請求の範囲】****【請求項 1】**

複数のセル(116)を有する磁気抵抗固体記憶素子(100)における誤りを最小限にするための方法であって、

前記素子内のセルのうち特定の磁化方向に留まる傾向を有することを特徴とする故障挙動を有するセルを識別し(501)、

前記識別されたセルの場所をマッピングし(503)、

該マッピングされた場所におけるセルの故障挙動を補償する(505)、

という各ステップを含む方法。

**【請求項 2】**

前記識別ステップが、

前記素子内の前記セルのサブセットを画定し、

該サブセット内のセルを検査して、該サブセット内のセルのうち特定の磁化方向に留まる傾向を有することを特徴とする故障挙動を有するセルを識別し、

前記サブセット内の前記識別されたセルに基づいて、前記サブセットの外部に位置する前記素子内のセルが、特定の磁化方向に留まる傾向を有することを特徴とする故障挙動を有するか否かを予測する、

という各ステップを含む、請求項1に記載の方法。

**【請求項 3】**

前記識別された各セルの前記傾向が平行な方向をとるか逆平行の方向をとるかを判定する 20

ステップを更に含む、請求項1に記載の方法。

**【請求項 4】**

前記識別ステップが、

前記素子内のセルに磁界を加え、

該磁界が加えられた該素子内のセルの各々毎にB-H曲線を解析して、該B-H曲線がオフセットされているセルを識別する、

という各ステップを含む、請求項1に記載の方法。

**【請求項 5】**

前記識別ステップが、

前記サブセット内のセルに磁界を加え、

該磁界が加えられた該サブセット内の各セル毎にB-H曲線を解析して、該B-H曲線がオフセットされているセルを識別し、

前記B-H曲線がオフセットされていると識別された前記サブセット内の前記セルに基づいて、前記素子内のセルのうち前記サブセットの外部に位置するセルの前記故障挙動を予測する、

という各ステップを更に含む、請求項2に記載の方法。

**【請求項 6】**

前記マッピングステップが、

平行な磁化方向をとる傾向を有するものと評価された前記セルを第1のグループに割り当てる、

逆平行の磁化方向をとる傾向を有するものと評価された前記セルを第2のグループに割り当てる、

前記第1のグループ内の各セルの場所を格納し、

前記第2のグループ内の各セルの場所を格納する、

という各ステップを含む、請求項3に記載の方法。

**【請求項 7】**

複数のセル(116)を有する磁気抵抗固体記憶素子(100)における誤りを最小限にするためのシステムであって、

メモリ要素(414)と、

前記素子内のセルのうち特定の磁化方向に留まる傾向を有することを特徴とする故障挙動 50

を有するセルを識別し、該識別されたセルの場所をマッピングし、及び該マッピングされたセルの前記故障挙動を補償するよう構成された、処理要素（412）とを含むシステム。

【請求項8】

前記処理要素が更に、前記識別されたセルの各々毎に該セルが平行な方向をとる傾向を有するか逆平行の方向をとる傾向を有するかを判定するよう構成される、請求項7に記載のシステム。

【請求項9】

前記処理要素が更に、平行な磁化方向をとる傾向を有する前記セルを第1のグループに割り当て、逆平行の磁化方向をとる傾向を有する前記セルを第2のグループに割り当て、及び前記第1のグループ内の各セルの場所と前記第2のグループ内の各セルの場所とを前記メモリ要素中にマッピングするよう構成される、請求項8に記載のシステム。

【請求項10】

前記処理要素が更に、前記第1のグループ内の前記セルを使用して平行な磁化状態に対応するデータを格納し、及び前記第2のグループ内の前記セルを使用して逆平行の磁化状態に対応するデータを格納するように構成される、請求項9に記載のシステム。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、一般に磁気抵抗固体記憶素子に関し、特に磁気抵抗固体記憶素子における誤りを最小限にすることに関する。

【0002】

【従来の技術】

磁気ランダムアクセスメモリ（MRAM）素子といった一般的な磁気抵抗固体記憶素子は、記憶セルのアレイを含む。各セルは典型的には、誘電体層により分離された2つの磁気薄膜層から構成される。その一方の磁気薄膜層の磁化方向は可変であり、一方、他方の磁気薄膜層の磁化方向は、特定の方向に固定され又は「ピン留め」（pinned）される。可変の磁化方向を有する磁気薄膜層は一般に「データ記憶層」と呼ばれ、固定された磁化方向を有する磁気薄膜層は一般に「基準層」と呼ばれる。

【0003】

かかる記憶セルのアレイにわたり複数の導電性トレースが配線される。該導電性トレースは、一般に行及び列に配列される。記憶セルの行に沿って延びる導電性トレースは一般に「ワード線」と呼ばれ、記憶セルの列に沿って延びる導電性トレースは一般に「ビット線」と呼ばれる。該ワード線及びビット線は、一般に互いに垂直に向けられる。各記憶セルは、ワード線とビット線との各交点に配置され、1つの磁化方向として1ビットの情報を格納する。

【0004】

一般に、データ記憶層内の磁化方向は、データ記憶層の軸（一般に磁化容易軸と呼ばれる）に沿って整列する。一般に、所望の論理状態に応じて、磁化容易軸に沿ったデータ記憶層内の磁化方向を基準層内の磁化方向に対して平行又は逆平行の何れかの方向に反転させるように、外部磁界がかけられる。

【0005】

各記憶セルの磁化方向は、あらゆる所与の時点で2つの安定した方向のうちの一方を呈することになる。一般に、これらの2つの安定した方向、すなわち平行及び逆平行は「1」及び「0」の論理値をそれぞれ表すものとなる。代替的に、逆平行状態を論理「1」と解釈し、平行状態を論理「0」と解釈するようシステムを構成することも可能である。選択された記憶セルの磁化方向は、該選択された記憶セルの位置で交差するワード線とビット線とに電流を供給することにより変更する（すなわち、平行から逆平行に又はその逆にする）ことが可能である。該電流は磁界を生成し、該磁界が組み合わされて、選択された記憶セルの磁化方向を平行から逆平行に（又はその逆に）切り替えることが可能となる。

10

20

30

40

50

**【 0 0 0 6 】**

理想的には、M R A Mアレイの各セル内の磁界は、平行又は逆平行の何れかの方向に整列することになる。しかし、残念ながら、M R A Mアレイを形成するために用いられる磁性材料の不完全性に起因して、M R A Mアレイ内の各セルは完全には直角に配置されない場合がある。それ故、記憶セルのうちの幾つかの磁界が互いに整列しなくなる場合がある。かかるセルの磁界は、一般に、逆平行又は平行の何れかの方向に整列しやすい傾向を有するものとなり、その結果として、該セルにデータを書き込もうとする際に誤りが生じる可能性がある。状況によっては、特定のセル内の磁界が逆平行又は平行の何れかの方向に固定されてしまうことすらある。一方の方向を他の方向よりも好む傾向を有するセルは一般に、書き込みが行われる際にその方向を確実に切り替えないため、データに誤りが導入されることになる。例えば、M R A Mアレイ内に2進数0 0 0 0を格納したいものと仮定する。しかし、2進数0 0 0 0の各ビットがアレイ内の各セルに書き込まれ、それらのビットのうちの1つが、論理「1」に対応する磁化方向に留まる傾向を有するセルに書き込まれる場合には、書き込まれた数がアレイから読み出される際に、論理「1」に対応する磁化方向に留まる傾向を有するセルから「0」でなく「1」が読み出され（例えば、該アレイから読み出される数が0 0 0 0ではなく0 0 1 0になる可能性があり）、このため、システム内に誤りが生じることになる。10

**【 0 0 0 7 】****【発明が解決しようとする課題】**

それ故、本発明の目的は、M R A M素子における上記の欠陥及び欠点を解消させることにある。20

**【 0 0 0 8 】****【課題を解決するための手段】**

本発明は、磁気ランダムアクセスメモリ（M R A M）素子アレイといった複数のセルを有する磁気抵抗固体記憶素子における誤りを最小限にすることを可能にする例示的な実施形態を提供する。本開示の方法は、特定の磁化方向に留まる傾向を有することを特徴とする故障挙動（failure mode）を有する磁気抵抗固体記憶素子内のセルを識別し、該識別されたセルの場所をマッピングし、該マッピングされた場所においてセルの故障挙動を補償する、という各ステップを含むことを特徴とするものである。30

**【 0 0 0 9 】**

1つの例示的なシステムは、特定の磁化方向に留まる傾向を有することを特徴とする故障挙動を有する磁気抵抗固体記憶素子内のセルを識別するよう構成された検査要素と、メモリ要素と、前記識別されたセルの場所を前記メモリ要素内にマッピングして該マッピングされたセルの故障挙動を補償するよう構成された処理要素とを含む。

**【 0 0 1 0 】**

本発明の他の特徴及び利点は、以下の図面及び詳細な説明を検討することにより当業者には明らかとなろう。全てのかかる特徴及び利点は、特許請求の範囲により規定される本発明の範囲内に含めることが意図されたものである。

**【 0 0 1 1 】****【発明の実施の形態】**

特許請求の範囲で規定する本発明は、図面を参照して一層良好に理解することが可能である。同図面における各構成要素は必ずしも互いに対し縮尺が一定である訳ではなく、本発明の原理を明瞭に示すことに重きがおかれている。40

**【 0 0 1 2 】**

本発明の以下に記載する詳細な説明では、その一部を形成し、一例として本発明が実施され得る特定の実施形態を示す、図面への参照がなされる。他の実施形態が用いられてもよく、本発明の範囲から逸脱することなく、構造的又は論理的な変更がなされ得ることを理解されたい。それ故、以下に記載される詳細な説明は、本発明を限定する意味に受け取られるべきではなく、本発明の範囲は、特許請求の範囲により規定される。例えば、以下の説明では、本発明を磁気ランダムアクセスメモリ（M R A M）アレイに適用されるものと50

して説明するが、本発明は一般に、M R A M、E E P R O M、フリップフロップ、シフトレジスタ等（但しこれらには限定されない）を含む、磁気抵抗記憶セルを記憶要素として用いる任意の素子に適用することが可能である。

### 【 0 0 1 3 】

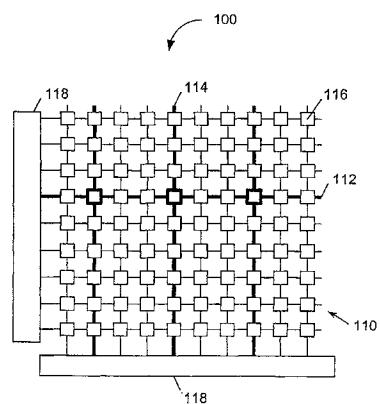

ここで図面を参照する。同図では、類似する参照符号は幾つかの図面を通して対応する構成要素を示している。図1は、本発明の実施形態が動作することが可能な例示的な磁気抵抗固体記憶素子である磁気ランダムアクセスメモリ（M R A M）素子アレイを単純化して示す説明図である。同図は、制御回路118に接続された記憶セル116のアレイ110を含むM R A M素子100を単純化して示している。

### 【 0 0 1 4 】

典型的な実施形態では、M R A M素子100は約 $1\,024 \times 1\,024$ の記憶セルを含むが、それよりも遙かに少数の記憶セルを有する例を図示している。記憶セル116はそれぞれ制御線112, 114の交点に形成される。この例では、制御線112は行をなすよう配列され、制御線114は列をなすよう配列されている。制御線112, 114は典型的には直交するが、他の更に複雑な格子構造も実施可能である。好適には、行線112及び列線114は制御回路118に接続され、該制御回路118は複数の読み出し／書き込み制御回路を含むものとなる。実装形態に応じて、一列につき1つの読み出し／書き込み制御回路が設けられ、又は複数列間で読み出し／書き込み制御回路が多重化されもしくは共有される。

### 【 0 0 1 5 】

書き込み動作又は読み出し動作といった素子へのアクセス時には、図1に示すように、必要とされる1つ又は2つ以上の記憶セル116にアクセスするために、典型的には1つの行112と1つ又は2つ以上の列114とが制御回路118により選択される。しかし、アレイ110の方向に応じて、1つの列114と複数の行112とを制御回路118により選択することが可能である。図1に示す例示的な構成を参照すると、選択されたセル116、選択された行線112、及び選択された列線114はそれぞれ太線により表されている。典型的なM R A M素子は、セル間の干渉を最小限にするために、選択された列線114間に最小距離m（例えば64セル）を必要とする。各アレイ110が、長さ1（例えば1024記憶セル）の行を有する場合には、該アレイ110から一意にアドレス指定することが可能な $1/m = 1\,024/64 = 16$ 個までのセルに同時にアクセスすることが可能である。

### 【 0 0 1 6 】

各記憶セル116は、数値、好適には2進値（すなわち1又は0）を適当に表す1ビットのデータを格納する。好適には、各記憶セルは、平行及び逆平行として知られる2つの安定した磁化方向のうちの一方を呈する2つの薄膜を含むものとなる。該磁化方向は、記憶セルの抵抗値に影響を与えるものとなる。記憶セル116が逆平行状態にある場合に、その抵抗値はその最も高くなり、該記憶セル116が平行状態にある場合には、その抵抗値はその最も低くなる。好適には、高抵抗の逆平行状態が「0」論理状態を画定し、低抵抗値の平行状態が「1」論理状態を画定する（その逆も可能である）。磁気抵抗固体記憶素子の1つの典型的な実施形態では、各記憶セル116の抵抗値は、スピントンネル現象として知られる現象にしたがって決定され、該記憶セルは、磁気トンネル接合記憶セルと呼ばれる。記憶セルの状態は、センス電流（抵抗値に比例する）、又は既知のキャパシタンスを放電するための応答時間といった関連するパラメータを測定し、各記憶セル毎に1つ又は2つ以上のパラメータ値を取得することにより求められる。次いで、取得された1つ又は2つ以上のパラメータ値から論理値を導出することができる。M R A M素子の特性及び構成に応じて、読み出し動作は、複数ステップを含むことが可能であり、又は読み出し及び再書き込み動作の組み合わせを必要とすることができる。

### 【 0 0 1 7 】

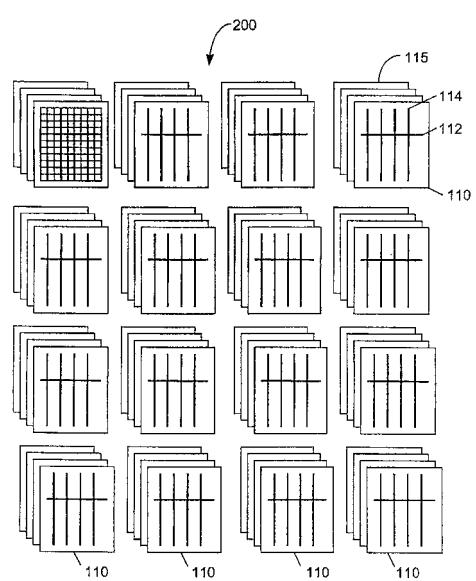

図2は、図1のM R A M素子100を更に詳細に示したものである。複数の個々のアレイ110を含むマクロアレイ200が形成され、その各アレイ110は、図1に関して上述

10

20

30

40

50

したように形成される（単純化のため制御回路 118 を図 2 から省略した）。複数のアレイを利用することにより、アレイ内の個々のアレイ 110 をその製造又は制御が困難になるほど大きくすることなく、所望の全データ記憶容量を有する M R A M 素子を得ることが可能となる。単純化のため、図 2 はマクロアレイ 200 の一部のみを示している。

【 0018 】

素子の製造中に適当な基板上にアレイ 110 をレイアウトする際には、当業者であれば数多くの設計上の選択が可能であるが、とりわけ、各アレイのための基板面積を縮小させることができが一般に望ましい。都合のよいことに、アレイ 110 を複数の層として製造できることがわかった。図 2 の例では、4 つのアレイ 110 が積層化されて 1 つのスタック 115 が形成される。144M b 程度の記憶容量を有する一例の実際的な素子の場合には、1152 個のアレイ 110 が、4 つのスタック層を有する幅 16 アレイ × 高さ 18 アレイ のマクロアレイとして配列される。随意選択的に、M R A M 素子は 2 つ以上のかかるマクロアレイを含むことが可能である。

【 0019 】

図 2 に示すように、マクロアレイ 200 に対するアクセスは、複数のアレイ 110 の各々における 1 つの行 112 を選択し及び該複数のアレイの各々から複数の列 114 を選択することで複数の記憶セル 116 ( 図 1 ) を選択することにより、行うことが可能である。複数のアレイの各々におけるアクセスされるセルは、一単位のデータの小部分に対応する。アクセスされるセルが共に一つになって、一単位のデータ全体 ( 例えは 1 セクタのデータ全体 ) 又は一単位のデータの少なくとも大部分が提供される。複数のアレイの各々にはほぼ同時にアクセスできることが有利であり、これは当業界では「マクロアレイのスライス・スルー ( a slice through the macro-array ) 」として知られている。スライス・スルーを用いることにより、読み出し動作又は書き込み動作に関する素子のアクセス速度が高められる。

【 0020 】

図 2 に示すように、複数のアレイ 110 の各々において同じ行アドレス及び同じ列アドレスを選択するのが好適である。すなわち、一単位のデータは、複数のアレイ 110 の各々において同じ行及び列アドレスを用いて複数のアレイ 110 にわたって格納される。

【 0021 】

また図 2 に示すように、アレイ 110 は典型的には積層化されてスタックが形成される。一度に各スタック内の 1 つのアレイにのみアクセスすることができる。それ故、1 セクタ単位のデータを格納するために用いられる複数のアレイ 110 はそれぞれ異なるスタック内に存在する ( すなわち選択された複数のアレイはその何れも同じスタック内には存在しない ) のが好適である。また、全て同じ層内に存在するアレイを選択するのが好適である。理想的には、各スタックから 1 つずつアレイが選択され、該アレイの各々が各スタック内の同じ層内に存在する。図 2 に示す例では、各スタック内の最上位のアレイが選択されている。

【 0022 】

最も好適には、マクロアレイ 200 において利用可能なアレイの数が、その素子内に格納されることになる 1 セクタ単位のデータのサイズと一致することである。この場合には、1 つのアレイ内で同時にアクセスできるセルの数が与えられた際に、素子の单一の層のアレイの全てのセルを使用して 1 セクタ単位を格納して、1 セクタ単位のデータ全体を格納するように、アレイの総数を与えるのが好適である。別の実施形態では、1 セクタ単位のデータの整数の分の一 ( 例えは 1 セクタ単位の 1 / 2 又は 1 / 3 ) に同時にアクセスするのが好適となる。

【 0023 】

概ね信頼性は高いが、素子が記憶セル 116 にデータを確実に格納するための能力に影響を与える故障が生じ得ることが分かった。故障は、極めて望ましくなく、素子内の少なくとも幾つかの記憶セルに対して確実に書き込み又は読み出しを行うことができないことを意味する。故障による影響を受けるセルは、読み出し不能になって該セルから論理値を読

10

20

30

40

50

み出すことができなくなり、又は信頼性がなくなって該セルから読み出される論理値が必ずしも該セルに書き込まれた値と同じでなくなる（例えば「1」を書き込んだのに「0」が読み出される）。素子の記憶容量及び信頼性が深刻な影響を受け、最悪の場合には素子全体が使用不能になる可能性がある。

#### 【0024】

故障のメカニズムは数多くの形をとり得るものである。本発明の一実施形態は、セルに異なる状態を書き込もうとしているにもかかわらず該セルが通常の動作時に平行又は逆平行の何れかの状態に留まる傾向を有する結果として生じる誤りを最小限にすることに向けられる。本書で用いるように、セルが特定の状態に留まる傾向は、セルの抵抗値がアレイ内の典型的なセルの抵抗値よりも極めて高い状況又は極めて低い状況、並びにセルが特定の方向に固定される状況を含む。セルの抵抗値がアレイ内の典型的なセルの抵抗値よりも極めて極めて低い場合には（一般に「短絡ビット」と呼ばれる）、該セルは典型的には、セルを逆平行状態に反転させるために一般に必要とされる電圧よりも高いバイアス電圧において平行状態に留まることになる。また、セルの抵抗がアレイ内の典型的なセルの抵抗よりも極めて高い場合には（一般に「開放ビット」と呼ばれる）、該セルは典型的には、セルを逆平行状態に反転させるために一般に必要とされる電圧よりも高いバイアス電圧において平行状態に留まることになる。セルが平行方向又は逆平行方向の何れかに拘束される場合には、該セルは、バイアス電圧を増加させた場合であっても書き込み命令に応じてその方向を変更しなくなる。

#### 【0025】

本発明の一実施形態は、平行状態又は逆平行状態の何れかをとる傾向を有するセルを含むメモリセクションにデータを正しく読み書きすることを可能にする。ここで、M R A Mアレイ内のセルを検査して、そのセルのうちの何れが（もしあるなら）通常の動作時に平行状態又は逆平行状態の何れかに留まる傾向を有するかを判定するための例示的な方法を、図3を参照して説明する。素子は、該素子内の各セルの検査を介して、また代替的には、セルの行及びノ/又は列の検査を介して、検査することが可能である、ということに留意されたい。上述の複数の故障挙動のうちの幾つかの結果として、関連する複数グループのセルの故障が生じ得るので（例えば、短絡ビットは典型的には、同じ行及び同じ列に存在する全ての記憶セルに影響を与え、開放ビットは（必ずではないが）同じ行もしくは列又はその両者に存在する全ての記憶セルに影響を与える）、アレイ内の各セルが特定の状態をとる傾向は、そのセルの統計的に有意なサンプルが検査される限り、実際に各セルを個々に検査することなく予測することが可能である。

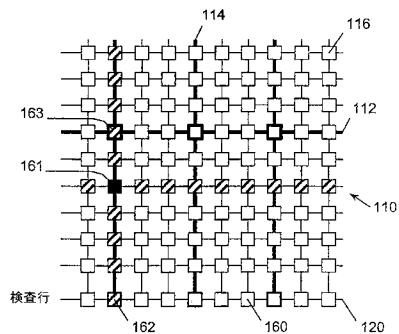

#### 【0026】

図3は、図1関して上述したアレイと類似したアレイ110の一部を概略的に示したものである。図3では、アレイ110は、検査セル160の行120を含む。好適には、検査セル160は、アレイの残りの部分の記憶セル116と同一に構成される。検査行120はあらゆる適当な場所（アレイ110の上部又は底部又は内部等）に設けることが可能である。典型的には、アレイ110の一行の記憶セル116が、検査行120として機能するよう選択される。検査行は、それ自体が故障のあるセルを含まず他の行内の故障のあるセルによる影響を受ける行となるよう適当に選択される。検査行は、好適には、素子の製造時に決定される。また必要であれば、検査行120は、場合に応じて選択し直し又は移動させることができる。

#### 【0027】

都合の良いことに、検査行120内の検査セル160の状態を調べることにより、アレイの他の部分の記憶セル116の状態を正確に予測することが可能であることが分かった。1つの例示として、図3は、アレイ110の一部を示しており、該部分でセル161に短絡ビット故障が生じる。図3の典型的なM R A M素子内の故障の性質に起因して、短絡ビットセル161は、同じ行及び同じ列内に存在する全てのセル（検査行120内の検査セル160中の検査セル162を含む）に影響を与える。それ故、検査セル162は、短絡ビット故障が生じており、該故障が検査セル162が存在する列に影響を与えていること

10

20

30

40

50

を示す。

#### 【0028】

読み出し動作中に、行線 112 と 1 つ又は 2 つ以上の列線 114 とが（例えば図 1 の制御回路 118 により）駆動されて、図 3 の太線で示すように、アレイ 110 内の一組の記憶セル 116 が選択される。短絡ビットセル 161 の影響を受けているセル 163 は、これら選択されたセルの中に存在する。検査セル 162 の状態を調べることにより、セル 163 が故障による影響を受けていることを予測することができる。次いで、該予測は、該選択されたセルに関する後続の読み出し動作ステージの改善を可能にする。

#### 【0029】

他の方式を用いて、アレイ内のセルのうちの何れが（もしあるなら）通常の動作時に平行又は逆平行の何れかの状態に留まる傾向を有するかを判定することも可能である。1 つの単純な動作モードでは、検査セルを一回だけ検査して、故障（特に短絡ビット故障、開放ビット故障、又は「固定された」ビット）による影響を受けるアレイ 110 内の列 114 を判定する。

#### 【0030】

検査セル 160 の検査は、あらゆる適当な形態をとることが可能である。一実施形態では、各検査セル 160 に論理「1」といった既知の値が書き込まれる。次いで、該検査セル 160 から論理値を読み出すことにより該検査セル 160 が検査される。検査セルのうちの任意のセルが論理値「0」を示す場合には、検査セル 160 が存在する列 114 に影響を与える短絡ビット故障等の故障が生じているものと予測することができる。同様に、検査セルに「0」を書き込み「1」が読み出された場合には、開放ビット故障が示されることになる。隨意選択的に、2 つの検査行を設けることが可能であり、この場合には、第 1 の検査行は短絡ビット故障を示すよう構成され、第 2 の検査行は開放ビット故障を示すよう構成される。検査セルは、一回だけ書き込んで繰り返し読み出すことが可能であり、又はセルの保全性を維持するために、必要に応じて各読み出しの後に再び書き込むことが可能である。検査セル 160 の場所及び性質、並びに検査セル 160 の検査方法は、特定の M R A M 素子の特定の性質に合わせて容易に変更することが可能である。

#### 【0031】

検査セル 160 を使用してアレイ内のセルの故障挙動を予測することが可能であるが、代替的に、アレイ中の各セルを（例えばバーンイン中に）検査して各セルの故障挙動を判定することが可能である。例えば、平行状態が論理「1」を構成し、逆平行状態が論理「0」を構成するものと仮定する。一実施形態では、アレイ 110 内の各セルに論理「1」といった既知の値が書き込まれる。セルから論理「0」が読み出された場合には、該セルは逆平行状態をとる傾向を有するものとみなされる。同様に、セルに「0」を書き込み「0」が読み出された場合には、該セルが平行状態をとる傾向を有することが示されることになる。

#### 【0032】

各セルを検査することにより、又は統計的に有意な数の選択された検査セルを検査し、該選択された検査セルの検査結果に基づいて他のセルの傾向を予測することにより、特定の方向をとる傾向を有するセルが識別されると、該傾向を補償する態様でデータがセルに格納される。こうして、本発明は、かかるセルを回避するのではなく、その使用を可能にする。

#### 【0033】

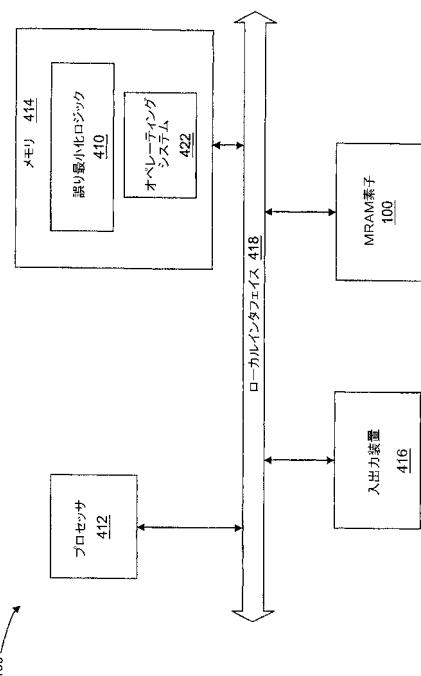

本発明の実施形態は、ソフトウェア（例えばファームウェア）、ハードウェア、又はそれらの組み合わせで実施することが可能である。一例として、そのシステムは、パーソナルコンピュータ（P C；I B M 互換機、A p p l e 互換機その他）、ワークステーション、ミニコンピュータ、又はメインフレームコンピュータにおけるプロセッサといった専用又は汎用プロセッサにより実行される実行可能プログラム等のソフトウェアを含むコンピュータシステムにおいて実施することが可能である（但しこれらには限定されない）。本発明の実施形態を実施することができる汎用コンピュータの一例を図 4 に示す。図 4 では、

10

20

30

40

50

コンピュータシステムは、符号400で示されている。

【0034】

一般的に、ハードウェア・アーキテクチャに関しては、図4に示すように、該コンピュータシステム400は、図1に関して上述したように構成されるMRAM素子100を含み、該MRAM素子は、本発明の実施形態を実施することが望ましい典型的な磁気抵抗固体記憶素子である。該コンピュータシステム400はまた、プロセッサ412と、メモリ414と、1つ又は2つ以上の入出力(I/O)装置416(又は周辺装置)を含み、それらは全て、ローカルインタフェイス418を介して通信可能となるよう接続される。該ローカルインタフェイス418は、例えば当業界で知られている1つ又は複数のバスその他の有線又は無線接続とすることが可能なものである(但しそれらには限定されない)。ローカルインタフェイス418は、単純化のため省略してあるが、コントローラ、バッファ(キャッシュ)、ドライバ、リピータ、及び受信機といった、通信を可能にするための更に別の装置を有することが可能である。更に、ローカルインタフェイスは、上記の構成要素間における適当な通信を可能にするためのアドレス接続、制御接続、及び/又はデータ接続を含むことが可能である。

【0035】

プロセッサ412は、ソフトウェア(特にメモリ414に格納されたソフトウェア)を実行するためのハードウェア要素である。プロセッサ412は、あらゆる特注品又は市販品のプロセッサ、すなわち中央演算処理装置(CPU)、コンピュータシステム400に付随する幾つかのプロセッサの中の補助プロセッサ、半導体ベースの(マイクロチップ又はチップセットという形の)マイクロプロセッサ、マクロプロセッサ、又は一般にソフトウェア命令を実行するためのあらゆる素子とすることが可能なものである。適当な市販のマイクロプロセッサの例として、ヒューレット・パッカード社のPA-RISCシリーズマイクロプロセッサ、インテル社の80x86又はPentium(R)シリーズマイクロプロセッサ、IBM社のPowerPCマイクロプロセッサ、サンマイクロシステムズ社のSparcマイクロプロセッサ、又はモトローラ社の68xxxシリーズマイクロプロセッサが挙げられる。

【0036】

メモリ414は、揮発性メモリ要素(例えばランダムアクセスメモリ(DRAM、SRAM、SDRAM等のRAM))又は不揮発性メモリ要素(例えば磁気ランダムアクセスメモリ(MRAM)、ROM、ハードドライブ、テープ、CD-ROM等)の何れか一方、又はそれらの組み合わせを含むことができる。MRAMは不揮発性であるが、他のタイプのRAM(すなわち、DRAM、SRAM、SDRAM等)は揮発性であることに留意されたい。このため、特定の応用形態では、揮発性RAMよりも不揮発性のMRAMを用いる方が有利となる。これは、MRAMアレイにおける誤りを最小限にすることの必要性を更に強調している。MRAM素子100は、メモリ414の外部に存在するものとして図示したが、代替的に、メモリ414の一部を構成することが可能である。

【0037】

メモリ414はまた、電子的、磁気的、光学的、及び/又はその他のタイプの記憶媒体を含むことが可能である。メモリ414は、分散形アーキテクチャを有することができ、この場合には種々の構成要素が互いから離隔して配置されるが、プロセッサ412によりアクセスすることが可能である、という点に留意されたい。

【0038】

メモリ414内のソフトウェアは、1つ又は2つ以上の別個のプログラムを含むことが可能であり、該プログラムの各々は、論理機能を実施するための実行可能命令を順に並べたリストを含むものとなる。図4の例では、メモリ414内のソフトウェアは、誤り最小化ロジック410及び適当なオペレーティングシステム(O/S)422を含む。市販の適当なオペレーティングシステム422の例として、(a)Microsoft社のWindowsオペレーティングシステム、(b)Novell社のNetwareオペレーティングシステム、(c)Apple Computer社のMacintoshオペレーティングシステム。

10

20

30

40

50

ィングシステム、(d) Hewlett-Packard社、Sun Microsystems社、及びAT&T社といった数多くのベンダから購入できるUNIXオペレーティングシステム、(e)インターネット上で容易に入手できるフリーウエアのLinuxオペレーティングシステム、(f) WindRiver Systems社のランタイムVxworksオペレーティングシステム、又は(g)ハンドヘルドコンピュータ又は個人情報端末(PDA)に実装されるようなアプライアンス・ベースのオペレーティングシステム(例えば、Palm Computing社のPalmOS、Microsoft社のWindows CE)が挙げられる(但し、これらには限定されない)。オペレーティングシステム422は、基本的には、誤り最小化ロジック410といった他のコンピュータプログラムの実行を制御し、スケジューリング、入出力制御、ファイル及びデータ管理、メモリ管理、並びに通信制御及びそれに関連するサービスを提供する。

10

#### 【0039】

誤り最小化ロジック410は、ソースプログラム、実行可能プログラム(オブジェクトコード)、スクリプト、又は実行すべき一組の命令を含む他のあらゆるエンティティとすることが可能である。ソースプログラムの場合には、該ソースプログラムは典型的には、O/S422に関連して適当に動作するように、コンパイラ、アセンブラー、インターフタ及びその類を介して翻訳されることになり、それらは、メモリ414内に含めることも含めないことも可能である。更に、誤り最小化ロジック410は、(a)データクラス及びメソッドを有するオブジェクト指向プログラミング言語として、又は(b)ルーチン、サブルーチン、及び/又は関数を有するプロシージャプログラミング言語(例えば、C、C++、Pascal、Basic、Fortran、Cobol、Perl、Java、及びAda)として書くことが可能である(但しこれらには限定されない)。

20

#### 【0040】

I/O装置416は、入力装置、例えば、キーボード、マウス、スキャナ、マイクロフォン等を含むことが可能である(但しこれらには限定されない)。更に、I/O装置416は、出力装置、例えば、プリンタ、ディスプレイ等を含むことが可能である(但しこれらには限定されない)。最後に、I/O装置416は更に、入力及び出力の両方と通信する装置、例えば、変調器/復調器(例えば、他の装置、システム、又はネットワークにアクセスするためのモデム)、無線周波数(RF)その他の送受信器、電話インターフェイス、ブリッジ、ルータ等を含むことが可能である。

30

#### 【0041】

コンピュータ400がPC、ワークステーション、及びその類である場合には、メモリ414内のソフトウェアは更に、BIOS(basic input output system)(単純化のため省略する)を含む可能性がある。BIOSは、始動時にハードウェアを初期化し及び検査し、O/S422を起動させ、ハードウェアデバイス間のデータ転送をサポートする、一組の基本的なソフトウェアルーチンである。BIOSは、コンピュータ300の起動時に実行できるようROMに格納される。

#### 【0042】

コンピュータ400が動作中である場合に、プロセッサ412は、メモリ414内に格納されているソフトウェアを実行し、該メモリ414との間でデータをやりとりし、及び該ソフトウェアに応じてコンピュータ400の動作を全般的に制御するよう構成される。誤り最小化ロジック410及びO/S422は、それらの全体又は一部(典型的には一部)が、プロセッサ412により読み出され、おそらくは該プロセッサ412内にバッファリングされ、次いで実行される。

40

#### 【0043】

図4に示すように、誤り最小化ロジック410がソフトウェアで実施される場合には、該誤り最小化ロジック410を、コンピュータによりデータを読み出すことが可能なあらゆる媒体(以下「コンピュータ読み出可能媒体」と称す)上に格納して、該コンピュータに関連するシステム又は方法により使用し又はそれらに関連して使用することができるようになることが可能である点に留意されたい。本書では、コンピュータ読み出可能媒体は、コン

50

ピュータ関連システム又は方法により使用し又はそれらに関連して使用するためのコンピュータプログラムを収容し又は格納することができる電子的、磁気的、光学的、又はその他の物理的な装置又は手段とすることが可能なものである。誤り最小化ロジック 410 は、命令実行システム、装置、又はデバイス（例えば、コンピュータベースのシステム、プロセッサを含むシステム、又は命令実行システム、装置、又はデバイスからの命令をフェッチして該命令を実行することができる他のシステム）により使用し、又はそれらに関連して使用するためのあらゆるコンピュータ読出可能媒体で実施することが可能である。本書では、「コンピュータ読出可能媒体」は、命令実行システム、装置、又はデバイスにより使用し又はそれらに関連して使用するためのプログラムを格納し、通信し、伝達し、又は移送することができる、あらゆる手段とすることが可能である。コンピュータ読出可能媒体は、例えば、電子、磁気、光学、電磁気、赤外線、又は半導体を利用したシステム、装置、デバイス、又は伝達媒体とすることが可能である（但しこれらには限定されない）。コンピュータ読出可能媒体の更なる特定の例として、1つ又は2つ以上の配線を有する電気的接続（電子的な一例）、ポータブルコンピュータディスク（磁気的な一例）、ランダムアクセスメモリ（RAM）（電子的な一例）、リードオンリーメモリ（ROM）（電子的な一例）、消去可能プログラマブルリードオンリーメモリ（EPROM、EEPROM、又はフラッシュメモリ）（電子的な一例）、光ファイバ（光学的な一例）、及びポータブルコンパクトディスク・リードオンリーメモリ（CD-ROM）（光学的な一例）が挙げられる（但しこれらには限定されない）。コンピュータ読出可能媒体は、プログラムが印刷された紙その他の適当な媒体とすることも可能である点に留意されたい。これは、プログラムを、例えば、紙その他の媒体の光学的な走査を介して電子的に捕捉し、次いで必要に応じて適当な態様でコンパイルし、解釈し、又はその他の処理を行って、コンピュータメモリに格納することができるからである。

10

20

30

40

50

#### 【0044】

システムがハードウェアで実施される代替的な実施形態では、誤り最小化ロジック 410 は、当業界で周知の技術、すなわち、複数のデータ信号に関して複数の論理機能を実施する複数の論理ゲートを有する離散的な論理回路（discrete logic circuit）、適当な組み合わせ論理ゲートを有する特定用途向け集積回路（ASIC）、プログラマブルゲートアレイ（PGA）、及びフィールドプログラマブルゲートアレイ（FPGA）等の何れか又はそれらの組み合わせを使用して実施することが可能である。

#### 【0045】

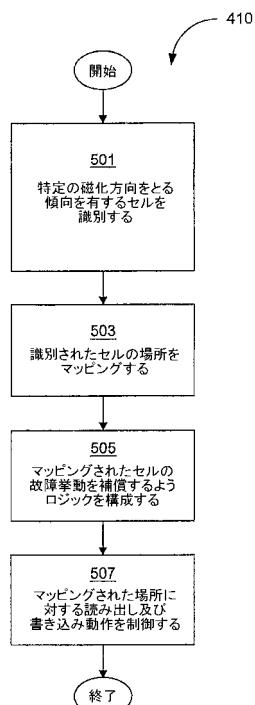

図5は、MRAM素子100等の磁気抵抗固体記憶素子にデータを格納する際の誤りを最小限にするために図4の誤り最小化ロジック 410 により実施することができる典型的な方法を示すフローチャートである。該フローチャートにおけるプロセスの記述又はブロックは、該プロセスにおける特定の論理機能又はステップを実施するための1つ又は2つ以上の実行可能命令を含むことが可能なコードのモジュール、セグメント、又は一部を表すものであることを理解されたい。また、関連する機能に応じて本書で説明し図示する順序とは異なる順序で（例えば、ほぼ同時に又は逆順で）機能が実行される代替的な実装形態もまた本発明の範囲内に含まれることが、当業者には理解されよう。

#### 【0046】

ブロック501では、誤り最小化ロジック 410 は、MRAM素子100中の各セルのうち、1つの磁化方向（逆平行よりも平行又はその逆）を他の方向よりも好む傾向を有することを特徴とする故障挙動を有するセル、及び各セルに関する特定の故障挙動とを識別する。図5に示す実施形態では、故障挙動の判定は、誤り最小化ロジック 410 により行われる。

#### 【0047】

本発明は、アレイ内のセルのうち1つの磁化方向を他の方向よりも好む傾向を有するセルを識別するために使用される特定の方法に限定されるものではない。当業者に知られているあらゆる検査方法（図3に関して上述した典型的な検査方法を含む（但しこれには限定されない））を使用して、素子内のセルの傾向を判定することが可能である。別の考え方得

る検査方法として（当業者にとって既知であるように）、素子中のセルの幾つか又は全てについてB H曲線を解析することが挙げられる。例えば、素子内の各セル（又は検査セット内の各セル）に磁界を加え、次いで、該素子（又は該素子のセルの検査用サブセット）内の各セル毎にB H曲線のオフセットを解析することに基づいて、各セル毎の故障挙動の判定を行う（又は検査セットを用いる場合には予測する）ことができる。

【0048】

ブロック501で故障挙動が判定されると、誤り最小化ロジックはブロック503に進む。ブロック503では、ブロック501で識別されたセルの場所が（例えば該場所をメモリ414に格納することにより）マッピングされる。ブロック501, 503は、特定の磁化状態をとる傾向を有するMRAM素子100内の各セルの場所の識別及びマッピングが完了するまで繰り返される。

【0049】

代替的な実施形態では（図示せず）、ブロック501, 503で実行される機能をMRAM素子100のバーンインプロセスの一部として実行し、及び判定された故障挙動を有するセルの場所をメモリ414内に予めマッピングすることが可能である。

【0050】

ここで図5の実施形態に戻る。各セルの場所についての特定の故障挙動が識別され（ブロック501）マッピングされる（ブロック503）と、ブロック505で、該マッピングされた各セルの特定の故障挙動を補償するように誤り最小化ロジック410が構成される。次いで、ブロック507で、該誤り最小化ロジック410を用いて、ブロック503でマッピングされた各場所に対する書き込み及び読み出し動作が制御され、これにより、それらの場所を使用すること及び該使用に関連する誤りを最小限にすることが可能となる。

【0051】

誤り最小化ロジック410は、種々の方法でデータを符号化及び復号化して、特定のセルに関する故障挙動を補償することが可能である。例えば、一実施形態では、誤り最小化ロジック410は、論理「1」の方向をとる傾向を有するセルを専ら使用して、論理「1」に対応するデータビットを格納し、論理「0」の方向をとる傾向を有するセルを専ら使用して、論理「0」に対応するデータビットを格納することが可能である。

【0052】

別の実施形態では、誤り最小化ロジック410は、論理「1」に対応するデータビットを、該ビットを論理「0」に反転させることにより符号化し、次いで、該反転されたビットを論理「0」の方向をとる傾向を有するセルに格納することが可能である。次いで、誤り最小化ロジック410は、該ビットをその復号化を行う際にその正しい論理状態に戻すことになる。

【0053】

更に別の実施形態では、誤り最小化ロジック410は、他の状態よりも一方の論理状態をとる傾向を有するセルを補償するために素子（又は該素子の検査セット）内の各セルについてのB H曲線のオフセットの解析を利用することが可能である。かかる解析に基づいて、誤り最小化ロジックは、特定のセルのB H曲線のオフセットを補償するために、（例えばB H曲線のオフセットを有するセルにおいて交差する特定のワード線及びビット線に加える電流を増大させることにより）該セルにデータを書き込むために加えられる磁界の強さを動的に変更することになる。

【0054】

本発明の原理から実質的に逸脱することなく上述の本発明の好適な実施形態に対して数多くの変更及び変形がなされ得ることは当業者には明らかであろう。他の状態よりも一方の論理状態を好む、アレイ内の幾つかのセルの傾向を補償することに関する基本的な概念を利用するために、本発明の他の修正例及び変形例を実施することが可能である。全てのかかる変更及び変形を特許請求の範囲で規定する本発明の範囲内に含めることができる。

【図面の簡単な説明】

10

20

30

40

50

【図1】本発明の実施形態が動作することが可能な典型的な磁気抵抗固体記憶素子である磁気ランダムアクセスメモリ(MRAM)素子アレイを単純化して示す説明図である。

【図2】図1のMRAM素子アレイの一実施形態を詳細に示す説明図である。

【図3】図1のMRAM素子アレイを示す別の説明図である。

【図4】本発明の一実施形態を実施するために用いることができるコンピュータシステムを単純化して示すブロック図である。

【図5】MRAM素子アレイ等の磁気抵抗固体記憶素子アレイにおける誤りを最小限にするために図4の誤り最小化ロジックにより実行される各ステップを示す例示的なフローチャートである。

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 テレル・アール・ムンデン

アメリカ合衆国アイダホ州 83702, ボイス, ノース・ナインティーンス・ストリート・202

0

(72)発明者 サラ・エム・プランデンバーガー

アメリカ合衆国アイダホ州 83704, ボイス, ノース・ハンプトン・2577

F ターム(参考) 5F083 FZ10 GA11