(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-318582

(P2005-318582A)

(43) 公開日 平成17年11月10日(2005.11.10)

(51) Int.C1.<sup>7</sup>H03M 1/10

H03M 1/14

F 1

H03M 1/10

H03M 1/14A

A

テーマコード(参考)

5J022

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 12 頁)

(21) 出願番号 特願2005-118765 (P2005-118765)

(22) 出願日 平成17年4月15日 (2005.4.15)

(31) 優先権主張番号 200410042087.5

(32) 優先日 平成16年4月30日 (2004.4.30)

(33) 優先権主張国 中国(CN)

(71) 出願人 505141934

リアルテック セミコンダクター コーポ

レイション

タイwan, シンチュー 300, サイエン

スベースド インダストリアル パーク

, イノベーション ロード ツー ナンバ

-2

(74) 代理人 100094318

弁理士 山田 行一

(74) 代理人 100123995

弁理士 野田 雅一

(72) 発明者 ジュイユアン サイ

タイwan, タイナン シティ 702,

ジンファ ロード, レーン475 セ

クション 1 ナンバー30

最終頁に続く

(54) 【発明の名称】パイプラインADC較正方法およびその装置

## (57) 【要約】 (修正有)

【課題】外部アナログ/デジタル変換モジュールを利用するデジタル自己較正・パイプライン・アナログ/デジタル変換器(ADC)と、それに関連する方法とを提供する。

【解決手段】パイプラインADCが、直列にカスケード接続されてパイプラインを形成する複数のアナログ/デジタル変換ユニットを有している。このパイプラインADCのための誤差補正方法は、第1モードであるときに、外部アナログ/デジタル変換モジュールを用いて前記複数のアナログ/デジタル変換ユニットを評価するステップと、前記評価ステップにおける前記外部アナログ/デジタル変換モジュールのデジタル出力値に基づいて複数の補正係数の組を計算するステップと、第2モードであるときに、前記補正係数の組に基づいて前記複数のアナログ/デジタル変換ユニットの出力信号を補正するステップとを含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

直列にカスケード接続されてパイプラインを形成する複数のアナログ／デジタル変換ユニットを有するパイプライン・アナログ／デジタル変換器（A D C）のための誤差補正方法であって、

第1モードであるときに、外部アナログ／デジタル変換モジュールを用いて前記複数のアナログ／デジタル変換ユニットを評価するステップと、

前記評価ステップにおける前記外部アナログ／デジタル変換モジュールのデジタル出力値に基づいて複数の補正係数の組を計算するステップと、

第2モードであるときに、前記補正係数の組に基づいて前記複数のアナログ／デジタル変換ユニットの出力信号を補正するステップと

10

を含む方法。

**【請求項 2】**

前記外部アナログ／デジタル変換モジュールがシグマ・デルタA D Cを備える、請求項1に記載の方法。

**【請求項 3】**

前記複数の補正係数の組を計算するステップが、前記外部アナログ／デジタル変換モジュールと前記パイプラインとの間の誤差を除去するための計算を実行するステップをさらに含む、請求項1に記載の方法。

**【請求項 4】**

前記複数の補正係数の組を計算するステップが、それぞれのアナログ／デジタル変換ユニットに対応して、前記パイプラインにおける後方段の誤差の影響を補償するための計算を実行するステップをさらに含む、請求項1に記載の方法。

**【請求項 5】**

アナログ入力信号をデジタル出力信号に変換するためのデジタル較正・パイプライン・アナログ／デジタル変換器（A D C）であって、

直列にカスケード接続されてパイプラインを形成し、複数のデジタル出力端を含む複数のアナログ／デジタル変換ユニットと、

第1モードであるときに、前記複数のアナログ／デジタル変換ユニットを評価するための、前記パイプラインに結合された外部アナログ／デジタル変換モジュールと、

第2モードであるときに、前記デジタル出力信号を生成するために、前記外部アナログ／デジタル変換モジュールにより実行された評価の結果に基づいて、前記デジタル出力端で信号を補正するための、前記アナログ／デジタル変換ユニットおよび前記外部アナログ／デジタル変換モジュールに結合された補正装置と

30

を備えるパイプラインA D C。

**【請求項 6】**

前記外部アナログ／デジタル変換モジュールがシグマ・デルタA D Cを備える、請求項5に記載のパイプラインA D C。

**【請求項 7】**

前記パイプラインと前記外部アナログ／デジタル変換モジュールとの間に結合されたマルチプレクサをさらに備える、請求項5に記載のパイプラインA D C。

**【請求項 8】**

前記外部アナログ／デジタル変換モジュールにより実行された評価の結果に基づいて、複数の補正係数の組を計算するための、前記外部アナログ／デジタル変換モジュールに結合された演算装置をさらに備える、請求項5に記載のパイプラインA D C。

**【請求項 9】**

前記演算装置が、前記外部アナログ／デジタル変換モジュールと前記パイプラインとの間の誤差を除去するための計算を実行する、請求項8に記載のパイプラインA D C。

**【請求項 10】**

前記演算装置が、それぞれのアナログ／デジタル変換ユニットについて、前記パイプラ

10

20

30

40

50

インにおける後方段の誤差の影響を補償するための計算を実行する、請求項 5 に記載のパイプライン A D C。

【発明の詳細な説明】

【発明の分野】

【0001】

本発明は、アナログ / デジタル変換器 (A D C) 較正方法およびその装置に関し、特に 10

は、パイプライン A D C のためのデジタル較正方法およびその装置に関する。

【従来技術の説明】

【0002】

パイプライン・アナログ / デジタル変換器 (A D C) は、高速・高分解能なアナログ / 10

デジタル変換のための A D C の典型的なものである。アナログ較正またはデジタル較正の

ようなトリミングや較正の技術を用いなければ、パイプライン A D C の分解能は、製造時

に引き起こされるコンデンサの不整合、またはオペアンプの限定されたゲイン値のような

制限要因のために、10 ~ 12 ビット程度にしか達しない。さらなる回路または較正技術

が、より大きなビット数を有する高分解能の A D C を実現するのに必要とされる。

【0003】

米国特許第 5 4 9 9 0 2 7 号および米国特許第 6 3 6 9 7 4 4 号（これらの内容を本明

細書に参照により援用する）を参照して頂きたい。上記の 2 つの特許においては、デジタル

自己較正機能およびそれに関連する回路を含むパイプライン A D C が開示されている。 20

上記特許によれば、A D C はパイプライン構造を含んでいる。このパイプライン構造は、

入力段および複数の後段を含む複数段のアナログ / デジタル変換ユニットを含んでいる。

このアナログ / デジタル変換ユニットの特定の段の較正により、上記の制限要因に起因す

る誤差を除去することができる。したがって、A D C はまた、アナログ / デジタル変換ユ

ニットの特定の段に対応する較正装置をも含んでいる。この A D C は、アナログ / デジタル

変換ユニットの特定の段を較正するために、アナログ / デジタル変換ユニットのうちの

後方段の変換ユニット、較正装置、および、アナログ / デジタル変換ユニットの特定の段

に対応する一組の較正パラメーターを利用する。

【0004】

較正セットアップモードにおいて、アナログ / デジタル変換ユニットの特定の段の入力

信号を所定の値に設定し、後方段の出力値を記録して、適切な計算を行なうことにより、

較正パラメーターの組が導き出される。この設計によって、較正パラメーターの組が、A 30

D C 回路に起因して存在する誤差を正確に表すように、ランモードと同じ条件下で評価さ

れる。

【0005】

上記の自己較正方法は、アナログ / デジタル変換ユニットの特定の段を較正するために、

パイプライン構造のアナログ / デジタル変換ユニットのうちの後方段の変換ユニットを

利用している。したがって、較正プロセスを実行するために、後方段の変換ユニットの精度

は一定程度に達していることが必要である。この目的を達するためには、パイプライン

構造の回路は、より消費電力が大きく、すなわちより大きな面積を占めるようになり（より

良いコンデンサの整合は、換言すればコンデンサの面積がより大きいことであるため）、

あるいは、回路がはるかに複雑になるか、または、誤差の評価または較正に非常に

時間がかかる。 40

【発明の概要】

【0006】

したがって、本発明の目的は、外部アナログ / デジタル変換モジュールを利用するデジ

タル自己較正・パイプライン・アナログ / デジタル変換器 (A D C) と、それに関連する

方法とを提供することにある。

【0007】

本発明の代表的な一実施形態によれば、パイプライン A D C のための誤差補正方法が開

示されている。パイプライン A D C は、直列にカスケード接続されてパイプラインを形成 50

する複数のアナログ／デジタル変換ユニットを有している。本方法は以下のステップ、すなわち、第1モードであるときに、外部アナログ／デジタル変換モジュールを用いて前記複数のアナログ／デジタル変換ユニットを評価するステップと、前記評価ステップにおける前記外部アナログ／デジタル変換モジュールのデジタル出力値に基づいて複数の補正係数の組を計算するステップと、第2モードであるときに、前記補正係数の組に基づいて前記複数のアナログ／デジタル変換ユニットの出力信号を補正するステップとを含んでいる。

#### 【0008】

本発明の他の代表的な実施形態によれば、アナログ入力信号をデジタル出力信号に変換するためのデジタル較正・パイプラインA D Cが開示されている。本パイプラインA D Cは、直列にカスケード接続されてパイプラインを形成し、複数のデジタル出力端を含む複数のアナログ／デジタル変換ユニットと、第1モードであるときに、前記複数のアナログ／デジタル変換ユニットを評価するための、前記パイプラインに結合された外部アナログ／デジタル変換モジュールと、前記アナログ／デジタル変換ユニットおよび前記外部アナログ／デジタル変換モジュールに結合された補正装置とを備えている。補正装置は、第2モードであるときに、前記デジタル出力信号を生成するために、前記外部アナログ／デジタル変換モジュールにより実行された評価の結果に基づいて、前記デジタル出力端で信号を補正する。

#### 【0009】

本発明のこれらおよび他の目的は、さまざまな図面に示す好ましい実施形態の以下の詳細な説明が読まれた後には、当業者には明らかとなるであろう。

#### 【詳細な説明】

#### 【0010】

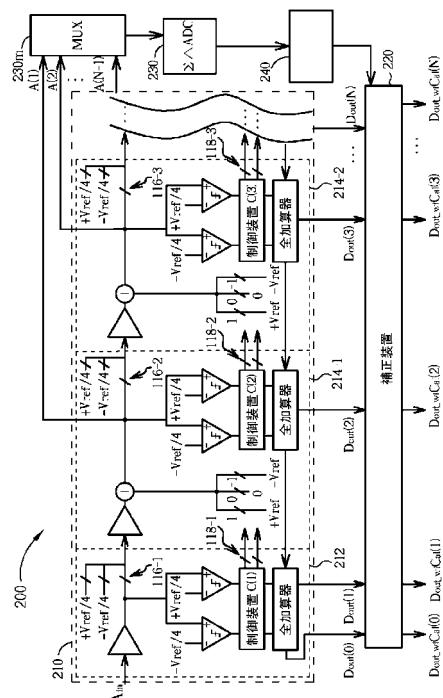

図1を参照する。これは、本発明の一実施形態によるデジタル較正・パイプライン・アナログ／デジタル変換器（A D C）200の図である。パイプラインA D C 200は、パイプライン構造210（「パイプライン」と呼ぶことができる）を含んでいる。パイプライン構造210は、図1に示すように直列にカスケード接続されている、入力段212と、複数の後段214-1、214-2、……、214-Nとを含んでいる。パイプラインA D C 200はさらに、複数の補正係数の組に基づいてパイプライン構造210のデジタル出力値（すなわちデジタル出力信号）を補正するための補正装置220を含んでいる。本実施形態の以下の説明においては、パイプラインA D C 200は、1.5ビット／段の構造を用いて示しているが、その回路構成および動作原理は当技術分野において周知であり、したがって本明細書中では説明しない。1.5ビット／段の他にも、本発明の方法および装置は、本発明の他の実施形態に従って、1ビット／段または複数ビット／段のアーキテクチャで用いることもできるということを当業者は理解できるはずであるということに留意されたい。

#### 【0011】

上記の構成要素に加えて、パイプラインA D C 200はさらに、マルチプレクサ230mによって後段214-1、214-2、……、214-（N-1）のうちの一つの後段214-Iのアナログ出力端に選択的に結合される、後段214-Iの較正を行うための外部アナログ／デジタル変換モジュール230を含んでいる（ここで、I=1, 2, ……, またはN-1）。パイプラインA D C 200はさらに演算装置240を含んでおり、この演算装置240は、外部アナログ／デジタル変換モジュール230のデジタル出力値に対して適切な計算を行って、補正係数（すなわち、上記の複数の補正係数の組）を生成するために、外部アナログ／デジタル変換モジュール230のデジタル出力端に結合されている。本実施形態においては、外部アナログ／デジタル変換モジュール230は、高分解能や小さな回路面積といった利点を有するシグマ・デルタA D Cを用いて実現されているということに留意して頂きたい。しかし、当業者には、これが本発明を限定するものではないということが理解されるはずである。本発明の実現が妨げられないかぎり、他の種類のA D Cを、本発明の他の実施形態に従う他のパイプラインA D Cに適用することができ

る。

【0012】

デジタル較正パイプラインADC200の動作は、較正セットアップモードおよびランモードに密接に関連する。較正セットアップモードの間、パイプラインADC200は、スイッチ116-Iおよび118-Iを用いて、基準電圧+V<sub>ref</sub>/4や基準電圧-V<sub>ref</sub>/4のような所定の値に較正される後段214-I(ここで、I=1, 2, ..., またはN-1)の入力端、および、後段214-Iの制御装置によって生成される制御信号C(I)をそれぞれ接続する。加えて、パイプラインADC200は、マルチプレクサ230mを用いて、後段214-Iのアナログ出力端を、外部アナログ/デジタル変換モジュール230の入力端に結合する。結果として、パイプラインADC200は、演算装置240を用いて、外部アナログ/デジタル変換モジュール230のデジタル出力値OUTに基づいて、それぞれの後段214-Iに対応する補正係数を計算することができる。一方、ランモードの間、パイプラインADC200は、補正装置220を用いて、較正セットアップモードから得られた補正係数に基づいて、パイプライン構造210により出力されたデジタル出力値を補正する。結果として、パイプラインADC200の回路に起因する誤差の影響を、減少または除去することができる。

【0013】

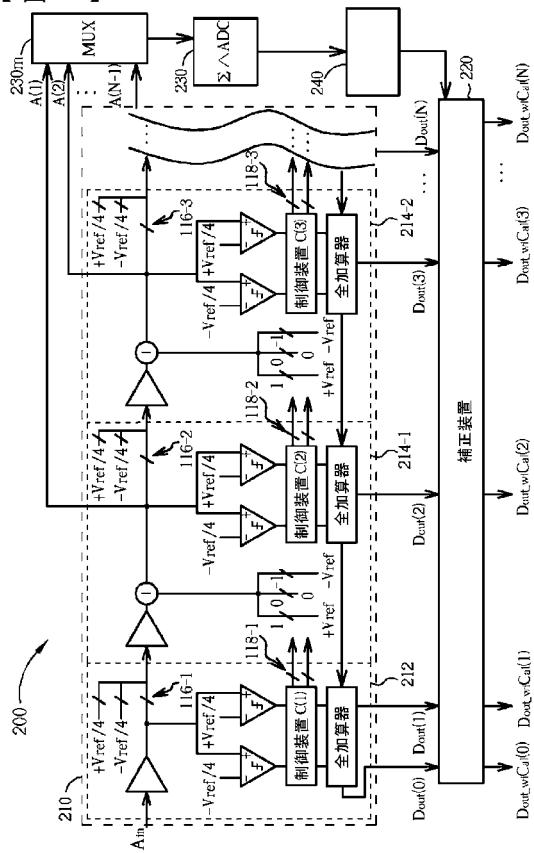

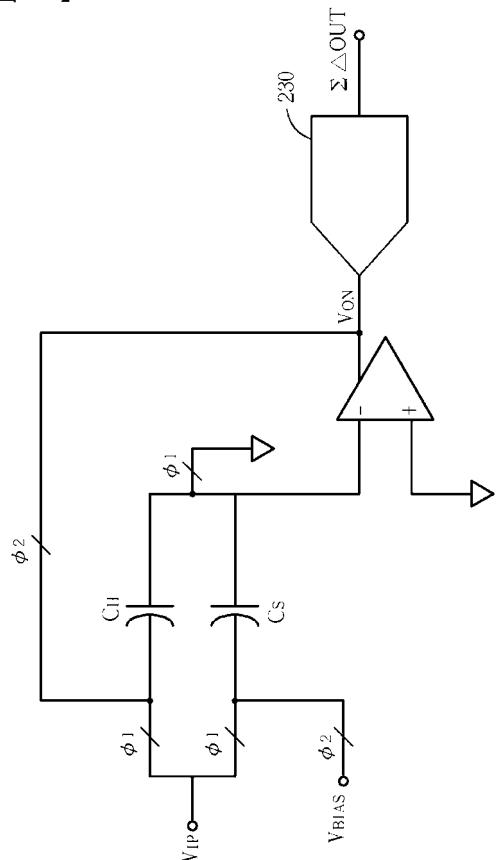

図2は、上記の較正セットアップモードであるときに用いられる外部アナログ/デジタル変換モジュール230と、較正される後段214-Iとの図を示している。図2に示すように、複数のスイッチを制御するための信号1および2は交互にアクティブとなり、これらの信号(1および2)および対応するスイッチの動作原理は、当技術分野において周知である。以下において、図1に示す演算装置240の動作原理を、一実施例に基づいて、図2を用いて詳細に説明する。まず、本実施形態においては、パイプライン構造210は14の段(すなわち1つの入力段および13の後段)を含んでおり、また、誤差が他の後段のそれらに比べて重要でないため、後段214-4、214-5、..., 214-13の出力値の影響は無視しうると仮定する。この場合、それらの後方段の出力値を較正する必要はなく、後段214-1、214-2、214-3、および214-4の補正係数の計算は以下のように説明される。

【0014】

後段214-Iに対応する補正係数[CALA(I), CALB(I)]を計算しているとき、図3に示す評価条件を図2に示す回路に適用するのが望ましい。図3に示すように、評価条件には、アナログ入力端に入力される電圧V<sub>IP</sub>と、デジタル入力端に入力される制御信号C(I)により制御される固定バイアスV<sub>BIAS</sub>と、上記のセットアップから導かれる、アナログ出力端から出力される電圧V<sub>ON</sub>とが含まれる。図3に各列で示す評価条件テーブルを参照して頂きたい。外部アナログ/デジタル変換モジュール230のデジタル出力端OUTからそれぞれの値S1(I)、S2(I)、S3(I)、およびS4(I)を読み込んだ後、演算装置240は、複数のパラメーターERA(I)およびERB(I)を、以下の式に従って計算する。

【数1】

$$ERA(I) = S1(I) - S2(I)$$

$$ERB(I) = S3(I) - S4(I)$$

上記の評価条件、ならびにパラメーターERA(I)およびERB(I)の意味は、当技術分野において周知であるので、本明細書中で説明する必要はない。

【0015】

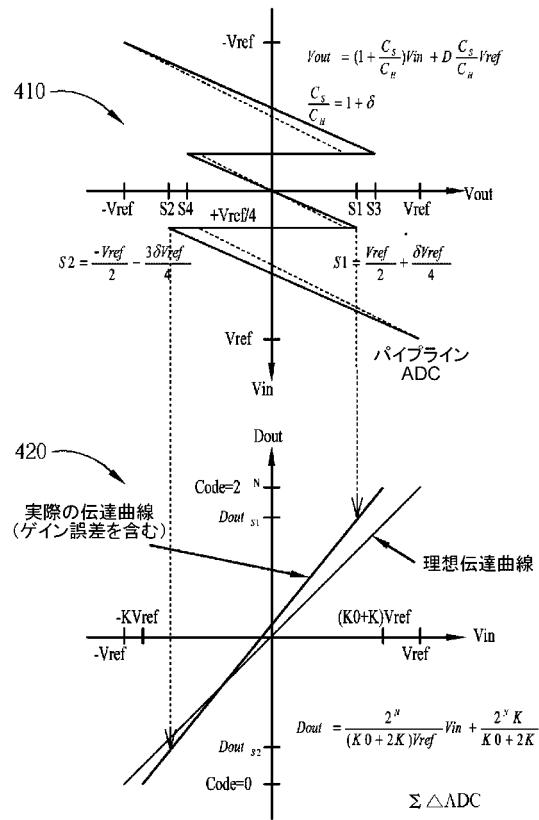

図4を参照して頂きたいが、これは、パイプライン構造210の後段214-Iの伝達曲線410(段214-Iが評価されている)と、外部アナログ/デジタル変換モジュール230の伝達曲線420とを同時に示している。伝達曲線410には理想伝達曲線が含まれてあり、これは破線で描かれていて、誤差が生じていないものを示している。図4に示すように、伝達曲線410にはさらに実際の伝達曲線が含まれており、これは太線で描

10

20

30

40

50

かれていて、後段 214-I におけるコンデンサの不整合のようなある原因に起因する誤差の影響が考慮されたものを見ている。さらに、伝達曲線 420 には理想伝達曲線が含まれており、これは細線で描かれていて、誤差が生じていないものを示している。図 4 に示すように、伝達曲線 420 にはさらに実際の伝達曲線が含まれており、これは太線で描かれていて、外部アナログ / デジタル変換モジュール 230 と、パイプライン構造 210 における低い段との間のゲイン誤差およびオフセット誤差の影響を示している。図 4 に示す伝達曲線の意味は、当技術分野において周知であり、米国特許第 5499027 号および米国特許第 6369744 号に示されているようなものである。

## 【0016】

ゲイン誤差およびオフセット誤差を十分に記述するために、2つのパラメーター  $K_0$  および  $K$  を以下において導入する。伝達曲線 420 における実際の伝達曲線の伝達関数は、以下の式を用いて記述することができる。

## 【数 2】

$$Dout = \frac{2^{(N-I)}}{(K_0 + 2K)Vref} Vin + \frac{2^{(N-I)}K}{K_0 + 2K} \quad (1)$$

この式 (1) において、 $Dout$  は外部アナログ / デジタル変換モジュール 230 のデジタル出力値、 $Vin$  は外部アナログ / デジタル変換モジュール 230 の入力信号、そして  $N$  はパイプライン構造 210 の段数である。本実施形態においては、段数は 14 である。

## 【0017】

伝達曲線 410 によって示されるように、後段 214-I の回路に起因する誤差の影響を記述するために、誤差パラメーター  $\delta$  を以下において導入する。値  $S_1$  および  $S_2$  に対応して、外部アナログ / デジタル変換モジュール 230 の入力信号  $Vin$  は、以下の式に従って記述することができる。

## 【数 3】

$$Vin_{S1} = \frac{Vref}{2} + \frac{\delta Vref}{4}$$

$$Vin_{S2} = -\frac{Vref}{2} - \frac{3\delta Vref}{4}$$

上記の 2 つの式を式 (1) に代入することによって、以下の式が導き出される。

## 【数 4】

$$Dout_{S1} = \frac{2^{(N-I)}}{K_0 + 2K} \frac{1}{2} + \frac{2^{(N-I)}K}{K_0 + 2K} + \frac{2^{(N-I)}\delta}{K_0 + 2K} \frac{1}{4}$$

$$Dout_{S2} = \frac{2^{(N-I)}}{K_0 + 2K} \frac{-1}{2} + \frac{2^{(N-I)}K}{K_0 + 2K} - \frac{2^{(N-I)}3\delta}{K_0 + 2K} \frac{1}{4}$$

$ERA = Dout_{S1} - Dout_{S2}$  であるので、式 (2) が以下のように導き出される。

## 【数 5】

$$ERA = Dout_{S1} - Dout_{S2} = \frac{2^{(N-I)}}{K_0 + 2K} + \frac{2^{(N-I)}\delta}{K_0 + 2K} \quad (2)$$

## 【0018】

演算装置 240 を用いて補正係数 [CALA(I), CALB(I)] を導き出すために、伝達曲線 410 および伝達曲線 420 に示される誤差 (すなわち  $K_0$  および  $K$ ) を、計算を利用して除去することが望ましい。本実施形態においては、伝達曲線 420 によって示される誤差が最初に処理される。理想的な場合について、式 (2) における 2 つのパ

10

20

30

40

50

ラメータ  $K_0$  および  $K$ 、ならびにパラメーター ERA の各値は以下のように列挙される。

## 【数6】

$$K_0 = 0$$

$$K = 1$$

$$ERA = 2^{(N-I-1)} + 2^{(N-I-1)} \delta$$

較正する最初の4段、すなわち 214-1、214-2、214-3、および 214-4 を考えると、以下の式が得られる。

## 【数7】

$$\begin{aligned} ERA(4) - 2^9 &= 2^9 \delta_4 \\ ERA(3) - 2^{10} &= 2^{10} \delta_3 \\ ERA(2) - 2^{11} &= 2^{11} \delta_2 \\ ERA(1) - 2^{12} &= 2^{12} \delta_1 \end{aligned} \tag{3}$$

ここで  $\delta_1$ 、 $\delta_2$ 、 $\delta_3$ 、 $\delta_4$  は、それぞれパイプライン構造 210 の1段、2段、3段、および4段の誤差である。しかし、実際の場合には、パラメーター  $K_0$  および  $K$  は無視できない。最初の4段をふたたび考えると、以下の式が得られる。

## 【数8】

$$\begin{aligned} ERA(4) &= \frac{2^{10}}{K_0 + 2K} + \frac{2^{10} \delta_4}{K_0 + 2K} \\ ERA(3) &= \frac{2^{11}}{K_0 + 2K} + \frac{2^{11} \delta_3}{K_0 + 2K} \\ ERA(2) &= \frac{2^{12}}{K_0 + 2K} + \frac{2^{12} \delta_2}{K_0 + 2K} \\ ERA(1) &= \frac{2^{13}}{K_0 + 2K} + \frac{2^{13} \delta_1}{K_0 + 2K} \end{aligned} \tag{4}$$

後段 214-4、214-5、……、214-13 の出力値の影響は無視できるという前述の仮定に基づいて、誤差  $\delta_4$  はゼロとすることができます。演算装置 240 の計算を利用して、式(4)に示されるように実際の測定値に基づく誤差によって影響されることのない理想値を得るために、本実施形態の演算装置 240 は、以下の式に従って計算を実行することができる。

## 【数9】

$$\begin{aligned} ERA\_Cal(4) &= 0 \\ ERA\_Cal(3) &= \text{Round}(ERA(3)/ERA(4)*512-1024) \\ ERA\_Cal(2) &= \text{Round}(ERA(2)/ERA(4)*512-2048) \\ ERA\_Cal(1) &= \text{Round}(ERA(1)/ERA(4)*512-4096) \end{aligned}$$

## 【0019】

上記 ERA\_Cal(I) は、伝達曲線 420 により示される誤差を除去した後に導き出される中間係数を表しており、Round( ) は、四捨五入の作用をする関数を示している。同様にして、以下の式が得られる。

10

20

30

40

## 【数10】

```

ERB_Cal(4)=0

ERB_Cal(3)=Round(ERB(3)/ERB(4)*512-1024)

ERB_Cal(2)=Round(ERB(2)/ERB(4)*512-2048)

ERB_Cal(1)=Round(ERB(1)/ERB(4)*512-4096)

```

## 【0020】

上記の計算を用いて外部アナログ / デジタル変換モジュール 230 とパイプライン 210 の後方段との間のゲイン誤差およびオフセット誤差を除去した後、演算装置はさらに、

10 パイプライン構造 210 の後方段の誤差に起因する影響を補償するための計算を実行する。本実施形態においては、演算装置 240 は、パイプライン構造 210 の後方段の誤差に起因する影響を補償するための複数の中間係数 ERA\_Cal\_Add(I) および ERB\_Cal\_Add(I) を計算することができる。これらの計算は、以下の式を用いて記述することができる。

## 【数11】

```

ERA_Cal_Add(4)=ERA_Cal(4)

ERB_Cal_Add(4)=ERB_Cal(4)

ERA_Cal_Add(3)=ERA_Cal(3)-ERA_Cal(4)

ERB_Cal_Add(3)=ERB_Cal(3)-ERB_Cal(4)

ERA_Cal_Add(2)=ERA_Cal(2)-ERA_Cal(3)

ERB_Cal_Add(2)=ERB_Cal(2)-ERB_Cal(3)

ERA_Cal_Add(1)=ERA_Cal(1)-ERA_Cal(2)

ERB_Cal_Add(1)=ERB_Cal(1)-ERB_Cal(2)

```

中間係数 ERA\_Cal\_Add(I) および ERB\_Cal\_Add(I) を計算した後、演算装置 240 は、以下に記述される伝達方程式を用いて、補正係数の組 CALA(I)

30 および CALB(I) (ここで、後方段の値は無視することができる、ここでは I = 1, 2, 3, 4) を生成することができる。

## 【数12】

```

CALA(4)=ERA_Cal_Add(4)

CALB(4)=ERB_Cal_Add(4)

CALA(3)=ERA(3)_Cal_Add +CALA(4)+CALB(4)

CALB(3)=ERB(3)_Cal_Add +CALA(4)+CALB(4)

CALA(2)=ERA(2)_Cal_Add +CALA(3)+CALB(3)

CALB(2)=ERB(2)_Cal_Add +CALA(3)+CALB(3)

CALA(1)=ERA(1)_Cal_Add +CALA(2)+CALB(2)

CALB(1)=ERB(1)_Cal_Add +CALA(2)+CALB(2)

```

## 【0021】

最後に、ランモードであるときの補正装置 220 の動作原理を以下において説明する。補正装置 220 は、ランモードであるときに、補正係数 CALA(I) および CALB(I)

40 に基づいて、パイプライン構造 210 のデジタル出力端で信号 (すなわち出力値 Dout(I)) を補正し、パイプライン ADC200 のデジタル出力信号 Dout\_wic

a1 の補正されたデジタル値 Dout\_wic\_a1(0) ~ Dout\_wic\_a1(N) を生成することができる。演算装置 240 が較正セットアップモードであるときに補正係数

50

C A L A ( I ) および C A L B ( I ) を導き出した後、補正装置 220 は、ランモードであるときに、以下のように、デジタル出力信号 D o u t \_ w i C a l の全てのビット D o u t \_ w i C a l ( I ) ( I = 1 , 2 , … … , N ) を生成することができる。

【数 1 3】

```

if C(I)=-1, then Dout_wiCal(I) = D(I) - CALB(I);

if C(I)= 0, then Dout_wiCal(I) = D(I);

if C(I)=+1, then Dout_wiCal(I) = D(I) + CALA(I).

```

【0 0 2 2】

上記の演算装置 240 および補正装置 220 の動作は、本発明の单なる一実施形態に基づいて説明されていることに留意して頂きたい。当業者には、本発明の実現が妨げられないかぎり、本発明のさまざまな種類のアーキテクチャや方法を本発明の他の実施形態に適用することができるということが理解されるはずである。

【0 0 2 3】

当業者にはまた、本発明の教示を保ちながら、本装置および方法の多くの変形および変更をなしうるということも容易に認められるであろう。したがって、上記の開示は、添付の特許請求の範囲の境界・限界によってのみ制限されるものとして解釈されるべきである。

【図面の簡単な説明】

【0 0 2 4】

【図 1】本発明の一実施形態によるデジタル較正・パイプライン・アナログ / デジタル変換器 ( A D C ) の図である。

【図 2】図 1 に示すパイプライン構造における 1 つの後段と、本発明の一実施形態に従つて用いられる外部アナログ / デジタル変換モジュールとの図である。

【図 3】図 2 に示す装置により用いられる評価条件テーブルである。

【図 4】図 1 に示すパイプライン構造と外部アナログ / デジタル変換モジュールとの伝達曲線の図である。

【符号の説明】

【0 0 2 5】

1 1 6 … スイッチ、2 1 0 … パイプライン、2 1 2 … 入力段、2 1 4 … 後段、2 2 0 … 補正装置、2 3 0 … デジタル変換モジュール。

【図 1】

【図 2】

【図 3】

| VIP          | VBIAS      | V <sub>ON</sub>  | $\Sigma \Delta$ OUT |

|--------------|------------|------------------|---------------------|

| $+V_{ref}/4$ | $-V_{ref}$ | $2V_n - V_{ref}$ | S2(1)               |

| $+V_{ref}/4$ | 0          | $2V_n$           | S1(1)               |

| $-V_{ref}/4$ | 0          | $2V_n$           | S4(1)               |

| $-V_{ref}/4$ | $+V_{ref}$ | $2V_n + V_{ref}$ | S3(1)               |

【図 4】

---

フロントページの続き

(72)発明者 チャオ - チエン リー

台湾, タオヤン カントリー 320, ジョグリ シティ, シンシェン ロード, サン・ギ アパートメント, レーン 2 ナンバー 61-1

(72)発明者 ウエン - チ ワン

台湾, ユウリン カントリー 648, シルオ タウンシップ, シンフォン ヴィレッジ ナンバー 225

(72)発明者 チア - リアン チャン

台湾, タイペイ カントリー 242, シンジャン シティ, ミン - アン ロード ナンバー 425

F ターム(参考) 5J022 AA05 BA03 BA04 CB06 CD02 CF01

【外國語明細書】

2005318582000001.pdf