(19)

REPUBLIK

ÖSTERREICH

Patentamt

(10) Nummer: AT 410 048 B

(12)

## PATENTSCHRIFT

(21) Anmeldenummer: A 504/99

(22) Anmeldetag: 19.03.1999

(42) Beginn der Patentdauer: 15.05.2002

(45) Ausgabetag: 27.01.2003

(51) Int. Cl.<sup>7</sup>: H04L 1/00

H03M 13/05, H04Q 11/04

(56) Entgegenhaltungen:

WO 98/49799A2

(73) Patentinhaber:

SIEMENS AG ÖSTERREICH

A-1210 WIEN (AT).

(72) Erfinder:

STADLER ANDREAS DIPL.ING. DR.

WIEN (AT).

(54) BITFEHLERKORREKTURVERFAHREN

AT 410 048 B

(57) Bei einem Verfahren zur gesicherten Datenübertragung in synchronen Übertragungssystemen wird der Übertragungsrahmen in fünf gleich lange Codierungsblöcke geteilt, wobei je alle ersten, zweiten bis achten Bits der zu sichernden Bytes durch einen zwei Fehler korrigierenden Block-Code gesichert werden, die jeweiligen Paritätsbytes der zugehörigen Codierungsblöcke auf die Zeilen des Rahmens aufgeteilt werden und zumindest in einer Zeile (Z 3) zusätzlich zu den Paritätsbytes (P 4) eines Blockes ein oder mehrere Paritätsbytes (P 3) des vorgehenden/nachfolgenden Blockes (BL 3) hinzugefügt werden. Ein ähnliches Verfahren verwendet einen acht oder zehn Fehler korrigierenden Code.

Die Erfindung bezieht sich auf ein Verfahren zur gesicherten Datenübertragung in synchronen Übertragungssystemen, bei welchem die Daten in Übertragungsrahmen mit einem Overhead und einer Payload und einer neunzeiligen Struktur übertragen werden, und bei welchen Paritätsbytes in der zweiten, dritten, sechsten, siebenten und achten Zeile des Overhead eingefügt werden, der Übertragungsrahmen in fünf gleich lange Codierungsblöcke geteilt wird, und je alle ersten, zweiten bis achten Bits der zu sichernden Bytes eines Codierungsblockes durch einen zwei Fehler korrigierenden Block-Code gesichert werden, dessen Kontrollinformation dem Overhead eingefügt wird.

Ebenso bezieht sich die Erfindung auf ein Verfahren zur gesicherten Datenübertragung in synchronen Übertragungssystemen, bei welchem die Daten in Übertragungsrahmen mit einem Overhead und einer Payload und einer neunzeiligen Struktur übertragen wurden, und bei welchem Paritätsbytes in den Overhead eingefügt werden sowie der Übertragungsrahmen in fünf gleich lange Codierungsblöcke geteilt wird.

Um bei der Datenübertragung in synchronen Übertragungssystemen, welche nach der synchronen digitalen Hierarchie SDH arbeiten, beispielsweise mit STM-N- oder OC-3N-Signalen, werden zur Verringerung der Fehlerrate fehlerkorrigierende Codes verwendet. Dabei muß allerdings besonders darauf geachtet werden, dass die vom ITU (International Telecommunication Union) empfohlenen Übertragungspulsrahmen nicht geändert werden. Für STM-1-Pulsrahmen ist in der Recommendation G.708 (März 1993), Fig. 5-2, ein Pulsrahmen dargestellt, bei welchem die benötigten Kontroll- oder Paritätsbytes in frei verfügbaren Zeitschlitzten (Bytes) eingefügt sind. (STM = Synchronous Transport Module)

Ein konkreteres Verfahren zur gesicherten Datenübertragung in SDH-Systemen ist in der WO 98/49799 der Anmelderin angegeben. Dabei wird eine strenge Aufteilung der Paritätsbytes jedes Blockes dahingehend vorgeschrieben, dass sämtliche Paritätsbytes eines Blockes genau in einer Zeile enthalten sind. Dies setzt wiederum eine ganz bestimmte Grundstruktur der Übertragungsrahmen voraus, die trotz der genannten Normung nicht überall vorhanden ist.

Eine Aufgabe der Erfindung liegt daher darin, ein Verfahren anzugeben, das umfangreicher und flexibler einzusetzen ist als die bekannten Verfahren.

Diese Aufgabe wird mit einem Verfahren der eingangs genannten Art gelöst, bei welchem erfindungsgemäß die jeweiligen Paritätsbytes der zugehörigen Codierungsblöcke auf die Zeilen des Rahmens aufgeteilt werden und zumindest in einer Zeile zusätzlich zu den Paritätsbytes eines Blockes ein oder mehrere Paritätsbytes des vorgehenden und/oder nachfolgenden Blockes hinzugefügt werden.

Dank der Erfindung kann das unterschiedliche Platzangebot an freien Bytes innerhalb der Rahmen berücksichtigt werden, wobei trotz der gewünschten Verbesserung der Flexibilität des Verfahrens zu Zwecken der Zwischenspeicherung nur geringfügige und nicht ins Gewicht fallende größere Verzögerungszeiten erforderlich sind.

Im Sinne einer Verringerung des Speicherbedarfes für Zwischenspeicherung ist es zweckmäßig, wenn zu den Paritätsbytes eines Blockes Paritätsbytes des vorgehenden Blockes hinzugefügt werden.

Weiters kann es vorteilhaft sein, wenn ein Codierungsblock mit dem Ende der siebenten Zeile endet. Damit wird ein Interleaving von Paritäts- und Informationsbytes eines Blockes vermieden, sodass keine zusätzliche Verzögerung von Informationsbytes in einem Coder notwendig ist.

Eine vorteilhafte Variante zeichnet sich weiters dadurch aus, dass der Block-Code ein BCH-Code mit 1944 Bits, davon 1922 Datenbits ist, da ein solcher Code relativ einfach zu implementieren ist und einen guten Schutz besitzt. BCH ist dabei die Abkürzung für Bose-Chandhuri-Hocquenghem.

Ein weiteres Verfahren nach der Erfindung, dessen Vorteil darin liegt, dass es relativ wenig Paritätsbits benötigt, zeichnet sich dadurch aus, dass alle Bits eines Codierungsblocks durch einen mindestens acht Fehler korrigierenden Blockcode gesichert werden. Dabei ist es ratsam, wenn die Paritätsbytes in der zweiten, dritten, fünften, siebenten und neunten Zeile des Overheads eingefügt werden.

Eine besonders zweckmäßige und die Ressourcen gut nutzende Ausführungsform ist dadurch gekennzeichnet, dass ein zehn Fehler korrigierender Block-Code verwendet wird.

Dabei kann es auch vorteilhaft sein, wenn jeweils sämtliche Paritätsbytes eines Codierungsblocks in einer Zeile des Pulsrahmens angeordnet sind.

Die Erfindung ist zweckmäßigerweise bei einem System realisiert, bei welchem das synchrone Übertragungssystem STM-N- bzw. OCN-3N-Signale verwendet.

Es empfiehlt sich besonders, wenn N ein ganzzahliges Vielfaches von vier ist, da sich eine größere Anzahl verfügbarer Overhead-Bytes ergibt.

5 Die Erfindung ist auch besonders dann sehr zweckmäßig, wenn die zur Einteilung der Codierungsblöcke verwendeten Übertragungsrahmen durch byteweises Demultiplexen aus Rahmen höherer Ordnung abgeleitet werden.

Es ist auch empfehlenswert, wenn die Spalten 1, 5, 9, 17, 21, 25, 29 und 33 von Paritätsbytes freigehalten werden.

10 Die Erfindung samt weiterer Vorteile ist im folgenden anhand beispielsweiser Ausführungsformen unter Bezugnahme auf die Zeichnung näher erläutert. In der Zeichnung zeigen

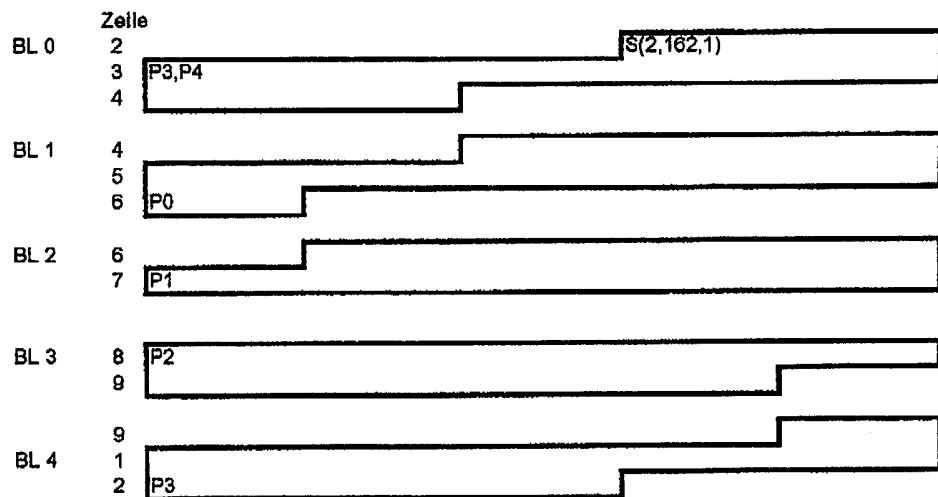

- Fig. 1 die Unterteilung eines STM-4-Rahmens in Codierungsblöcke,

- Fig. 2 die Belegung des Section Overhead mit Paritätsbytes bei einem Block-Code BCH (1944, 1922, 2),

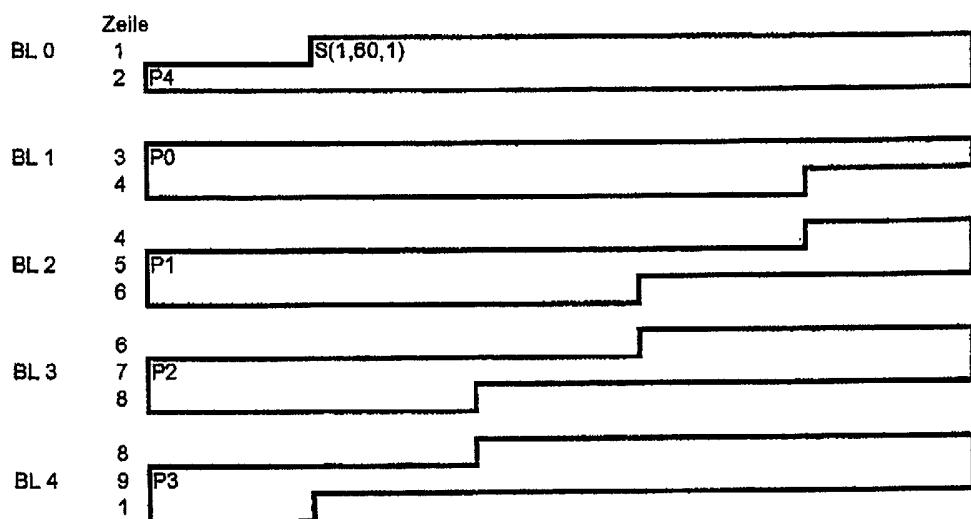

- Fig. 3 bei einer anderen Ausführungsform die Unterteilung des STM-4-Rahmens in Codierungsblöcke bei einer achtfach-Sicherung,

- Fig. 4 die Belegung des Section Overhead im Falle eines Codeblocks BCH (15552, 15440, 8),

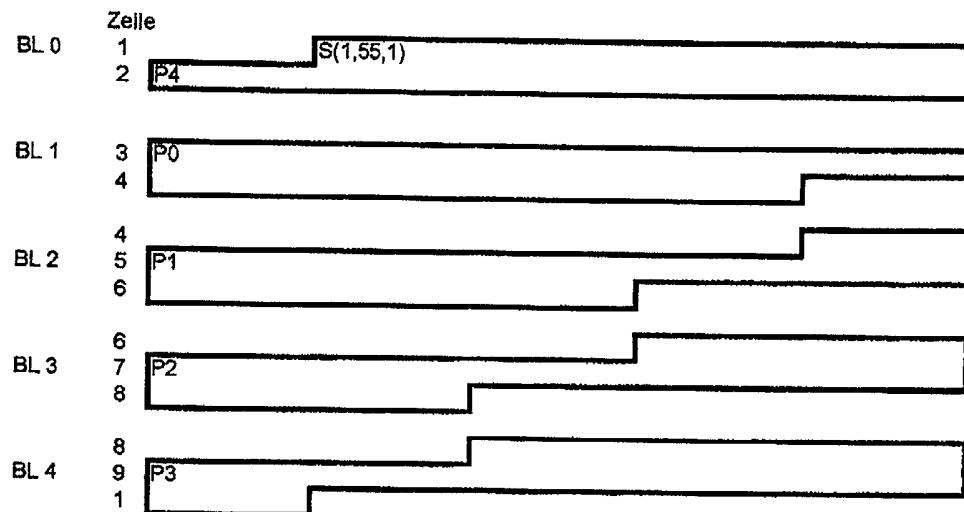

- Fig. 5 die Unterteilung eines STM-4-Rahmens in Codierungsblöcke bei einer zehnfach-Sicherung, und

- Fig. 6 die Belegung des Section Overhead mit Paritätsbytes bei einem Code BCH (15552, 15412, 10).

15 Der in Fig. 1 dargestellte Pulsrahmen entsteht aus einem STM-N oder OC3-N-Signal, durch byteweises Demultiplexen in STM-4-ähnliche Signale. Beispielsweise kann ein STM-16-Signal in vier derartige Pulsrahmen geteilt werden. Jeder Pulsrahmen wird dann in 40 Codierungs-Sub-Blöcke unterteilt, wobei die acht Bit eines STM-Bytes jeweils parallel bearbeitet - in acht „Spuren“ - werden, und pro Spur fünf Sub-Blöcke aufeinanderfolgen. Die Darstellung nach Fig. 1 geht von einem 1944, 1922, 2-BCH-Code aus, somit von einem zwei Fehler korrigierenden Code. In Fig. 1 sind die einzelnen Blöcke zur besseren Übersicht auseinandergezogen, und man sieht, daß jeder, 20 tatsächlich aus acht Subblöcken zusammengesetzte Codierungsblock aus insgesamt drei oder zwei Zeilen besteht. Die Darstellung ist ähnlich wie jene in der bereits eingangs erwähnten WO 98/49799. Die einzelnen Blöcke sind mit BL 0 bis BL 4 bezeichnet, und man sieht, daß bei dieser Ausführungsform der Erfindung der Block BL 2 mit dem Ende der siebenten Zeile endet, 25 wodurch ein Interleaving von Paritäts- und Informationsbytes vermieden wird, was vorteilhaft ist, da ein solches Interleaving eine Verzögerung der Informationsbytes in einem Coder nach sich ziehen würde.

30 BCH-Codes und ihre Implementierung sind beispielsweise beschrieben in: Lin, Shu/Costello, Daniel J., Error Controlling, Prentice Hall, 1983, oder in Rhee, Man Young, Error Correcting Theory, McGraw Hall, 1989.

35 Bei STM-N- bzw. OC-3N-Signalen besteht die Grundstruktur aus Rahmen oder Abschnitten mit einer Dauer von 125 µs, und jeder solcher Rahmen wird in neun Zeilen und 270\*N Spalten unterteilt. Zu Beginn jedes Rahmens ist ein Rahmenkennwort mit 6\*N bzw. 24 Byte zur Synchronisierung vorgesehen. Die Bedeutung der Bytes in den Overheads wird in den Normen angegeben, wobei einige dieser Bytes frei definierbar sind. Verwiesen wird hier auf die bereits erwähnte ITU-Recommendation G.708, jedoch auch auf die ITU-Recommendation G.707 (3/96). In diesen Empfehlungen sind auch die Bezeichnungen der einzelnen Bytes, wie später in Fig. 2 verwendet, angegeben. Bezüglich der Struktur von OC-3N-Signalen (SONET) sei verwiesen auf das Dokument ANSI T1.105-1995 des American National Standards Institute, Inc.

40 Die genannte Blockeinteilung bedingt eine Signalverzögerung von 55,7 µs, und es können, unabhängig von der Datensignalrate, Fehlerbursts mit einer maximalen Dauer von 25,7 ns korrigiert werden.

45 Für jede Spur eines Blocks werden 22 Paritätsbits benötigt, die im Section Overhead gemäß Fig. 2 untergebracht werden. Dabei sind die Positionen der normspezifischen Bytes B1, D1 bis 12, E1, E2, F1, K1, K2 und S1 nur im ersten STM-4-Teil belegt, falls beispielsweise ein STM-16-Signal vorliegt. Die Position von M1 befindet sich dann nur im dritten STM-4-Teil. Bei Anwendungen mit

STM-4-Signalen liegt das Byte MS-REI (Multiplex Section Remote Error Indication) an der Position M1' statt auf M1.

Wie sich aus den Darstellungen ergibt, werden Paritätsbytes in der zweiten, dritten, sechsten, siebten und achten Zeile des Overhead eingefügt, und je alle ersten, zweiten bis achten Bits jedes Bytes eines Codierungsblockes werden durch den Block-Code so gesichert, daß zwei Fehler korrigiert werden können. Dabei sind die jeweiligen Paritätsbytes  $P_i$  der entsprechenden Codierungsblöcke BLi auf die Zeilen des Rahmens aufgeteilt. Zumindest in einer Zeile, hier der Zeile Z 3, werden zusätzlich zu den Paritätsbytes P 4 eines Blockes BL 4 ein oder mehrere Paritätsbytes P 3 des hier vorgehenden Blockes BL 3 hinzugefügt. Prinzipiell könnten auch Paritätsbytes eines nachfolgenden Blockes hinzugefügt werden, doch ist es im Hinblick auf die Nutzung der vorhandenen Speicherressourcen zweckmäßiger, Paritätsbytes des vorgehenden Blockes zu verwenden.

Wenn im Rahmen der Erfindung von einer STM-4-Struktur gesprochen wird, so ist darauf hinzuweisen, daß diese STM-4-Struktur durch entsprechendes Demultiplexen von Rahmen höherer Ordnung, wie z.B. STM-16- oder STM-64-Rahmen entstehen kann. Da die Erfindung die starre, in der WO 98/49799 angegebene Struktur bezüglich der Einordnung der Blöcke in die Zeilen verläßt, ergibt sich eine höhere Flexibilität, und es können je nach den vorhandenen Möglichkeiten verfügbare Bytes genutzt werden. Es kann sich zwar die Notwendigkeit ergeben, geringfügig größere Verzögerungszeiten bei der Signalverarbeitung zu verwenden, doch fallen diese im Hinblick auf die erreichbare Flexibilität des Verfahrens nicht ins Gewicht.

Prinzipiell lassen sich Paritätsbytes zur Sicherung ökonomischer verwenden, wenn die Blöcke länger sind. Bei der Ausführung nach Fig. 3 und 4 der Erfindung geht man in ähnlicher Weise wie die WO 98/49799 von einem Verfahren zur Sicherung von Daten aus, wobei jedoch die Paritätsbytes  $P_i$  in der zweiten, dritten, fünften, siebten und neunten Zeile des Overheads eines Übertragungsrahmens mit einer STM-4-Struktur verwendet werden. Auch hier wird der Übertragungsrahmen in fünf gleich lange Codierungsblöcke eingeteilt, und alle Bits eines Codierungsblockes werden durch einen acht Fehler korrigierenden Block-Code gesichert. Es handelt sich um einen BCH-Code mit insgesamt 15 552 Bytes, wobei vierzehn Paritätsbytes je Codierungsblock vorgesehen sind. Der Code ist vom Typ BCH (15 552, 15 440, 8). Die Positionen von B1, D1 bis 12, E1, E2, F1, K1, K2 und S1 sind nur im ersten STM-4-Teil belegt, die Position von M1 nur im dritten STM-4-Teil. Bei Anwendungen mit STM-4-Signalen liegt MS-REI an der Position M1' statt M1.

Eine solche Blockeinteilung bedingt eine Signalverzögerung von 36,1  $\mu$ s, und es können, unabhängig von der Datensignalrate Fehlerbursts mit einer maximalen Dauer von 12,8 ns korrigiert werden. Insgesamt benötigt man 70 Paritätsbytes, d.h. 14 für jeden der fünf Blöcke, die gemäß Fig. 4 in dem Section Overhead untergebracht sind.

Bei einer Variante der Erfindung, die in den Fig. 5 und 6 veranschaulicht ist, wird ein zehnfach korrigierender BCH-Code des Typs BCH (15 552, 15 412, 10) verwendet, und auch hier wird wiederum ein STM-N bzw. OC-3N-Signal durch byteweises Demultiplexen in N/4 STM-4-ähnliche Signale aufgeteilt, und diese wiederum in fünf Codierungsblöcke unterteilt. Der Block BL 0 startet mit dem Byte S (1, 55, 1) des STM-4-Rahmens.

Bei dieser Blockeinteilung wird eine Signalverzögerung von 36,4  $\mu$ s benötigt, und es können bei STM-4-Signalen Fehlerbursts mit einer maximalen Dauer von 16 ns korrigiert werden, bei STM-64-Signalen hingegen beträgt die maximal korrigierbare Burst-Fehlerlänge 13 ns. Es werden 90 Paritätsbytes benötigt, und davon werden 5 Bytes nur zur Hälfte zur Unterbringung der Parität genutzt und gemäß Fig. 6 im Section Overhead untergebracht. Hier sind die Positionen von B1, D1 bis 12, E1, E2, F1, K1, K2 und S1 nur im ersten STM-4-Teil belegt, die Position von M1 nur im dritten STM-4-Teil. Bei Anwendungen mit STM-4-Signalen ist M1 mit dem 11.P 3 (Position S(9, 4, 3)) zu vertauschen.

Der Fachmann erkennt noch, daß die Spalten 1, 5, 9, 17, 21, 25, 29 und 33 von Paritätsbytes freigehalten werden, wobei die Ausführungen nach Fig. 1 bis 4 auch eine freie dreizehnte Spalte aufweisen.

Es ist weiters erwähnenswert, daß diejenigen Datenbytes (-bits) eines Codierungsabschnitts, deren Veränderung durch zwischen Codern und Decodern befindliche Geräte beabsichtigt ist, von der Korrektur ausgeschlossen werden, und im Coder wie im Decoder durch fixe Bitfolgen ersetzt werden, z.B. werden bei einem FEC-Verfahren (Forward Error Correction) über einen Multiplex-Abschnitt die Bytes des gesamten RSOH (Regenerator Section Overhead) oder zumindest deren

von einem Regenerator veränderbaren Anteile ausgeschlossen. Beispielsweise gehört das Rahmenwort zum RSOH, doch es wird von jedem Regenerator ident eingesetzt.

5

### PATENTANSPRÜCHE:

1. Verfahren zur gesicherten Datenübertragung in synchronen Übertragungssystemen, bei welchem die Daten in Übertragungsrahmen mit einem Overhead und einer Payload und einer neunzeiligen Struktur übertragen werden, und bei welchen Paritätsbytes in der zweiten, dritten, sechsten, siebenten und achten Zeile des Overhead eingefügt werden, der Übertragungsrahmen in fünf gleich lange Codierungsblöcke geteilt wird, und je alle ersten, zweiten bis achten Bits der zu sichernden Bytes eines Codierungsblocks durch einen zwei Fehler korrigierenden Block-Code gesichert werden, dessen Kontrollinformation dem Overhead eingefügt wird,

**dadurch gekennzeichnet, dass**

die jeweiligen Paritätsbytes der zugehörigen Codierungsblöcke auf die Zeilen des Rahmens aufgeteilt werden und zumindest in einer Zeile (Z 3) zusätzlich zu den Paritätsbytes (P 4) eines Blockes ein oder mehrere Paritätsbytes (P 3) des vorgehenden und/oder nachfolgenden Blockes (BL 3) hinzugefügt werden.

2. Verfahren nach Anspruch 1, **dadurch gekennzeichnet, dass** zu den Paritätsbytes (P 4) eines Blockes Paritätsbytes (P 3) des vorgehenden Blockes (BL 3) hinzugefügt werden.

3. Verfahren nach Anspruch 1 oder 2, **dadurch gekennzeichnet, dass** ein Codierungsblock (BL 2) mit dem Ende der siebenten Zeile endet.

4. Verfahren nach einem der Ansprüche 1 bis 3, **dadurch gekennzeichnet, dass** der Block-Code zur Sicherung der jeweils ersten, zweiten bis achten Bits des zu sichernden Bytes eines Codierungsblocks ein BCH-Code mit 1944 Bits, davon 1922 Datenbits und 22 Paritätsbits ist.

5. Verfahren zur gesicherten Datenübertragung in synchronen Übertragungssystemen, bei welchem die Daten in Übertragungsrahmen mit einem Overhead und einer Payload und einer neunzeiligen Struktur übertragen wurden, und bei welchem Paritätsbytes in den Overhead eingefügt werden sowie der Übertragungsrahmen in fünf gleich lange Codierungsblöcke geteilt wird,

**dadurch gekennzeichnet, dass**

alle Bits eines Codierungsblocks durch einen mindestens acht Fehler korrigierenden Blockcode gesichert werden.

6. Verfahren nach Anspruch 5, **dadurch gekennzeichnet, dass** die Paritätsbytes in der zweiten, dritten, fünften, siebenten und neunten Zeile des Overheads eingefügt werden.

7. Verfahren nach Anspruch 5 oder 6, **dadurch gekennzeichnet, dass** ein zehn Fehler korrigierender Block-Code verwendet wird.

8. Verfahren nach einem der Ansprüche 5 bis 7, **dadurch gekennzeichnet, dass** jeweils sämtliche Paritätsbytes eines Codierungsblocks in einer Zeile des Pulsrahmens angeordnet sind.

9. Verfahren nach einem der Ansprüche 1 bis 8, **dadurch gekennzeichnet, dass** das synchrone Übertragungssystem STM-N- bzw. OC-3N-Signale verwendet.

10. Verfahren nach Anspruch 9, **dadurch gekennzeichnet, dass** N ein ganzzahliges Vielfaches von vier ist.

11. Verfahren nach einem der Ansprüche 1 bis 10, **dadurch gekennzeichnet, dass** die zur Einteilung der Codierungsblöcke verwendeten Übertragungsrahmen durch byte-weises Demultiplexen aus Rahmen höherer Ordnung abgeleitet werden.

12. Verfahren nach einem der Ansprüche 1 bis 11, **dadurch gekennzeichnet, dass** die Spalten 1, 5, 9, 17, 21, 25, 29 und 33 von Paritätsbytes freigehalten werden.

### HIEZU 3 BLATT ZEICHNUNGEN

55

Fig. 1

Zelle

|   |             |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |   |

|---|-------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|---|

| 1 | A1          | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A2  | A2 | J0 | Z0 | Z0 | Z0 | X  | X  | X  | X  | X  | X |

| 2 | B1          | P3 | E1 | P3 | F1  | X  | X  | X  | X  | X  | X  | X  | X  | X  | X  |   |

| 3 | D1          | P3 | P4 | P4 | P4 | D2 | P4 | D3  | P4 |   |

| 4 | AU pointers |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |   |

| 5 | B2          | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | K1 |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |   |

| 6 | D4          | P0 | D5 | P0 | D6  | P0 | P0 | P0 | P0 | P0 | P0 |    |    |    |    |   |

| 7 | D7          | P1 | D8 | P1 | D9  | P1 | P1 | P1 | P1 | P1 | P1 |    |    |    |    |   |

| 8 | P10         | P2 | B12 | P2 | P2 | P2 | P2 | P2 | P2 |    |    |    |    |   |

| 9 | S1          |    |    |    |    |    |    |    |    | M1 | M1 |    |    |    |    |    |    |    |    |    |    | E2  | X  | X  | X  | X  | X  | X  | X  | X  | X  | X  |   |

p

a

y

l

o

a

d

Fig. 2

Fig. 3

Zeile

|             |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |   |   |   |   |  |  |  |  |

|-------------|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|--|--|--|--|

| 1           | A1  | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A1 | A2 | A2  | A2 | A2 | A2 | A2 | A2  | A2 | J0 | Z0 | Z0 | X  | X  | X  | X  | X  | X  | X |   |   |   |  |  |  |  |

| 2           | B1  | P4 | F1  | X  | X  | X  | X  | X   | X  | X  | X  | X  | X  | X  | X  | X  | X  | X  | X | X |   |   |  |  |  |  |

| 3           | D1  | P0 | D3  |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |   |   |   |   |  |  |  |  |

| AU pointers |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |   |   |   |   |  |  |  |  |

| 5           | B2  | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | B2 | K1 | P1 | P1 | P1 | P1  | P1 | P1 | P1 | K2 | P1  | P1 | P1 | P1 | P1 | P1 | P1 | P1 | P1 | P1 | P1 |   |   |   |   |  |  |  |  |

| 6           | D4  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | D5  |    |    |    |    | D6  |    |    |    |    |    |    |    |    |    |    |   |   |   |   |  |  |  |  |

| 7           | D7  | P2 | D8 | P2  | D9 |    |    |    |     |    |    |    |    |    |    |    |    |    |    |   |   |   |   |  |  |  |  |

| 8           | 0:0 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | D11 |    |    |    |    | D12 |    |    |    |    |    |    |    |    |    |    |   |   |   |   |  |  |  |  |

| 9           | S1  | P3 | M1 | P3 | M1 | P3 | P3 | P3 | P3 | E2  | X  | X  | X  | X  | X   | X  | X  | X  | X  | X  | X  | X  | X  | X  | X  | X | X | X | X |  |  |  |  |

p

a

y

i

o

a

d

Fig. 4

Fig. 5

Fig. 6