(19)**日本国特許庁(JP)**

# (12)**公開特許公報(A)**

(11)公開番号 特開2023-161036 (P2023-161036A)

(43)公開日 令和5年11月2日(2023.11.2)

FΤ (51)国際特許分類

H 0 1 L 6 1 6 S H 0 1 L 29/786 (2006.01) 29/78

H 0 1 L 29/78 6 1 8 B

#### 審査請求 有 請求項の数 1 OL (全27頁)

| (21)出願番号<br>(22)出願日<br>(62)分割の表示 | 特願2023-150027(P2023-150027)<br>令和5年9月15日(2023.9.15)<br>特願2021-178623(P2021-178623 | (71)出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

|----------------------------------|-----------------------------------------------------------------------------------|---------|------------------------------------------------|

| 原出願日<br>(31)優先権主張番号              | )の分割<br>平成22年11月5日(2010.11.5)<br>特願2009-260368(P2009-260368)                      | (72)発明者 | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会<br>社半導体エネルギー研究所内   |

| (32)優先日<br>(33)優先権主張国・±          | 平成21年11月13日(2009.11.13)<br>地域又は機関<br>日本国(JP)                                      | (72)発明者 | 小山 潤<br>神奈川県厚木市長谷398番地 株式会<br>社半導体エネルギー研究所内    |

|                                  |                                                                                   |         |                                                |

# (54)【発明の名称】 半導体装置

# (57)【要約】

【課題】良好な特性を備えた、新たな構造の半導体装置 を提供することを目的の一とする

【解決手段】酸化物半導体層と、酸化物半導体層と電気 的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレ イン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、ソース電極お よびドレイン電極は、その側面が

酸化された酸化領域を有する半導体装置である。なお、

ソース電極およびドレイン電極の

酸化領域は、300MHz以上300GHz以下の高周 波電力、および、酸素とアルゴン

の混合ガスを用いたプラズマ処理により形成されたもの であることが望ましい。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

酸化物半導体層と、

前記酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、前 記酸化物半導体層、前記ソース電極および前記ドレイン電極を覆う領域を有するゲート 絶縁層と、

前記ゲート絶縁層上のゲート電極と、を有し、

前記ソース電極および前記ドレイン電極は、その側面が酸化された酸化領域を有する、 半導体装置。

【発明の詳細な説明】

【技術分野】

[00001]

発明の技術分野は、半導体装置及びその作製方法に関する。ここで、半導体装置とは、半 導体特性を利用することで機能する素子および装置全般を指すものである。

#### 【背景技術】

[00002]

金属酸化物は多様に存在し、さまざまな用途に用いられている。酸化インジウムはよく知 られた材料であり、液晶表示装置などに必要とされる透明電極の材料として用いられてい

[0003]

金属酸化物の中には半導体特性を示すものがある。半導体特性を示す金属酸化物としては 、例えば、酸化タングステン、酸化錫、酸化インジウム、酸化亜鉛などがあり、このよう な金属酸化物をチャネル形成領域に用いた薄膜トランジスタが既に知られている(例えば 、特許文献 1 乃至特許文献 4 、非特許文献 1 等参照)。

[00004]

ところで、金属酸化物には、多元系酸化物も知られている。例えば、ホモロガス相を有す るInGaOq(ZnO)m(m:自然数)は、In、GaおよびZnを有する多元系酸 化物半導体として知られている(例えば、非特許文献2乃至非特許文献4等参照)。

[00005]

そして、上記のようなIn-Ga-Zn系酸化物で構成される酸化物半導体も、薄膜トラ ンジスタのチャネル形成領域に適用可能であることが確認されている(例えば、特許文献 5、非特許文献5および非特許文献6等参照)。

【先行技術文献】

【特許文献】

[0006]

【特許文献 1 】特開昭 6 0 - 1 9 8 8 6 1 号公報

【特許文献2】特開平8-264794号公報

【特許文献3】特表平11-505377号公報

【特許文献4】特開2000-150900号公報

【特許文献 5 】特開 2 0 0 4 - 1 0 3 9 5 7 号公報

【非特許文献】

[0007]

【非特許文献1】M. W. Prins, K. O. Grosse-Holz, G. Muller, J. F. M. Cillessen, J. B. Gies Wolf、 bers, R. P. Weening, and R. M. rroelectric transparent thin-film transi stor」、 Appl. Phys. Lett.、17 June 1996、 p. 3 6 5 0 - 3 6 5 2

【非特許文献 2】M. Nakamura, N. Kimizuka, and T. Mohri, The Phase Relations in the In20310

20

30

40

Ga2ZnO4-ZnO System at 1350 , J. Solid State Chem., 1991, Vol. 93, p. 298-315

【非特許文献 3】 N. Kimizuka, M. Isobe, and M. Nakamura、「Syntheses and Single-Crystal Data of Homologous Compounds, In 2 O 3 (ZnO) m (m = 3,4, and 5), In GaO 3 (ZnO) 3, and Ga2 O 3 (ZnO) m (m = 7,8,9, and 16) in the In 2 O 3-ZnGa2 O 4-ZnO System」、 J. Solid State Chem.、1995、Vol.116, p.170-178

【非特許文献4】中村真佐樹、君塚昇、毛利尚彦、磯部光正、「ホモロガス相、InFeO3(ZnO)m(m:自然数)とその同型化合物の合成および結晶構造」、固体物理、1993年、Vol.28、No.5、p.317-327

【非特許文献 5】 K. Nomura, H. Ohta, K. Ueda, T. Kamiya, M. Hirano, and H. Hosono、「Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor」、SCIENCE、2003、Vol.300、p.1269-1272

【非特許文献 6】 K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono、「Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors」、NATURE、2004、Vol.432 p.488-492

【発明の概要】

【発明が解決しようとする課題】

[0008]

ところで、現状の酸化物半導体を用いたトランジスタは、実用に十分な特性を有しているとは言い難く、S値やオンオフ比、信頼性などのトランジスタの諸特性に関して、より優れたものが求められている。

[0009]

そこで、開示する発明の一態様は、良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

[ 0 0 1 0 ]

または、新たな構造の半導体装置の作製方法を提供することを目的の一とする。

【課題を解決するための手段】

[0011]

発明の一態様である酸化物半導体を用いたトランジスタは、ソース電極またはドレイン電極の側面が酸化されたことにより、S値やオンオフ比、信頼性などにおいて優れた特性を示すものである。具体的には、例えば、次のような構成とすることができる。

[0012]

本発明の一態様は、酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、上記の酸化領域は、酸化物半導体層への酸素の供給と共に形成されるものである。

[0013]

上記において、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。また、ソース電極およびドレイン電極の上に、平面形状がソース電極およびドレイン電極と略同一の保護絶縁層を有することが望ましい。

10

20

30

なお、「略同一」の表現は、厳密に同一であることを要しない趣旨で用いるものであり、同一と見なすことができる範囲が含まる。例えば、一のエッチング処理によって形成される場合の差異は許容される。

#### [ 0 0 1 4 ]

また、上記において、酸化物半導体層の水素濃度は  $5 \times 10^{-19}$  /  $c \times m^3$  以下であることが望ましい。また、オフ電流は  $1 \times 10^{-13}$  A 以下であることが望ましい。

#### [0015]

本発明の一態様は、基板上に酸化物半導体層を形成し、酸化物半導体層と電気的に接続するソース電極およびドレイン電極を形成し、ソース電極およびドレイン電極の側面を酸化した後に、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層を形成し、ゲート絶縁層上にゲート電極を形成する、半導体装置の作製方法である。なお、ソース電極およびドレイン電極の側面を酸化する際に、酸化物半導体層への酸素の供給が行われる。

### [0016]

上記において、ソース電極およびドレイン電極の側面の酸化は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理によって行われることが望ましい。

#### [0017]

また、上記において、ソース電極およびドレイン電極上に、平面形状がソース電極および ドレイン電極と略同一の保護絶縁層を形成することが望ましい。

#### [0018]

また、上記において、酸化物半導体層の水素濃度を  $5 \times 10^{-19}$  / c m  $^3$  以下とすることにより、オフ電流を  $1 \times 10^{-13}$  A 以下とすることが望ましい。

#### [0019]

なお、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上の第1のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。また、「上」「下」の用語は説明の便宜のために用いる表現に過ぎず、特に言及する場合を除き、その上下を入れ替えたものも含む。

#### [0020]

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

#### [0021]

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や 、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため 、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることがで きるものとする。

#### [0022]

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

#### [0023]

例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

# 【発明の効果】

# [ 0 0 2 4 ]

開示する発明の一態様では、酸化物半導体層に酸素を供給することで、酸化物半導体を用

10

20

30

40

いたトランジスタの特性をさらに向上させている。ここで、当該酸素の供給処理は、酸化物半導体を用いたトランジスタにおいて、ソース電極またはドレイン電極の側面が酸化されるという形になって現れる。

[0025]

また、ソース電極またはドレイン電極の側面が酸化されることにより、ゲート絶縁層の薄膜化やカバレッジ不良などに起因して生じ得る、ゲート電極と、ソース電極またはドレイン電極のショートを防止することが可能である。

[0026]

このように、酸化物半導体層に酸素を供給することで、優れた特性を有する新たな構造の 半導体装置を実現することができる。

10

20

30

【図面の簡単な説明】

[0027]

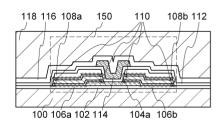

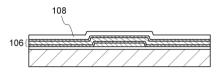

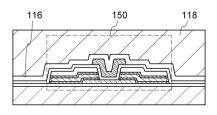

- 【図1】半導体装置を説明するための断面図である。

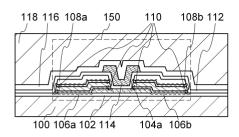

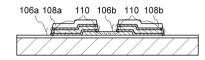

- 【図2】半導体装置の作製工程を説明するための断面図である。

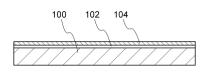

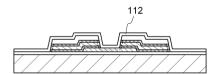

- 【図3】半導体装置の作製工程を説明するための断面図である。

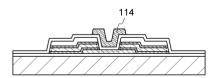

- 【図4】酸化物半導体を用いたトランジスタの断面図である。

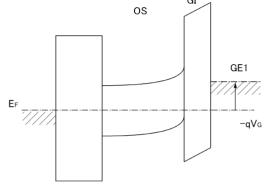

- 【図5】図4のA-A′断面におけるエネルギーバンド図(模式図)である。

- 【図 6 】(A)ゲート(G E 1)に正の電圧(V<sub>G</sub> > 0)が与えられた状態を示し、(B )ゲート(G E 1)に負の電圧(V<sub>G</sub> < 0)が与えられた状態示す図である。

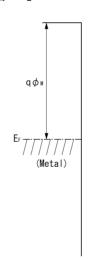

- 【図7】真空準位と金属の仕事関数(M)、酸化物半導体の電子親和力()の関係を示す図である。

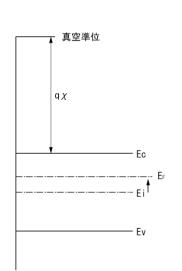

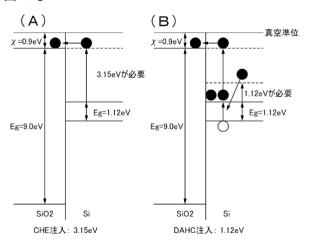

- 【図8】シリコン(Si)において、ホットキャリア注入に要するエネルギーを示す図である。

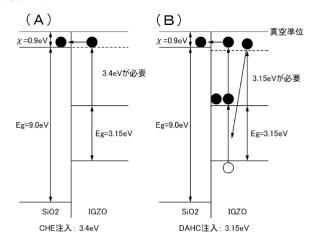

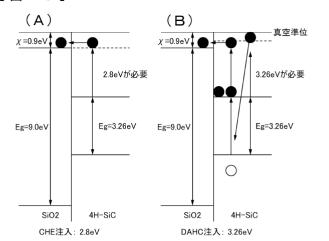

- 【図9】In-Ga-Zn-O系の酸化物半導体(IGZO)において、ホットキャリア 注入に要するエネルギーを示す図である。

- 【図 1 0 】炭化シリコン(4 H S i C ) において、ホットキャリア注入に要するエネルギーを示す図である。

- 【図11】短チャネル効果に関するデバイスシミュレーションの結果を示す図である。

- 【図12】短チャネル効果に関するデバイスシミュレーションの結果を示す図である。

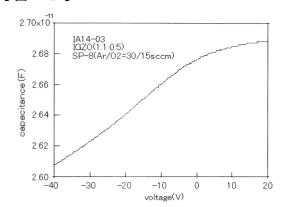

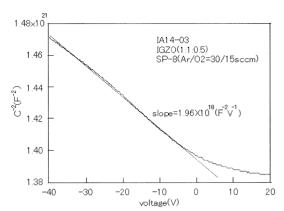

- 【図13】C-V特性を示す図である。

- 【図 1 4 】 V g と ( 1 / C ) <sup>2</sup> との関係を示す図である。

- 【図15】半導体装置を用いた電子機器を説明するための図である。

- 【図16】プラズマ処理によって形成される酸化領域の厚みと処理時間との関係を示す図である。

- 【発明を実施するための形態】

- [0028]

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

40

[0029]

また、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

[0030]

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

[0031]

(実施の形態1)

本実施の形態では、開示する発明の一態様に係る半導体装置の構成および作製方法につい

て、図1乃至図3を参照して説明する。

#### [0032]

<半導体装置の構成>

図 1 は、半導体装置の構成の一例であるトランジスタ 1 5 0 を示す断面図である。なお、トランジスタ 1 5 0 は、 n 型トランジスタとして説明するが、 p 型トランジスタを採用しても良い。

#### [0033]

トランジスタ150は、基板100上に絶縁層102を介して設けられた酸化物半導体層104aと、酸化物半導体層104aと電気的に接続するソース電極またはドレイン電極106a、ソース電極またはドレイン電極106bと、ソース電極またはドレイン電極106bを覆うゲート絶縁層112と、ゲート絶縁層112上のゲート電極114と、を有する(図1参照)。

#### [0034]

また、トランジスタ 1 5 0 上には、層間絶縁層 1 1 6 および層間絶縁層 1 1 8 が設けられている。

#### [0035]

ここで、ソース電極またはドレイン電極106a、ソース電極またはドレイン電極106 bは、それぞれ、その側面が酸化された酸化領域110を有する。当該酸化領域110を 有することにより、ゲート絶縁層の薄膜化やカバレッジ不良などに起因して生じ得る、ゲート電極と、ソース電極またはドレイン電極のショートを防止することが可能である。

#### [0036]

また、酸化物半導体層104aは、水素などの不純物が十分に除去され、酸素が供給されることにより高純度化されたものであることが望ましい。具体的には、酸化物半導体層104aの水素濃度は5×10<sup>19</sup>/сm³以下、望ましくは5×10<sup>18</sup>/сm³以下、より望ましくは5×10<sup>17</sup>/сm³以下とする。なお、水素濃度が十分に低減され、酸素が供給されることにより高純度化された酸化物半導体層104aでは、一般的なシリコンウェハ(リンやボロンなどの不純物元素が微量に添加されたシリコンウェハ)におけるキャリア濃度(1×10<sup>14</sup>/сm³程度)と比較して、十分に小さいキャリア濃度の値(例えば、1×10<sup>12</sup>/сm³未満、望ましくは、1×10<sup>11</sup>/сm³以下)をとる。このように、i型化または実質的にi型化された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタ150を得ることができる。例えば、ドレイン電圧Vdが+1Vまたは+10Vの場合であって、ゲート電圧Vgが-5Vから-20Vの範囲では、オフ電流は1×10・<sup>13</sup>A以下である。なお、上述の酸化物半導体層104a中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectroscopy)で測定したものである。

# [0037]

なお、酸化物半導体層を構成する酸化物半導体は、非単結晶構造であれば特に限定されない。例えば、非晶質構造、微結晶(マイクロクリスタル、ナノクリスタルなど)構造、多結晶構造、非晶質中に微結晶や多結晶が含まれる構造、非晶質構造の表面に微結晶や多結晶が形成された構造など、各種構造を適用することができる。

# [ 0 0 3 8 ]

<半導体装置の作製方法>

次に、トランジスタ150の作製方法について図2および図3を参照して説明する。

#### [0039]

まず、基板100上に、絶縁層102を成膜する。そして、絶縁層102上に酸化物半導体層104を成膜する(図2(A)参照)。

#### [0040]

基板100は、絶縁表面を有する基板であればよく、例えば、ガラス基板とすることができる。ガラス基板は無アルカリガラス基板であることが好ましい。無アルカリガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケ

10

20

30

40

20

30

40

50

イ酸ガラス等のガラス材料が用いられる。他にも、基板 1 0 0 として、セラミック基板、石英基板、サファイア基板等の絶縁体でなる絶縁性基板、シリコン等の半導体材料でなる半導体基板の表面を絶縁材料で被覆したもの、金属やステンレス等の導電体でなる導電性基板の表面を絶縁材料で被覆したものを用いることができる。また、作製工程の熱処理に耐えられることを条件に、プラスチック基板を用いることもできる。

#### [0041]

絶縁層102は下地として機能するものであり、CVD法やスパッタリング法等を用いて成膜することができる。また、絶縁層102は、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどを含むように形成するのが好適である。なお、絶縁層102は、単層構造としても良いし、積層構造としても良い。絶縁層102の厚さは特に限定されないが、例えば、10nm以上500nm以下とすることができる。ここで、絶縁層102は必須の構成要素ではないから、絶縁層102を設けない構成とすることも可能である。

#### [0042]

なお、絶縁層102に水素や水などが含まれると、水素の酸化物半導体層への侵入や、水素による酸化物半導体層中の酸素の引き抜きなどが生じ、トランジスタの特性が悪化するおそれがある。よって、絶縁層102は、できるだけ水素や水を含まないように成膜することが望ましい。

### [0043]

例えば、スパッタリング法などを用いる場合には、処理室内の残留水分を除去した状態で絶縁層102を成膜することが望ましい。また、処理室内の残留水分を除去するためには、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどの、吸着型の真空ポンプを用いることが望ましい。ターボポンプにコールドトラップを加えたものを用いてもよい。クライオポンプなどを用いて排気した処理室は、水素や水などが十分に除去されているため、絶縁層102に含まれる不純物の濃度を低減することができる。

### [0044]

また、絶縁層102を成膜する際には、水素や水などの不純物が、濃度ppm程度(望ましくは、濃度ppb程度)にまで低減された高純度ガスを用いることが望ましい。

#### [0045]

# [0046]

### [0047]

本実施の形態では、酸化物半導体層104としてIn-Ga-Zn-O系の酸化物半導体 成膜用ターゲットを用いて、非晶質の酸化物半導体層をスパッタ法により成膜することとする。なお、非晶質の酸化物半導体層中にシリコンを添加することで、その結晶化を抑制することができるから、例えば、SiO₂を2重量%以上10重量%以下含むターゲットを用いて酸化物半導体層104を形成しても良い。

#### [0048]

酸化物半導体層104をスパッタリング法で成膜するためのターゲットとしては、例えば、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、In、Ga、およびZnを含む酸化物半導体成膜用ターゲット(組成比として、In203:Ga203:Znol:1:1[mol比]、または、In:Ga:Zn=1:1:0.5[atom比])などを用いることもできる。また、In、Ga、およびZnを含む酸化物半導体成膜用ターゲットとして、In:Ga:Zn=1:1:1[atom比]、またはIn:Ga:Zn=1:1:1[atom比]、またはIn:Ga:Zn=1:1:2[atom比]の組成比を有するターゲットなどを用いても良い。酸化物半導体成膜用ターゲットの充填率は90%以上100%以下、好ましくは95%以上(例えば99.9%)である。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、緻密な酸化物半導体層104が成膜される。

[0049]

酸化物半導体層104の成膜雰囲気は、希ガス(代表的にはアルゴン)雰囲気、酸素雰囲気、または、希ガス(代表的にはアルゴン)と酸素との混合雰囲気とするのが好適である。具体的には、例えば、水素、水、水酸基、水素化物などの不純物が、濃度ppm程度(望ましくは濃度ppb程度)にまで除去された高純度ガス雰囲気を用いるのが好適である

#### [0050]

酸化物半導体層104の成膜の際には、減圧状態に保持された処理室内に基板を保持し、基板温度を100 以上600 以下好ましくは200 以上400 以下に熱する。そして、処理室内の残留水分を除去しつつ水素および水が除去されたスパッタガスを導入し、金属酸化物をターゲットとして酸化物半導体層104を成膜する。基板を熱しながら酸化物半導体層104を成膜することにより、酸化物半導体層104に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどを用いることができる。また、ターボポンプにコールドトラップを加えたものを用いてもよい。クライオポンプを用いて排気した処理室は、水素や水などが除去されており、酸化物半導体層104中の不純物濃度を低減できる。

[0051]

酸化物半導体層104の成膜条件としては、例えば、基板とターゲットとの距離が100mm、圧力が0.6Pa、直流(DC)電力が0.5kW、雰囲気が酸素(酸素流量比率100%)雰囲気、といった条件を適用することができる。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も均一となるため好ましい。酸化物半導体層104の厚さは、2nm以上200nm以下、好ましくは5nm以上30nm以下とする。ただし、適用する酸化物半導体材料や用途などにより適切な厚さは異なるから、その厚さは、用いる材料や用途などに応じて選択すればよい。

[0052]

なお、酸化物半導体層104をスパッタ法により成膜する前には、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁層102の表面の付着物を除去するのが好適である。ここで、逆スパッタとは、通常のスパッタにおいては、スパッタターゲットにイオンを衝突させるところ、逆に、処理表面にイオンを衝突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突させる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、基板付近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などによる雰囲気を適用してもよい。

# [0053]

次に、マスクを用いたエッチングなどの方法によって酸化物半導体層104を加工して、 島状の酸化物半導体層104aを形成する(図2(B)参照)。 10

20

30

50

20

30

40

50

#### [0054]

酸化物半導体層 1 0 4 のエッチングには、ドライエッチング、ウェットエッチングのいずれを用いても良い。もちろん、その両方を組み合わせて用いることもできる。酸化物半導体層 1 0 4 を所望の形状にエッチングできるよう、材料に合わせてエッチング条件(エッチングガスやエッチング液、エッチング時間、温度等)は適宜設定する。

#### [0055]

ドライエッチングとしては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法などを用いることができる。この場合にも、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)は適宜設定する必要がある。

#### [0056]

### [0057]

ウェットエッチングに用いることができるエッチング液としては、燐酸と酢酸と硝酸を混ぜた溶液、アンモニア - 過酸化水素水混合液(3 1 重量%過酸化水素水: 2 8 重量%アンモニア水:水 = 5 : 2 : 2 ) などがある。また、ITOO7N(関東化学社製)などのエッチング液を用いてもよい。

#### [0058]

その後、酸化物半導体層104aに対して、第1の熱処理を行うことが望ましい。この第1の熱処理によって酸化物半導体層104a中の水(水酸基を含む)や水素などを除去することができる。第1の熱処理の温度は、300 以上750 以下、好ましくは400以上700 以下とする。例えば、抵抗発熱体などを用いた電気炉に基板100を導入し、酸化物半導体層104aに対して窒素雰囲気下450 において1時間の熱処理を行う。この間、酸化物半導体層104aは大気に触れさせず、水や水素の混入が行われないようにする。

#### [0059]

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置であっても良い。例えば、GRTA(Gas Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。気体としては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。

### [0060]

例えば、第1の熱処理として、650 以上700 以下の高温に熱した不活性ガス雰囲気中に基板を投入し、数分間熱した後、当該不活性ガス雰囲気から基板を取り出すGRTA処理を行ってもよい。GRTA処理を用いると短時間での高温熱処理が可能となる。また、短時間の熱処理であるため、基板の耐熱温度を超える温度条件であっても適用が可能となる。例えば、ガラス基板を用いる場合、耐熱温度(歪み点)を超える温度では基板のシュリンクが問題となるが、短時間の熱処理の場合にはこれは問題とならない。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。酸素を含む雰囲気において

第1の熱処理を行うことで、酸素欠損に起因する欠陥を低減することができるためである

#### [0061]

なお、不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.999%)以上、好ましくは7N(99.9999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とする。

# [0062]

第1の熱処理の条件、または酸化物半導体層を構成する材料によっては、酸化物半導体層が結晶化し、微結晶または多結晶となる場合もある。例えば、結晶化率が90%以上、または80%以上の微結晶の酸化物半導体層となる場合もある。また、第1の熱処理の条件、または酸化物半導体層を構成する材料によっては、結晶成分を含まない非晶質の酸化物半導体層となる場合もある。

#### [0063]

また、非晶質の酸化物半導体(例えば、酸化物半導体層の表面)に微結晶(粒径1 n m 以上2 0 n m 以下(代表的には2 n m 以上4 n m 以下))が混在する酸化物半導体層となる場合もある。このように、非晶質中に微結晶を混在させ、配列させることで、酸化物半導体層の電気的特性を変化させることも可能である。

#### [0064]

例えば、In-Ga-Zn-O系の酸化物半導体成膜用ターゲットを用いて酸化物半導体層を形成する場合には、電気的異方性を有するIn₂Ga₂ZnOァの結晶粒が配向した微結晶領域を形成することで、酸化物半導体層の電気的特性を変化させることができる。上記微結晶領域は、例えば、In₂Ga₂ZnOァ結晶のc軸が酸化物半導体層の表面に垂直な方向をとるように配向した領域とするのが好適である。このように結晶粒を配向させた領域を形成することで、酸化物半導体層の表面に平行な方向の導電性を向上させ、酸化物半導体層の表面に垂直な方向の絶縁性を向上させることができる。また、このような微結晶領域は、酸化物半導体層中への水や水素などの不純物の侵入を抑制する機能を有する。

### [0065]

なお、上述の微結晶領域を有する酸化物半導体層は、 G R T A 処理による酸化物半導体層の表面加熱によって形成することができる。また、 Z n の含有量が I n または G a の含有量より小さいスパッタターゲットを用いることで、より好適に形成することが可能である

### [0066]

酸化物半導体層に対する第1の熱処理は、島状の酸化物半導体層104aに加工する前の酸化物半導体層104に行うこともできる。その場合には、第1の熱処理後に、加熱装置から基板100を取り出し、フォトリソグラフィエ程を行うことになる。

### [0067]

なお、上記第1の熱処理は、脱水化処理、脱水素化処理などと呼ぶこともできる。当該脱水化処理、脱水素化処理は、酸化物半導体層の形成後、酸化物半導体層104a上にソース電極またはドレイン電極を積層させた後、ソース電極またはドレイン電極上にゲート絶縁層を形成した後、などのタイミングにおいて行うことが可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

# [0068]

次に、酸化物半導体層104aに接するように導電層106を成膜した後、導電層106上に絶縁層108を形成する(図2(C)参照)。なお、絶縁層108は必須の構成要素ではないが、後に形成されるソース電極またはドレイン電極の側面を選択的に酸化させるためには有効である。

#### [0069]

20

10

30

40

導電層106は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形成することができる。また、導電層106は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素や、上述した元素を成分とする合金等を用いて形成することができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムのいずれか一または複数を含む材料を用いてもよい。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を一または複数含有させた材料を用いてもよい。

[0070]

また、導電層106は、導電性の金属酸化物を用いて成膜しても良い。導電性の金属酸化物としては、酸化インジウム(In<sub>2</sub>О<sub>3</sub>)、酸化スズ(SnO<sub>2</sub>)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In<sub>2</sub>О<sub>3</sub> SnO<sub>2</sub>、ITOと略記する場合がある)、酸化インジウム酸化亜鉛合金(In<sub>2</sub>О<sub>3</sub> ZnO)、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。

[ 0 0 7 1 ]

導電層106は、単層構造であっても良いし、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された 2層構造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。ここでは、チタン膜とアルミニウム膜とチタン膜の3層構造を適用することとする。

[0072]

なお、酸化物半導体層104aと導電層106との間には、酸化物導電層を成膜してもよい。酸化物導電層と導電層106は、連続して形成すること(連続成膜)が可能である。このような酸化物導電層を設けることで、ソース領域またはドレイン領域の低抵抗化を図ることができるため、トランジスタの高速動作が実現される。

[0073]

絶縁層108は、CVD法やスパッタリング法等を用いて成膜することができる。また、 絶縁層108は、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム 、酸化ハフニウム、酸化タンタルなどを含むように成膜するのが好適である。なお、絶縁 層108は、単層構造としても良いし、積層構造としても良い。絶縁層108の厚さは特 に限定されないが、例えば、10nm以上500nm以下とすることができる。

[0074]

次に、導電層106および絶縁層108を選択的にエッチングして、ソース電極またはドレイン電極106a、ソース電極またはドレイン電極106b、絶縁層108a、絶縁層108bを形成する。そして、酸化物半導体層104aに酸素を供給すべく酸化処理を行う。当該酸化処理によって、ソース電極またはドレイン電極106a、および、ソース電極またはドレイン電極106a、および、ソース電極またはドレイン電極106bの一部には酸化領域110が形成される(図2(D)参照)。また、点線で示すように、酸化物半導体層104a中には酸素が供給された領域が形成される。なお、上記酸素が供給された領域の範囲は、酸化物半導体層104aを構成する材料や、酸化処理の条件などによって様々に変化する。例えば、酸化物半導体層104aの下部界面にまで酸素を供給することも可能である。

[0075]

エッチングに用いるマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いるのが好適である。特に、チャネル長(L)が25nm未満の露光を行う場合には、数nm以上数10nm以下と極めて波長が短い超紫外線(Extreme Ultraviolet)を用いてマスク形成の露光を行うのが好適である。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長(L)を10nm以上1000nm以下とすることも可能である。このような方法でチャネル長(L)を小さくすることにより、動作速度を向上させることができる。また、上記酸化物半導体を用いたトランジスタはオフ電流が僅かであるため、微細化による消費電力の増大を抑制できる。

[0076]

10

20

30

20

30

40

導電層106のエッチングの際には、酸化物半導体層104aが除去されないように、それぞれの材料およびエッチング条件を適宜調節する。なお、材料およびエッチング条件によっては、当該工程において、酸化物半導体層104aの一部がエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。

#### [0077]

また、上記マスクの使用数や工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによってレジストマスクを形成し、これを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは、複数の厚みを有する形状(階段状)となり、アッシングによりさらに形状を変形させることができるため、複数のエッチング工程に用いることができる。つまり、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができるよって、露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が図れる。

### [0078]

酸化処理は、マイクロ波(300MHz以上300GHz以下)によって励起された酸素プラズマを用いた酸化処理(プラズマ酸化処理)とするのが好適である。マイクロ波によってプラズマを励起することで、高密度プラズマが実現され、酸化物半導体層104aへのダメージを十分に低減することができるからである。

#### [0079]

より具体的には、例えば、周波数を300MHz以上300GHz以下(代表的には2.45GHz)、圧力を50Pa以上5000Pa以下(代表的には500Pa)、基板温度を200 以上400 以下(代表的には300 )とし、酸素とアルゴンとの混合ガスを用いて上記処理を行うことができる。

# [0800]

上記酸化処理によって、酸化物半導体層104aに酸素が供給されることになるため、酸化物半導体層104aへのダメージを十分に低減しつつ、酸素欠損に起因する局在準位を減少させることができる。つまり、酸化物半導体層104aの特性を一層向上させることができる。

# [0081]

なお、酸化物半導体層 1 0 4 a へのダメージを十分に低減しつつ、酸化物半導体層 1 0 4 a に酸素を供給することができる方法であれば、マイクロ波を用いたプラズマ酸化処理に限定する必要は無い。例えば、酸素を含む雰囲気における熱処理などの方法を用いることもできる。

# [0082]

また、上記酸化処理と併せて、酸化物半導体層 1 0 4 a から水や水素などを除去する処理を行ってもよい。例えば、窒素やアルゴンなどのガスを用いたプラズマ処理を行うことができる。

### [0083]

なお、上記酸化処理によって、ソース電極またはドレイン電極106a、および、ソース電極またはドレイン電極106bの一部(特に、その側面に相当する部分)には酸化領域110が形成されることになる。この酸化領域110は、トランジスタ150が微細化されている場合(例えば、チャネル長が1000mm未満である場合)には、特に有効である。トランジスタの微細化に伴い、ゲート絶縁層に対してはその厚みを小さくすることが要求されるが、酸化領域110を有することで、ゲート絶縁層の薄膜化やカバレッジ不良などに起因して生じ得る、ゲート電極と、ソース電極またはドレイン電極のショートを防止できるためである。なお、当該酸化領域110は、5mm以上(好ましくは10mm以上)の厚みを有していれば、十分に効果的である。

# [0084]

また、上記酸化処理は、露出した絶縁層102の膜質改善の観点からも有効である。

#### [0085]

なお、ソース電極またはドレイン電極106aや、ソース電極またはドレイン電極106 bの上部の酸化を防止する役割を有する点で、絶縁層108aおよび絶縁層108bは重 要である。エッチングの際に用いたマスクを残存させたまま、上記プラズマ処理をするに は大きな困難が伴うからである。

#### [0086]

なお、図2(D)では、図2(C)に示す導電層106および絶縁層108を選択的にエッチングして、ソース電極またはドレイン電極106a、ソース電極またはドレイン電極106b、絶縁層108a、絶縁層108bを一度に形成する場合を例示しているが、開示する発明の一態様はこれに限定されない。

#### [ 0 0 8 7 ]

例えば、導電層106および絶縁層108の酸化物半導体層104aと重畳する領域のみを選択的にエッチングして、トランジスタのチャネル形成領域にまで達する開口を形成した後に、当該領域に対して上記プラズマ処理を行って、酸化物半導体層104aに酸素を供給し、また、導電層106の露出した部分を酸化し、その後、再度のエッチングによって、ソース電極またはドレイン電極106a、ソース電極またはドレイン電極106b、絶縁層108a、絶縁層108bを完成させても良い。このような工程を採用する場合には、目的とする部分にのみ酸化処理を適用することができるため、他の部分に対して、酸化処理に起因する悪影響を与えずに済むというメリットがある。

### [0088]

次に、大気に触れさせることなく、酸化物半導体層104aの一部に接するゲート絶縁層112を形成する(図3(A)参照)。ゲート絶縁層112は、CVD法やスパッタリング法等を用いて形成することができる。また、ゲート絶縁層112は、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどを含むように形成するのが好適である。なお、ゲート絶縁層112は、単層構造としても良いし、積層構造としても良い。ゲート絶縁層112の厚さは特に限定されないが、例えば、10nm以上500nm以下とすることができる。

### [0089]

なお、不純物を除去することなどによりi型化または実質的にi型化された酸化物半導体 (高純度化された酸化物半導体)は、界面準位や界面電荷に対して極めて敏感であるため 、ゲート絶縁層 1 1 2 には、高い品質が要求されることになる。

### [0090]

例えば、マイクロ波(例えば、2.45GHz)を用いた高密度プラズマCVD法は、緻密で絶縁耐圧の高い高品質なゲート絶縁層112を形成できる点で好適である。高純度化された酸化物半導体層と高品質なゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

# [0091]

もちろん、ゲート絶縁層112として良質な絶縁層を形成できるのであれば、スパッタリング法やプラズマCVD法など他の方法を適用することも可能である。また、形成後の熱処理によって、膜質や界面特性などが改質される絶縁層を適用しても良い。いずれにしても、ゲート絶縁層112としての膜質が良好であると共に、酸化物半導体層との界面準位密度を低減し、良好な界面を形成できるものを設ければよい。

#### [0092]

このようにゲート絶縁層との界面特性を良好にするとともに、酸化物半導体の不純物、特に水素や水などを排除することで、ゲートバイアス・熱ストレス試験(BT試験:例えば、85 、2×10<sup>6</sup> V/cm、12時間など)に対してしきい値電圧(Vth)が変動しない、安定なトランジスタを得ることが可能である。

#### [0093]

その後、不活性ガス雰囲気下、または酸素雰囲気下で第2の熱処理を行う。熱処理の温度は、200 以上400 以下、望ましくは250 以上350 以下である。例えば、窒素雰囲気下で250 、1時間の熱処理を行えばよい。第2の熱処理を行うと、トラン

10

20

30

40

ジスタの電気的特性のばらつきを軽減することができる。なお、本実施の形態では、ゲート絶縁層112の形成後に第2の熱処理を行っているが、第2の熱処理のタイミングは、第1の熱処理の後であれば特に限定されない。

#### [0094]

次に、ゲート絶縁層112上の酸化物半導体層104aと重畳する領域にゲート電極114を形成する(図3(B)参照)。ゲート電極114は、ゲート絶縁層112上に導電層を成膜した後に、当該導電層を選択的にパターニングすることによって形成することができる。

#### [0095]

上記導電層は、スパッタ法をはじめとする P V D 法や、プラズマ C V D 法などの C V D 法を用いて成膜することができる。また、導電層は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンからから選ばれた元素や、上述した元素を成分とする合金等を用いて成膜することができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムのいずれか一または複数を含む材料を用いてもよい。また、アルミニウムに、チタン、タンタル、タングステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素を一または複数含有させた材料を用いてもよい。

#### [0096]

また、導電層は、導電性の金属酸化物を用いて成膜しても良い。導電性の金属酸化物としては酸化インジウム(In2O3)、酸化スズ(SnO2)、酸化亜鉛(ZnO)、酸化インジウム酸化スズ合金(In2O3 SnO2、ITOと略記する場合がある)、酸化インジウム酸化亜鉛合金(In2O3 ZnO)、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。

#### [0097]

導電層は、単層構造であっても良いし、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された2層構造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。こでは、チタンを含む材料を用いて導電層を成膜し、ゲート電極114に加工する。

#### [0098]

次に、ゲート絶縁層112およびゲート電極114上に、層間絶縁層116および層間絶縁層118を成膜する(図3(C)参照)。層間絶縁層116および層間絶縁層118は、PVD法やCVD法などを用いて成膜することができる。また、酸化シリコン、窒化酸化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル等の無機絶縁材料を含む材料を用いて成膜することができる。なお、本実施の形態では、層間絶縁層118と層間絶縁層118の積層構造としているが、開示する発明の一態様はこれに限定されない。1層としても良いし、3層以上の積層構造としても良い。

# [0099]

なお、上記層間絶縁層118は、その表面が平坦になるように成膜することが望ましい。 表面が平坦になるように層間絶縁層118を形成することで、層間絶縁層118上に、電極や配線などを好適に形成することができるためである。

#### [ 0 1 0 0 ]

以上により、酸化物半導体を用いたトランジスタ150が完成する。

#### [ 0 1 0 1 ]

上述のような方法でトランジスタ150を作製した場合、酸化物半導体層104aの水素濃度は $5 \times 10^{19}$  /  $cm^3$  以下となり、また、トランジスタ150のオフ電流は1 $\times$ 10 $^{-13}$  A 以下となる。このように、水素濃度が十分に低減され、酸素が供給されることにより高純度化された酸化物半導体層104aを適用することで、優れた特性のトランジスタ150を得ることができる。なお、水素濃度を低減した直後に、酸素の供給を行う場合には、酸化物半導体層に水素や水などが混入するおそれがないため、極めて良好な特性の酸化物半導体層を実現することができるという点で好適である。もちろん、良好な特性の酸化物半導体層を実現できるのであれば、水素濃度の低減処理と、酸素の供給処理は、

10

20

30

30

20

30

40

50

連続的に行われる必要はない。例えば、これらの処理の間に別の処理を含んでいても良い。また、これらの処理を、同時に行っても良い。

#### [0102]

また、本実施の形態では、酸化物半導体層104aに酸素を供給すべく、酸化物半導体層104aに酸素プラズマ処理を施している。このため、トランジスタ150の特性はさらに高いものとなる。また、ソース電極またはドレイン電極の側面に相当する領域が酸化されることになるため、ゲート絶縁層の薄膜化に起因して生じるおそれのある、ゲート電極・ソース電極(またはドレイン電極)間の短絡を防止することができる。

#### [0103]

なお、酸化物半導体において、物性研究は多くなされているが、これらの研究は、局在準位そのものを十分に減らすという思想を含まない。開示する発明の一態様では、局在準位の原因になり得る水や水素を酸化物半導体中より除去することで、高純度化した酸化物半導体を作製する。これは、局在準位そのものを十分に減らすという思想に立脚するものである。そして、これによって極めて優れた工業製品の製造を可能とするものである。

#### [0104]

なお、水素や水などを除去する際には、同時に酸素が除去されてしまうことがある。このため、酸素欠乏により発生する金属の未結合手に対して酸素を供給し、酸素欠陥による局在準位を減少させることにより、酸化物半導体をさらに高純度化(i型化)するのは好適である。たとえば、チャネル形成領域に密接して酸素過剰の酸化膜を形成し、200以上400以下、代表的には250程度の温度条件での熱処理を行うことで、当該酸化膜から酸素を供給して、酸素欠陥による局在準位を減少させることが可能である。また、第2の熱処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。第2の熱処理に続けて、酸素雰囲気、または水素や水を十分に除去した雰囲気における降温過程を経ることで、酸化物半導体中に酸素を供給することも可能である。

#### [ 0 1 0 5 ]

酸化物半導体の特性を悪化させる要因は、過剰な水素による伝導帯下 0 . 1 e V 以上 0 . 2 e V 以下の浅い準位や、酸素欠損による深い準位、などに起因するものと考えられる。 これらの欠陥を無くすために、水素を徹底的に除去し、酸素を十分に供給するという技術 思想は正しいものであろう。

#### [0106]

なお、酸化物半導体は一般にn型とされているが、開示する発明の一態様では、水や水素などの不純物を除去すると共に、酸化物半導体の構成元素である酸素を供給することでi型化を実現する。この点、シリコンなどのように不純物を添加してのi型化ではなく、従来にない技術思想を含むものといえる。

### [0107]

<酸化物半導体を用いたトランジスタの電導機構>

ここで、酸化物半導体を用いたトランジスタの電導機構につき、図 4 乃至図 7 を用いて説明する。なお、以下の説明では、理解の容易のため理想的な状況を仮定しており、そのすべてが現実の様子を反映しているとは限らない。また、以下の説明はあくまでも一考察に過ぎず、発明の有効性に影響を与えるものではないことを付記する。

# [0108]

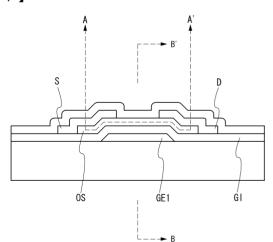

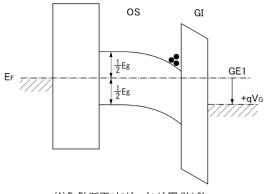

図4は、酸化物半導体を用いたトランジスタ(薄膜トランジスタ)の断面図である。ゲート電極(GE1)上にゲート絶縁層(GI)を介して酸化物半導体層(OS)が設けられ、その上にソース電極(S)およびドレイン電極(D)が設けられ、ソース電極(S)およびドレイン電極(D)を覆うように絶縁層が設けられている。

### [0109]

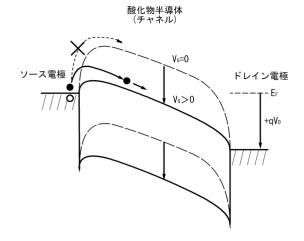

図 5 には、図 4 の A - A '断面におけるエネルギーバンド図(模式図)を示す。また、図 5 中の黒丸( )は電子を示し、白丸( )は正孔を示し、それぞれは電荷(  $- q \times + q$ )を有している。ドレイン電極に正の電圧( $V_D > 0$ )を印加した上で、破線はゲート電極に電圧を印加しない場合( $V_G = 0$ )、実線はゲート電極に正の電圧( $V_G > 0$ )を印

加する場合を示す。ゲート電極に電圧を印加しない場合は高いポテンシャル障壁のために電極から酸化物半導体側へキャリア(電子)が注入されず、電流を流さないオフ状態を示す。一方、ゲートに正の電圧を印加するとポテンシャル障壁が低下し、電流を流すオン状態を示す。

[0110]

図6には、図4におけるB-B'の断面におけるエネルギーバンド図(模式図)を示す。図6(A)は、ゲート電極(GE1)に正の電圧(V $_{G}>0$ )が与えられた状態であり、ソース電極とドレイン電極との間にキャリア(電子)が流れるオン状態を示している。また、図6(B)は、ゲート電極(GE1)に負の電圧(V $_{G}<0$ )が印加された状態であり、オフ状態(少数キャリアは流れない状態)である場合を示す。

[0111]

図 7 は、真空準位と金属の仕事関数 (M)、酸化物半導体の電子親和力 ()の関係を示す。

[0112]

常温において金属中の電子は縮退しており、フェルミ準位は伝導帯内に位置する。一方、従来の酸化物半導体は n 型であり、そのフェルミ準位(E<sub>F</sub>)は、バンドギャップ中央に位置する真性フェルミ準位(E<sub>i</sub>)から離れて、伝導帯寄りに位置している。なお、酸化物半導体において水素の一部はドナーとなり n 型化する要因の一つであることが知られている。

[0113]

これに対して開示する発明の一態様に係る酸化物半導体は、n型化の要因である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の元素(不純物元素)が極力含まれないように高純度化することにより真性(i型)とし、または真性とせんとしたものである。すなわち、不純物元素を添加してi型化するのではなく、水素や水等の不純物を極力除去することにより、高純度化されたi型(真性半導体)またはそれに近づけることを特徴としている。これにより、フェルミ準位(EF)は真性フェルミ準位(Ei)と同程度とすることができる。

[0114]

酸化物半導体のバンドギャップ(Eg)は3.15eVで、電子親和力()は4.3Vと言われている。ソース電極およびドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体の電子親和力()とほぼ等しい。この場合、金属・酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

[0115]

このとき電子は、図 6 ( A ) で示すように、ゲート絶縁層と高純度化された酸化物半導体 との界面付近(酸化物半導体のエネルギー的に安定な最低部)を移動する。

[0116]

また、図 6 ( B ) に示すように、ゲート電極( G E 1 ) に負の電位が与えられると、少数 キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

[0117]

このように、酸化物半導体の主成分以外の元素(不純物元素)が極力含まれないように高純度化することにより、真性(i型)とし、または実質的に真性となるため、ゲート絶縁層との界面特性が顕在化する。そのため、ゲート絶縁層には、酸化物半導体と良好な界面を形成できるものが要求される。具体的には、例えば、VHF帯~マイクロ波帯の電源周波数で生成される高密度プラズマを用いたCVD法で作製される絶縁層や、スパッタリング法で作製される絶縁層などを用いることが好ましい。

[0118]

10

20

30

40

#### [0119]

このように、酸化物半導体の主成分以外の元素(不純物元素)が極力含まれないように高 純度化することにより、トランジスタの動作を良好なものとすることができる。

#### [ 0 1 2 0 ]

< 酸化物半導体を用いたトランジスタのホットキャリア劣化耐性 >

次に、酸化物半導体を用いたトランジスタのホットキャリア劣化耐性につき、図 8 乃至図 1 0 を用いて説明する。なお、以下の説明では、理解の容易のため理想的な状況を仮定しており、そのすべてが現実の様子を反映しているとは限らない。また、以下の説明はあくまでも一考察に過ぎないことを付記する。

#### [ 0 1 2 1 ]

ホットキャリア劣化の主要因としては、チャネルホットエレクトロン注入(CHE注入) とドレインアバランシェホットキャリア注入(DAHC注入)がある。なお、以下では簡 単のため、電子のみを考慮する。

#### [0122]

CHE注入とは、半導体層中においてゲート絶縁層の障壁以上のエネルギーを有するようになった電子が、ゲート絶縁層などに注入される現象をいう。電子へのエネルギーの授与は、電子が低電界で加速される事で行われる。

#### [ 0 1 2 3 ]

DAHC注入とは、高電界により加速された電子の衝突によって生じる新たな電子がゲート絶縁層などに注入される現象を言う。 DAHC注入とCHE注入との相違は、衝突イオン化によるアバランシェ降伏を伴うか否かにある。なお、 DAHC注入では、半導体のバンドギャップ以上の運動エネルギーを持つ電子が必要となる。

#### [0124]

図8に、シリコン(Si)のバンド構造から見積もった各種ホットキャリア注入に要するエネルギーを示し、図9に、In-Ga-Zn-O系の酸化物半導体(IGZO)のバンド構造から見積もった各種ホットキャリア注入に要するエネルギーを示す。また、図8(A)および図9(A)はCHE注入を表し、図8(B)および図9(B)はDAHC注入を表す。

# [0125]

シリコンでは、 C H E 注入よりも D A H C 注入による劣化が深刻となる。これは、シリコン中において衝突せずに加速されるキャリア (例えば電子)はごく僅かであるのに対して、シリコンはバンドギャップが小さく、アバランシェ降伏が生じやすいことに起因している。アバランシェ降伏によりゲート絶縁層の障壁を越えられる電子の数は増加し、 C H E 注入の確率を容易に上回る。

### [0126]

In-Ga-Zn-O系の酸化物半導体では、CHE注入に必要なエネルギーはシリコンの場合と大きく異ならず、やはりその確率は低いものである。また、DAHC注入に必要なエネルギーは、バンドギャップの広さからCHE注入に必要なエネルギーと同程度となる。

#### [0127]

つまり、CHE注入とDAHC注入の確率はいずれも低く、シリコンと比較してホットキャリア劣化の耐性は高い。

#### [0128]

ところで、In-Ga-Zn-O系の酸化物半導体のバンドギャップは高耐圧材料として注目される炭化シリコン(SiC)と同程度である。図10に、4H-SiCについての各種ホットキャリア注入に必要なエネルギーを示す。また、図10(A)はCHE注入を表し、図10(B)はDAHC注入を表す。CHE注入に関しては、In-Ga-Zn-O系の酸化物半導体の方が若干そのしきいが高く、有利といえる。

#### [0129]

以上、In-Ga-Zn-O系の酸化物半導体はシリコンと比較してホットキャリア劣化

10

20

30

00

40

20

30

40

50

への耐性やソース・ドレイン破壊への耐性が非常に高いということが分かる。また、炭化シリコンと比較しても遜色のない耐圧が得られるといえる。

#### [0130]

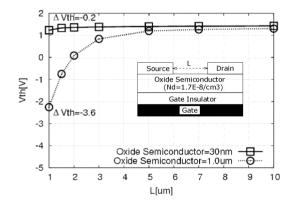

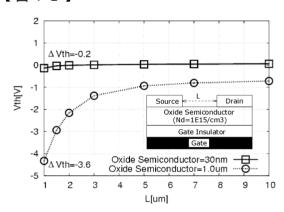

< 酸化物半導体を用いたトランジスタにおける短チャネル効果 >

次に、酸化物半導体を用いたトランジスタにおける短チャネル効果に関し、図 1 1 および図 1 2 を用いて説明する。なお、以下の説明では、理解の容易のため理想的な状況を仮定しており、そのすべてが現実の様子を反映しているとは限らない。また、以下の説明はあくまでも一考察に過ぎないことを付記する。

#### [ 0 1 3 1 ]

短チャネル効果とは、トランジスタの微細化(チャネル長(L)の縮小)に伴って顕在化する電気特性の劣化をいう。短チャネル効果は、ドレインの効果がソースにまでおよぶことに起因するものである。短チャネル効果の具体例としては、しきい値電圧の低下、S値の増大、漏れ電流の増大などがある。

### [0132]

ここでは、デバイスシミュレーションを用い、短チャネル効果を抑制することができる構造に関して検証した。具体的には、キャリア濃度および酸化物半導体層の厚さを異ならせた4種類のモデルを用意して、チャネル長(L)としきい値電圧(Vth)の関係を確認した。モデルとしては、ボトムゲート構造のトランジスタを採用し、酸化物半導体のキャリア濃度を1.7×10・8/cm³、または1.0×10<sup>15</sup>/cm³のいずれかとし、酸化物半導体層の厚さを1μm、または30nmのいずれかとした。なお、酸化物半導体としてIn・Ga・Zn・O系の酸化物半導体を用い、ゲート絶縁層として100nmの厚さの酸化窒化珪素膜を用いた。酸化物半導体のバンドギャップを3.15eV、電子親和力を4.3eV、比誘電率を15、電子移動度を10cm²/Vsと仮定した。酸化窒化珪素膜の比誘電率を4.0と仮定した。計算にはシルバコ社製デバイスシミュレーションソフト「Atlas」を使用した。

### [ 0 1 3 3 ]

なお、トップゲート構造とボトムゲート構造では、計算結果に大きな相違はない。

#### [0134]

計 算 結 果 を 図 1 1 お よ び 図 1 2 に 示 す 。 図 1 1 は 、 キ ャ リ ア 濃 度 が 1 . 7 × 1 0 <sup>- 8</sup> / c m<sup>3</sup>の場合、図12は、キャリア濃度が1.0×10<sup>15</sup>/cm<sup>3</sup>の場合である。図11 および図12には、チャネル長(L)が10μmのトランジスタを基準とし、チャネル長 (L)を $10\mu$ mから $1\mu$ mまで変化させたときのしきい値電圧(Vth)の変化量( Vth)を示している。図11に示すとおり、酸化物半導体のキャリア濃度が1.7x1 0 <sup>- 8</sup> / c m <sup>3</sup> であり、酸化物半導体層の厚さが 1 μ m の場合は、しきい値電圧の変化量 ( Vth)は-3.6 Vであった。また、図11に示すとおり、酸化物半導体のキャリ ア 濃 度 が 1 . 7 × 1 0 <sup>-8</sup> / c m <sup>3</sup> で あ り 、 酸 化 物 半 導 体 層 の 厚 さ が 3 0 n m の 場 合 は 、 しきい値電圧の変化量( Vth)は - 0 . 2 Vであった。また、図12に示すとおり、 酸化物半導体のキャリア濃度が1.0×10<sup>15</sup>/cm<sup>3</sup>であり、酸化物半導体層の厚さ が 1 μ m の 場合は、しきい値電圧の変化量( Vth)は - 3.6Vであった。また、図 1 2 に示すとおり、酸化物半導体のキャリア濃度が1.0 × 1 0 <sup>1 5</sup> / c m <sup>3</sup> であり、酸 化物半導体層の厚さが30nmの場合は、しきい値電圧の変化量( Vth)は-0.2 V であった。 当 該 結 果 は 、 酸 化 物 半 導 体 を 用 い た ト ラ ン ジ ス タ に お い て 、 酸 化 物 半 導 体 層 の厚さを小さくすることで、短チャネル効果を抑制できることを示すものといえる。例え ば、チャネル長(L)が 1 μ m 程度の場合、キャリア濃度が十分に大きい酸化物半導体層 であっても、その厚さを30nm程度とすれば、短チャネル効果を十分に抑制することが できることが理解される。

#### [0135]

<キャリア濃度>

開示する発明に係る技術思想は、酸化物半導体層におけるキャリア濃度を十分に小さくし、できるだけ真性(i型)に近づけようとするものである。以下、キャリア濃度の求め方

、および、実際に測定したキャリア濃度に関し、図13および図14を参照して説明する

#### [0136]

まず、キャリア濃度の求め方について簡単に説明する。キャリア濃度は、MOSキャパシタを作製し、MOSキャパシタのCV測定の結果(CV特性)を評価することで求めることが可能である。

#### [0137]

より具体的には、MOSキャパシタのゲート電圧Vgと容量Cとの関係をプロットしたC-V特性を取得し、当該C-V特性からゲート電圧Vgと(1/C) $^2$ との関係を表すグラフを取得し、当該グラフにおいて弱反転領域での(1/C) $^2$ の微分値を求め、当該微分値を式(1)に代入することによりキャリア濃度Ndの大きさが求められる。なお、式(1)において、eは電気素量、 $^0$ は真空の誘電率、 は酸化物半導体の比誘電率である。

[0138]

【数1】

$$N_d = -\left(\frac{2}{e\varepsilon_0\varepsilon}\right) / \frac{d(1/C)^2}{dV} \tag{1}$$

#### [0139]

[0140]

図 1 3 には C - V 特性を、図 1 4 には V g E ( 1 / E ) E との関係を、それぞれ示す。図 1 4 の弱反転領域における( 1 / E ) E の微分値から式( 1 ) を用いて得られたキャリア 濃度は、 E 6 . E 0 × 1 0 E 0 / E 0 E 0 E 0 E 0 × 1 0 E 0 × 1 0 E 0 / E 0 E 0 × 1 0 E 0 × 1 0 E 0 / E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0 × 1 0 E 0

### [0141]

このように、 i 型化または実質的に i 型化された酸化物半導体(例えば、キャリア濃度が  $1 \times 10^{-12}$  / c m  $^3$  未満、望ましくは、  $1 \times 10^{-11}$  / c m  $^3$  以下)を用いることで、極めて優れたオフ電流特性のトランジスタを得ることが可能である。

### [0142]

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

[0143]

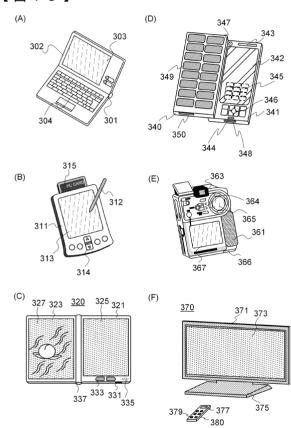

(実施の形態2)

本実施の形態では、先の実施の形態で得られる半導体装置を搭載した電子機器の例について図 1 5 を用いて説明する。先の実施の形態で得られる半導体装置は、従来にない優れた特性を有するものである。このため、当該半導体装置を用いて新たな構成の電子機器を提供することが可能である。なお、先の実施の形態に係る半導体装置は、集積化されて回路基板などに実装され、各電子機器の内部に搭載されることになる。

### [0144]

図 1 5 ( A ) は、先の実施の形態に係る半導体装置を含むノート型のパーソナルコンピュ

20

10

30

50

ータであり、本体301、筐体302、表示部303、キーボード304などによって構成されている。開示する発明に係る半導体装置をパーソナルコンピュータに適用することで、優れた性能のパーソナルコンピュータを提供することができる。

#### [0145]

図 1 5 ( B ) は、先の実施の形態に係る半導体装置を含む携帯情報端末(P D A ) であり、本体 3 1 1 には表示部 3 1 3 と、外部インターフェイス 3 1 5 と、操作ボタン 3 1 4 等が設けられている。また、操作用の付属品としてスタイラス 3 1 2 がある。開示する発明に係る半導体装置を携帯情報端末(P D A ) に適用することで、優れた性能の携帯情報端末(P D A ) を提供することができる。

#### [0146]

図15(C)には、先の実施の形態に係る半導体装置を含む電子ペーパーの一例として、電子書籍320を示す。電子書籍320は、筐体321および筐体323の2つの筐体で構成されている。筐体321および筐体323は、軸部337により一体とされており、該軸部337を軸として開閉動作を行うことができる。このような構成により、電子書籍320は、紙の書籍のように用いることが可能である。

#### [ 0 1 4 7 ]

筐体321には表示部325が組み込まれ、筐体323には表示部327が組み込まれている。表示部325および表示部327は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成とすることで、例えば右側の表示部(図15(C)では表示部325)に文章を表示し、左側の表示部(図15(C)では表示部327)に画像を表示することができる。

#### [0148]

また、図15(C)では、筐体321に操作部などを備えた例を示している。例えば、筐体321は、電源331、操作キー333、スピーカー335などを備えている。操作キー333により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍320は、電子辞書としての機能を持たせた構成としてもよい。

#### [0149]

また、電子書籍 3 2 0 は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

# [0150]

なお、電子ペーパーは、情報を表示するものであればあらゆる分野に適用することが可能である。例えば、電子書籍以外にも、ポスター、電車などの乗り物の車内広告、クレジットカード等の各種カードにおける表示などに適用することができる。開示する発明に係る半導体装置を電子ペーパーに適用することで、優れた性能の電子ペーパーを提供することができる。

#### [0151]

図 1 5 ( D ) は、先の実施の形態に係る半導体装置を含む携帯電話機である。当該携帯電話機は、筐体3 4 0 および筐体3 4 1 の二つの筐体で構成されている。筐体3 4 1 は、表示パネル3 4 2、スピーカー3 4 3、マイクロフォン3 4 4、ポインティングデバイス3 4 6、カメラ用レンズ3 4 7、外部接続端子3 4 8 などを備えている。また、筐体3 4 0 は、当該携帯電話機の充電を行う太陽電池セル3 4 9、外部メモリスロット3 5 0 などを備えている。また、アンテナは筐体3 4 1 内部に内蔵されている。

#### [ 0 1 5 2 ]

表示パネル342はタッチパネル機能を備えており、図15(D)には映像表示されている複数の操作キー345を点線で示している。なお、当該携帯電話は、太陽電池セル34 9で出力される電圧を各回路に必要な電圧に昇圧するための昇圧回路を実装している。ま 10

20

30

40

た、上記構成に加えて、非接触ICチップ、小型記録装置などを内蔵した構成とすることもできる。

#### [0153]

表示パネル342は、使用形態に応じて表示の方向が適宜変化する。また、表示パネル342と同一面上にカメラ用レンズ347を備えているため、テレビ電話が可能である。スピーカー343およびマイクロフォン344は音声通話に限らず、テレビ電話、録音、再生などが可能である。さらに、筐体340と筐体341はスライドし、図15(D)のように展開している状態から重なり合った状態とすることができ、携帯に適した小型化が可能である。

### [0154]

外部接続端子348はACアダプタやUSBケーブルなどの各種ケーブルと接続可能であり、充電やデータ通信が可能になっている。また、外部メモリスロット350に記録媒体を挿入し、より大量のデータの保存および移動に対応できる。また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。開示する発明に係る半導体装置を携帯電話機に適用することで、優れた性能の携帯電話機を提供することができる。

#### [0155]

図 1 5 ( E ) は、先の実施の形態に係る半導体装置を含むデジタルカメラである。当該デジタルカメラは、本体 3 6 1 、表示部 ( A ) 3 6 7 、接眼部 3 6 3 、操作スイッチ 3 6 4 、表示部 ( B ) 3 6 5 、バッテリー 3 6 6 などによって構成されている。開示する発明に係る半導体装置をデジタルカメラに適用することで、優れた性能のデジタルカメラを提供することができる。

#### [0156]

図 1 5 (F)は、先の実施の形態に係る半導体装置を含むテレビジョン装置である。テレビジョン装置 3 7 0 では、筐体 3 7 1 に表示部 3 7 3 が組み込まれている。表示部 3 7 3 により、映像を表示することが可能である。なお、ここでは、スタンド 3 7 5 により筐体 3 7 1 を支持した構成を示している。

#### [ 0 1 5 7 ]

テレビジョン装置370の操作は、筐体371が備える操作スイッチや、別体のリモコン操作機380により行うことができる。リモコン操作機380が備える操作キー379により、チャンネルや音量の操作を行うことができ、表示部373に表示される映像を操作することができる。また、リモコン操作機380に、当該リモコン操作機380から出力する情報を表示する表示部377を設ける構成としてもよい。

# [0158]

なお、テレビジョン装置 3 7 0 は、受信機やモデムなどを備えた構成とするのが好適である。受信機により、一般のテレビ放送の受信を行うことができる。また、モデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことが可能である。開示する発明に係る半導体装置をテレビジョン装置に適用することで、優れた性能のテレビジョン装置を提供することができる。

### [ 0 1 5 9 ]

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

# 【実施例1】

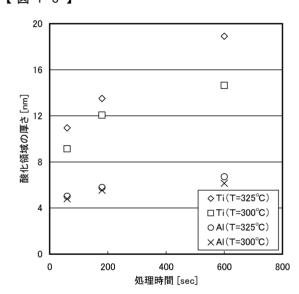

### [0160]

本実施例では、開示する発明の一態様に係る高密度プラズマ処理によって、導電層が酸化される様子を確認した。以下、詳細に説明する。

# [0161]

本実施例では、電源の周波数が2.45GHz、圧力が500Paの条件で、酸素とアルゴンとの混合ガスからプラズマを励起し、これを用いて導電層を処理した。また、処理時

10

20

30

40

間を1分(60秒)、3分(180秒)、10分(600秒)の3条件とすることで、処理時間と酸化領域の厚みとの関係を調査した。

#### [0162]

導電層としては、ガラス基板上に形成されたチタン膜およびガラス基板上に形成されたアルミニウム膜をそれぞれ用意した。また、基板温度をそれぞれ300 、325 として上記プラズマ処理を行った。つまり、基板温度が300 におけるチタン膜、基板温度が325 におけるチタン膜、基板温度が300 におけるアルミニウム膜、基板温度が325 におけるアルミニウム膜、の4条件に関して、処理時間と酸化領域の厚みとの関係を調査した。

#### [ 0 1 6 3 ]

調査結果を図16に示す。図16から、アルミニウムと比較して、チタンの方が、酸化速度が大きいことが分かる。また、チタンでは酸化速度の温度依存が大きいのに対して、アルミニウムでは酸化速度の温度依存が小さい。さらに、アルミニウムでは、酸化領域の厚さが、短時間で飽和する傾向にあるといえる。

#### [0164]

いずれの材料についても、ゲート電極と、ソース電極またはドレイン電極のショートを抑制するために十分な厚み (5 n m 以上)の酸化領域を得ることが可能である。

#### [ 0 1 6 5 ]

本実施例で示したような高密度プラズマによる酸化処理を適用することで、通常のプラズマ処理による酸化処理を適用する場合と比較して、酸化物半導体層へのダメージを軽減しつつ、酸素欠損に起因する局在準位を減少させることができる。つまり、酸化物半導体層の特性を一層向上させることができる。

#### [0166]

また、上記酸化処理によって、ソース電極またはドレイン電極の一部(特に、その側面に相当する部分)に酸化領域が形成されるため、ゲート電極と、ソース電極またはドレイン電極のショートを防止できる。

# [0167]

以上により、開示する発明の一態様は、酸化物半導体を用いたトランジスタの信頼性、その他の特性の向上に、極めて効果的であることが理解される。

#### 【符号の説明】

[0168]

- 100 基板

- 102 絶縁層

- 104 酸化物半導体層

- 1 0 4 a 酸化物半導体層

- 106 導電層

- 1 0 6 a ソース電極またはドレイン電極

- 106b ソース電極またはドレイン電極

- 108 絶縁層

- 1 0 8 a 絶縁層

- 108b 絶縁層

- 1 1 0 酸化領域

- 1 1 2 ゲート絶縁層

- 1 1 4 ゲート電極

- 1 1 6 層間絶縁層

- 1 1 8 層間絶縁層

- 150 トランジスタ

- 3 0 1 本体

- 3 0 2 筐体

- 3 0 3 表示部

30

10

20

50

| 3 0 4 | キーボード          |     |

|-------|----------------|-----|

| 3 1 1 | 本 体            |     |

| 3 1 2 | スタイラス          |     |

| 3 1 3 | 表示部            |     |

| 3 1 4 | 操作ボタン          |     |

| 3 1 5 | 外部インターフェイス     |     |

| 3 2 0 | 電子書籍           |     |

| 3 2 1 | 筐体             |     |

| 3 2 3 | 筐体             |     |

| 3 2 5 | 表示部            | 10  |

| 3 2 7 | 表示部            |     |

| 3 3 1 | 電源             |     |

| 3 3 3 | 操 作 キ ー        |     |

| 3 3 5 | スピーカー          |     |

| 3 3 7 | 軸 部            |     |

| 3 4 0 | 筐体             |     |

| 3 4 1 | 筐体             |     |

| 3 4 2 | 表示パネル          |     |

| 3 4 3 | スピーカー          |     |

| 3 4 4 | マイクロフォン        | 20  |

| 3 4 5 | 操 作 キ <b>-</b> |     |

| 3 4 6 | ポインティングデバイス    |     |

| 3 4 7 | カメラ用レンズ        |     |

| 3 4 8 | 外 部 接 続 端 子    |     |

| 3 4 9 | 太陽電池セル         |     |

| 3 5 0 | 外部メモリスロット      |     |

| 3 6 1 | 本体             |     |

| 3 6 3 | 接眼部            |     |

| 3 6 4 | 操作スイッチ         |     |

| 3 6 5 | 表示部(B)         | 30  |

| 3 6 6 | バッテリー          |     |

| 3 6 7 | 表示部(A)         |     |

| 3 7 0 | テレビジョン装置       |     |

| 3 7 1 | 筐 体            |     |

| 3 7 3 | 表示部            |     |

| 3 7 5 | スタンド           |     |

| 3 7 7 | 表示部            |     |

| 3 7 9 | 操作 <i>キー</i>   |     |

| 3 8 0 | リモコン操作機        | 4.0 |

|       |                | 40  |

# 【図面】

# 【図1】

# 【図2】

(A)

(B)

(C)

(D)

# 【図3】

(A)

(B)

(C)

# 【図4】

40

10

20

# 【図5】

# 【図6】

(A) B-B' 断面エネルギーバンド図(Vն>0)

(B) B-B' 断面エネルギーバンド図(VG<0)

# 【図7】

# 【図8】

40

10

20

# 【図9】

# 【図10】

# 【図11】

# 【図12】

30

10

20

# 【図13】

# 【図14】

10

# 【図15】

# 【図16】

30

20