(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4641043号

(P4641043)

(45) 発行日 平成23年3月2日(2011.3.2)

(24) 登録日 平成22年12月10日(2010.12.10)

(51) Int.Cl.

A 63 F 7/02 (2006.01)

F 1

A 63 F 7/02 326 Z

請求項の数 4 (全 39 頁)

(21) 出願番号 特願2008-279217 (P2008-279217)

(22) 出願日 平成20年10月30日 (2008.10.30)

(62) 分割の表示 特願平11-320345の分割

原出願日 平成11年11月10日 (1999.11.10)

(65) 公開番号 特開2009-18209 (P2009-18209A)

(43) 公開日 平成21年1月29日 (2009.1.29)

(54) 審査請求日 平成20年11月28日 (2008.11.28)

(73) 特許権者 000132747

株式会社ソフィア

群馬県桐生市境野町7丁目201番地

(74) 代理人 100096699

弁理士 鹿嶋 英實

(72) 発明者 井置 定男

群馬県桐生市宮本町3-7-28

審査官 ▲吉▼川 康史

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

ガイドレールで取り囲まれた遊技領域に入賞口が形成され、前記入賞口への入賞球に対して賞球が払い出される遊技機であって、

当該遊技機の制御に係わる制御基板をケースに収納して構成した制御装置を備えるとともに、前記制御装置にはワンチップ化してパッケージングされた遊技用演算処理装置が備えられ、

前記遊技用演算処理装置は、

遊技制御を行う遊技制御手段と、

前記遊技制御手段の制御を受けつつ、当該遊技用演算処理装置の外部のI/Oリソースを選択するための選択信号を発生する信号発生手段と、

前記外部のI/Oリソースとの間でデータ信号の授受を行う外部バスインターフェースと、

を備えるとともに、

前記遊技制御手段、前記信号発生手段及び前記外部バスインターフェースが共通の半導体基板上に実装され、

前記データ信号の入出力を行なう端子が備えられ、

さらに、前記選択信号を外部出力するチップセレクト信号端子が、前記データ信号の入出力を行なう端子とは別個に備えられ、

前記信号発生手段は、

10

20

前記遊技制御手段からの信号に基づいてM個の内部選択信号のいずれかを発生する第1信号発生手段と、

前記M個の内部選択信号のうちN個の内部選択信号の各々に対応する1ビットの信号を、前記選択信号として発生する第2信号発生手段と、

前記M個の内部選択信号のうち $2^X$ 個の内部選択信号の各々に対応するXビットの信号の各ビットを、前記選択信号として発生する第3信号発生手段と、

所定のモード指定信号に基づいて、前記第2信号発生手段からのN個の選択信号を前記チップセレクト信号端子から外部出力するか、または前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力するかを選択する選択手段と、を含んでおり、

前記制御装置には、前記チップセレクト信号端子からの信号により選択される前記I/Oリソースが備えられ、

前記選択手段により、前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力することが選択されると、前記チップセレクト信号端子のうちの1個の端子がストローブ信号の端子として機能し、前記チップセレクト信号端子のうちのX個の端子が前記ストローブ信号のタイミングでデコードされるコード化信号の端子として機能することを特徴とする遊技機。

#### 【請求項2】

前記制御装置は、前記遊技用演算処理装置のチップセレクト信号端子から出力されるXビットの前記コード化信号をデコードして、 $2^X$ 個の前記選択信号を再生する再生手段を備えたことを特徴とする請求項1記載の遊技機。

#### 【請求項3】

ガイドレールで取り囲まれた遊技領域に入賞口が形成され、前記入賞口への入賞球に応じて賞球が払い出される遊技機であって、

当該遊技機の制御に係わる制御基板をケースに収納して構成した制御装置を備えるとともに、前記制御装置にはワンチップ化してパッケージングされた遊技用演算処理装置が備えられ、

前記遊技用演算処理装置は、

遊技制御を行う遊技制御手段と、

前記遊技制御手段の制御を受けつつ、当該遊技用演算処理装置の外部のI/Oリソースを選択するための選択信号を発生する信号発生手段と、

前記外部のI/Oリソースとの間でデータ信号の授受を行う外部バスインターフェースと、

を備えるとともに、

前記遊技制御手段、前記信号発生手段及び前記外部バスインターフェースが共通の半導体基板上に実装され、

前記データ信号の入出力を行なう端子が備えられ、

さらに、前記選択信号を外部出力するチップセレクト信号端子が、前記データ信号の入出力を行なう端子とは別個に備えられ、

前記信号発生手段は、

前記遊技制御手段からの信号に基づいてM個の内部選択信号のいずれかを発生する第1信号発生手段と、

前記M個の内部選択信号のうちN個の内部選択信号の各々に対応する1ビットの信号を、前記選択信号として発生する第2信号発生手段と、

前記M個の内部選択信号のうち $2^X$ 個の内部選択信号の各々に対応するXビットの信号の各ビットを、前記選択信号として発生する第3信号発生手段と、

所定のモード指定信号に基づいて、前記第2信号発生手段からのN個の選択信号を前記チップセレクト信号端子から外部出力するか、または前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力するかを選択する選択手段と、を含んでおり、

10

20

30

40

50

前記制御装置には、前記チップセレクト信号端子からの信号により選択される前記I/Oリソースが備えられ、

前記遊技用演算処理装置には前記チップセレクト信号端子がN個設けられ、

前記選択手段によって前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力することが選択されると、前記N個のチップセレクト信号端子のうちの1個がストローブ信号の端子となる一方で、

前記選択手段によって前記何れの選択を行った場合であっても、前記N個のチップセレクト信号端子のうちの、前記ストローブ信号の端子を含むX+1個の端子以外の端子からは、前記選択信号として1ビットの信号が出力されることを特徴とする遊技機。

#### 【請求項4】

10

前記制御装置は、前記第3信号発生手段により発生したXビットの信号を前記ストローブ信号のタイミングでデコードして、2<sup>X</sup>個の前記選択信号を再生する再生手段を備えたことを特徴とする請求項3記載の遊技機。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、例えば、パチンコ遊技機、スロットマシンまたは映像式ゲーム機などの射幸心をあおるおそれのある遊技機（以下単に遊技機という）に関し、特に当該遊技機の内部基板（例えばパチンコ遊技機の場合は遊技制御基板）に取り付けられる、いわゆる“アミューズメントチップ”（共通の半導体基板上に形成されてパッケージングされたもの）と呼ばれる遊技用演算処理装置の改良に関する。 20

#### 【背景技術】

#### 【0002】

従来より、射幸心をあおるおそれのある遊技機の製造販売ならびに遊技店（以下ホールという）への設置および移動は、法令に基づく様々な規制に従って行われている。すなわち、製造販売に際しては所定の検査機関（以下「第三者機関」ということもある）の検査を必要とし、ホールへの設置に際しては所轄の警察署等（以下当局という）による確認を必要とする。さらに、同一ホール内での遊技機の移動や新台への入れ替え（遊技制御基板や同基板上の遊技用演算処理装置のみの入れ替えも含む）の際にも当局による確認を必要とする。 30

こうした様々な手続きは、遊技機の性能を一定の基準に維持し、且つ、ホールに設置された遊技機を当局の管理下に置くことにより、不正な遊技を排除し、以って法令の目的（「風俗営業の健全化」等）を達成するという社会ニーズに沿うものである。

#### 【0003】

しかし、上記の様々な規制にも関わらず、不正な行為はあとを絶たず、例えば、正規の遊技プログラムを収めたプログラムROM（Read Only Memory）を“裏ROM”と呼ばれる大当たりが出やすいように改竄（かいざん）されたROMに付け替えるなどの行為が問題視されるようになってきた。そこで、プログラムROMをCPU（Central Processor Unit）や主記憶および周辺回路などと一緒に同一半導体基板上にワンチップ化して、いわゆるアミューズメントチップ化し、それを遊技制御基板に取り付けるというハードウェア的なセキュリティ対策が取られている。 40

これによれば、プログラムROMをチップ内に実装しているため、少なくともアミューズメントチップそれ自体またはアミューズメントチップを搭載した制御基板を交換されない限り、不正な遊技プログラム（改竄された遊技プログラム）を走らせることができず、上記法令の目的を達成して社会ニーズに応えることができる。

#### 【0004】

ここで、上記アミューズメントチップは、既述のとおり、CPUコア、プログラムROM、主記憶および周辺回路などのハードウェアブロックをワンチップ化し、パッケージングされたものであるが、特に周辺回路の実装計画については、パッケージのサイズやピン数および汎用性の点で充分な検討が必要である。 50

例えば、周辺回路の一つに外部信号の入出力を行うI/Oブロックがあるが、このI/Oブロックの数は遊技機の種類によって様々であり、予想最大数のI/Oブロックを実装した場合は、汎用性の点で好ましいものの、パッケージサイズやピン数の増大を招くため現実的でない。

そこで、I/Oブロックを実装する代わりに、I/Oブロックを選択するための信号（以下チップセレクト信号という）を生成出力する回路ブロック（以下チップセレクトコントローラという）を実装することが考えられる。

これによれば、例えば、CS<sub>0</sub>～CS<sub>n</sub>のn個のチップセレクト信号を発生可能なチップセレクトコントローラをアミューズメントチップに実装し、各信号をCPUのメモリ空間の固有のアドレスに割り付けることにより、プログラム上でn個のチップセレクト信号を選択的に使用することができ、外付けされた最大n個のI/Oブロックを自由に利用できるようになるうえ、パッケージサイズもn個のI/Oブロックを実装するのに比べて大幅に小さくでき、しかも、ピン数増大もチップセレクト信号の数（n）に抑えることができる。

このような従来の遊技機としては、例えば以下の特許文献1に開示のものがある。

(特に、特許文献1の段落[0036]を参照)。

**【特許文献1】特開11-235454号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

ところで、アミューズメントチップの汎用性を考慮した場合、上記チップセレクト信号の数（n）は、アミューズメントチップの搭載が予想されるすべての遊技機のうちで最もI/Oブロックの数（m）が多いものに一致していなければならない。すなわち、n = mになつていなければならない。

しかしながら、このようにすると、1個からm個までのI/Oブロックを持つすべての遊技機に適用でき、汎用性の点で望ましいものの、例えば、m個未満のm個のI/Oブロックを持つ遊技機に適用した場合は、n - m個のチップセレクト信号とピンが無駄になる（当該遊技機においては永久に使用されない）という問題点がある。

したがって、本発明が解決しようとする課題は、パチンコ機や回胴式遊技機などの遊技機の製造分野または当該遊技機を遊技に供する遊技場（遊技店またはホールともいう）の分野もしくは当該遊技機の検査分野において、遊技機の汎用性を高め、且つ、外部I/O選択用信号の無駄と同信号出力用ピンの無駄を少なくして構成の簡素化と製造コストの削減を達成した遊技機用演算処理装置を提供することにある。

**【課題を解決するための手段】**

**【0006】**

請求項1記載の遊技機は、ガイドレールで取り囲まれた遊技領域に入賞口が形成され、前記入賞口への入賞球に対応して賞球が払い出される遊技機であつて、

当該遊技機の制御に係わる制御基板をケースに収納して構成した制御装置を備えるとともに、前記制御装置にはワンチップ化してパッケージングされた遊技用演算処理装置が備えられ、

前記遊技用演算処理装置は、

遊技制御を行う遊技制御手段と、

前記遊技制御手段の制御を受けつつ、当該遊技用演算処理装置の外部のI/Oリソースを選択するための選択信号を発生する信号発生手段と、

前記外部のI/Oリソースとの間でデータ信号の授受を行う外部バスインターフェースと、

を備えるとともに、

前記遊技制御手段、前記信号発生手段及び前記外部バスインターフェースが共通の半導体基板上に実装され、

前記データ信号の入出力を行なう端子が備えられ、

10

20

30

40

50

さらに、前記選択信号を外部出力するチップセレクト信号端子が、前記データ信号の入出力を行なう端子とは別個に備えられ、

前記信号発生手段は、

前記遊技制御手段からの信号に基づいてM個の内部選択信号のいずれかを発生する第1信号発生手段と、

前記M個の内部選択信号のうちN個の内部選択信号の各々に対応する1ビットの信号を、前記選択信号として発生する第2信号発生手段と、

前記M個の内部選択信号のうち $2^X$ 個の内部選択信号の各々に対応するXビットの信号の各ビットを、前記選択信号として発生する第3信号発生手段と、

所定のモード指定信号に基づいて、前記第2信号発生手段からのN個の選択信号を前記チップセレクト信号端子から外部出力するか、または前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力するかを選択する選択手段と、を含んでおり、

前記制御装置には、前記チップセレクト信号端子からの信号により選択される前記I/Oリソースが備えられ、

前記選択手段により、前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力することが選択されると、前記チップセレクト信号端子のうちの1個の端子がストローブ信号の端子として機能し、前記チップセレクト信号端子のうちのX個の端子が前記ストローブ信号のタイミングでデコードされるコード化信号の端子として機能することを特徴とする。

請求項2記載の遊技機は、前記制御装置は、前記遊技用演算処理装置のチップセレクト信号端子から出力されるXビットの前記コード化信号をデコードして、 $2^X$ 個の前記選択信号を再生する再生手段を備えたことを特徴とする。

請求項3記載の遊技機は、ガイドレールで取り囲まれた遊技領域に入賞口が形成され、前記入賞口への入賞球に対応して賞球が払い出される遊技機であって、

当該遊技機の制御に係わる制御基板をケースに収納して構成した制御装置を備えるとともに、前記制御装置にはワンチップ化してパッケージングされた遊技用演算処理装置が備えられ、

前記遊技用演算処理装置は、

遊技制御を行う遊技制御手段と、

前記遊技制御手段の制御を受けつつ、当該遊技用演算処理装置の外部のI/Oリソースを選択するための選択信号を発生する信号発生手段と、

前記外部のI/Oリソースとの間でデータ信号の授受を行う外部バスインターフェースと、

を備えるとともに、

前記遊技制御手段、前記信号発生手段及び前記外部バスインターフェースが共通の半導体基板上に実装され、

前記データ信号の入出力を行なう端子が備えられ、

さらに、前記選択信号を外部出力するチップセレクト信号端子が、前記データ信号の入出力を行なう端子とは別個に備えられ、

前記信号発生手段は、

前記遊技制御手段からの信号に基づいてM個の内部選択信号のいずれかを発生する第1信号発生手段と、

前記M個の内部選択信号のうちN個の内部選択信号の各々に対応する1ビットの信号を、前記選択信号として発生する第2信号発生手段と、

前記M個の内部選択信号のうち $2^X$ 個の内部選択信号の各々に対応するXビットの信号の各ビットを、前記選択信号として発生する第3信号発生手段と、

所定のモード指定信号に基づいて、前記第2信号発生手段からのN個の選択信号を前記チップセレクト信号端子から外部出力するか、または前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力するかを選択する選択手

10

20

30

40

50

段と、を含んでおり、

前記制御装置には、前記チップセレクト信号端子からの信号により選択される前記I/Oリソースが備えられ、

前記遊技用演算処理装置には前記チップセレクト信号端子がN個設けられ、

前記選択手段によって前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力することが選択されると、前記N個のチップセレクト信号端子のうちの1個がストローブ信号の端子となる一方で、

前記選択手段によって前記何れの選択を行った場合であっても、前記N個のチップセレクト信号端子のうちの、前記ストローブ信号の端子を含むX+1個の端子以外の端子からは、前記選択信号として1ビットの信号が出力されることを特徴とする。

請求項4記載の遊技機は、前記制御装置は、前記第3信号発生手段により発生したXビットの信号を前記ストローブ信号のタイミングでデコードして、2<sup>X</sup>個の前記選択信号を再生する再生手段を備えたことを特徴とする。

#### 【発明の効果】

#### 【0007】

請求項1記載の遊技機によれば、ガイドレールで取り囲まれた遊技領域に入賞口が形成され、前記入賞口への入賞球に対応して賞球が払い出される遊技機であって、当該遊技機の制御に係わる制御基板をケースに収納して構成した制御装置を備えるとともに、前記制御装置にはワンチップ化してパッケージングされた遊技用演算処理装置が備えられ、前記遊技用演算処理装置は、遊技制御を行う遊技制御手段と、前記遊技制御手段の制御を受けつつ、当該遊技用演算処理装置の外部のI/Oリソースを選択するための選択信号を発生する信号発生手段と、前記外部のI/Oリソースとの間でデータ信号の授受を行う外部バスインターフェースと、を備えるとともに、前記遊技制御手段、前記信号発生手段及び前記外部バスインターフェースが共通の半導体基板上に実装され、前記データ信号の入出力を行なう端子が備えられ、さらに、前記選択信号を外部出力するチップセレクト信号端子が、前記データ信号の入出力を行なう端子とは別個に備えられ、前記信号発生手段は、前記遊技制御手段からの信号に基づいてM個の内部選択信号のいずれかを発生する第1信号発生手段と、前記M個の内部選択信号のうちN個の内部選択信号の各々に対応する1ビットの信号を、前記選択信号として発生する第2信号発生手段と、前記M個の内部選択信号のうち2<sup>X</sup>個の内部選択信号の各々に対応するXビットの信号の各ビットを、前記選択信号として発生する第3信号発生手段と、所定のモード指定信号に基づいて、前記第2信号発生手段からのN個の選択信号を前記チップセレクト信号端子から外部出力するか、または前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力するかを選択する選択手段と、を含んでおり、前記制御装置には、前記チップセレクト信号端子からの信号により選択される前記I/Oリソースが備えられ、前記選択手段により、前記第2信号発生手段と前記第3信号発生手段の両出力を前記チップセレクト信号端子から外部出力することが選択されると、前記チップセレクト信号端子のうちの1個の端子がストローブ信号の端子として機能し、前記チップセレクト信号端子のうちのX個の端子が前記ストローブ信号のタイミングでデコードされるコード化信号の端子として機能するので、所定のモード指定信号(CS/ECOS信号)に基づいて、N個の選択信号を出力可能な第1の外部I/O制御モード(CSモード)と、2<sup>X</sup>個の内部選択信号の各々に対応するXビットの選択信号を出力可能な第2の外部I/O制御モード(ECOSモード)とに切り換えて使用できる遊技用演算処理装置を提供でき、Xビットの選択信号は外部デコードすることにより、全部でM個の選択信号を得ることができる。したがって、外部I/Oの数が異なるシステムにも柔軟に適用できる汎用性の高い遊技用演算処理装置を実現できるとともに、遊技用演算処理装置のチップセレクト信号端子の数をN個に留め置くことが可能となり、パッケージピン数の増加問題を解消することができる。

請求項2記載の遊技機によれば、前記制御装置は、前記遊技用演算処理装置のチップセレクト信号端子から出力されるXビットの前記コード化信号をデコードして、2<sup>X</sup>個の前記選択信号を再生する再生手段を備えたので、外部I/Oの数が多いシステムにも適用で

10

20

30

40

50

き、遊技用演算処理装置の汎用性を向上できる。

請求項3記載の遊技機によれば、請求項1と同様の効果が得られる。

請求項4記載の遊技機によれば、請求項2と同様の効果が得られる。

**【発明を実施するための最良の形態】**

**【0008】**

以下、本発明の実施の形態を、多数のパチンコ遊技機を設置したホールを例にして図面を参照しながら説明する。

<ホールの全体構成>

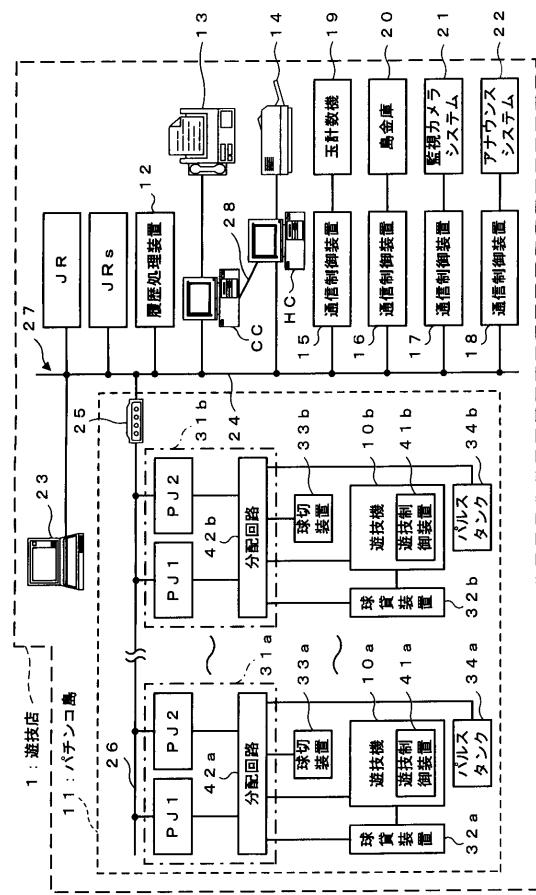

最初に、ホールの全体構成を説明する。図1はホールの全体構成を示すブロック図である。この図において、1はホール(遊技店)であり、ホール1にはCR(カードリーダ)式の遊技機10j(jはa、b…;以下同様)が多数設置されたパチンコ島11、状態変化情報記録装置JR、補助状態変化情報記録装置JRs、履歴処理装置12、カウンタ用コンピュータCC、FAX装置13、事務所用コンピュータHC、プリンタ14、通信制御装置15~18、玉計数機19、島金庫20、監視カメラシステム21、アナウンスシステム22および設定・検査装置23が配置されている。なお、設定・検査装置23は常設されない。必要な都度、店内ネットワーク24に接続して用いられる。

10

**【0009】**

パチンコ島11は、情報収集BOXとも呼ばれる情報収集端末装置31a、31b(以下適宜に情報収集端末装置31で代表する)、遊技機10a、10b(遊技機10)、カード式球貸装置32a、32b(カード式球貸装置32)、球切装置33a、33b(球切装置33)、パルスタング34a、34b(パルスタング34)およびネットワーク中継装置25を備えている。なお、パチンコ島11はホール1に複数配置されるが、それぞれの“島”は類似(但し、島ごとに遊技機の機種が異なることが多い)の構成のため、ここでは1つのパチンコ島11について説明することにする。

20

ネットワーク中継装置25は1つのパチンコ島11について、それぞれ1台ずつ配置されるが、その他の各装置(例えば、情報収集端末装置31、球切装置33、パルスタング34)は遊技機10a、10bと同数だけ(すなわち、遊技機10と対をなして)配置される。

**【0010】**

遊技機10は、遊技状態を制御する遊技制御装置41a、41b(以下適宜に遊技制御装置41で代表する)をそれぞれ有しており、遊技制御装置41は役物の制御を行う遊技用演算処理装置(図5参照:但し、図5では単に演算処理装置と表記している)200(冒頭で説明したアミューズメントチップに相当;詳細な構成は後述する)を内蔵している。遊技制御装置41は遊技制御基板やその基板を収納するケース等を含む。

30

遊技機10の側方にはカード式球貸装置32が配置されており、プリペイドカード(PC)を使用した球の貸出し操作等を遊技機10で行うことが可能になっている。

球切装置33は遊技機10の補給タンクへパチンコ島11から球を補給するもので、例えば、球が10個補給される毎に1パルスとなる信号(後述の図2に示す補給球数信号)が球切装置33から出力される。パルスタング34は遊技機10から外部に回収された遊技終了後の球を計数するもので、パルスタング34からは、例えば、球の10個流出(回収)ごとに1パルスとなる信号(後述の図2に示す回収球数信号)が出力される。

40

**【0011】**

情報収集端末装置31は、それぞれ、PJ1およびPJ2並びに分配回路42a、42b(以下適宜に分配回路42で代表する)を備えている。分配回路42は遊技機10、カード式球貸装置32、球切装置33およびパルスタング34に接続され、これらの各装置から入出力される信号をPJ1やPJ2に分配して転送する。例えば、分配回路42は、PJ1に対して売上信号、補給球数信号、回収球数信号、大当たり信号、特図回転信号、確変信号およびアミューズ通信信号を分配して転送し、PJ2に対して打止信号、金枠開閉信号、木枠開閉信号、空皿信号(遊技機10の貯留タンクにパチンコ島11から補給される球量が少なくなったことを検出する信号)、異常信号(不正な電磁波を出す等の不正な

50

磁気力および電磁波を検出する信号)および電源断信号を分配して転送する。

#### 【0012】

PJ1は売上信号、補給球数信号、回収球数信号、大当たり信号、特図回転信号および確変信号並びに遊技制御装置41から入出力されるアミューズ通信信号に基づいて、自分が受け持つ遊技機10および遊技設備装置(球貸装置32等)より出力された遊技情報と、PJ2から転送された遊技情報(状態変化情報)とを併せて演算加工し、収集した遊技情報より遊技情報の変化を検出する処理等を行うとともに、遊技用演算処理装置200の正当性判定(真偽判定)も行うもので、その詳細なブロック構成は後述する。

PJ2は遊技機10および遊技設備装置(球貸装置32等)より収集した主に遊技機10を監視するための状態変化情報(例えば、金枠開放信号、空皿信号等)をPJ1へ転送する処理やPJ1から発射停止要求があった場合に遊技機10を不能動化する処理(打止信号や電源断信号の発生処理)等を行うもので、PJ1と同様に、その詳細なブロック構成は後述する。10

ネットワーク中継装置25は、例えば、ルータ(Router)の機能を有し、島内ネットワーク26と店内ネットワーク24の各LON間を中継接続する装置である。島内ネットワーク26にはLON(米国エシヤロン社によって開発されたLON(Local Operating Network:同社の登録商標)が採用されている。

#### 【0013】

パチンコ島11は、島内ネットワーク26、ネットワーク中継装置25および店内ネットワーク24を介してJR、JRs、履歴処理装置12、CC、HC、通信制御装置15~18並びに設定・検査装置23に接続されている。店内ネットワーク24にも上記同様のLONが採用されている。20

島内ネットワーク26、ネットワーク中継装置25および店内ネットワーク24は、全体としてPJ1、PJ2、JR、JRs、CCおよびHCの間を接続する通信網27(以下LON通信網ということもある)を構成する。なお、LON通信網27に接続される各ノード間では、LONTALKプロトコルを使用した認証付きメッセージで情報の転送を行い、ノード双方を相互に認証して信頼性を確保するようになっている。

JRおよびJRsはホール1に1台ずつ設けられている。例えば、遊技機500台に対して1台設置されている。または、複数の遊技フロアがある場合は各フロア毎に1台設置されることもある。JRは各パチンコ島11のPJ1から通報される遊技情報(状態変化情報)を遊技機毎に整理して記録し、JRsはJRをバックアップする。30

履歴処理装置12は店内ネットワーク24に接続されているPJ1、PJ2、JR、JRs等からのエラー情報を記録する装置であり、エラー履歴を事後に分析して故障の発生したノード(PJ1、PJ2、JR、JRs等が接続されたノード)を特定するためのものである。

#### 【0014】

CCとしては、汎用のパーソナルコンピュータを使用することができる。CCは当日の遊技機10の状態変化情報をJRもしくはJRsをポーリングして収集し、状態変化を検出して表示する処理を行う。一般に状態変化情報の中で大当たりや確率変動は、CCで当該事象が発生した遊技機10の詳細な遊技情報を確認したい場合が普通なので、この特定の状態変化の場合は直接に該当する遊技機10のPJ1から遊技情報を収集し、先の状態変化情報と併せて詳細な遊技情報を表示する。また、JRがトラブルを起こして情報を収集できない場合は、直ちにバックアップ用のJRsに切り替えて同様の情報収集と表示を行う。40

さらに、CCで所望の遊技機10の遊技情報を確認したい場合は、直接該当するPJ1から遊技情報を収集して表示する機能もある。CCとHCとの間は専用のネットワークケーブル28(例えば、イーサネット(登録商標))で接続されており、CCで売上や機種情報および時系列情報等の経営情報を確認したい場合は、HCから当該情報を入手して表示できるようになっている。

なお、CCにはFAX装置13が接続されており、CCで収集分析した情報を所定の印

50

刷フォーマットに加工して外部に送信可能である。

#### 【0015】

H C にも汎用のパーソナルコンピュータを使用することができる。H C は当日や過去分の遊技情報を元にして経営判断に資する各種情報を生成するものであり、P J 1 もしくは P J 2 を所定間隔毎にポーリングして遊技情報を収集し、ハードディスクなどに記録するとともに、所定のフォーマットで表示したり印刷したりできるものである。また、H C で特定の遊技機 1 0 の遊技情報を確認したい場合は、直接該当する P J 1 から遊技情報を収集して表示する機能もある。さらに、H C で遊技機 1 0 の状態変化情報（リアル系の情報）を確認したい場合は、ネットワークケーブル 2 8 を介して C C から当該情報を入手して表示することもできる。なお、H C にはプリンタ 1 4 が接続されており、収集した情報を所定のフォーマットで印刷可能である。C C および H C は遊技店 1 の全体的な遊技情報を管理する管理装置を構成する。10

#### 【0016】

通信制御装置 1 5 ~ 1 8 は玉計数機 1 9 、島金庫 2 0 、監視カメラシステム 2 1 および アナウンスシステム 2 2 と店内ネットワーク 2 4 との間の通信インターフェースを行う装置である。

玉計数機 1 9 は遊技者が獲得した球（例えば、景品交換のため）の計数を行い、計数値を C C および H C に転送するとともに、当該遊技者に対して景品交換用の計数結果紙片をプリントアウトして出力する。島金庫 2 0 はホール 1 に設けられた両替機や現金式球貸装置等から回収した硬貨および紙幣を収納する装置であり、現在の収納金額を H C および C C に逐一転送する。20

監視カメラシステム 2 1 はホール 1 内に配置された監視カメラを管理して、撮像された画像を記録するシステムであり、アナウンスシステム 2 2 はホール 1 内のアナウンスを手動および自動的に行うシステムである。

#### 【0017】

設定・検査装置 2 3 には、例えば、ノート型のパーソナルコンピュータを使用することができる。設定・検査装置 2 3 は必要に応じて店内ネットワーク 2 4 に接続することができ、接続時に L O N 通信網 2 7 のアカウントを自動取得し、任意の P J 1 に接続された遊技機 1 0 の遊技制御装置 4 1 に内蔵されている遊技用演算処理装置 2 0 0 をアクセスして正当性判定のための固有 I D を設定することができるものである。30

既述のとおり、設定・検査装置 2 3 は“必要な都度”、店内ネットワーク 2 4 に接続される。必要な都度とは、例えば、新台に入れ替える場合または遊技用演算処理装置 2 0 0 のみを入れ替える場合もしくは遊技用演算処理装置 2 0 0 を含む遊技制御装置 4 1 を入れ替える場合であり、入れ替え後に設定・検査装置 2 3 を店内ネットワーク 2 4 に接続し、新台の P J 1 を介してその台（入れ換えられた遊技機 1 0 ）の遊技制御装置 4 1 に内蔵されている遊技用演算処理装置 2 0 0 をアクセスして正当性判定のための固有 I D を設定する。

#### 【0018】

なお、P J 1 で遊技用演算処理装置 2 0 0 の正当性を判定する場合に、上記のような固有 I D の判定に加えて、遊技プログラムを判定情報として使用してもよく、その場合には遊技用演算処理装置 2 0 0 に内蔵されている遊技プログラムと同一の基準遊技プログラムを設定・検査装置 2 3 から P J 1 に設定する。P J 1 は遊技用演算処理装置 2 0 0 から遊技プログラムを読み出し、設定された基準遊技プログラムと比較して正当性の判定を行う。40

#### 【0019】

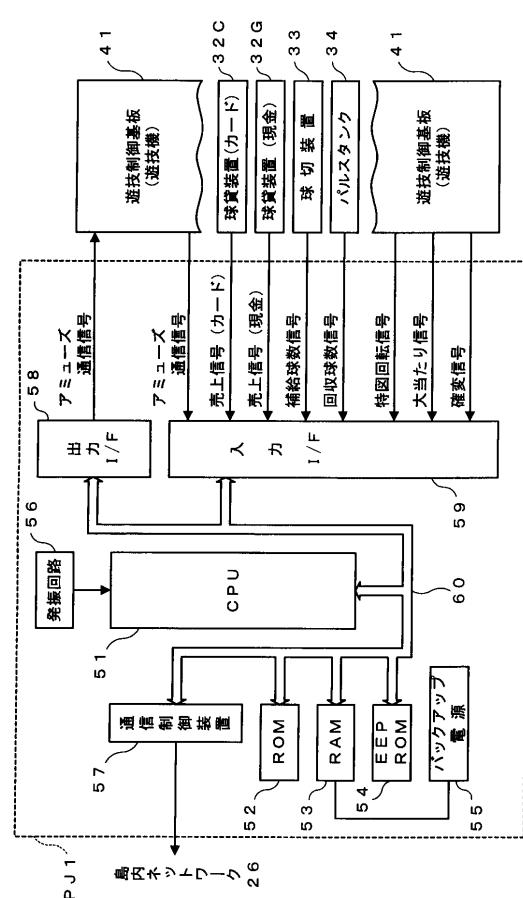

< P J 1 の構成 >

次に、P J 1 のブロック構成について説明する。図 2 は P J 1 のブロック図である。この図において、P J 1 は C P U 5 1 、R O M 5 2 、R A M 5 3 、E E P R O M 5 4 、バッカアップ電源 5 5 、発振回路 5 6 、通信制御装置 5 7 、出力インターフェース（I / F ）5 8 、入力インターフェース（I / F ）5 9 およびバス 6 0 を備えている。50

CPU51はROM52に格納されている処理プログラムに基づいて自分が受け持つ遊技機10および遊技設備装置（球貸装置32等）より出力された遊技情報と、PJ2より転送された遊技情報（状態変化情報）とを併せて演算加工し、収集した遊技情報より遊技情報の変化を検出する処理等を行うとともに、遊技用演算処理装置200の正当性判定を行う。ROM52は遊技用演算処理装置200の正当性判定を行う処理プログラムや遊技情報の収集・加工等のための処理プログラムを格納しており、RAM53はワークエリアとして用いられる。

#### 【0020】

EERPROM54は当該PJ1に接続された遊技用演算処理装置200に製造時に格納されている固有IDと同一の情報（以下「照合用ID」ということもある）を記憶する。

例えば、ホール1にN台の遊技機10が遊技可能な状態で設置されている場合、EEPROM54はN台分の照合用IDを記憶する。この記憶動作は、設定・検査装置23によって行われる。また、EERPROM54は状態変化情報の監視用の設定値も記憶する。この設定値は、CCもしくはHCにより設定される。

バックアップ電源55はRAM53の記憶情報を停電時も保持するための電源（一次電池または二次電池）である。発振回路56はCPU51に制御クロック信号を供給する。通信制御装置57は島内ネットワーク26を介して当該PJ1と他のネットワーク端末（例えば、PJ2あるいはネットワーク中継装置25を介した店内ネットワーク24につながる各端末）との間で情報の転送等に必要な通信の制御を行う。

#### 【0021】

出力インターフェース58は遊技機10とCPU51との間の出力インターフェース処理を行うもので、出力インターフェース58から遊技機10の遊技制御装置41に対してアミューズ通信信号が出力される。アミューズ通信信号は遊技制御装置41に内蔵されている遊技用演算処理装置200へ各種コマンド（例えば、認証チェックコマンド）を出力するための信号である。

入力インターフェース59は遊技機10および遊技設備装置（球貸装置32等）とCPU51との間の入力インターフェース処理を行うもので、アミューズ通信信号、カード式の球貸装置32Cからのカードによる売上信号、現金式の球貸装置32Gからの現金による売上信号、球切装置33からの補給球数信号、パルスタングク34からの回収球数信号、遊技制御装置41からの特図回転信号、大当たり信号、確変信号がそれぞれ入力されるようになっている。入力インターフェース59は、これらの信号をインターフェース処理してCPU51に送る。

#### 【0022】

入力インターフェース回路59に入力されるアミューズ通信信号は、例えば、遊技機10の遊技用演算処理装置200より送信される認証コード（固有IDを含む）信号であり、この信号をCPU51によって監視（認証判断）することにより、正規の遊技用演算処理装置200が装着されているか否かを判断する。カードによる売上信号はカード式球貸装置32Cによるプリペイドカードを使用した球の貸し出しの売上を知らせる信号である。なお、球貸装置にはプリペイドカードを使用したカード式球貸装置32Cのほかに、現金の投入によって球の貸し出しを行う現金式球貸装置32Gがあり、現金式球貸装置32Gの場合には、現金の投入に伴う球の貸し出しに対応した現金売上信号となる。補給球数信号は入賞による賞球に伴って当該遊技機10の補給タンクの球が減少した場合に、パチンコ島11から当該遊技機10の補給タンクに補給した球数情報を知らせる信号であり、球切装置33より出力されるいわゆるイン信号（例えば、球の10個補給で1パルスとなる信号あるいは球の100個補給で1パルスとなる信号または球の400個補給で1パルスとなる信号）が利用される。また、遊技機10より直接賞球数を外部に連絡する端子を備えているタイプの遊技機であれば、当該端子より信号を取得してもよい。

#### 【0023】

回収球数信号は当該遊技機10からパチンコ島11の方に（つまり遊技を終了して遊技の結果が確定した球を遊技機外部に）球が流れたことを知らせる信号であり、例えば、パ

10

20

30

40

50

ルスタンク 3 4 より球の 10 個流出に対応して 1 パルスとなるアウト信号が利用される。特図回転信号は当該遊技機 10 が第 1 種である場合に、特別図柄表示装置の図柄（以下特図という）変動が終了したときに、特図の回転を知らせる信号である。大当たり信号は当該遊技機 10 の特図が特定の利益状態（例えば、大当たりのゾロ目状態：“777”など）に揃って大当たりが発生していることを知らせる信号であり、この信号は遊技機 10 より大当たり発生時から大当たり終了時まで出力される。確変信号は当該遊技機 10 が確率変動遊技付きの遊技機である場合に、確率変動中および大当たり中に、それを知らせる信号である。

#### 【0024】

以上のとおり、PJ1 は、遊技機 10 の各々毎に設けられ、アミューズ通信信号に基づいて遊技用演算処理装置 200 の正当性判定を行い、遊技用演算処理装置 200 の非正当性が認められた場合に PJ2 に対して球の発射停止を要求して遊技機 10 を不能動化する処理を行うとともに、カードによる売上信号、現金による売上信号、補給球数信号、回収球数信号、特図回転信号、大当たり信号または確変信号の入力に基づいて遊技情報および状態変化情報の加工処理を行う。また、PJ1 は、PJ2 より転送された遊技情報（状態変化情報）も併せて上位ノード（JR、JRs）へ転送する処理を行うとともに、収集した遊技情報より遊技情報の変化を検出すると、状態変化情報の内容を JR および JRs へ自立的に通報する。さらに、PJ1 は、CC や HC からの要求指令があった場合に、遊技情報の内容を現在の遊技情報として要求元の CC や HC に転送する。

#### 【0025】

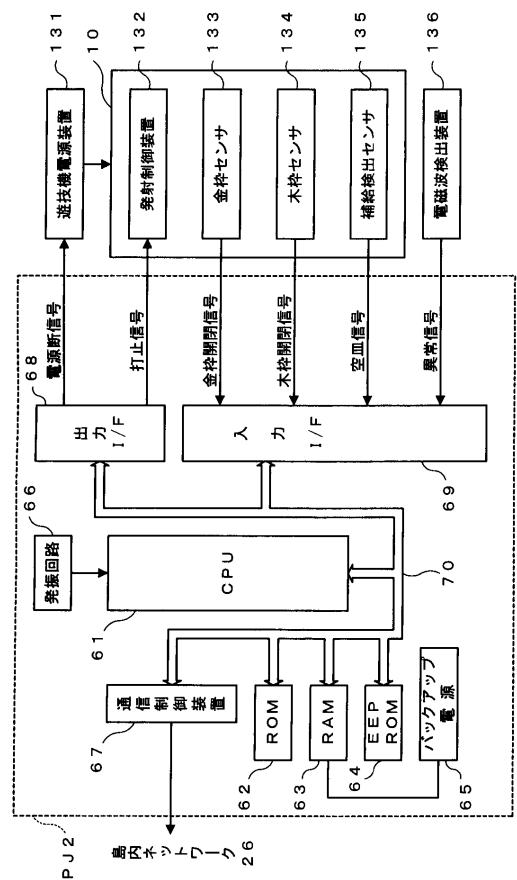

##### < PJ2 の構成 >

次に、PJ2 のブロック構成について説明する。図 3 は PJ2 のブロック図である。この図において、PJ2 は CPU61、ROM62、RAM63、EEPROM64、バックアップ電源 65、発振回路 66、通信制御装置 67、出力インターフェース（I/F）68、入力インターフェース（I/F）69 およびバス 70 を備えている。

CPU61 は ROM62 に格納されている処理プログラムに基づいて自分が受け持つ遊技機 10 および遊技設備装置（金枠センサ 133 等）より収集した信号から状態変化を検出（例えば、金枠の開閉等）し、その情報を PJ1 へ転送し、PJ1 より上位ノードへ転送してもらう処理を行うとともに、PJ1 から発射停止要求があった場合には遊技機 10 を不能動化（例えば、球の発射停止または遊技プログラム停止）する処理を行う。ROM62 は状態変化検出等のための処理プログラムを格納しており、RAM63 はワーカエリアとして用いられる。

#### 【0026】

EEPROM64 は当該 PJ2 における状態変化情報の監視用の設定値を記憶している。この設定値は、CC もしくは HC によって設定される。

バックアップ電源 65 は RAM63 の記憶情報を停電時も保持するための電源（一次電池または二次電池）である。発振回路 66 は CPU61 に制御クロック信号を供給し、通信制御装置 67 は島内ネットワーク 26 を介して当該 PJ2 と PJ1 との間の通信制御を行う。

出力インターフェース 68 は遊技機 10 と CPU61 との間の出力インターフェース処理を行うもので、出力インターフェース 68 から遊技機 10 の遊技機電源装置 131 に対して電源断信号が出力されるとともに、発射制御装置 132 に対して打止信号が出力される。遊技機電源装置 131 は、遊技機 10 への電源供給をオンオフする装置であり、電源断信号が入力されると遊技機 10 への電源供給をオフにする。打止信号は遊技機 10 へ発射停止を指令する信号であり、CC 等よりの指令で PJ2 を介して出力される。発射制御装置 132 はこの打止信号の入力に応答して球の発射を停止する。

入力インターフェース 69 は遊技機 10 および遊技設備装置（金枠センサ 133 等）と CPU61 との間の入力インターフェース処理を行うもので、入力インターフェース 69 には、遊技機 10 の金枠センサ 133 からの金枠開閉信号、木枠センサ 134 からの木枠開閉信号、補給検出センサ 135 からの空皿信号、電磁波検出装置 136 からの異常信号

10

20

30

40

50

がそれぞれ入力されている。入力インターフェース 69 は、これらの信号をインターフェース処理して CPU 61 に送る。

#### 【0027】

金枠センサ 133 は遊技機 10 における金枠の開閉状態を検出するもので、金枠近傍に設けられた金枠の開閉を検出するスイッチによって構成される。木枠センサ 134 は遊技機 10 における額縁状前面枠の開閉状態を検出するもので、額縁状前面枠近傍に設けられた木枠の開閉を検出するスイッチによって構成される。補給検出センサ 135 は遊技機 10 のタンク（タンクにはパチンコ島 11 から遊技球が補給される）に補給されている球量が少なくなったことを検出して空皿信号を出力する。電磁波検出装置 136 は遊技機 10 への磁石の接近、あるいは遊技機 10 に対する電波の放射を検出すると異常信号を出力する。10

#### 【0028】

以上のとおり、PJ2 は、遊技機 10 の各々毎に設けられ、遊技機 10 および遊技設備装置（金枠センサ 133 等）より収集した信号から状態変化を検出（例えば、金枠が 10 秒間開放したら金枠開放とする等）し、その情報を PJ1 へ転送し、PJ1 より上位ノードへ転送してもらうとともに、PJ1 から発射停止要求があった場合に遊技機 10 を不能動化する。なお、PJ2 は PJ1 の中に一体的に組み込んでもよく、例えば、PJ1 の基板上に PJ2 を一体的に搭載するようにしてもよい。

ここで、PJ1 および PJ2 は、全体として、遊技機 10 の遊技制御装置 41 に含まれる遊技用演算処理装置 200 の固有 ID を監視して当該遊技用演算処理装置 200 の正当性を評価する監視装置を構成する。20

#### 【0029】

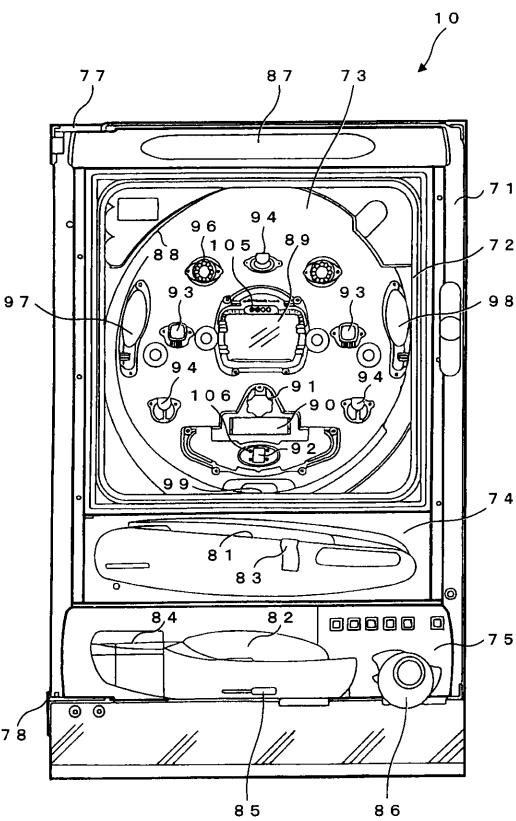

##### <遊技機の構成>

図 4 は遊技機 10 を示す図であり、遊技機 10 は額縁状の前面枠 71 と、ガラスを支持する金枠（ガラス枠）72 と、遊技領域が形成された遊技盤 73 と、前面表示パネル 74 と、前面表示パネル 74 の下方に設けられた操作パネル 75 とを有している。前面枠 71 は遊技機 10 を設置している木製の機枠（図示略）に対して上部蝶番 77 および下部蝶番 78 によって開閉可能に支持され、金枠 72 は前面枠 71 に開閉可能に支持されている。

表示パネル 74 は一端側が前面枠 71 に開閉可能に支持され、賞球を受ける上皿 81 が形成されるとともに、上皿 81 の球を球貯留皿（受皿ともいう）82 に移すために両者を接続する通路を開閉するための開閉レバー 83 が設けられている。操作パネル 75 には、灰皿 84 および前述の球貯留皿 82 が形成されるとともに、球貯留皿 82 に貯留された球を外部下方に抜くための球抜きレバー 85 が設けられている。また、操作パネル 75 の右端部側には玉発射用の操作ノブ 86 が設けられており、遊技機 10 の前面枠 71 の上部には大当たり時に点灯または点滅する大当たり表示器 87 が設けられている。30

#### 【0030】

遊技盤 73 には前面の略円形領域をガイドレール 88 で取り囲んだ遊技領域が形成されており、この遊技領域には、複数の識別情報（いわゆる特別図柄；以下特図という）を複数列で変動表示する特図表示装置 89、大入賞口を有する特別変動入賞装置 90、特図始動口として機能する普通変動入賞装置 91（いわゆる普電）、普通変動入賞装置 91 に設けられた普通図柄（いわゆる普図；以下普図という）を表示する普図表示装置 92、スルーチャッカー形式の複数の普図始動ゲート 93、複数の一般入賞口 94、風車と呼ばれる複数の打球方向変換部材 96、左右のサイドランプ 97、98、アウト穴 99 などが備えられている。40

普通変動入賞装置 91 内の入賞流路には特図始動スイッチ 100 が設けられており、普図始動ゲート 93 内の通過流路には普図始動ゲートスイッチ 101 が設けられている。また、特別変動入賞装置 90 の大入賞口内における継続入賞流路には継続スイッチ 102 が設けられており、一般入賞流路にはカウントスイッチ 103 が設けられている（上記各スイッチは図 5 参照）。

#### 【0031】

10

20

30

40

50

特図表示装置 8 9 の上部には前述した一般入賞口 9 4 が配置され、また、4 個の特図始動記憶表示器 1 0 5 が設けられており、普通変動入賞装置 9 1 には、4 個の普図始動記憶表示器 1 0 6 が設けられている。普図表示装置 9 2 は、例えば、一桁の数字を表示する 7 セグメントの表示部を有する液晶または L E D 等よりなる表示器であり、この場合、普通図柄（普図）は一桁の数字である。始動記憶表示器 1 0 5 、 1 0 6 は、特図あるいは普図の始動記憶数をそれぞれ表示するものである。

特図始動スイッチ 1 0 0 は普通変動入賞装置 9 1 に玉が入賞したことを検出し、普図始動ゲートスイッチ 1 0 1 は普図始動ゲート 9 3 を玉が通過したことを検出し、カウントスイッチ 1 0 3 は特別変動入賞装置 9 0 の大入賞口に入った全ての玉を検出し、継続スイッチ 1 0 2 は大入賞口に入った玉のうち継続入賞（いわゆる V 入賞）した玉を検出する。

10

なお、遊技盤 7 3 の遊技領域には、天釘やヨロイ釘などと呼ばれる多数の障害釘が設けられているが、ここでは図面の輻輳を避けるために省略している。また、遊技盤 7 3 には、その他の各種装飾ランプや L E D 等が設けられていてもよい。

遊技盤における遊技領域の種類は、いわゆる第 1 種に属するものや図柄表示装置を備えた第 3 種に属するものを含め種々のものがあるが、本発明は何れの種類にも適用できる。要は、遊技制御を司る遊技用演算処理装置 2 0 0 を備えるものであればよい。ちなみに、本実施の形態のものは第 1 種に属するタイプである。

### 【 0 0 3 2 】

#### < 遊技制御装置の構成 >

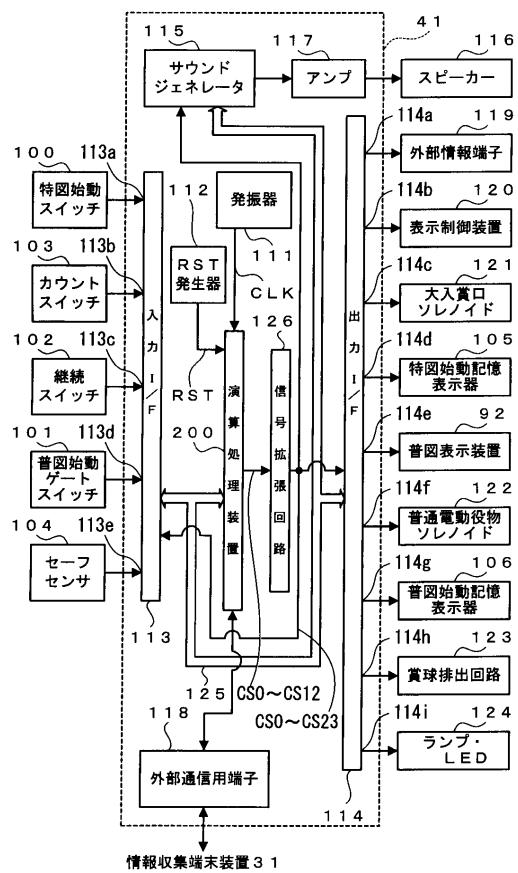

図 5 は遊技制御装置 4 1 のブロック図であり、遊技制御装置 4 1 は、パチンコ遊技等に必要な役物制御を行うアミューズメントチップとしての遊技用演算処理装置 2 0 0 と、振動素子の固有振動数を分周して所定のクロック信号（ C L K ）を発生する発振器 1 1 1 と、遊技制御装置 4 1 への電源投入を検出してシステムリセット信号（ R S T ）を発生する電源投入検出回路（図では R S T 発生器と表記） 1 1 2 と、各種センサ信号を入力する 5 個のポート 1 1 3 a ~ 1 1 3 e を有する入力インターフェース 1 1 3 と、各種駆動信号を出力する 9 個のポート 1 1 4 a ~ 1 1 4 i を有する出力インターフェース 1 1 4 と、遊技に必要な効果音（電子音や音声合成音）を生成するサウンドジェネレータ 1 1 5 と、サウンドジェネレータ 1 1 5 からの効果音信号を増幅して遊技機 1 0 の所定箇所に設置されたスピーカー 1 1 6 に出力するアンプ 1 1 7 と、遊技用演算処理装置 2 0 0 と情報収集端末装置 3 1 j （図 1 の情報収集端末装置 3 1 a 、 3 1 b 参照）との間で信号の受け渡しを行う外部通信端子 1 1 8 と、遊技用演算処理装置 2 0 0 と入力インターフェース 1 1 3 および出力インターフェース 1 1 4 ならびにサウンドジェネレータ 1 1 5 の間を接続する外部バス 1 2 5 （“外部”とは遊技用演算処理装置 2 0 0 の外側という意味である）と、遊技用演算処理装置 2 0 0 から出力される 1 3 個のチップセレクト信号（発明の要旨に記載の選択信号に相当） C S 0 ~ C S 1 2 を 2 4 個のチップセレクト信号 C S 0 ~ C S 2 3 に拡張する信号拡張回路 1 2 6 と、を含んで構成される。

20

30

なお、本実施の形態における遊技機 1 0 は、上記のとおり、その遊技制御装置 4 1 に、遊技用演算処理装置 2 0 0 から出力される 1 3 個のチップセレクト信号 C S 0 ~ C S 1 2 を 2 4 個のチップセレクト信号 C S 0 ~ C S 2 3 に拡張する信号拡張回路 1 2 6 を含むため、後で詳述する C S / E C S モードを E C S モードに設定して使用する。

40

### 【 0 0 3 3 】

入力インターフェース 1 1 3 の各ポート 1 1 3 a ~ 1 1 3 e （図では 5 個のポート）には、特図始動スイッチ 1 0 0 、普図始動ゲートスイッチ 1 0 1 、継続スイッチ 1 0 2 、カウントスイッチ 1 0 3 およびセーフセンサ 1 0 4 からの信号が入力される。セーフセンサ 1 0 4 は入賞した遊技球を検出する。出力インターフェース 1 1 4 の各ポート 1 1 4 a ~ 1 1 4 i （図では 9 個のポート）からは、情報収集端末装置 3 1 に遊技情報を出力するための外部情報端子 1 1 9 、特図表示装置 8 9 の表示制御を行う表示制御装置 1 2 0 、特別変動入賞装置 9 0 である大入賞口を開閉駆動する大入賞口ソレノイド 1 2 1 、特図始動記憶表示器 1 0 5 、普図表示装置 9 2 、普通変動入賞装置 9 1 を駆動する普通電動役物ソレノイド 1 2 2 、普図始動記憶表示器 1 0 6 、入賞球に対応して賞球の排出を制御する賞球

50

排出回路 123、各種装飾ランプ、LED（例えばサイドランプ 97、98 等を含む装飾具）124 に制御信号が output される。

#### 【0034】

入力インターフェース 113、出力インターフェース 114 およびサウンドジェネレータ 115 には、外部バス 125 が接続されるとともに、信号拡張回路 126 からの 24 個のチップセレクト信号 CS0 ~ CS23 が入力されており、発明の要旨に記載の外部 I/O に相当する入力インターフェース 113 の 5 個のポート 113a ~ 113e、出力インターフェース 114 の 9 個のポート 114a ~ 114i およびサウンドジェネレータ 115 は、24 個のチップセレクト信号 CS0 ~ CS23 の状態ならびに外部バス 125 に含まれるいくつかの制御信号（例えば、MREQ、IOREQ、WR、RD 信号）の状態に応じて、一つが選択され、その選択された I/O ブロックと外部バス 125 を介して、入力信号、例えば、特図始動スイッチ 100 の信号を遊技用演算処理装置 200 に取り込み、または、遊技用演算処理装置 200 からの信号を、例えば、表示制御装置 120 に出力する。

#### 【0035】

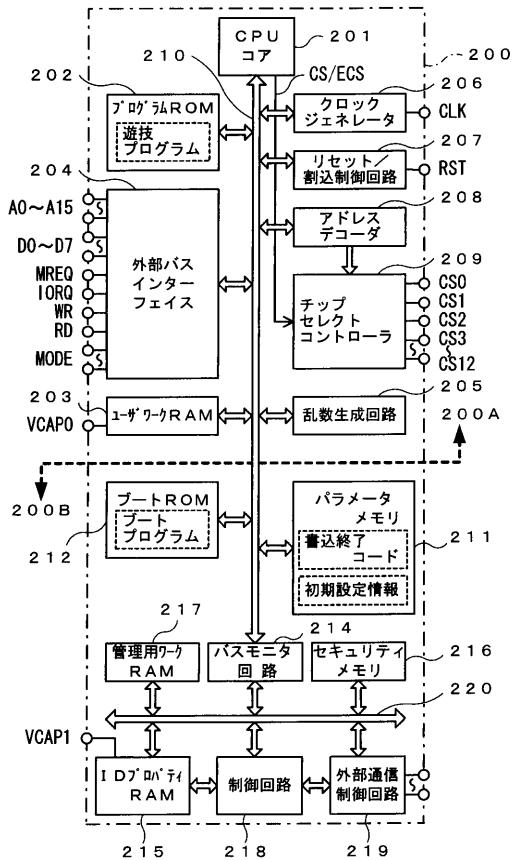

<遊技用演算処理装置の構成>

図 6 は遊技用演算処理装置 200 のブロック図である。遊技用演算処理装置 200 は遊技制御を行う遊技ブロック 200A と、情報管理を行う管理ブロック 200B とに区分され、各ブロックの（以下の）構成要素を共通の半導体基板上に実装してワンチップ化し、パッケージングして製造された、アミューズメントチップである。

遊技ブロック 200A は、CPU コア（発明の要旨に記載の遊技制御手段に相当）201 やプログラム ROM 202 およびユーザワーク RAM 203 といった主構成要素を含むとともに、外部バスインターフェース 204、乱数生成回路 205、クロックジェネレータ 206、リセット／割込制御回路 207、アドレスデコーダ（発明の要旨に記載の信号発生手段、第 1 信号発生手段に相当）208 およびチップセレクトコントローラ（発明の要旨に記載の信号発生手段、第 2 信号発生手段、第 3 信号発生手段、選択手段に相当）209 などの従構成要素（CPU コア 201 の周辺回路要素）を含み、且つ、これらの構成要素を接続する CPU バス 210 を含む。

#### 【0036】

CPU コア 201 は、特に限定しないが、Z80 コアであり、遊技制御のための演算処理を行い、プログラム ROM 202 はその制御プログラム（遊技プログラム）を格納し、ユーザワーク RAM 203 は遊技ブロック 200A における遊技プログラムに基づく処理を実行する際にワークエリア（作業領域）として用いられるものである。なお、ユーザワーク RAM 203 は、遊技用演算処理装置 200 の端子群の一つに割り当てられた専用の端子（以下、便宜的に VCAP0 という）を用いて、電源バックアップ機能を付加できるようになっており、遊技機 10 の電源オフ後もその記憶内容を保持することが可能になっている。VCAP0 の使用法は後述する。

#### 【0037】

外部バスインターフェース 204 は、図 5 の外部バス 125 との間で、複数ビット（例えば、16 ビット）のアドレス信号 A0 ~ A15、複数ビット（例えば、8 ビット）のデータ信号 D0 ~ D7、メモリリクエスト信号 MREQ、入出力リクエスト信号 IORQ、メモリ書き込み信号 WR、メモリ読み出し信号 RD およびモード信号 MODE などの信号インターフェース処理を行うものである。

例えば、MODE 信号をアクティブにした状態で、アドレス信号 A0 ~ A15 を順次にインクリメントしながら、データ信号 D0 ~ D7 を加えると、プログラム ROM 202 への書き込みモードとなって遊技機の製造メーカーあるいは第三者機関による遊技プログラムの書き込みが可能になる。プログラム ROM 202 への遊技プログラムの書き込みが終了すると、後述のパラメータメモリ 211 の所定領域に書き終了コードが記録（例えば、所定のコードもしくは所定ビットを物理的に切断することで記録）されるようになっており、パラメータメモリ 211 に書き終了コードが記録されている場合には、プログラム RO

10

20

30

40

50

M 2 0 2への遊技プログラムの書き込みができないようになっている。

また、M R E Q 信号またはI O R E Q 信号をアクティブにした状態でW R 信号をアクティブにすると、所定の外部I / OにD 0 ~ D 7を書き込むことができ、R D 信号をアクティブにすると、所定の外部I / OからD 0 ~ D 7を取り込むことができる。なお、所定の外部I / Oとは、図5の入力インターフェース1 1 3の各ポート1 1 3 a ~ 1 1 3 e、出力インターフェース1 1 4の各ポート1 1 4 a ~ 1 1 4 iおよびサウンドジェネレータ1 1 5のうち、チップセレクト信号C S 0 ~ C S 1 2（正確には図5の信号拡張回路1 2 6から出力される2 4個のチップセレクト信号C S 0 ~ C S 2 3）の状態とW RまたはR D信号の状態に応じて選択される一つの要素のことである。

#### 【0 0 3 8】

10

乱数生成回路2 0 5は遊技の実行過程において遊技価値（例えば、大当たり）を付加するか否か等に係わる乱数（乱数は、大当たりの決定や停止時の図柄の決定等に使用）を生成するもので、一様性乱数を生成する数学的手法（例えば、合同法あるいはM系列法等）を利用している。本実施の形態では、機種に関連した情報を乱数生成の際ににおける種値として利用する。

クロックジェネレータ2 0 6は、発振器1 1 1からのクロック信号C L Kを基に、C P Uコア2 0 1を含む遊技用演算処理装置2 0 0の各ブロックに動作クロック信号を供給する。

リセット／割込制御回路2 0 7は電源投入検出回路1 1 2からのシステムリセット信号（R S T）に応答してC P Uコア2 0 1をシステムリセット（詳細は後述）するとともに、遊技用演算処理装置2 0 0の内部の各種リソースを初期状態に設定する。

20

#### 【0 0 3 9】

アドレスデコーダ2 0 8はC P Uバス2 1 0のアドレスバスの情報をデコードし、そのデコード結果に応じて、2 4個のI / Oリソース選択用の内部信号（発明の要旨に記載の内部選択信号に相当）i C S 0 ~ i C S 2 3の一つをアクティブにする。ここで、C P Uバス2 1 0のアドレスバス上の情報ビット数はi A 0からi A 1 5までの1 6ビットであり、アドレスデコーダ2 0 8は、このi A 0からi A 1 5までをフルデコードし、1 6ビットで表現される0 0 0 0 hからF F F F hまでのアドレス空間の所定番地に予め割り付けられた2 4個のI / Oアドレス（例えば、2 3 0 0 h ~ 2 3 1 7 hまでの2 4バイトのアドレス）のいずれかを検出すると、当該I / Oアドレスに対応する一つのI / Oリソース選択用の内部信号をアクティブにする。

30

#### 【0 0 4 0】

チップセレクトコントローラ2 0 9はアドレスデコーダ2 0 8からの2 4個のI / Oリソース選択用の内部信号i C S 0 ~ i C S 2 3と、C P Uコア2 0 1からのモード指定信号C S / E C Sに基づいて、1 3個のチップセレクト信号C S 0 ~ C S 1 2の状態をコントロールする。具体的には、モード指定信号C S / E C Sが“C Sモード指定”的場合には、1 3個のチップセレクト信号C S 0 ~ C S 1 2のすべてを外部I / O選択用にしてその状態をコントロールする一方、“E C Sモード”的場合には、1 3個のチップセレクト信号C S 0 ~ C S 1 2のうち8個（C S 0 ~ C S 7）を外部I / O選択用にして、その状態をコントロールするとともに、残り5個のチップセレクト信号C S 8 ~ C S 1 2の組合せ状態をコントロールする。C Sモードの場合は、1 3個のチップセレクト信号C S 0 ~ C S 1 2を用いて、最大1 3個までの外部I / Oを制御できるが、E C Sモードの場合は、さらに、最大2 4個までの外部I / Oを制御することができる。すなわち、E C Sモードの場合は、8個のチップセレクト信号C S 0 ~ C S 7で最大8個、および、残り5個のチップセレクト信号C S 8 ~ C S 1 2のうちの4個（C S 8 ~ C S 1 1）の組合せで2<sup>4</sup>個（= 1 6個；指数の4は発明の要旨に記載のXに相当）、したがって、最大8個+1 6個 = 2 4個までの外部I / Oを制御できる。

40

#### 【0 0 4 1】

本実施の形態における外部I / Oは、図5における、入力インターフェース1 1 3の5個のポート1 1 3 a ~ 1 1 3 e、出力インターフェース1 1 4の9個のポート1 1 4 a ~

50

114 i およびサウンドジェネレータ 115 であり、5 個 + 9 個 + 1 個の計 15 個の外部 I/O を備えるから、CS モードを使用せずに、ECS モードを使用する。すなわち、ECS モードを使用することにより、チップセレクト信号 CS0 ~ CS12 の実質数（13 個）を 24 個に拡張し、その拡張チップセレクト信号 CS0 ~ CS23 を用いて、15 個の外部 I/O に対応している。

#### 【0042】

CPU バス 210 はデータバス、アドレスバスおよびコントロールバスを含み、CPU コア 210 とプログラム ROM 202、外部バスインターフェース 204、ユーザワーク RAM 203、クロックジェネレータ 206、リセット割制御回路 207、アドレスデコーダ 208、乱数生成回路 205 の間を接続するとともに、管理ブロック 200B の一部の構成要素（ブート ROM 212、パラメータメモリ 211 およびバスモニタ回路 214）にも接続されている。10

#### 【0043】

次に、遊技用演算処理装置 200 における情報管理を行う管理ブロック 200B の構成を説明する。管理ブロック 22B は、パラメータメモリ 211、ブート ROM 212、バスモニタ回路 214、ID プロパティ RAM 215、セキュリティメモリ 216、管理用ワーク RAM 217、制御回路 218、外部通信回路 219 および管理バス 220 を含むとともに、遊技ブロック 200A から延びる CPU バス 210 の一部を含んで構成されており、CPU バス 210 は、ブート ROM 212、パラメータメモリ 211 およびバスモニタ回路 214 に接続されている。20

#### 【0044】

ブート ROM 212 はブートプログラムを格納しており、遊技用演算処理装置 200 のシステムリセット時（正確には、システムリセット直後に実行される管理ブロック 200B の自己診断および初期化処理の正常完了後に）、このブートプログラムが立ち上がって、所定の簡易チェックを行い、正常であれば遊技プログラムの所定アドレス（CPU 201 のアドレス空間内における所定アドレス；一般に当該アドレス空間の先頭番地 0000h）に処理を渡すようになっている。パラメータメモリ 211 は書き終了コードおよび初期設定情報を格納している。書き終了コードとは、先にも述べたとおり、プログラム ROM 202 に遊技プログラムを書き込んだことを示す情報である。また、初期設定情報とは、遊技機の製造メーカーが遊技プログラムを書き込む際に、チップセレクト信号 CS0 ~ CS12 の拡張機能（ECS モード）のオンオフ設定や、チップセレクト信号 CS0 ~ CS12 の用途（但し ECS モードをオンにした場合は CS0 ~ CS23 の用途）などを設定するための情報である。チップセレクト信号 CS0 ~ CS12 の拡張機能とは、チップセレクト信号の数を拡張する機能であり、この機能をオン（ECS モード）にすると CS0 から CS12 までの 13 個しかないチップセレクト信号を CS0 から CS23 までの 24 個に拡張することができるというものである。本実施の形態は、前述のとおり、ECS モードを使用する。30

#### 【0045】

バスモニタ回路 214 は、CPU バス 210 の状態監視を行い、CPU バス 210 が CPU コア 201 によって使用されていないときに、必要に応じて、CPU バス 210 を介して遊技ブロック 200A のプログラム ROM 202 やユーザワーク RAM 203 などをアクセスし、所要のデータ（遊技プログラムやユーザワーク RAM 203 の内容など）を管理ブロック 200B に取り込む。40

#### 【0046】

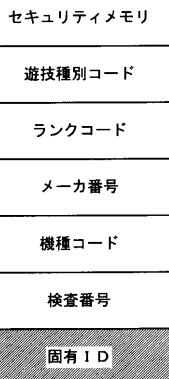

セキュリティメモリ 216（ワンタイム PROM で構成）には、遊技用演算処理装置 200 の識別や正当性の判定のために使用する固有 ID が書き込まれており、さらに、この固有 ID に加え、遊技種別コード、ランクコード、メーカー番号、機種コードおよび検査番号などの各情報が書き込まれている。なお、遊技種別コードはパチンコ遊技機やスロットルマシン等を区別するための情報であり、例えば、パチンコ遊技機の場合は“P”、スロットルマシンの場合は“G”となる。ランクコードは遊技機の機種ランクコード（第 1 種

1020304050

、第2種等を区別するためのコード)、メーカー番号当該遊技機の製造メーカーを識別するためのメーカーID(またはメーカーコード)であり、機種コードは製造メーカーが設定する当該遊技機の製品コードである、検査番号(または検定コード)は第三者機関による検査に合格した遊技機に付与される番号である。

#### 【0047】

IDプロパティRAM215には、セキュリティメモリ216の内容がコピーされている。すなわち、固有ID、遊技種別コード、ランクコード、メーカー番号、機種コードおよび検査番号が書き込まれている。コピーのタイミングは、遊技機10の電源投入時または遊技用演算処理装置200のシステムリセット時であり、例えば、システムリセット直後に管理ブロック200Bで実行される初期化処理の中で行われる。IDプロパティRAM215は、前述のユーザワークRAM203と同様に、遊技用演算処理装置200の端子群の一つに割り当てられた専用の端子(以下便宜的にVCAPIという)を用いて、電源バックアップ機能を附加できるようになっており、遊技機10の電源オフ後もその記憶内容を保持することが可能になっている。なお、VCAPIの使用法は後述する。

管理用ワークRAM217は、バスモニタ回路214を介して読み込まれた遊技ブロック200Aの情報(プログラムRAM202の内容やユーザワークRAM203の内容など)を一時的に保持するための記憶領域である。

#### 【0048】

制御回路218は所定のシーケンスを実行して、管理ブロック200Bの動作を制御するもので、例えば、システムリセット時に(正確にはシステムリセット直後に管理ブロック200Bで実行される初期化処理で)セキュリティメモリ216の内容をIDプロパティRAM215にコピーしたり、また、遊技中にバスモニタ回路214を介してCPUコア201のバス解放期間を検出し、同期間中に遊技ブロック200AのプログラムROM202の内容やユーザワークRAM203の内容を読み出して管理用ワークRAM217へ書き込んだりするほか、外部装置であるPJ1からの管理情報要求指令に応答して管理用ワークRAM217やIDプロパティRAM215の内容を外部へ転送したりする。

外部通信回路219は前述のPJ1(図2参照)との通信を行うもので、例えば、外部からの指令に基づいて、管理用ワークRAM217やIDプロパティRAM215の記憶内容を外部へ転送する等の処理を行う。なお、外部通信回路219から外部に転送される情報に対して暗号化処理を施してもよい。

#### 【0049】

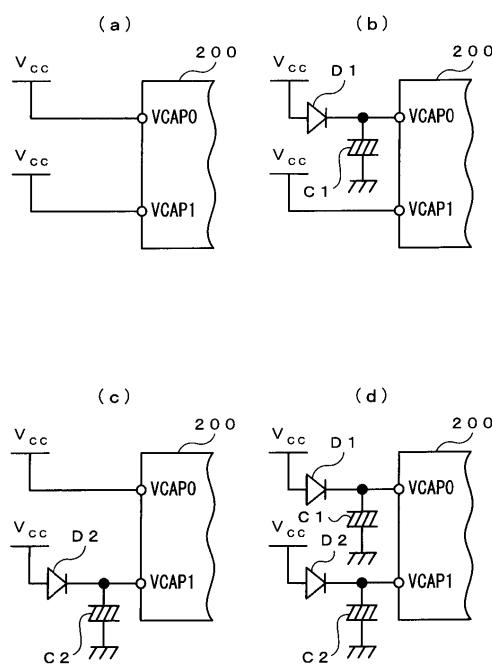

図7は、遊技用演算処理装置200の端子群に割り当てられた二つの電源バックアップ端子(VCAP0およびVCAP1)の使い方を示す図である。既述のとおり、VCAP0は遊技ブロック200Aに設けられたユーザワークRAM203の電源バックアップ端子であり、また、VCAP1は管理ブロック200Bに設けられたIDプロパティRAM215の電源バックアップ端子である。これら二つの端子VCAP0、VCAP1は、図示のとおり、四つのパターンのいずれかで使用することができる。

図7(a)は、二つの端子VCAP0、VCAP1に電源(以下Vcc)を加える使い方のパターンである。Vccは遊技機10の電源をオンにしている間、所定の電位を保持する直流電源である。このパターンで使用すると、遊技機10の電源をオンにしている間だけユーザワークRAM203とIDプロパティRAM215の双方に電源(Vcc)が供給されるので、ユーザワークRAM203とIDプロパティRAM215の電源バックアップを行わない使い方をすることができる。したがって、このパターンでは、遊技機10の電源をオンにしている間だけユーザワークRAM203とIDプロパティRAM215の記憶内容を保持することができ、言い換えれば、遊技機10の電源オフ時にユーザワークRAM203とIDプロパティRAM215の記憶内容を消去することができる。

#### 【0050】

図7(b)は、二つの端子VCAP0、VCAP1にVccを加えるとともに、VCAP0にコンデンサC1を接続する使い方のパターンである。このパターンで使用すると、遊技機10の電源をオフにした後もVCAP0を介してコンデンサC1の充電電圧がユ

10

20

30

40

50

ザワークRAM203に供給され続けるので、ユーザワークRAM203に対する電源バックアップを行うことができる。したがって、このパターンでは、遊技機10の電源オフ後もユーザワークRAM203の記憶内容を保持し続けることができるとともに、遊技機10の電源オフ時にIDプロパティRAM215の記憶内容を消去することができる。

図7(c)は、二つの端子VCAP0、VCAP1にVccを加えるとともに、VCA

P1にコンデンサC2を接続する使い方のパターンである。このパターンで使用すると、遊技機10の電源をオフにした後もVCAP1を介してコンデンサC2の充電電圧がID

プロパティRAM215に供給され続けるので、IDプロパティRAM215に対する電源

バックアップを行うことができる。したがって、このパターンでは、遊技機10の電源

オフ後もIDプロパティRAM215の記憶内容を保持し続けることができるとともに、

遊技機10の電源オフ時にユーザワークRAM203の記憶内容を消去することができる。

。

#### 【0051】

図7(d)は、二つの端子VCAP0、VCAP1にVccを加えるとともに、VCA

P0とVCAP1にそれぞれコンデンサC1、C2を接続する使い方のパターンである。

このパターンで使用すると、遊技機10の電源をオフにした後もVCA

P0、VCAP1を介してコンデンサC1、C2の充電電圧がユーザワークRAM203とID

プロパティRAM215に供給され続けるので、ユーザワークRAM203とID

プロパティRAM215の双方に対する電源バックアップを行うことができる。したがって、このパターン

では、遊技機10の電源オフ後もユーザワークRAM203とID

プロパティRAM215の記憶内容を保持し続けることができる。

#### 【0052】

コンデンサC1、C2は、Vccの電位に向けて電荷を蓄積(充電)するとともに、Vccのオフ後はその充電電荷を負荷(VCAP0、VCAP1)に供給(放電)するから、いわゆる二次電池として機能する。但し、これらC1、C2の代わりに一次電池(放電のみの電池)やその他の電池(例えば、燃料電池)を用いることも可能である。

なお、図7(b)～(d)において、VccとコンデンサC1(VccとコンデンサC2)

の間にダイオードD1(D2)を挿入することが望ましい。Vccを正電源とするなら、

ダイオードD1(D2)のアノードをVccに接続し、カソードをコンデンサC1

(C2)に接続する。電源オフ時にVccの電位が0V方向に低下しても、コンデンサC

1(C2)からVccへと電流が逆流せず、バックアップ端子VCAP0(VCAP1)

へのコンデンサC1(C2)からの電源供給を支障なく行うことができる。また、ダイオ

ードD1(D2)にはショットキー型のものを使用することが好ましい。ショットキー型

のダイオードは、アノード-カソード間の順方向電圧が小さく、ダイオードD1(D2)

の挿入に伴う電圧降下を低く抑えることができるからである。

#### 【0053】

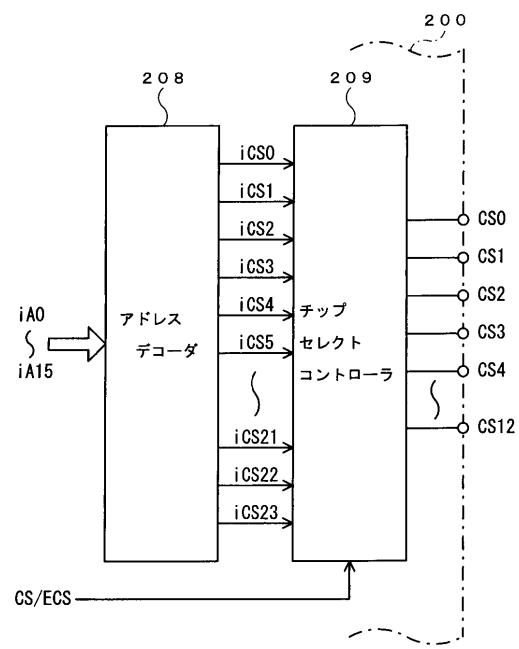

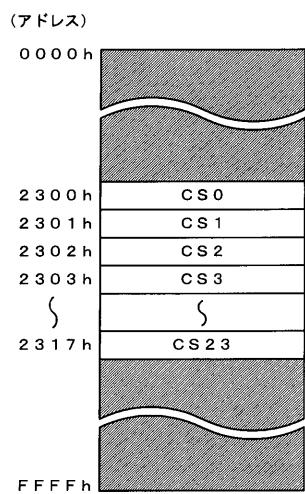

図8は遊技用演算処理装置200の要部構成図であり、チップセレクト信号CS0～CS12の発生部分を示す図である。既述のとおり、アドレスデコーダ208はCPUバス

210のアドレスバス上の情報(iA0からiA15までの16ビットのアドレス情報)

をフルデコードし、図9に示すように、16ビットで表現される0000hからFFFF

hまでのアドレス空間の所定番地に予め割り付けられた24個のI/Oアドレス(例えば

、2300h～2317hまでの24バイトのアドレス)のいずれかを検出すると、当該

I/Oアドレスに対応する一つのI/Oリソース選択用内部信号(iCS0～iCS23

のうちの一つ)をアクティブにする。例えば、アドレス2300hを検出すると、CS0

に対応するiCS0をアクティブにし、アドレス2301hを検出すると、CS1に対応

するiCS1をアクティブにし、……、アドレス2317hを検出すると、CS23に対

応するiCS23をアクティブにする。

#### 【0054】

また、既述のとおり、チップセレクトコントローラ209はアドレスデコーダ208から

の24個のI/Oリソース選択用の内部信号iCS0～iCS23と、CPUコア20

。

1からのモード指定信号CS/ECSに基づいて、13個のチップセレクト信号CS0～CS12の状態をコントロールする。例えば、CSモードの場合、iCS0がアクティブで入力すると、対応するチップセレクト信号CS0をアクティブにして出力し、iCS1がアクティブで入力すると、対応するチップセレクト信号CS1をアクティブにして出力し、……、iCS12がアクティブで入力すると、対応するチップセレクト信号CS12をアクティブにして出力する(CSモードの場合、iCS13～iCS23は未使用)。一方、ECSモードの場合、同様に、iCS0がアクティブで入力すると、対応するチップセレクト信号CS0をアクティブにして出力し、iCS1がアクティブで入力すると、対応するチップセレクト信号CS1をアクティブにして出力し、……、iCS7がアクティブで入力すると、対応するチップセレクト信号CS7をアクティブにして出力するが、iCS8からiCS23までについては、そのうちの一つのアクティブに対応させて、4つのチップセレクト信号CS8～CS11の組合せをコード化して出力するとともに、最後のチップセレクト信号CS12をアクティブ固定にして出力する。10

#### 【0055】

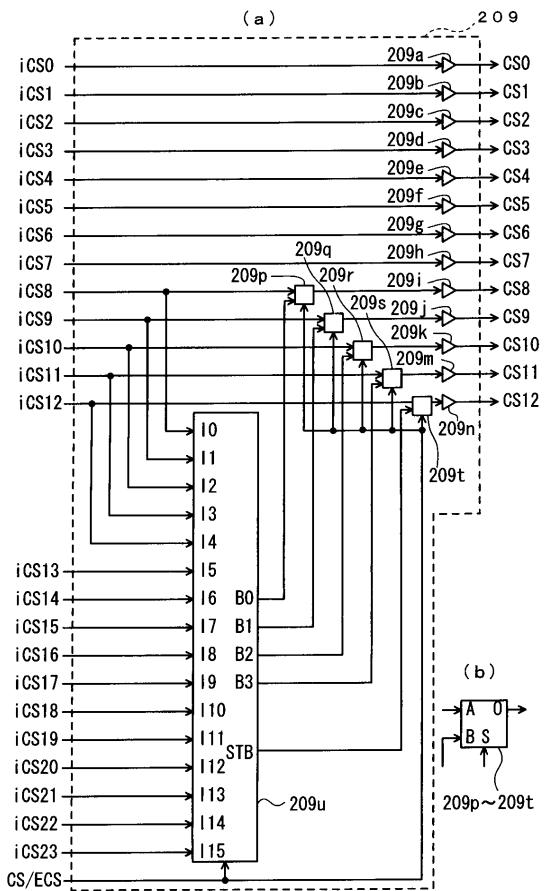

図10はチップセレクトコントローラ209の構成図である。13個のバッファ209a、209b、209c、209d、209e、209f、209g、209h、209i、209j、209k、209m、209nと、5個のセレクタ209p、209q、209r、209s、209tと、1個のコーダ209uとを備える。

13個のバッファ209a、209b、209c、209d、209e、209f、209g、209h、209i、209j、209k、209m、209nのうち図面の上から8個のバッファ209a、209b、209c、209d、209e、209f、209g、209hは、iCS0からiCS7までをスルーで通過させるが、残り5個のバッファ209i、209j、209k、209m、209nは、セレクタ209p、209q、209r、209s、209tの出力(O)に現れた信号を通過させる。20

セレクタ209p、209q、209r、209s、209tは、図中(b)にその拡大図を示すように、二つの入力A,B、一つの出力Oおよび選択入力Sの各端子を備え、選択入力Sを一の論理状態(CS/ECS信号がCSモードのときの状態)にすると入力Aに加えられた信号、すなわち、iCS8～iCS12を出力Oから取り出し、選択入力Sを他の論理状態(CS/ECS信号がECSモードのときの状態)にすると入力Bに加えられた信号(コーダ209uの出力信号；セレクタ209p、209q、209r、209sについてはB0～B3、セレクタ209tについてはSTB)を出力Oから取り出すという選択動作を行うものである。なお、STBは4ビットのコードB0～B3の状態確定を表す信号(いわゆるストローブ信号)である。30

#### 【0056】

コーダ209uはI0からI15までの16ビット入力のいずれか一つをアクティブにすると、そのアクティブのビット位置に対応した4ビットのコードB0～B3を発生(ただし、CS/ECS信号がECSモード指定の場合)するというものであり、ビットB0～B3の各々は4個のセレクタ209p、209q、209r、209sの入力Bに加えられている。また、コーダ209uからは、既述のとおり4ビットのコードB0～B3の確定状態を表すストローブ信号STBが取り出されており、このSTBは5個目のセレクタ209tの入力Bに与えられている。40

図11はコーダ209uの入出力真理値表であり、この真理値表はコーダ209uの16ビットの入力I0～I15の一つがアクティブになると、4ビットの出力B0～B3が「0000」～「1111」までのいずれかのビット配列にコード化されることを示している。

#### 【0057】

すなわち、I0(アドレスデコーダ208の出力iCS8)がアクティブになると、4ビットの出力B0～B3が「0000」のビット配列にコード化され、I1(アドレスデコーダ208の出力iCS9)がアクティブになると、4ビットの出力B0～B3が「0001」のビット配列にコード化され、I2(アドレスデコーダ208の出力iCS10)50

) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「0010」のビット配列にコード化され、I<sub>3</sub> (アドレスデコーダ208の出力 iCS11) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「0011」のビット配列にコード化され、I<sub>4</sub> (アドレスデコーダ208の出力 iCS12) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「0100」のビット配列にコード化され、I<sub>5</sub> (アドレスデコーダ208の出力 iCS13) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「0101」のビット配列にコード化され、I<sub>6</sub> (アドレスデコーダ208の出力 iCS14) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「0110」のビット配列にコード化され、I<sub>7</sub> (アドレスデコーダ208の出力 iCS15) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「0111」のビット配列にコード化され、I<sub>8</sub> (アドレスデコーダ208の出力 iCS16) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1000」のビット配列にコード化され、I<sub>9</sub> (アドレスデコーダ208の出力 iCS17) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1001」のビット配列にコード化され、I<sub>10</sub> (アドレスデコーダ208の出力 iCS18) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1010」のビット配列にコード化され、I<sub>11</sub> (アドレスデコーダ208の出力 iCS19) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1011」のビット配列にコード化され、I<sub>12</sub> (アドレスデコーダ208の出力 iCS20) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1100」のビット配列にコード化され、I<sub>13</sub> (アドレスデコーダ208の出力 iCS21) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1101」のビット配列にコード化され、I<sub>14</sub> (アドレスデコーダ208の出力 iCS22) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1110」のビット配列にコード化され、I<sub>15</sub> (アドレスデコーダ208の出力 iCS23) がアクティブになると、4ビットの出力 B<sub>0</sub> ~ B<sub>3</sub> が「1111」のビット配列にコード化されることを示している。

10

20

#### 【0058】

したがって、本実施の形態のチップセレクトコントローラ209によれば、CS / ECS信号をCSモードにすることにより、アドレスデコーダ208からの13個の信号(iCS0 ~ iCS12)をそのままスルーさせて13個のチップセレクト信号CS0 ~ CS12を外部出力できる一方、CS / ECS信号をECSモードにすることにより、アドレスデコーダ208からの13個の信号のうちの8個(iCS0 ~ iCS7)をそのままスルーセンサで8個のチップセレクト信号CS0 ~ CS7を外部出力できるとともに、残り16個の信号(iCS8 ~ iCS22)をコード化して2<sup>4</sup>個の状態を持つ4ビットの信号B<sub>0</sub> ~ B<sub>3</sub>を作り、この4ビットの信号を4個のチップセレクト信号CS8 ~ CS11として外部出力することができる。その結果、CSモードにおいては、最大13個の外部I/Oを制御でき、ECSモードにおいては、最大8個 + 2<sup>4</sup>個 = 24個の外部I/Oを制御できる。

30

なお、ECSモードで最大24個の外部I/Oを制御するためには、後述するように、チップセレクトコントローラ209から出力されるコード情報(すなわち、チップセレクト信号CS8 ~ CS11)をデコードし、2<sup>4</sup>個分の拡張チップセレクト信号CS8 ~ CS23を生成するための手段(図13の外部デコーダ330参照)を遊技用演算処理装置200の外部に設けなければならない。

40

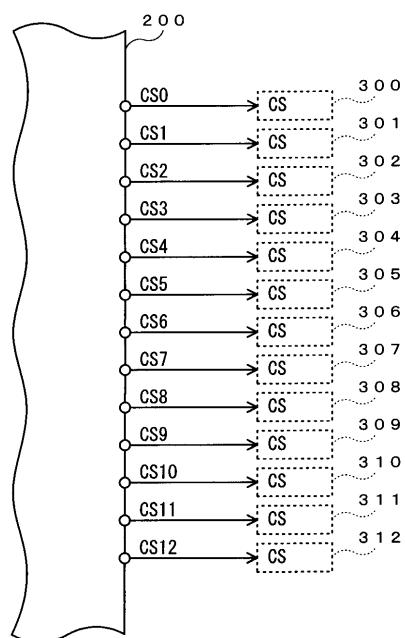

#### 【0059】

図12はCSモードにおけるチップセレクト信号CS0 ~ CS12の使用例である。上記のとおり、CSモードの場合、遊技用演算処理装置200から出力される13個のチップセレクト信号CS0 ~ CS12は各々個別の外部I/Oに対応し、最大13個までの任意の外部I/Oを制御できる。

今、第0から第12までの任意の外部I/O300 ~ 312を想定すると、各々の外部I/O300 ~ 312のチップセレクト端子(CS)に、13個のチップセレクト信号CS0 ~ CS12のそれぞれを入力させればよい。そして、遊技プログラム上で、例えば、アドレス2300h(図9参照)をコールしてWR信号またはRD信号をアクティブにす

50

れば、当該アドレス 2300h に対応づけられた特定のチップセレクト信号 (CS0) をアクティブにして第 0 の外部 I/O 300 へ信号を書き込み (WR 信号のアクティブ時) 、または、第 0 の外部 I/O 300 から信号を読み出す (RD 信号のアクティブ時) ことができる。

しかし、CS モードの場合、外部 I/O の制御数は、遊技用演算処理装置 200 から出力されるチップセレクト信号 CS0 ~ CS12 の数 (13 個) を越えることができないため、本実施の形態のように、15 個の外部 I/O (図 5 の入力インターフェース 113 の 5 個のポート 113a ~ 113e、出力インターフェース 114 の 9 個のポート 114a ~ 114i およびサウンドジェネレータ 115) を備えるものにあっては、ECS モードを使用する。

10

#### 【0060】

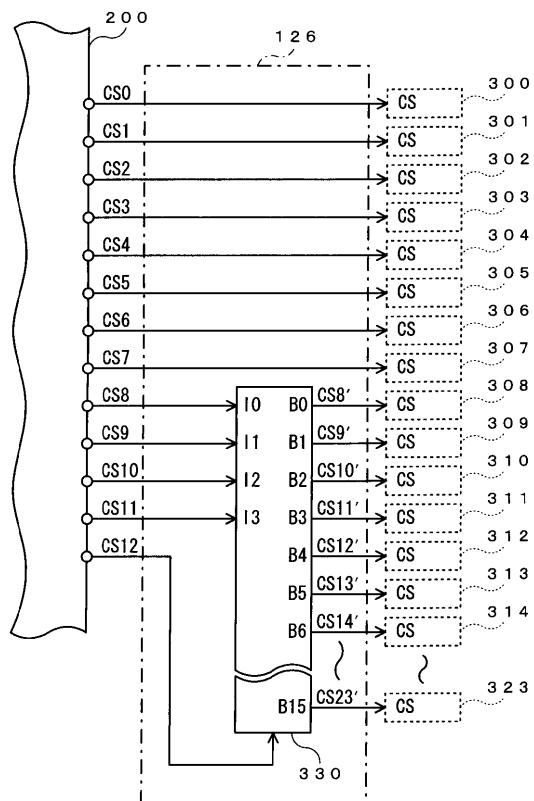

図 13 は ECS モードにおけるチップセレクト信号 CS0 ~ CS12 の使用例である。CS モードとの相違は、遊技用演算処理装置 200 から出力される 13 個のチップセレクト信号 CS0 ~ CS12 のうちの 4 個、すなわち、コード化された 4 個のチップセレクト信号 CS8 ~ CS11 を所定のストローブ信号 (CS12 ; 図) のタイミングでデコードし、 $2^4$  個の拡張チップセレクト信号 CS8 ~ CS23 を生成する外部デコーダ (発明の要旨に記載の再生手段に相当) 330 を含む信号拡張回路 126 を備えた点にある。

#### 【0061】

図 14 はデコーダ 330 の入出力真理値表であり、この真理値表は 4 ビット入力 I0 ~ I3 の組合せ (CS12 によって示された所定のタイミング (前記コーダ 209u の 4 ビット出力の確定タイミング) のときの組み合わせ) に応じて B0 から B15 までの 16 個の出力の一つをアクティブにすることを示している。

20

すなわち、4 ビット入力 (チップセレクト信号 CS8 ~ CS11) の組み合わせが「0000」の場合に、B0 (拡張チップセレクト信号 CS8 ) をアクティブにして出力し、同組み合わせが「0001」の場合に、B1 (拡張チップセレクト信号 CS9 ) をアクティブにして出力し、同組み合わせが「0010」の場合に、B2 (拡張チップセレクト信号 CS10 ) をアクティブにして出力し、同組み合わせが「0011」の場合に、B3 (拡張チップセレクト信号 CS11 ) をアクティブにして出力し、同組み合わせが「0100」の場合に、B4 (拡張チップセレクト信号 CS12 ) をアクティブにして出力し、同組み合わせが「0101」の場合に、B5 (拡張チップセレクト信号 CS13 ) をアクティブにして出力し、同組み合わせが「0110」の場合に、B6 (拡張チップセレクト信号 CS14 ) をアクティブにして出力し、同組み合わせが「0111」の場合に、B7 (拡張チップセレクト信号 CS15 ) をアクティブにして出力し、同組み合わせが「1000」の場合に、B8 (拡張チップセレクト信号 CS16 ) をアクティブにして出力し、同組み合わせが「1001」の場合に、B9 (拡張チップセレクト信号 CS17 ) をアクティブにして出力し、同組み合わせが「1010」の場合に、B10 (拡張チップセレクト信号 CS18 ) をアクティブにして出力し、同組み合わせが「1100」の場合に、B12 (拡張チップセレクト信号 CS20 ) をアクティブにして出力し、同組み合わせが「1101」の場合に、B13 (拡張チップセレクト信号 CS21 ) をアクティブにして出力し、同組み合わせが「1110」の場合に、B14 (拡張チップセレクト信号 CS22 ) をアクティブにして出力し、同組み合わせが「1111」の場合に、B15 (拡張チップセレクト信号 CS23 ) をアクティブにして出力することを示している。

30

【0062】

今、第 0 ~ 第 23 までの最大 24 個の外部 I/O 300 ~ 323 を想定する。一つの外部 I/O を制御する場合、遊技プログラム上で、アドレス 2300h からアドレス 2317h (図 9 参照) までのいずれかの番地をコールして WR 信号または RD 信号をアクティブにすればよい。例えば、アドレス 2300h をコールした場合はチップセレクト信号 CS0 がアクティブとなって第 0 の外部 I/O 300 が制御され、……、アドレス 2307h をコールした場合はチップセレクト信号 CS7 がアクティブとなって第 7 の外部 I/O

40

50

307が制御される。あるいは、アドレス2308hをコールした場合は外部デコーダ330から出力される拡張チップセレクト信号CS8がアクティブとなって第8の外部I/O308が制御され、……、アドレス2317hをコールした場合は外部デコーダ330から出力される拡張チップセレクト信号CS23がアクティブとなって第23の外部I/O323が制御される。

#### 【0063】

次に、作用を説明するが、始めに、遊技用演算処理装置200の正当性の判定に関する各部の動作を説明し、その後、遊技用演算処理装置200のシステムリセット動作等の説明を行い、そのシステムリセット動作の説明の最後に、本願発明のポイントであるチップセレクト動作(CSモードとECSモード)の説明を行うこととする。

10

#### <遊技用演算処理装置200の正当性の判定動作>

遊技用演算処理装置200の正当性の判定動作は、PJ1、PJ2、JR、JRsおよび遊技用演算処理装置200が相互に関連しあって行われる。

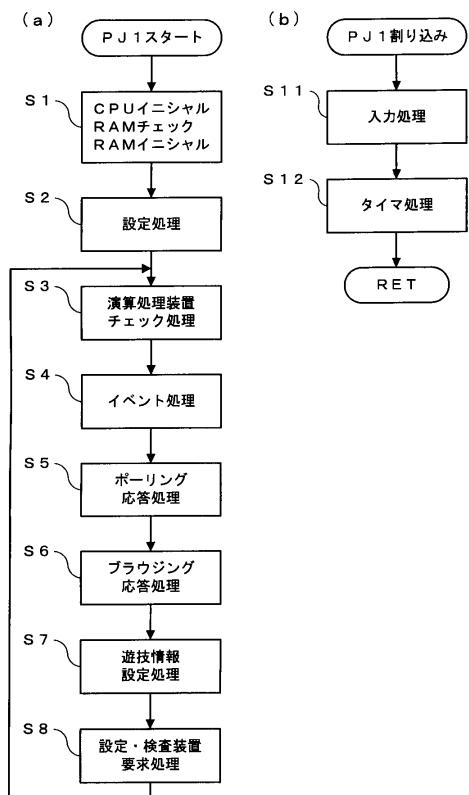

図15(a)、(b)はPJ1のメインルーチンおよび割り込みルーチンをそれぞれ示すフローチャートである。PJ1のメインルーチンは、PJ1の電源投入(パワーオン)時に開始される。PJ1がパワーオンすると、まずステップS1でCPU51のイニシャライズ、RAM53のチェックおよびイニシャライズを行う。これにより、CPU51が初期化され、システム内部のレジスタの設定処理、フラグのイニシャライズ等が行われるとともに、RAM53の正常判定処理、ワークエリアのイニシャライズ等が行われる。

#### 【0064】

20

次いで、ステップS2で設定処理を行う。これは、PJ1へ設定・検査装置23より遊技用演算処理装置200の固有IDと同一の照合用IDを設定するもので、ステップS1を経た後に、ステップS2にて設定処理を行っている。次いで、ステップS3で遊技用演算処理装置200のチェック処理を行う。これは、遊技用演算処理装置200の固有IDが正当であるか否かを判定するものである。すなわち、遊技用演算処理装置200には製造時に予め固有ID(遊技用演算処理装置200毎に異なるID)がセキュリティメモリ216に格納されており、セキュリティメモリ216の格納データ(固有ID等)がIDプロパティRAM215にコピーされるようになっている。そして、ホール1に遊技機10が納入された後、PJ1がIDプロパティRAM215の格納データを定期的に読み出し、設定・検査装置23より設定された照合用IDと比較することにより遊技用演算処理装置200の正当性を判定するようになっている(詳細な判定動作は後述のサブルーチンで説明する)。なお、メインルーチンにおける処理の内容は必要に応じて逐次後述のサブルーチンで詳述する。これは、以下のステップについても同様である。また、PJ1以外のその他の装置についても同様である。

30

#### 【0065】

次いで、ステップS4でイベント処理を行う。これは、遊技機10等(これには遊技機10および遊技設備装置も含まれる。以下同様)より出力される各信号およびPJ2より転送されてくる遊技情報を加工・記録する処理を行うとともに、遊技情報に状態変化があった場合に、その状態変化情報をJRおよびJRsに送信するものである(後述のサブルーチンで詳述)。

40

ここで、遊技機10等より出力される各信号およびPJ2より転送されてくる遊技情報を加工したものとしては、例えば時刻(時分:遊技情報を収集したときの発生時刻)、累計セーフ、累計アウト、累計特賞回数、累計確変回数、累計特賞中セーフ、累計特賞中アウト、累計確変中セーフ、累計確変中アウト、累計確変中スタート、累計スタート、累計カード売上、累計現金売上、最終スタート回数、打止回数、打止目標値、最終アウト玉数、金枠開放回数、木枠開放回数および電磁波異常回数等がある。また、遊技情報の状態変化を監視するステータスおよびその内容としては、特賞、確変、稼働中検出、自動打止、手動打止、アウト異常、セーフ異常、ベース異常、出過ぎ異常、入賞異常、特賞異常、演算処理異常(遊技用演算処理装置200の固有IDが異常のときに状態1となるビットである)、ノード異常(端末装置間の相互認証が異常のときに状態1となるビットであ

50

る。なお、相互認証は L O N プロトコルによって行われる)、金枠開、金枠開異常、木枠開、木枠開異常、電磁波異常、空皿検出、空皿検出異常およびコール等がある。

#### 【 0 0 6 6 】

次いで、ステップ S 5 で H C より遊技情報のポーリングに対する応答処理を行う。次いで、ステップ S 6 で H C もしくは C C より要求される所望遊技機 1 0 の遊技情報を取得したい場合に、その要求に対して応答するブラウジング応答処理を行う。次いで、ステップ S 7 で遊技情報設定処理を行う。これは、H C もしくは C C より設定される状態変化情報の監視用の設定処理を行うとともに、P J 1 は夜間も動作しているので、例えば H C より開店等の要求があった場合に、前日の遊技機情報等をクリアする処理を行うものである。

次いで、ステップ S 8 で設定・検査装置要求処理を行う。これは、設定・検査装置 2 3 よりのメモリ内容 ( R A M 5 3 : 作業メモリの内容 ) の要求指令、もしくは R O M 5 2 に格納されている基準遊技プログラムの要求指令等を遊技用演算処理装置 2 0 0 へ連絡したり、遊技用演算処理装置 2 0 0 より設定・検査装置 2 3 へ上記要求指令に対して応答する情報 ( メモリ内容、遊技プログラム ) を中継する処理を行うものである。なお、設定・検査装置 2 3 はホール 1 における当局の立入検査時のみならず、遊技機 1 0 の検定検査を行うときにも使用できる。

#### 【 0 0 6 7 】

ステップ S 8 を経ると、ステップ S 3 に戻って処理ループ ( ステップ S 3 ~ ステップ S 8 ) を繰り返す。P J 1 ( P J 2 も同様 ) および L O N 通信網 2 7 ( 島内ネットワーク 2 6 、ネットワーク中継装置 2 5 および店内ネットワーク 2 4 ) は夜間も動作しており、特に島内ネットワーク 2 6 に接続されるノード ( 端末装置 ) は夜間も遊技情報の状態変化を監視している。したがって、ステップ S 3 ~ ステップ S 8 の処理ループを繰り返すことにより、翌朝、開店前に各遊技情報を取得することで、不正を監視できる。また、夜間、通電している L O N 通信網 2 7 に外部通信装置 ( 例えば、F A X 装置等 ) を接続しておけば、不正が発生した時点で外部に不正発生という状況を送信することができ、不正に有効に対処することが可能になる。

#### 【 0 0 6 8 】

P J 1 の割り込みルーチンでは、図 1 5 ( b ) に示すように、ステップ S 1 1 で入力処理を行う。これは、P J 1 の入力インターフェース 5 9 にアミューズ通信信号、売上信号 ( カード、現金 ) 、補給球数信号、回収球数信号、特図回転信号、大当たり信号および確変信号の何れかの信号が入力された際に、その入力信号をトリガーとして割り込みがかかり、その入力された信号を保存しておく処理を行うものである。入力処理で保存した信号は P J 1 のメインルーチンの処理で使用される。次いで、ステップ S 1 2 でタイマ処理を行う。これにより、P J 1 において使用する各種のタイマが作成され、例えば、1 0 0 m s 等のタイマが作られる。ステップ S 1 2 を経ると、割り込みを終了する。

なお、P J 2 についても、図 1 5 ( a ) ( b ) に示す内容と同様の処理が行われるので、ここでの説明は省略する。但し、P J 2 は遊技機 1 0 および遊技設備装置より収集した状態変化情報 ( 例えば、金枠開放信号、空皿信号等 ) を P J 1 へ転送し、P J 1 より上位ノードの端末装置 ( 例えば、J R や J R s ) に転送してもらうとともに、発射停止要求に応答して遊技機 1 0 を不能動化する処理を行う点で P J 1 と相違する。

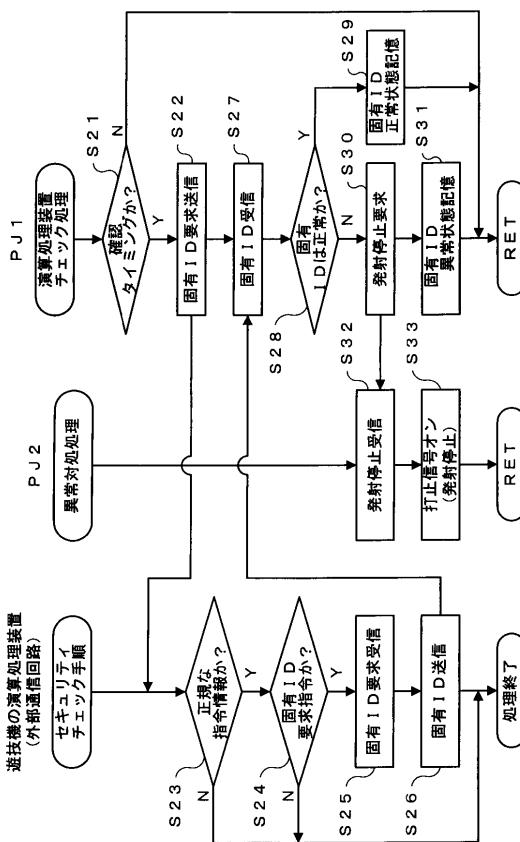

#### 【 0 0 6 9 】

次に、遊技用演算処理装置 2 0 0 のチェックに関するサブルーチンについて説明する。図 1 6 は遊技用演算処理装置チェックのサブルーチンを示すフローチャートである。遊技用演算処理装置 2 0 0 をチェックする過程では、遊技用演算処理装置 2 0 0 、P J 1 および P J 2 において関連する処理が行われる。

既述のとおり、遊技用演算処理装置 2 0 0 には製造時に予め固有 I D ( 遊技用演算処理装置 2 0 0 每に異なる I D ) がセキュリティメモリ 2 1 6 に格納されており、セキュリティメモリ 2 1 6 の格納データ ( 固有 I D 等 ) が I D プロパティ R A M 2 1 5 にコピーされるようになっている。そして、ホール 1 に遊技機 1 0 が納入された後、P J 1 が固有 I D に基づいて正当な遊技用演算処理装置 2 0 0 であるか否かを判断できるように、L O N 通

10

20

30

40

50

信綱 27 に設定・検査装置 23 を接続し、当該遊技用演算処理装置 200 に予め格納されている固有 ID と同一の情報（照合用 ID）を、当該遊技機 10 が接続される PJ1 へ設定する。PJ1 では所定間隔毎に遊技用演算処理装置 200 に固有 ID 読み出しコマンドを送信し、遊技用演算処理装置 200 はそれに応答すべく ID プロパティ RAM 215 にコピーされている固有 ID を含む情報を PJ1 へ送信し、PJ1 は受け取った情報に含まれている固有 ID を設定・検査装置 23 により設定された照合用 ID と比較することで、遊技用演算処理装置 200 の正当性を判断する。そして、特定の者（例えば、製造時に遊技用演算処理装置 200 に固有 ID を格納し、管理している者）しか知り得ない固有 ID が正当であれば、その正当な遊技用演算処理装置 200 に書き込まれている遊技プログラムは正当であると判断する。

10

#### 【0070】

図 16 に示すプログラムで遊技用演算処理装置 200 の正当性を判断する場合、まず、PJ1 のメインルーチンの遊技用演算処理装置チェック処理において、ステップ S21 で所定間隔毎の固有 ID の確認タイミング（例えば、1 秒毎）であるか否かを判別し、確認タイミングでなければ、今回のルーチンを終了してメインルーチンにリターンする。確認タイミングであれば、ステップ S22 に進んで当該 PJ1 に接続される遊技機 10 の遊技用演算処理装置 200 に対して固有 ID 要求（例えば、固有 ID 読み出しコマンド）を送信する。これは、PJ1 と対になっている（つまり PJ1 がチェック対象としている）遊技機 10 における遊技制御基板 41 に内蔵されている遊技用演算処理装置 200 に対して固有 ID を要求するものである。

20

#### 【0071】

遊技用演算処理装置 200 では、外部通信回路 219 が処理を行い、まずステップ S23 で PJ1 から送られてきた固有 ID 要求指令が正規な指令情報であるか否かを判別し、正規のものでなければルーチンを終了する。したがって、このときは無応答となる。無応答とすることによって、不正の防止を行う。例えば、何かしら応答すると、その応答を解析される懼れがあるので、無応答にしているものである。要は、不正なコマンドに対する応答動作はしないという構成である。なお、無応答に限らず、予め決められた一定の情報がけを返す（例えば、応答不能です）ようにしてもよい。このように無応答にすることにより、不正者による解析を著しく困難にすることができます。

30

#### 【0072】

一方、ステップ S23 で正規の指令情報である場合には、ステップ S24 に進んでそれが固有 ID の要求指令であるか否かを判別する。固有 ID の要求指令でなければルーチンを終了する。固有 ID の要求指令であれば、ステップ S25 で PJ1 より送信されてきた固有 ID 要求を受信し、ステップ S26 で ID プロパティ RAM 215 にコピーされている情報（固有 ID を含む情報）を PJ1 へ送信してルーチンを終了する。

#### 【0073】

固有 ID は遊技用演算処理装置 200 の正当性を判断する情報であり、予め遊技用演算処理装置 200 のセキュリティメモリ 216 に格納されている情報であるが、PJ1 への送信対象となる情報は、セキュリティメモリ 216 から ID プロパティ RAM 215 にコピーされた情報である。

40

なお、遊技用演算処理装置 200 における固有 ID 要求の受付けとその応答処理は CPU コア 201 の関与を受けることなく、管理ブロック 200B の動作のみで行われる。すなわち、管理ブロック 200B の外部通信回路 219 で固有 ID 要求を受付け、それに応答して ID プロパティ RAM 215 にコピーされている固有 ID を含む情報を外部に送信する。したがって、CPU コア 201 の動作に何ら影響を与えることなく、固有 ID 要求の受付けおよび応答処理を実行できる。このように、管理ブロック 200B が独立して固有 ID 要求に対する応答を行うことにより、例えば遊技プログラムの実行中（すなわち、遊技中）でも固有 ID に基づくセキュリティチェックを実現することが可能になるという利点がある。

#### 【0074】

50

P J 1 ではステップ S 2 7 で遊技用演算処理装置 2 0 0 の外部通信回路 2 1 9 から送信された固有 ID を受信し、ステップ S 2 8 で受信した固有 ID が正常であるか（正規なものであるか）否かを判別する。なお、チェック用の固有 ID（照合用 ID）は予め設定・検査装置 2 3 により P J 1 に対して設定（例えば、EEPROM 5 4 に格納）されている。照合用 ID は設定・検査装置 2 3 によって設定する例に限らず、例えば CC などによって設定してもよい。

#### 【0075】

ステップ S 2 8 の判別結果で、遊技用演算処理装置 2 0 0 から受信した固有 ID が正常であれば、ステップ S 2 9 で固有 ID 正常状態を記憶（例えば、状態変化情報のうち遊技用演算処理装置異常のビットを「0」にして正常なものとして記憶：図 1 7 に示すイベント処理のステップ S 4 4 で使用される）してメインルーチンにリターンする。一方、遊技用演算処理装置 2 0 0 の固有 ID が正常でない場合（例えば、偽造された遊技用演算処理装置である場合）には、ステップ S 3 0 に進んで固有 ID の異常にに対応した処置を行うべく、発射停止要求を P J 2 に送信するとともに、ステップ S 5 7 で固有 ID 異常状態を記憶（例えば、状態変化情報のうち遊技用演算処理装置異常のビットを「1」にして記憶：図 1 7 に示すイベント処理のステップ S 4 4 で使用される）してメインルーチンにリターンする。

#### 【0076】

P J 2 では、異常対処処理において、ステップ S 3 2 で P J 1 から発射停止要求を受信すると、ステップ S 3 3 に進んで異常の遊技機に対して打止信号をオンにして球の発射を停止し、メインルーチンにリターンする。これにより、P J 2 に接続されている該当する遊技機 1 0 における遊技球の発射が停止され、遊技機 1 0 の動作が不能動化される。したがって、遊技用演算処理装置 2 0 0 が偽造されて固有 ID が正規のものでない場合には、遊技を継続できなくなり、不正を防止することができる。なお、ステップ S 3 3 では異常の遊技機の発射をオフしているが、これに限らず、例えば、遊技機電源断信号を遊技機電源装置 8 1 へ出力して異常の遊技機の電源をオフしてもよい。要は、遊技を実行できなくすればよい。

#### 【0077】

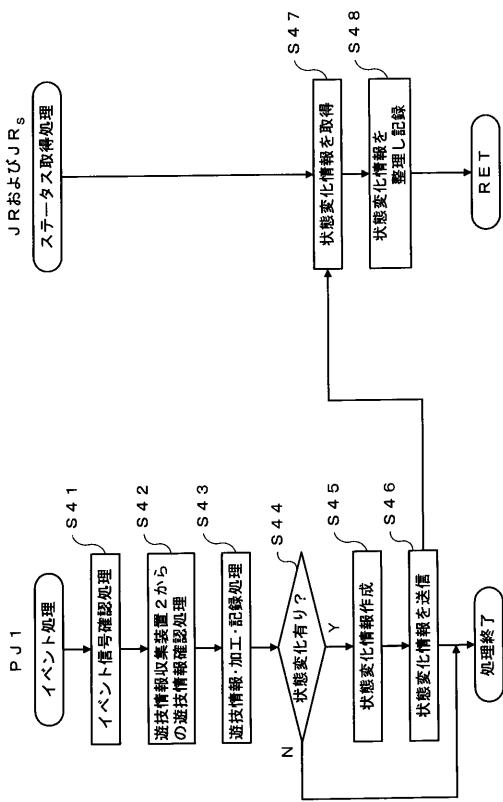

次に、P J 1 のイベント処理に関するサブルーチンについて説明する。図 1 7 はイベント処理のサブルーチンを示すフローチャートである。イベント処理の過程では、P J 1、JR および JR s において関連する処理が行われる。まず、P J 1 のメインルーチンのイベント処理において、ステップ S 4 1 でイベント信号確認処理を行う。これは、P J 1 が管理する遊技機 1 0 や遊技設備装置よりの遊技情報を取得するために、まずこれらの各端末からの信号（イベント信号）の入力の確認を行うものである。すなわち、P J 1 では、売上信号（カード、現金）、補給球数信号、回収球数信号、特図回転信号、大当たり信号および確変信号の入力の受け入れが可能であるが、これらの信号は常時入力されるものではなく、該当するイベント（例えば、プリペイドカードによる球貸しというイベントが発生すると、売上信号（カード）が入力される等）の発生に応じて入力されるものであり、ステップ S 4 1 ではイベントの発生があった場合に、当該イベントに対応した信号の受け入れを確認することになる。

#### 【0078】

次いで、ステップ S 4 2 で P J 2 より送信された遊技情報の確認処理を行い、ステップ S 4 3 で送信されたそれらの情報に基づいて遊技情報の加工・記録処理を行う。これにより、収集した情報が遊技情報に加工され、当日分の遊技情報が記録（例えば、RAM 5 3 に記録）される。次いで、ステップ S 4 4 で遊技情報の状態変化（ステータスの変化）があるか否かを判別し、変化がなければ今回のルーチンを終了してメインルーチンにリターンする。状態変化があれば、ステップ S 4 5 に進んで状態変化情報を作成する。これにより、ステータスの変化に応じた内容の状態変化情報が作成される。次いで、ステップ S 4 6 で作成した状態変化情報を JR および JR s に送信（通報）してルーチンを終了する。

J R ( および J R s ; 以下 J R で代表 ) では、P J 1 から状態変化情報の通報を受ける

10

20

30

40

50

と、ステップ S 4 7 でそれを取得し、ステップ S 4 8 で各遊技機 1 0 毎に状態変化情報を整理して記録しルーチンを終了する。その後、CC よりの要求（所定間隔毎のポーリング要求）を受けると、整理した状態変化情報を送信することになる。

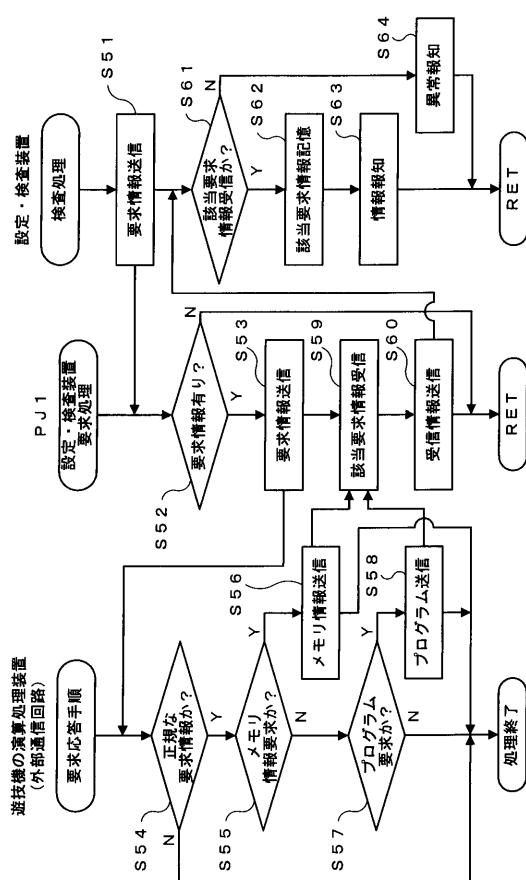

#### 【 0 0 7 9 】

次に、設定・検査装置 2 3 の検査処理に関するサブルーチンについて説明する。図 1 8 は検査処理のサブルーチンを示すフローチャートである。検査処理の過程では、設定・検査装置 2 3 、PJ 1 および遊技用演算処理装置 2 0 0 において関連する処理が行われる。これは、設定・検査装置 2 3 により PJ 1 を介して遊技用演算処理装置 2 0 0 ヘメモリ内容（ユーザワーク RAM 2 0 3 の記憶内容）の要求指令、もしくは、プログラム ROM 2 0 2 に格納されている遊技プログラムの要求指令に対して、遊技用演算処理装置 2 0 0 が PJ 1 を介して設定・検査装置 2 3 に当該要求指令に対する応答情報を連絡する処理である。この場合、設定・検査装置 2 3 を使用するのは当局の立入り検査時のみならず、遊技機 1 0 の検定検査の試験時にも使用される。そのため、設定・検査装置 2 3 はホール 1 に常時設置されていない。10

#### 【 0 0 8 0 】

図 1 8 に示すプログラムで検査処理を行う場合、まず、設定・検査装置 2 3 における検査処理ルーチンにおいて、ステップ S 5 1 で要求情報を送信する処理を行う。これは、設定・検査装置 2 3 が管理する所望の要求指令（内容はメモリ要求指令、遊技プログラム指令であり、要求は操作者による入力となる）を所望の遊技用演算処理装置 2 0 0 （すなわち、遊技機 1 0 ）に対応する PJ 1 へ送信し、ステップ S 6 1 で要求に対する応答を所定時間待つ。PJ 1 では、ステップ S 5 2 で要求情報があるか否かを判別し、要求情報がなければルーチンを終了する。要求情報があればステップ S 5 3 に進んで要求情報を下位ノードである遊技機 1 0 の遊技用演算処理装置 2 0 0 へ送信する。20

#### 【 0 0 8 1 】

遊技用演算処理装置 2 0 0 では、ステップ S 5 4 で PJ 1 より受け取った要求指令が正規な要求情報である否かを判別し、正規なものでない場合はルーチンを終了する。すなわち、不正な要求指令に対して無応答となる。正規なものである場合は、ステップ S 5 5 でその要求指令がメモリ情報（メモリ内容）の要求であるか否かを判別し、メモリ情報の要求の場合はステップ S 5 6 で現在のメモリ内容（ユーザワーク RAM 2 0 3 の内容）を PJ 1 を介して設定・検査装置 2 3 へ送信する。また、メモリ情報の要求でない場合は、ステップ S 5 7 で遊技プログラムの要求か否かを判別し、遊技プログラムの要求でない場合はルーチンを終了し、無応答とする。一方、遊技プログラムの要求である場合は、ステップ S 5 8 に進んで遊技プログラムを PJ 1 を介して設定・検査装置 2 3 へ送信し、ルーチンを終了する。30

#### 【 0 0 8 2 】

ステップ S 5 4 ～ステップ S 5 8 の処理は、遊技プログラムの実行（CPU コア 2 0 1 ）の処理の妨げにならないように独立して処理される。ただし、遊技プログラムの読み出しの場合は、遊技プログラムの動作停止状態が前提条件となり、バスモニタ回路 2 1 4 により CPU バス 2 1 0 を外部通信回路 2 1 9 が使用できるようにして、CPU バス 2 1 0 を利用してプログラム ROM 2 0 2 の内容を外部通信回路 2 1 9 より外部に転送可能にしている。一方、メモリ内容（ユーザワーク RAM 2 0 3 の情報）を外部に転送する場合は、遊技プログラム実行中においても可能なように、ユーザワーク RAM 2 0 3 を使用するようにして、CPU コア 2 0 1 側からも、外部通信回路 2 1 9 側からもアクセス可能である。40

PJ 1 では、ステップ S 5 8 で要求情報を送信した後、ステップ S 5 9 で遊技用演算処理装置 2 0 0 から当該要求に対する応答を受信し、ステップ S 6 0 で取得した情報を設定・検査装置 2 3 へ送信してルーチンを終了する。したがって、この場合の PJ 1 は遊技用演算処理装置 2 0 0 と設定・検査装置 2 3 との通信処理および設定・検査装置側 2 3 との通信処理を行う中継装置的な処理を行うものとなる。

#### 【 0 0 8 3 】

50

設定・検査装置23では、ステップS61で該当要求情報（すなわち、ステップS51で送信した要求に対する応答情報）を受信したか否の判別のため所定期間応答を待ち、所定期間を過ぎても応答がない場合はステップS64に進んで異常報知を行い、ルーチンを終了する。所定期間内に応答を受信した場合は、ステップS62で該当要求に対する応答情報（メモリ情報応答、あるいは遊技プログラム応答）を記憶し、ステップS63で情報を報知（例えば、表示）してルーチンを終了する。このようにして、設定・検査装置23を使用してホール1への立入り検査時の処理、あるいは遊技機10の検定検査の試験で遊技用演算処理装置200のメモリ内容の読み出し、あるいは遊技プログラムの読み出しが行われ、例えばメモリ内容に不審な情報がないかとか、遊技プログラムの真偽等が判断されることになる。

10

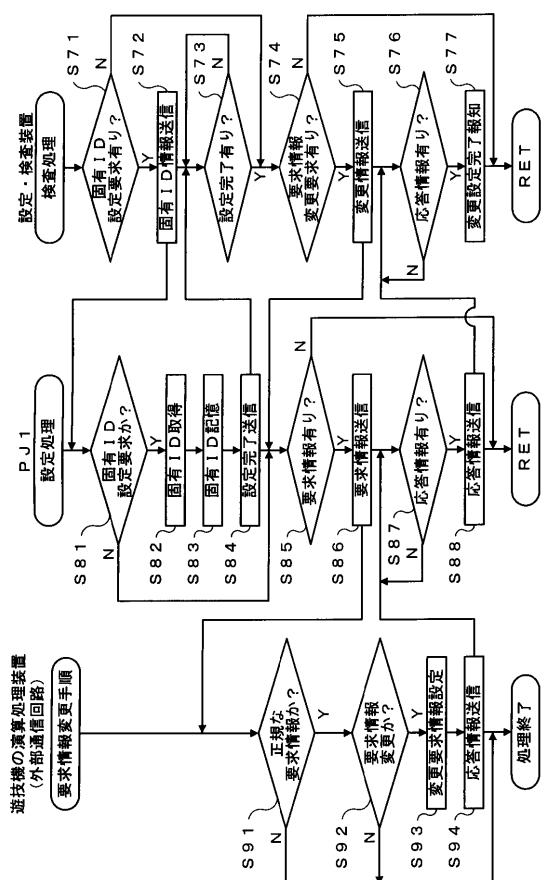

#### 【0084】

次に、設定・検査装置23の設定処理に関するサブルーチンについて説明する。図19は設定処理のサブルーチンを示すフローチャートである。設定処理の過程では、設定・検査装置23、PJ1および遊技用演算処理装置200において関連する処理が行われる。これは、ホール1に新たな遊技機10（すなわち、遊技用演算処理装置200）が納入されたときに、それを監視するPJ1へ設定・検査装置23より固有IDを設定する処理、および設定・検査装置23より遊技用演算処理装置200へPJ1を介して要求するコマンドを変更する処理である。この場合、設定・検査装置23をLON通信網27に接続して使用する。

20

#### 【0085】

PJ1への固有IDの設定を行う場合、まず、設定・検査装置23における設定処理ルーチンにおいて、ステップS71で固有ID設定要求があるか否かを判別する。固有ID設定要求は、操作者が設定・検査装置23（ノート型パーソナルコンピュータ等）に対して入力することによって行う。固有ID設定要求がある場合はステップS72で固有IDを含む情報をPJ1へ送信し、ステップS73で設定完了ありか否かを判別して待機する。設定・検査装置23の操作者は第3者機関等である。そして、新たな遊技機10に備えられている遊技用演算処理装置200の固有IDは、例えば管理表のようなものがあり、それに基づいてPJ1へ固有IDを設定していく。すなわち、PJ1毎に固有IDが設定される。

30

#### 【0086】

一方、PJ1では、ステップS81で設定・検査装置23から固有ID設定要求があるか否かを監視し、固有ID設定要求があれば、ステップS82に進んで設定・検査装置23から送信してきた固有IDを取得し、ステップS83で固有IDを照合用IDとして記憶（例えば、EEPROM54に記憶）する。次いで、ステップS84で固有IDの設定完了を設定・検査装置23へ送信し、ステップS85へ進む。設定・検査装置23では、前述したようにステップS73で設定完了ありか否かを判別して待機しており、PJ1から固有IDの設定完了が送信されると、ステップS73の判別結果がYESとなってステップS74に移行する。

40

#### 【0087】

遊技用演算処理装置200へ要求指令するコマンド変更の設定処理を行う場合は、まず、ステップS74で要求情報変更要求があるか否かを判別する。この要求情報変更要求についても、同様に第3者機関の操作者が入力を行う。要求情報変更要求がなければ今回のルーチンを終了する。要求情報変更要求がある場合、例えば、遊技プログラムの要求指令が「5A5A」であるとき、それを「5555」に変更したい場合とかには、ステップS75に進んで該当する要求指令の変更情報を入力（この場合は「5A5A」→変更→「5555」と入力）するとともに、その情報をPJ1へ送信する。これにより、要求指令の変更情報をPJ1を介して遊技用演算処理装置200へ送信されることになる（詳しくは後述）。なお、変更した要求指令を操作者が忘れてしまう場合もあることを考慮し、要求指令をデフォルト値に戻すこともできる（処理ステップは後述する）。

#### 【0088】

50

P J 1 では、ステップ S 8 6 で設定・検査装置 2 3 よりの要求情報があるか否かを判別し、要求情報がなければルーチンを終了する。要求情報があれば、ステップ S 8 6 に進んで要求情報を遊技用演算処理装置 2 0 0 へ送信し、ステップ S 8 7 でその応答を待つ。遊技用演算処理装置 2 0 0 では、ステップ S 9 1 で P J 1 から受け取った要求情報が正規な要求情報であるか否かを判別し、正規なものない場合はルーチンを終了する（無応答となる）。正規な要求情報である場合は、ステップ S 9 2 でその要求指令が要求情報の変更であるか否かを判別する。要求情報の変更でなければルーチンを終了する（無応答となる）。要求情報の変更であれば、ステップ S 9 3 に進んで変更要求情報設定処理を行う。これは、変更要求情報をセキュリティメモリ 2 1 6 に記憶するものである。セキュリティメモリ 2 1 6 には予め固有 I D などの情報が記憶されており、要求指令変更後は、それらの情報に併せて変更情報が記憶される。10

#### 【 0 0 8 9 】

次いで、ステップ S 9 4 で設定変更完了という応答情報を P J 1 へ送信してルーチンを終了する。上記ステップ S 9 1 ~ ステップ S 9 4 の処理は遊技用演算処理装置 2 0 0 における外部通信回路 2 1 9 およびセキュリティメモリ 2 1 6 によって実行され、C P U コア 2 0 1 が行うものではなく、遊技プログラムの動作にかかわらず実行可能である。すなわち、遊技プログラムの実行（C P U コア 2 0 1 ）を妨げないように独立して処理される。

P J 1 では、前述したようにステップ S 8 7 で遊技用演算処理装置 2 0 0 からの応答情報があるか否かを判別して待機しており、P J 1 から設定変更完了という応答情報が送信されると、ステップ S 8 7 の判別結果が Y E S となってステップ S 8 8 へ進む。ステップ S 8 8 では応答情報を設定・検査装置 2 3 へ送信してルーチンを終了する。したがって、この場合の P J 1 は遊技用演算処理装置 2 0 0 と設定・検査装置 2 3 との中継装置的な処理を行うものになる。設定・検査装置 2 3 では、ステップ S 7 6 で P J 1 を介して遊技用演算処理装置 2 0 0 から設定変更が完了したか否かの応答情報を待ち、応答があった場合はステップ S 7 7 に進んで操作者に設定変更完了の報知を行いルーチンを終了する。このようにして、設定・検査装置 2 3 を使用して遊技用演算処理装置 2 0 0 へ要求指令するコマンドの変更が行われる。20

#### 【 0 0 9 0 】

なお、変更した要求指令を操作者が忘れてしまった場合に、要求指令をデフォルト値に戻す処理は、設定・検査装置 2 3 のステップ S 7 5 で要求指令としてデフォルト値に戻すコマンドを入力し、それを、P J 1 を介して遊技用演算処理装置 2 0 0 に送信する。遊技用演算処理装置 2 0 0 はそのデフォルト値への変更指令を受け取ると、予め記憶されているデフォルト値に要求指令を変更し、設定変更完了の応答情報を P J 1 を介して設定・検査装置 2 3 に送信する。このように、要求指令の変更、デフォルト値の変更も含めて、上記ステップ S 7 5 ~ ステップ S 7 7 、ステップ S 8 5 ~ ステップ S 8 8 、ステップ S 9 1 ~ ステップ S 9 4 を実行することにより、要求指令をデフォルト値に戻す処理が行われる。30

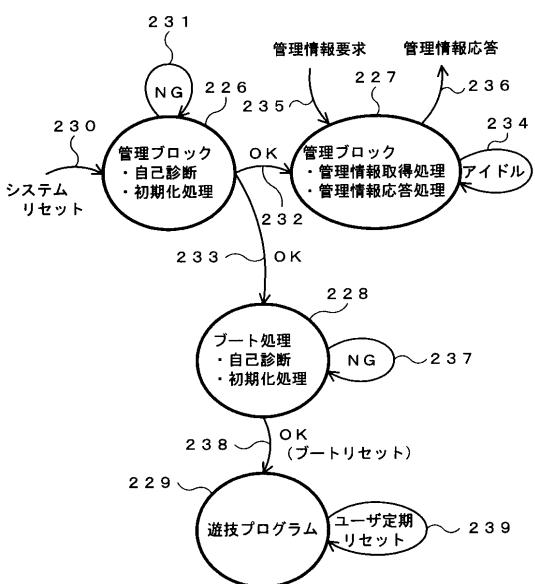

#### 【 0 0 9 1 】

##### < 遊技用演算処理装置 2 0 0 のシステムリセット動作 >

次に、遊技用演算処理装置 2 0 0 のシステムリセット動作について説明する。図 2 0 は、遊技用演算処理装置 2 0 0 の状態遷移図であり、2 2 6 ~ 2 2 9 は状態、2 3 0 ~ 2 3 9 は遷移線である。まず、電源投入によってシステムリセットが発生（遷移線 2 3 0 ）すると、管理ブロック 2 0 0 B で自己診断と初期化処理を実行し（状態 2 2 6 ）、その結果が N G （遷移線 2 3 1 ）であれば、所要の警報等を発生して待機状態に移行し、O K （遷移線 2 3 2 、 2 3 3 ）であれば、管理ブロック 2 0 0 B をアイドル状態（遷移線 2 3 4 : 管理情報要求の待ち受け状態）にするとともに、ブート R O M 2 1 2 に格納されているブートプログラムを実行する（状態 2 2 8 ）。

そして、ブート結果が N G （遷移線 2 3 7 ）であれば、所要の警報等を発生して待機状態に移行し、O K （遷移線 2 3 8 ）であれば、ブートリセット（遊技プログラムのスタートアドレス発生）を発生してプログラム R O M 2 0 2 に格納されている遊技プログラムを40

実行し（状態 229）、以降、ユーザ定期リセットが発生（遷移線 239）する度に遊技プログラムを繰り返す。なお、遷移線 235 は、外部装置である PJ1 からの管理情報要求指令を表し、遷移線 236 は PJ1 への管理情報応答を表す。

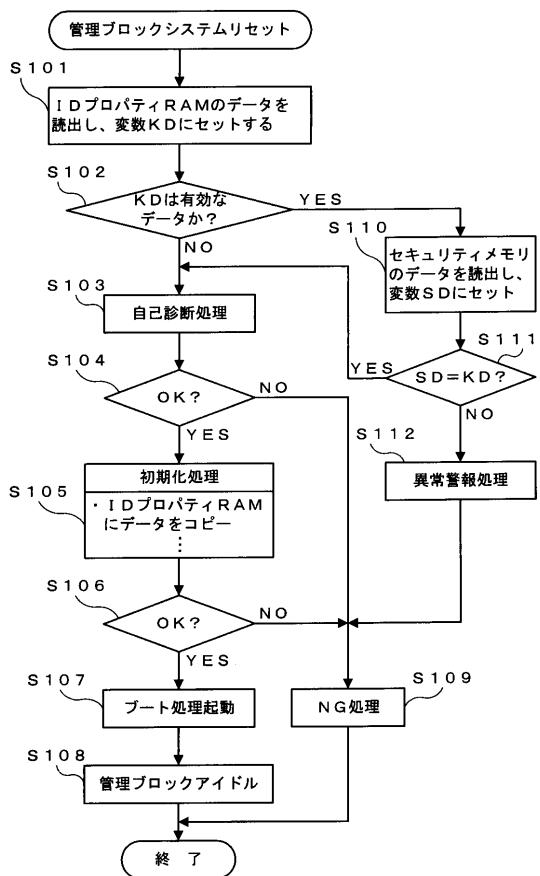

#### 【0092】

図 21 は、図 20 の状態 226 で実行される管理ロックシステムリセット動作のフローチャートである。このフローチャートにおいて、システムリセットが発生すると、まず、ステップ S101 で ID プロパティ RAM215 の記憶内容を変数 KD にセットし、ステップ S102 で変数 KD に有効なデータ（有意データ）が格納されている否かを調べる。今、ID プロパティ RAM215 が電源バックアップされていない場合、すなわち、V CAP1 にコンデンサ C2 が接続されていない場合（図 7 (a) または図 7 (b) 参照）を想定すると、システムリセット直後の ID プロパティ RAM215 の記憶内容は消去されて“不定”となっているから、この記憶内容をセットした変数 KD のデータもまた不定となり、結局、ステップ S102 の判定結果は“NO”となる。一方、ID プロパティ RAM215 が電源バックアップされている場合、すなわち、V CAP1 にコンデンサ C2 が接続されている場合（図 7 (c) または図 7 (d) 参照）を想定すると、システムリセット直後の ID プロパティ RAM215 の記憶内容は、固有 ID を含む有意データになっているから、この記憶内容をセットした変数 KD のデータもまた有意データとなり、結局、ステップ S102 の判定結果は“YES”となる。したがって、ステップ S102 における判定動作は、ID プロパティ RAM215 の電源バックアップの有無を判定する動作であるということもできる。

10

20

#### 【0093】

ステップ S102 の判定結果が“YES”的の場合、すなわち、ID プロパティ RAM215 の電源バックアップ有が判定された場合、ステップ S110 でセキュリティメモリ 216 の記憶内容を読み出して、それを変数 SD にセットし、ステップ S111 で二つの変数 KD、SD の内容一致を判定する。この判定動作は、電源バックアップされた ID プロパティ RAM215 の記憶内容と、この ID プロパティ RAM215 の記憶内容のコピー元であるセキュリティメモリ 216 の記憶内容との一致を判定することに相当する。そして、この判定結果が“NO”となった場合は、電源バックアップ中の ID プロパティ RAM215 の記憶内容が何らかの原因で変化（例えば、ビット化け）したことを意味し、かかる記憶内容の変化は不正な行為に起因することも有り得るから、ステップ S112 で異常警報処理を行った後、ステップ S109 で NG 处理（図 20 の状態 231）を行い、フローチャートを終了する。異常警報処理としては、例えば、ランプ等による報知表示、電子音や音声合成音等による報知音出力、異常を示す信号の外部出力等がある。特に、異常を示す信号の外部出力をを行う場合、この信号を利用してポケベルの呼び出しや E-mail の送信等を実行でき、在宅中や外出中の管理者等に遅滞なく異常を通報できるので好ましい。なお、ステップ S109 の NG 处理においては、正当な手続（例えば、所定の認証コードの入力や所定のスイッチ操作）によって異常状態の解除が行われるという条件の下に、自動的に、管理ロック 200B のセキュリティメモリ 216 から ID プロパティ RAM215 へのデータコピーを実行し、その後、正常な状態と同様に起動を開始するようにしてもよい。このようにすると、ノイズ等による突発的な異常状態が発生しても、緊急避難的に起動を開始することができる。

30

40

#### 【0094】

他方、ステップ S111 の判定結果が YES の場合、すなわち、二つの変数 KD、SD の内容が一致した場合は、電源バックアップ中の ID プロパティ RAM215 の記憶内容が何ら変化しておらず、セキュリティメモリ 216 の記憶内容と一致しているので、ステップ S103 に進んで、管理ロック 200B の自己診断処理を行い、その自己診断結果が OK（ステップ S104 の YES 判定）であれば、ステップ S105 で管理ロック 200B の初期化処理を実行し、初期化処理の結果が OK（ステップ S106 の YES 判定）であれば、ステップ 107 でブート起動（図 20 の状態 228）を行い、ステップ S108 で管理ロック 200B のアイドル（図 20 の遷移線 234）に移行した後、フロー

50

チャートを終了する。

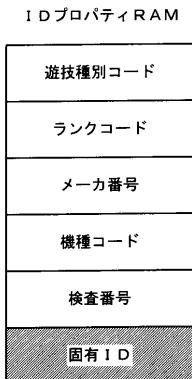

**【0095】**

ステップS105における管理ブロック200Bの初期化処理では、IDプロパティRAM215へのデータコピーが行われる。データのコピー元は管理ブロック200Bのセキュリティメモリ216である。図22はセキュリティメモリ216からIDプロパティRAM215へのデータコピーの概念図であり、この図では、セキュリティメモリ216からIDプロパティRAM215に、遊技種別コード、ランクコード、メーカ番号、機種コード、検査番号および固有IDの各情報がコピーされている。

**【0096】**

<チップセレクト動作：CSモード / ECSモード>

10

ここで、上記ステップS107におけるブート処理起動においては、ブートROM212に格納されたブートプログラムをCPUコア201で実行し、CPUコア201の動作環境を始めとする各種の初期化処理を行うが、その初期化処理の一つにCS/ECSモードの指定がある。CS/ECSモードの指定は拡張チップセレクト信号CS8～CS23を使用するかどうかを指定するものであり、本実施の形態のように13個を越える外部I/Oを有するシステムの場合はECSモードを指定し、13個以内の外部I/Oを有する他のシステムの場合はCSモードを指定する。

**【0097】**

すなわち、CSモードを指定したときと、ECSモードを指定したときの外部I/Oのアドレス割り当てマップは、図23のように表すことができる。図23において、2300hから2317hまでのアドレスは、それぞれ外部I/Oの割り当て候補アドレスであり、CPUコア201で実行されるプログラム上で当該アドレスの一つをコールすると、その右側に位置するチップセレクト信号がアクティブになることを表している。

20

図からも理解されるように、CSモードのときに2300h～230Chのいずれかをコールすると、13個のチップセレクト信号CS0～CS12のいずれか一つがアクティブになり、そのチップセレクト信号を用いて一つの外部I/Oを制御することができる。CSモードのときの外部I/O制御数は最大13個であり、この数はチップセレクト信号CS0～CS12の数に等しい。

**【0098】**

一方、ECSモードにしたときに2300h～2317hのいずれかをコールすると、24個のチップセレクト信号CS0～CS23のいずれか一つがアクティブになり、そのチップセレクト信号を用いて一つの外部I/Oを制御することができる。ECSモードのときの外部I/O制御数は最大24個であり、この数は拡張チップセレクト信号を含むすべてのチップセレクト信号CS0～CS23の数に等しい。

30

ECSモードにおいて、遊技用演算処理装置200から取り出されるチップセレクト信号数はCS0～CS12までの13個であり、この数はCSモードのときの数と同じである。CSモードとの相違は、遊技用演算処理装置200から取り出されるチップセレクト信号CS0～CS12のうち4個のチップセレクト信号CS8～CS11をコード化することにより、 $2^4$ 個 = 16個の情報を持たせている点にある。

**【0099】**

40

このため、遊技用演算処理装置200の外側にチップセレクト信号CS8～CS11のデコード手段（図13の外部デコーダ330参照）を設けることにより、コード化された4個のチップセレクト信号CS8～CS11をデコードして16個の拡張チップセレクト信号CS8～CS23を生成することができる。

**【0100】**

以上のとおり、本実施の形態によれば、コード化されない8個のチップセレクト信号CS0～CS7と、16個の拡張チップセレクト信号CS8～CS23とを合わせて合計24個のチップセレクト信号CS0～CS23を利用することができ、13個を越える多量の外部I/Oを有する本実施の形態のようなシステムにも支障なく適用することができる。

50

さらに、本実施の形態によれば、CSモードとECSモードを切り換えるだけで、チップセレクト信号の利用形態（すなわち、13個以内の外部I/Oへの利用形態と13個を越える外部I/Oへの利用形態）を簡単に変更することができるうえ、遊技用演算処理装置200のチップセレクト信号端子の数についても、CSモードやECSモードに関わらず、少ない方の数（13個）に留め置くことができ、パッケージピン数の増加問題も解消できるという格別の効果が得られる。

#### 【0101】

なお、実施の形態におけるCSモード時のチップセレクト信号数N（N=13）およびECSモード時における拡張チップセレクト信号を含むチップセレクト信号数M（M=24）は説明上の便宜値であることはもちろんである。 10

#### 【0102】

本発明の実施の形態は、上記例示に限定されず、以下に述べるような各種の変形実施が可能である。

(a) 遊技装置としての遊技機はパチンコ遊技機に限らず、スロットルマシンであってもよい。

(b) 本発明における遊技装置はパチンコ遊技機でなく、例えば映像式ゲーム機のようなものにも適用できる。

(c) 遊技装置としての遊技機は実球式に限るものではなく、封入球式の遊技機であってもよい。また、本発明の適用対象となる遊技装置としての遊技機は、どのような種類の遊技機でも本発明を適用できる。例えば、磁気カードで玉貸しを行うもの、ICカードで玉貸しを行う等の遊技機のタイプに限定されずに、本発明を適用することができる。 20

(d) 遊技店内の通信網は遊技情報等の転送が可能なものであれば、光通信方式、LAN、LON、無線方式、赤外線方式、有線方式等の種類に限らず、どのようなネットワークシステムを使用してもよい。

#### 【図面の簡単な説明】

#### 【0103】

【図1】遊技店の全体構成を示すブロック図である。

【図2】PJ1（遊技情報収集装置1）のブロック図である。

【図3】PJ2（遊技情報収集装置2）のブロック図である。

【図4】遊技機の正面図である。 30

【図5】遊技制御装置の構成を示すブロック図である。

【図6】遊技用演算処理装置の構成を示すブロック図である。

【図7】遊技用演算処理装置の端子群に割り当てられた二つの電源バックアップ端子（VCAP0およびVCAP1）の使い方を示す図である。

【図8】アドレスデコーダおよびチップセレクトコントロールを含む遊技用演算処理装置の要部構成図である。

【図9】外部I/Oのアドレス割り付概念図である。

【図10】チップセレクトコントローラの具体的な構成図である。

【図11】チップセレクトコントローラに含まれるコーダの入出力真理値を示す図である。 40

【図12】CSモードにおける13個のチップセレクト信号の利用状態図である。

【図13】ECSモードにおける24個のチップセレクト信号の利用状態図である。

【図14】ECSモードにおいて必要となる外部デコーダの入出力真理値を示す図である。

【図15】PJ1（遊技情報収集装置1）のプログラムを示すフローチャートである。

【図16】遊技用演算処理装置のチェック処理サブルーチンプログラムを示すフローチャートである。

【図17】イベント処理サブルーチンプログラムを示すフローチャートである。

【図18】設定・検査処理のサブルーチンプログラムを示すフローチャートである。

【図19】設定処理のサブルーチンプログラムを示すフローチャートである。 50

【図20】遊技用演算処理装置の状態遷移図である。

【図21】管理プロックのシステムリセット動作のフローチャートである。

【図22】セキュリティメモリからIDプロパティRAMへのデータコピーの概念図である。

【図23】CSモードおよびECSモードにおける外部I/Oのアドレス割り当てマップを示す図である。

#### 【符号の説明】

#### 【0104】

CS0 ~ CS12 チップセレクト信号(選択信号)

iCS0 ~ iCS23 (内部選択信号)

10

10 遊技機

113a ~ 113e ポート(外部I/O)

114a ~ 114i ポート(外部I/O)

115 サウンドジェネレータ(外部I/O)

200 遊技用演算処理装置

201 CPUコア(遊技制御手段)

208 アドレスデコーダ(信号発生手段、第1信号発生手段)

209 チップセレクトコントローラ(信号発生手段、第2信号発生手段、第3信号発生手段、選択手段)

330 外部デコーダ(再生手段)

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

| 入力            | 出力 |    |    |    |

|---------------|----|----|----|----|

|               | B3 | B2 | B1 | B0 |

| I 0 (iCS 8)   | 0  | 0  | 0  | 0  |

| I 1 (iCS 9)   | 0  | 0  | 0  | 1  |

| I 2 (iCS 10)  | 0  | 0  | 1  | 0  |

| I 3 (iCS 11)  | 0  | 0  | 1  | 1  |

| I 4 (iCS 12)  | 0  | 1  | 0  | 0  |

| I 5 (iCS 13)  | 0  | 1  | 0  | 1  |

| I 6 (iCS 14)  | 0  | 1  | 1  | 0  |

| I 7 (iCS 15)  | 0  | 1  | 1  | 1  |

| I 8 (iCS 16)  | 1  | 0  | 0  | 0  |

| I 9 (iCS 17)  | 1  | 0  | 0  | 1  |

| I 10 (iCS 18) | 1  | 0  | 1  | 0  |

| I 11 (iCS 19) | 1  | 0  | 1  | 1  |

| I 12 (iCS 20) | 1  | 1  | 0  | 0  |

| I 13 (iCS 21) | 1  | 1  | 0  | 1  |

| I 14 (iCS 22) | 1  | 1  | 1  | 0  |

| I 15 (iCS 23) | 1  | 1  | 1  | 1  |

【図12】

【図13】

【図14】

| 入力 | 出力  |     |     |     |               |

|----|-----|-----|-----|-----|---------------|

|    | I 3 | I 2 | I 1 | I 0 | 出力            |

| 0  | 0   | 0   | 0   | 0   | B 0 (CS 8')   |

| 0  | 0   | 0   | 1   | 1   | B 1 (CS 9')   |

| 0  | 0   | 1   | 0   | 0   | B 2 (CS 10')  |

| 0  | 0   | 1   | 1   | 1   | B 3 (CS 11')  |

| 0  | 1   | 0   | 0   | 0   | B 4 (CS 12')  |

| 0  | 1   | 0   | 1   | 1   | B 5 (CS 13')  |

| 0  | 1   | 1   | 0   | 0   | B 6 (CS 14')  |

| 0  | 1   | 1   | 1   | 1   | B 7 (CS 15')  |

| 1  | 0   | 0   | 0   | 0   | B 8 (CS 16')  |

| 1  | 0   | 0   | 1   | 1   | B 9 (CS 17')  |

| 1  | 0   | 1   | 0   | 0   | B 10 (CS 18') |

| 1  | 0   | 1   | 1   | 1   | B 11 (CS 19') |

| 1  | 1   | 0   | 0   | 0   | B 12 (CS 20') |

| 1  | 1   | 0   | 1   | 1   | B 13 (CS 21') |

| 1  | 1   | 1   | 0   | 0   | B 14 (CS 22') |

| 1  | 1   | 1   | 1   | 1   | B 15 (CS 23') |

【図15】

【 図 1 6 】

【 17 】

【 18 】

【図19】

【図20】

【図21】

コピー

【図23】

| アドレス  | CSモード  | ECSモード         |

|-------|--------|----------------|

| 2300h | CS 0   | CS 0           |

| 2301h | CS 1   | CS 1           |

| 2302h | CS 2   | CS 2           |

| 2303h | CS 3   | CS 3           |

| 2304h | CS 4   | CS 4           |

| 2305h | CS 5   | CS 5           |

| 2306h | CS 6   | CS 6           |

| 2307h | CS 7   | CS 7           |

| 2308h | CS 8   | CS 8 (CS 8')   |

| 2309h | CS 9   | CS 9 (CS 9')   |

| 230Ah | CS 10  | CS 10 (CS 10') |

| 230Bh | CS 11  | CS 11 (CS 11') |

| 230Ch | CS 12  | CS 12 (CS 12') |

| 230Dh | (使用不可) | CS 13 (CS 13') |

| 230Eh |        | CS 14 (CS 14') |

| 230Fh |        | CS 15 (CS 15') |

| 2310h |        | CS 16 (CS 16') |

| 2311h |        | CS 17 (CS 17') |

| 2312h |        | CS 18 (CS 18') |

| 2313h |        | CS 19 (CS 19') |

| 2314h |        | CS 20 (CS 20') |

| 2315h |        | CS 21 (CS 21') |

| 2316h |        | CS 22 (CS 22') |

| 2317h |        | CS 23 (CS 23') |

---

フロントページの続き

(56)参考文献 特開2009-082733(JP,A)

特開平09-234272(JP,A)

特開平11-126179(JP,A)

特開平11-104340(JP,A)

(58)調査した分野(Int.Cl., DB名)

A 6 3 F 7 / 0 2