(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4207912号

(P4207912)

(45) 発行日 平成21年1月14日(2009.1.14)

(24) 登録日 平成20年10月31日(2008.10.31)

(51) Int.Cl.

F 1

G06F 13/38 (2006.01)

G06F 13/36 (2006.01)G06F 13/38 350

G06F 13/36 320B

請求項の数 5 (全 24 頁)

(21) 出願番号 特願2005-86187 (P2005-86187)

(22) 出願日 平成17年3月24日 (2005.3.24)

(65) 公開番号 特開2006-268483 (P2006-268483A)

(43) 公開日 平成18年10月5日 (2006.10.5)

審査請求日 平成17年9月29日 (2005.9.29)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100124626

弁理士 榎並 智和

(74) 代理人 100124682

弁理士 黒田 泰

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100090387

弁理士 布施 行夫

(74) 代理人 100090398

弁理士 大渕 美千栄

最終頁に続く

(54) 【発明の名称】データ転送制御装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

データ転送を制御するデータ転送制御装置であつて、

1つのデータ単位がKビット (Kは2以上の整数)であり前記Kがそのデータフォーマットにより異なるデータが、インターフェースバスに接続されるデバイスから前記インターフェースバスを介して入力されるインターフェース回路と、

シリアルバスを介して送信するパケットの生成を行うリンクコントローラとを含み、

前記リンクコントローラは、

Kビットの前記データに対してLビット (Lは0以上の整数)のダミーデータを付加することで得られる (K+L)ビットのデータが、M個 (Mは1以上の整数)ずつ集まつた (N×I)バイト (N、Iは1以上の整数)のパック化データを生成するデータフォーマッタと、

前記M、Nを設定するための設定情報を記憶する内部レジスタと、

前記データのビット数のカウント処理を行うビットカウンタと、

前記データのバイト数のカウント処理を行うバイトカウンタと、

前記シリアルバスを介して送信するパケットとして、前記パック化データがデータフィールドに挿入されるパケットを生成するパケット生成回路とを含み、

前記データフォーマッタは、

前記ビットカウンタからのビット数のカウント値と前記バイトカウンタからのバイト数のカウント値と前記内部レジスタの前記設定情報とに基づいてデコード処理を行って、前

記ダミーデータを挿入するビット位置を決定し、

前記インターフェースバスに接続される前記デバイスによりその値が決定される前記Kに応じて、前記L及びMが可変に設定される前記パック化データであり、

K = 6、 I = 1 である場合には L = 0、 M = 4、 N = 3 となり、或いは

K = 7、 I = 1 である場合には L = 1、 M = 2、 N = 2 となり、或いは

K = 8、 I = 1 である場合には L = 0、 M = 2、 N = 2 となり、或いは

K = 10、 I = 1 である場合には L = 2、 M = 2、 N = 3 となり、或いは

K = 12、 I = 1 である場合には L = 0、 M = 2、 N = 3 となり、或いは

K = 16、 I = 1 である場合には L = 0、 M = 1、 N = 2 となり、或いは

K = 24、 I = 1 である場合には L = 0、 M = 1、 N = 3 となるパック化データを生成することを特徴とするデータ転送制御装置。 10

#### 【請求項2】

データ転送を制御するデータ転送制御装置であって、

1つのデータ単位がKビット (Kは2以上の整数) であり前記Kがそのデータフォーマットにより異なるデータが、インターフェースバスに接続されるデバイスから前記インターフェースバスを介して入力されるインターフェース回路と、

シリアルバスを介して送信するパケットの生成を行うリンクコントローラとを含み、前記リンクコントローラは、

Kビットの前記データに対してLビット (Lは0以上の整数) のダミーデータを付加することで得られる (K+L) ビットのデータが、M個 (Mは1以上の整数) ずつ集まつた (N×I) バイト (N、Iは1以上の整数) のパック化データ (但しK=10の場合には (K+L) ビットのデータが2個とKビットのデータが1個ずつ集まつたパック化データ) を生成するデータフォーマッタと、 20

前記M、Nを設定するための設定情報を記憶する内部レジスタと、

前記データのビット数のカウント処理を行うビットカウンタと、

前記データのバイト数のカウント処理を行うバイトカウンタと、

前記シリアルバスを介して送信するパケットとして、前記パック化データがデータフィールドに挿入されるパケットを生成するパケット生成回路とを含み、

前記データフォーマッタは、

前記ビットカウンタからのビット数のカウント値と前記バイトカウンタからのバイト数のカウント値と前記内部レジスタの前記設定情報とに基づいてデコード処理を行って、前記ダミーデータを挿入するビット位置を決定し、 30

前記インターフェースバスに接続される前記デバイスによりその値が決定される前記Kに応じて、前記L及びMが可変に設定される前記パック化データであり、

K = 6、 I = 2 である場合には L = 0、 M = 8、 N = 3 となり、或いは

K = 7、 I = 2 である場合には L = 1、 M = 4、 N = 2 となり、或いは

K = 8、 I = 2 である場合には L = 0、 M = 4、 N = 2 となり、或いは

K = 10、 I = 2 である場合には L = 1、 M = 3、 N = 2 となり、或いは

K = 12、 I = 2 である場合には L = 0、 M = 4、 N = 3 となり、或いは

K = 16、 I = 2 である場合には L = 0、 M = 2、 N = 2 となり、或いは 40

K = 24、 I = 2 である場合には L = 0、 M = 2、 N = 3 となるパック化データを生成することを特徴とするデータ転送制御装置。

#### 【請求項3】

請求項1又は2において、

$N \times 8 \times I = (K + L) \times M$  であることを特徴とするデータ転送制御装置。

#### 【請求項4】

請求項1乃至3のいずれかにおいて、

前記パケット生成回路は、

前記シリアルバスを介して送信するパケットのヘッダに、前記M、Nを設定するための設定情報を挿入することを特徴とするデータ転送制御装置。 50

**【請求項 5】**

請求項 1 乃至 4 のいずれかに記載のデータ転送制御装置と、

前記インターフェースバスを介して前記データ転送制御装置に接続される 1 又は複数の

デバイスとを含むことを特徴とする電子機器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、データ転送制御装置及び電子機器に関する。

**【背景技術】****【0002】**

近年、EMIノイズの低減などを目的としたインターフェースとしてLVDS (Low Voltage Differential Signaling)などの高速シリアル転送のインターフェースが脚光を浴びている。この高速シリアル転送では、トランスミッタ回路がシリアル化されたデータを差動信号 (Differential Signals) により送信し、レシーバ回路が差動信号を差動増幅することでデータ転送を実現する。

10

**【0003】**

一般的な携帯電話は、電話番号入力や文字入力のためのボタンが設けられる第1の機器部分と、メインLCD (Liquid Crystal Display) やサブLCDやカメラ (CCD) が設けられる第2の機器部分と、第1、第2の機器部分を接続するヒンジなどの接続部分により構成される。従って、第1の機器部分に設けられる第1の基板と、第2の機器部分に設けられる第2の基板との間のデータ転送を、差動信号を用いたシリアル転送により行えば、接続部分を通る配線の本数を減らすことができ、好都合である。

20

**【0004】**

ところで、CCDやCMOSなどのカメラ (撮像デバイス) から出力されるカメラデータには、種々のフォーマットがある。具体的にはYUV422、YUV420、RGB888、RGB565、RGB444、RAW6、RAW7、RAW8、RAW10、RAW12、JPEG8などのフォーマットがある。ここでYUV422及びYUV420は8ビットのデータ (1つのデータ単位が8ビットのデータ) として入力され、RGB888は24ビット、RGB565は16ビット、RGB444は12ビットのデータとして入力される。またRAW6、RAW7、RAW8、RAW10、RAW12は、各々、6、7、8、10、12ビットのデータとして入力され、JPEG8は8ビットのデータとして入力される。従って、カメラデータをパケット化して、カメラが設けられている第2の機器部分から、ホストデバイスが設けられている第1の機器部分へとシリアル転送する場合には、これらの多様なフォーマットをサポートできることが望ましい。

30

**【0005】**

ところが、このような多様なフォーマットのカメラデータをパケット化する場合に、冗長データのビット数が多くなってしまうと、シリアルバスでのデータ転送量が大きくなってしまう。一方、冗長データのビット数を0にして上述の多様なフォーマットに対応しようとすると、回路規模の増大化などの問題を招く。

**【特許文献1】特開2001-222249号公報**

40

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

本発明は、以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、回路の大規模化を抑えながらも多様なフォーマットのデータの効率的なシリアル転送を実現できるデータ転送制御装置及びこれを含む電子機器を提供することにある。

**【課題を解決するための手段】****【0007】**

本発明は、データ転送を制御するデータ転送制御装置であって、1つのデータ単位がKビット (Kは2以上の整数) となるデータがインターフェースバスを介して入力されるイ

50

ンターフェース回路と、シリアルバスを介して送信するパケットの生成を行うリンクコントローラとを含み、前記リンクコントローラは、Kビットの前記データに対してLビット（Lは0以上の整数）のダミーデータを付加することで得られる（K+L）ビットのデータが、M個（Mは1以上の整数）ずつ集まつた（N×I）バイト（N、Iは1以上の整数）のパック化データを生成するデータフォーマッタと、前記シリアルバスを介して送信するパケットとして、前記パック化データがデータフィールドに挿入されるパケットを生成するパケット生成回路とを含み、前記データフォーマッタは、前記Kに応じて前記L及びMが可変に設定される前記パック化データを生成するデータ転送制御装置に関係する。

## 【0008】

本発明によれば、Kビットのデータに対してLビットのダミーデータを付加することで得られる（K+L）ビットのデータが、M個ずつ集まつた（N×I）バイトのデータであって、Kに応じてL及びMが可変に設定されるパック化データが生成される。そしてこのパック化データが、シリアルバスを介して送信されるパケットのデータフィールドに挿入（設定）される。このようにKに応じてパック化データのLを可変に設定することで、シリアルバスでのデータ転送量を低減することが可能になる。またKに応じてパック化データのMを可変に設定することで、回路の大規模化を抑えることが可能になる。従って本発明によれば、回路規模を抑えながらも、多様なフォーマットのデータの効率的なシリアル転送を実現できるようになる。

## 【0009】

また本発明では、前記データフォーマッタは、K=6、I=1である場合にはL=0、M=4、N=3となり、或いはK=7、I=1である場合にはL=1、M=2、N=2となり、或いはK=8、I=1である場合にはL=0、M=2、N=2となり、或いはK=10、I=1である場合にはL=2、M=2、N=3となり、或いはK=12、I=1である場合にはL=0、M=2、N=3となり、或いはK=16、I=1である場合にはL=0、M=1、N=2となり、或いはK=24、I=1である場合にはL=0、M=1、N=3となるパック化データを生成するようにしてもよい。なおこれら以外のフォーマットを採用してもよい。

## 【0010】

また本発明では、前記データフォーマッタは、K=6、I=2である場合にはL=0、M=8、N=3となり、或いはK=7、I=2である場合にはL=1、M=4、N=2となり、或いはK=8、I=2である場合にはL=0、M=4、N=2となり、或いはK=10、I=2である場合にはL=1、M=3、N=2となり、或いはK=12、I=2である場合にはL=0、M=4、N=3となり、或いはK=16、I=2である場合にはL=0、M=2、N=2となり、或いはK=24、I=2である場合にはL=0、M=2、N=3となるパック化データを生成するようにしてもよい。なおこれら以外のフォーマットを採用してもよい。

## 【0011】

また本発明では、 $N \times 8 \times I = (K + L) \times M$ であってもよい。但し、例外的に $N \times 8 \times I = (K + L) \times M$ とならない場合があってもよい。

## 【0012】

また本発明では、前記パケット生成回路は、前記シリアルバスを介して送信するパケットのヘッダに、前記M、Nを設定するための設定情報を挿入するようにしてもよい。

## 【0013】

このようにすれば、パケットの受信側が行うパック化データのフォーマット変換を容易化できる。

## 【0014】

また本発明では、前記M、Nを設定するための設定情報を記憶する内部レジスタを含み、前記データフォーマッタは、前記設定情報に基づいて、前記ダミーデータを挿入するようにしてもよい。

## 【0015】

10

20

30

40

50

このようにすれば、ダミーデータの挿入処理を簡素化できる。なお、データフォーマッタは、ビットカウンタでのカウント値やバイトカウンタでのカウント値に基づいて、ダミーデータの挿入位置等を判断できる。

#### 【0016】

また本発明は、上記のいずれかに記載のデータ転送制御装置と、前記インターフェースバスを介して前記データ転送制御装置に接続される1又は複数のデバイスとを含む電子機器に関するもの。

#### 【0017】

また本発明は、データ転送を制御するデータ転送制御装置であって、システムバスを介して接続されるホストデバイスとの間でのインターフェース処理を行うインターフェース回路と、シリアルバスを介して受信したパケットの解析を行い、1つのデータ単位がKビット（Kは2以上の整数）となるデータを前記インターフェース回路に出力するリンクコントローラとを含み、前記シリアルバスを介して受信したパケットのデータフィールドには、Kビットの前記データに対してLビット（Lは0以上の整数）のダミーデータを付加することで得られる（K+L）ビットのデータが、M個（Mは1以上の整数）ずつ集まつた（N×I）バイト（N、Iは1以上の整数）のデータであって、前記Kに応じて前記L及びMが可変に設定されるパック化データが挿入され、前記リンクコントローラは、前記パック化データからKビットの前記データを抽出して前記インターフェース回路に出力するデータフォーマッタを含むデータ転送制御装置に関するもの。

#### 【0018】

本発明によれば、Kビットのデータに対してLビットのダミーデータを付加することで得られる（K+L）ビットのデータが、M個ずつ集まつた（N×I）バイトのデータであって、Kに応じてL及びMが可変に設定されるパック化データが、シリアルバスを介して受信したパケットのデータフィールドに挿入される。そしてデータフォーマッタは、パケットのデータフィールドに挿入されたこのパック化データから、Kビットのデータを抽出してインターフェース回路に出力する。このようにKに応じてパック化データのLが可変に設定されることで、シリアルバスでのデータ転送量を低減することが可能になる。またKに応じてパック化データのMが可変に設定されることで、回路の大規模化を抑えることが可能になる。従って本発明によれば、回路規模を抑えながらも、多様なフォーマットのデータの効率的なシリアル転送を実現できるようになる。

#### 【0019】

また本発明では、パケットに挿入される前記パック化データは、K=6、I=1である場合にはL=0、M=4、N=3となり、或いはK=7、I=1である場合にはL=1、M=2、N=2となり、或いはK=8、I=1である場合にはL=0、M=2、N=2となり、或いはK=10、I=1である場合にはL=2、M=2、N=3となり、或いはK=12、I=1である場合にはL=0、M=2、N=3となり、或いはK=16、I=1である場合にはL=0、M=1、N=2となり、或いはK=24、I=1である場合にはL=0、M=1、N=3となるデータであってもよい。なおこれら以外のフォーマットを採用してもよい。

#### 【0020】

また本発明では、パケットに挿入される前記パック化データは、K=6、I=2である場合にはL=0、M=8、N=3となり、或いはK=7、I=2である場合にはL=1、M=4、N=2となり、或いはK=8、I=2である場合にはL=0、M=4、N=2となり、或いはK=10、I=2である場合にはL=1、M=3、N=2となり、或いはK=12、I=2である場合にはL=0、M=4、N=3となり、或いはK=16、I=2である場合にはL=0、M=2、N=2となり、或いはK=24、I=2である場合にはL=0、M=2、N=3となるデータであってもよい。なおこれら以外のフォーマットを採用してもよい。

#### 【0021】

また本発明では、 $N \times 8 \times I = (K + L) \times M$ であってもよい。但し、例外的に $N \times 8$

10

20

30

40

50

$\times I = (K + L) \times M$  とならない場合があつてもよい。

【0022】

また本発明では、前記シリアルバスを介して受信したパケットのヘッダには、前記M、Nを設定するための設定情報が挿入され、前記リンクコントローラは、受信したパケットのヘッダを解析し、前記設定情報をパケットのヘッダから抽出するパケット解析回路を含み、前記データフォーマッタは、前記設定情報に基づいて、前記パック化データからKビットの前記データを抽出するようにしてもよい。

【0023】

このようにすれば、パック化データからKビットのデータを抽出する処理を容易化できる。

10

【0024】

また本発明では、前記シリアルバスを介して受信したパケットのヘッダには、前記M、Nを設定するための設定情報が挿入され、前記リンクコントローラは、受信したパケットのヘッダを解析し、前記設定情報をパケットのヘッダから抽出するパケット解析回路を含み、前記データフォーマッタは、前記設定情報に基づいて、前記ダミーデータを削除するようにしてもよい。

【0025】

このようにすれば、ダミーデータの削除処理を簡素化できる。なお、データフォーマッタは、ビットカウンタでのカウント値やバイトカウンタでのカウント値に基づいて、ダミーデータの削除位置等を判断できる。

20

【0026】

また本発明は、上記のいずれかに記載のデータ転送制御装置と、前記システムバスを介して前記データ転送制御装置に接続される前記ホストデバイスとを含む電子機器に関する。

【発明を実施するための最良の形態】

【0027】

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0028】

30

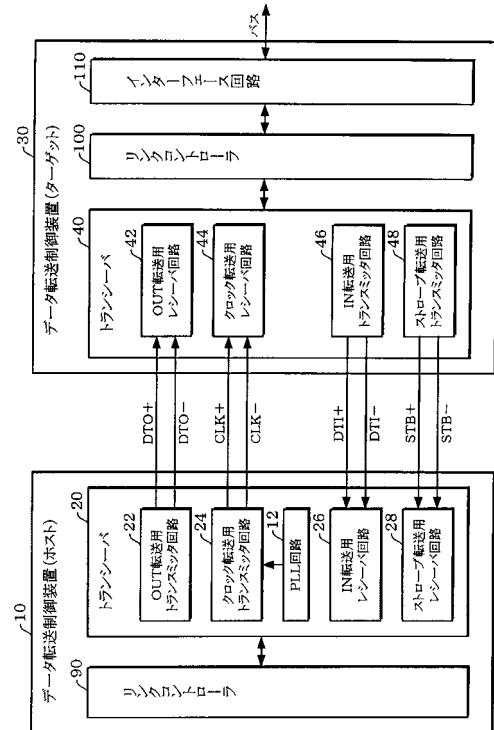

1. システム構成

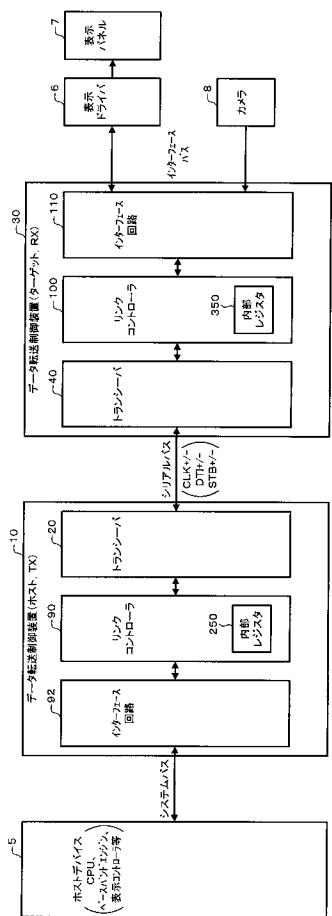

図1に本実施形態のデータ転送制御装置（データ転送制御回路）及びそのシステム構成例を示す。本実施形態では図1のホスト側、ターゲット側のデータ転送制御装置10、30を用いることで、いわゆるシステムバス、インターフェースバス間のブリッジ機能を実現している。

【0029】

なおデータ転送制御装置10、30は図1の構成に限定されず、図1の回路ブロックの一部を省略したり、回路ブロック間の接続形態を変更したり、図1とは異なる回路ブロックを追加してもよい。例えばホスト側データ転送制御装置10においてトランシーバ20の構成を省略したり、ターゲット側データ転送制御装置30においてトランシーバ40の構成を省略してもよい。またデータ転送制御装置30と表示ドライバ6又はカメラ8（撮像デバイス、カメラデバイス）は2チップ（半導体チップ）で構成してもよいが、1チップで構成することもできる。ホストデバイス5（システムデバイス）とデータ転送制御装置10についても同様に1チップで構成することもできる。

40

【0030】

ホスト（TX）側データ転送制御装置10とターゲット（RX）側データ転送制御装置30は、差動信号(differential signals)のシリアルバスを介してパケット転送を行う。より具体的には、シリアルバスの差動信号線(differential signal lines)を電流駆動又は電圧駆動することによりパケットの送受信を行う。

【0031】

50

ホスト側データ転送制御装置 10 は、ホストデバイス 5 (CPU、ベースバンドエンジン、表示コントローラ等)との間のインターフェース処理を行うインターフェース回路 92 を含む。このインターフェース回路 92 はシステムバス (ホストバス) を介してホストデバイス 5 に接続される。システムバスは、RGBインターフェースバスとして用いたり、MPU(Micro Processor Unit)インターフェースバスとして用いたり、シリアルインターフェースバスとして用いたり、カメラインターフェースバスとして用いることができる。RGBインターフェースバスとして用いる場合には、システムバスは、水平同期信号、垂直同期信号、クロック信号、データ信号などの信号線を含むことができる。MPUインターフェースバスとして用いる場合には、システムバスは、データ信号、リード信号、ライト信号、アドレス0信号(コマンド/パラメータ識別信号)、チップセレクト信号などの信号線を含むことができる。シリアルインターフェースバスとして用いる場合には、システムバスは、シリアルインターフェース用のチップセレクト信号、リード/ライト信号、アドレス0信号、データ信号、クロック信号などの信号線を含むことができる。カメラインターフェースバスとして用いる場合には、システムバスは、カメラインターフェース用の水平同期信号、垂直同期信号、クロック信号、データ信号などの信号線を含むことができる。10

#### 【0032】

ホスト側データ転送制御装置 10 は、リンク層の処理を行うリンクコントローラ 90 (リンク層回路) を含む。このリンクコントローラ 90 は、シリアルバス (LVDS) を介してターゲット側データ転送制御装置 30 に転送されるパケット (リクエストパケット、ストリームパケット等) を生成し、生成したパケットを送信する処理を行う。具体的には、送信トランザクションを起動して、生成したパケットの送信をトランシーバ 20 に指示する。20

#### 【0033】

ホスト側データ転送制御装置 10 は、物理層の処理等を行うトランシーバ 20 (PHY) を含む。このトランシーバ 20 は、リンクコントローラ 90 により指示されたパケットを、シリアルバスを介してターゲット側データ転送制御装置 30 に送信する。またトランシーバ 20 はターゲット側データ転送制御装置 30 からのパケットの受信も行う。この場合にはリンクコントローラ 90 が、受信したパケットを解析して、リンク層 (トランザクション層) の処理を行う。30

#### 【0034】

ターゲット側データ転送制御装置 30 は、物理層の処理等を行うトランシーバ 40 (PHY) を含む。このトランシーバ 40 は、シリアルバスを介してホスト側データ転送制御装置 10 からのパケットを受信する。またトランシーバ 40 はホスト側データ転送制御装置 10 へのパケットの送信も行う。この場合にはリンクコントローラ 100 が、送信するパケットを生成し、生成したパケットの送信を指示する。

#### 【0035】

ターゲット側データ転送制御装置 30 はリンクコントローラ 100 (リンク層回路) を含む。このリンクコントローラ 100 は、ホスト側データ転送制御装置 10 からのパケットの受信処理を行い、受信したパケットを解析するリンク層 (トランザクション層) の処理を行う。40

#### 【0036】

ターゲット側データ転送制御装置 30 は、表示パネル 7 (LCD 等) を駆動する表示ドライバ 6 や、カメラ 8 (広義には 1 又は複数のデバイス) との間のインターフェース処理を行うインターフェース回路 110 を含む。このインターフェース回路 110 は、各種のインターフェース信号を生成し、インターフェースバスを介して表示ドライバ 6 等に出力する。またインターフェースバスを介してカメラ 8 から各種のインターフェース信号を受ける。このインターフェース回路 110 は、RGBインターフェース回路、MPUインターフェース回路、シリアルインターフェース回路、或いはカメラインターフェース回路 (広義には第 1 ~ 第 N のインターフェース回路) などを含むことができる。50

## 【0037】

ホスト側（ホストデバイス5）のシステムバスがRGBインターフェースバスとして用いられる場合には、ターゲット側（表示ドライバ6）のインターフェースバスもRGBインターフェースバスとして用いられる。そしてインターフェース回路110（RGBインターフェース回路）は、RGB用のインターフェース信号を生成して表示ドライバ6（広義にはデバイス）に出力する。またホスト側のシステムバスがMPUインターフェースバスとして用いられる場合には、ターゲット側のインターフェースバスもMPUインターフェースバスとして用いられる。そしてインターフェース回路110（MPUインターフェース回路）は、MPU用のインターフェース信号を生成して表示ドライバ6に出力する。またホスト側のシステムバスがカーラインインターフェースバスとして用いられる場合には、ターゲット側のインターフェースバスもカーラインインターフェースバスとして用いられる。そしてターゲット側のインターフェース回路110（カーラインインターフェース回路）はカメラ8からインターフェース信号を受ける。一方、ホスト側のインターフェース回路92（カーラインインターフェース回路）は、カーラインインターフェース信号を生成してホストデバイス5に出力する。なおシステムバスとインターフェースバスのインターフェース形式を異ならせててもよい。

10

## 【0038】

以上のようなインターフェース回路92、110を設けることで、本実施形態ではホスト側のシステムバスとターゲット側のインターフェースバスとの間のバスプリッジ機能を実現している。

20

## 【0039】

即ちシステムバスがRGBインターフェースバスとして用いられる場合には、ホストデバイス5が出力したRGBインターフェース信号を、差動信号のシリアルバスを介したパケット転送によりターゲット側に伝える。そしてターゲット側のインターフェース回路110が、ホスト側からのRGBインターフェース信号に応じたRGBインターフェース信号を表示ドライバ6に出力する。またシステムバスがMPUインターフェースバスとして用いられる場合には、ホストデバイス5が出力したMPUインターフェース信号を、差動信号のシリアルバスを介したパケット転送によりターゲット側に伝える。そしてターゲット側のインターフェース回路110が、ホスト側からのMPUインターフェース信号に応じたMPUインターフェース信号を表示ドライバ6に出力する。

30

## 【0040】

またシステムバスがカーラインインターフェースバスとして用いられる場合には、カメラ8が出力したカーラインインターフェース信号（データ信号、垂直同期信号、水平同期信号）を、差動信号のシリアルバスを介したパケット転送によりターゲット側がホスト側に伝える。そしてホスト側のインターフェース回路92が、ターゲット側からのカーラインインターフェース信号に応じたカーラインインターフェース信号をホストデバイス5に出力する。

## 【0041】

なお図1では、ホストデバイス5が接続されるデータ転送制御装置10がホスト側（TX）となり、カメラ8が接続されるデータ転送制御装置30がターゲット側（RX）になっているが、本実施形態はこれに限定されない。例えば図2に示すように、カメラ8が接続されるデータ転送制御装置30をホスト側（TX）にして、ホストデバイス5が接続されるデータ転送制御装置10をターゲット側（RX）にしてもよい。

40

## 【0042】

即ち本実施形態ではホスト側のデータ転送制御装置がクロック生成回路（PLL回路）を有しており、生成されたクロックをターゲット側のデータ転送制御装置に出力する。そして図1の場合には、ホスト側のデータ転送制御装置10は、クロック生成回路により生成した差動のクロック信号CLK+/-をターゲット側のデータ転送制御装置30に出力する。するとターゲット側のデータ転送制御装置30は、このCLK+/-に基づいて差動のストローブ信号STB+/-を生成する。そしてターゲット側のデータ転送制御装置30は、STB+/-のエッジ（立ち上がりエッジ又は立ち下がりエッジ）に同期して、

50

差動のデータ信号 D T I + / - (カメラデータ) を、ホスト側のデータ転送制御装置 10 に出力する。

#### 【 0 0 4 3 】

一方、図 2 の場合には、ホスト側のデータ転送制御装置 30 は、クロック生成回路により差動のクロック信号 C L K + / - を生成する。そしてホスト側のデータ転送制御装置 30 は、C L K + / - のエッジに同期して差動のデータ信号 D T O + / - (カメラデータ) を、ターゲット側のデータ転送制御装置 10 に出力する。

#### 【 0 0 4 4 】

なお差動信号である D T O + / - 、 C L K + / - 、 D T I + / - 、 S T B + / - を用いたシリアル転送手法については、後述する図 13 で詳細に説明する。

10

#### 【 0 0 4 5 】

##### 2. カメラデータのフォーマット変換

C C D や C M O S などのカメラから出力されるカメラデータには、Y U V 4 2 2 、 Y U V 4 2 0 、 R G B 8 8 8 、 R G B 5 6 5 、 R G B 4 4 4 、 R A W 6 、 R A W 7 、 R A W 8 、 R A W 1 0 、 R A W 1 2 、 J P E G 8 などの種々のフォーマットがある。そしてこれらのフォーマットでは、入力データのデータ単位のビット数が、6、7、8、10、12、16、24ビット(広義にはKビット)というように異なっている。

#### 【 0 0 4 6 】

ところが、シリアルバスを介して転送されるパケットは、バイト単位又はワード単位(広義には1バイト単位)のデータで構成される。従って、カメラデータをパケット化してシリアル転送するためには、6、7、8、10、12、16又は24ビットのカメラデータをバイト単位又はワード単位(1バイト単位)のデータにフォーマット変換する必要がある。

20

#### 【 0 0 4 7 】

このようなフォーマット変換を実現する第1、第2の比較例の手法を図3(A)(B)、図4(A)(B)に示す。図3(A)～図4(B)は、フォーマット変換の対象となるデータ(カメラデータ)が10ビット(RAW10)である場合の例である。そして図3(A)(B)はこの10ビット単位のデータをバイト単位のデータに変換する場合の例であり、図4(A)(B)は、10ビット単位のデータを2バイト単位(ワード単位)のデータに変換する場合の例である。

30

#### 【 0 0 4 8 】

なお図3(A)等において、(101)は、1個目のデータ(10ビットデータ)の1ビット目を意味し、(102)は、1個目のデータの2ビット目を意味する。また(201)は、2個目のデータの1ビット目を意味し、(202)は、2個目のデータの2ビット目を意味する。従って、(101)～(110)は1個目のデータの1～10ビットを表し、(201)～(210)は2個目のデータの1～10ビットを表すことになる。(301)～(310)、(301)～(410)等も同様である。

#### 【 0 0 4 9 】

第1の比較例では、図3(A)、図4(A)に示すように、冗長データが挿入されるアンパックド(unpacked)のフォーマット変換を行っている。即ち図3(A)では(101)～(108)が1個目のバイトデータに設定され、(109)、(110)と6ビットの冗長データ(×)が2個目のバイトデータに設定される。また(201)～(208)が3個目のバイトデータに設定され、(209)、(210)と6ビットの冗長データが4個目のバイトデータに設定される。

40

#### 【 0 0 5 0 】

このように第1の比較例では、2個のバイトデータを転送する毎に6ビットの冗長データを転送する必要がある。従ってVGA画面のデータを転送する毎に、 $640 \times 480 \times 6 / 8 / 1024 = 225$ Kバイトの冗長データを転送しなければならなくなる。このため、シリアルバスのデータ転送量(トライフィック量)が過大になり、データ転送が非効率化する。

50

## 【0051】

一方、第2の比較例では図3(B)、図4(B)に示すように、冗長データが全く挿入されないパックド(packed)のフォーマット変換を行っている。この第2の比較例では、冗長データが挿入されないため、第1の比較例に比べるとシリアルバスのデータ転送量を低減できる。しかしながら、この第2の比較例では、データフォーマッタ(デコード回路)やカウンタの回路規模が大きくなり、データ転送制御装置の大規模化や処理の繁雑化の問題を招く。特に、前述した多様なフォーマットの全てをサポートしようとすると、データ転送制御装置の大規模化や処理の繁雑化の問題は更に深刻になる。

## 【0052】

## 3. データ転送制御装置の構成例

10

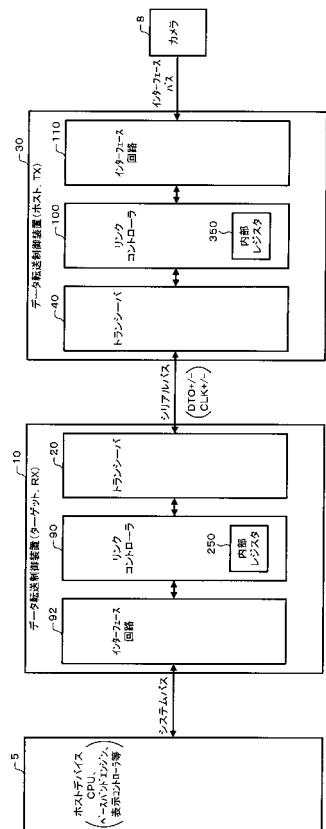

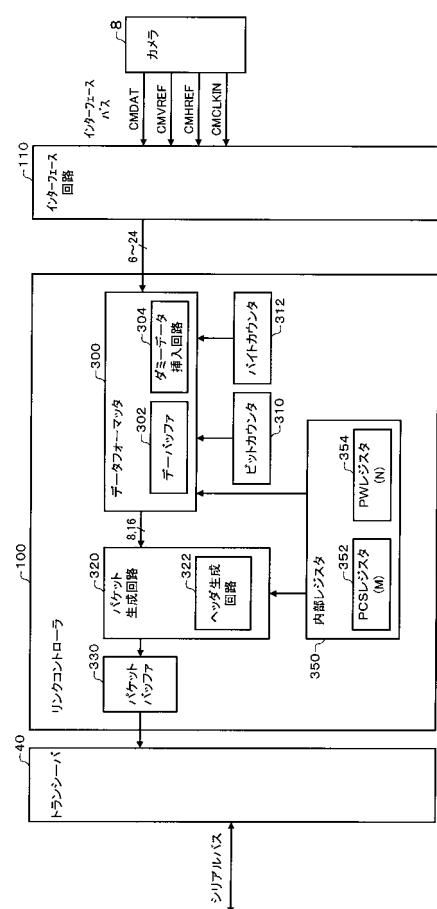

以上のような問題を解決する本実施形態のデータ転送制御装置の構成例を図5、図6に示す。なお図5、図6の回路ブロックの一部を省略したり、回路ブロック間の接続形態を変更したり、図5、図6とは異なる他の回路ブロックを追加してもよい。

## 【0053】

図5はターゲット側(図2の場合はホスト側)のデータ転送制御装置30の構成例である。図5において、インターフェース回路110はカメラ8(広義にはデバイス)との間のインターフェース処理を行う。そしてインターフェース回路110には、1つのデータ単位がKビットとなるデータがインターフェースバスを介して入力される。なお、Kは2(或いは6)以上の整数である。

## 【0054】

20

具体的にはインターフェース回路110には、1つのデータ単位のビット数が6、7、8、10、12、16又は24ビット(以下、適宜、6~24ビットと表記する)となるカメラデータCMDATが入力される。また垂直同期信号、水平同期信号に相当するCMVREF、CMHREFや、CMDATを取り込むためのクロック信号CMCLKINが入力される。

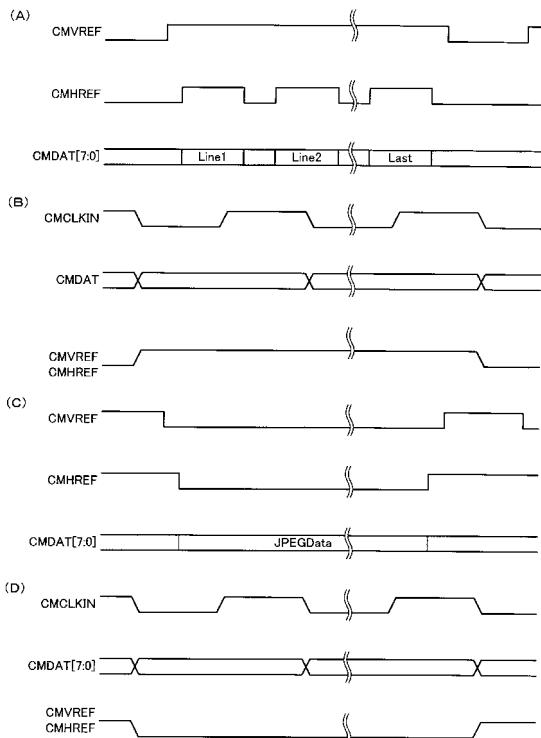

## 【0055】

図7(A)(B)にカメラデータが8ビットのYUVフォーマットである場合のCMDAT、CMVREF、CMHREF、CMCLKINの信号波形例を示す。図7(A)に示すように、CMVREFがアクティブ(ハイレベル)になった後、CMHREFがアクティブになる毎に1ライン分のCMDATがインターフェース回路110に入力される。また図7(B)に示すようにCMDATはCMCLKINの例えれば立ち上がりエッジによりサンプリングできる。インターフェース回路110はこのようにサンプリングされて取り込まれたデータ(カメラデータ)をリンクコントローラ100に出力する。なお図7(C)(D)はカメラデータがJPEGフォーマットである場合の信号波形例である。

30

## 【0056】

リンクコントローラ100は、データフォーマッタ300、ビットカウンタ310、バイトカウンタ312、パケット生成回路320、パケットバッファ330、内部レジスタ350を含む。なおこれらの一部を省略した構成としてもよい。

## 【0057】

40

データフォーマッタ300はデータのフォーマット変換を行う。例えばインターフェース回路110から順次入力されるKビット(6~24ビット)のデータを受けて、フォーマット変換を行い、パック化データ(packed data)を生成する。そして生成されたパック化データを例えれば8ビット又は16ビット(広義にはエバイト)単位でパケット生成回路320に出力する。

## 【0058】

より具体的にはデータフォーマッタ300は、Kビットのデータ(Kビット単位のデータ)に対してLビットのダミーデータを付加することで得られる(K+L)ビットのデータが、M個ずつ集まつた(N×I)バイトのパック化データを生成する。なおLは0以上の整数であり、Mは1以上の整数であり、Nは1(或いは2)以上の整数である。またIは1以上の整数である。

50

**【 0 0 5 9 】**

この場合に本実施形態ではデータフォーマッタ300は、Kに応じてL及びMが可変に設定される（Kに応じてL及びMが変化する）パック化データを生成する。またデータフォーマッタ300は、内部レジスタ350に記憶されるPCS、PW（M、N）の設定情報に基づき決められるビット位置にダミーデータを挿入する処理を行う。

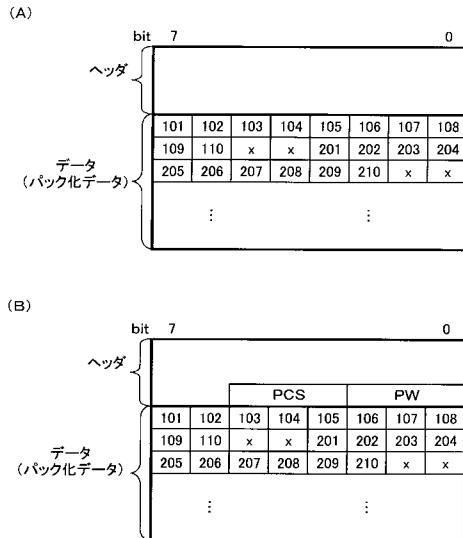

**【 0 0 6 0 】**

図8、図9に、データフォーマッタ300により生成されるパック化データの例を示す。図8は、生成されたパック化データを1バイト（8ビット）毎に出力する場合の例であり、図9は2バイト（16ビット）毎に出力する場合の例である。

**【 0 0 6 1 】**

図8、図9において、DATAは、Kビット単位で入力されるデータ（カメラデータ）を表す。PWはパック幅（パック化データのサイズ）である。このパック幅PWは $N \times I$ バイトと表すことができ、図8ではPWはNバイトになり、図9ではPWは $N \times 2$ バイト（Nワード）になる。またPCSはパック内データ個数（パック化データ内におけるKビットデータの個数）であり、PCS = Mと表すことができる。なお図8、図9におけるダミーデータ（冗長データ）のビット数（個数）はLと表すことができる。

**【 0 0 6 2 】**

図8では、入力データ（カメラデータ）がK = 6、7、8、10、12、16、24ビットである場合に、各々、A1、A2、A3、A4、A5、A6、A7に示すようなパック化データが生成される。図9では、入力データがK = 6、7、8、10、12、16、24ビットである場合に、各々、B1、B2、B3、B4、B5、B6、B7に示すようなパック化データが生成される。そして図8、図9では、入力データのビット数Kに応じて、ダミーデータのビット数Lと、パック内データ個数PCSに相当するM（或いはパック幅PWに相当するN）が可変に変化している。なお図8、図9の詳細については後述する。

**【 0 0 6 3 】**

データフォーマッタ300は、データバッファ302、ダミーデータ挿入回路304を含む。データバッファ302には、Kビット（8～24ビット）単位のデータが入力され、8ビット又は16ビット単位でパック化データを出力する。ダミーデータ挿入回路304は、冗長データであるダミーデータの挿入処理を行う。具体的には内部レジスタ350に記憶されるPCS、PW（M、N）の設定情報に基づき、ダミーデータのビット位置（データバッファ302上のビット位置）を決定（設定）し、そのビット位置にダミーデータ（0又は1のデータ）を挿入するための処理を行う。

**【 0 0 6 4 】**

ビットカウンタ310（ピクセルカウンタ）はデータのビット数のカウント処理を行う。バイトカウンタ312はデータのバイト数のカウント処理を行う。そしてデータフォーマッタ300（ダミーデータ挿入回路304）は、ビットカウンタ310からのビット数のカウント値や、バイトカウンタ312からのバイト数のカウント値や、内部レジスタ350に記憶されるPCS、PW（M、N）の設定情報などに基づきデコード処理を行い、ダミーデータを挿入するビット位置を決める。

**【 0 0 6 5 】**

パケット生成回路320は、シリアルバスを介して送信するパケットの生成を行う。具体的には、送信するパケットのヘッダを生成し、ヘッダとデータを結合してパケットを組み立てる。そして生成されたパケットはパケットバッファ330に書き込まれて、トランシーバ40に転送される。この場合に、パケットのヘッダの生成はヘッダ生成回路322により行われる。

**【 0 0 6 6 】**

そして本実施形態では図10（A）に示すように、パケット生成回路320は、シリアルバスを介して送信するパケットとして、データフォーマッタ300により生成されたパック化データがデータフィールドに挿入（設定）されるパケットを生成する。図10（A）

10

20

30

40

50

) は、入力データのビット数が  $K = 10$  であり図 8 の A 4 に示すパック化データがデータフィールドに挿入された場合の例である。

#### 【 0 0 6 7 】

なおパケットのデータフィールドには、1 個のパック化データだけを挿入してもよいし、複数個のパック化データを挿入してもよい。また図 10 ( A ) は、パケットのデータ幅が 1 バイトの場合の例を示しているが、パケットのデータ幅は 2 バイト以上 ( I バイト ) であってもよい。パケットのデータ幅を 1 バイトにする場合には、データフォーマッタ 300 からパケット生成回路 320 に対して、パック化データを 1 バイト ( 8 ビット ) 単位で出力すればよい。この場合には図 8 の A 1 ~ A 7 に示すようなパック化データを用いることになる。一方、パケットのデータ幅を 2 バイトにする場合には、データフォーマッタ 300 からパケット生成回路 320 に対して、パック化データを 2 バイト ( 16 ビット ) 单位で出力すればよい。この場合には図 9 の B 1 ~ B 7 に示すようなパック化データを用いることになる。10

#### 【 0 0 6 8 】

また図 10 ( B ) に示すように、パケット生成回路 320 が、パケットのヘッダに、 PCS、 PW ( M、 N ) を設定するための設定情報を挿入するようにしてもよい。具体的には、パケットのヘッダにパック内データ個数 PCS のフィールドと、パック幅 PW のフィールドを設ける。そしてこれらの PCS フィールド、 PW フィールドに、 PCS の設定情報と PW の設定情報を挿入する。例えば図 8 の A 1 の場合には、 PCS = 4、 PW = 24 の設定情報を、 PCS フィールド、 PW フィールドに挿入する。A 2 の場合には、 PCS = 2、 PW = 16 の設定情報を、 PCS フィールド、 PW フィールドに挿入する。20

#### 【 0 0 6 9 】

なおパケットのヘッダに挿入する上述の設定情報は、パック内データ個数 PCS やパック幅 PW の値そのものである必要はなく、少なくとも M、 N を設定 ( 特定 ) できる情報であればよい。例えば PW の値そのものではなく、 N ( 或いは  $N \times I$  ) の値を設定情報として用いてよい。或いは、 N の代わりに L を設定情報として用い、 M と L によって N を特定するようにしてよい。

#### 【 0 0 7 0 】

パケットバッファ 330 は、シリアルバスを介して送信するパケットが書き込まれる送信用のパケットバッファである。即ちシリアルバスを介して送信するパケットは、パケット生成回路 320 により生成されてパケットバッファ 330 に書き込まれ、トランシーバ 40 に転送される。このパケットバッファ 330 は、例えば FIFO ( First In First Out ) や RAM により構成できる。なおパケットバッファ 330 をリングバッファ構造とすることも可能である。また受信用のパケットバッファをリンクコントローラ 100 内に更に設けてよい。

#### 【 0 0 7 1 】

内部レジスタ 350 は各種の制御レジスタやステータスレジスタを含む。この内部レジスタ 350 は、 PCS、 PW ( M、 N ) を設定するための設定情報を記憶する。具体的には、内部レジスタ 350 は PCS レジスタ 352 と PW レジスタ 354 を含み、これらの各レジスタに、 PCS、 PW の設定情報が記憶される。データフォーマッタ 300 は、これらの PCS、 PW に基づきダミーデータの挿入ビット位置を決定する。またパケット生成回路 320 は、これらの PCS、 PW をパケットの PCS、 PW フィールドに挿入する。なお、 PCS、 PW ( M、 N ) の設定情報は、シリアルバスを介して相手デバイス ( ホストデバイス ) から自デバイスに転送して、内部レジスタ 350 に書き込むことができる。

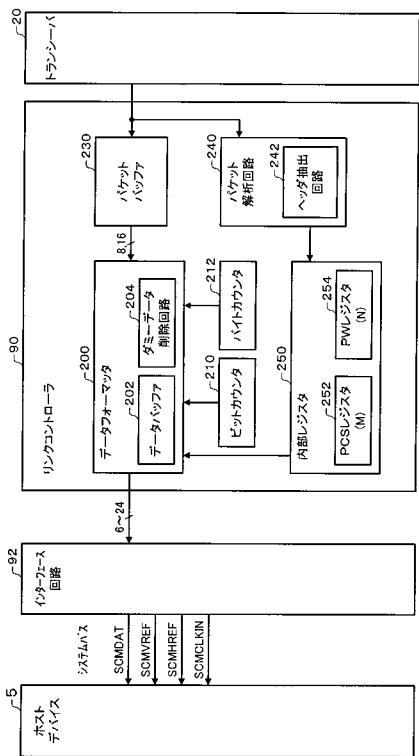

#### 【 0 0 7 2 】

図 6 はホスト側 ( 図 2 の場合にはターゲット側 ) のデータ転送制御装置 10 の構成例である。図 6 に示すように、データ転送制御装置 10 が含むリンクコントローラ 90 は、データフォーマッタ 200、 ビットカウンタ 210、 バイトカウンタ 212、 パケットバッファ 230、 パケット解析回路 240、 内部レジスタ 250 を含む。なおこれらの一部を50

省略する構成としてもよい。

#### 【0073】

パケットバッファ230は、シリアルバスを介して受信したパケットが書き込まれる受信用のパケットバッファである。即ちシリアルバスを介してトランシーバ20が受信したパケットは、パケットバッファ230に書き込まれる。そして、書き込まれたパケットのデータフィールドに設定されたパック化データ（図10（A）（B）参照）は、データフォーマッタ200に出力される。この場合に、パック化データは例えば8ビット又は16ビット（1バイト）単位でデータフォーマッタ200に出力される。

#### 【0074】

パケットバッファ230は、例えば FIFO や RAM により構成できる。なおパケットバッファ230をリングバッファ構造とすることも可能である。またパケットバッファ230をダブルバッファ構成にしたり、送信用のパケットバッファをリンクコントローラ90内に更に設けてもよい。

10

#### 【0075】

パケット解析回路240は、シリアルバスを介して受信したパケットの解析を行う。具体的には受信したパケットのヘッダとデータを分離して、ヘッダを抽出する。このヘッダの抽出は、ヘッダ抽出回路242により行われる。

#### 【0076】

例えばパケット解析回路240は、ヘッダのパケットタイプフィールドを解析して、受信したパケットのタイプ（リクエストパケット、レスポンスパケット、アクノリッジパケット）等を判断する。またヘッダの同期信号コードフィールドを解析して、受信したパケットが、同期信号（垂直同期信号、水平同期信号）の生成をインターフェース回路92に指示する同期信号コードを含んでいるか否かを判断する。

20

#### 【0077】

例えば図5において、カメラ8が垂直同期信号CMVERFを出力した場合には、垂直同期信号の生成を指示する同期信号コードを含むパケットを、パケット生成回路320が生成する。またカメラ8が水平同期信号CMHREFを出力した場合には、水平同期信号の生成を指示する同期信号コードを含むパケットを生成する。そして生成されたパケットはシリアルバスを介して転送される。パケット解析回路240は、転送されて来たパケットを解析し、垂直同期信号のコードを検出すると、インターフェース回路92に対して、垂直同期信号SCMVERFの生成・出力を指示する。また水平同期信号のコードを検出すると、水平同期信号SCMHREFの生成・出力を指示する。このようにしてインターフェースバスとシステムバスとの間のバスブリッジ機能が実現される。

30

#### 【0078】

またパケット解析回路240は、受信したパケットのヘッダを解析し、PCS、PW（M、N）の設定情報を抽出する。具体的には図10（B）に示すようにPCSフィールド、PWフィールドにPCS、PWが設定されている場合に、これらのPCS、PWの情報を抽出する。

#### 【0079】

内部レジスタ250は各種の制御レジスタやステータスレジスタを含む。この内部レジスタ250は、パケット解析回路240により抽出されたPCS、PW（M、N）の設定情報を記憶する。具体的には、内部レジスタ250が含むPCSレジスタ252、PWレジスタ254が、PCS、PWの情報を記憶する。

40

#### 【0080】

図10（A）（B）に示すように、シリアルバスを介して受信したパケットのデータフィールドにはパック化データが挿入されている。このパック化データは、Kビットのデータに対してLビットのダミーデータを付加することで得られる（K+L）ビットのデータが、M個ずつ集まつた（N×I）バイトのデータである。そして、Kに応じてL及びM（あるいはN）が可変に設定されるデータである。

#### 【0081】

50

そしてデータフォーマッタ200（リンクコントローラ90）は、このパック化データからKビット（6～24ビット）のデータ（カメラデータ）を抽出してインターフェース回路92に出力する。またデータフォーマッタ200は、内部レジスタ250に記憶されるP C S、P W（M、N）の設定情報に基づき決められるビット位置から、ダミーデータを削除する処理を行う。

#### 【0082】

例えば図8のA1に示すパック化データがデータフィールドに挿入されていた場合は、データフォーマッタ200は、K=6ビットのデータ（11）～（16）、（21）～（26）、（31）～（36）、（41）～（46）をパック化データから抽出して、インターフェース回路92に順次出力する。同様に、図8のA2、A3、A4、A5、A6、

A7に示すパック化データが挿入されていた場合は、各々、K=7、8、10、12、16、24ビットのデータを抽出して、インターフェース回路92に順次出力する。また図9のB1、B2、B3、B4、B5、B6、B7に示すパック化データが挿入されていた場合は、各々、K=6、7、8、10、12、16、24ビットのデータを抽出して、インターフェース回路92に順次出力する。

10

#### 【0083】

データフォーマッタ200は、データバッファ202、ダミーデータ削除回路204を含む。データバッファ202には、8ビット又は16ビット単位でパック化データが入力され、Kビット（8～24ビット）単位のデータを出力する。ダミーデータ削除回路204は、冗長データであるダミーデータの削除処理を行う。具体的には内部レジスタ250に記憶されるP C S、P W（M、N）の設定情報に基づき、ダミーデータのビット位置（データバッファ202上のビット位置）を決定（設定）し、そのビット位置からダミーデータ（0又は1のデータ）を削除するための処理を行う。

20

#### 【0084】

ビットカウンタ210はデータのビット数のカウント処理を行う。バイトカウンタ212はデータのバイト数のカウント処理を行う。そしてデータフォーマッタ200（ダミーデータ削除回路204）は、ビットカウンタ210からのビット数のカウント値や、バイトカウンタ212からのバイト数のカウント値や、内部レジスタ250に記憶されるP C S、P W（M、N）の設定情報に基づきデコード処理を行い、ダミーデータを削除するビット位置を決める。

30

#### 【0085】

インターフェース回路92は、データフォーマッタ200からのKビット（6～24ビット）のデータ（カメラデータ）を受ける。そしてこのデータをS C M D A Tとしてホストデバイス5に出力する。そしてこの際に、図7（A）～（D）と同様な波形の垂直同期信号S C M V R E F、水平同期信号S C M H R E F、クロック信号S C M C L K I Nをホストデバイス5に出力する。このようにすることで、カメラ8から出力されたC M D A T、C M V R E F、C M H R E F等の再生処理が可能になる。

#### 【0086】

##### 4. フォーマット変換手法

次に本実施形態のフォーマット変換手法について詳細に説明する。例えば図8のA1では、入力されるカメラデータのフォーマットがR A W 6であり、K=6ビットのデータ（11）～（16）、（21）～（26）、（31）～（36）、（41）～（46）が入力される。なお（11）は1個目のデータ（6ビットデータ）の1ビット目を意味し、（12）は1個目のデータの2ビット目を意味する。また（21）は2個目のデータの1ビット目を意味し、（22）は2個目のデータの2ビット目を意味する。また（×）はダミーデータ（冗長データ）を意味する。

40

#### 【0087】

そして図8のA1のようにビット数K=6である場合には、パック幅P W=24、パック内データ個数P C S=4に設定される。またダミーデータのビット数L=0になる。従ってこの場合には、6ビット（K+Lビット）のデータがP C S=4個（M個）集まつた

50

、 $PW = 24$  ビット ( $N = 3$ ) のパック化データが生成される。

#### 【0088】

また図8のA2ではカメラデータのフォーマットがRAW7であり、 $K = 7$ ビットのデータ(11)～(17)、(21)～(27)が入力される。そしてこのように $K = 7$ である場合には、 $PW = 16$ 、 $PCS = 2$ に設定される。またダミーデータのビット数 $L = 1$ になる。従ってこの場合には、8ビット( $K + L$ ビット)のデータが $PCS = 2$ 個( $M$ 個)集まつた、 $PW = 16$ ビット( $N = 2$ )のパック化データが生成される。

#### 【0089】

なお図8のA2の場合には、バイトカウンタのカウント値=1でありビットカウンタのカウント値=8である場合と、バイトカウンタのカウント値=2でありビットカウンタのカウント値=8である場合に、ダミーデータを挿入すればよい。10

#### 【0090】

また図8のA3では、カメラデータのフォーマットがYUV422、YUV420、RAW8又はJPEG8であり、 $K = 8$ ビットのデータ(11)～(18)、(21)～(28)が入力される。そしてこのように $K = 8$ である場合には、 $PW = 16$ 、 $PCS = 2$ に設定される。またダミーデータのビット数 $L = 0$ になる。従ってこの場合には、8ビット( $K + L$ ビット)のデータが $PCS = 2$ 個( $M$ 個)集まつた、 $PW = 16$ ビット( $N = 2$ )のパック化データが生成される。

#### 【0091】

なお図8のA4の場合には、バイトカウンタのカウント値=2でありビットカウンタのカウント値=3、4である場合と、バイトカウンタのカウント値=3でありビットカウンタのカウント値=7、8である場合に、ダミーデータを挿入すればよい。20

#### 【0092】

また図8のA4ではカメラデータのフォーマットがRAW10であり、 $K = 10$ ビットのデータ(101)～(110)、(201)～(210)が入力される。そしてこのように $K = 10$ である場合には、 $PW = 24$ 、 $PCS = 2$ に設定される。またダミーデータのビット数 $L = 2$ になる。従ってこの場合には、12ビット( $K + L$ ビット)のデータが $PCS = 2$ 個( $M$ 個)集まつた、 $PW = 24$ ビット( $N = 3$ バイト)のパック化データが生成される。図8のA5～A7、図9のB1～B7の場合も同様にしてパック化データが生成される。30

#### 【0093】

図3(A)、図4(A)に示す第1の比較例では冗長データのビット数が多い。このためシリアルバスでのデータ転送量が大きくなってしまうという問題点がある。一方、図3(B)、図4(B)の第2の比較例では冗長データは無いが、全てのフォーマットのカメラデータをサポートしようとすると、データフォーマッタやカウンタが大規模化するという問題点がある。

#### 【0094】

これに対して本実施形態の手法では、冗長データは存在するが、そのビット数は第1の比較例に比べて十分に少ない。従ってシリアルバスでのデータ転送量がそれほど大きくならず、データ転送を効率化できる。また、図8、図9に示すように全てのフォーマットのカメラデータをサポートしようとした場合にも、データフォーマッタやカウンタの回路規模が、第2の比較例に比べるとそれほど大きくはならない。40

#### 【0095】

次に図11(A)～図12(C)を用いて、第1、第2の比較例に対する本実施形態の手法の優位点について説明する。図11(A)～(C)は、図8のパック化データが設定されるパケットの幅(バス幅)が8ビット( $I = 1$ )である場合の例であり、図12(A)～(C)は、図9のパック化データが設定されるパケットの幅が16ビット( $I = 2$ )である場合の例である。

#### 【0096】

そして図11(A)～図12(C)において、 $N$ はパック化データのバイト数又はワード数

50

ド数であり、 $L$ は冗長データ（ダミーデータ）のビット数である。また $K$ は入力データのビット数であり、 $M$ はパック化データ内にある $(K + L)$ ビットデータの個数である。

#### 【0097】

フォーマット変換を行うためには、図11(A)～図12(C)のN、M、Kのそれぞれをカウントするカウンタ（バイトカウンタ、ビットカウンタ等）が必要になる。ここでKについては、第1、第2の比較例及び本実施形態で条件は同じである。従って、N、Mをカウントするカウンタや、カウンタからのカウント値をマルチプレクスしてデコードする回路等が、回路規模を左右する。従って回路規模の削減のためには、 $N \times M$ なるべく少なくする必要がある。なお $N / M$ の組み合わせの数が回路の個数に相当する。

#### 【0098】

一方、シリアルバスのデータ転送量を減らすためには、冗長データのビット数である $L$ を少なくする必要がある。

#### 【0099】

従って、データ転送量の低減化と回路の小規模化を両立するためには、 $N \times M$ の最小化と、 $L$ の最小化を両立できることが望まれる。

#### 【0100】

この点、図11(A)、図12(A)の第1の比較例では、 $M = 1$ に固定されている。従って $N \times M$ （回路規模）については小さくできる。例えば $N \times M$ の合計を計算すると、図11(A)では12ポイントになり、図12(A)では8ポイントになる。

#### 【0101】

しかしながらこの第1の比較例では、冗長データのビット数 $L$ （データ転送量）が大きくなってしまう。例えば $L$ の合計を計算すると、図11(A)では13ビットになり、図12(A)では45ビットになり、非常に大きくなってしまう。

#### 【0102】

また図11(B)、図12(B)の第2の比較例では、 $L = 1$ に固定されている。従って $L$ （データ転送量）については小さくできる。例えば $L$ の合計を計算すると、図11(B)、図12(B)では共に0ビットになる。

#### 【0103】

しかしながらこの第2の比較例では、 $N$ や $M$ が大きいため、 $N \times M$ （回路規模）が大きくなってしまう。例えば $N \times M$ の合計を計算すると、図11(B)では100ポイントになり、図12(B)では197ポイントになり、非常に大きくなってしまう。

#### 【0104】

これに対して図11(C)、図12(C)の本実施形態の手法では、 $K$ に応じて $L$ 、 $M$ を可変に設定している。即ち $K$ に応じて $L$ 、 $M$ を適正な値に変化させている。

#### 【0105】

より具体的には、 $I = 1$ となる図11(C)では、

(1)  $K = 6$ である場合には、 $L = 0$ 、 $M = 4$ 、 $N = 3$

(2)  $K = 7$ である場合には、 $L = 1$ 、 $M = 2$ 、 $N = 2$

(3)  $K = 8$ である場合には、 $L = 0$ 、 $M = 2$ 、 $N = 2$

(4)  $K = 10$ である場合には $L = 2$ 、 $M = 2$ 、 $N = 3$

(5)  $K = 12$ である場合には $L = 0$ 、 $M = 2$ 、 $N = 3$

(6)  $K = 16$ である場合には $L = 0$ 、 $M = 1$ 、 $N = 2$ 、或いは

(7)  $K = 24$ である場合には $L = 0$ 、 $M = 1$ 、 $N = 3$ となるように、パック化データが生成されている。

#### 【0106】

また $I = 2$ となる図12(C)では、

(11)  $K = 6$ 、 $I = 2$ である場合には $L = 0$ 、 $M = 8$ 、 $N = 3$

(12)  $K = 7$ 、 $I = 2$ である場合には $L = 1$ 、 $M = 4$ 、 $N = 2$

(13)  $K = 8$ 、 $I = 2$ である場合には $L = 0$ 、 $M = 4$ 、 $N = 2$

(14)  $K = 10$ 、 $I = 2$ である場合には $L = 1$ 、 $M = 3$ 、 $N = 2$

10

20

30

40

50

(15) K = 12、I = 2である場合にはL = 0、M = 4、N = 3

(16) K = 16、I = 2である場合にはL = 0、M = 2、N = 2、或いは

(17) K = 24、I = 2である場合にはL = 0、M = 2、N = 3となるように、

パック化データが生成されている。

#### 【0107】

この場合に本実施形態の手法では、 $N \times 8 \times I = (K + L) \times M$ の式が成立する。例えばI = 1となる図11(C)では、 $N \times 8 = (K + L) \times M$ の式が成立する。またI = 2となる図12(C)では、 $N \times 8 \times 2 = (K + L) \times M$ の式が成立する。但し図12(C)のK = 10の場合(上述の(14)の場合)だけは例外である。

#### 【0108】

なお上述の(1)~(7)、(11)~(17)の全てを満たさなくても、(1)~(7)、(11)~(17)の一部だけを満たすようにパック化データを生成してもよい。即ちYUV422、YUV420、RGB888、RGB565、RGB444、RAW6、RAW7、RAW8、RAW10、RAW12、JPEG8の一部のフォーマットだけをサポートできるようにしてよい。

#### 【0109】

以上の本実施形態の手法によれば、図11(C)、図12(C)から明らかなように、 $N \times M$ (回路規模)を第2の比較例に比べて小さくできる。例えば $N \times M$ の合計を計算すると、図11(C)では37ポイントになり、図12(C)では68ポイントになる。従って、 $N \times M$ の合計が100、197ポイントになる第2の比較例に比べて、回路規模を十分に小さくできる。

#### 【0110】

また本実施形態の手法では、冗長データのビット数が第1の比較例に比べて少ないため、L(データ転送量)も小さくできる。例えばLの合計を計算すると、図11(C)では3ビットになり、図12(C)では2ビットになる。従って、Lの合計が13、45ビットになる第1の比較例に比べて、データ転送量を十分に小さくできる。

#### 【0111】

このように本実施形態の手法によれば、 $N \times M$ の最小化とLの最小化を両立できる。従って、回路規模をそれほど大きくすることなく、多様なフォーマットのデータの効率的なシリアル転送を実現できるという効果がある。

#### 【0112】

##### 5. 差動信号によるデータ転送方式

次に図13を用いて本実施形態のシリアル転送手法について説明する。図13においてD TO+、D TO-はホスト側(データ転送制御装置10)がターゲット側(データ転送制御装置30)に出力するデータ(OUTデータ)である。CLK+、CLK-は、ホスト側がターゲット側に供給するクロックである。ホスト側はCLK+/ -のエッジ(例えば立ち上がりエッジ。立ち下がりエッジでもよい)に同期してD TO+/-を出力する。従ってターゲット側は、CLK+/ -を用いてD TO+/-をサンプリングして取り込むことができる。更に図13では、ターゲット側はホスト側から供給されたクロックCLK+/-に基づいて動作する。即ちCLK+/ -はターゲット側のシステムクロックになる。このためPLL(Phase Locked Loop)回路12は(広義にはクロック生成回路)はホスト側に設けられ、ターゲット側には設けられていない。

#### 【0113】

D TI+、D TI-はターゲット側がホスト側に出力するデータ(INデータ)である。STB+、STB-は、ターゲット側がホスト側に供給するストローブ(広義にはクロック)である。ターゲット側はホスト側から供給されたCLK+/ -に基づいてSTB+/-を生成して出力する。そしてターゲット側はSTB+/-のエッジ(例えば立ち上がりエッジ。立ち下がりエッジでもよい)に同期してD TI+/-を出力する。従ってホスト側は、STB+/-を用いてD TI+/-をサンプリングして取り込むことができる。

#### 【0114】

10

20

30

40

50

D T O + / -、C L K + / -、D T I + / -、S T B + / -の各々は、トランスマッタ回路（ドライバ回路）がこれらの各々に対応する差動信号線（Differential Signal Lines）を例えれば電流駆動（又は電圧駆動）することにより送信される。なお、より高速な転送を実現するためには、D T O + / -、D T I + / -の各差動信号線を2ペア以上設ければよい。

#### 【0115】

ホスト側のトランシーバ20は、O U T 転送用（広義にはデータ転送用）、クロック転送用のトランスマッタ回路22、24や、I N 転送用（広義にはデータ転送用）、ストローブ転送用（広義にはクロック転送用）のレシーバ回路26、28を含む。ターゲット側のトランシーバ40は、O U T 転送用、クロック転送用のレシーバ回路42、44や、I N 転送用、ストローブ転送用のトランスマッタ回路46、48を含む。なおこれらの回路ブロックの一部を含まない構成としてもよい。10

#### 【0116】

O U T 転送用、クロック転送用のトランスマッタ回路22、24は、各々、D T O + / -、C L K + / -の差動信号線を電流駆動することでD T O + / -、C L K + / -を送信する。O U T 転送用、クロック転送用のレシーバ回路42、44は、各々、D T O + / -、C L K + / -の差動信号線に流れる電流に基づいて電流・電圧変換を行い、電流・電圧変換により得られた差動電圧信号（第1、第2の電圧信号）の比較処理（差動増幅処理）を行うことで、D T O + / -、C L K + / -を受信する。

#### 【0117】

I N 転送用、クロック転送用のトランスマッタ回路46、48は、各々、D T I + / -、S T B + / -の差動信号線を電流駆動することでD T I + / -、S T B + / -を送信する。I N 転送用、ストローブ転送用のレシーバ回路26、28は、各々、D T I + / -、S T B + / -の差動信号線に流れる電流に基づいて電流・電圧変換を行い、電流・電圧変換により得られた差動電圧信号（第1、第2の電圧信号）の比較処理（差動増幅処理）を行うことで、D T I + / -、S T B + / -を受信する。20

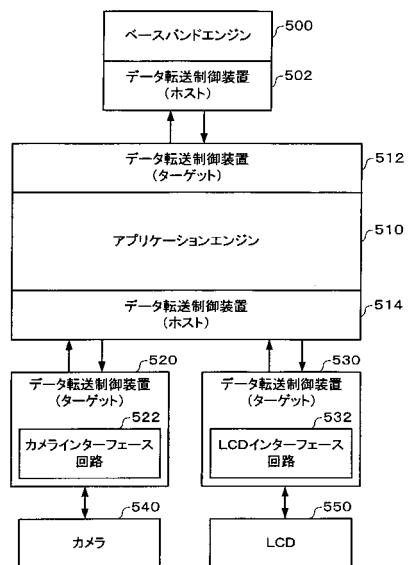

#### 【0118】

##### 6. 電子機器

図14に本実施形態の電子機器の構成例を示す。この電子機器は本実施形態で説明したデータ転送制御装置502、512、514、520、530を含む。またベースバンドエンジン500（広義には通信デバイス）、アプリケーションエンジン510（広義にはプロセッサ）、カメラ540（広義には撮像デバイス）、或いはLCD550（広義には表示デバイス）を含む。なおこれらの一部を省略する構成としてもよい。この構成によればカメラ機能とLCD（Liquid Crystal Display）の表示機能を有する携帯電話などを実現できる。但し本実施形態の電子機器は携帯電話には限定されず、デジタルカメラ、PDA、電子手帳、電子辞書、或いは携帯型情報端末など種々の電子機器に適用できる。30

#### 【0119】

図14に示すようにベースバンドエンジン500に設けられたホスト側のデータ転送制御装置502と、アプリケーションエンジン510（グラフィックエンジン）に設けられたターゲット側のデータ転送制御装置512との間で、本実施形態で説明したシリアル転送が行われる。またアプリケーションエンジン510に設けられたホスト側のデータ転送制御装置514と、カーメラインターフェース回路522を含むデータ転送制御装置520や、LCDインターフェース回路532を含むデータ転送制御装置530との間でも、本実施形態で説明したシリアル転送が行われる。なおベースバンドエンジン500とアプリケーションエンジン510を同一のハードウェア（CPU等）で実現してもよい。40

#### 【0120】

図14の構成によれば、従来の電子機器に比べて、EMIノイズを低減できる。またデータ転送制御装置の小規模化、省電力化を実現することで、電子機器の更なる省電力化を図れる。また電子機器が携帯電話である場合には、携帯電話の接続部分（ヒンジ部分）に通る信号線をシリアル信号線にすることが可能になり、実装の容易化を図れる。50

## 【0121】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語（デバイス、エバイト等）と共に記載された用語（カメラ・表示ドライバ、8・16ビット等）は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。

## 【0122】

またデータ転送制御装置や電子機器の構成や動作も本実施形態で説明した構成や動作に限定に限定されず、種々の変形実施が可能である。またフォーマット変換手法も図8、図12(C)等で説明したものに限定されない。例えばKも6、7、8、10、12、16、24に限定されず、Iも1、2には限定されない。またカメラデータ以外のフォーマット変換に本発明の手法を用いることも可能である。

10

## 【図面の簡単な説明】

## 【0123】

【図1】本実施形態のデータ転送制御装置及びそのシステム構成例。

【図2】本実施形態のデータ転送制御装置及びそのシステム構成例。

【図3】図3(A)(B)は比較例の手法の説明図。

【図4】図4(A)(B)は比較例の手法の説明図。

20

【図5】本実施形態のデータ転送制御装置の構成例。

【図6】本実施形態のデータ転送制御装置の構成例。

【図7】図7(A)～(D)は、カメラインターフェース信号の波形例。

【図8】本実施形態のフォーマット変換手法の説明図。

【図9】本実施形態のフォーマット変換手法の説明図。

【図10】図10(A)(B)は本実施形態で使用されるパケットの説明図。

【図11】図11(A)(B)(C)は本実施形態の優位点を説明する図。

【図12】図12(A)(B)(C)は本実施形態の優位点を説明する図。

【図13】本実施形態のシリアル転送の説明図。

【図14】電子機器の構成例。

30

## 【符号の説明】

## 【0124】

5 ホストデバイス、6 表示ドライバ、7 表示パネル、8 カメラ、

10 データ転送制御装置（ホスト側）、20 トランシーバ、

30 データ転送制御装置（ターゲット側）、40 トランシーバ、

90、100 リンクコントローラ、92、110 インターフェース回路、

200 データフォーマッタ、202 データバッファ、

204 ダミーデータ削除回路、210 ビットカウンタ、212 バイトカウンタ、

230 パケットバッファ、240 パケット解析回路、242 ヘッダ抽出回路、

250 内部レジスタ、252 PCSレジスタ、254 PWレジスタ、

300 データフォーマッタ、302 データバッファ、

304 ダミーデータ挿入回路、310 ビットカウンタ、312 バイトカウンタ、

320 パケット生成回路、322 ヘッダ生成回路、330 パケットバッファ、

350 内部レジスタ、352 PCSレジスタ、354 PWレジスタ、

40

【図1】

【図2】

【図3】

(A)第1の比較例

|     | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8 |

|-----|-----|-----|-----|-----|-----|-----|-----|---|

| 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 |   |

| 109 | 110 | x   | x   | x   | x   | x   | x   |   |

| 201 | 202 | 203 | 204 | 205 | 206 | 207 | 208 |   |

| 209 | 210 | x   | x   | x   | x   | x   | x   | x |

(B)第2の比較例

|     | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|

| 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 | 109 | 110 | x  | x  | x  | x  | x  | x  | x  |

| 109 | 110 | 201 | 202 | 203 | 204 | 205 | 206 |     |     |    |    |    |    |    |    |    |

| 207 | 208 | 209 | 210 | 301 | 302 | 303 | 304 |     |     |    |    |    |    |    |    |    |

| 305 | 306 | 307 | 308 | 309 | 310 | 401 | 402 |     |     |    |    |    |    |    |    |    |

| 403 | 404 | 405 | 406 | 407 | 408 | 409 | 410 |     |     |    |    |    |    |    |    |    |

【図4】

(A)第1の比較例

|     | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 | 109 | 110 | 201 | 202 | 203 | 204 | 205 | 206 |    |

| 207 | 208 | 209 | 210 | 301 | 302 | 303 | 304 | 305 | 306 | 307 | 308 | 309 | 310 | 401 | 402 |    |

| 403 | 404 | 405 | 406 | 407 | 408 | 409 | 410 | 501 | 502 | 503 | 504 | 505 | 506 | 507 | 508 |    |

| 509 | 510 | 601 | 602 | 603 | 604 | 605 | 606 | 607 | 608 | 609 | 610 | 701 | 702 | 703 | 704 |    |

| 705 | 706 | 707 | 708 | 709 | 710 | A01 | A02 | A03 | A04 | A05 | A06 | A07 | A08 | A09 | A10 |    |

(B)第2の比較例

|     | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 | 109 | 110 | 201 | 202 | 203 | 204 | 205 | 206 |    |

| 207 | 208 | 209 | 210 | 301 | 302 | 303 | 304 | 305 | 306 | 307 | 308 | 309 | 310 | 401 | 402 |    |

| 403 | 404 | 405 | 406 | 407 | 408 | 409 | 410 | 501 | 502 | 503 | 504 | 505 | 506 | 507 | 508 |    |

| 509 | 510 | 601 | 602 | 603 | 604 | 605 | 606 | 607 | 608 | 609 | 610 | 701 | 702 | 703 | 704 |    |

| 705 | 706 | 707 | 708 | 709 | 710 | A01 | A02 | A03 | A04 | A05 | A06 | A07 | A08 | A09 | A10 |    |

【図5】

【図6】

【図7】

【図8】

|    | DATA<br>(Kビット) | PW<br>(Nバイト) | PCS<br>(M回) | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   |

|----|----------------|--------------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| 6  | 24<br>(N=3)    | 4            |             | 11  | 12  | 13  | 14  | 15  | 16  | 21  | 22  |

|    |                |              |             | 23  | 24  | 25  | 26  | 31  | 32  | 33  | 34  |

|    |                |              |             | 35  | 36  | 41  | 42  | 43  | 44  | 45  | 46  |

| 7  | 16<br>(N=2)    | 2            |             | 11  | 12  | 13  | 14  | 15  | 16  | 17  | x   |

|    |                |              |             | 21  | 22  | 23  | 24  | 25  | 26  | 27  | x   |

| 8  | 16<br>(N=2)    | 2            |             | 11  | 12  | 13  | 14  | 15  | 16  | 17  | 18  |

|    |                |              |             | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  |

| 10 | 24<br>(N=3)    | 2            |             | 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 |

|    |                |              |             | 109 | 110 | x   | x   | 201 | 202 | 203 | 204 |

|    |                |              |             | 205 | 206 | 207 | 208 | 209 | 210 | x   | x   |

| 12 | 24<br>(N=3)    | 2            |             | 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 |

|    |                |              |             | 109 | 110 | 111 | 112 | 201 | 202 | 203 | 204 |

|    |                |              |             | 205 | 206 | 207 | 208 | 209 | 210 | 211 | 212 |

| 16 | 16<br>(N=2)    | 1            |             | 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 |

|    |                |              |             | 109 | 110 | 111 | 112 | 113 | 114 | 115 | 116 |

| 24 | 24<br>(N=3)    | 1            |             | 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 |

|    |                |              |             | 109 | 110 | 111 | 112 | 113 | 114 | 115 | 116 |

|    |                |              |             | 117 | 118 | 119 | 120 | 121 | 122 | 123 | 124 |

【図9】

|  | DATA<br>(Kビット) | PW<br>(N×2 <sup>N-1</sup> ) | PCS<br>(M回) | 1 | 2 | 3 | 4 | 5 | 6 |

|--|----------------|-----------------------------|-------------|---|---|---|---|---|---|

|--|----------------|-----------------------------|-------------|---|---|---|---|---|---|

【図10】

【図11】

(A) 第1の比較例(M=1に固定)

| N | L | K  | M |

|---|---|----|---|

| 1 | 2 | 6  | 1 |

| 1 | 1 | 7  | 1 |

| 1 | 0 | 8  | 1 |

| 2 | 6 | 10 | 1 |

| 2 | 4 | 12 | 1 |

| 2 | 0 | 16 | 1 |

| 3 | 0 | 24 | 1 |

(B) 第2の比較例(L=0に固定)

| N | L | K  | M |

|---|---|----|---|

| 3 | 0 | 6  | 4 |

| 7 | 0 | 7  | 8 |

| 1 | 0 | 8  | 1 |

| 5 | 0 | 10 | 4 |

| 3 | 0 | 12 | 2 |

| 2 | 0 | 16 | 1 |

| 3 | 0 | 24 | 1 |

(C) 本実施形態(Kに応じてL及びMを可変)

| N(PW) | L(ダミーデータ) | K(データ) | M(PCS) |

|-------|-----------|--------|--------|

| 3     | 0         | 6      | 4      |

| 2     | 1         | 7      | 2      |

| 2     | 0         | 8      | 2      |

| 3     | 0         | 10     | 2      |

| 3     | 0         | 12     | 2      |

| 2     | 0         | 16     | 1      |

| 3     | 0         | 24     | 1      |

$$N \times 8 = (K+L) \times M \\ (i=1)$$

【図12】

(A) 第1の比較例(M=1に固定)

| N | L  | K  | M |

|---|----|----|---|

| 1 | 10 | 6  | 1 |

| 1 | 9  | 7  | 1 |

| 1 | 8  | 8  | 1 |

| 1 | 6  | 10 | 1 |

| 1 | 4  | 12 | 1 |

| 1 | 0  | 16 | 1 |

| 2 | 8  | 24 | 1 |

(B) 第2の比較例(L=0に固定)

| N | L | K  | M  |

|---|---|----|----|

| 3 | 0 | 6  | 8  |

| 7 | 0 | 7  | 16 |

| 1 | 0 | 8  | 2  |

| 5 | 0 | 10 | 8  |

| 3 | 0 | 12 | 4  |

| 1 | 0 | 16 | 1  |

| 3 | 0 | 24 | 2  |

(C) 本実施形態(Kに応じてL及びMを可変)

| N(PW) | L(ダミーデータ) | K(データ) | M(PCS) |

|-------|-----------|--------|--------|

| 3     | 0         | 6      | 8      |

| 2     | 1         | 7      | 4      |

| 2     | 0         | 8      | 4      |

| 2     | 1         | 10     | 3      |

| 3     | 0         | 12     | 4      |

| 2     | 0         | 16     | 2      |

| 3     | 0         | 24     | 2      |

$$N \times 8 \times 2 = (K+L) \times M \\ (i=2)$$

【図13】

【図14】

---

フロントページの続き

(74)代理人 100101649

弁理士 伊奈 達也

(72)発明者 本田 裕康

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 梅景 篤

(56)参考文献 特開2004-139431(JP,A)

特開2001-222249(JP,A)

特開平11-331108(JP,A)

特開2004-110876(JP,A)

特開2003-272359(JP,A)

特開2004-310963(JP,A)

特開2003-141059(JP,A)

特開平11-112573(JP,A)

特開平03-078344(JP,A)

特開平11-161466(JP,A)

特開2004-061612(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 13 / 38 - 13 / 42

G 06 F 13 / 10 - 13 / 14

G 06 F 13 / 20 - 13 / 378

G 06 F 3 / 06 - 3 / 08