(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4054093号

(P4054093)

(45) 発行日 平成20年2月27日(2008.2.27)

(24) 登録日 平成19年12月14日(2007.12.14)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 29/78

623Z

H01L 21/822 (2006.01)

H01L 27/04

H

H01L 27/04 (2006.01)

請求項の数 7 (全 27 頁)

(21) 出願番号

特願平9-277133

(22) 出願日

平成9年10月9日(1997.10.9)

(65) 公開番号

特開平11-121750

(43) 公開日

平成11年4月30日(1999.4.30)

審査請求日

平成15年9月22日(2003.9.22)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 山口 泰男

東京都千代田区丸の内二丁目2番3号 三

菱電機株式会社内

(72) 発明者 一法師 隆志

東京都千代田区丸の内二丁目2番3号 三

菱電機株式会社内

審査官 河本 充雄

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

S O I 基板上に形成され、各信号端子に接続される信号ノードにそれぞれ対応する入出力保護回路部と、前記信号ノードに接続された内部回路とを有する半導体装置であって、電源電位に接続される電源ノードと、

基準電位に接続される基準電位ノードとを備え、

前記入出力保護回路部は、

前記電源ノードと前記信号ノードとの間に設けられ、それぞれ P N 接合部を有するとともに前記信号端子に、前記電源電位と前記基準電位との間の電位である動作信号が印加されるとき逆方向バイアスとなり、第 1 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 1 の放電素子と、第 2 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 2 の放電素子と、

前記信号ノードと前記基準電位ノードとの間に設けられ、それぞれ P N 接合部を有するとともに前記信号端子に前記動作信号が印加されるとき逆方向バイアスとなり、第 1 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 3 の放電素子と、第 2 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 4 の放電素子と、

を備える、

半導体装置。

## 【請求項 2】

前記第 1 及び第 3 の放電素子は第 1 の導電型の第 1 及び第 3 の M O S ロンジスタを含

10

20

み、前記第2及び第4の放電素子は第2の導電型の第2及び第4のMOSトランジスタを含み、前記第1及び第3のMOSトランジスタの制御電極はそれぞれ前記基準電位ノードに接続され、前記第2及び第4のMOSトランジスタの制御電極はそれぞれ前記電源ノードに接続されていることを特徴とする。

請求項1記載の半導体装置。

**【請求項3】**

前記電源電位は前記基準電位より高く、前記第1の導電型はN型であり、前記第2の導電型はP型であり、前記第1の極性は負、前記第2の極性は正である。

請求項2記載の半導体装置。

**【請求項4】**

前記信号端子と前記信号ノードとの間に介挿される第1の内部抵抗と、

前記信号ノードと前記内部回路との間に介挿される第2の内部抵抗と、

をさらに備える請求項2記載の半導体装置。

**【請求項5】**

前記第1の放電素子は第1の導電型のMOSトランジスタであり、その制御電極が前記基準電位ノードに接続され、前記第2及び第3の放電素子はダイオードであり、前記第4の放電素子は第2の導電型のMOSトランジスタであり、その制御電極は前記電源ノードに接続されていることを特徴とする。

請求項1記載の半導体装置。

**【請求項6】**

前記電源電位は前記基準電位より高く、前記第1の導電型はN型であり、前記第2の導電型はP型であり、前記第1の極性は負、前記第2の極性は正である。

請求項5記載の半導体装置。

**【請求項7】**

前記信号端子と前記信号ノードとの間に介挿される第1の内部抵抗と、

前記信号ノードと前記内部回路との間に介挿される第2の内部抵抗と、

をさらに備える請求項5記載の半導体装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

この発明は、SOI基板上にMOSトランジスタを形成した半導体装置に関し、特のその入出力保護機能に関する。

**【0002】**

**【従来の技術】**

バルクシリコン基板上にMOSデバイスを形成する場合、サージをPN接合を通じて基板に放電することができるが、埋め込み絶縁層上のSOI層にMOSデバイスを形成したSOI(Silicon-on-insulator)デバイスの場合、埋め込み絶縁層により基板にサージを逃す経路が構造的に存在しない。特に、MOSトランジスタのソース領域及びドレイン領域が埋め込み酸化膜まで達する薄膜SOI構造では縦方向の放電経路は存在せず、構造上横方向への放電が必須となる。このため、MOSトランジスタやダイオードを通じて横方向に電源線や接地線に放電することになる。

**【0003】**

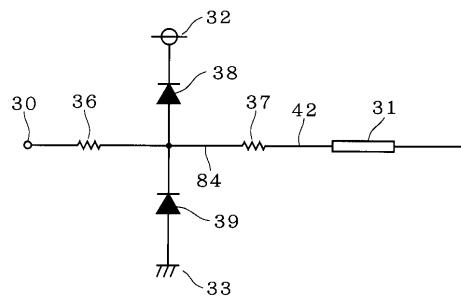

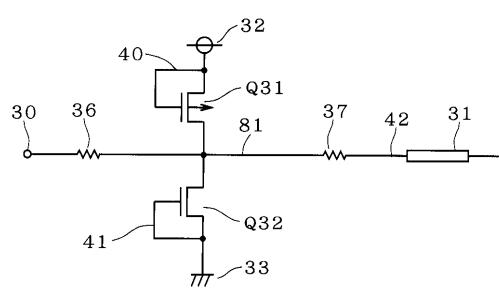

図31は従来のSOI構造での入出力保護回路の回路構成を示す回路図である。同図に示すように、まず、信号端子30に突入電流を制限する抵抗36(以下、「保護抵抗」と呼ぶ)の一端を接続し、信号端子30よりサージ電圧が内部に伝わるのを遅らせ過大な電流が流れるのを防いでいる。次に電源(ノード)32と接地レベル(ノード)33との間に電荷を逃すための放電素子として、PMOSトランジスタQ31及びNMOSトランジスタQ32を直列に設けている。ここで、PMOSトランジスタQ31及びNMOSトランジスタQ32それぞれのゲートは電源32及び接地レベル33に接続され、それぞれのドレインは共通に保護抵抗36の他端に接続される。したがって、PMOSトランジスタQ

10

20

30

40

50

3 1 及び N M O S トランジスタ Q 3 2 は通常時オフ状態となっている。

**【 0 0 0 4 】**

サージ電圧が信号端子 3 0 に印加された場合には、各 M O S トランジスタ Q 3 1 , Q 3 2 のアバランシェ降伏により、速やかに電荷を電源 3 2 あるいは接地レベル 3 3 に放電させ内部素子 3 1 を保護する。さらに、保護抵抗 3 6 の他端と内部抵抗 3 7 の一端を接続し、内部抵抗 3 7 の他端に内部素子 3 1 を接続するように構成することにより、内部素子 3 1 へのサージ電圧が伝播しにくくしている。

**【 0 0 0 5 】**

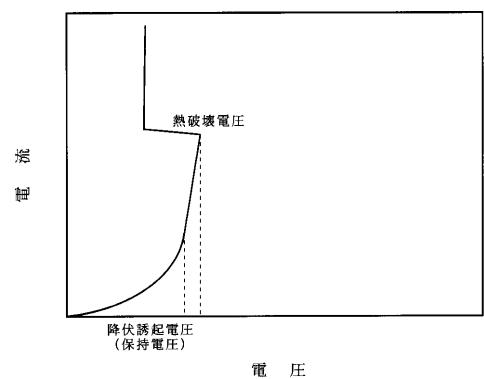

図 3 2 は放電素子としてダイオード 3 8 , 3 9 を用いて同様に形成した入出力保護回路である。同図に示すように、まず、信号端子 3 0 に保護抵抗 3 6 の一端を接続し、信号端子 3 0 よりサージ電圧が内部に伝播するのを遅らせ過大な電流が流れるのを防いでいる。次に電源 3 2 と接地レベル 3 3 との間に電荷を逃すための放電素子として、ダイオード 3 8 , 3 9 を直列に設けている。ここで、ダイオード 3 8 のカソードが電源 3 2 に接続され、ダイオード 3 9 のアノードが接地レベル 3 3 に接続される。したがって、ダイオード 3 8 , 3 9 は電源 3 2 , 接地レベル 3 3 間を逆方向に接続される。

10

**【 0 0 0 6 】**

サージ電圧が信号端子 3 0 に印加された場合には、ダイオード 3 8 , 3 9 の逆方向アバランシェ降伏あるいは順方向電流により速やかに電荷を電源 3 2 あるいは接地レベル 3 3 に放電させ内部素子 3 1 を保護する。さらに、保護抵抗 3 6 と内部素子 3 1 との間に内部抵抗 3 7 を介挿することにより、内部素子 3 1 へのサージ電圧が伝播しにくくしている。

20

**【 0 0 0 7 】**

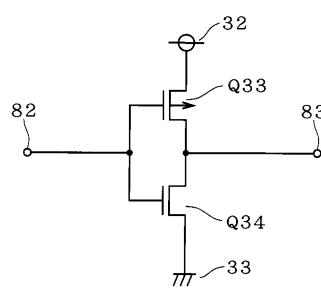

図 3 3 には典型的な内部回路の一つであるインバータ回路を示している。同図に示すように、電源 3 2 , 接地レベル 3 3 間に P M O S トランジスタ Q 3 3 及び N M O S トランジスタ Q 3 4 が直列に接続され、 P M O S トランジスタ Q 3 3 及び N M O S トランジスタ Q 3 4 のゲートが共通に入力信号端子 8 2 に接続され、ドレインが共通に出力信号端子 8 3 に接続される。

20

**【 0 0 0 8 】**

図 3 3 で示した内部回路に対し、図 3 1 , 図 3 2 に示した構成の入出力保護回路が入力信号端子 8 2 ( 内部回路の入力部 ) に接続された場合は入力保護回路として機能し、出力信号端子 8 3 ( 内部回路の出力部 ) に接続された場合は出力保護回路として機能する。保護回路の機能、動作は入力部、出力部とも同様であるので、以下「入出力保護回路」として述べる。但し、出力保護回路として使用する場合は抵抗を付加しない事が多い。

30

**【 0 0 0 9 】**

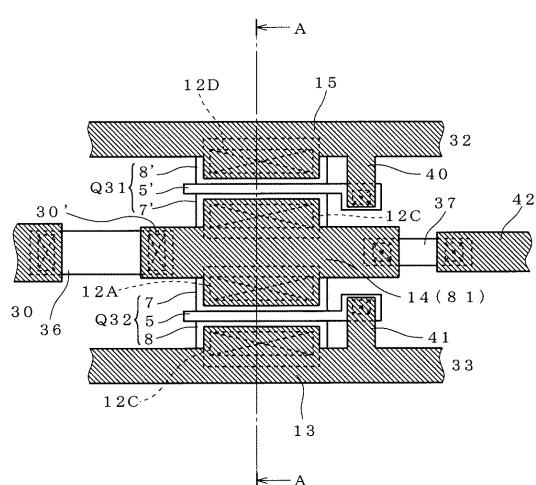

図 3 4 は図 3 1 に示した M O S 型の入出力保護回路の平面構造を示す平面図、図 3 5 は図 3 4 の A - A 断面図である。これらの図に示すように、シリコン基板 1 上には絶縁層である埋め込み酸化膜 2 を挟んで S O I 層であるシリコン薄膜 3 が設けられる。シリコン薄膜 3 は層間絶縁膜 1 1 によって 2 つの島 1 8 A , 1 8 B に分離されており、  $10^{17} / \text{cm}^3$  程度の不純物 ( N M O S では p 型 , P M O S では n 型 ) が導入されたチャネル形成領域 6 , 6 、チャネル形成領域 6 を挟んで  $10^{20} / \text{cm}^3$  程度の不純物 ( N M O S では n 型 , P M O S では p 型 ) が導入されたドレイン領域 7 及びソース領域 8 、チャネル形成領域 6 を挟んで  $10^{20} / \text{cm}^3$  程度の不純物が導入されたドレイン領域 7 及びソース領域 8 が設けられる。さらに、シリコン薄膜 3 のチャネル形成領域 6 , 6 並びにドレイン領域 7 , 7 及びソース領域 8 , 8 の一部上にはゲート酸化膜 4 , 4 を挟んでゲート電極 5 , 5 がそれぞれ形成される。したがって、島 1 8 A にはゲート酸化膜 4 、ゲート電極 5 、チャネル形成領域 6 、ドレイン領域 7 及びソース領域 8 によって N M O S トランジスタ Q 3 2 が形成され、島 1 8 B にはゲート酸化膜 4 、ゲート電極 5 、チャネル形成領域 6 、ドレイン領域 7 及びソース領域 8 からなる P M O S トランジスタ Q 3 1 が形成される。

40

**【 0 0 1 0 】**

さらに、層間絶縁膜 1 1 が島 1 8 A , 1 8 B を分離するとともにシリコン薄膜 3 上全面に

50

形成され、ドレイン領域 7, 7 の一部、ソース領域 8, 8 の一部上の層間絶縁膜 11 にコンタクトホール 12 A ~ 12 D が設けられ、コンタクトホール 12 A, 12 B を介してドレイン領域 7, 7 に電気的に接続されたアルミ配線 14 が設けられ、コンタクトホール 12 C を介してソース領域 8 に電気的に接続されたアルミ配線 13 が設けられ、コンタクトホール 12 D を介してソース領域 8 に電気的に接続されたアルミ配線 15 が設けられる。そして、アルミ配線 13 は接地レベル 33 に接続され、アルミ配線 14 は入力部 30 に接続され、アルミ配線 15 は電源 32 に接続される。なお、入力部 30 は図 32 に示すように保護抵抗 36 の他端に接続される部分を意味する。また、図 34において層間絶縁膜 11 は省略している。

## 【0011】

10

図 34 に示すように、信号端子 30 と放電素子である PMOS ドランジスタ Q31, NMOS ドランジスタ Q32 には、ゲート電極材料やシリコン薄膜で形成された保護抵抗 36 が、さらに、放電素子 Q31, Q32 と内部素子 31 との間にゲート電極材料やシリコン薄膜で形成された内部抵抗 37 が設けられている。通常、保護抵抗 36 は放電素子 Q31, Q32 に流れる突入電流に耐えるために、内部抵抗 37 よりも幅を広くして電流密度を低減している。

## 【0012】

ここで、PMOS ドランジスタ Q31 のゲート電極 5 はゲート電位固定配線 40 により電源 32 に、NMOS ドランジスタ Q32 のゲート電極 5 もゲート電位固定配線 41 により接地レベル 33 に接続されており、おののオフ状態に設定されている。

20

## 【0013】

次に動作について、図 31, 図 34 及び図 35 を参照して説明する。静電気によるサージは信号端子 30 から入り、まず保護抵抗 36 により遅延させ放電素子 Q31, Q32 に大きな突入電流の流れることを防ぐ。保護抵抗 36 を伝播したサージは次に放電素子 Q31, Q32 を介して速やかに電源 32 または接地レベル 33 に放出される。ここで、内部抵抗 37 は、サージを内部素子方向ではなく放電素子方向に流す役割がある。保護抵抗 36 を伝播したサージは放電素子部に印加される。ここで、正のサージ電圧が印加されると、NMOS ドランジスタ Q32 のドレイン領域 7 とチャネル形成領域 6 との間の接合が降伏し、接地レベル 33 にサージを放出する。同時に PMOS ドランジスタ Q31 が順方向バイアスされ、電源 32 にもサージが放出される。また、負のサージ電圧が印加される場合には逆に PMOS ドランジスタ Q31 のドレイン領域 7 とチャネル形成領域 6 との間の接合が降伏し電源 32 にサージを放出するとともに、NMOS ドランジスタ Q32 が順方向バイアスされてサージ放出が行われる。なお、通常の動作時には、PMOS ドランジスタ Q31 及び NMOS ドランジスタ Q32 はオフ状態であるため、信号端子 30 に印加される動作信号は保護抵抗 36、内部抵抗 37 を経由して内部素子 31 に伝播する。

30

## 【0014】

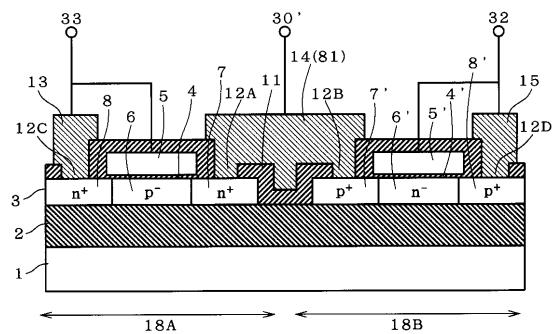

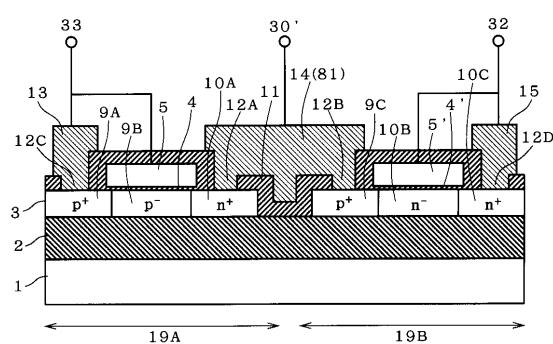

図 36 は図 32 に示したダイオード型の入出力保護回路の断面構造を示す断面図である。同図に示すように、シリコン基板 1 上には絶縁層である埋め込み酸化膜 2 を挟んでシリコン薄膜 3 が設けられる。シリコン薄膜 3 は層間絶縁膜 11 によって 2 つの島 19A, 19B に分離されており、 $10^{17} / \text{cm}^3$  程度の p 型の不純物が導入されたアノード領域 9B、 $10^{17} / \text{cm}^3$  程度の n 型の不純物が導入されたカソード領域 10B がそれぞれ設けられ、アノード領域 9B を挟んでアノード領域 9A 及びカソード領域 10A が設けられ、カソード領域 10B を挟んでアノード領域 9C 及びカソード領域 10C が設けられる。なお、アノード領域 9A 及びアノード領域 9C には  $10^{20} / \text{cm}^3$  程度の p 型の不純物が導入され、カソード領域 10A 及びカソード領域 10C には  $10^{20} / \text{cm}^3$  程度の n 型の不純物が導入される。

40

## 【0015】

さらに、シリコン薄膜 3 のアノード領域 9B 並びにアノード領域 9A 及びカソード領域 10A の一部上には酸化膜 4 を介して電極 5 が形成され、カソード領域 10B 並びにアノード領域 9C 及びカソード領域 10C の一部上には酸化膜 4 を介して電極 5 が形成され

50

る。アノード領域 9 A , 9 B 及びカソード領域 10 A によってダイオード 39 が構成され、アノード領域 9 C 、カソード領域 10 B 及び 10 C によってダイオード 38 が構成される。

#### 【 0 0 1 6 】

ダイオード部の構成は図 3 5 で示した構造と同様である。ただし、チャネル形成領域 6 、ソース領域 8 及びドレイン領域 7 それぞれにアノード領域 9 B 、アノード領域 9 A 及びカソード領域 10 A が置き代わり、チャネル形成領域 6 、ドレイン領域 7 及びソース領域 8 それにカソード領域 10 B 、アノード領域 9 C 及びカソード領域 10 C が置き代わっている。また、電極 5 , 5 はアノード領域 9 A , 9 C 及びカソード領域 10 A , 10 C 形成時のマスクして利用されるが、素子の構成要素としては機能しない。 10

#### 【 0 0 1 7 】

次に動作について、図 3 2 及び図 3 6 に示す入出力保護回路はダイオード 39 のアノード領域 9 B とカソード領域 10 Aとの間の接合の降伏、ダイオード 38 のアノード領域 9 C とカソード領域 10 B との間の接合の降伏を伴う放出以外は図 3 1 及び図 3 5 に示す入出力保護回路の場合と同様である。

#### 【 0 0 1 8 】

##### 【発明が解決しようとする課題】

S O I 構造においては、埋め込み酸化膜 2 の存在により熱伝導率が悪く、バルク基板上に形成されるバルク素子と同じ電力を放電素子に投入しても、温度上昇が大きく（バルク基板の場合の 3 倍程度の温度上昇がある）、2 次降伏（熱暴走、thermal runaway）を引き起こして破壊にいたりやすい。さらに、電流のが不均一に流れ、一部の素子に集中することにより、電流の集中する素子に急激な温度上昇が生じてその素子だけが 2 次降伏し、結果として装置全体の E S D ( ElectroS tatic D ischarge; 静電気放電 ) 耐性の低下を招いてしまうという問題点があった。 20

#### 【 0 0 1 9 】

さらに、S O I 構造においては、シリコン薄膜 3 の品質がバルク基板ほど良好でないため、シリコン薄膜 3 上に形成されるゲート酸化膜 4 の膜質が劣化しやすく E S D 耐性が低下するという問題点がある。ゲート酸化膜 4 の膜質の劣化は特に、絶縁層 2 と段差が形成されるシリコン薄膜 3 の活性領域境界部（分離端）で顕著となる。 30

#### 【 0 0 2 0 】

この発明は上記問題点を解決するためになされたもので、E S D 耐性の向上を図ったS O I 構造の半導体装置を得ることを目的とする。

#### 【 0 0 2 1 】

##### 【課題を解決するための手段】

この発明に係る請求項 1 記載の半導体装置は、S O I 基板上に形成され、各信号端子に接続される信号ノードにそれぞれ対応する入出力保護回路部と、前記信号ノードに接続された内部回路とを有しており、電源電位に接続される電源ノードと、基準電位に接続される基準電位ノードとを備え、前記入出力保護回路部は、前記電源ノードと前記信号ノードとの間に設けられ、それぞれ P N 接合部を有するとともに前記信号端子に、前記電源電位と前記基準電位との間の電位である動作信号が印加されるとき逆方向バイアスとなり、第 1 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 1 の放電素子と、第 2 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 2 の放電素子と、前記信号ノードと前記基準電位ノードとの間に設けられ、それぞれ P N 接合部を有するとともに前記信号端子に前記動作信号が印加されるとき逆方向バイアスとなり、第 1 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 3 の放電素子と、第 2 の極性を有するサージ電圧が印加されたとき順方向バイアスとなる第 4 の放電素子とを備えている。 40

#### 【 0 0 2 2 】

また、請求項 2 記載の半導体装置において、前記第 1 及び第 3 の放電素子は第 1 の導電型の第 1 及び第 3 の M O S ロンジスタを含み、前記第 2 及び第 4 の放電素子は第 2 の導

電型の第2及び第4のMOSトランジスタを含み、前記第1及び第3のMOSトランジスタの制御電極はそれぞれ前記基準電位ノードに接続され、前記第2及び第4のMOSトランジスタの制御電極はそれぞれ前記電源ノードに接続されている。

また、請求項3記載の半導体装置において、前記電源電位は前記基準電位より高く、前記第1の導電型はN型であり、前記第2の導電型はP型であり、前記第1の極性は負、前記第2の極性は正である。

また、請求項4記載の半導体装置において、前記信号端子と前記信号ノードとの間に介挿される第1の内部抵抗と、前記信号ノードと前記内部回路との間に介挿される第2の内部抵抗とをさらに備えている。

#### 【0023】

10

また、請求項5記載の半導体装置において、前記第1の放電素子は第1の導電型のMOSトランジスタであり、その制御電極が前記基準電位ノードに接続され、前記第2及び第3の放電素子はダイオードであり、前記第4の放電素子は第2の導電型のMOSトランジスタであり、その制御電極は前記電源電位ノードに接続されている。

また、請求項6記載の半導体装置において、前記電源電位は前記基準電位より高く、前記第1の導電型はN型であり、前記第2の導電型はP型であり、前記第1の極性は負、前記第2の極性は正である。

#### 【0024】

20

さらに、請求項7記載の半導体装置は、前記信号端子と前記信号ノードとの間に介挿される第1の内部抵抗と、前記信号ノードと前記内部回路との間に介挿される第2の内部抵抗とを備えている。

#### 【0035】

##### 【発明の実施の形態】

<< 実施の形態 1 >>

< 原理 >

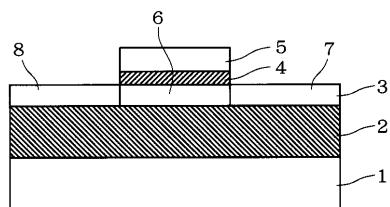

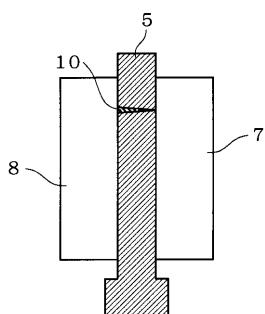

図18はSOI構造を示す断面図である。同図に示すように、シリコン基板1上に埋め込み酸化膜2が形成され、埋め込み酸化膜2上にシリコン薄膜3が形成される。このように、シリコン基板1、埋め込み酸化膜2及びシリコン薄膜3からなる構成はSOI基板といわれている。そして、シリコン薄膜3上にゲート酸化膜4が選択的に形成され、ゲート酸化膜4上にゲート電極5が形成される。ゲート酸化膜4下のシリコン薄膜3がチャネル形成領域6となり、チャネル形成領域6に隣接したシリコン薄膜3内の領域がドレイン領域7及びソース領域8となる。

30

#### 【0036】

このようなSOI構造は、前述したように、熱伝導率の悪い（シリコンの約1/10）埋め込み酸化膜2が存在するため、サーボ電圧印加時に発生する熱が蓄積し、熱暴走により、SOI基板上に形成される半導体素子の永久的な破壊が起こりやすい。

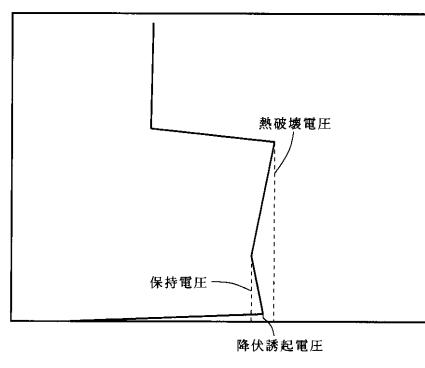

#### 【0037】

40

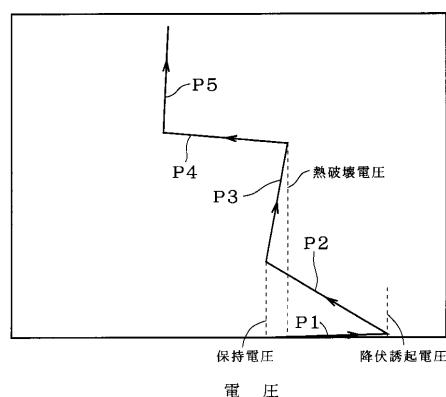

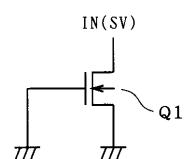

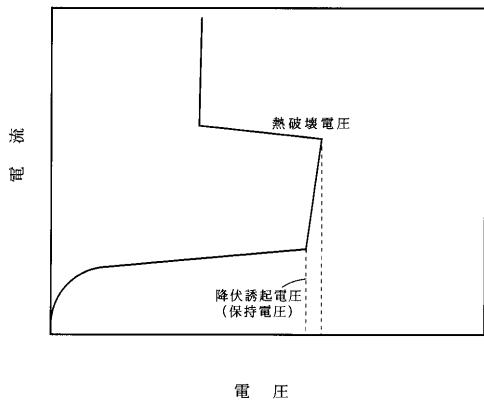

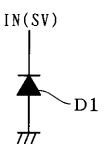

図19は逆方向バイアス接続時のNMOSトランジスタの放電特性を示すグラフである。図19のグラフは図20のようにソース及びゲートが接地されたNMOSトランジスタQ1のドレインに入力電圧IN（サーボ電圧SV）が印加された場合等の逆方向バイアス接続時の熱暴走の経緯を示しており、図19で示す熱暴走のプロセスは部分プロセスP1～P5からなる。

#### 【0038】

図20で示したNMOSトランジスタQ1のドレインに通常時を大きく上回る正のサーボ電圧SVが印加されると、そのドレイン電圧は急激に上昇する（P1）。部分プロセスP1の期間中はNMOSトランジスタQ1は逆方向バイアスとなるため電流はほとんど流れない。そして、降伏誘起電圧に達するとNMOSトランジスタQ1はアバランシェ降伏して、寄生バイポーラ動作を起こし保持電圧まで低下する（P2）。その後、NMOSトランジスタQ1の内部抵抗により再び上昇し（P3）、熱破壊電圧に達するとNMOSトランジスタQ1の一部を形成するシリコン部分が溶融状態となり、急激にソース、ドレイン

50

間の抵抗値が低下するため電圧が低下する( P 4 )。その結果、ソース、ドレイン間の抵抗が低下したN M O SトランジスタQ 1に集中して電流が流れるという正帰還が働き( P 5 )、N M O SトランジスタQ 1は完全に破壊されてしまう。例えば、図2 1に示すように、熱破壊によってゲート電極5(あるいはチャネル形成領域6)に大きな欠陥部分10が生じ、トランジスタ動作が不可能となる。

#### 【 0 0 3 9 】

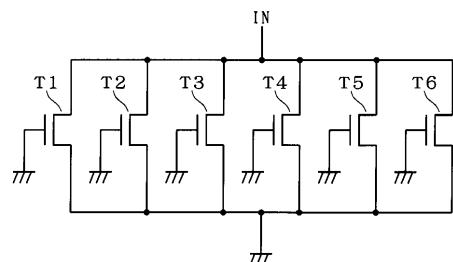

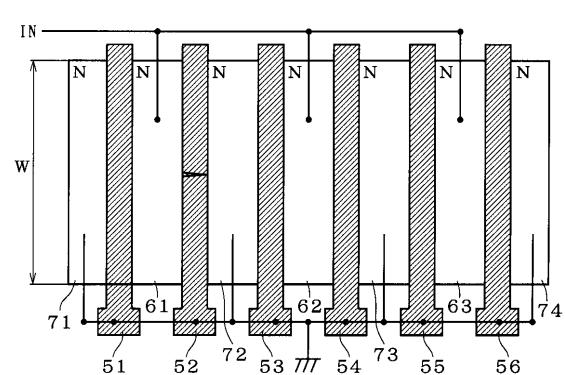

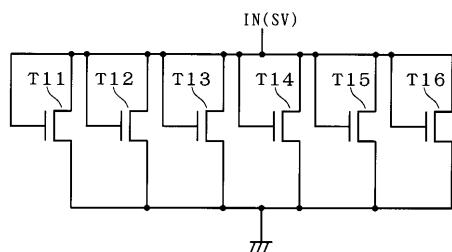

通常、S O I基板上の入出力保護回路としてN M O Sトランジスタを逆方向バイアスで設ける場合、図2 2に示すように、入力(電圧)I Nと接地レベルとの間にチャネル幅WのN M O Sトランジスタが並列に接続されるようとする。図2 2の例では、図2 3に示すように、ゲートが接地された6つのN M O SトランジスタT 1 ~ T 6が入力I Nと接地レベルとの間に並列に設けられることになる。なお、N M O SトランジスタT 1はゲート電極5 1、ドレイン領域6 1及びソース領域7 1により構成され、N M O SトランジスタT 2はゲート電極5 2、ドレイン領域6 1及びソース領域7 2より構成され、N M O SトランジスタT 3はゲート電極5 3、ドレイン領域6 2及びソース領域7 2より構成され、N M O SトランジスタT 4はゲート電極5 4、ドレイン領域6 2及びソース領域7 3より構成され、N M O SトランジスタT 5はゲート電極5 5、ドレイン領域6 3及びソース領域7 3より構成され、N M O SトランジスタT 6はゲート電極5 6、ドレイン領域6 3及びソース領域7 4より構成される。なお、サージ電圧は、信号端子3 0から印加される。

#### 【 0 0 4 0 】

このように、S O I基板上の入出力保護回路として6個のN M O SトランジスタT 1 ~ T 6を入力I N、接地レベル間に並列に設けることにより、入力I N、接地レベル間を電流が流れる場合、6つのN M O SトランジスタT 1 ~ T 6に分割して電流が流れるようにしている。

#### 【 0 0 4 1 】

しかしながら、N M O SトランジスタT 1 ~ T 6のうち、1つのトランジスタがアバランシェ降伏電圧に到達すると、そのトランジスタのソース、ドレイン間の抵抗が減少するため、アバランシェ降伏したトランジスタに電流が集中するため、当該トランジスタが熱破壊電圧に達し熱破壊するのを抑制することはできない。

#### 【 0 0 4 2 】

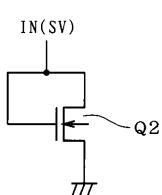

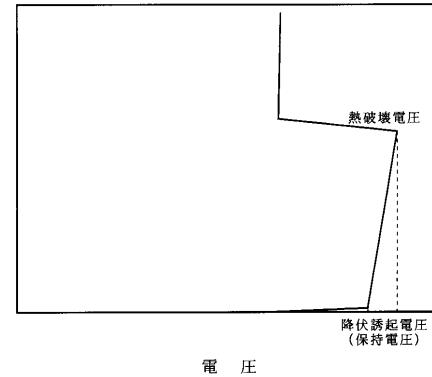

図2 5は順方向バイアス接続時のN M O Sトランジスタの放電特性を示すグラフである。図2 5のグラフは図2 4のようにソースが接地されたN M O SトランジスタQ 2のドレイン及びゲートに入力電圧I N(サージ電圧S V)が印加された場合等の順方向バイアス接続時の熱暴走の経緯を示している。

#### 【 0 0 4 3 】

図2 5は、図2 4で示す順方向バイアス接続時のN M O Sトランジスタの放電特性を示すグラフである。図2 5に示すように、順方向バイアス接続時は降伏誘起電圧に達するとドレイン電圧が低下するというスナップバック現象は生じない。したがって、図2 6に示すように、入力I Nと接地レベルとの間に並列に設けられた複数のN M O SトランジスタT 1 1 ~ T 1 6は、サージ電圧S Vの印加とともにほぼ均一にアバランシェ降伏を起こし、さらなるサージ電圧S Vの印加により熱破壊電圧に達すると逆方向バイアス接続時と同様に熱暴走状態となる。

#### 【 0 0 4 4 】

図2 6で示すように複数のN M O Sトランジスタを並列に接続すると、そのうち一部のトランジスタがアバランシェ降伏すると、ドレイン電圧が上昇して他のトランジスタもアバランシェ降伏する。その結果、すべてのトランジスタがアバランシェ降伏することになり、すべてのトランジスタに均一に電流が流れるため、降伏誘起電圧より高い熱破壊電圧で熱破壊される。

#### 【 0 0 4 5 】

このように、順方向バイアス接続時は、逆方向バイアス接続時のようにアバランシェ降伏した一部のトランジスタに集中して電流が流れるという現象が起こらないため、比較的良

10

20

30

40

50

好な ESD 耐性を得ることができる。

**【0046】**

図28は逆方向バイアス接続時のダイオードの放電特性を示すグラフである。図28のグラフは図27のようにアノードが接地されたダイオードD1のカソードにサージ電圧SVが印加された場合等の逆方向バイアス接続時の熱暴走の経緯を示している。

**【0047】**

ダイオードでは寄生バイポーラ動作が起こらないので、アバランシェ降伏後も電圧上昇が続き、熱破壊に至る。熱破壊電圧が降伏誘起電圧よりも高いことは、上記した順方向バイアス接続時のNMOStランジスタと同様に、電流集中を防ぐという観点から有効であるが、ダイオードの降伏誘起電圧自体が高い(MOSトランジスタの2~3倍程度)ため、電圧と電流の積で表される消費電力が増大し(すなわち熱も増加し)、結果としてESD耐性の劣化を招いてしまう。ただし、高濃度接合などでダイオードの接合耐圧を低下させると、降伏誘起電圧を低下させることができ、ESD耐性の改善することができる。

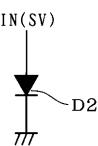

**【0048】**

図30は順方向バイアス接続時のダイオードの放電特性を示すグラフである。図30のグラフは図29のようにカソードが接地されたダイオードD1のアノードにサージ電圧SVが印加された場合等の順方向バイアス接続時の熱暴走の経緯を示している。

**【0049】**

ダイオードの順方向接続は低電圧で大きな電流を放電することが可能となるためESD耐性にとって望ましい放電特性が得られる。図30に示すように、電圧の増加によりアバランシェ降伏が起こり、他の素子と同様に熱破壊電圧に達すると、熱爆走により素子の永久的な破壊が起こる。

**【0050】**

以上述べてきたように、トランジスタを用いる場合でも、ダイオードを用いる場合でも順方向接続を利用したときの方が容易に電流の不均一性を防ぎ、ESD耐性を向上させることが可能になる。

**【0051】**

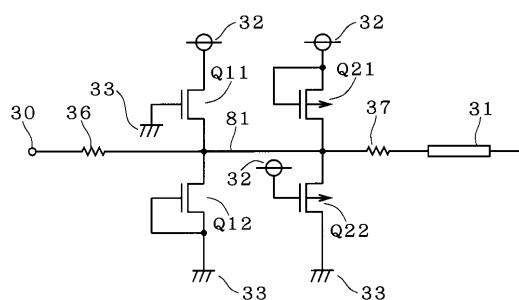

<第1の態様の構成及び動作>

図1にこの発明の実施の形態1の第1の態様である入出力保護回路の構成を示す回路図である。同図に示すように、信号端子30は保護抵抗36の一端に接続され、保護抵抗36の他端は信号線(信号ノード)81を介して内部抵抗37の一端に接続され、内部抵抗37の他端は内部素子31に接続される。

**【0052】**

また、電源32、接地レベル33間にNMOStランジスタQ11及びQ12が直列に接続されるとともに、PMOSトランジスタQ21及びQ22が直列に接続される。NMOStランジスタQ11はゲートが接地レベル33に接続され、ドレインが電源32に接続され、ソースが保護抵抗36の他端(内部抵抗37の一端)に接続される。NMOStランジスタQ12のゲート及びソースは接地レベル33に接続され、ドレインはNMOStランジスタQ11のソースに接続される。PMOSトランジスタQ21のゲート及びソースは電源32に接続され、ドレインは保護抵抗36の他端に接続され、PMOSトランジスタQ22のゲートは電源32に接続され、ソースは保護抵抗36の他端に接続され、ドレインは接地レベル33に接続される。なお、NMOStランジスタQ11、Q12及びPMOSトランジスタQ21、Q22を、図23や図26に示すように複数のMOSトランジスタの並列接続で構成してもよい。

**【0053】**

このような構成において、正のサージ電圧が信号端子30に印加された場合は、電源電圧にPMOSトランジスタQ21及びQ22の閾値電圧を加えた電圧を上回る電圧が信号端子30に印加されることになり、信号端子30に対して順方向バイアス状態となるPMOSトランジスタQ21及びQ22を介して、サージ電圧を電源32及び接地レベル33にそれぞれ放電することができる。

10

20

30

40

50

**【 0 0 5 4 】**

一方、負のサージ電圧が信号端子 3 0 に印加された場合は、接地レベルに N M O S トランジスタ Q 1 1 及び Q 1 2 の閾値電圧を差し引いた電圧を下回る電圧が信号端子 3 0 に印加されることになり、信号端子 3 0 に対して順方向バイアス状態となる N M O S トランジスタ Q 1 1 及び Q 1 2 を介して、サージ電圧を電源 3 2 及び接地レベル 3 3 に放電することができる。

**【 0 0 5 5 】**

また、通常の動作時には、信号端子 3 0 に印加される動作信号は主として接地レベル～電源レベルの電圧であるため、N M O S トランジスタ Q 1 1 , Q 1 2 及び P M O S トランジスタ Q 2 1 , Q 2 2 は全て逆方向バイアスされてオフ状態となり、動作信号は M O S トランジスタ Q 1 1 , Q 1 2 , Q 2 1 あるいは Q 2 2 を介して電源 3 2 あるいは接地レベル 3 3 に漏れることなく、保護抵抗 3 6 及び内部抵抗 3 7 を経由して内部素子 3 1 に伝達される。特に、動作信号の電圧が接地レベル～電源レベルの電圧に制限されている場合には N M O S トランジスタ Q 1 1 , Q 1 2 及び P M O S トランジスタ Q 2 1 , Q 2 2 は確実にオフ状態となる。

10

**【 0 0 5 6 】**

このように、実施の形態 1 の第 1 の態様の入出力保護回路は、正のサージ電圧、負のサージ電圧が印加されても、N M O S トランジスタ Q 1 1 及び Q 1 2 並びに P M O S トランジスタ Q 2 1 及び Q 2 2 のうち一方が、必ずサージ電圧に対して順方向バイアス状態となるため、E S D 耐性良い入出力保護回路が得られる。

20

**【 0 0 5 7 】**

また、N M O S トランジスタ Q 1 1 , Q 1 2 及び P M O S トランジスタ Q 2 1 , Q 2 2 は信号端子 3 0 に動作信号が入力された場合は逆方向バイアス状態となるように接続されているため、通常の動作時には影響を与えない。

**【 0 0 5 8 】**

この入出力保護回路では P チャネルおよび N チャネルの M O S トランジスタを 2 個ずつ用いている。通常、内部素子 3 1 として、図 3 3 に示すように、P M O S トランジスタ及び N M O S トランジスタからなる C M O S インバータを形成するが多く、2 つの C M O S インバータの構成を少し変更するだけで、実施の形態 1 の第 1 の態様の入出力保護回路を簡単に製造することができる。

30

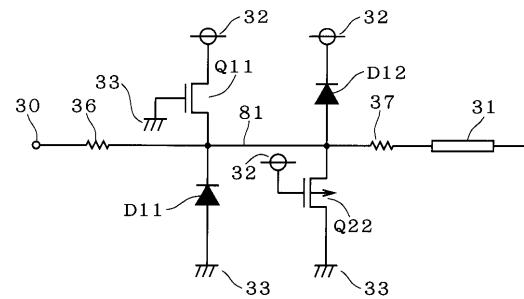

**【 0 0 5 9 】**

## &lt; 第 2 の態様の構成及び動作 &gt;

なお、第 2 の態様として、図 2 に示すように、N M O S トランジスタ Q 1 2 及び P M O S トランジスタ Q 2 1 をダイオード D 1 1 及び D 1 2 に置き換え、ダイオード D 1 1 のカソードを保護抵抗 3 6 の他端に接続するとともにアノードを接地レベル 3 3 に接続し、ダイオード D 1 2 のアノードを信号線 8 1 に接続するとともにカソードを電源 3 2 に接続するように構成してもよい。

**【 0 0 6 0 】**

第 2 の態様において、正のサージ電圧が信号端子 3 0 に印加された場合には、信号端子 3 0 に対して順方向バイアス状態のダイオード D 1 2 及び P M O S トランジスタ Q 2 2 を介して、サージ電圧を電源 3 2 及び接地レベル 3 3 にそれぞれ放電することができる。

40

**【 0 0 6 1 】**

一方、負のサージ電圧が信号端子 3 0 に印加された場合には、信号端子 3 0 に対して順方向バイアス状態の N M O S トランジスタ Q 1 1 及びダイオード D 1 1 を介して、サージ電圧を電源 3 2 及び接地レベル 3 3 にそれぞれ放電することができる。

**【 0 0 6 2 】**

このように、実施の形態 1 の第 2 の態様の入出力保護回路は、正あるいは負のサージ電圧が印加された場合、N M O S トランジスタ Q 1 1 及びダイオード D 1 1 並びにダイオード D 1 2 及び P M O S トランジスタ Q 2 2 のうち一方が、必ずサージ電圧に対して順方向バイアス状態となるため、E S D 耐性良い入出力保護回路が得られる。

50

**【 0 0 6 3 】**

また、N M O SトランジスタQ 1 1、ダイオードD 1 1、D 1 2及びP M O SトランジスタQ 2 2は信号端子3 0に動作信号が入力された場合は常にオフ状態となるように接続されているため、通常の動作時には影響を与えない。

**【 0 0 6 4 】**

さらに、第2の態様は、導電型式のM O Sトランジスタを1個ずつバランス良く用いているため、第1の態様と同様、比較的簡単に製造することができる。

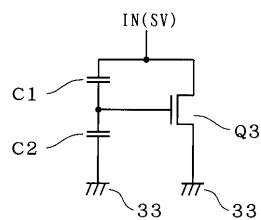

**【 0 0 6 5 】**

<< 実施の形態2 >>

< 原理 >

10

図3はトランジスタの逆方向バイアスのゲートカップリング構造を示す回路図である。同図に示すように、入力信号I N(サージ電圧S V)に対し逆方向バイアス接続されたN M O SトランジスタQ 3のゲートはキャパシタC 1を介して入力信号I Nを受け、キャパシタC 2を介して接地レベル3 3に接続される。すなわち、N M O SトランジスタQ 3のゲートをキャパシタC 1、C 2によって電気的にフローティング状態にした構造がゲートカップリング構造である。このようなゲートカップリング構造はE S D耐性を向上させる一つの手法として、例えばIEEE IRPS 1992 p・141に報告されている。

**【 0 0 6 6 】**

このようなゲートカップリング構造では、入力信号I Nが通常の動作電圧の場合、キャパシタC 1、C 2のカップリングによりN M O SトランジスタQ 3のゲート電位上昇が低く抑えられるため、N M O SトランジスタQ 3はオフ状態となる。

20

**【 0 0 6 7 】**

一方、正のサージ電圧S Vの印加時などの場合は、N M O SトランジスタQ 3のゲート電位が上昇し電流を流すため順方向バイアス接続された状態に近づけることが可能となる。このため、図4の放電特性のグラフに示すように、降伏誘起電圧を熱破壊電圧をよりも低く設定することが可能になり、順方向バイアス時に見られたように、図3で示したゲートカップリング構造のN M O SトランジスタQ 3を入力信号I N、接地レベル3 3間に複数個並列接続した場合においても均一に電流を流すことが可能になり、E S D耐性を向上させることができる。このようなゲートカップリング構造をS O I基板上に効率的に形成したのが実施の形態2である。

30

**【 0 0 6 8 】**

< 第1の態様の構成及び動作 >

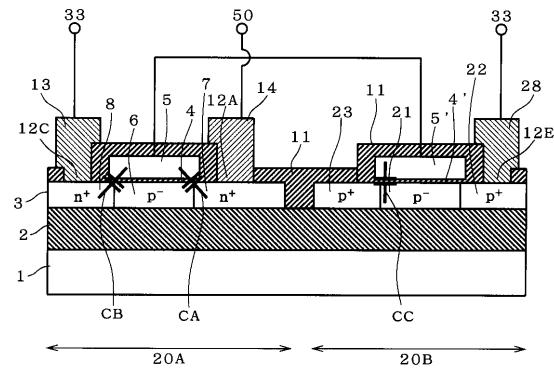

図5はこの発明の実施の形態2の第1の態様である入出力保護回路の構造を示す断面図である。同図に示すように、シリコン基板1上には絶縁層である埋め込み酸化膜2を挟んでS O I層であるシリコン薄膜3が設けられる。シリコン薄膜3は層間絶縁膜1 1によって2つの島2 0 A、2 0 Bに分離されている。島2 0 Aにおいて、 $10^{17} / \text{cm}^3$ 程度のp型の不純物が導入されたチャネル形成領域6、チャネル形成領域6を挟んで $10^{20} / \text{cm}^3$ 程度のn型の不純物が導入されたドレイン領域7及びソース領域8が形成される。一方、島2 0 Bにおいて、 $10^{15} \sim 10^{17} / \text{cm}^3$ 程度のp型の不純物が導入されたp型拡散領域2 1、p型拡散領域2 1を挟んで $10^{20} / \text{cm}^3$ 程度のp型の不純物が導入されたp型拡散領域2 2、2 3が設けられる。

40

**【 0 0 6 9 】**

さらに、島2 0 Aのシリコン薄膜3のチャネル形成領域6並びにドレイン領域7及びソース領域8の一部上にはゲート酸化膜4を挟んでゲート電極5が形成される。一方、島2 0 Bのシリコン薄膜3のp型拡散領域2 1及びp型拡散領域2 2、2 3の一部上にはゲート酸化膜4を挟んでゲート電極5が形成される。

**【 0 0 7 0 】**

さらに、層間絶縁膜1 1が島2 0 A、2 0 Bを分離するとともにシリコン薄膜3上全面に形成され、ドレイン領域7の一部、ソース領域8の一部及びp型拡散領域2 2の一部上の層間絶縁膜1 1にコンタクトホール1 2 A、1 2 C及び1 2 Eが設けられ、コンタクトホ

50

ール 1 2 A を介してドレイン領域 7 に電気的に接続されたアルミ配線 1 4 が設けられ、コンタクトホール 1 2 C を介してソース領域 8 に電気的に接続されたアルミ配線 1 3 が設けられ、コンタクトホール 1 2 E を介して p 型拡散領域 2 2 に電気的に接続されたアルミ配線 2 8 が設けられる。そして、アルミ配線 1 3 は接地レベル 3 3 に接続され、アルミ配線 1 4 は入力端子 5 0 に接続され、アルミ配線 2 8 は接地レベル 3 3 に接続される。なお、入力端子 5 0 は図 3 4 のように保護抵抗を介して入力信号 IN を受ける構成でも、直接入力信号 IN を受ける構成であってもよい。

#### 【 0 0 7 1 】

したがって、島 2 0 A にはゲート酸化膜 4 、ゲート電極 5 、チャネル形成領域 6 、ドレイン領域 7 及びソース領域 8 によって N M O S トランジスタ Q 3 が形成されるとともに、ゲート酸化膜 4 を挟んで平面的に重複したゲート電極 5 の一部とドレイン領域 7 の一部とによって（ゲートオーバーラップ）キャパシタ C A 、ゲート酸化膜 4 を挟んで平面的に重複したゲート電極 5 の一部とソース領域 8 の一部とによって（ゲートオーバーラップ）キャパシタ C B が形成される。10

#### 【 0 0 7 2 】

一方、島 2 0 B にはゲート酸化膜 4 、ゲート電極 5 、p 型拡散領域 2 1 ~ 2 3 によって N M O S トランジスタ Q 3 と構造が類似した疑似 M O S トランジスタ構造が得られる。そして、ゲート酸化膜 4 を挟んで平面的に従属したゲート電極 5 と p 型拡散領域 2 1 及び p 型拡散領域 2 2 , 2 3 の一部とによってキャパシタ C C が形成される。そして、キャパシタ C A は図 3 のキャパシタ C 1 に相当し、キャパシタ C B 及びキャパシタ C C の合成容量がキャパシタ C 2 に相当する。20

#### 【 0 0 7 3 】

このように、実施の形態 2 の第 1 の態様の入出力保護回路は S O I 基板上にゲートカップリング構造の M O S トランジスタを形成している。このような構成において、入力端子 5 0 からの入力信号 IN 印加時には、キャパシタ C A によってフローティング領域の電位が上昇する。ここでキャパシタ C A 基準電位である接地レベル 3 3 , ゲート電極 5 間に接続されたキャパシタ C B 及び C C の合成容量に比較して小さいため、 N M O S トランジスタ Q 3 のドレイン電位に比べ大きく低減されたゲート電位が付与されることになる。したがって、入力信号 IN が動作電圧（通常、接地レベル～電源レベル及びその近傍領域の電圧となる）である場合はそのゲート電位は N M O S トランジスタ Q 3 の閾値電圧を下回り N M O S トランジスタ Q 3 がオフ状態となる。一方、入力信号 IN が正の高電圧の場合はゲート電位が N M O S トランジスタ Q 3 の閾値電圧以上の上昇するとにより N M O S トランジスタ Q 3 がオン状態となる。すなわち、 N M O S トランジスタ Q 3 は入力信号 IN に対して順方向バイアス接続状態となる。30

#### 【 0 0 7 4 】

このように、実施の形態 2 の第 1 の態様の入出力保護回路は、効果的に降伏誘起電圧を低下させ、 E S D 耐性を向上させることができる。

#### 【 0 0 7 5 】

< 第 2 の態様の構成及び動作 >

図 6 はこの発明の実施の形態 2 の第 2 の態様である入出力保護回路の構造を示す断面図である。同図に示すように、シリコン基板 1 上には絶縁層である埋め込み酸化膜 2 を挟んで S O I 層であるシリコン薄膜 3 が設けられる。シリコン薄膜 3 は層間絶縁膜 1 1 によって 2 つの島 2 0 A , 2 0 B に分離されている。島 2 0 A の構成は図 5 で示した第 1 の態様と同様である。40

#### 【 0 0 7 6 】

島 2 0 B において、  $10^{16} / \text{cm}^3$  程度の p 型の不純物が導入されたチャネル形成領域 2 4 、チャネル形成領域 2 4 を挟んで  $10^{20} / \text{cm}^3$  程度の p 型の不純物が導入されたドレイン領域 2 5 , ソース領域 2 6 が設けられる。さらに、島 2 0 B のシリコン薄膜 3 のチャネル形成領域 2 4 並びにドレイン領域 2 5 及びソース領域 2 6 の一部上にはゲート酸化膜 4 を挟んでゲート電極 5 が形成される。50

## 【0077】

さらに、層間絶縁膜11が島20A, 20Bを分離するとともにシリコン薄膜3上全面に形成され、ドレイン領域7の一部、ソース領域8の一部及びソース領域26の一部上の層間絶縁膜11にコンタクトホール12A, 12C及び12Fが設けられ、コンタクトホール12Aを介してドレイン領域7に電気的に接続されたアルミ配線14が設けられ、コンタクトホール12Cを介してソース領域8に電気的に接続されたアルミ配線13が設けられ、コンタクトホール12Fを介してソース領域26に電気的に接続されたアルミ配線29が設けられる。そして、アルミ配線13は接地レベル33に接続され、アルミ配線14は入力端子50に接続され、アルミ配線29は接地レベル33に接続される。

## 【0078】

10

したがって、島20Aにはゲート酸化膜4、ゲート電極5、チャネル形成領域6、ドレイン領域7及びソース領域8によってN MOSトランジスタQ3が形成されるとともに、ゲート酸化膜4を挟んだゲート電極5の一部とドレイン領域7の一部とによってキャパシタCA、ゲート酸化膜4を挟んだゲート電極5の一部とソース領域8の一部とによってキャパシタCBが形成される。

## 【0079】

一方、島20Bにはゲート酸化膜4、ゲート電極5、p型拡散領域21, 25及び26によってN MOSトランジスタQ3と構造が類似した疑似N MOSトランジスタ構造が得られる。そして、ゲート酸化膜4を挟んだゲート電極5とドレイン領域25とソース領域26の一部とによってキャパシタCDが形成される。そして、キャパシタCAは図3のキャパシタC1に相当し、キャパシタCB及びキャパシタCDの合成容量がキャパシタC2に相当する。

20

## 【0080】

ただし、キャパシタCDはチャネル形成領域24が反転する程度の電圧がゲート電極5に与えられたときはじめて機能する。チャネル形成領域24は $10^{16} / cm^3$ 程度と低いため、比較的低い電圧がゲート電極5に与えられてもチャネル形成領域24は反転する。

## 【0081】

30

このように、実施の形態2の第2の態様の入出力保護回路はSOI基板上にゲートカップリング構造のMOSトランジスタを形成することにより、第1の態様と同様、入力信号INが動作信号の場合は逆方向バイアス接続状態となり、入力信号INが正の高電圧の場合は順方向バイアス接続状態となり、第1の態様と同様の効果を奏する。

## 【0082】

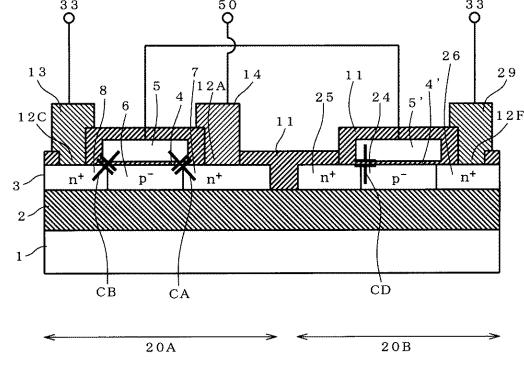

<第3の態様の構成及び動作>

図7はこの発明の実施の形態2の第3の態様である入出力保護回路の構造を示す断面図である。同図に示すように、シリコン基板1上には絶縁層である埋め込み酸化膜2を挟んでシリコン薄膜3が設けられる。シリコン薄膜3は層間絶縁膜11によって2つの島20A, 20Bに分離されている。島20Aの構成は図5で示した第1の態様と同様である。

## 【0083】

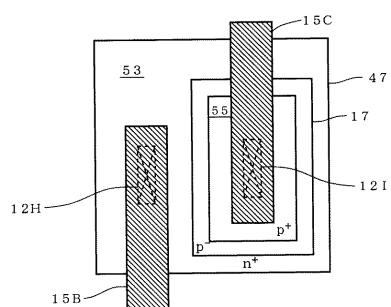

島20Bにおいて、 $10^{15} \sim 10^{17} / cm^3$ 程度のp型の不純物が導入されたp型拡散領域52, 54、チャネル形成領域52を挟んで $10^{20} / cm^3$ 程度のp型の不純物及びn型の不純物がそれぞれ導入されたp型拡散領域51及びn型拡散領域53、p型拡散領域54を挟んで $10^{20} / cm^3$ 程度のn型の不純物及びp型の不純物がそれぞれ導入されたn型拡散領域53及びp型拡散領域55が形成される。したがって、n型拡散領域53はp型拡散領域52, 54間に形成される。さらに、島20Bのシリコン薄膜3のp型拡散領域52及びp型拡散領域54上にはゲート酸化膜43及び44を挟んでゲート電極16及び17が形成される。

40

## 【0084】

さらに、層間絶縁膜11が島20A, 20Bを分離するとともにシリコン薄膜3上全面に形成され、ドレイン領域7の一部、ソース領域8の一部、p型拡散領域51の一部、n型

50

拡散領域 5 3 の一部及び p 型拡散領域 5 5 の一部上の層間絶縁膜 1 1 にコンタクトホール 1 2 A , 1 2 C 、 1 2 G 、 1 2 H 及び 1 2 I が設けられ、コンタクトホール 1 2 A を介してドレイン領域 7 に電気的に接続されたアルミ配線 1 4 が設けられ、コンタクトホール 1 2 C を介してソース領域 8 に電気的に接続されたアルミ配線 1 3 が設けられ、コンタクトホール 1 2 G を介して p 型拡散領域 5 1 に電気的に接続されたアルミ配線 1 5 A が設けられ、コンタクトホール 1 2 H を介して n 型拡散領域 5 3 に電気的に接続されたアルミ配線 1 5 B が設けられ、コンタクトホール 1 2 I を介して p 型拡散領域 5 5 に電気的に接続されたアルミ配線 1 5 C が設けられる。そして、アルミ配線 1 3 は接地レベル 3 3 に接続され、アルミ配線 1 4 は入力端子 5 0 に接続され、アルミ配線 1 5 A 及び 1 5 C は接地レベル 3 3 に接続され、アルミ配線 1 5 B は島 2 0 A のゲート電極 5 に接続される。

10

## 【 0 0 8 5 】

したがって、島 2 0 A には、第 1 及び第 2 の態様と同様に、ゲート酸化膜 4、ゲート電極 5、チャネル形成領域 6、ドレイン領域 7 及びソース領域 8によって N M O S トランジスタ Q 3 が形成されるとともに、ゲート酸化膜 4を挟んだゲート電極 5の一部とドレイン領域 7の一部とによってキャパシタ C A に相当するキャパシタ、ゲート酸化膜 4を挟んだゲート電極 5の一部とソース領域 8の一部とによってキャパシタ C B に相当するキャパシタが形成される。

## 【 0 0 8 6 】

一方、島 2 0 B にはゲート酸化膜 4 3 、ゲート電極 1 6 、 p 型拡散領域 5 1 , 5 2 及び n 型拡散領域 5 3 によって N M O S トランジスタ Q 3 と構造が類似した第 1 の疑似 M O S トランジスタ構造が得られ、ゲート酸化膜 4 4 、ゲート電極 1 7 、 p 型拡散領域 5 4 , 5 5 及び n 型拡散領域 5 3 によって N M O S トランジスタ Q 3 と構造が類似した第 2 の疑似 M O S トランジスタ構造が得られる。

20

## 【 0 0 8 7 】

そして、島 2 0 B には p 型拡散領域 5 2 と n 型拡散領域 5 3 及び n 型拡散領域 5 3 と p 型拡散領域 5 4 との接合容量の合成容量であるキャパシタ C E ( 図示せず ) が形成される。そして、キャパシタ C A は図 3 のキャパシタ C 1 に相当し、キャパシタ C B 及びキャパシタ C E の合成容量がキャパシタ C 2 に相当する。

## 【 0 0 8 8 】

このように、実施の形態 2 の第 3 の態様の入出力保護回路は S O I 基板上にゲートカップリング構造の M O S トランジスタを形成することにより、第 1 及び第 2 の態様と同様、入力信号 I N が動作信号の場合に逆方向バイアス接続状態となり、入力信号 I N が正の高電圧の場合に順方向バイアス接続状態となり、第 1 の態様と同様の効果を奏する。

30

## 【 0 0 8 9 】

さらに第 3 の態様は以下の効果も奏する。第 1 及び第 2 の態様のように M O S トランジスタ Q 3 のゲート電極 5 がフローティング状態の場合、初期電圧が不安定になる欠点がある。しかしながら、第 3 の態様ではゲート電極 5 , 接地レベル 3 3 間に接合容量からなるキャパシタ C E を用いているため、接合を流れる微少電流により、基準電位である接地レベル 3 3 に N M O S トランジスタ Q 3 のゲート電極 5 を固定することができる。したがって、第 3 の態様では、通常動作時には、初期電圧が不安定になることなく N M O S トランジスタ Q 3 のゲート電極 5 を接地レベルに固定し、サージ電圧印加時のみにゲート電位を効率的に持ち上げることができる効果を奏する。

40

## 【 0 0 9 0 】

< < 実施の形態 3 > >

< 原理 >

M O S トランジスタの E S D 耐性を向上させるにはパンチスルーガーが起きやすい構造にしてパンチスルーガー電圧を降伏誘起電圧より低下させる方法がある。このような構造の M O S トランジスタを図 2 0 に示すように入力端子に対し逆バイアス接続した場合、サージが印加時に低く設定されたパンチスルーガー電圧に達すると M O S トランジスタはパンチスルーガー現象によって早期に降伏し、図 3 0 で示したダイオードの順方向接続の放電現象と同様な放電

50

現象を起こすようになるため、E D S 耐性が向上する。

**【 0 0 9 1 】**

しかしながら、パンチスルーレ電圧を低下させるのはM O S トランジスタの動作特性を劣化させるため実動作上は望ましくない。以上の技術的背景を考慮したのが実施の形態3である。

**【 0 0 9 2 】**

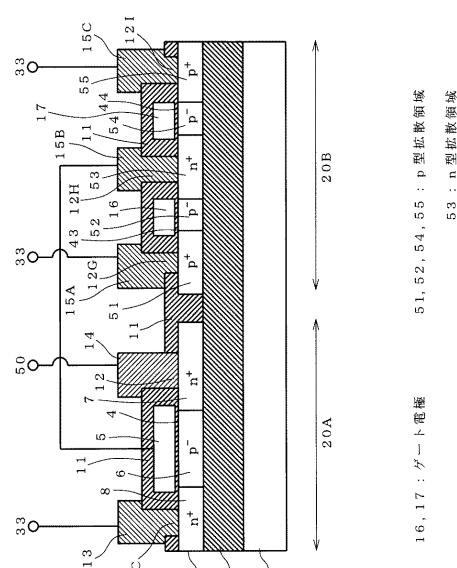

< 第1の態様の構成及び動作 >

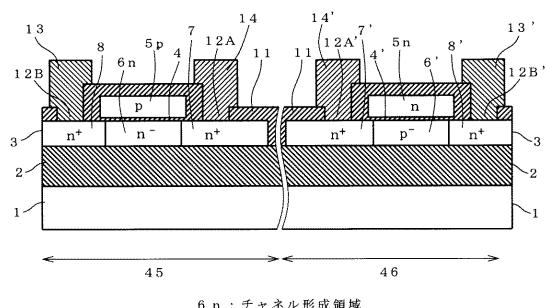

図8はこの発明の実施の形態3の第1の態様である半導体装置の入出力保護回路部と内部回路部とにそれぞれ形成されるS O I 基板上のM O S トランジスタ構造を示す断面図である。同図に示すように、シリコン基板1上には絶縁層である埋め込み酸化膜2を挟んでS O I 層であるシリコン薄膜3が設けられる。シリコン薄膜3は層間絶縁膜11等によって入出力保護回路部45、内部回路部46に分離されている。入出力保護回路部45において、 $10^{16} / \text{cm}^3$ のp型の不純物が導入されたチャネル形成領域6A、チャネル形成領域6Aを挟んで $10^{20} / \text{cm}^3$ 程度のn型の不純物が導入されたドレイン領域7及びソース領域8が形成される。一方、内部回路部46において、 $10^{17} / \text{cm}^3$ 程度のp型の不純物が導入されたチャネル形成領域6、チャネル形成領域6を挟んで $10^{20} / \text{cm}^3$ 程度のn型の不純物が導入されたドレイン領域7及びソース領域8が設けられる。

10

**【 0 0 9 3 】**

さらに、入出力保護回路部45のシリコン薄膜3のチャネル形成領域6A並びにドレイン領域7及びソース領域8の一部上にはゲート酸化膜4を挟んでゲート電極5pが形成される。一方、内部回路部46のシリコン薄膜3のチャネル形成領域6並びにドレイン領域7及びソース領域8の一部上にはゲート酸化膜4を挟んでゲート電極5nが形成される。ただし、ゲート電極5pはp型のポリシリコンを用いて形成され、ゲート電極5nはn型のポリシリコンを用いて形成される。

20

**【 0 0 9 4 】**

さらに、層間絶縁膜11が入出力保護回路部45、内部回路部46を分離するとともにシリコン薄膜3上全面に形成され、ドレイン領域7、7の一部、ソース領域8、8の一部上の層間絶縁膜11にコンタクトホール12A、12A、12B、12Bがそれぞれ設けられ、コンタクトホール12A、12Aを介してドレイン領域7、7に電気的に接続されたアルミ配線14、14がそれぞれ設けられ、コンタクトホール12B、12Bを介してソース領域8、8に電気的に接続されたアルミ配線13、13がそれぞれ設けられる。

30

**【 0 0 9 5 】**

したがって、入出力保護回路部45にはゲート電極5p、チャネル形成領域6A、ドレイン領域7及びソース領域8によってN M O S トランジスタ(入出力保護用N M O S トランジスタ)が形成され、内部回路部46にはゲート電極5n、チャネル形成領域6、ドレイン領域7及びソース領域8によってN M O S トランジスタ(内部回路用N M O S トランジスタ)が形成される。

**【 0 0 9 6 】**

チャネル形成領域6Aはチャネル形成領域6より不純物濃度が低く設定されているためパンチスルーレ電圧が低くなる。一方、チャネル形成領域6Aの不純物濃度が低いとその閾値電圧が低くなる性質があり、これを補うべくゲート電極5pをn型のポリシリコンを用いるよりも閾値が高くなる性質を有するp型のポリシリコンを用いる。そして、チャネル形成領域6Aの不純物濃度とゲート電極5nの不純物濃度を調整することにより、内部回路部46に形成されるN M O S トランジスタと同程度の閾値電圧に設定することができる。

40

**【 0 0 9 7 】**

このように、実施の形態4の第1の態様の入出力保護回路部45に形成されるN M O S トランジスタは、内部回路部46に形成されるN M O S トランジスタと同程度の閾値電圧を維持しながら、パンチスルーレ電圧を下げているため、E S D 耐性の高い入出力保護回路を

50

得ることができる。また、内部回路部46に形成されるN M O Sトランジスタはパンチスルーレ電圧を下げていないため、パンチスルーレ電圧低下による動作特性の劣化はない。

#### 【0098】

<第2の態様の構成及び動作>

図9はこの発明の実施の形態4の第2の態様である半導体装置の入出力保護回路部と内部回路部とにそれぞれ形成されるS O I基板上のM O Sトランジスタ構造を示す断面図である。同図に示すように、シリコン基板1上には絶縁層である埋め込み酸化膜2を挟んでS O I層であるシリコン薄膜3が設けられる。シリコン薄膜3は層間絶縁膜11等によって入出力保護回路部45、内部回路部46に分離されている。入出力保護回路部45において、 $10^{17} / \text{cm}^3$ 程度のn型の不純物が導入されたチャネル形成領域6n、チャネル形成領域6nを挟んで $10^{20} / \text{cm}^3$ 程度のn型の不純物が導入されたドレイン領域7及びソース領域8が形成される。

10

#### 【0099】

さらに、入出力保護回路部45のシリコン薄膜3のチャネル形成領域6n並びにドレイン領域7及びソース領域8の一部上にはゲート酸化膜4を挟んでp型のポリシリコンからなるゲート電極5pが形成される。なお、上記以外の構成は図8で示した第1の態様と同様である。

#### 【0100】

したがって、入出力保護回路部45にはゲート電極5p、チャネル形成領域6n、ドレイン領域7及びソース領域8によってN M O Sトランジスタが形成され、内部回路部46にはゲート電極5n、チャネル形成領域6n、ドレイン領域7及びソース領域8によってN M O Sトランジスタが形成される。

20

#### 【0101】

入出力保護回路部45に形成されるN M O Sトランジスタのチャネル形成領域6nはドレイン領域7及びソース領域8と同じ導電型のアキュミュレーションモードで形成されるためパンチスルーレ電圧が低くなる。一方、アキュミュレーションモードの場合はその閾値電圧が低くなる性質があるため、第1の態様と同様、これを補うべくゲート電極5nをn型のポリシリコンを用いるよりも閾値が高くなる性質を有するp型のポリシリコンを用いることにより、内部回路部46に形成されるN M O Sトランジスタと同程度の閾値電圧に設定している。したがって、入出力保護回路部45のN M O Sトランジスタを逆バイアス接続した場合に、そのゲート電位が多少上昇しても誤ってオン状態となることはない。

30

#### 【0102】

このように、実施の形態4の第2の態様の入出力保護回路部45に形成されるN M O Sトランジスタは、内部回路部46に形成されるN M O Sトランジスタと同程度の閾値電圧を維持しながら、パンチスルーレ電圧を下げているため、E S D耐性の高い入出力保護回路を得ることができる。また、内部回路部46に形成されるN M O Sトランジスタはパンチスルーレ電圧を下げていないため、パンチスルーレ電圧低下による動作特性の劣化はない。

#### 【0103】

<その他>

なお、実施の形態3の第1及び第2の態様はN M O Sトランジスタを例にして説明したが、各構成要素の導電型を逆にすることによってP M O Sトランジスタにも適用可能であることは勿論である。

40

#### 【0104】

また、第1及び第2の態様では、入出力保護回路部45のN M O Sトランジスタのゲート電極5pの導電型をp型にしたが、内部回路部46のN M O Sトランジスタのゲート電極5nと同様にn型に構成しても、閾値電圧は低下するもののパンチスルーレ電圧の低下によるE S D耐性の向上を図ることはできる。

#### 【0105】

さらに、図1あるいは図2で示した実施の形態1のN M O SトランジスタQ11, Q12及びP M O SトランジスタQ21, Q22として、実施の形態3の第1あるいは第2の態

50

様の構造のMOSトランジスタを用いることにより、より一層ESD耐性の向上を図ることができる。

#### 【0106】

<<実施の形態4>>

<原理>

SOI基板上にMOSトランジスタと共にダイオードを形成する場合、MOSトランジスタの製造プロセスを利用して、図36で示したような上部にゲート酸化膜4,4及びゲート電極5,5が形成されるダイオードが用いられるのが一般的である。

#### 【0107】

しかしながら、ゲート酸化膜4,4は破壊されやすく、ゲート酸化膜4,4の存在はESD耐性を劣化させる要因となっている。そこで、SOI基板上にゲート酸化膜及びゲート電極が形成されないダイオードを用いて入出力保護回路を構成したのが実施の形態4である。

#### 【0108】

<構成及び動作>

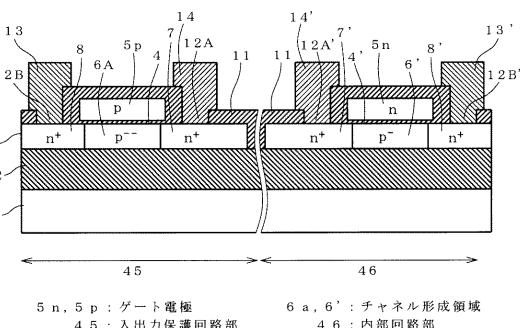

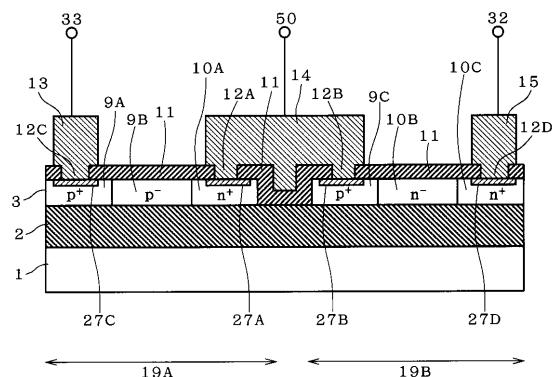

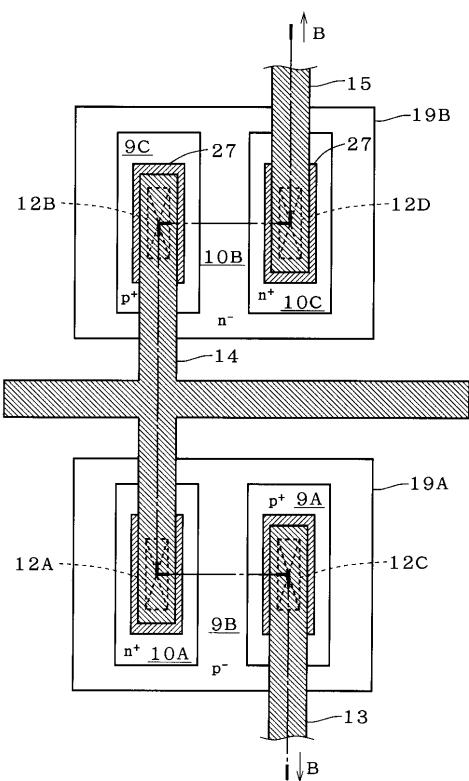

図10及び図11はこの発明の実施の形態4である半導体装置に用いられる入出力保護回路の構成を示す断面図及び平面図である。なお、図11のBB断面が図10となる。また、図10及び図11で示されるダイオードは例えば図32のダイオード38,39、図2のダイオードD11,D12に相当する。

#### 【0109】

図10及び図11に示すように、シリコン基板1上には絶縁層である埋め込み酸化膜2を挟んでシリコン薄膜3が設けられる。シリコン薄膜3は層間絶縁膜11によって2つの島19A,19Bに分離されており、 $10^{17}/cm^3$ 程度のp型の不純物が導入されたアノード領域9B、 $10^{17}/cm^3$ 程度のn型の不純物が導入されたカソード領域10Bがそれぞれ設けられ、アノード領域9Bを挟んでアノード領域9A及びカソード領域10Aが設けられ、カソード領域10Bを挟んでアノード領域9C及びカソード領域10Cが設けられる。なお、アノード領域9A及びアノード領域9Cには $10^{20}/cm^3$ 程度のp型の不純物が導入され、カソード領域10A及びカソード領域10Cには $10^{20}/cm^3$ 程度のn型の不純物が導入される。したがって、アノード領域9A,9B及びカソード領域10Aによってダイオード39が構成され、アノード領域9C、カソード領域10B及び10Cによってダイオード38が構成される。

#### 【0110】

そして、カソード領域10A、アノード領域9C、アノード領域9A及びカソード領域10Cそれぞれの表面にシリサイド領域27A~27Dが選択的に形成される。

#### 【0111】

シリサイド領域27A~27Dはアノード領域9A~9C及びカソード領域10A~10C形成後に絶縁膜を堆積し、アノード領域9A,9C及びカソード領域10A,10C一部を開口して開口部分に自己整合的に形成してもよい。あるいは内部回路部46のシリサイド形成時には入出力保護回路部45の全面を絶縁膜で覆うことによりシリサイド領域は形成せず、コンタクトホールの形成工程でコンタクトホール12A~12Dを設けた後、コンタクトホール12A~12Dを介してカソード領域10A、アノード領域9C、アノード領域9A及びカソード領域10Cの表面に選択的にシリサイド領域を形成してもよい。

#### 【0112】

さらに、層間絶縁膜11が島19A,19Bを分離するとともにシリコン薄膜3上全面に形成され、シリサイド領域27A~27Dの一部上の層間絶縁膜11にコンタクトホール12A~12Dが設けられ、コンタクトホール12A,12Bを介してシリサイド領域27A,27Bに電気的に接続されたアルミ配線14が設けられ、コンタクトホール12Cを介してシリサイド領域27Cに電気的に接続されたアルミ配線13が設けられ、コンタクトホール12Dを介してシリサイド領域27Dに電気的に接続されたアルミ配線15

10

20

30

40

50

が設けられる。そして、アルミ配線 13 は接地レベル 33 に接続され、アルミ配線 14 は入力端子 50 に接続され、アルミ配線 15 は電源 32 に接続される。なお、入力端子 50 は図 32 の保護抵抗 36 の他端に接続されても、直接入力信号 IN を受ける構成であってもよい。また、図 11 において層間絶縁膜 11 は図示していない。

#### 【0113】

このような構成の実施の形態 4 の入出力保護回路は、図 32 及び図 36 で示した従来の入出力保護回路と同様、正のサージ電圧が印加されると、ダイオード 39 のアノード領域 9B とカソード領域 10A との間の接合が降伏し、接地レベル 33 にサージ電圧を放電する。同時にダイオード 38 が順方向バイアスされ、電源 32 にサージ電圧を放電する。また、サージ電圧として負の高電圧が印加される場合には逆にダイオード 38 のアノード領域 9C とカソード領域 10B との間の接合が降伏し電源 32 にサージ電圧を放電するとともに、ダイオード 39 が順方向バイアスされて接地レベル 33 にサージ電圧を放電する。10

#### 【0114】

実施の形態 4 の入出力保護回路で用いられるダイオードは上部に ESD 耐性劣化の要因となるゲート酸化膜が形成されない分、図 36 で示した従来構造のダイオードを用いた場合よりも、良好な ESD 耐性を得ることができる。

#### 【0115】

加えて、アノード領域 9A, 9C 及びカソード領域 10A, 10C とアルミ配線 13 ~ 15 との接続をシリサイド領域 27A ~ 27D を用いて行うことにより、コンタクト抵抗の低減を図ることができる。20

#### 【0116】

<その他>

さらに、図 2 で示した実施の形態 1 の第 2 の態様のダイオード D11, D12 として、実施の形態 4 の構造の MOS ドラフィンジスタを用いることにより、より一層 ESD 耐性の向上を図ることができる。

#### 【0117】

<<実施の形態 5>>

<原理>

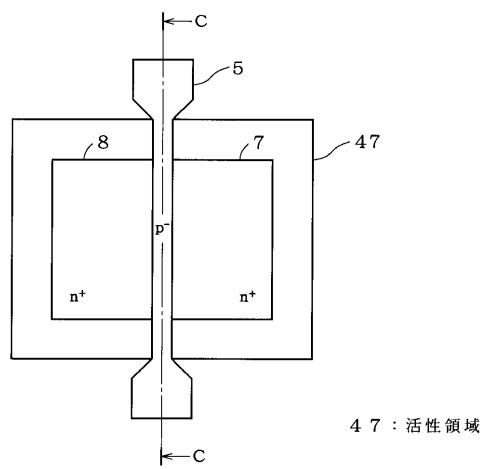

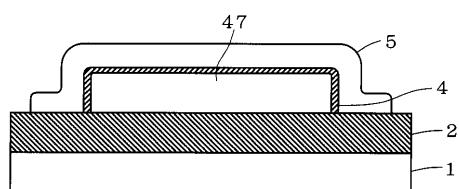

SOI 基板上に形成される MOS ドラフィンジスタ（上部にゲート電極を有するダイオード、キャパシタを含む）において、図 12 の平面図に示すように、ゲート電極 5 が、シリコン薄膜 3 の活性領域 47（ドレイン領域 7, ソース領域 8 を内部に有する）からみ出した平面構造の場合、図 12 の C-C 断面である図 13 に示すように、絶縁層 2 上に島状に形成された活性領域 47（シリコン薄膜 3）の端部を覆うようにゲート電極 5 を形成することになる。30

#### 【0118】

活性領域 47 の端部は活性領域 47 のパターニング時に受けたエッチングダメージによって結晶品質は悪いため活性領域 47 の端部近傍領域に形成されるゲート酸化膜 4 の品質は元々悪い。そこに、活性領域 47 の端部を覆ってゲート電極 5 を形成すると、ゲート電極 5 の材料形成時に活性領域 47 の端部により大きなストレスが発生するため、活性領域 47 の端部のゲート酸化膜 4 の品質はさらに悪化してしまい、その結果、ESD 耐性を劣化を招いてしまう。40

#### 【0119】

そこで、SOI 基板上にシリコン薄膜 3 の活性領域からはみ出さない平面構造のゲート電極を有する MOS ドラフィンジスタを用いて入出力保護回路を構成したのが実施の形態 5 である。

#### 【0120】

<第 1 の態様>

図 14 はこの発明の実施の形態 5 の半導体装置の入出力保護回路に用いられる MOS ドラフィンジスタの第 1 の態様の平面構造を示す平面図である。同図に示すように、ゲート電極 5 を内部に 2 つの開口部を有する「日」の字状に形成し、2 つの開口部分にドレイン領域 7

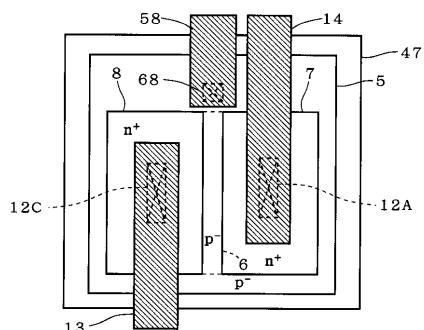

、ソース領域 8 を形成している。そして、コンタクトホール 1 2 A を介してドレイン領域 7 と電気的に接続したアルミ配線 1 4 を形成し、コンタクトホール 1 2 C を介してソース領域 8 と電気的に接続したアルミ配線 1 3 を形成し、コンタクトホール 6 8 を介してゲート電極 5 と電気的に接続したアルミ配線 5 8 を形成している。なお、図 1 4 で示した平面構造は、例えば図 5 で示した実施の形態 2 の第 1 の態様において島 2 0 A に形成されるN M O S トランジスタに適用することができる。

#### 【 0 1 2 1 】

このように、実施の形態 5 の第 1 の態様は、平面上においてゲート電極 5 が活性領域 4 7 内に形成されているため、活性領域 4 7 の端部にゲート電極 5 が形成されない分、E S D 耐性の向上を図ることができる。

10

#### 【 0 1 2 2 】

##### < 第 2 の態様 >

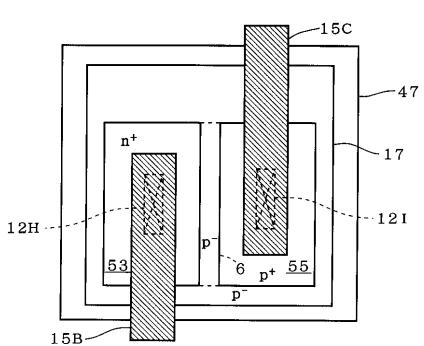

図 1 5 はこの発明の実施の形態 5 の半導体装置の入出力保護回路に用いられるM O S トランジスタの第 2 の態様の平面構造を示す平面図である。同図に示すように、ゲート電極 1 7 を内部に 2 つの開口部を有する「日」の字状に形成し、2 つの開口部分に n 型拡散領域 5 3 、 p 型拡散領域 5 5 を形成している。そして、コンタクトホール 1 2 H を介して n 型拡散領域 5 3 と電気的に接続したアルミ配線 1 5 B を形成し、コンタクトホール 1 2 I を介して p 型拡散領域 5 5 と電気的に接続したアルミ配線 1 5 C を形成している。なお、図 1 5 で示した平面構造は、例えば図 7 で示した実施の形態 2 の第 3 の態様において島 2 0 B に形成されるゲート電極 1 7 がフローティング状態となったゲートカップリング構造のキャパシタに適用することができる。

20

#### 【 0 1 2 3 】

このように、実施の形態 5 の第 2 の態様は、平面上においてゲート電極 1 7 が活性領域 4 7 内に形成されているため、活性領域 4 7 の端部にゲート電極 1 7 が形成されない分、E S D 耐性の向上を図ることができる。

#### 【 0 1 2 4 】

##### < 第 3 の態様 >

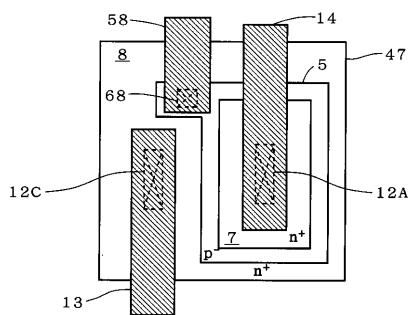

図 1 6 はこの発明の実施の形態 5 の半導体装置の入出力保護回路に用いられるM O S トランジスタの第 3 の態様の平面構造を示す平面図である。同図に示すように、ゲート電極 5 を内部に 1 つの開口部を囲む「口」の字状に形成し、その開口部分にドレイン領域 7 を形成し、ゲート電極 5 の外側にある活性領域 4 7 にソース領域 8 を形成している。そして、コンタクトホール 1 2 A を介してドレイン領域 7 と電気的に接続したアルミ配線 1 4 を形成し、コンタクトホール 1 2 C を介してソース領域 8 と電気的に接続したアルミ配線 1 3 を形成し、コンタクトホール 6 8 を介してゲート電極 5 と電気的に接続したアルミ配線 5 8 を形成している。なお、図 1 6 で示した平面構造は、例えば図 5 で示した実施の形態 2 の第 1 の態様において島 2 0 A に形成されるN M O S トランジスタに適用することができる。

30

#### 【 0 1 2 5 】

このように、実施の形態 5 の第 3 の態様は、平面上においてゲート電極 5 が活性領域 4 7 内に形成されているため、活性領域 4 7 の端部にゲート電極 5 が形成されない分、E S D 耐性の向上を図ることができる。

40

#### 【 0 1 2 6 】

##### < 第 4 の態様 >

図 1 7 はこの発明の実施の形態 5 の半導体装置の入出力保護回路に用いられるM O S トランジスタの第 4 の態様の平面構造を示す平面図である。同図に示すように、ゲート電極 1 7 を内部に 1 つの開口部を囲む「口」の字状に形成し、その開口部分に p 型拡散領域 5 5 を形成し、ゲート電極 1 7 の外側にある活性領域 4 7 に n 型拡散領域 5 3 を形成している。そして、コンタクトホール 1 2 H を介して n 型拡散領域 5 3 と電気的に接続したアルミ配線 1 5 B を形成し、コンタクトホール 1 2 I を介して p 型拡散領域 5 5 と電気的に接続したアルミ配線 1 5 C を形成している。なお、図 1 7 で示した平面構造は例えば、図 7

50

で示した実施の形態 2 の第 3 の態様において島 20B に形成されるゲート電極 17 がフローティング状態となったキャパシタに適用することができる。

#### 【 0 1 2 7 】

このように、実施の形態 5 の第 4 の態様は、平面上においてゲート電極 17 が活性領域 47 内に形成されているため、活性領域 47 の端部にゲート電極 17 が形成されることができない分、E S D 耐性の向上を図ることができる。

#### 【 0 1 2 8 】

< その他 >

また、図 1 あるいは図 2 で示した実施の形態 1 の N M O S ドランジスタ Q 1 1 , Q 1 2 及び P M O S ドランジスタ Q 2 1 , Q 2 2 として、実施の形態 5 の第 1 あるいは第 3 の態様の構造の M O S ドランジスタを用いることにより、より一層 E S D 耐性の向上を図ることができる。

10

#### 【 0 1 2 9 】

< < 補足 > >

上記した実施の形態 2 ~ 実施の形態 5 の構成では、N M O S ドランジスタを中心に説明したが、導電型式を逆にすることによって P M O S ドランジスタに適用可能なのは勿論である。また、主に電源 3 2 側に P M O S ドランジスタ、接地レベル 3 3 側に N M O S ドランジスタを配置する構成を示したが、電源 3 2 及び接地レベル 3 3 のうち一方に入出力保護用 M O S ドランジスタを設ける構成でも同様の効果を有する。また、M O S ドランジスタをダイオード接続して、電源 3 2 側に N M O S ドランジスタ、接地 3 3 側に P M O S ドランジスタを設けても同様の効果を奏する。

20

#### 【 0 1 3 0 】

さらに、M O S ドランジスタ、ダイオードを各種組み合わせて接続して複雑な入出力保護回路を構成しても少なくとも上記した実施の形態と同様な効果が得られるのはいうまでもない。

#### 【 0 1 3 1 】

##### 【 発明の効果 】

以上説明したように、この発明における請求項 1 記載の半導体装置の入出力保護回路は、各々が電源ノードあるいは基準電位ノードと信号端子との間に設けられ、信号端子に動作信号が印加されるときに逆方向バイアスとなり、第 1 あるいは第 2 の極性の電圧が印加されるときに順方向バイアスとなる P N 接合部を有する第 1 ~ 第 4 の放電素子を有している。

30

#### 【 0 1 3 2 】

したがって、第 1 の極性を有するサージ電圧が信号端子より印加されるときは、順方向バイアス状態の第 1 及び第 3 の放電素子がそれぞれ電源ノード及び基準電位ノードにそのサージ高電圧を放電させ、第 2 の極性を有するサージ電圧が信号端子より印加されるときは、順方向バイアス状態の第 2 及び第 4 の放電素子がそれぞれ電源ノード及び基準電位ノードにそのサージ電圧を放電させることができる。

#### 【 0 1 3 3 】

その結果、どのようなサージ電圧に対しても必ず順方向バイアス状態で電源ノード及び基準電位ノードそれぞれに放電する 2 つの放電素子が存在するため、E S D 耐性の良い入出力保護回路を得ることができる。

40

#### 【 0 1 3 4 】

また、第 1 ~ 第 4 の放電素子の P N 接合部は、信号端子に動作信号が印加された場合にすべて逆方向バイアス状態となるため、動作信号が第 1 ~ 第 4 の放電素子を介して電源ノードあるいは接地線に漏れることはなく、入出力保護回路が内部回路の通常動作に悪影響を与えることもない。

#### 【 0 1 3 5 】

請求項 2 記載の半導体装置は、第 1 の導電型の第 1 及び第 3 の M O S ドランジスタと、第 2 の導電型の第 2 及び第 4 の M O S ドランジスタとによって入出力保護回路を構成する

50

ことにより、異なる導電型式のトランジスタを2個ずつ用いているため、入出力保護回路を容易に製造することができる。

【0136】

請求項5記載の半導体装置は、1つの第1の導電型の第1のトランジスタと、1つの第2の導電型の第2のトランジスタと2つの第1及び第2のダイオードによって入出力保護回路を構成することにより、異なる導電型式のトランジスタを1個ずつ用いているため、入出力保護回路を容易に製造することができる。

【0137】

請求項7記載の半導体装置は、信号端子と信号ノードとの間に介挿される第1の内部抵抗と、信号ノードと内部回路との間に介挿される第2の内部抵抗とを有しているため、信号端子に第1あるいは第2の極性のサージ電圧が印加された場合に、第1の内部抵抗によってその伝播遅延を生じさせ、第2の内部抵抗により内部回路への伝播を妨げたりすることにより内部回路の保護を図ることができる。10

【図面の簡単な説明】

【図1】この発明の実施の形態1である半導体装置の入出力保護回路の構成を示す回路図である。

【図2】この発明の実施の形態1である半導体装置の入出力保護回路の他の構成を示す回路図である。

【図3】ゲートカップリング断面構造のN MOSトランジスタを示す回路図である。

【図4】図3で示したN MOSトランジスタの放電特性を示すグラフである。20

【図5】この発明の実施の形態2である半導体装置の入出力保護回路の第1の態様の断面構造を示す断面図である。

【図6】実施の形態2の第2の態様の断面構造を示す断面図である。

【図7】実施の形態2の第3の態様の断面構造を示す断面図である。

【図8】この発明の実施の形態3である半導体装置の入出力保護回路の第1の態様の断面構造を示す断面図である。

【図9】実施の形態3の第2の態様の断面構造を示す断面図である。

【図10】この発明の実施の形態4である半導体装置の入出力保護回路の断面構造を示す断面図である。

【図11】図10で示した実施の形態4の平面構造を示す平面図である。30

【図12】実施の形態5の原理説明用の平面図である。

【図13】実施の形態5の原理説明用の断面図である。

【図14】この発明の実施の形態5である半導体装置の入出力保護回路の第1の態様の平面構造を示す平面図である。

【図15】実施の形態5の第2の態様の平面構造を示す平面図である。

【図16】実施の形態5の第3の態様の平面構造を示す平面図である。

【図17】実施の形態5の第4の態様の平面構造を示す平面図である。

【図18】SOI断面構造を示す断面図である。

【図19】逆方向バイアス接続されたN MOSトランジスタの放電特性を示すグラフである。40

【図20】逆方向バイアス接続のN MOSトランジスタを示す回路図である。

【図21】熱暴走破壊されたMOSトランジスタの平面構造を示す平面図である。

【図22】入力、接地間に複数のN MOSトランジスタを並列に接続した平面構造を示す平面図である。

【図23】図22の回路構成を示す回路図である。

【図24】順方向バイアス接続のN MOSトランジスタを示す回路図である。

【図25】順方向バイアス接続されたN MOSトランジスタの放電特性を示す説明図である。

【図26】複数のN MOSトランジスタを用いて順方向バイアス接続を行う場合の構成を示す回路図である。50

- 【図27】逆方向バイアス接続のダイオードを示す回路図である。

- 【図28】逆方向バイアス接続されたダイオードの放電特性を示すグラフである。

- 【図29】順方向バイアス接続のダイオードを示す回路図である。

- 【図30】順方向バイアス接続されたダイオードの放電特性を示すグラフである。

- 【図31】従来の入出力保護回路の構成を示す回路図である。

- 【図32】従来の入出力保護回路の構成を示す回路図である。

- 【図33】内部素子の一例を示す回路図である。

- 【図34】図31で示した入出力保護回路の一部の平面構造を示す平面図である。

- 【図35】図31で示した入出力保護回路の一部の断面構造を示す断面図である。

- 【図36】図32で示した入出力保護回路の一部の断面構造を示す断面図である。 10

## 【符号の説明】

5, 5 , 5 n , 5 p , 16 , 17 ゲート電極、6, 6 , 6 A , 6 n チャネル形成領域、7, 7 , 25 ドレイン領域、8, 8 , 26 ソース領域、9 A ~ 9 C アノード領域、10 A ~ 10 C カソード領域、14 シリサイドプロテクト層、21 ~ 23, 51 , 52 , 54 , 55 p型拡散領域、53 n型拡散領域 53, 27 A ~ 27 D シリサイド領域、30 信号端子、31 内部素子、32 電源(ノード)、33 接地レベル(ノード)、45 入出力保護回路部、46 内部回路部、47 活性領域、D11, D12 ダイオード、Q11, Q12 NMOSトランジスタ、Q21, Q22 PMOSトランジスタ。

【図1】

30 : 信号端子

31 : 内部素子

32 : 電源(ノード)

33 : 接地レベル(ノード)

Q11, Q12 : NMOSトランジスタ

Q21, Q22 : PMOSトランジスタ

【図2】

D11, D12 : ダイオード

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

9A～9C：アノード領域

10A～10C：カソード領域

27A～27C：シリサイド領域

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

【図25】

【図28】

【図26】

【図29】

【図27】

【図30】

【図32】

【図31】

【図33】

【図34】

【図35】

【図36】

---

フロントページの続き

(56)参考文献 特開平07-094679(JP,A)

特開平07-335894(JP,A)

特開昭61-051877(JP,A)

特開平08-037284(JP,A)

特開平07-235604(JP,A)

特開昭60-086856(JP,A)

特開昭60-000767(JP,A)

特開平03-073568(JP,A)

特開平04-241452(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/336

H01L 27/04

H01L 21/822