(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5090117号

(P5090117)

(45) 発行日 平成24年12月5日(2012.12.5)

(24) 登録日 平成24年9月21日(2012.9.21)

(51) Int.Cl.

H01F 27/06

(2006.01)

F 1

H01F 15/02

G

H01F 27/00

(2006.01)

H01F 15/00

B

H05K 1/02

(2006.01)

H05K 1/02

R

請求項の数 6 (全 11 頁)

(21) 出願番号

特願2007-254661 (P2007-254661)

(22) 出願日

平成19年9月28日 (2007.9.28)

(65) 公開番号

特開2009-88162 (P2009-88162A)

(43) 公開日

平成21年4月23日 (2009.4.23)

審査請求日

平成22年8月18日 (2010.8.18)

(73) 特許権者 000204284

太陽誘電株式会社

東京都台東区上野6丁目16番20号

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100087480

弁理士 片山 修平

(72) 発明者 上田 知史

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

(72) 発明者 高橋 岳雄

神奈川県横浜市港北区新横浜二丁目3番地

12 富士通メディアデバイス株式会社内

最終頁に続く

(54) 【発明の名称】電子部品

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板上に設けられたスパイラル状のコイルと、

前記コイルの内側に設けられ、前記コイルの表面の光の反射率より高い光の反射率を有し、複数に分割された導電性パターンと、

前記基板上に下部電極と前記下部電極上に形成された誘電体層と前記誘電体層上に形成された上部電極とを含み、前記コイルと電気的に接続されたキャパシタと、

を具備し、前記導電性パターンは、前記下部電極と同じ材料から形成され、前記コイルはめっき層

から形成されることを特徴とする電子部品。

## 【請求項 2】

前記コイルは、縦方向に離間して設けられ互いに電気的に接続された複数のコイルであることを特徴とする請求項1記載の電子部品。

## 【請求項 3】

前記複数に分割された導電性パターンは、位置確認用マーカであることを特徴とする請求項1または2記載の電子部品。

## 【請求項 4】

前記複数に分割された導電性パターンは、画像認識用パターンであることを特徴とする請求項1または2記載の電子部品。

10

20

**【請求項 5】**

前記複数の分割された導電性パターンそれぞれの形状は、円形、方形、三角形、菱形および橢円形のいずれかであることを特徴とする請求項 1 から 4 のいずれか一項記載の電子部品。

**【請求項 6】**

基板と、

前記基板上に設けられたスパイラル状のコイルと、

前記コイルの外周から前記コイルの半径の距離以内に設けられ、前記コイルの表面の光の反射率より高い光の反射率を有し、複数に分割された位置確認用マーカである導電性パターンと、

前記基板上に下部電極と前記下部電極上に形成された誘電体層と前記誘電体層上に形成された上部電極とを含み、前記コイルと電気的に接続されたキャパシタと、

を具備し、

前記導電性パターンは画像認識用パターンであり、

前記導電性パターンは、前記下部電極と同じ材料から形成され、前記コイルはめっき層から形成されることを特徴とする電子部品。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は電子部品に関し、導電性パターンを有する電子部品に関する。

20

**【背景技術】****【0002】**

位相整合等を行う場合、インダクタやキャパシタが用いられる。例えば、携帯電話やワイヤレス LAN (Local Area Network) 等の RF (Radio frequency) システムにおいては、小型化、低コスト化、高性能化の要求がある。この要求を満たすため、基板上にインダクタやキャパシタ等の受動素子を集積化した集積型受動素子等の電子部品が用いられる。

**【0003】**

集積型受動素子をパッケージまたはモジュール基板に実装する場合、高性能化のためフェースダウン実装を行うことが有効である。集積化受動素子をフェースダウン実装するためには、まず、集積化受動素子の外部に接続するためのパッド上に、金等のスタッドバンプ、めっきバンプ、または、半田ボールを形成する。スタッドバンプはワイヤボンダを用い形成され、半田ボールはボールマウンタを用い形成される。次に、フリップチップボンダを用い、集積化受動素子をパッケージまたはモジュール基板に実装する。

30

**【0004】**

特許文献 1 には、基板上にスパイラル状のコイルをインダクタとして用いた集積電子部品が開示されている。特許文献 2 および特許文献 3 には、スパイラル状の複数のコイルが縦方向に離間して設けられたインダクタが開示されている。

【特許文献 1】特開 2006-157738 号公報

【特許文献 2】特開 2007-67236 号公報

【特許文献 3】米国特許第 6,518,165 号明細書

40

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

ワイヤボンダ、ボールマウンタまたはフリップチップボンダ等のボンダを使用する際は、位置確認用マーカを、予め集積化受動素子内に形成する。ボンディングの際は、位置確認用マーカを基準に、スタッドバンプや半田ボールの形成またはフリップチップ実装を行う。ボンダにおいて、位置確認用マーカの認識は画像認識によって行われる。このため、位置確認用マーカの大きさやコントラストはボンダが画像認識できる程度であることが求められる。したがって、位置確認用マーカは一定以上の大きさで、かつ光の反射率の大きな導電性パターンとすることが求められる。一方、導電性である位置確認用マーカが大き

50

くなると、コイルからの誘導電流が位置確認用マーカに生じて渦電流損が発生しインダクタ特性に影響を及ぼしてしまう。

#### 【0006】

本発明は、上記課題に鑑みなされたものであり、導電性パターンを有する電子部品において、導電性パターンの画像認識が可能で、導電性パターンのインダクタ特性への影響を抑制することを可能とすることを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

本発明は、基板と、前記基板上に設けられたスパイラル状のコイルと、前記コイルの内側に設けられ、前記コイルの表面の光の反射率より高い光の反射率を有し、複数に分割された導電性パターンと、前記基板上に下部電極と前記下部電極上に形成された誘電体層と前記誘電体層上に形成された上部電極とを含み、前記コイルと電気的に接続されたキャパシタと、を具備し、前記導電性パターンは、前記下部電極と同じ材料から形成され、前記コイルはめっき層から形成されることを特徴とする電子部品である。本発明によれば、導電性パターンの光の反射率が高いため導電性パターンの画像認識が可能であり、かつ導電性パターンが複数に分割されているため導電性パターンのインダクタ特性への影響を抑制することができる。

#### 【0008】

上記構成において、前記コイルは、縦方向に離間して設けられ互いに電気的に接続された複数のコイルである構成とすることができます。

#### 【0009】

上記構成において、前記複数に分割された導電性パターンは、位置確認用マーカである構成とすることができます。また、上記構成において、前記複数に分割された導電性パターンは、画像認識用パターンである構成とすることができます。さらに、上記構成において、前記複数の分割された導電性パターンそれぞれの形状は、円形、方形、三角形、菱形および橢円形のいずれかである構成とすることができます。

#### 【0012】

本発明は、基板と、前記基板上に設けられたスパイラル状のコイルと、前記コイルの外周から前記コイルの半径の距離以内に設けられ、前記コイルの表面の光の反射率より高い光の反射率を有し、複数に分割された位置確認用マーカである導電性パターンと、前記基板上に下部電極と前記下部電極上に形成された誘電体層と前記誘電体層上に形成された上部電極とを含み、前記コイルと電気的に接続されたキャパシタと、を具備し、前記導電性パターンは画像認識用パターンであり、前記導電性パターンは、前記下部電極と同じ材料から形成され、前記コイルはめっき層から形成されることを特徴とする電子部品である。

#### 【発明の効果】

#### 【0013】

本発明によれば、導電性パターンの光の反射率が高いため導電性パターンの画像認識が可能であり、かつ導電性パターンが複数に分割されているため導電性パターンのインダクタ特性への影響を抑制することができます。

#### 【発明を実施するための最良の形態】

#### 【0014】

以下、図面を参照に、本発明の実施例について説明する。

#### 【実施例1】

#### 【0015】

大きな位置確認用マーカは、集積化受動素子のチップ面積削減の障害となる。そこで、インダクタのコイル内に位置確認用マーカを配置することが考えられる。しかしながら、インダクタコイル内に位置確認用マーカを配置するとインダクタのインダクタンスおよびQ値（先鋭度）が低下することがわかった。以下に、この課題を解決するために行った実験および実施例1について説明する。

#### 【0016】

10

20

30

40

50

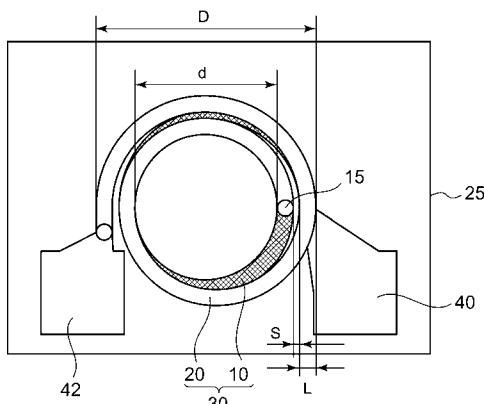

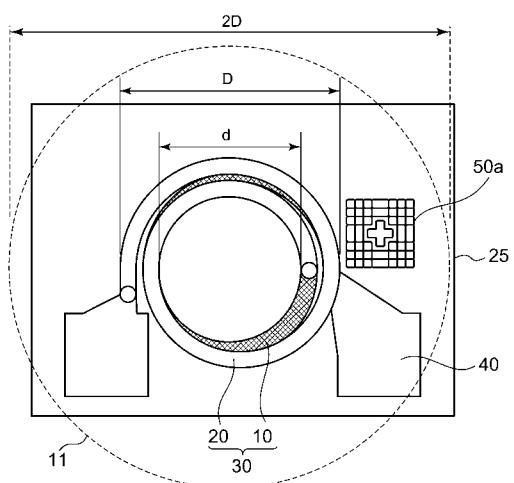

図 1 から図 4 は試作したインダクタ素子の平面図である。図 1 は比較例 1 に係るインダクタ素子、図 2 は実施例 1 に係るインダクタ素子、図 3 は実施例 1 の変形例に係るインダクタ素子、図 4 は比較例 2 に係るインダクタ素子を示している。図 1 から図 4 において、インダクタ素子は全て同じ構成である。図 1 を参照に、作製したインダクタ素子の構成を説明する。インダクタ素子はガラス基板 25 上に設けられたインダクタ 30 とパッド 40 および 42 を有している。インダクタ 30 は円形スパイラル状の第 1 コイル 10 と第 2 コイルとを有している。基板 25 上にスパイラル状の第 1 コイル 10 、第 1 コイル 10 上にスパイラル状の第 2 コイル 20 が離間して設けられ、第 1 コイル 10 と第 2 コイル 20 との間は空隙となっている。すなわち大気が充満している。第 1 コイル 10 および第 2 コイル 20 はほぼ重なるように設けられている。第 1 コイル 10 は、最外周においてパッド 40 に接続され 1 周のスパイラルである。第 2 コイル 20 は、最外周においてパッド 42 に接続され 1.5 周のスパイラルである。第 1 コイル 10 と第 2 コイル 20 とは、最内周において接続部 15 で接続されている。インダクタ 30 の外径 D は  $480 \mu\text{m}$  、内径 d は  $300 \mu\text{m}$  、線幅 L は  $40 \mu\text{m}$  、線間隔 S は  $10 \mu\text{m}$  である。

## 【0017】

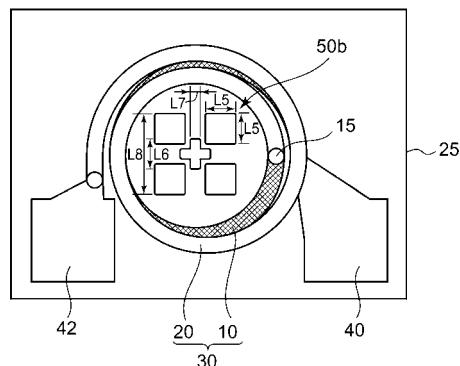

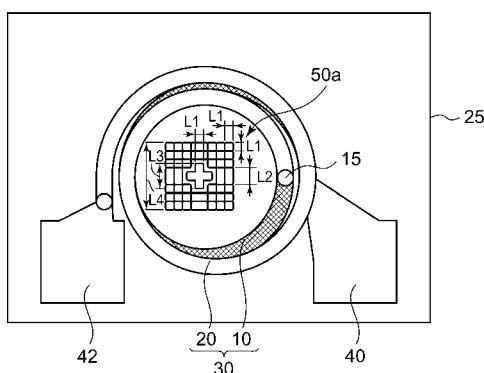

図 2 を参照に、実施例 1 に係るインダクタ素子においては、インダクタ 30 の内径内に位置確認用マーカとして導電性パターン 50a が設けられている。導電性パターン 50a は、一辺  $L_1$  が  $15 \mu\text{m}$  の正方形パターンが 36 個と、辺  $L_1$  および辺  $L_2$  がそれぞれ  $15 \mu\text{m}$  および  $30 \mu\text{m}$  の長方形パターンが 8 個と、最小幅  $L_1$  および最大幅  $L_3$  がそれぞれ  $15 \mu\text{m}$  および  $70 \mu\text{m}$  で中央に設けられた十字パターンとを有している。正方形パターンと長方形パターンとの間隔は  $5 \mu\text{m}$  であり、導電性パターン 50a の外辺  $L_4$  は  $150 \mu\text{m}$  である。

## 【0018】

図 3 を参照に、実施例 1 の変形例に係るインダクタ素子においては、インダクタ 30 の内径内に位置確認用マーカとして導電性パターン 50b が設けられている。導電性パターン 50b は、一辺  $L_5$  が  $65 \mu\text{m}$  の正方形パターンが 4 個と、最小幅  $L_7$  および最大幅  $L_6$  がそれぞれ  $25 \mu\text{m}$  および  $75 \mu\text{m}$  で中央に設けられた十字パターンとを有している。正方形パターン同士の間隔は  $50 \mu\text{m}$  であり、導電性パターン 50b の外辺  $L_8$  は  $180 \mu\text{m}$  である。

## 【0019】

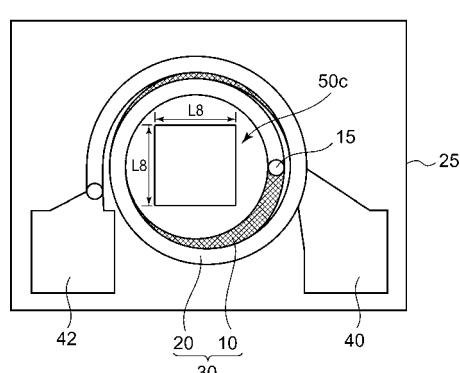

図 4 を参照に、実施例 1 に係るインダクタ素子においては、インダクタ 30 の内径内に位置確認用マーカとして導電性パターン 50c が設けられている。導電性パターン 50c は、一辺  $L_8$  が  $180 \mu\text{m}$  の正方形パターンである。第 1 コイル 10 および第 2 コイル 20 は、めっき法を用い形成された膜厚が約  $10 \mu\text{m}$  の銅からなる。一方、導電性パターン 50a から 50c は、スパッタ法を用い形成された下から順にチタン ( $20 \text{ nm}$ ) / 金 ( $1000 \text{ nm}$ ) からなる。第 1 コイル 10 および第 2 コイル 20 はめっき法を用い形成されているため、表面に形成される凹凸が大きく、光の反射率は小さい。一方、導電性パターン 50a から 50c はスパッタ法を用い形成され、かつ表面が金のため、表面の光の反射率が大きい。

## 【0020】

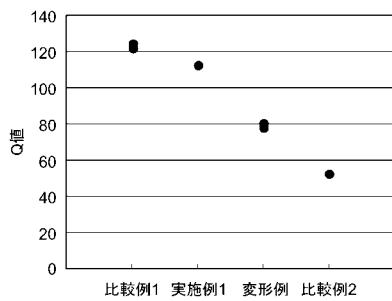

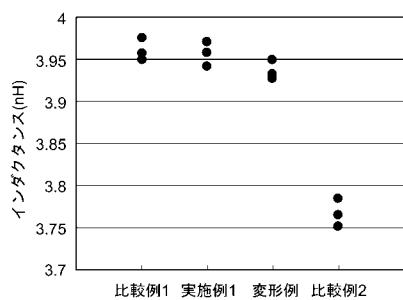

図 5 は作製した各種類（比較例 1 、実施例 1 、実施例 1 の変形例および比較例 2 ）のインダクタ素子の Q 値を測定した結果を示す図であり、図 6 は作製した各種類のインダクタ素子のインダクタンス値を測定した結果を示す図である。図 5 および図 6 において、各種類のインダクタ素子について図示された複数のドットは、1 つの種類につき測定した複数のインダクタ素子の結果である。

## 【0021】

図 5 を参照に、Q 値は、比較例 1 が最も大きく、比較例 2 が最も小さい。実施例 1 およびその変形例は、比較例 1 および比較例 2 の間の値となる。図 6 を参照に、インダクタンス値は、比較例 1 が最も大きく、比較例 2 が最も小さい。実施例 1 およびその変形例は比較例 1 とほとんど同じインダクタンス値である。

## 【0022】

比較例1に係るインダクタ素子は、インダクタ30内に導電性パターンが設けられておらず、本来のQ値およびインダクタンス値を有している。これに対し比較例2に係るインダクタンス素子は、インダクタ30内に導電性パターンを設けることにより、Q値およびインダクタンス値が小さくなっている。これは、インダクタ30内に導電性パターン50cを配置したことに起因し、渦電流損が生じたためである。実施例1およびその変形例においては、導電性パターン50aおよび50bが分割されている。このため、導電性パターン50aおよび50bに生じる渦電流が抑制され、インダクタ30のQ値およびインダクタンス値が比較例2に対し向上する。

## 【0023】

実施例1によれば、導電性パターン50aまたは50bが第1コイル10および第2コイル20の内側に設けられていることにより、導電性パターン50aまたは50bを配置するチップ面積を削減することができる。また、導電性パターン50aまたは50bが複数に分割されていることにより、図5および図6に示したように導電性パターン50aまたは50bのインダクタ特性への影響を抑制することができる。さらに、導電性パターン50aまたは50bの光の反射率が、第1コイル10および第2コイル20の光の反射率より高いことにより、導電性パターン50aまたは50bを一体として位置確認用マーカとして使用することができる。ワイヤボンダ、ボーリュマウンタまたはフリップチップボンダ等のボンダを使用する際の位置の認識は、光学顕微鏡を用い行われる。このため、パターンの光の反射率が高いと分割されたパターンは一体として認識される。よって、導電性パターン50aおよび50bを一体として画像認識用パターンとして用いることができる。

## 【実施例2】

## 【0024】

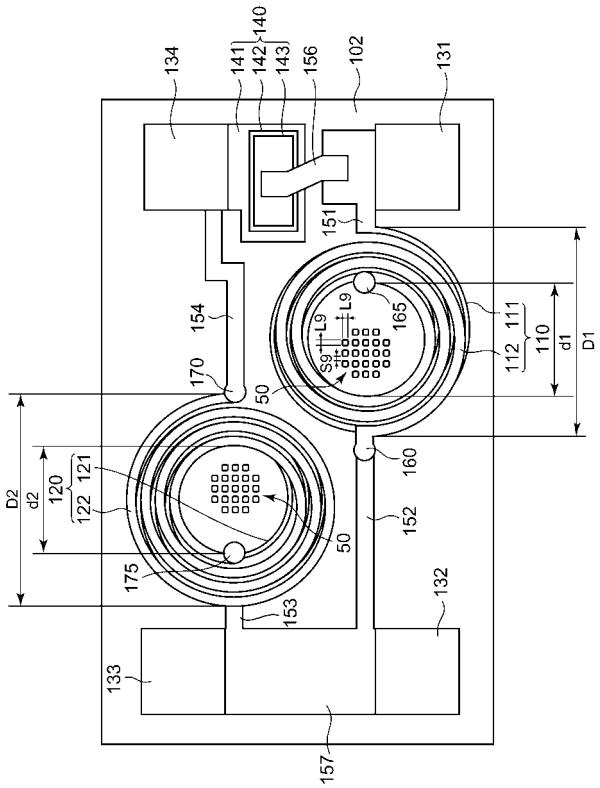

実施例2は、インダクタとキャパシタとを用いた集積化受動素子の例である。図7は実施例2に係る集積化受動素子の上面図である。図7を参照に、基板102上に、第1コイル111および第2コイル112からなるインダクタ110並びに第1コイル121および第2コイル122からなるインダクタ120が形成されている。インダクタ110の第1コイル111および第2コイル112の内端は接続部165により互いに接続され、第1コイル111は外端で配線151に接続され、第2コイル112は外端で接続部160を介し配線152に接続されている。インダクタ120の第1コイル121および第2コイル122の内端は接続部175により互いに接続され、第1コイル121は外端で配線153に接続され、第2コイル122は外端で接続部170を介し配線154に接続されている。配線151から154は基板102上に形成され、それぞれパッド131から134に接続されている。パッド132と133とは配線157で接続されている。パッド131と134の間には、下部電極141、誘電体層142および上部電極143からなるキャパシタ140が接続されている。上部電極143と配線151とは上部の配線156で接続されている。パッド131を入力、パッド134を出力、パッド132および133を接地することにより、集積化受動素子は、パッド131と134間にL-C-L回路を構成する。インダクタ110の外径D1は350μm、内径d1は200μm、インダクタ120の外径D2は400μm、内径d2は190μmである。第1コイル111および121並びに第2コイル112および122の線幅は15μm、線間隔は15μmである。

## 【0025】

図7を参照に、第2コイル112および122の内側にそれぞれ導電性パターン50が配置されている。導電性パターン50は、一辺L9が10μmの正方形パターンが21個からなり、外径は115μmである。正方形パターンの間隔S9は10μmである。

## 【0026】

実施例2に係る集積化受動素子を複数作製したところ、インダクタ110および120のインダクタンス値はそれぞれ設計値と±5%以内の精度で一致し、かつ高いQ値を得る

10

20

30

40

50

ことができた。また、導電性パターン 50 を用いスタッドバンプの形成およびフェースダウン実装を問題なく行うことができた。これにより、導電性パターン 50 は画像認識用パターンとして用いることができることを確認した。

【実施例 3】

【0027】

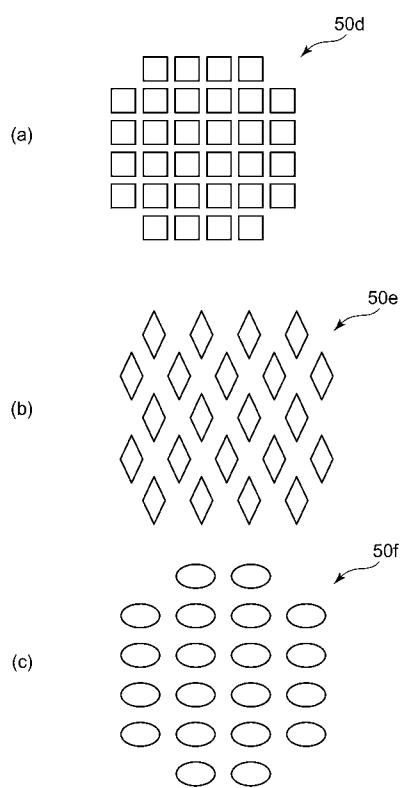

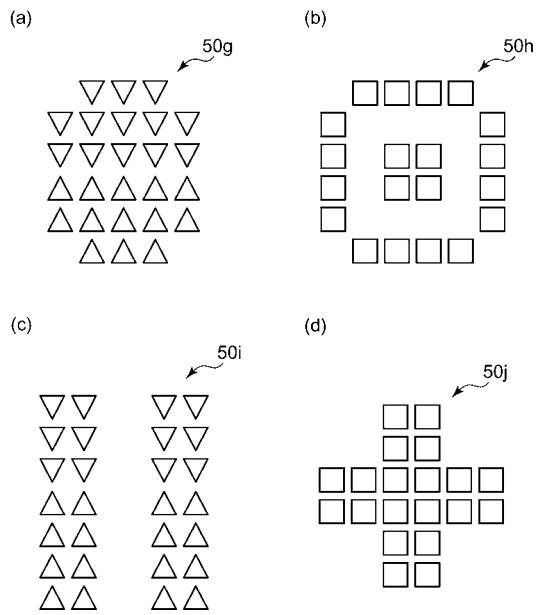

実施例 3 は導電性パターンの例である。図 8 (a) のように、導電性パターン 50 d は、複数の正方形パターンが配列したパターンでもよい。また、図 8 (b) のように、導電性パターン 50 e は、複数の菱形パターンが配列したパターンでもよい。図 8 (c) のように、導電性パターン 50 f は橜円形パターンが配列したパターンでもよい。図 9 (a) のように、導電性パターン 50 g は複数の三角形パターンが配列したパターンでもよい。図 9 (b) のように、導電性パターン 50 h は分割されたパターンが 2 重に配列された形状でもよい。図 9 (c) のように、導電性パターン 50 i は、分割されたパターンが 2 列に配列されたパターンでもよい。図 9 (d) のように、導電性パターン 50 j は、分割されたパターンが十字状に配置されたパターンでもよい。以上のように、導電性パターンは、ボンダ等に画像認識可能なパターンであれば、いずれのパターンでもよい。画像認識に用いる光は一般的には可視光であるが、赤外光等の可視光以外の光でもよい。

10

【実施例 4】

【0028】

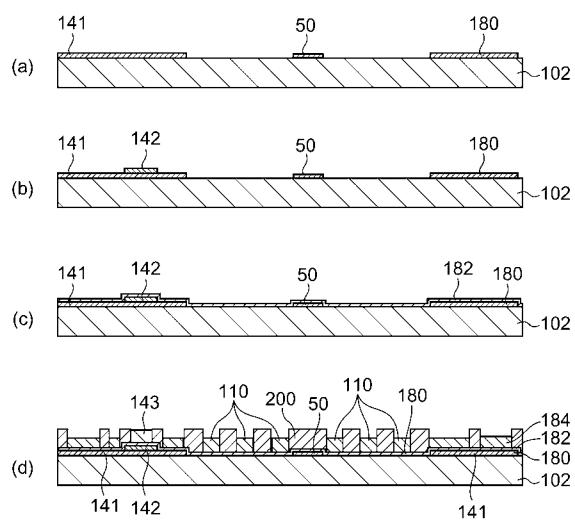

実施例 4 は、基板上にインダクタおよびキャパシタを形成する製造方法の例である。図 10 (a) を参照に、基板 102 上に、MIM (Metal Insulator Metal) キャパシタの下部電極 141、導電性パターン 50 およびパッドの下部層として金属層 180 をスパッタ法または蒸着法を用い形成する。基板 102 は、石英 (合成石英を含む)、ガラス (パイレックス (登録商標)、テンパックス、アルミニノシリケート、ホウケイ酸ガラスなど)、セラミック基板等の絶縁基板または高抵抗シリコン基板、LiNbO<sub>3</sub> 基板、LiTaO<sub>3</sub> 基板等を用いることができる。金属層 180 は比較的抵抗が低い Al、Au 又は Cu を主材料として用いることが好ましい。金属層 180 は多層構成でもよい。例えば、基板 102 側から順に Ti / Au / Ni / Au (20 nm / 500 nm / 20 nm / 500 nm) の 4 層構成、または Ti / Au / Ti (20 nm / 1000 nm / 20 nm) 若しくは Ti / Cu / Ti (20 nm / 1000 nm / 20 nm) の 3 層構成とすることができます。

20

【0029】

図 10 (b) を参照に、下部電極 141 上に誘電体層 142 をスパッタ法やPECVD (Plasma enhanced chemical vapor deposition) 法を用い形成する。誘電体層 142 としては、SiO<sub>2</sub>、Si<sub>3</sub>N<sub>4</sub>、Al<sub>2</sub>O<sub>3</sub>、Ta<sub>2</sub>O<sub>5</sub> 等を用いることができる。例えば、誘電体層 142 は、厚さが 195 nm の PECVD 法を用い形成した SiO<sub>2</sub> 膜である。図 10 (c) を参照に、電気メッキ用の種層 182 を形成する。種層 182 の材料として、後に電気めっきを行う材料と同じものが望ましく、例えば Ti / Cu (20 nm / 500 nm) をスパッタ法を用い形成する。

30

【0030】

図 10 (d) を参照に、種層 182 上にめっきを行う開口部を有するフォトレジス 200 を形成する。開口部内に電解めっきを行い、例えば膜厚が 10 μm の Cu からなるめっき層 184 を形成する。

40

【0031】

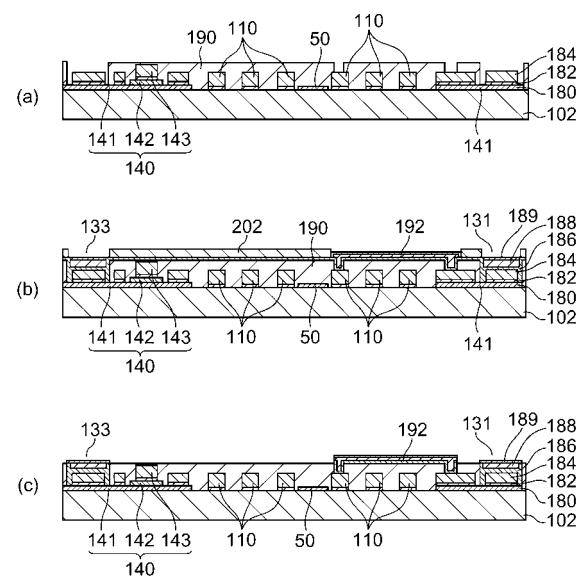

図 11 (a) を参照に、フォトレジスト 200 を除去する。めっき層 184 をマスクに種層 182 を除去する。めっき層 184 および種層 182 により、インダクタ 110、キャパシタの上部電極 143、パッド部等が形成される。下部電極 141、誘電体層 142 および上部電極 143 によりキャパシタ 140 が形成される。めっき層 184 を覆うように上面が平坦な厚膜誘電体層 190 を形成する。厚膜誘電体層 190 としては、ポリイミド、BCB (Benzocyclobutene) 等を用いることができる。厚膜誘電体層 190 のパッドとなるべき領域等の所定領域を除去する。

50

## 【0032】

図11(b)を参照に、厚膜誘電体層190上に種層182と同じ膜厚の種層186を形成する。種層186上に開口部を有するフォトレジスト202を形成する。開口部内に電解めっきを行い、例えば膜厚が10μmのCuからなるめっき層188を形成する。めっき層188上にNi/Auからなる表面層189を形成する。

## 【0033】

図11(c)を参照に、フォトレジスト202を除去する。表面層189をマスクに種層186を除去する。種層186、めっき層188および表面層189により、パッド131および133並びに上部配線192が形成される。以上により、実施例4に係る集積化受動素子が完成する。実施例4に係る集積化受動素子において、インダクタ110は、特許文献1と同様にスパイラル状のコイルが1層で形成されている。このように、インダクタ110はスパイラル状のコイルが1層でもよい。また、実施例1および実施例2のように、インダクタは、縦方向に離間して設けられ互いに電気的に接続された複数のコイルでもよい。

10

## 【0034】

実施例4によれば、図10(a)のように、導電性パターン50は、基板102上に形成されたキャパシタ140の下部電極141と同時に形成されている。つまり、導電性パターン50は、下部電極141と同じ材料からなる。これにより、製造工程を簡略化することができる。また、導電性パターン50の光の反射率を高くするためには、導電性パターン50の上面が平坦であることが好ましい。よって、導電性パターン50をスパッタ法または蒸着法を用い形成することが好ましい。

20

## 【0035】

実施例1および実施例2に係るインダクタ素子の製造は、特許文献1に記載された方法で製造することができる。この場合も実施例4のように、キャパシタの下部電極と同時に導電性パターンを形成することができる。

## 【実施例5】

## 【0036】

実施例5は導電性パターンがコイルの外にある例である。図12は実施例5に係るインダクタ素子の平面図である。図12を参照に、実施例1の図2と比較して、導電性パターン50aがインダクタ30の外側に設けられている。導電性パターン50aは、インダクタ30の外周からインダクタ30の半径D/2外側の円11(径が2Dの円)の内側に形成されている。インダクタ30の磁場はインダクタ30の外側にも発生している。インダクタ30の外側の磁場はインダクタ30の半径程度の距離まで及ぶ。よって、導電性パターン50aがインダクタ30(つまり第1コイル10および第2コイル20)の外周からインダクタ30の半分の距離以内に設けられる場合にも、導電性パターンを分割することが有効である。これにより、インダクタ30のQ値およびインダクタンス値の低下を抑制することができる。

30

## 【0037】

実施例1から実施例5において、導電性パターンの材料は、基板との密着性の高い高融点材料、例えばTi、Cr、Ni、Mo、Ta、W等と、高周波抵抗の低いAu、Cu、Al、Ag等とを積層した膜が好ましい。特に、Ti/Au/Ti、Ti/Cu/Ti、CrまたはNi/AuまたはCuを用いることが好ましい。これにより、導電性パターンの高周波抵抗を低減でき、基板との密着性を向上させることができる。さらに、導電性パターンとキャパシタの下部電極とを同じ材料で形成した場合、下部電極とキャパシタの誘電体層との密着性を高めることができる。

40

## 【0038】

以上、本発明の実施例について詳述したが、本発明は係る特定の実施例に限定されるものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

## 【図面の簡単な説明】

50

## 【0039】

【図1】図1は比較例1に係るインダクタ素子の上面図である。

【図2】図2は実施例1に係るインダクタ素子の上面図である。

【図3】図3は実施例1の変形例に係るインダクタ素子の上面図である。

【図4】図4は比較例2に係るインダクタ素子の上面図である。

【図5】図5は各種類のインダクタ素子のQ値を示す図である。

【図6】図6は各種類のインダクタ素子のインダクタンス値を示す図である。

【図7】図7は実施例2に係る集積化受動素子の上面図である。

【図8】図8(a)から図8(c)は、実施例3の導電性パターンを示す図(その1)である。

【図9】図9(a)から図9(d)は、実施例3の導電性パターンを示す図(その2)である。

【図10】図10(a)から図10(d)は実施例4に係る集積化受動素子の製造工程を示す図(その1)である。

【図11】図11(a)から図11(c)は実施例4に係る集積化受動素子の製造工程を示す図(その2)である。

【図12】図12は実施例5に係るインダクタ素子の上面図である。

## 【符号の説明】

## 【0040】

|       |         |

|-------|---------|

| 1 0   | 第1コイル   |

| 2 0   | 第2コイル   |

| 2 5   | 基板      |

| 3 0   | インダクタ   |

| 5 0   | 導電性パターン |

| 1 4 1 | 下部電極    |

【図1】

【図3】

【図2】

【図4】

10

20

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(72)発明者 松本 剛

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 横山 剛

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 ミイ シヤオユウ

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 右田 勝則

(56)参考文献 特開平04-228135 (JP, A)

特開2007-067236 (JP, A)

特開2004-140587 (JP, A)

特開2005-045161 (JP, A)

特開2002-230496 (JP, A)

特開2007-173759 (JP, A)

特開2003-243570 (JP, A)

特開2000-058329 (JP, A)

実開昭56-139231 (JP, U)

特開2002-175508 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01F 27/06

H01F 27/00

H05K 1/02