**【特許請求の範囲】****【請求項 1】**

画素アレイ部の複数の画素列が少なくとも 2 つのグループに分割されており、そのうちの第 1 のグループの画素列から出力される第 1 の画素信号と第 1 のランプ信号とを比較することにより、前記第 1 の画素信号をAD変換する第 1 のAD変換部と、

前記画素アレイ部の前記第 1 のグループと異なる第 2 のグループの画素列から出力される第 2 の画素信号と第 2 のランプ信号とを比較することにより、前記第 2 の画素信号をAD変換する第 2 のAD変換部と

を備え、

前記第 1 のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第 2 のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

AD変換器。

**【請求項 2】**

前記画素アレイ部の複数の画素列は 2 つのグループに分割されており、

前記第 1 のグループと前記第 2 のグループは、前記画素アレイ部の奇数画素列と偶数画素列とで分割されている

請求項 1 に記載のAD変換器。

**【請求項 3】**

前記第 2 のAD変換部は、前記D相期間の前のリセットレベルを検出するP相期間のカウント値に前記D相期間の最大カウント値を加算した結果に、前記D相期間において前記第 2 のランプ信号のレベルが上昇を開始してから前記第 2 の画素信号のレベルと同一になるまでのカウント値を加算する

請求項 1 に記載のAD変換器。

**【請求項 4】**

前記第 2 のAD変換部は、前記D相期間の前のリセットレベルを検出するP相期間のカウント値に、前記D相期間において前記第 2 のランプ信号のレベルが上昇を開始して前記第 2 の画素信号のレベルと同一になってから最大レベルとなるまでのカウント値を加算する

請求項 1 に記載のAD変換器。

**【請求項 5】**

前記第 1 のランプ信号と前記第 2 のランプ信号を生成する参照信号生成部をさらに備える

請求項 1 に記載のAD変換器。

**【請求項 6】**

前記画素アレイ部の複数の画素列は 2 つのグループに分割されており、

前記第 1 のグループと前記第 2 のグループは、前記画素アレイ部の全ての画素列の右側半分と左側半分とで分割されている

請求項 1 に記載のAD変換器。

**【請求項 7】**

前記画素アレイ部の複数の画素列が 3 つのグループに分割されている

請求項 1 に記載のAD変換器。

**【請求項 8】**

画素アレイ部の複数の画素列が少なくとも 2 つのグループに分割されており、そのうちの第 1 のグループの画素列から出力される第 1 の画素信号をAD変換する第 1 のAD変換部と、前記画素アレイ部の前記第 1 のグループと異なる第 2 のグループの画素列から出力される第 2 の画素信号をAD変換する第 2 のAD変換部とを備えるAD変換器の

前記第 1 のAD変換部が、前記第 1 の画素信号と第 1 のランプ信号とを比較することにより、前記第 1 の画素信号をAD変換し、

前記第 2 のAD変換部が、前記第 2 の画素信号と第 2 のランプ信号とを比較することによ

10

20

30

40

50

り、前記第2の画素信号をAD変換し、

前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

信号処理方法。

#### 【請求項9】

複数の画素が行列状に2次元配置された画素アレイ部と、

前記画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、

前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部と

を備え、

前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

固体撮像装置。

#### 【請求項10】

複数の画素が行列状に2次元配置された画素アレイ部と、

前記画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、

前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部と

を備え、

前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

固体撮像装置

を備える電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本技術は、AD変換器、信号処理方法、固体撮像装置、および電子機器に関し、特に、より簡単な回路構成で、ストリーキングの発生を低減させることができるようとするAD変換器、信号処理方法、固体撮像装置、および電子機器に関する。

##### 【背景技術】

##### 【0002】

カラムAD方式のCMOSイメージセンサでは、画素固有の固定パターンノイズを除去するため、CDS(Correlated Double Sampling；相関2重サンプリング)処理が行われている。CDS処理では、コンパレータにおいて、各画素から出力されたアナログの画素信号が、時間経過に応じて一定の傾きで低下するランプ信号と比較される。そして、P相(Preset Phase)期間では、例えば、比較結果としてHiの差信号が供給されている間だけダウンカウントするとともに、D相(Data Phase)期間では、比較結果としてHiの差信号が供給されている間だけアップカウントする。

10

20

30

40

50

**【0003】**

従来のCDS処理では、黒地の画像の中に、一部、白い領域があるような画像を撮像する場合に、ストリーキングが発生することが問題となっていた。ストリーキングとは、黒地の画像の中に、一部、白い領域があるような画像において、白い領域の左右方向の黒地となるべき画素がグレーとなってしまう現象のことをいう。ストリーキングの発生原因としては、コンパレータ出力からのクロストークによるランプ信号の歪みが主な原因となっている。

**【0004】**

本出願人は、特許文献1において、ストリーキングの発生を低減させる方法を先に提案している。

10

**【先行技術文献】****【特許文献】****【0005】**

【特許文献1】特開2010-161484号公報

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

しかしながら、より簡単な回路構成で、ストリーキングの発生を低減させることが望まれている。

**【0007】**

本技術は、このような状況に鑑みてなされたものであり、より簡単な回路構成で、ストリーキングの発生を低減させることができるようとするものである。

20

**【課題を解決するための手段】****【0008】**

本技術の第1の側面のAD変換器は、画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部とを備え、前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である。

30

**【0009】**

本技術の第2の側面の信号処理方法は、画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号をAD変換する第1のAD変換部と、前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号をAD変換する第2のAD変換部とを備えるAD変換器の前記第1のAD変換部が、前記第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換し、前記第2のAD変換部が、前記第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換し、前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である。

40

**【0010】**

本技術の第3の側面の固体撮像装置は、複数の画素が行列状に2次元配置された画素アレイ部と、前記画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の

50

画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部とを備え、前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である。

【0011】

本技術の第4の側面の電子機器は、複数の画素が行列状に2次元配置された画素アレイ部と、前記画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部とを備え、前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である固体撮像装置を備える。

10

【0012】

本技術の第1乃至第4の側面においては、複画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号をAD変換する第1のAD変換部において、前記第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号がAD変換され、前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号をAD変換する第2のAD変換部において、前記第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号がAD変換され、前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下し、前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する。

20

【0013】

AD変換器、固体撮像装置、及び電子機器は、独立した装置であっても良いし、他の装置に組み込まれるモジュールであっても良い。

30

【発明の効果】

【0014】

本技術の第1乃至第4の側面によれば、より簡単な回路構成で、ストリーキングの発生を低減させることができる。

【図面の簡単な説明】

【0015】

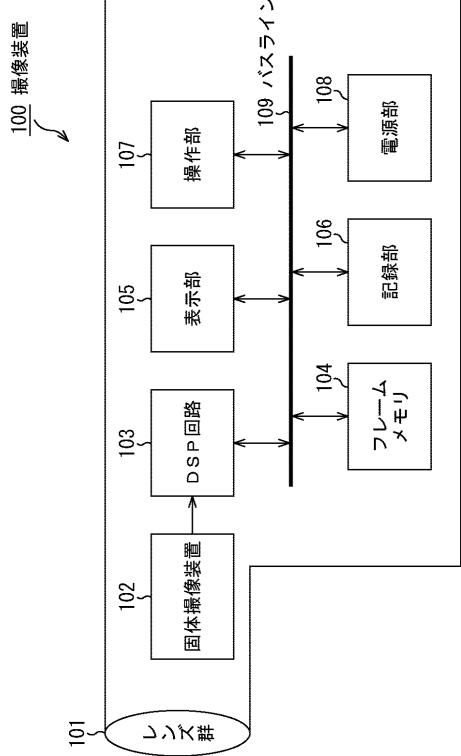

【図1】本技術が適用された固体撮像装置の第1の実施の形態の構成を示すブロック図である。

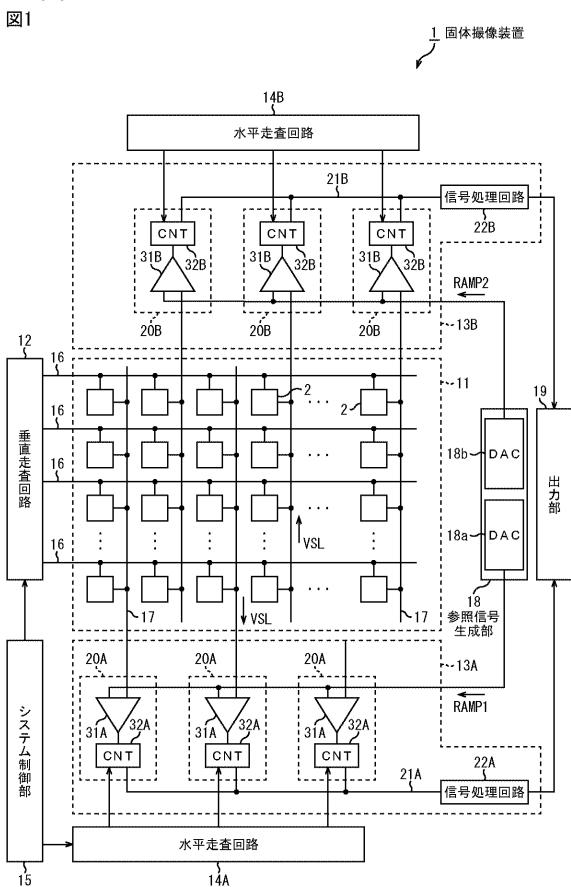

【図2】画素の回路構成例を示す図である。

40

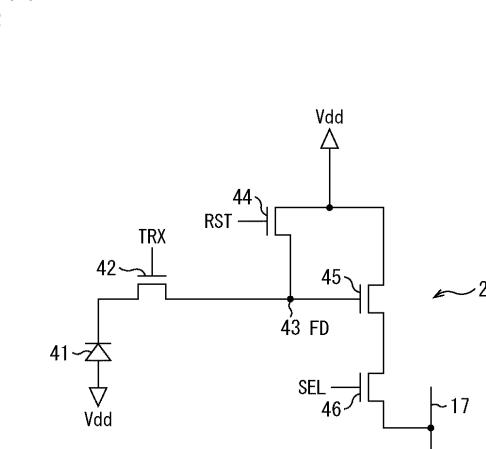

【図3】ストリーキングの現象とその原因について説明する図である。

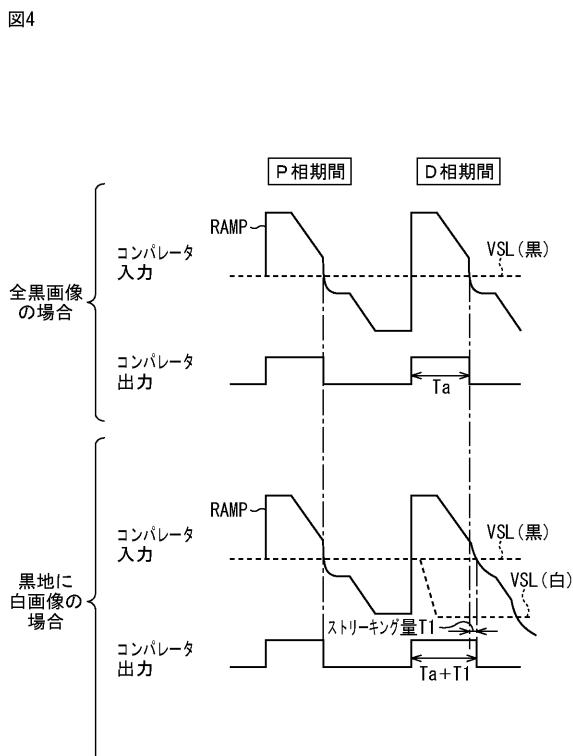

【図4】ストリーキングの現象とその原因について説明する図である。

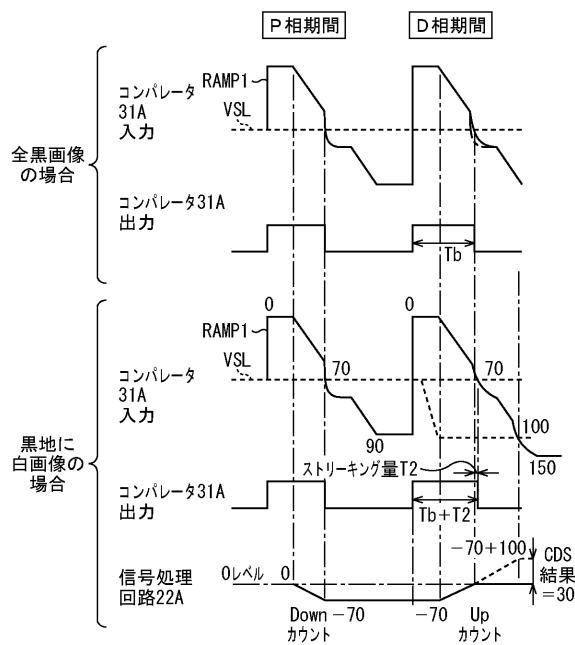

【図5】画素アレイ部の下側のAD変換部の第1のAD変換処理の動作を説明する図である。

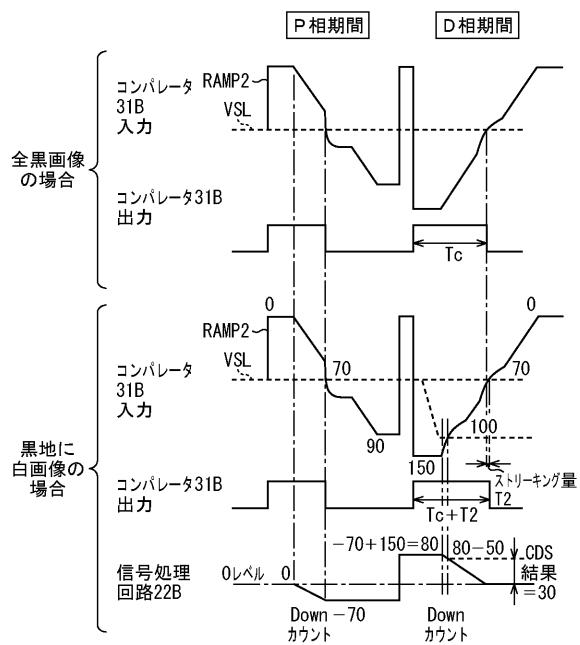

【図6】画素アレイ部の上側のAD変換部の第1のAD変換処理の動作を説明する図である。

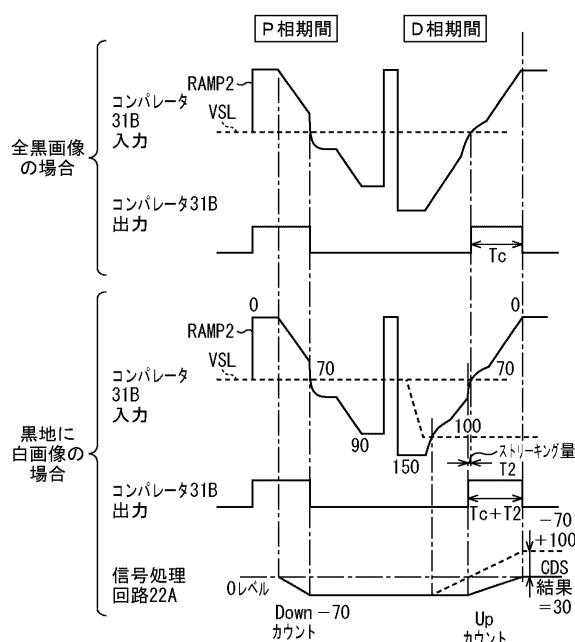

【図7】画素アレイ部の上側のAD変換部の第2のAD変換処理の動作を説明する図である。

【図8】本技術が適用された固体撮像装置の第2の実施の形態の構成を示すブロック図である。

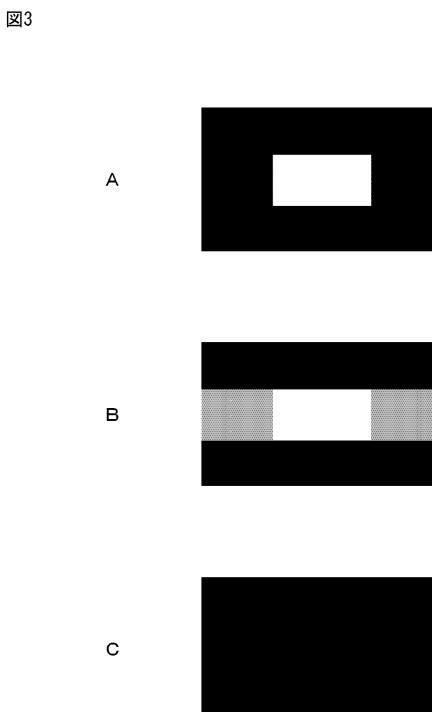

【図9】本技術を適用した電子機器としての撮像装置の構成例を示すブロック図である。

【発明を実施するための形態】

【0016】

以下、本技術を実施するための形態（以下、実施の形態という）について説明する。な

50

お、説明は以下の順序で行う。

1. 第1の実施の形態（奇数画素列と偶数画素列でAD変換処理を分けた固体撮像装置の構成例）

2. 第2の実施の形態（画素アレイ部の右側半分と左側半分でAD変換処理を分けた固体撮像装置の構成例）

3. 第3の実施の形態（電子機器の構成例）

【0017】

<1. 第1の実施の形態>

<固体撮像装置の全体構成例>

図1は、本技術が適用された固体撮像装置の第1の実施の形態の構成を示すブロック図である。

【0018】

図1に示される固体撮像装置1は、画素アレイ部11、垂直走査回路12、AD変換部13、水平走査回路14、システム制御部15、画素駆動線16、垂直信号線17、参照信号生成部18、及び出力部19などを含んで構成される。

【0019】

ここで、AD変換部13と水平走査回路14は、画素アレイ部11の上側と下側のそれぞれに配置されている。具体的には、画素アレイ部11の下側には、AD変換部13Aと水平走査回路14Aが配置され、画素アレイ部11の上側には、AD変換部13Bと水平走査回路14Bが配置されている。

【0020】

画素アレイ部11は、受光した光量に応じた光電荷を生成し、かつ、蓄積する光電変換部を有する画素2が行方向及び列方向の行列状に2次元配置された構成となっている。ここで、行方向とは画素行の配列方向、即ち、水平方向を言い、列方向とは画素列の配列方向、即ち、垂直方向を言う。

【0021】

画素2は、フォトダイオードなどの光電変換部と複数の画素トランジスタを有して成る。複数の画素トランジスタは、例えば、転送トランジスタ、選択トランジスタ、リセットトランジスタ及び増幅トランジスタの4つのMOSトランジスタで構成される。

【0022】

また、画素2は、共有画素構造とすることもできる。この画素共有構造は、複数のフォトダイオードと、複数の転送トランジスタと、共有する1つのフローティングディフュージョン（浮遊拡散領域）と、共有する1つずつの他の画素トランジスタとから構成される。すなわち、共有画素では、複数の単位画素を構成するフォトダイオード及び転送トランジスタが、他の1つずつの画素トランジスタを共有して構成される。

【0023】

画素アレイ部11の行列状の画素配列に対して、画素行ごとに画素駆動線16が水平方向に沿って配線され、画素列ごとに垂直信号線17が垂直方向に沿って配線されている。画素駆動線16は、画素2から画素信号VSLを読み出す際の駆動を行うための駆動信号を伝送する。図1では、画素駆動線16について1本の配線として示しているが、1本に限られるものではない。画素駆動線16の一端は、垂直走査回路12の各画素行に対応した出力端に接続されている。

【0024】

垂直走査回路12は、シフトレジスタやアドレスデコーダなどによって構成され、画素アレイ部11の各画素2を全画素同時あるいは行単位等で駆動する。垂直走査回路12の具体的な構成については図示を省略するが、一般的に、読み出し走査系と掃出し走査系の2つの走査系を有する構成となっている。

【0025】

読み出し走査系は、画素2から画素信号VSLを読み出すために、画素アレイ部11の画素2を行単位で順に選択走査する。画素2から読み出される画素信号VSLはアナログ信号

10

20

30

40

50

である。掃出し走査系は、読み出し走査系によって読み出し走査が行われる読み出し行に對して、その読み出し走査よりもシャッタスピードの時間分だけ先行して掃出し走査を行う。

【0026】

この掃出し走査系による掃出し走査により、読み出し行の画素2の光電変換部から不要な電荷が掃き出されることによって光電変換部がリセットされる。そして、この掃出し走査系によって不要電荷を掃き出す（リセットする）ことにより、所謂電子シャッタ動作が行われる。ここで、電子シャッタ動作とは、光電変換部の光電荷を捨てて、新たに露光を開始する（光電荷の蓄積を開始する）動作のことを言う。

【0027】

読み出し走査系による読み出し動作によって読み出される画素信号VSLは、その直前の読み出し動作または電子シャッタ動作以降に受光した光量に対応するものである。そして、直前の読み出し動作による読み出しタイミングまたは電子シャッタ動作による掃出しタイミングから、今回の読み出し動作による読み出しタイミングまでの期間が、画素2における光電荷の露光期間となる。

【0028】

垂直走査回路12によって選択走査された画素行の各画素2から出力される画素信号VSLは、画素列ごとに垂直信号線17の各々を通してAD変換部13Aまたは13Bに入力される。

【0029】

画素アレイ部11の奇数画素列の垂直信号線17は、画素アレイ部11の下側に配置されたAD変換部13Aに接続されている。AD変換部13Aは、画素アレイ部11の奇数画素列の画素2から出力される画素信号VSLをCDS(Correlated Double Sampling；相関2重サンプリング)処理およびAD変換処理するカラムAD変換部20Aと信号処理回路22Aを有している。

【0030】

一方、画素アレイ部11の偶数画素列の垂直信号線17は、画素アレイ部11の上側に配置されたAD変換部13Bに接続されている。AD変換部13Bは、画素アレイ部11の偶数画素列の画素2から出力される画素信号VSLをCDS処理およびAD変換処理するカラムAD変換部20Bと信号処理回路22Bを有している。

【0031】

各カラムAD変換部20（20Aおよび20B）は、同列の画素2から垂直信号線17を介して供給される画素信号VSLに基づいて、CDS処理のためのカウント処理を実行する。カラムAD変換部20は、コンパレータ（比較器）31とアップダウンカウンタ（CNT）32を有する。

【0032】

画素アレイ部11の下側に配置されたカラムAD変換部20Aには、参照信号生成部18のDAC18aから、ランプ信号RAMP1が供給される。カラムAD変換部20Aのコンパレータ31Aは、画素アレイ部11の奇数画素列の画素2が出力する画素信号VSLと、DAC18aからのランプ信号RAMP1とを比較する。アップダウンカウンタ32Aは、コンパレータ31Aの比較結果に応じて、ダウンカウントまたはアップカウントし、その結果を、水平出力線21Aを介して信号処理回路22Aに出力する。

【0033】

信号処理回路22Aは、P相（Preset Phase）期間のカウント結果とD相（Data Phase）期間のカウント結果に基づいて、アナログの画素信号VSLをCDS処理およびAD変換処理した画素データを算出する。ここで、P相期間は、CDS処理においてリセットレベルを検出する期間であり、D相期間は、CDS処理において信号レベルを検出する期間である。

【0034】

画素アレイ部11の上側に配置されたカラムAD変換部20Bには、参照信号生成部18のDAC18bから、ランプ信号RAMP2が供給される。ランプ信号RAMP1とランプ信号RAMP2の

10

20

30

40

50

違いについては後述する。

【0035】

カラムAD変換部20Bのコンパレータ31Bは、画素アレイ部11の偶数画素列の画素2が<sup>2</sup>出力する画素信号VSLと、DAC18bからのランプ信号RAMP2とを比較する。アップダウンカウンタ32Bは、コンパレータ31Bの比較結果に応じて、ダウンカウントまたはアップカウントし、その結果を、水平出力線21Bを介して信号処理回路22Bに出力する。

【0036】

信号処理回路22Bは、P相期間のカウント結果と、D相期間のカウント結果に基づいて、アナログの画素信号VSLをCDS処理およびAD変換処理した画素データを算出する。

【0037】

AD変換部13A及び13Bは、アナログの画素信号VSLをCDS処理し、かつ、AD変換するAD変換装置を構成する。また、ランプ信号RAMP1及びRAMP2を生成する参照信号生成部18を含めた構成をAD変換装置とすることもできる。以下では、AD変換部13A及び13Bが行うCDS処理し、かつ、AD変換する処理を、まとめてAD変換処理ともいう。

10

【0038】

水平走査回路14Aは、シフトレジスタやアドレスデコーダなどによって構成され、奇数画素列に対応する各カラムAD変換部20Aを所定の順番で選択する。この水平走査回路14Aによる選択走査により、AD変換部13A内の各カラムAD変換部20Aで一時的に保持されているカウント結果が、水平出力線21Aを通って順番に信号処理回路22Aに出力される。

20

【0039】

水平走査回路14Bも同様に、シフトレジスタやアドレスデコーダなどによって構成され、偶数画素列に対応する各カラムAD変換部20Bを所定の順番で選択する。この水平走査回路14Bによる選択走査により、AD変換部13B内の各カラムAD変換部20Bで一時的に保持されているカウント結果が、水平出力線21Bを通って順番に信号処理回路22Bに出力される。

20

【0040】

システム制御部15は、各種のタイミング信号を生成するタイミングジェネレータなどによって構成され、タイミングジェネレータで生成された各種のタイミングを基に、垂直走査回路12、AD変換部13、及び、水平走査回路14などの駆動制御を行う。なお、図1では、システム制御部15から各部への制御信号の図示が一部省略されている。

30

【0041】

参照信号生成部18は、異なるランプ信号RAMP1及びRAMP2を生成するDAC(Digital to Analog Converter)18aと18bを有する。DAC18aで生成されたランプ信号RAMP1は、AD変換部13Aの各カラムAD変換部20Aのコンパレータ31Aに供給される。DAC18bで生成されたランプ信号RAMP2は、AD変換部13Bの各カラムAD変換部20Bのコンパレータ31Bに供給される。

【0042】

出力部19は、例えば、信号処理回路22Aから供給される奇数画素列の画素データと、信号処理回路22Bから供給される偶数画素列の画素データとを、画素アレイ部11内の画素2の配列順序となるように交互に選択して、固体撮像装置1の外部へ出力する。

40

【0043】

以上のように構成される固体撮像装置1は、CDS処理とAD変換処理を行うカラムAD変換部20が画素列ごとに配置されたカラムAD方式と呼ばれるCMOSイメージセンサである。

【0044】

<画素の回路構成例>

図2は、画素2の回路構成例を示している。

【0045】

画素2は、光電変換素子としてのフォトダイオード41、転送トランジスタ42、FD(フローティングディフュージョン)43、リセットトランジスタ44、増幅トランジスタ

50

45、および選択トランジスタ46を有する。

【0046】

フォトダイオード41は、受光した光量に応じた電荷（信号電荷）を生成し、かつ、蓄積する。フォトダイオード41は、アノード端子が接地されているとともに、カソード端子が転送トランジスタ42を介して、FD43に接続されている。

【0047】

転送トランジスタ42は、転送信号TRXによりオンされたとき、フォトダイオード41で生成された電荷を読み出し、FD43に転送する。

【0048】

FD43は、フォトダイオード41から読み出された電荷を保持する。リセットトランジスタ44は、リセット信号RSTによりオンされたとき、FD43に蓄積されている電荷がドレイン（定電圧源Vdd）に排出されることで、FD43の電位をリセットする。

【0049】

増幅トランジスタ45は、FD43の電位に応じた画素信号を出力する。すなわち、増幅トランジスタ45は、垂直信号線17を介して接続されている定電流源としての負荷MOS（不図示）とソースフォロワ回路を構成し、FD43に蓄積されている電荷に応じたレベルを示す画素信号が、増幅トランジスタ45から選択トランジスタ46を介してカラムAD変換部20に出力される。

【0050】

選択トランジスタ46は、選択信号SELにより画素2が選択されたときオンされ、画素2の画素信号を、垂直信号線17を介してカラムAD変換部20に出力する。転送信号TRX、選択信号SEL、及びリセット信号RSTが伝送される各信号線は、図1の画素駆動線16に対応する。

【0051】

画素2は、以上のように構成することができるが、この構成に限定されるものではなく、その他の構成を採用することもできる。

【0052】

図1の固体撮像装置1は、ストリーキングの発生を低減させるため、奇数画素列の画素信号をAD変換処理するAD変換部13Aと、偶数画素列の画素信号をAD変換処理するAD変換部13Bとで異なる処理を行う構成とされている。

【0053】

そこで以下において、AD変換部13AとAD変換部13Bのそれぞれが行う処理の詳細について説明する。

【0054】

初めに、図3および図4を参照して、ストリーキングの現象と、その原因について説明する。

【0055】

ストリーキングとは、図3Aに示されるような、黒地（暗い領域）の画像の一部に白い領域（明るい領域）が存在する画像を撮像した場合に、図3Bに示されるように、白い領域の左右方向の黒地となるべき画素が、グレーとなってしまう現象のことをいう。ストリーキングが発生する原因について、図3Cに示される全画素が黒地の画像を撮像する場合と比較して説明する。なお、以下において、図3Cに示されるような、全画素の画素値が黒である画像を全黒画像と称し、図3Aに示されるような、黒地の画像の一部に白い領域が存在する画像を、黒地に白画像と称する。

【0056】

図4は、従来のAD変換処理を行うコンパレータの入出力信号を示している。

【0057】

図4上側は、図3Cに示した全黒画像となる被写体を撮像した場合のコンパレータの入出力信号を示しており、図4下側は、図3Aに示した黒地に白画像となる被写体を撮像した場合のコンパレータの入出力信号を示している。

10

20

30

40

50

## 【0058】

コンパレータには、各画素から出力されたアナログの画素信号VSLと、時間経過に応じてレベル（電圧値）が一定の傾きをもって低下するランプ信号RAMPが、入力される。なお、ランプ信号RAMPは、厳密には、一定の傾斜となるように、時間経過に応じてレベルが階段状に変化する信号である。

## 【0059】

P相期間において、コンパレータは、入力された画素信号VSLと、レベルが一定の傾きで低下するランプ信号RAMPとを比較して、ランプ信号RAMPのレベルが画素信号VSLのレベルより大である場合に、Hi(High)の差信号を出力する。そして、画素信号VSLとランプ信号RAMPが同一のレベルとなったとき、コンパレータは、出力を反転させ、Lo(Low)の差信号を出力する。アップダウンカウンタは、P相期間において、ランプ信号RAMPが電圧降下を開始してから画素信号VSLと同一のレベルとなるまでの時間をダウンカウントする。

10

## 【0060】

P相期間が終了すると、ランプ信号RAMPのレベルがカウント開始前の所定電圧に再度設定される。そして、D相期間において、コンパレータは、入力された画素信号VSLと、レベルが一定の傾きで低下するランプ信号RAMPを比較して、ランプ信号RAMPのレベルが画素信号VSLのレベルより大である場合に、Hiの差信号を出力する。そして、画素信号VSLとランプ信号RAMPが同一のレベルとなったとき、コンパレータは、出力を反転させ、Loの差信号を出力する。アップダウンカウンタは、D相期間において、ランプ信号RAMPが電圧降下を開始してから画素信号VSLと同一のレベルとなるまでの時間をアップカウントする。

20

## 【0061】

そして、アップダウンカウンタの後段の信号処理回路は、P相期間のダウンカウント値とD相期間のアップカウント値を取得し、それらを加算して、AD変換後の画素データ（デジタルの画素信号）として出力する。

## 【0062】

ランプ信号RAMPは、理想的には、レベルが時間経過に応じて一定の傾斜で低下する信号であるが、実際には、コンパレータ出力が一斉に反転することによりクロストークが発生し、図4に示されるように、コンパレータ出力の一斉反転のタイミングで、ランプ信号RAMPに歪みが生ずる。

30

## 【0063】

図4上側に示される全黒画像を撮像した場合には、コンパレータ出力が、P相期間とD相期間のいずれにおいても、読み出し画素行の全画素で同時に反転（一斉反転）する。そのため、P相期間における一斉反転時のランプ信号RAMPの歪み量と、D相期間における一斉反転時のランプ信号RAMPの歪み量はほぼ同一となり、ランプ信号RAMPの歪みによるカウント値のずれはキャンセルされる。ここで、全黒画像におけるD相期間のHi信号出力期間をTaとする。

## 【0064】

これに対して、図4下側に示される黒地に白画像を撮像した場合には、図4下側に示されるように、D相期間の画素信号VSLのレベルが、白画素に対応するレベルと、黒画素に対応するレベルの2種類存在する。そのため、全黒画像のD相期間では、コンパレータ出力が、読み出し画素行の全画素で一斉反転するのに対して、黒地に白画像のD相期間では、黒画素に対応する読み出し画素行の一部の画素が先に反転し、その後、白画素に対応する残りの画素が反転する。これにより、コンパレータ出力が反転するタイミングが、黒画素のタイミングと白画素のタイミングの2回に分かれるため、黒地に白画像の場合の黒画素の反転タイミングにおけるランプ信号RAMPの歪み量は、全黒画像の場合の黒画素の反転タイミングにおけるランプ信号RAMPの歪み量よりも少なくなる。この全黒画像における黒画素の一斉反転時のランプ信号RAMPの歪み量と、黒地に白画像における黒画素の一斉反転時のランプ信号RAMPの歪み量の違いにより、黒地に白画像におけるD相期間のHi信号出力期間は、全黒画像のときのHi信号出力期間TaよりもT1時間だけ長いTa + T1となる。黒地に白画像におけるD相期間のHi信号出力期間Ta + T1と、全黒画像のときのHi信号出力期間Taと

40

50

の差分T1が、カウント値として現れ、ストリーキング量T1となる。

【0065】

以上のように、従来のCDS処理では、コンパレータ出力が一斉に反転することによりクロストークが発生し、全黒画像のときの一斉反転時のランプ信号RAMPの歪み量と、黒地に白画像のときの一斉反転時のランプ信号RAMPの歪み量の違いが、ストリーキング発生の要因となっていた。

【0066】

＜第1のAD変換処理＞

次に、ストリーキングの発生を低減させた固体撮像装置1が行う第1のAD変換処理について説明する。

10

【0067】

固体撮像装置1では、画素アレイ部11の下側に配置されたAD変換部13Aと、画素アレイ部11の上側に配置されたAD変換部13Bとで、同一レベルの画素信号VSLであっても、コンパレータ出力の反転タイミングが異なるように構成されている。換言すれば、画素アレイ部11の奇数画素列と偶数画素列とで、同一レベルの画素信号VSLであっても、コンパレータ出力の反転タイミングが異なるように構成されている。

【0068】

具体的には、画素アレイ部11の下側に配置されたAD変換部13Aのコンパレータ31Aには、DAC18aから、従来と同様の、時間経過に応じてレベルが一定の傾きで低下するランプ信号RAMP1が供給される。

20

【0069】

一方、画素アレイ部11の上側に配置されたAD変換部13Bのコンパレータ31Bには、DAC18bから、D相期間においてランプ信号RAMP1とはレベルが反転されたランプ信号RAMP2が供給される。すなわち、D相期間のコンパレータ31Bには、DAC18bから、時間経過に応じてレベルが一定の傾きで上昇するランプ信号RAMP2が供給される。これにより、ランプ信号RAMP1が供給されるコンパレータ31Aと、ランプ信号RAMP2が供給されるコンパレータ31Bとは、同一レベルの画素信号VSLであっても、コンパレータ出力の反転タイミングが異なるものとなる。

【0070】

ランプ信号RAMP1が供給されるコンパレータ31Aと、ランプ信号RAMP2が供給されるコンパレータ31Bのそれぞれの動作について、図5と図6を参照して順に説明する。

30

【0071】

＜AD変換部13AのAD変換処理＞

初めに、図5を参照して、画素アレイ部11の下側に配置されたAD変換部13Aの動作について説明する。

【0072】

画素アレイ部11の下側に配置されたAD変換部13Aにおいて、図4に示した従来の駆動と異なる点は、全黒画像のD相期間において、コンパレータ31Aの出力が一斉反転する際のランプ信号RAMP1の歪み量が、図4に示した従来のランプ信号RAMPの歪み量よりも少なくなっている点である。図5上側の全黒画像のランプ信号RAMP1には、比較のため、図4に示した従来のランプ信号RAMPの歪みを一点鎖線で示している。

40

【0073】

ランプ信号RAMP1の歪みは、上述したように、コンパレータ出力が一斉に反転することによるクロストークにより生じる。本実施の形態では、画素アレイ部11の下側のAD変換部13Aには、奇数画素列に対応するカラムAD変換部20のみが配置されているため、コンパレータ31Aの個数は従来構成の半分である。そして、詳細は図6で後述するが、ランプ信号RAMP1とランプ信号RAMP2が異なることで、AD変換部13Aのコンパレータ31Aの出力が一斉反転するタイミングは、画素アレイ部11の上側のAD変換部13Bのコンパレータ31Bの出力が一斉反転するタイミングと異なるものとなる。これにより、全黒画像のD相期間において、出力が一斉反転するコンパレータ31Aの個数は従来の半分となるの

50

で、コンパレータ31Aの出力が一斉反転する際のランプ信号RAMP1の歪み量は、図4に示した従来のランプ信号RAMPの歪み量よりも少なくなる。

【0074】

全黒画像のD相期間におけるランプ信号RAMP1の歪み量が図4のランプ信号RAMPの歪み量よりも少ないことにより、全黒画像のD相期間におけるコンパレータ31AのHi信号出力期間Tbは、図4のHi信号出力期間Taよりも長くなる(Ta< Tb)。

【0075】

そのため、図5下側に示される黒地に白画像を撮像した場合のD相期間のランプ信号RAMP1の歪み量と、図5上側の全黒画像におけるD相期間のランプ信号RAMP1の歪み量の違いに相当するストリーキング量T2は、従来のストリーキング量T1よりも小さくなる(T1>T2)。したがって、固体撮像装置1によれば、ストリーキングの発生を低減させることができる。

10

【0076】

AD変換部13Aが行う動作自体は、図4を参照して説明した従来のAD変換処理と同様である。

【0077】

すなわち、コンパレータ31Aには、各画素から出力されたアナログの画素信号VSLと、P相期間とD相期間のいずれにおいても時間経過に応じてレベル(電圧値)が一定の傾きで低下するランプ信号RAMP1が、入力される。

20

【0078】

P相期間において、コンパレータ31Aは、入力された画素信号VSLと、レベルが一定の傾きで低下するランプ信号RAMP1とを比較して、ランプ信号RAMP1のレベルが画素信号VSLのレベルより大である場合に、Hiの差信号を出力する。そして、画素信号VSLとランプ信号RAMP1が同一のレベルとなったとき、コンパレータ31Aは、出力を反転させ、Loの差信号を出力する。アップダウンカウンタ32Aは、P相期間において、ランプ信号RAMP1が電圧降下を開始してから画素信号VSLと同一のレベルとなるまでの時間をダウンカウントする。

20

【0079】

P相期間が終了すると、ランプ信号RAMP1のレベルがカウント開始前の所定電圧に再度設定される。そして、D相期間において、コンパレータ31Aは、入力された画素信号VSLと、レベルが一定の傾きで低下するランプ信号RAMP1を比較して、ランプ信号RAMP1のレベルが画素信号VSLのレベルより大である場合に、Hiの差信号を出力する。そして、画素信号VSLとランプ信号RAMP1が同一のレベルとなったとき、コンパレータ31Aは、出力を反転させ、Loの差信号を出力する。アップダウンカウンタ32Aは、D相期間において、ランプ信号RAMP1が電圧降下を開始してから画素信号VSLと同一のレベルとなるまでの時間をアップカウントする。

30

【0080】

信号処理回路22Aは、P相期間のダウンカウント値とD相期間のアップカウント値を取得し、それらを加算して、AD変換後の画素データとして出力する。

30

【0081】

例えば、図5に示されるように、黒地に白画像を撮像した場合のP相期間のアップダウンカウンタ32Aのダウンカウント値が-70である。また、D相期間において、ランプ信号RAMP1が黒画素の画素信号VSLと交差するまでのアップダウンカウンタ32Aのアップカウント値は70であり、ランプ信号RAMP1が白画素の画素信号VSLと交差するまでのアップダウンカウンタ32Aのアップカウント値は100である。この場合、信号処理回路22Aにより計算される黒画素(黒地)のAD変換後の画素データは、-70+70=0であり、白画素(白い領域)のAD変換後の画素データは、-70+100=30となる。

40

【0082】

なお、図5の例では、P相期間の最大カウント値(Pレンジ)は、90であり、D相期間の最大カウント値(Dレンジ)は、150に設定されている。

50

## 【0083】

&lt;AD変換部13BのAD変換処理&gt;

次に、図6を参照して、画素アレイ部11の上側に配置されたAD変換部13Bの動作について説明する。

## 【0084】

AD変換部13BにおけるP相期間の動作は、上述したAD変換部13Aと同様である。したがって、P相期間でDAC18bから供給されるランプ信号RAMP2は、ランプ信号RAMP1と同様に、時間経過に応じてレベルが一定の傾きで低下する信号である。アップダウンカウンタ32Bは、P相期間において、ランプ信号RAMP2が電圧降下を開始してから画素信号VSLと同一のレベルとなるまでの時間をダウンカウントする。例えば、図6に示されるように、P相期間のアップダウンカウンタ32Bのダウンカウント値が-70となる。

10

## 【0085】

次のD相期間では、DAC18bから供給されるランプ信号RAMP2は、図6に示されるように、Dレンジ分だけ反転され、時間経過に応じてレベルが一定の傾きで上昇する信号となる。そして、アップダウンカウンタ32Bは、D相期間において、ランプ信号RAMP2のレベルが電圧上昇を開始してから白画素または黒画素の画素信号VSLのレベルと同一になるまでのダウンカウントする。ランプ信号RAMP2は、時間経過に応じてレベルが一定の傾きで上昇していくので、白画素の画素信号VSLと最初に交差し、その後、黒画素の画素信号VSLと交差する。

20

## 【0086】

信号処理回路22Bは、初めに、P相期間におけるアップダウンカウンタ32Bのダウンカウント値を取得する。図6の例では、信号処理回路22Bは、ダウンカウント値として、-70を取得する。

## 【0087】

そして、信号処理回路22Bは、D相期間の最初のランプ信号RAMP2のレベル反転に応じて、Dレンジに相当するカウント数を、P相期間のダウンカウント値に加算する。いまの例では、Dレンジは150であるので、信号処理回路22Bは、 $-70 + 150 = 80$ を算出する。

## 【0088】

最後に、信号処理回路22Bは、D相期間におけるアップダウンカウンタ32Bのダウンカウント値を取得し、保持しているカウント結果と加算する。図6の例では、ランプ信号RAMP2のレベルが白画素の画素信号VSLのレベルと同一レベルになるまでのアップダウンカウンタ32Bのダウンカウント値は-50であり、黒画素の画素信号VSLのレベルと同一レベルになるまでのアップダウンカウンタ32Bのダウンカウント値は-80である。この場合、信号処理回路22Bにより計算される白画素(白い領域)のAD変換後の画素データは、 $80 - 50 = 30$ であり、黒画素(黒地)のAD変換後の画素データは、 $80 - 80 = 0$ となる。したがって、白画素と黒画素のいずれにおいても、従来駆動を行っているAD変換部13Aと同一の画素データが得られる。

30

## 【0089】

図6上側の全黒画像において、コンパレータ31BのHi信号出力期間Tcは、ランプ信号RAMP2のレベルがランプ信号RAMP1とは反転されたものとなっていることによって、AD変換部13Aのコンパレータ31AのHi信号出力期間Tbとは異なる時間となる。その結果、全黒画像のD相期間において、出力が一斉反転するコンパレータ31Bの個数は従来の半分となるので、コンパレータ31Bの出力が一斉反転する際のランプ信号RAMP2の歪み量は、図4に示した従来のランプ信号RAMPの歪み量よりも少なくなる。これにより、図6下側に示される黒地に白画像を撮像した場合のD相期間のランプ信号RAMP2の歪み量と、図6上側の全黒画像におけるD相期間のランプ信号RAMP2の歪み量の違いに相当するストリーリング量T2は、従来のストリーリング量T1よりも小さくなる( $T1 > T2$ )。したがって、固体撮像装置1によれば、ストリーリングの発生を低減させることができる。

40

## 【0090】

50

## &lt;第2のAD変換処理&gt;

次に、図1の固体撮像装置1が行うことができる、上述した第1のAD変換処理とは異なる第2のAD変換処理について説明する。

## 【0091】

上述した第1のAD変換処理では、D相期間のランプ信号RAMP2のDレンジ分のレベル反転に応じて、信号処理回路22Bが、Dレンジに相当するカウント数をP相期間のダウンカウント値に加算する必要がある。

## 【0092】

しかしながら、画素信号VSLのばらつきにより、実際のDレンジはばらつくことが考えられ、P相期間のダウンカウント値に加算されるDレンジ相当のカウント数とは一致しない場合がある。そこで、以下に説明する第2のAD変換処理では、Dレンジ相当のカウント数を加算しない方法が採用されている。

## 【0093】

第2のAD変換処理におけるAD変換部13Aの動作は、図5に示した第1のAD変換処理におけるAD変換部13Aの動作と同様であるので、その説明は省略する。

## 【0094】

図7は、第2のAD変換処理におけるAD変換部13Bの動作を示している。

## 【0095】

P相期間の動作は、上述した第1のAD変換処理のAD変換部13Bと同様である。すなわち、P相期間では、コンパレータ31Bは、時間経過に応じてレベルが一定の傾きで低下するランプ信号RAMP2と、画素信号VSLとを比較して差信号を出力する。アップダウンカウンタ32Bは、ランプ信号RAMP2が電圧降下を開始してから画素信号VSLと同一のレベルとなるまでの時間をダウンカウントする。

## 【0096】

次のD相期間では、DAC18bから供給されるランプ信号RAMP2のレベルが、図7に示されるように、Dレンジ分だけ反転され、時間経過に応じて一定の傾きで上昇していく。コンパレータ31Bは、ランプ信号RAMP2のレベルが画素信号VSLのレベルと同一レベルとなってから最大レベルに到達するまで、Hiの差信号を出力する。アップダウンカウンタ32Bは、D相期間において、ランプ信号RAMP2のレベルが画素信号VSLのレベルと同一レベルとなってから最大レベルに到達するまでアップカウントする。

## 【0097】

信号処理回路22Bは、P相期間におけるアップダウンカウンタ32Bのダウンカウント値と、D相期間におけるアップダウンカウンタ32Bのアップカウント値を取得する。そして、信号処理回路22Bは、P相期間のダウンカウント値と、D相期間のアップカウント値とを加算した結果を、画素データとして出力する。

## 【0098】

例えば、図7に示されるように、P相期間のアップダウンカウンタ32Bのダウンカウント値が-70である。そして、D相期間において、ランプ信号RAMP2のレベルが白画素の画素信号VSLのレベルと同一になってから最大レベルに到達するまでのアップカウント値は100である。また、ランプ信号RAMP2のレベルが黒画素の画素信号VSLのレベルと同一レベルになってから最大レベルに到達するまでのアップカウント値は70である。この場合、信号処理回路22Bにより計算される白画素(白い領域)のAD変換後の画素データは、 $-70 + 100 = 30$ であり、黒画素(黒地)のAD変換後の画素データは、 $-70 + 70 = 0$ となる。したがって、従来駆動を行っているAD変換部13Aと同一の画素データが得られる。

## 【0099】

第2のAD変換処理においても、ランプ信号RAMP2のレベルがランプ信号RAMP1とは反転されたものとなっていることによって、コンパレータ31BのHi信号出力期間Tcは、AD変換部13Aのコンパレータ31AのHi信号出力期間Tbとは異なる時間となる。その結果、全黒画像のD相期間において、出力が一斉反転するコンパレータ31Bの個数は従来の半分とな

10

20

30

40

50

るので、コンパレータ31Bの出力が一斉反転する際のランプ信号RAMP2の歪み量は、図4に示した従来のランプ信号RAMPの歪み量よりも少なくなる。これにより、図7下側に示される黒地に白画像を撮像した場合のD相期間のランプ信号RAMP2の歪み量と、図7上側の全黒画像におけるD相期間のランプ信号RAMP2の歪み量の違いに相当するストリーキング量T2は、従来のストリーキング量T1よりも小さくなる( $T1 > T2$ )。したがって、固体撮像装置1によれば、ストリーキングの発生を低減させることができる。

## 【0100】

そして、第2のAD変換処理では、信号処理回路22Bが、D相期間のランプ信号RAMP2のレベル反転に応じて、Dレンジ相当のカウント数をP相期間のダウンカウント値に加算する必要がないので、Dレンジのばらつきの影響を受けない構成とすることができる。

10

## 【0101】

固体撮像装置1は、例えば、外部からの設定制御信号に基づいて、上述した第1のAD変換処理と第2のAD変換処理のいずれか一つを選択して、実行することができる。勿論、固体撮像装置1は、上述した第1のAD変換処理と第2のAD変換処理のいずれか一方のみを固定的に実行するようにしてもよい。

## 【0102】

なお、本実施の形態では、奇数画素列の画素信号VSLをAD変換処理するAD変換部13Aにランプ信号RAMP1を供給し、偶数画素列の画素信号VSLをAD変換処理するAD変換部13Bにランプ信号RAMP2を供給するようにしたが、AD変換部13Aにランプ信号RAMP2を供給し、AD変換部13Bにランプ信号RAMP1を供給するようにしてもよい。

20

## 【0103】

<2. 第2の実施の形態>

<固体撮像装置の全体構成例>

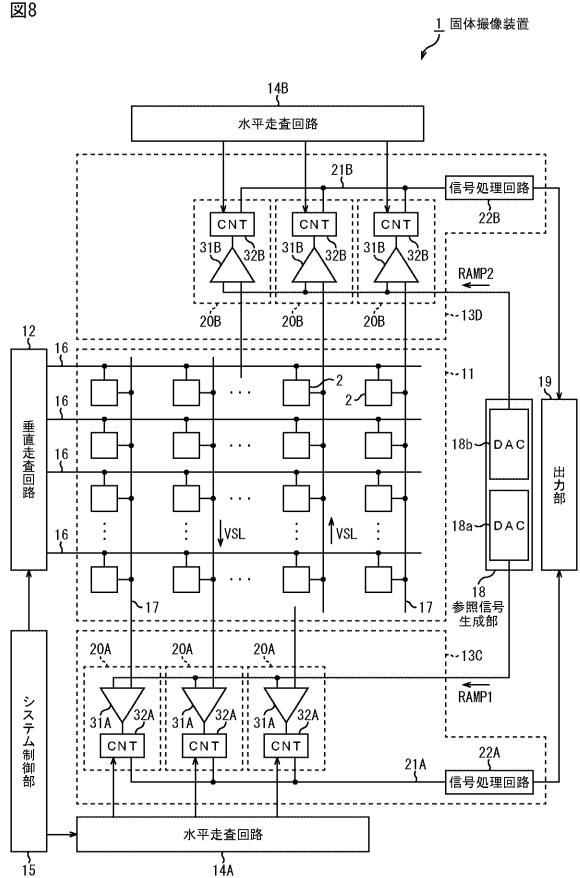

図8は、本技術が適用された固体撮像装置の第2の実施の形態の構成を示すブロック図である。

## 【0104】

図8において、上述した第1の実施の形態と対応する部分については同一の符号を付してあり、その説明は適宜省略する。

## 【0105】

図8に示される第2の実施の形態の固体撮像装置1では、図1に示した固体撮像装置1のAD変換部13Aおよび13Bに代えて、AD変換部13Cおよび13Dが設けられている点が異なる。

30

## 【0106】

第1の実施の形態では、AD変換処理する対象画素列が、奇数画素列と偶数画素列でAD変換部13AとAD変換部13Bに分けられていた。第2の実施の形態では、AD変換処理する対象画素列が、画素アレイ部11の左側半分と右側半分でAD変換部13CとAD変換部13Dに分けられている。

## 【0107】

具体的には、AD変換部13Cの複数のカラムAD変換部20Aは、画素アレイ部11の左側半分の画素列の垂直信号線17と1対1に接続されている。また、AD変換部13Dの複数のカラムAD変換部20Bは、画素アレイ部11の右側半分の画素列の垂直信号線17と1対1に接続されている。

40

## 【0108】

従って、画素アレイ部11の下側に配置されたAD変換部13Cは、画素アレイ部11の左側半分の画素列の画素2から出力される画素信号VSLをCDS処理およびAD変換処理する。一方、画素アレイ部11の上側に配置されたAD変換部13Dは、画素アレイ部11の右側半分の画素列の画素2から出力される画素信号VSLをCDS処理およびAD変換処理する。

## 【0109】

画素アレイ部11の下側に配置されたAD変換部13Cには、DAC18aから、従来と同様の、時間経過に応じてレベルが一定の傾きで低下するランプ信号RAMP1が供給される。一

50

方、画素アレイ部11の上側に配置されたAD変換部13Dには、DAC18bから、D相期間において時間経過に応じてレベルが一定の傾きで上昇するランプ信号RAMP2が供給される。これにより、図8の固体撮像装置1では、画素アレイ部11の下側に配置されたAD変換部13Cと、画素アレイ部11の上側に配置されたAD変換部13Dとで、同一レベルの画素信号VSLであっても、コンパレータ出力の反転タイミングが異なる。これにより、コンパレータ31A及び31Bの出力が一斉反転する際のランプ信号RAMP1及びRAMP2の歪み量は、図4に示した従来のランプ信号RAMPの歪み量よりも少なくなるので、第2の実施の形態においても、従来と比較して、ストリーキングの発生を低減させることができる。

#### 【0110】

なお、本実施の形態では、左側半分の画素列の画素信号VSLをAD変換処理するAD変換部13Cにランプ信号RAMP1を供給し、右側半分の画素列の画素信号VSLをAD変換処理するAD変換部13Dにランプ信号RAMP2を供給するようにしたが、AD変換部13Cにランプ信号RAMP2を供給し、AD変換部13Dにランプ信号RAMP1を供給するようにしてもよい。

#### 【0111】

以上のように、第1および第2の実施の形態の固体撮像装置1は、画素アレイ部11の複数の画素列が第1のグループと第2のグループの2つのグループに分割され、コンパレータ出力の反転タイミングが、第1のグループと第2のグループとで異なるように構成されている。これにより、従来と比較して、ストリーキングの発生を低減（半減）させることができる。また、コンパレーター一斉反転による電源電圧およびGND電圧の揺れが低減されることから、ノイズも低減させることができる。さらに、コンパレータ31の回路変更や複雑なノイズキャンセル回路を必要としないので、簡単な回路構成でストリーキングを低減させることができる。

#### 【0112】

##### <応用例>

上述した第1および第2の実施の形態では、いずれも、画素アレイ部11の複数の画素列を2つのグループに分割してAD変換処理を行うようにしたが、画素アレイ部11の複数の画素列を3つ以上のグループに分割して、それぞれのコンパレータ出力の反転タイミングが異なる構成としてもよい。

#### 【0113】

例えば、画素アレイ部11の複数の画素列を3つのグループに分割し、固体撮像装置1は、第1のグループでは、D相期間において、レベルが一定の傾きで低下するランプ信号RAMP1を用いるAD変換処理を行う。また、固体撮像装置1は、第2のグループでは、D相期間において、レベルが一定の傾きで上昇するランプ信号RAMP2を用いるAD変換処理を行う。そして、固体撮像装置1は、第3のグループでは、ランプ信号RAMP1を画素信号VSLとともに時間軸方向にディレイさせてから、第1のグループと同様のAD変換処理を行う。

#### 【0114】

その他、例えば、第3のグループに対しては、Dレンジを拡大し、ランプ信号RAMP1と画素信号VSLのレベルをレベル方向にオフセットさせることにより、コンパレータ出力の反転タイミングを第1および第2のグループと異なるようにさせてもよい。また、第3のグループに対しては、ランプ信号RAMP1及びRAMP2の傾きとカウントクロックを変更したものを使用することにより、コンパレータ出力の反転タイミングを他の第1および第2のグループと異なるようにしてもよい。

#### 【0115】

画素アレイ部11の複数の画素列を4つ以上のグループに分割した場合には、上述した複数の方法を適宜組み合わせて、それぞれのコンパレータ出力の反転タイミングが異なる構成とすることができる。

#### 【0116】

また、コンパレータ出力の反転タイミングが第1のグループと第2のグループとで異なるようにする構成としては、例えば、画素アレイ部11の第1のグループの画素列と第2のグループの画素列とで半導体基板のP型とN型を逆にすることで、画素信号VSLの動きを

10

20

30

40

50

電子とホール（正孔）で反対とすることもできる。

【0117】

<3. 第3の実施の形態>

<本技術を適用した電子機器の構成例>

本技術は、固体撮像装置への適用に限られるものではない。即ち、本技術は、デジタルスチルカメラやビデオカメラ等の撮像装置や、撮像機能を有する携帯端末装置や、画像読取部に固体撮像装置を用いる複写機など、画像取込部（光電変換部）に固体撮像装置を用いる電子機器全般に対して適用可能である。固体撮像装置は、ワンチップとして形成された形態であってもよいし、撮像部と信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

10

【0118】

図9は、本技術を適用した電子機器としての撮像装置の構成例を示すブロック図である。

【0119】

図9の撮像装置100は、レンズ群などからなる光学部101、図1または図8の固体撮像装置1の構成が採用される固体撮像装置（撮像デバイス）102、およびカメラ信号処理回路であるDSP(Digital Signal Processor)回路103を備える。また、撮像装置100は、フレームメモリ104、表示部105、記録部106、操作部107、および電源部108も備える。DSP回路103、フレームメモリ104、表示部105、記録部106、操作部107および電源部108は、バスライン109を介して相互に接続されている。

20

【0120】

光学部101は、被写体からの入射光（像光）を取り込んで固体撮像装置102の撮像面上に結像する。固体撮像装置102は、光学部101によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この固体撮像装置102として、図1または図8の固体撮像装置1、即ちストリーキングの発生を低減させることができる固体撮像装置を用いることができる。

20

【0121】

表示部105は、例えば、液晶パネルや有機EL(Electro Luminescence)パネル等のパネル型表示装置からなり、固体撮像装置102で撮像された動画または静止画を表示する。記録部106は、固体撮像装置102で撮像された動画または静止画を、ハードディスクや半導体メモリ等の記録媒体に記録する。

30

【0122】

操作部107は、ユーザによる操作の下に、撮像装置100が持つ様々な機能について操作指令を発する。電源部108は、DSP回路103、フレームメモリ104、表示部105、記録部106および操作部107の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

【0123】

上述したように、固体撮像装置102として、上述した実施の形態に係る固体撮像装置1を用いることで、ストリーキングの発生を低減させることができる。従って、ビデオカメラやデジタルスチルカメラ、さらには携帯電話機等のモバイル機器向けカメラモジュールなどの撮像装置100においても、撮像画像の高画質化を図ることができる。

40

【0124】

また、本技術は、可視光の入射光量の分布を検知して画像として撮像する固体撮像装置への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像装置や、広義の意味として、圧力や静電容量など、他の物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像装置（物理量分布検知装置）全般に対して適用可能である。

【0125】

なお、固体撮像装置はワンチップとして形成された形態であってもよいし、撮像部と、

50

信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

【0126】

本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

【0127】

なお、本技術は以下のような構成も取ることができる。

(1)

画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、

前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部と

を備え、

前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

AD変換器。

10

20

(2)

前記画素アレイ部の複数の画素列は2つのグループに分割されており、

前記第1のグループと前記第2のグループは、前記画素アレイ部の奇数画素列と偶数画素列とで分割されている

前記(1)に記載のAD変換器。

(3)

前記第2のAD変換部は、前記D相期間の前のリセットレベルを検出するP相期間のカウント値に前記D相期間の最大カウント値を加算した結果に、前記D相期間において前記第2のランプ信号のレベルが上昇を開始してから前記第2の画素信号のレベルと同一になるまでのカウント値を加算する

30

前記(1)または(2)に記載のAD変換器。

(4)

前記第2のAD変換部は、前記D相期間の前のリセットレベルを検出するP相期間のカウント値に、前記D相期間において前記第2のランプ信号のレベルが上昇を開始して前記第2の画素信号のレベルと同一になってから最大レベルとなるまでのカウント値を加算する

前記(1)または(2)に記載のAD変換器。

(5)

前記第1のランプ信号と前記第2のランプ信号を生成する参照信号生成部をさらに備える

前記(1)乃至(4)のいずれかに記載のAD変換器。

40

(6)

前記画素アレイ部の複数の画素列は2つのグループに分割されており、

前記第1のグループと前記第2のグループは、前記画素アレイ部の全ての画素列の右側半分と左側半分とで分割されている

前記(1)、(3)乃至(5)のいずれかに記載のAD変換器。

(7)

前記画素アレイ部の複数の画素列が3つのグループに分割されている

前記(3)乃至(5)のいずれかに記載のAD変換器。

(8)

画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうち

50

の第1のグループの画素列から出力される第1の画素信号をAD変換する第1のAD変換部と、前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号をAD変換する第2のAD変換部とを備えるAD変換器の

前記第1のAD変換部が、前記第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換し、

前記第2のAD変換部が、前記第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換し、

前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

信号処理方法。

( 9 )

複数の画素が行列状に2次元配置された画素アレイ部と、

前記画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、

前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部と

を備え、

前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

固体撮像装置。

( 10 )

複数の画素が行列状に2次元配置された画素アレイ部と、

前記画素アレイ部の複数の画素列が少なくとも2つのグループに分割されており、そのうちの第1のグループの画素列から出力される第1の画素信号と第1のランプ信号とを比較することにより、前記第1の画素信号をAD変換する第1のAD変換部と、

前記画素アレイ部の前記第1のグループと異なる第2のグループの画素列から出力される第2の画素信号と第2のランプ信号とを比較することにより、前記第2の画素信号をAD変換する第2のAD変換部と

を備え、

前記第1のランプ信号は、画素信号の信号レベルを検出するD相期間において、時間経過に応じて一定の傾きでレベルが低下する信号であり、

前記第2のランプ信号は、前記D相期間において、時間経過に応じて一定の傾きでレベルが上昇する信号である

固体撮像装置

を備える電子機器。

【符号の説明】

【 0 1 2 8 】

1 固体撮像装置, 2 画素, 11 画素アレイ部, 13A, 13B, 13C, 13D AD変換部, 18 参照信号生成部, 18a, 18b DAC, 20A, 20B 力ラムAD変換部, 22A, 22B 信号処理回路, 31A, 31B コンパレータ, 32A, 32B アップダウンカウンタ, 100 撮像装置, 102 固体撮像装置

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】