# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H01L 29/786** (2006.01) **H01L 27/32** (2006.01) **H01L 29/732** (2006.01)

(52) CPC특허분류 *H01L 29/78642* (2013.01) *H01L 27/3262* (2013.01)

(21) 출원번호 **10-2018-0143817**

(22) 출원일자 2018년11월20일

심사청구일자 없음

(11) 공개번호 10-2020-0059016

(43) 공개일자 2020년05월28일

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

조인탁

경기도 파주시 월롱면 엘지로 245

서정석

경기도 파주시 월롱면 엘지로 245

(뒷면에 계속)

(74) 대리인

특허법인(유한)유일하이스트

전체 청구항 수 : 총 19 항

### (54) 발명의 명칭 수직 구조 트랜지스터 및 전자장치

#### (57) 요 약

본 발명의 실시예들은 수직 구조 트랜지스터 및 전자장치에 관한 것으로서, 더욱 상세하게는, 기판 상에 배치된 제1 전극, 절연 패턴, 제2 전극과 및 액티브층을 포함하고, 액티브층은 제1 및 제2 전극과 미 중첩한 영역에서 채널 영역을 구비하며, 액티브층의 채널 영역은 절연 패턴의 측면에 대응되는 영역과, 액티브층이 절연 패턴의 상면의 일부와 중첩하되 제2 전극과 미 중첩하는 영역을 포함하고, 절연 패턴의 측면에 대응되는 영역에서의 게이트 절연막의 두께는 절연 패턴의 상면의 일부와 중첩하되 제2 전극과 미 중첩하는 영역에서의 게이트 절연막의 두께는 절연 패턴의 상면의 일부와 중첩하되 제2 전극과 미 중첩하는 영역에서의 게이트 절연막의 두께보다 얇을 수 있다. 이를 통해, 짧은 채널 구현 및 구동 마진이 증가한 수직 구조의 트랜지스터 및 전자장치를 제공할 수 있다.

#### 대 표 도 - 도7

(52) CPC특허분류

**H01L 29/732** (2013.01)

**H01L 29/78606** (2013.01)

**H01L 29/78618** (2013.01)

**H01L 29/78696** (2013.01)

(72) 발명자

### 박세희

경기도 파주시 월롱면 엘지로 245

### 박재윤

경기도 파주시 월롱면 엘지로 245

### 성상윤

경기도 파주시 월롱면 엘지로 245

#### 명세서

#### 청구범위

#### 청구항 1

패널; 및

상기 패널을 구동하기 위한 구동회로를 포함하고,

상기 패널에 배치되는 트랜지스터는,

기판 상에 배치된 제1 전극;

상기 기판 상에 배치되고, 상기 제1 전극의 일 단과 중첩된 절연 패턴;

상기 절연 패턴의 상면의 일부에 배치된 제2 전극;

상기 제1 전극, 상기 절연 패턴 및 상기 제2 전극 상에 배치된 액티브층;

상기 액티브층 상에 배치된 게이트 절연막; 및

상기 게이트 절연막 상에 배치된 게이트 전극을 포함하고,

상기 액티브층의 일 단은 상기 제1 전극과 중첩되고 상기 액티브층의 타 단은 상기 제2 전극과 중첩되며, 상기 액티브층이 상기 제1 및 제2 전극과 미 중첩한 영역에 채널 영역이 구비되고,

상기 채널 영역은 상기 채널 영역이 상기 절연 패턴의 일 측면에 대응되는 영역인 제1 부분과, 상기 제1 부분에서 연장되어 상기 액티브층이 상기 절연 패턴의 상면의 일부와 중첩하되 상기 제2 전극과 미 중첩하는 영역인 제2 부분을 포함하고,

상기 절연 패턴의 측면에 대응되는 영역에서의 상기 게이트 절연막의 두께는 상기 절연 패턴의 상면의 일부와 중첩하되 상기 제2 전극과 미 중첩하는 영역에서의 상기 게이트 절연막의 두께보다 얇은 전자장치.

#### 청구항 2

제1항에 있어서,

상기 절연 패턴의 폭은 기판으로부터 수직한 방향으로 멀어질수록 넓어지는 영역을 갖는 전자장치.

#### 청구항 3

제1항에 있어서,

상기 액티브층의 채널 영역의 길이는 상기 절연 패턴의 높이에 비례하는 전자장치.

### 청구항 4

제1항에 있어서,

상기 게이트 절연막은,

상기 액티브층의 상면에 배치되되, 상기 제1 전극의 일부 및 상기 제2 전극의 일부 또는 전부와 중첩된 제1 게이트 절연막; 및

상기 제1 게이트 절연막 상에 배치되고, 상기 액티브층의 채널 영역과 중첩된 상기 제2 게이트 절연막을 포함하는 전자장치.

### 청구항 5

제4항에 있어서,

상기 제1 게이트 절연막은 상기 절연 패턴의 측면에 배치된 액티브층의 일부 또는 전부를 노출하도록 배치된 전

자장치.

#### 청구항 6

제4항에 있어서,

상기 제1 게이트 절연막은 제1 영역 및 제2 영역을 포함하고,

상기 제1 영역은 상기 액티브층의 일 단 및 제1 전극의 일부와 중첩되고,

상기 제2 영역은 상기 액티브층의 타 단 및 제2 전극의 일부 또는 전부와 중첩되는 전자장치.

#### 청구항 7

제6항에 있어서,

상기 제2 영역은, 상기 채널 영역의 제2 부분 상에 배치된 전자장치.

### 청구항 8

제4항에 있어서,

상기 제2 게이트 절연막이 최대 두께의 갖는 영역의 두께는 상기 제1 게이트 절연막이 최대 두께를 갖는 영역의 두께보다 얇은 전자장치.

#### 청구항 9

제4항에 있어서,

상 제2 게이트 절연막은 상기 제1 게이트 절연막에 비해 작은 두께 편차를 갖는 전자장치.

#### 청구항 10

제4항에 있어서,

상기 제2 게이트 절연막은 상기 제1 게이트 절연막에 비해 높은 밀도를 갖는 전자장치.

### 청구항 11

제1항에 있어서,

상기 액티브층은 비정질 실리콘 반도체 또는 산화물 반도체로 구성되는 전자장치.

#### 청구항 12

제1항에 있어서,

상기 제1 전극, 상기 절연 패턴 및 상기 제2 전극 상에 배치되고, 상기 액티브층 하부에 배치된 중간층을 더 포함하는 전자장치.

### 청구항 13

제12항에 있어서,

상기 중간층은 10Å 내지 30Å 두께를 갖는 무기막인 전자장치.

#### 청구항 14

제12항에 있어서,

상기 중간층의 두께는 상기 제1 및 제2 게이트 절연막의 두께보다 얇은 전자장치.

#### 청구항 15

제1항에 있어서,

상기 트랜지스터가 액티브 영역 내 배치되는 경우,

상기 트랜지스터의 상기 게이트 전극을 덮으면서 패시베이션층이 배치되고,

상기 패시베이션층 상에 픽셀 전극이 위치하며,

상기 픽셀 전극은 상기 패시베이션층의 홀을 통해 상기 제1 전극 또는 상기 제2 전극과 전기적으로 연결되는 전 자장치.

#### 청구항 16

제15항에 있어서,

상기 게이트 전극에 데이터 전압이 인가되는 전자장치.

#### 청구항 17

제1항에 있어서.

상기 트랜지스터는 상기 패널의 액티브 영역 내 다수의 서브픽셀 각각의 영역에 배치되는 전자장치.

### 청구항 18

제1항에 있어서,

상기 트랜지스터는 상기 패널의 액티브 영역의 외곽 영역인 넌-액티브 영역에 배치된 게이트 구동회로에 포함되는 전자장치.

#### 청구항 19

기판 상에 배치된 제1 전극;

상기 기판 상에 배치되고, 상기 제1 전극의 일 단과 중첩된 절연 패턴;

상기 절연 패턴의 상면의 일부에 배치된 제2 전극;

상기 제1 전극, 상기 절연 패턴 및 상기 제2 전극 상에 배치된 액티브층;

상기 액티브층 상에 배치된 게이트 절연막; 및

상기 게이트 절연막 상에 배치된 게이트 전극을 포함하고,

상기 액티브층의 일 단은 상기 제1 전극과 중첩되고 타 단은 상기 제2 전극과 중첩되며, 상기 액티브층이 상기 제1 및 제2 전극과 미 중첩한 영역에 채널 영역이 구비되고,

상기 액티브층의 채널 영역은 상기 절연 패턴의 일 측면에 대응되는 영역인 제1 부분과, 상기 제1 부분에서 연장되어 상기 액티브층이 상기 절연 패턴의 상면의 일부와 중첩하되 상기 제2 전극과 미 중첩하는 영역인 제2 부분을 포함하고.

상기 절연 패턴의 측면에 대응되는 영역에서의 상기 게이트 절연막의 두께는 상기 절연 패턴의 상면의 일부와 중첩하되 상기 제2 전극과 미 중첩하는 영역에서의 상기 게이트 절연막의 두께보다 얇은 수직 구조 트랜지스터.

### 발명의 설명

#### 기술분야

[0001] 본 발명의 실시예들은 수직 구조 트랜지스터 및 전자장치에 관한 것이다.

#### 배경기술

[0002] 정보화 사회가 발전함에 따라, 표시장치, 조명장치 등의 다양한 전자장치에 대한 요구가 다양한 형태로 증가하고 있다. 이러한 전자장치는 데이터 라인들과 게이트 라인들이 배치된 패널과, 데이터 라인들을 구동하기 위한 데이터 드라이버와, 게이트 라인들을 구동하기 위한 게이트 드라이버를 포함할 수 있다.

- [0003] 이러한 전자장치의 핵심 구성인 패널은 구동을 위하여 수많은 트랜지스터들이 다양한 기능으로 배치될 수 있다.

- [0004] 이로 인해, 패널 제작 공정은 복잡해지고 어려워질 수밖에 없다. 이에 따라, 공정 편의성을 추구하다 보면, 트랜지스터의 소자 성능이 떨어지는 문제점이 발생할 수 있다.

- [0005] 또한, 높은 해상도 등의 전자장치의 우수한 특성을 구현하기 위해서는 트랜지스터의 집적도가 높아져야 한다. 그러나, 공정 및 설계 등의 문제로 트랜지스터의 크기를 무한정 줄일 수 없으므로, 트랜지스터의 특성을 떨어트 리지 않으면서 이들이 차지하는 면적을 조절해야 할 필요가 있다.

#### 발명의 내용

#### 해결하려는 과제

- [0006] 본 발명의 실시예들의 목적은, 짧은 채널(Short Channel) 구현 및 집적화가 가능한 수직 구조 트랜지스터 및 전 자장치를 제공하는 데 있다.

- [0007] 본 발명의 실시예들의 다른 목적은, 트랜지스터의 높은 S-계수를 통해 구동 마진이 증가한 수직 구조의 트랜지스터 및 전자장치를 제공하는 데 있다.

- [0008] 본 발명의 실시예들의 또 다른 목적은, 액티브층의 단선이 없는 구조를 갖는 수직 구조 트랜지스터 및 전자장치를 제공하는 데 있다.

- [0009] 본 발명의 실시예들의 또 다른 목적은, 소자 면적 감소로 인한 초고해상도 패널을 구현할 수 있는 수직 구조 트랜지스터 및 전자장치를 제공하는 데 있다.

- [0010] 본 발명의 실시에들의 또 다른 목적은, 트랜지스터의 구동 전류를 증가시키고, 넌-액티브 영역의 크기를 줄일수 있는 수직 구조 트랜지스터 및 전자장치를 제공하는 데 있다.

#### 과제의 해결 수단

- [0011] 본 발명의 실시예들은, 패널과, 패널을 구동하기 위한 구동회로를 포함하는 전자장치를 제공할 수 있다.

- [0012] 이러한 전자장치에서, 본 발명의 실시예들은, 패널 및 패널을 구동하기 위한 구동회로를 포함하고, 패널에 배치되는 트랜지스터는, 기판 상에 배치된 제1 전극, 기판 상에 배치되고, 제1 전극의 일 단과 중첩된 절연 패턴, 제1 전극, 절연 패턴 및 제2 전극 상에 배치된 액티브층, 액티브층 상에 배치된 게이트 절연막 및 게이트 절연막 상에 배치된 게이트 전극을 포함하고, 액티브층의 일 단은 제1 전극과 중첩되고, 액티브층의 타 단은 제2 전극과 중첩되며, 액티브층이 제1 및 제2 전극과 미 중첩한 영역에 채널 영역이 구비되고, 채널 영역은 채널 영역이 절연 패턴의 일 측면에 대응되는 영역인 제1 부분과, 제1 부분에서 연장되어 액티브층이 절연 패턴의 상면의일부와 중첩하되 제2 전극과 미 중첩하는 영역인 제2 부분을 포함하고, 절연 패턴의 측면에 대응되는 영역에서의 게이트 절연막의 두께는 절연 패턴의 상면의일부와 중첩하되 제2 전극과 미 중첩하는 영역에서의 게이트 절연막의 두께보다 얇을 수 있다.

- [0013] 절연 패턴의 폭은 기판으로부터 수직한 방향으로 멀어질수록 넓어지는 영역을 포함할 수 있다.

- [0014] 액티브층의 채널 영역의 길이는 절연 패턴의 높이에 비례할 수 있다.

- [0015] 게이트 절연막은 액티브층의 상면에 배치되되, 제1 전극의 일부 또는 전부 및 제2 전극의 일부 또는 전부와 중 첩된 제1 게이트 절연막 및 제1 게이트 절연막 상에 배치되고, 액티브층의 채널 영역과 중첩된 제2 게이트 절연 막을 포함할 수 있다.

- [0016] 제1 게이트 절연막은 절연 패턴의 측면에 배치된 액티브층의 일부 또는 전부를 노출하도록 배치될 수 있다.

- [0017] 제1 게이트 절연막은 제1 영역 및 제2 영역을 포함하고, 제1 영역은 액티브층의 일 단 및 제1 전극의 일부 또는 전부와 중첩되고, 제2 영역은 액티브층의 타 단 및 제2 전극의 일부 또는 전부와 중첩될 수 있다.

- [0018] 제2 영역은 절연 패턴의 상면의 일부와 중첩하되, 제2 전극과 미 중첩하는 액티브층의 채널 영역 상에 배치될 수 있다.

- [0019] 제2 게이트 절연막이 최대 두께의 갖는 영역의 두께는 제1 게이트 절연막이 최대 두께를 갖는 영역의 두께보다 얇을 수 있다.

- [0020] 제1 전극, 절연 패턴 및 제2 전극 상에 배치되고, 액티브층 하부에 배치된 중간층을 더 포함할 수 있다,

- [0021] 중간층은 10Å 내지 30Å의 두께를 갖는 무기막일 수 있다.

- [0022] 중간층의 두께는 제1 및 제2 게이트 절연막의 두께보다 얇을 수 있다.

- [0023] 트랜지스터가 액티브 영역 내 배치되는 경우, 트랜지스터의 게이트 전극을 덮으면서 패시베이션층이 배치되고, 패시베이션층 상에 픽셀 전극이 위치하며. 픽셀 전극은 패시베이션층의 홀을 통해 제1 전극 또는 제2 전극과 전 기적으로 연결될 수 있다. 그리고, 게이트 전극에 데이터 전압이 인가될 수 있다.

- [0024] 트랜지스터는 패널의 액티브 영역 내 다수의 서브픽셀 각각의 영역에 배치될 수 있다.

- [0025] 트랜지스터는 패널의 액티브 영역의 외곽 영역인 넌-액티브 영역에 배치된 게이트 구동회로에도 포함될 수 있다.

#### 발명의 효과

- [0026] 본 발명의 실시예들에 의하면, 짧은 채널 구현 및 집적화가 가능한 수직 구조 트랜지스터 및 전자장치를 제공할 수 있다.

- [0027] 본 발명의 실시예들에 의하면, 트랜지스터의 높은 S-계수를 통해 구동 마진이 증가한 수직 구조의 트랜지스터 및 전자장치를 제공할 수 있다.

- [0028] 본 발명의 실시예들에 의하면, 액티브층의 단선이 없는 구조를 갖는 수직 구조 트랜지스터 및 전자장치를 제공할 수 있다.

- [0029] 본 발명의 실시예들에 의하면, 소자 면적 감소로 인한 초고해상도 패널을 구현할 수 있는 수직 구조 트랜지스터 및 전자장치를 제공할 수 있다.

- [0030] 본 발명의 실시예들에 의하면, 트랜지스터의 구동 전류를 증가시키고, 넌-액티브 영역의 크기를 줄일 수 있는 수직 구조 트랜지스터 및 전자장치를 제공할 수 있다.

### 도면의 간단한 설명

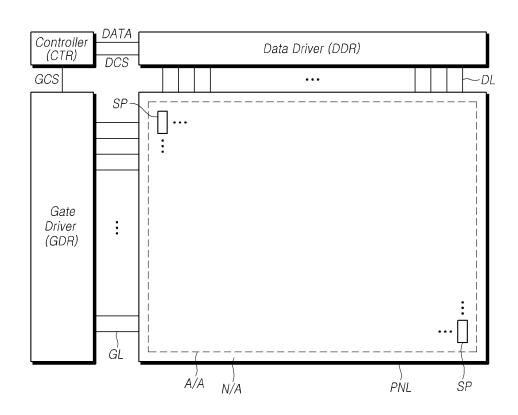

[0031] 도 1은 본 발명의 실시예들에 따른 전자장치의 개략적인 시스템 구성도이다.

도 2는 본 발명의 실시예들에 따른 전자장치의 시스템 구현 예시도이다.

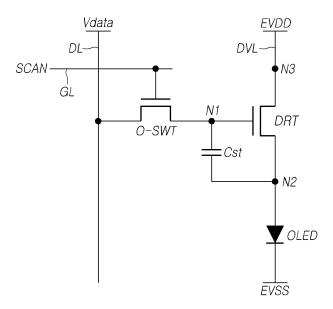

도 3은 본 발명의 실시예들에 따른 패널이 OLED (Organic Light Emitting Diode) 패널인 경우, 서브픽셀의 구조를 나타낸 도면이다.

도 4는 하나의 서브픽셀이 구동 트랜지스터의 제2 노드와 기준 전압 라인 사이에 전기적으로 연결된 제2 트랜지스터를 더 포함하는 3T(Transistor)1C(Capacitor) 구조를 예시적으로 나타낸 도면이다.

도 5는 본 발명의 실시예들에 따른 패널이 LCD (Liquid Crystal Display) 패널인 경우, 서브픽셀의 구조를 나타 낸 도면이다.

도 6은 본 발명의 실시예들에 따른 패널(PNL)에 배치된 게이트 구동회로(GDC)를 개략적으로 나타낸 도면이다.

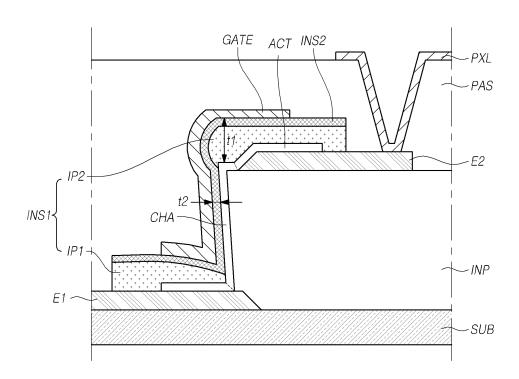

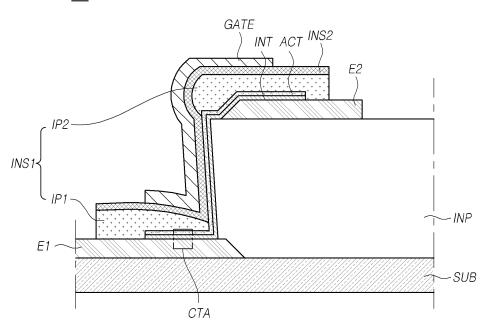

도 7은 본 발명의 실시예에 따른 수직 구조의 트랜지스터를 나타낸 도면이다.

도 8은 본 발명의 실시예에 따른 절연 패턴의 형상을 도시한 도면이다.

도 9는 본 발명의 다른 실시예에 따른 수직 구조의 트랜지스터를 나타낸 도면이다.

도 10은 제1 전극 및 절연 패턴의 배치 구조에 따른 채널 영역의 길이의 관련성을 도시한 도면이다.

도 11은 본 발명의 또 다른 실시예에 따른 수직 구조의 트랜지스터를 나타낸 도면이다.

도 12를 참조하여 도 11의 컨택 영역을 설명하면 다음과 같다.

도 13은 본 발명의 실시예들에 따른 수직 구조 트랜지스터가 서브픽셀 내 배치된 경우, 픽셀 전극과 연결된 구조의 트랜지스터를 도시한 도면이다.

도 14 내지 도 17은 서브픽셀 내에 배치된 다수의 트랜지스터들의 구조를 도시한 도면이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0032] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다.

- [0033] 또한, 본 발명의 실시예들을 설명하기 위한 도면에 개시된 형상, 크기, 비율, 각도, 개수 등은 예시적인 것이므로 본 발명이 도시된 사항에 한정되는 것은 아니다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다. 또한, 본 발명을 설명함에 있어서, 관련된 공지 기술에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명은 생략한다. 본 명세서 상에서 언급된 '포함한다', '갖는다', '이루어진다' 등이 사용되는 경우 '~만'이 사용되지 않는 이상 다른 부분이 추가될 수 있다. 구성 요소를 단수로 표현한 경우에 특별히 명시적인 기재 사항이 없는 한 복수를 포함하는 경우를 포함할 수 있다.

- [0034] 또한, 본 발명의 실시예들에서의 구성 요소들을 해석함에 있어서, 별도의 명시적 기재가 없더라도 오차 범위를 포함하는 것으로 해석되어야 할 것이다.

- [0035] 또한, 본 발명의 구성 요소를 설명하는 데 있어서, 제 1, 제 2, A, B, (a), (b) 등의 용어를 사용할 수 있다. 이러한 용어는 그 구성 요소를 다른 구성 요소와 구별하기 위한 것일 뿐, 그 용어에 의해 해당 구성 요소의 본질, 차례, 순서 또는 개수 등이 한정되지 않는다. 어떤 구성 요소가 다른 구성 요소에 "연결", "결합" 또는 "접속"된다고 기재된 경우, 그 구성 요소는 그 다른 구성 요소에 직접적으로 연결되거나 또는 접속될 수 있지만, 각 구성 요소 사이에 다른 구성 요소가 "개재"되거나, 각 구성 요소가 다른 구성 요소를 통해 "연결", "결합" 또는 "접속"될 수도 있다고 이해되어야 할 것이다. 위치 관계에 대한 설명일 경우, 예를 들어, '~상에', '~상부에', '~하부에', '~옆에' 등으로 두 부분의 위치 관계가 설명되는 경우, '바로' 또는 '직접'이 사용되지 않는 이상 두 부분 사이에 하나 이상의 다른 부분이 위치할 수도 있다.

- [0036] 또한, 본 발명의 실시예들에서의 구성 요소들은 이들 용어에 의해 제한되지 않는다. 이들 용어들은 단지 하나의 구성 요소를 다른 구성 요소와 구별하기 위하여 사용하는 것일 뿐이다. 따라서, 이하에서 언급되는 제1 구성 요소는 본 발명의 기술적 사상 내에서 제2 구성 요소일 수도 있다.

- [0037] 또한, 본 발명의 실시예들에서의 특징들(구성들)이 부분적으로 또는 전체적으로 서로 결합 또는 조합 또는 분리 가능하고, 기술적으로 다양한 연동 및 구동이 가능하며, 각 실시예는 서로에 대하여 독립적으로 실시 가능할 수도 있고 연관 관계로 함께 실시 가능할 수도 있다.

- [0038] 이하에서는, 본 발명의 실시예들을 첨부된 도면을 참조하여 상세히 설명한다. 도 1은 본 발명의 실시예들에 따른 전자장치의 개략적인 시스템 구성도이다.

- [0039] 본 발명의 실시예들에 따른 전자장치는 표시장치, 조명장치, 발광장치 등을 포함할 수 있다. 아래에서는, 설명의 편의를 위하여, 표시장치를 중심으로 설명한다. 하지만, 표시장치뿐만 아니라, 트랜지스터를 포함하기만 하면, 조명장치, 발광장치 등의 다른 다양한 전자장치에도 동일하게 적용될 수 있을 것이다.

- [0040] 본 발명의 실시예들에 따른 전자장치는, 영상을 표시하거나 빛을 출력하는 패널(PNL)과, 이러한 패널(PNL)을 구동하기 위한 구동회로를 포함할 수 있다.

- [0041] 패널(PNL)은, 다수의 데이터 라인(DL) 및 다수의 게이트 라인(GL)이 배치되고 다수의 데이터 라인(DL) 및 다수의 게이트 라인(GL)에 의해 정의되는 다수의 서브픽셀(SP)이 매트릭스 타입으로 배열될 수 있다.

- [0042] 패널(PNL)에서 다수의 데이터 라인(DL) 및 다수의 게이트 라인(GL)은 서로 교차하여 배치될 수 있다. 예를 들어, 다수의 게이트 라인(GL)은 행(Row) 또는 열(Column)으로 배열될 수 있고, 다수의 데이터 라인(DL)은 열(Column) 또는 행(Row)으로 배열될 수 있다. 아래에서는, 설명의 편의를 위하여, 다수의 게이트 라인(GL)은 행(Row)으로 배치되고, 다수의 데이터 라인(DL)은 열(Column)로 배치되는 것으로 가정한다.

- [0043] 패널(PNL)에는, 서브픽셀 구조 등에 따라, 다수의 데이터 라인(DL) 및 다수의 게이트 라인(GL) 이외에, 다른 종류의 신호배선들이 배치될 수 있다. 구동전압 배선, 기준전압 배선, 또는 공통전압 배선 등이 더 배치될 수 있다.

- [0044] 패널(PNL)은 LCD (Liquid Crystal Display) 패널, OLED (Organic Light Emitting Diode) 패널 등 다양한 타입

의 패널일 수 있다.

- [0045] 패널(PNL)에 배치되는 신호배선들의 종류는, 서브픽셀 구조, 패널 타입(예: LCD 패널, OLED 패널 등) 등에 따라 달라질 수 있다. 그리고, 본 명세서에서는 신호배선은 신호가 인가되는 전극을 포함하는 개념일 수도 있다.

- [0046] 패널(PNL)은 화상(영상)이 표시되는 액티브 영역(A/A)과, 그 외곽 영역이고 화상이 표시되지 않는 넌-액티브 영역(N/A)을 포함할 수 있다. 여기서, 넌-액티브 영역(N/A)은 베젤 영역이라고도 한다.

- [0047] 액티브 영역(A/A)에는 화상 표시를 위한 다수의 서브픽셀(SP)이 배치된다.

- [0048] 년-액티브 영역(N/A)에는 데이터 드라이버(DDR)가 전기적으로 연결되기 위한 패드부가 배치되고, 이러한 패드부와 다수의 데이터 라인(DL) 간의 연결을 위한 다수의 데이터 링크 라인이 배치될 수도 있다. 여기서, 다수의 데이터 링크 라인은 다수의 데이터 라인(DL)이 넌-액티브 영역(N/A)으로 연장된 부분들이거나, 다수의 데이터 라인(DL)과 전기적으로 연결된 별도의 패턴들일 수 있다.

- [0049] 또한, 년-액티브 영역(N/A)에는 데이터 드라이버(DDR)가 전기적으로 연결되는 패드 부를 통해 게이트 드라이버 (GDR)로 게이트 구동에 필요한 전압(신호)을 전달해주기 위한 게이트 구동 관련 배선들이 배치될 수 있다. 예를 들어, 게이트 구동 관련 배선들은, 클릭 신호를 전달해주기 위한 클릭 배선들, 게이트 전압(VGH, VGL)을 전달해주는 게이트 전압 배선들, 스캔신호 생성에 필요한 각종 제어신호를 전달해주는 게이트 구동 제어 신호배선들 등을 포함할 수 있다. 이러한 게이트 구동 관련 배선들은, 액티브 영역(A/A)에 배치되는 게이트 라인들(GL)과 다르게, 년-액티브 영역(N/A)에 배치된다.

- [0050] 구동회로는, 다수의 데이터 라인(DL)을 구동하는 데이터 드라이버(DDR)와, 다수의 게이트 라인(GL)을 구동하는 게이트 드라이버(GDR)와, 데이터 드라이버(DDR) 및 게이트 드라이버(GDR)를 제어하는 컨트롤러(CTR) 등을 포함할 수 있다.

- [0051] 데이터 드라이버(DDR)는 다수의 데이터 라인(DL)으로 데이터 전압을 출력함으로써 다수의 데이터 라인(DL)을 구동할 수 있다.

- [0052] 게이트 드라이버(GDR)는 다수의 게이트 라인(GL)으로 스캔신호를 출력함으로써 다수의 게이트 라인(GL)을 구동할 수 있다.

- [0053] 컨트롤러(CTR)는, 데이터 드라이버(DDR) 및 게이트 드라이버(GDR)의 구동 동작에 필요한 각종 제어신호(DCS, GCS)를 공급하여 데이터 드라이버(DDR) 및 게이트 드라이버(GDR)의 구동 동작을 제어할 수 있다. 또한, 컨트롤러(CTR)는 데이터 드라이버(DDR)로 영상데이터(DATA)를 공급할 수 있다.

- [0054] 컨트롤러(CTR)는, 각 프레임에서 구현하는 타이밍에 따라 스캔을 시작하고, 외부에서 입력되는 입력 영상데이터 를 데이터 드라이버(DDR)에서 사용하는 데이터 신호 형식에 맞게 전환하여 전환된 영상데이터(DATA)를 출력하고, 스캔에 맞춰 적당한 시간에 데이터 구동을 통제한다.

- [0055] 컨트롤러(CTR)는, 데이터 드라이버(DDR) 및 게이트 드라이버(GDR)를 제어하기 위하여, 수직 동기 신호(Vsync), 수평 동기 신호(Hsync), 입력 데이터 인에이블(DE: Data Enable) 신호, 클럭 신호(CLK) 등의 타이밍 신호를 외부 (예: 호스트 시스템)로부터 입력 받아, 각종 제어 신호들을 생성하여 데이터 드라이버(DDR) 및 게이트 드라이버(GDR)로 출력한다.

- [0056] 예를 들어, 컨트롤러(CTR)는, 게이트 드라이버(GDR)를 제어하기 위하여, 게이트 스타트 펄스(GSP: Gate Start Pulse), 게이트 쉬프트 클럭(GSC: Gate Shift Clock), 게이트 출력 인에이블 신호(GOE: Gate Output Enable) 등을 포함하는 각종 게이트 제어 신호(GCS: Gate Control Signal)를 출력한다.

- [0057] 또한, 컨트롤러(CTR)는, 데이터 드라이버(DDR)를 제어하기 위하여, 소스 스타트 펄스(SSP: Source Start Pulse), 소스 샘플링 클럭(SSC: Source Sampling Clock), 소스 출력 인에이블 신호(SOE: Source Output Enable) 등을 포함하는 각종 데이터 제어 신호(DCS: Data Control Signal)를 출력한다.

- [0058] 컨트롤러(CTR)는, 통상의 디스플레이 기술에서 이용되는 타이밍 컨트롤러(Timing Controller)이거나, 타이밍 컨트롤러(Timing Controller)를 포함하여 다른 제어 기능도 더 수행할 수 있는 제어장치일 수 있다.

- [0059] 컨트롤러(CTR)는, 데이터 드라이버(DDR)와 별도의 부품으로 구현될 수도 있고, 데이터 드라이버(DDR)와 함께 통합되어 집적회로로 구현될 수 있다.

- [0060] 데이터 드라이버(DDR)는, 컨트롤러(CTR)로부터 영상데이터(DATA)를 입력 받아 다수의 데이터 라인(DL)로 데이터

전압을 공급함으로써, 다수의 데이터 라인(DL)을 구동한다. 여기서, 데이터 드라이버(DDR)는 소스 드라이버라고 도 한다.

- [0061] 데이터 드라이버(DDR)는 다양한 인터페이스를 통해 컨트롤러(CTR)와 각종 신호를 주고받을 수 있다.

- [0062] 게이트 드라이버(GDR)는, 다수의 게이트 라인(GL)로 스캔신호를 순차적으로 공급함으로써, 다수의 게이트 라인 (GL)을 순차적으로 구동한다. 여기서, 게이트 드라이버(GDR)는 스캔 드라이버라고도 한다.

- [0063] 게이트 드라이버(GDR)는, 컨트롤러(CTR)의 제어에 따라, 온(On) 전압 또는 오프(Off) 전압의 스캔신호를 다수의 게이트 라인(GL)로 순차적으로 공급한다.

- [0064] 데이터 드라이버(DDR)는, 게이트 드라이버(GDR)에 의해 특정 게이트 라인이 열리면, 컨트롤러(CTR)로부터 수신 한 영상데이터(DATA)를 아날로그 형태의 데이터 전압으로 변환하여 다수의 데이터 라인(DL)로 공급한다.

- [0065] 데이터 드라이버(DDR)는, 패널(PNL)의 일 측(예: 상측 또는 하측)에만 위치할 수도 있고, 경우에 따라서는, 구동 방식, 패널 설계 방식 등에 따라 패널(PNL)의 양측(예: 상 측과 하 측)에 모두 위치할 수도 있다.

- [0066] 게이트 드라이버(GDR)는, 패널(PNL)의 일 측(예: 좌측 또는 우측)에만 위치할 수도 있고, 경우에 따라서는, 구동 방식, 패널 설계 방식 등에 따라 패널(PNL)의 양측(예: 좌 측과 우 측)에 모두 위치할 수도 있다.

- [0067] 데이터 드라이버(DDR)는 하나 이상의 소스 드라이버 집적회로(SDIC: Source Driver Integrated Circuit)를 포 함하여 구현될 수 있다.

- [0068] 각 소스 드라이버 집적회로(SDIC)는 시프트 레지스터(Shift Register), 래치 회로(Latch Circuit), 디지털 아 날로그 컨버터(DAC: Digital to Analog Converter), 출력 버퍼(Output Buffer) 등을 포함할 수 있다. 데이터 드라이버(DDR)는, 경우에 따라서, 하나 이상의 아날로그 디지털 컨버터(ADC: Analog to Digital Converter)를 더 포함할 수 있다.

- [0069] 각 소스 드라이버 집적회로(SDIC)는, TAB (Tape Automated Bonding) 타입 또는 COG (Chip On Glass) 타입으로 패널(PNL)의 본딩 패드(Bonding Pad)에 연결되거나 패널(PNL) 상에 직접 배치될 수도 있다. 경우에 따라서, 각소스 드라이버 집적회로(SDIC)는 패널(PNL)에 집적화되어 배치될 수도 있다. 또한, 각소스 드라이버 집적회로 (SDIC)는 COF (Chip On Film) 타입으로 구현될 수 있다. 이 경우, 각소스 드라이버 집적회로(SDIC)는 회로필름 상에 실장 되어, 회로필름을 통해 패널(PNL)에서의 데이터 라인들(DL)과 전기적으로 연결될 수 있다.

- [0070] 게이트 드라이버(GDR)는 다수의 게이트 구동회로(GDC)를 포함할 수 있다. 여기서, 다수의 게이트 구동회로(GD C)는 다수의 게이트 라인(GL)과 각각 대응될 수 있다.

- [0071] 각 게이트 구동회로(GDC)는 시프트 레지스터(Shift Register), 레벨 시프터(Level Shifter) 등을 포함할 수 있다.

- [0072] 각 게이트 구동회로(GDC)는 TAB (Tape Automated Bonding) 타입 또는 COG (Chip On Glass) 타입으로 패널(PN L)의 본딩 패드(Bonding Pad)에 연결될 수 있다. 또한, 각 게이트 구동회로(GDC)는 COF (Chip On Film) 방식으로 구현될 수 있다. 이 경우, 각 게이트 구동회로(GDC)는 회로필름 상에 실장 되어, 회로필름을 통해 패널(PN L)에서의 게이트 라인들(GL)과 전기적으로 연결될 수 있다. 또한, 각 게이트 구동회로(GDC)는 GIP (Gate In Panel) 타입으로 구현되어 패널(PNL)에 내장될 수 있다. 즉, 각 게이트 구동회로(GDC)는 패널(PNL)에 직접 형성될 수 있다.

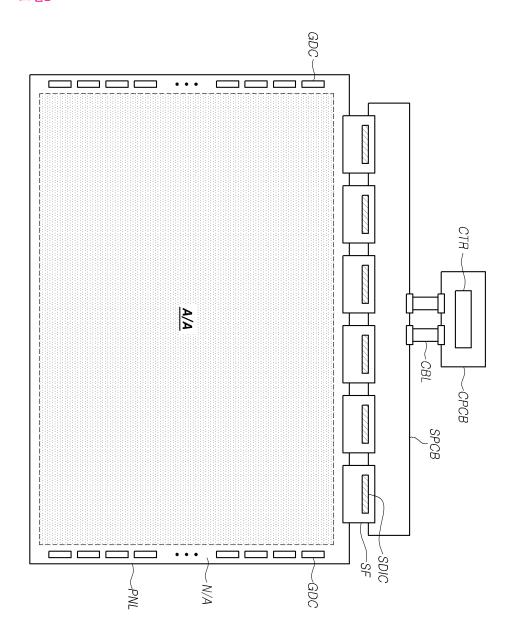

- [0073] 도 2는 본 발명의 실시예들에 따른 전자장치의 시스템 구현 예시도이다.

- [0074] 도 2를 참조하면, 본 발명의 실시예들에 따른 전자장치에서, 데이터 드라이버(DDR)는 다양한 타입들(TAB, COG, COF 등) 중 COF (Chip On Film) 타입으로 구현되고, 게이트 드라이버(GDR)는 다양한 타입들(TAB, COG, COF, GIP 등) 중 GIP (Gate In Panel) 타입으로 구현될 수 있다.

- [0075] 데이터 드라이버(DDR)는 하나 이상의 소스 드라이버 집적회로(SDIC)로 구현될 수 있다. 도 2는 데이터 드라이버 (DDR)가 다수의 소스 드라이버 집적회로(SDIC)로 구현된 경우를 예시한 것이다.

- [0076] 데이터 드라이버(DDR)가 COF 타입으로 구현된 경우, 데이터 드라이버(DDR)를 구현한 각 소스 드라이버 집적회로 (SDIC)는, 소스 측 회로필름(SF) 상에 실장 될 수 있다.

- [0077] 소스 측 회로필름(SF)의 일 측은 패널(PNL)의 넌-액티브 영역(N/A)에 존재하는 패드 부 (패드들의 집합체)와 전

기적으로 연결될 수 있다.

- [0078] 소스 측 회로필름(SF) 상에는, 소스 드라이버 집적회로(SDIC)와 패널(PNL)을 전기적으로 연결해주기 위한 배선 들이 배치될 수 있다.

- [0079] 전자장치는, 다수의 소스 드라이버 집적회로(SDIC)와 다른 장치들 간의 회로적인 연결을 위해, 하나 이상의 소스 인쇄회로기판(SPCB)과, 제어 부품들과 각종 전기 장치들을 실장 하기 위한 컨트롤 인쇄회로기판(CPCB)을 포함할 수 있다.

- [0080] 하나 이상의 소스 인쇄회로기판(SPCB)에는 소스 드라이버 집적회로(SDIC)가 실장 된 소스 측 회로필름(SF)의 타 측이 연결될 수 있다.

- [0081] 즉, 소스 드라이버 집적회로(SDIC)가 실장 된 소스 측 회로필름(SF)은, 일 측이 패널(PNL)의 넌-액티브 영역 (N/A)과 전기적으로 연결되고, 타 측이 소스 인쇄회로기판(SPCB)과 전기적으로 연결될 수 있다.

- [0082] 컨트롤 인쇄회로기판(CPCB)에는, 데이터 드라이버(DDR) 및 게이트 드라이버(GDR) 등의 동작을 제어하는 컨트롤 러(CTR)가 배치될 수 있다.

- [0083] 또한, 컨트롤 인쇄회로기판(CPCB)에는, 패널(PNL), 데이터 드라이버(DDR) 및 게이트 드라이버(GDR) 등으로 각종 전압 또는 전류를 공급해주거나 공급할 각종 전압 또는 전류를 제어하는 파워 관리 집적회로(PMIC: Power Management IC) 등이 더 배치될 수도 있다.

- [0084] 소스 인쇄회로기판(SPCB)과 컨트롤 인쇄회로기판(CPCB)은 적어도 하나의 연결 부재(CBL)를 통해 회로적으로 연결될 수 있다. 여기서, 연결 부재(CBL)는, 일 예로, 가요성 인쇄 회로(FPC: Flexible Printed Circuit), 가요성 플랫 케이블(FFC: Flexible Flat Cable) 등일 수 있다.

- [0085] 하나 이상의 소스 인쇄회로기판(SPCB)과 컨트롤 인쇄회로기판(CPCB)은 하나의 인쇄회로기판으로 통합되어 구현 될 수도 있다.

- [0086] 게이트 드라이버(GDR)가 GIP (Gate In Panel) 타입으로 구현된 경우, 게이트 드라이버(GDR)에 포함된 다수의 게이트 구동회로(GDC)는 패널(PNL)의 넌-액티브 영역(N/A) 상에 직접 형성될 수 있다.

- [0087] 다수의 게이트 구동회로(GDC) 각각은 패널(PNL)에서의 액티브 영역(A/A)에 배치된 해당 게이트 라인(GL)으로 해당 스캔신호(SCAN)를 출력할 수 있다.

- [0088] 패널(PNL) 상에 배치된 다수의 게이트 구동회로(GDC)는, 년-액티브 영역(N/A)에 배치된 게이트 구동 관련 배선 들을 통해, 스캔신호 생성에 필요한 각종 신호(클럭신호, 하이 레벨 게이트 전압(VGH), 로우 레벨 게이트 전압(VGL), 스타트 신호(VST), 리셋 신호(RST) 등)를 공급받을 수 있다.

- [0089] 넌-액티브 영역(N/A)에 배치된 게이트 구동 관련 배선들은, 다수의 게이트 구동회로(GDC)에 가장 인접하게 배치된 소스 측 회로필름(SF)과 전기적으로 연결될 수 있다.

- [0090] 도 3은 본 발명의 실시예들에 따른 패널(PNL)이 OLED (Organic Light Emitting Diode) 패널인 경우, 서브픽셀(SP)의 구조를 나타낸 도면이다.

- [0091] 도 3을 참조하면, OLED 패널인 패널(PNL)에서의 각 서브픽셀(SP)은, 유기발광다이오드(OLED)와, 유기발광다이오드(OLED)를 구동하는 구동 트랜지스터(DRT)와, 구동 트랜지스터(DRT)의 제1 노드(N1)와 해당 데이터 라인(DL) 사이에 전기적으로 연결된 스위칭 트랜지스터(O-SWT)와, 구동 트랜지스터(DRT)의 제1 노드(N1)와 제2 노드(N2) 사이에 전기적으로 연결된 스토리지 캐패시터(Cst) 등을 포함하여 구현될 수 있다.

- [0092] 유기발광다이오드(OLED)는 애노드 전극, 유기발광층 및 캐소드 전극 등으로 이루어질 수 있다.

- [0093] 도 3의 회로 예시에 따르면, 유기발광다이오드(OLED)의 애노드 전극(픽셀전극이라고도 함)은 구동 트랜지스터 (DRT)의 제2 노드(N2)와 전기적으로 연결될 수 있다. 유기발광다이오드(OLED)의 캐소드 전극(공통전극이라고도함)에는 기저전압(EVSS)이 인가될 수 있다.

- [0094] 여기서, 기저전압(EVSS)은, 일 예로, 그라운드 전압이거나 그라운드 전압보다 높거나 낮은 전압일 수 있다. 또한, 기저전압(EVSS)은 구동상태에 따라 가변될 수 있다. 예를 들어, 영상 구동 시 기저전압(EVSS)과 센싱 구동 시 기저전압(EVSS)은 서로 다르게 설정될 수 있다.

- [0095] 구동 트랜지스터(DRT)는 유기발광다이오드(OLED)로 구동전류를 공급해줌으로써 유기발광다이오드(OLED)를 구동

해준다.

- [0096] 구동 트랜지스터(DRT)는 제1 노드(N1), 제2 노드(N2) 및 제3 노드(N3) 등을 포함할 수 있다.

- [0097] 구동 트랜지스터(DRT)의 제1 노드(N1)는 게이트 노드일 수 있으며, 스위칭 트랜지스터(O-SWT)의 소스 노드 또는 드레인 노드와 전기적으로 연결될 수 있다. 구동 트랜지스터(DRT)의 제2 노드(N2)는 소스 노드 또는 드레인 노드일 수 있으며, 유기발광다이오드(OLED)의 애노드 전극(또는 캐소드 전극)과 전기적으로 연결될 수 있다. 구동 트랜지스터(DRT)의 제3 노드(N3)는 드레인 노드 또는 소스 노드일 수 있으며, 구동전압(EVDD)이 인가될 수 있고, 구동전압(EVDD)을 공급하는 구동전압 라인(DVL: Driving Voltage Line)과 전기적으로 연결될 수 있다.

- [0098] 스토리지 캐패시터(Cst)는 구동 트랜지스터(DRT)의 제1 노드(N1)와 제2 노드(N2) 사이에 전기적으로 연결되어, 영상 신호 전압에 해당하는 데이터 전압(Vdata) 또는 이에 대응되는 전압을 한 프레임 시간 (또는 정해진 시간) 동안 유지해줄 수 있다.

- [0099] 스위칭 트랜지스터(O-SWT)의 드레인 노드 또는 소스 노드는 해당 데이터 라인(DL)에 전기적으로 연결되고, 스위칭 트랜지스터(O-SWT)의 소스 노드 또는 드레인 노드는 구동 트랜지스터(DRT)의 제1 노드(N1)에 전기적으로 연결되고, 스위칭 트랜지스터(O-SWT)의 게이트 노드는 해당 게이트 라인과 전기적으로 연결되어 스캔신호(SCAN)를 인가 받을 수 있다.

- [0100] 스위칭 트랜지스터(O-SWT)는 해당 게이트 라인을 통해 스캔신호(SCAN)를 게이트 노드로 인가 받아 온-오프가 제어될 수 있다.

- [0101] 이러한 스위칭 트랜지스터(O-SWT)는 스캔신호(SCAN)에 의해 턴-온 되어 해당 데이터 라인(DL)으로부터 공급된 데이터 전압(Vdata)을 구동 트랜지스터(DRT)의 제1 노드(N1)로 전달해줄 수 있다.

- [0102] 한편, 스토리지 캐패시터(Cst)는, 구동 트랜지스터(DRT)의 제1 노드(N1)와 제2 노드(N2) 사이에 존재하는 내부 캐패시터(Internal Capacitor)인 기생 캐패시터(예: Cgs, Cgd)가 아니라, 구동 트랜지스터(DRT)의 외부에 의도 적으로 설계한 외부 캐패시터(External Capacitor)일 수 있다.

- [0103] 구동 트랜지스터(DRT) 및 스위칭 트랜지스터(O-SWT) 각각은 n 타입 트랜지스터이거나 p 타입 트랜지스터일 수 있다.

- [0104] 도 3에 예시된 각 서브픽셀 구조는 2T(Transistor) 1C (Capacitor) 구조로서, 설명을 위한 예시일 뿐, 1개 이상의 트랜지스터를 더 포함하거나, 경우에 따라서는, 1개 이상의 캐패시터를 더 포함할 수도 있다. 또는, 다수의 서브픽셀들 각각이 동일한 구조로 되어 있을 수도 있고, 다수의 서브픽셀들 중 일부는 다른 구조로 되어 있을 수도 있다.

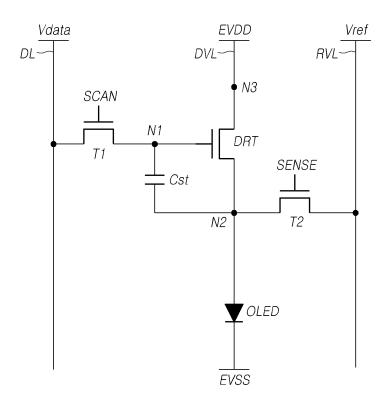

- [0105] 도 4는 하나의 서브픽셀(SP)이 구동 트랜지스터(DRT)의 제2 노드(N2)와 기준 전압 라인(RVL) 사이에 전기적으로 연결된 제2 트랜지스터(T2)를 더 포함하는 3T(Transistor)1C(Capacitor) 구조를 예시적으로 나타낸 도면이다.

- [0106] 도 4를 참조하면, 제2 트랜지스터(T2)는 구동 트랜지스터(DRT)의 제2 노드(N2)와 기준 전압 라인(RVL) 사이에 전기적으로 연결되어, 게이트 노드로 제2 스캔 신호(SCAN2)를 인가 받아 온-오프가 제어될 수 있다.

- [0107] 제2 트랜지스터(T2)의 드레인 노드 또는 소스 노드는 기준 전압 라인(RVL)에 전기적으로 연결되고, 제2 트랜지스터(T2)의 소스 노드 또는 드레인 노드는 구동 트랜지스터(DRT)의 제2 노드(N2)에 전기적으로 연결될 수 있다.

- [0108] 제2 트랜지스터(T2)는, 일 예로, 디스플레이 구동 시 구간에서 턴-온 될 수 있고, 구동 트랜지스터(DRT)의 특성 치 또는 유기발광다이오드(OLED)의 특성치를 센싱하기 위한 센싱 구동 시 구간에서 턴-온 될 수 있다.

- [0109] 제2 트랜지스터(T2)는 해당 구동 타이밍(예: 디스플레이 구동 타이밍 또는 센싱 구동 시 구간 내 초기화 타이밍)에 맞추어, 제2 스캔 신호(SCAN2)에 의해 턴-온 되어, 기준 전압 라인(RVL)에 공급된 기준 전압(Vref)을 구동 트랜지스터(DRT)의 제2 노드(N2)에 전달해줄 수 있다.

- [0110] 또한, 제2 트랜지스터(T2)는 해당 구동 타이밍(예: 센싱 구동 시 구간 내 샘플링 타이밍)에 맞추어, 제2 스캔 신호(SCAN2)에 의해 턴-온 되어, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압을 기준 전압 라인(RVL)으로 전달 해줄 수 있다.

- [0111] 다시 말해, 제2 트랜지스터(T2)는, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압 상태를 제어하거나, 구동 트랜지스터(DRT)의 제2 노드(N2)의 전압을 기준 전압 라인(RVL)에 전달해줄 수 있다.

- [0112] 여기서, 기준 전압 라인(RVL)은 기준 전압 라인(RVL)의 전압을 센싱하여 디지털 값으로 변환하여, 디지털 값을

포함하는 센싱 데이터를 출력하는 아날로그 디지털 컨버터와 전기적으로 연결될 수 있다.

- [0113] 아날로그 디지털 컨버터는 데이터 구동 회로(DDR)를 구현한 소스 드라이버 집적회로(SDIC)의 내부에 포함될 수도 있다.

- [0114] 아날로그 디지털 컨버터에서 출력된 센싱 데이터는 구동 트랜지스터(DRT)의 특성치(예: 문턱전압, 이동도 등) 또는 유기발광다이오드(OLED)의 특성치(예: 문턱전압 등)를 센싱하는데 이용될 수 있다.

- [0115] 한편, 캐패시터(Cst)는, 구동 트랜지스터(DRT)의 제1 노드(N1)와 제2 노드(N2) 사이에 존재하는 내부 캐패시터 (Internal Capacitor)인 기생 캐패시터(예: Cgs, Cgd)가 아니라, 구동 트랜지스터(DRT)의 외부에 의도적으로 설계한 외부 캐패시터(External Capacitor)일 수 있다.

- [0116] 구동 트랜지스터(DRT), 제1 트랜지스터(T1) 및 제2 트랜지스터(T2) 각각은 n 타입 트랜지스터이거나 p 타입 트랜지스터일 수 있다.

- [0117] 한편, 제1 스캔 신호(SCAN1) 및 제2 스캔 신호(SCAN2)는 별개의 게이트 신호일 수 있다. 이 경우, 제1 스캔 신호(SCAN1) 및 제2 스캔 신호(SCAN2)는 서로 다른 게이트 라인을 통해, 제1 트랜지스터(T1)의 게이트 노드 및 제2 트랜지스터(T2)의 게이트 노드로 각각 인가될 수도 있다.

- [0118] 경우에 따라서는, 제1 스캔 신호(SCAN1) 및 제2 스캔 신호(SCAN2)는 동일한 게이트 신호일 수도 있다. 이 경우, 제1 스캔 신호(SCAN1) 및 제2 스캔 신호(SCAN2)는 동일한 게이트 라인을 통해 제1 트랜지스터(T1)의 게이트 노드 및 제2 트랜지스터(T2)의 게이트 노드에 공통으로 인가될 수도 있다.

- [0119] 도 3 및 도 4에 예시된 각 서브픽셀 구조는 설명을 위한 예시일 뿐, 1개 이상의 트랜지스터를 더 포함하거나, 경우에 따라서는, 1개 이상의 캐패시터를 더 포함할 수도 있다.

- [0120] 또는, 다수의 서브픽셀들 각각이 동일한 구조로 되어 있을 수도 있고, 다수의 서브픽셀들 중 일부는 다른 구조로 되어 있을 수도 있다.

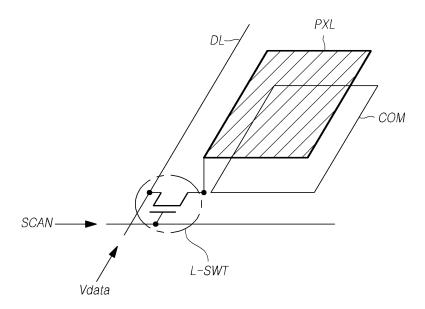

- [0121] 도 5는 본 발명의 실시예들에 따른 패널(PNL)이 LCD (Liquid Crystal Display) 패널인 경우, 서브픽셀(SP)의 구조를 나타낸 도면이다.

- [0122] 도 5를 참조하면, LCD 패널인 패널(PNL)에서의 각 서브픽셀(SP)은 픽셀전극(PXL) 및 스위칭 트랜지스터(L-SWT) 등을 포함할 수 있다.

- [0123] 스위칭 트랜지스터(L-SWT)는, 스캔신호(SCAN)에 의해 제어되며, 데이터 라인(DL)과 픽셀전극(PXL) 사이에 전기적으로 연결될 수 있다.

- [0124] 스위칭 트랜지스터(L-SWT)는 스캔신호(SCAN)에 의해 턴-온 되어, 데이터 라인(DL)에서 공급된 데이터 전압 (Vdata)을 픽셀전극(PXL)에 전달해준다. 데이터전압(Vdata)이 인가된 픽셀전극(PXL)은 공통전압이 인가되는 공통전극(COM)과 전계를 형성할 수 있다. 즉, 픽셀전극(PXL)과 공통전극(COM) 사이에 캐패시터 (스토리지 캐패시터)가 형성될 수 있다.

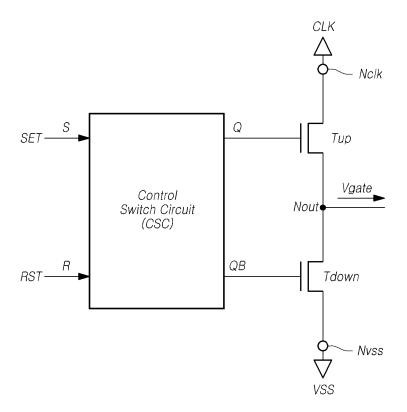

- [0125] 도 6은 본 발명의 실시예들에 따른 패널(PNL)에 배치된 게이트 구동회로(GDC)를 개략적으로 나타낸 도면이다.

- [0126] 도 6을 참조하면, 각 게이트 구동회로(GDC)는 풀-업 트랜지스터(Tup), 풀-다운 트랜지스터(Tdown) 및 제어 스위치 회로(CSC) 등을 포함할 수 있다.

- [0127] 제어 스위치 회로(CSC)는 풀-업 트랜지스터(Tup)의 게이트 노드에 해당하는 Q 노드의 전압과, 풀-다운 트랜지스터(Tdown)의 게이트 노드에 해당하는 QB 노드의 전압을 제어하는 회로로서, 여러 개의 스위치(트랜지스터)를 포함할 수 있다.

- [0128] 풀-업 트랜지스터(Tup)는 게이트 신호 출력 노드(Nout)를 통해 게이트 라인(GL)으로 제1 레벨 전압(예: 하이 레벨 전압(VGH))에 해당하는 게이트 신호(Vgate)를 공급하는 트랜지스터이다. 풀-다운 트랜지스터(Tdown)는 게이트 신호 출력 노드(Nout)를 통해 게이트 라인(GL)으로 제2 레벨 전압(예: 로우 레벨 전압(VGL))에 해당하는 게이트 신호(Vgate)를 공급하는 트랜지스터이다. 풀-업 트랜지스터(Tup)와 풀-다운 트랜지스터(Tdown)는 서로 다른 타이밍에 턴-온 될 수 있다.

- [0129] 풀-업 트랜지스터(Tup)는, 클럭신호(CLK)가 인가되는 클럭신호 인가 노드(Nclk)와 게이트 라인(GL)에 전기적으로 연결된 게이트 신호 출력 노드(Nout) 사이에 전기적으로 연결되고, Q 노드의 전압에 의해 턴 온 또는 턴 오

프 된다.

- [0130] 풀-업 트랜지스터(Tup)의 게이트 노드는 Q 노드에 전기적으로 연결된다. 풀-업 트랜지스터(Tup)의 드레인 노드 또는 소스 노드는 클럭신호 인가 노드(Nclk)에 전기적으로 연결된다. 풀-업 트랜지스터(Tup)의 소스 노드 또는 드레인 노드는 게이트 신호(Vgate)가 출력되는 게이트 신호 출력 노드(Nout)에 전기적으로 연결된다.

- [0131] 풀-업 트랜지스터(Tup)는, Q 노드의 전압에 의해 턴 온 되어, 클럭신호(CLK)의 하이 레벨 구간에서의 하이 레벨 전압(VGH)을 갖는 게이트 신호(Vgate)를 게이트 신호 출력 노드(Nout)로 출력한다.

- [0132] 게이트 신호 출력 노드(Nout)에 출력된 하이 레벨 전압(VGH)의 게이트 신호(Vgate)는 해당 게이트 라인(GL)에 공급된다.

- [0133] 풀-다운 트랜지스터(Tdown)는, 게이트 신호 출력 노드(Nout)와 기저 전압 노드(Nvss) 사이에 전기적으로 연결되고, QB 노드의 전압에 의해 턴 온 또는 턴 오프 된다.

- [0134] 풀-다운 트랜지스터(Tdown)의 게이트 노드는, QB 노드에 전기적으로 연결된다. 풀-다운 트랜지스터(Tdown)의 드 레인 노드 또는 소스 노드는 기저 전압 노드(Nvss)에 전기적으로 연결되어 정 전압에 해당하는 기저 전압(VSS)을 인가받는다. 풀-다운 트랜지스터(Tdown)의 소스 노드 또는 드레인 노드는, 게이트 신호(Vgate)가 출력되는 게이트 신호 출력 노드(Nout)에 전기적으로 연결된다.

- [0135] 풀-다운 트랜지스터(Tdown)는, QB 노드의 전압에 의해 턴 온 되어, 로우 레벨 전압(VGL)의 게이트 신호(Vgate)를 게이트 신호 출력 노드(Nout)로 출력한다. 이에 따라, 로우 레벨 전압(VGL)의 게이트 신호(Vgate)는 게이트 신호 출력 노드(Nout)를 통해 해당 게이트 라인(GL)으로 공급될 수 있다. 여기서, 로우 레벨 전압(VGL)의 게이트 신호(Vgate)는, 일 예로, 기저 전압(VSS)일 수 있다.

- [0136] 한편, 제어 스위치 회로(CSC)는, 둘 이상의 트랜지스터 등으로 구성될 수 있으며, Q 노드, QB 노드, 세트 노드 (S, 스타트 노드라고도 함), 리셋 노드(R) 등의 주요 노드가 있다. 경우에 따라서, 제어 스위치 회로(CSC)는 구 동전압(VDD) 등의 각종 전압이 입력되는 입력 노드 등이 더 있을 수 있다.

- [0137] 제어 스위치 회로(CSC)에서, Q 노드는 풀-업 트랜지스터(Tup)의 게이트 노드와 전기적으로 연결되고, 충전과 방전이 반복된다.

- [0138] 제어 스위치 회로(CSC)에서, QB 노드는 풀-다운 트랜지스터(Tdown)의 게이트 노드와 전기적으로 연결되고, 충전과 방전이 반복된다.

- [0139] 제어 스위치 회로(CSC)에서, 세트 노드(S)는 해당 게이트 구동회로(GDC)의 게이트 구동의 시작을 지시하기 위한 세트 신호(SET)를 인가 받는다.

- [0140] 여기서, 세트 노드(S)에 인가되는 세트 신호(SET)는 게이트 드라이버(GDR)의 외부에서 입력되는 스타트 신호 (VST)일 수도 있고, 현재의 게이트 구동회로(GD)보다 앞선 이전 스테이지(stage)의 게이트 구동 회로(GDC)에서 출력된 게이트 신호(Vgate)가 피드백 된 신호(캐리 신호)일 수도 있다.

- [0141] 제어 스위치 회로(CSC)에서 리셋 노드(R)에 인가되는 리셋 신호(RST)는 모든 스테이지의 게이트 구동회로들 (GDC)을 동시에 초기화하기 위한 리셋 신호일 수도 있고, 다른 스테이지(이전 또는 이후 스테이지)로부터 입력된 캐리 신호일 수 있다.

- [0142] 제어 스위치 회로(CSC)는 세트 신호(SET)에 응답하여 Q 노드를 충전하고, 리셋 신호(RST)에 응답하여 Q 노드를 방전한다. 제어 스위치 회로(CSC)는 Q 노드와 QB 노드 각각을 서로 다른 타이밍에 충전 또는 방전시키기 위하여 인버터 회로를 포함할 수 있다.

- [0143] 도 3에 도시된 바와 같이, OLED 패널에 해당하는 패널(PNL)의 액티브 영역(A/A) 내 다수의 서브픽셀(SP) 각각에는 구동 트랜지스터(DRT) 및 스위칭 트랜지스터(O-SWT)가 배치될 수 있다. 다만, 본 실시예들은 이에 한정되지 않으며, 도 4에 도시된 바와 같이, OLED 패널에 해당하는 패널(PNL)의 액티브 영역(A/A) 내 3개 이상의 트랜지스터가 배치될 수도 있다.

- [0144] 또한, 도 5에 도시된 바와 같이, LCD 패널에 해당하는 패널(PNL)의 액티브 영역(A/A) 내 다수의 서브픽셀(SP) 각각에는 스위칭 트랜지스터(L-SWT)가 배치될 수 있다.

- [0145] 이와 같이, OLED 패널 또는 LCD 패널 등일 수 있는 패널(PNL)의 액티브 영역(A/A) 내 다수의 서브픽셀(SP) 각각 의 영역에는 트랜지스터(DRT, O-SWT, L-SWT)가 배치될 수 있다.

- [0146] 또한, 도 2에 도시된 바와 같이, 게이트 구동회로(GDC)가 INSIP 타입으로 구현된 경우, 즉, 게이트 구동회로 (GDC)가 패널(PNL)에 내장되는 경우, 도 5와 같은 게이트 구동회로(GDC)를 구성하는 각종 트랜지스터(Tup, Tdown, CSC 내부의 트랜지스터들)이 패널(PNL)의 액티브 영역(A/A)의 외곽 영역인 넌-액티브 영역(N/A)에 배치될 수 있다.

- [0147] 한편, 패널(PNL)의 액티브 영역(A/A) 및/또는 넌-액티브 영역(N/A)에 배치되는 트랜지스터(TR)는 채널 길이와 S-계수(Sub-threshold swing: S-factor or SS)에 따라 트랜지스터(TR)의 소자 성능 (예: 이동도, 온-커런트 특성 등)이 달라질 수 있다. 이에, 아래에서는, 소자 성능을 향상시켜줄 수 있는 짧은 채널(Short Channel)을 갖고 높은 S-계수를 갖는 트랜지스터(TR)의 구조를 설명한다.

- [0148] 본 발명의 실시예들에 따른 트랜지스터(TR)는 기판 상에 배치된 제1 전극, 기판 상에 배치되고, 제1 전극의 일단과 중첩된 절연 패턴, 절연 패턴의 상면의 일부에 배치된 제2 전극, 제1 전극, 절연 패턴, 제2 전극 상에 배치된 액티브층, 액티브층 상에 배치된 게이트 절연막 및 게이트 절연막 상에 배치된 게이트 전극을 포함하고, 액티브층의 일 단은 제1 전극과 중첩되고 액티브층의 타 단은 제2 전극과 중첩되며 제1 및 제2 전극과 미 중첩한 영역에 채널 영역이 구비되고, 채널 영역은 채널 영역이 절연 패턴의 일 측면에 대응되는 영역인 제1부분과, 제1부분에서 연장되어 액티브층이 절연 패턴의 상면의 일부와 중첩하되 제2 전극과 미 중첩하는 영역인 제2부분을 포함하고, 절연 패턴의 측면에 대응되는 영역에서의 게이트 절연막의 두께는 절연 패턴의 상면의일부와 중첩하되 제2 전극과 미 중첩하는 영역에서의 상기 게이트 절연막의 두께보다 얇을 수 있다.

- [0149] 이와 같이, 간략하게 설명한 트랜지스터 구조(TR)에 대하여, 여러 도면들을 참조하여 더욱 상세하게 설명한다.

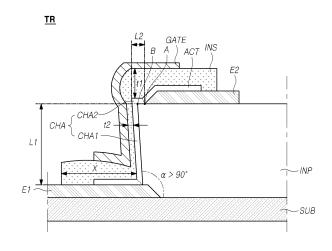

- [0150] 도 7은 본 발명의 실시예에 따른 수직(Vertical) 구조의 트랜지스터를 나타낸 도면이다. 도 8은 본 발명의 실시 예에 따른 절연 패턴의 형상을 도시한 도면이다.

- [0151] 본 발명에 따른 실시예들에서 정의하는 수직 구조의 트랜지스터(TR)는 액티브층(ACT)의 채널 영역(CHA; Channel Area)이 기판(SUB)과 평행하지 않도록 배치된 트랜지스터(TR)를 의미한다. 포괄적으로는, 액티브층(ACT)의 채널 영역(CHA)과 기판(SUB) 사이의 각도가 0° 초과 180° 미만인 경우를 모두 포함할 수 있다.

- [0152] 도 7을 참조하면, 패널(PNL)에 배치되는 수직 구조의 트랜지스터(TR)는 게이트 전극(GATE), 액티브층(ACT), 제1 전극(E1) 및 제2 전극(E2)을 포함할 수 있다.

- [0153] 제1 전극(E1)은 소스 전극이고, 제2 전극(E2)은 드레인 전극일 수 있고, 다른 경우에, 제1 전극(E1)은 드레인 전극이고, 제2 전극(E2)은 소스 전극일 수도 있다.

- [0154] 구체적으로, 기판(SUB) 상에 제1 전극(E1)이 배치된다.

- [0155] 제1 전극(E1)이 배치된 기판(SUB) 상에는 제1 전극(E1)의 일 단과 중첩된 절연 패턴(INP)이 배치된다.

- [0156] 절연 패턴(INP)은 수직 구조의 트랜지스터(TR)에서 액티브층(ACT)의 채널 영역(CHA)을 기판(SUB)과 평행하지 않도록 세우기 위한 구조물일 수 있다. 이러한 절연 패턴(INP)은 무기절연물질, 예를 들면, SiOx, SiO<sub>2</sub>, SiON, SiNx 등 중 하나 이상을 포함하여 구성될 수 있다.

- [0157] 이러한 절연 패턴(INP)의 상면의 일부에 제2 전극(E2)이 배치된다.

- [0158] 또한, 도 7에 도시된 바와 같이, 제2 전극(E2)의 일 단(A)은 절연 패턴(INP)의 일 단(B)과 이격된다.

- [0159] 액티브충(ACT)은 제1 전극(E1)의 일부, 제2 전극(E2)의 일부(또는 전부) 및 절연 패턴(INP)의 일 측면 상에 배치되어 이들과 중첩된다.

- [0160] 구체적으로, 도 7에 도시된 바와 같이, 액티브층(ACT)의 일 단은 제1 전극(E1)과 중첩되고, 타 단은 제2 전극(E2)과 중첩될 수 있다.

- [0161] 도 7에서는 액티브층(ACT)이 단일층인 것으로 도시되었으나, 본 발명이 이에 국한되는 것은 아니며, 액티브층 (ACT)은 2층 이상의 다중층으로 구성될 수도 있다.

- [0162] 이러한 액티브층(ACT)은 채널 영역(CHA)을 포함할 수 있다.

- [0163] 채널 영역(CHA)은 액티브충(ACT)이 절연 패턴(INP)의 일 측면에 대응되는 영역과, 액티브충(ACT)이 절연 패턴 (INP)의 상면의 일부와 중첩하되, 제2 전극(E2)과 미 중첩하는 영역을 포함하는 영역일 수 있다.

- [0164] 즉, 채널 영역(CHA)은 액티브층(ACT)이 제1 전극(E1) 및 제2 전극(E2) 각각과 미 중첩된 영역일 수 있다. 이러한 채널 영역(CHA)은 단면 상에서 수직 또는 수평 방향으로 게이트 전극(GATE)과 중첩될 수 있다.

- [0165] 다른 측면으로, 채널 영역(CHA)은 액티브층(ACT)이 절연 패턴(INP)의 일 측면과 중첩하는 영역(CHA1, 제1 부분) 및 제1 부분(CHA1)에서 연장되는 영역을 포함하고 제2 전극(E2)의 일 단(A)과 절연 패턴(INP)의 일 단(B)이 이 격되어 절연 패턴(INP)의 상부가 제2 전극(E2)에 의해 노출된 영역(CHA2, 제2 부분)과 대응되는 영역일 수 있다.

- [0166] 이에, 채널 영역(CHA)의 길이는, 제1 부분(CHA1)의 길이(L1), 제2 부분(CHA1)의 길이(L2)일 수 있다.

- [0167] 다시 말해, 채널 영역(CHA)의 길이는 절연 패턴(INP)의 측면에 위치한 액티브층(ACT)의 길이(L1)와,절연 패턴 (INP)의 측면에 위치한 액티브층(ACT)에서 연장되고 절연 패턴(INP)의 상면의 일부와 중첩하되 제2 전극(E2)과 미 중첩하는 영역에 배치된 액티브층(ACT)의 길이(L2)의 합일 수 있다.

- [0168] 상술한 바와 같이, L1은 절연 패턴(INP)의 일 측면과 중첩하는 영역에서의 액티브층(ACT)의 길이를 의미한다.

- [0169] 본 발명의 실시예에 따른 액티브충(ACT)의 채널 영역(CHA)의 길이는, 절연 패턴(INP)의 일 측면과 중첩하는 영역에서의 액티브충(ACT)의 길이를 포함하므로, 절연 패턴(INP)의 높이가 달라지면, 채널 영역(CHA)의 길이 역시달라질 수 있다. 즉, 채널 영역(CHA)의 길이는 절연 패턴(INP)의 높이에 비례할 수 있다.

- [0170] 예를 들면, 절연 패턴(INP)의 높이가 낮아질 경우, 절연 패턴(INP)의 일 측면과 중첩하는 영역에서의 액티브층 (ACT)의 길이가 짧아지므로, 전체적인 채널 영역(CHA)의 길이가 짧아질 수 있다.

- [0171] 다시 말해, 본 발명의 트랜지스터(TR)는 노광 공정 등을 통해 액티브층(ACT)의 채널 영역(CHA)의 길이를 결정하지 않고, 절연 패턴(INP)의 높이 조절만으로도 채널 영역(CHA)의 길이를 조절할 수 있다.

- [0172] 본 발명의 실시예에서 절연 패턴(INP)의 높이는 100nm 내지 500nm 일 수 있으나, 본 발명이 이에 한정되는 것은 아니다.

- [0173] 한편, 수평 구조의 트랜지스터의 경우, 액티브층(ACT)의 채널영역(CHA)의 길이를 줄이기 위해서는 미세 사이즈에 대한 노광 공정이 적용되어야 하나, 노광 장비의 한계로 채널영역(CHA)의 길이를 저감시키는 데 한계가 있다.

- [0174] 또한, 노광 장비를 통해 짧은 채널을 갖는 액티브층(ACT)을 형성하더라도, 패널(PNL)에 형성된 트랜지스터(TR) 들의 채널영역(CHA)의 길이가 일정하지 않고, 트랜지스터(TR)마다 불균일한 채널영역(CHA)의 길이를 가질 수 있다.

- [0175] 그러나, 본 발명의 실시예들에 따른 트랜지스터(TR)는 절연 패턴(INP)의 높이를 통해 액티브층(ACT)의 채널 영역의 길이를 조절할 수 있으므로, 짧은 채널을 갖는 액티브층(ACT)을 형성하기 위해, 노광 공정을 적용할 필요가 없다.

- [0176] 게이트 절연막(INS)은 액티브층(ACT)을 덮으면서 배치된다. 게이트 절연막(INS)은 액티브층(ACT)의 상면 및 측면을 덮고 제1 전극(E1)의 일부 및 제2 전극(E2)의 일부 또는 전부를 덮도록 배치될 수 있다..

- [0177] 게이트 절연막(INS) 상에는 게이트 전극(GATE)이 배치된다.

- [0178] 상술한 구조의 트랜지스터(TR)는 OLED 패널(PNL) 내에 배치된 다수의 트랜지스터(TR) 중 구동 트랜지스터(DRT)에 적용될 수 있다.

- [0179] 구동 트랜지스터(DRT)는 높은 S-계수와 높은 온-커런트(On-Current, 패널이 켜져 있을 때의 전류) 특성이 요구되고, 특히, 모바일용 OLED 패널(PNL)에 사용되는 구동 트랜지스터(DRT)는 상술한 특성이 더욱 요구된다.

- [0180] S-계수는 S-계수 그래프(Sub-threshold graph)를 통해 알 수 있다.

- [0181] S-계수 그래프는 구동 트랜지스터의 게이트 전압의 변화량과 구동 전류의 변화량 간의 비율을 나타낸 그래프이 며, 구동 트랜지스터(DRT)의 S-계수 그래프의 기울기가 큰 경우 가용 데이터 전압 범위가 좁아 저 계조 표현에 불리하다는 문제가 있으며, 구동 트랜지스터가 오프(off) 상태에서 온(on) 상태로 가는 속도가 느릴 수 있다.

- [0182] 여기서, S-계수 그래프의 기울기는 1/S-계수일 수 있다.

- [0183] 다시 말해, S-계수는 게이트 전압이 변할 때, 채널 포텐셜(channel potential)이 얼마나 빠르게 변하는지를 나타내는 것이고, S-계수가 크다는 것은 S-계수가 작을 때에 비해서, 채널 포텐셜이 느리게 변하는 것을

의미한다.

- [0184] 이러한 S-계수는 게이트 절연막(INS)의 캐패시턴스 값과 관련이 있다. 구체적으로, 게이트 절연막(INS)의 캐패시턴스 값은 S-계수와 반비례 관계에 있다.

- [0185] 여기서, 게이트 절연막(INS)의 캐패시턴스 값이란, 게이트 전극(GATE)과 채널 영역(CHA)에 의해서 형성된 단위 면적 당 커패시턴스 값을 의미한다. 게이트 절연막(INS)의 커패시턴스 값, 게이트 절연막(INS)의 두께 및, 게이트 절연막(INS)의 유전율의 관계는 하기 식 1로 표현될 수 있다.

- [0186] [식 1]

$$C_{INS} \propto \frac{\varepsilon_{INS}}{T_{INS}}$$

[0187]

- [0188] 식 1에서, CINS는 게이트 절연막(INS)의 커패시턴스 값이고, TINS는 게이트 절연막(INS)의 두께이며, ε INS는 게이트 절연막(INS)의 유전율일 수 있다.

- [0189] 식 1에 의하면, 채널 영역(CHA) 게이트 전극(GATE) 사이에 위치된 게이트 절연막(INS)의 캐패시턴스 값은 게이트 절연막(INS)의 두께와 반비례 관계에 있음을 알 수 있다. 그리고, 게이트 절연막(INS)의 두께가 두꺼우면 S-계수가 커질 수 있다.

- [0190] 즉, 게이트 절연막(INS)의 두께가 두꺼우면, 게이트 절연막(INS)의 두께가 얇을 때보다, 게이트 전압이 채널 영역(CHA)에 천천히 도달하게 되므로 S-계수가 커질 수 있다.

- [0191] 상술한 바와 같이 S-계수는 게이트 전극(GATE)과 중첩하는 영역 내에서 게이트 게이트 절연막의 두께 조절을 통해 조절될 수 있다.

- [0192] 그러나, 일반적인 평면 구조의 트랜지스터 구조에서 게이트 게이트 절연막의 두께가 얇아지면 높은 온-커런트를 얻을 수 있는 반면 S-계수는 작아지고, 게이트 게이트 절연막의 두께가 두꺼워지면 높은 S-계수를 얻을 수 있는 반면 온-커런트가 낮아지는 문제가 있다.

- [0193] 또한, 게이트 게이트 절연막의 두께뿐만 아니라 액티브층의 채널 길이를 조절하여 온-커런트 크기를 조절할 수 있다. 구체적으로, 액티브층의 채널 길이가 짧아질수록 문턱 전압(threshold voltage)이 감소하게 되어 온-커런 트가 커질 수 있다.

- [0194] 이에, 일반적인 평면 구조의 트랜지스터에서 게이트 게이트 절연막의 두께를 두껍게 유지하고 액티브층의 짧은 채널을 이용하여 높은 S-계수와 높은 온-커런트 특성을 구현하기 위한 연구가 진행되었으나, 상술한 바와 같이, 공정 상의 한계로 짧은 채널을 갖는 액티브층을 제조하는데 어려움이 있었다.

- [0195] 본 발명의 실시예에 따른 전자장치는, 구동 트랜지스터(DRT)를 수직 구조 트랜지스터(TR)로 사용하여 짧은 채널 영역(CHA)을 갖는 액티브층(ACT)을 포함하고, 게이트 절연막(INS)의 두께를 영역 별로 조절하여, 높은 S-계수 (factor)와 높은 온-커런트 특성을 구현할 수 있다.

- [0196] 본 발명의 실시예에 따른 수직 구조의 트랜지스터(TR)에서, 액티브층(ACT)의 채널(CHA) 영역은 절연 패턴(INP)의 높이를 낮추는 방법을 통해 구현될 수 있다. 절연 패턴(INP)의 높이는 100nm 내지 500nm 일 수 있으나, 본 발명이 이에 한정되는 것은 아니다.

- [0197] 즉, 수평 구조 트랜지스터에서는 공정 상의 문제 등으로 인해 구현하지 못한 짧은 채널을 갖는 액티브충(ACT)을 용이하게 구현할 수 있다.

- [0198] 또한, 본 발명의 실시예에 따른 전자장치는 게이트 절연막(INS)의 두께를 부분적으로 두껍게 하여 S-계수를 크게 할 수 있다.

- [0199] 구체적으로, 제2 전국(E2)의 일 단과 절연 패턴(INP)의 일 단이 이격된 영역과 대응되는 영역에 배치된 액티브 층(ACT) 상의 게이트 절연막(INS)의 두께(t1, 제1 두께로 명명함)는, 절연 패턴(INP)의 일 측면과 중첩하는 일부 영역에서의 액티브층(ACT) 상에 배치된 게이트 절연막(INS)의 두께(t2, 제2 두께로 명명함)보다 두꺼울 수있다.

- [0200] 즉, 액티브층(ACT)의 채널 영역(CHA) 상에 배치된 게이트 절연막(INS)의 제1 두께(t1)는 제2 두께(t2)보다 두꺼울 수 있다. 여기서, 제1 두께(t1)는 기판(SUB)과 평행하지 않은 방향을 기준으로 한 게이트 절연막(INS)의 두께이고, 제2 두께(t2)는 기판(SUB)과 평행한 방향을 기준으로 한 게이트 절연막(INS)의 두께이다.

- [0201] 제1 두께(t1)가 제2 두께(t2)보다 두꺼우므로, 게이트 절연막(INS)이 제1 두께(t1)를 갖는 영역과 대응되는 영역에서의 채널 영역(CHA)의 저항은, 게이트 절연막(INS)이 제2 두께를(T2)를 갖는 영역과 대응되는 영역에서의 채널 영역(CHA)의 저항보다 클 수 있다.

- [0202] 따라서, 제1 두께(t1)가 제2 두께(t2)보다 두꺼우므로, 게이트 절연막(INS)이 제1 두께(t1)를 갖는 영역과 대응되는 영역에서의 채널 포텐셜(Potential)은 게이트 절연막(INS)이 제2 두께를(T2)를 갖는 영역과 대응되는 영역에서의 채널 포텐셜보다 느리게 변할 수 있다.

- [0203] 채널 영역(CHA)의 포텐셜이 일부 영역에서 빠르게 변할지라도, 나머지 영역에서 느리게 변한다면, 전체 채널 영역(CHA)의 포텐셜은 가장 느리게 변하는 영역의 속도를 따라가게 된다.

- [0204] 즉, 채널 영역(CHA) 상에 배치된 게이트 절연막(INS)막을 일부 영역에서만 두껍게 형성해도 S-계수를 크게 하는 효과를 얻을 수 있다.

- [0205] 다시 말해, 본 발명의 실시예에 따른 수직 구조의 트랜지스터(TR)는 액티브층(ACT)이 짧은 채널을 구비함으로써 높은 온-커런트 특성을 가질 수 있고, 채널 영역(CHA) 영역 상에 배치된 게이트 절연막(INS)의 두께를 일부분에 서만 두껍게 조절하여 S-계를 높임으로써, 가용 데이터 전압 범위를 넓힐 수 있는 효과가 있다.

- [0206] 또한, 액티브층(ACT)의 짧은 채널은 수직 구조 트랜지스터(TR)의 구동 전류를 증가시킬 수 있다.

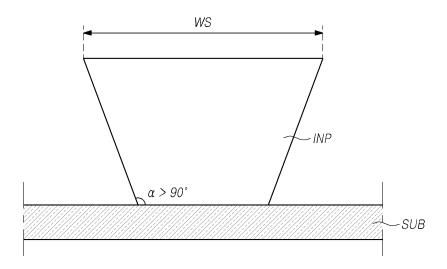

- [0207] 한편, 도 7 및 도 8에 도시된 바와 같이, 게이트 절연막(INS)이 절연 패턴(INP)의 측면의 일부와 대응되는 영역에서 얇은 두께인 제2 두께(t2)를 갖기 위해서, 절연 패턴(INP)의 폭(WS)이 기판(SUB)으로부터 멀어질수록 넓어지는 영역을 포함할 수 있다.

- [0208] 구체적으로, 절연 패턴(INP)의 일 측면과 기판(SUB)이 이루는 각도(a)는 90o보다 큰 각도일 수 있다. 즉, 절연 패턴(INP)은 역테이퍼 형상일 수 있다. 여기서, 절연 패턴(INP)의 폭(WS)은 기판(SUB)과 수평한 방향을 기준으로 한 길이일 수 있다.

- [0209] 본 발명에서, 게이트 절연막(INS)은 증착 공법을 통해 형성될 수 있다.

- [0210] 그러나, 절연 패턴(INP)이 역테이퍼 형상을 가짐으로써, 게이트 절연막(INS)을 형성하는 원료물질이 절연 패턴 (INP)의 상부의 끝 단에 가려져 절연 패턴(INP)의 측면에는 적정한 양이 도달하지 못하게 된다. 이로 인해, 절 연 패턴(INP)의 상면 및 제1 전극(E1) 상에 형성된 게이트 절연막(INS)의 두께보다 절연 패턴(INP)의 측면에 형성된 게이트 절연막(INS)의 두께가 얇아질 수 있다.

- [0211] 본 발명의 실시예들에 따른 트랜지스터(TR)들은 일반적인 수평 구조의 트랜지스터에 비해 소자의 면적을 감소시킬 수 있다. 구체적으로, 본 발명의 실시예들에 따른 트랜지스터(TR)는 액티브층(ACT)이 절연 패턴(INP)에 의해기판(SUB)과 평행하지 않은 방향으로 세워지기 때문에, 채널 영역(CHA)이 짧아질 수 있고 이를 통해, 액티브층(ACT)의 길이 역시 짧아질 수 있으므로 소자의 면적이 작아질 수 있다.

- [0212] 또한, 액티브층(ACT)과, 제1 전극(E1) 및 제2 전극(E2)이 직접 컨택하는 구조를 갖는다.

- [0213] 액티브층(ACT)과, 제1 전극(E1) 및 제2 전극(E2) 사이에 게이트 절연막을 두고 게이트 절연막에 형성된 컨택홀을 형성하여 제1 전극(E1) 및 제2 전극(E2) 각각을 액티브층(ACT)과 컨택시키는 경우, 게이트 절연막에 형성된 컨택홀의 입구 폭만큼 제1 전극(E1) 및 제2 전극(E2)의 면적이 커질 수 밖에 없다. 반면, 본 발명의 실시예에 따른 트랜지스터(TR)는 상술한 바와 같이 액티브층(ACT)과, 제1 전극(E1) 및 제2 전극(E2)이 직접 컨택하는 구조를 가지므로, 소자의 면적을 줄일 수 있다.

- [0214] 도 7에서는 액티브층(ACT)과 게이트 전극(GATE) 사이에 배치된 게이트 절연막(INS)이 단일층인 구성을 도시하였으나, 본 발명은 이에 한정되지 않으며, 게이트 절연막(INS) 둘 이상의 층으로 이루어질 수 있다. 이를 도 9를 참조하여 검토하면 다음과 같다.

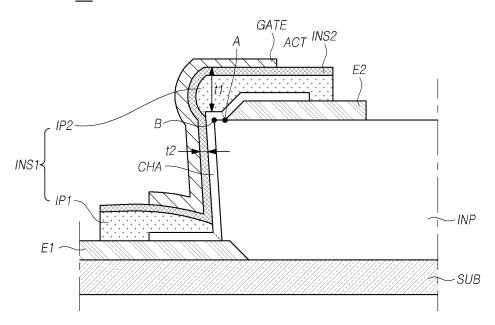

- [0215] 도 9는 본 발명의 다른 실시예에 따른 수직 구조의 트랜지스터를 나타낸 도면이다.

- [0216] 후술하는 설명에서는 앞서 설명한 실시예들과 중복되는 내용(구성, 효과 등)은 생략할 수 있다.

- [0217] 도 9를 참조하면, 본 발명의 다른 실시예에 따른 수직 구조의 트랜지스터(TR)는 게이트 전극(GATE), 액티브층 (ACT), 제1 전극(E1) 및 제2 전극(E2)을 포함할 수 있다.

- [0218] 제1 전극(E1)이 배치된 기판(SUB) 상에는 제1 전극(E1)의 일 단과 중첩된 절연 패턴(INP)이 배치된다.

- [0219] 절연 패턴(INP)이 제1 전극(E1)의 일 단과 중첩하도록 배치됨으로써, 액티브충(ACT)의 채널 영역(CHA)의 길이가 짧아질 수 있다.

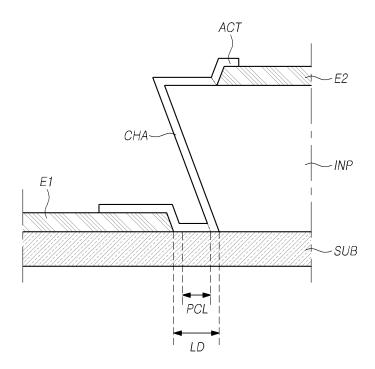

- [0220] 구체적으로, 도 10을 참조하여, 제1 전극(E1) 및 절연 패턴(INP)의 배치 구조에 따른 채널 영역(CHA)의 길이의 관련성을 검토하면 다음과 같다.

- [0221] 도 10은 제1 전극 및 절연 패턴(INP)의 배치 구조에 따른 채널 영역의 길이의 관련성을 도시한 도면이다.

- [0222] 도 10을 참조하면, 제1 전극(E1)과 절연 패턴(INP)(INP)가 이격하여 배치될 수 있다. 그리고, 액티브층(ACT)의 일 단은 제1 전극(E1)과 중첩되고, 액티브층(ACT)의 타 단은 제2 전극(E2)과 중첩할 수 있다.

- [0223] 액티브충(ACT)의 채널 영역(CHA)은 절연 패턴(INP)의 일 측면 및 상면의 일부를 따라 구비될 수 있다. 그리고, 제1 전극(E1)과 절연 패턴(INP) 사이의 기판(SUB) 상에도 구비될 수 있다.

- [0224] 따라서, 도 10의 액티브층(ACT)의 채널 영역(CHA)의 길이는 도 7 및 도 9의 채널 영역(CHA)의 길이보다 제1 전 극(E1)과 절연 패턴(INP) 사이의 기판(SUB) 상에 배치된 채널 영역(CHA)의 길이(PCL)만큼 길어질 수 있다.

- [0225] 여기서, 제1 전극(E1)과 절연 패턴(INP) 사이의 기판(SUB) 상에 배치된 채널 영역(CHA)의 길이(PCL)는 제1 전극(E1)과 절연 패턴(INP) 사이의 이격거리(LD)보다 짧을 수 있다.

- [0226] 즉, 본 발명의 실시예들에 따른 수직 구조의 트랜지스터(TR)는 제1 전극(E1)의 일 단과 절연 패턴(INP)이 중첩 하도록 배치됨으로써, 짧은 채널을 구현할 수 있다.

- [0227] 도 9에서, 액티브층(ACT)의 일 단은 제1 전극(E1)의 상면의 일부와 절연 패턴(INP)의 일 측면, 절연 패턴(INP)의 상면의 일부 및 제2 전극(E2)의 상면의 일부를 따라 배치된다.

- [0228] 액티브층(ACT) 상에는 제1 게이트 절연막(INS1) 및 제2 게이트 절연막(INS2)이 배치된다.

- [0229] 제1 게이트 절연막(INS)은 제1 전극(E1)과 중첩하는 제1 영역(IP1)과, 제2 전극(E2)과 중첩하는 제2 영역(IP2)을 포함한다.

- [0230] 제1 게이트 절연막(INS1)은 절연 패턴(INP)의 측면의 일부와 대응되는 영역에 배치된 액티브층(ACT)의 상면을 노출하도록 배치된다. 제1 게이트 절연막(INS1)에 의해 상면의 일부가 노출된 액티브층(ACT)의 영역은 채널 영역(CHA)의 일부일 수 있다.

- [0231] 한편, 제2 영역(IP2)은 제2 전극(E2)의 일 단(A)과 절연 패턴(INP)의 일 단(B)이 이격되어 제2 전극(E2)이 절연 패턴(INP)의 상면을 노출하는 영역에도 배치될 수 있다.

- [0232] 제2 전극(E2)의 일 단(A)과 절연 패턴(INP)의 일 단(B)이 이격되어 제2 전극(E2)이 절연 패턴(INP)의 상면을 노출하는 영역 상에는 액티브층(ACT)의 채널 영역(CHA)이 구비될 수 있다.

- [0233] 즉, 제2 영역(IP2)은 채널 영역(CHA)의 일부, 예를 들면, 채널 영역(CHA)의 제2 부분(CHA2) 상에도 배치될 수 있다.

- [0234] 제1 게이트 절연막(INS1)과 액티브층(ACT) 상에는 제2 게이트 절연막(INS2)이 배치될 수 있다.

- [0235] 제2 게이트 절연막(INS)은 제1 게이트 절연막(INS) 및 액티브층(ACT)을 덮으면서 배치될 수 있다.

- [0236] 한편, 도 9에서는 제1 게이트 절연막(INS1) 및 제2 게이트 절연막(ISN2)의 끝 단이 제1 전극(E1) 및 제2 전극 (E2)과 중첩하는 구조로 도시되어 있으나, 본 발명에 이에 한정되는 것은 아니다. 예를 들면, 제1 게이트 절연 막(INS1)은 절연 패턴(INP)의 측면에 대응되는 부분을 제외한 기판(SUB) 전면에 배치될 수 있고, 제2 게이트 절연연막은 기판(SUB) 전면에 배치될 수도 있다.

- [0237] 본 발명의 실시예들에 따른 수직 구조 트랜지스터(TR)는 절연 패턴(INP)을 이용하여 액티브층(ACT)의 채널 영역 (CHA)의 일부가 기판(SUB)과 평행하지 않은 방향으로 세워지는 효과를 얻을 수 있다.

- [0238] 다만, 절연 패턴(INP) 상에 배치되는 구성들 중에서, 액티브충(ACT)과 제2 게이트 절연막(INS2)과 같이 절연 패턴(INP)을 따라 형성되면서 얇은 두께가 요구되는 구성들은 절연 패턴(INP)로 인한 단차 때문에 두께 신뢰성을

얻기 어렵다.

- [0239] 이러한 문제점을 해결하기 위해, 본 발명의 실시예들에 따른 전자장치에서, 액티브층(ACT)과 제2 게이트 절연막 (INS2)은 일 예로, MOCVD (Metal-Organic Chemical Vapor Deposition) 또는 ALD (Atomic Layer Deposition) 등의 박막 증착 제어가 가능한 박막 증착 공법을 통해 형성될 수 있다.

- [0240] 여기서, MOCVD (Metal-Organic Chemical Vapor Deposition) 공법은, 고온의 기판 위에 원료 가스를 유출시켜 그 표면 상에서 분해 반응을 일으켜 박막을 형성하는 화학 중착(CVD: Chemical Vapor Deposition)의 일종으로서, 원료 가스 중에 유기 금속 착물을 포함하는 경우를 말하며, 유기 금속 가스를 가열한 기판 상에 열분해 시켜 반도체 박막을 성장시키는 기술이다. MOCVD의 경우, 다른 화학 중착 공법, 예를 들면, PECVD(Plasma Enhanced Chemical Vapor Deposition) 또는 LPCVD(Low Pressure Chemical Vapor Deposition) 보다 저온에서 조작하게 되고, 원자 오더에서의 박막 제어가 가능하며 균일한 막을 얻을 수 있다.

- [0241] ALD (Atomic Layer Deposition) 공법은, 반응원료를 각각 분리, 공급하여 반응가스 간 화학반응으로 형성된 입자를 기판 표면에 증착, 박막을 형성하는 증착법으로서, 하나의 반응원료가 박막이 증착되는 기판 위에 화학흡착이 일어난 후, 제2 또는 제3의 기체가 들어와 기판 위에서 다시 화학 흡착이 일어나면서 박막이 증착 되는 증착법이다.

- [0242] 이러한 MOCVD 또는 ALD 공법을 이용하는 경우, 일반적인 PVD (Physical Vapor Deposition) 및 일반적인 다른 CVD (Chemical Vapor Deposition) 공법에 비해, 박막 생산성이나 성장 속도는 늘릴 수 있으나, 박막 도포성이 좋아, 이를 통한 미세한 박막 두께 조절이 가능하다. 즉, MOCVD 또는 ALD 공법을 이용하는 경우, 우수한 스텝 커버리지(Step Coverage) 특성을 갖는 박막을 형성할 수 있다.

- [0243] 또한, MOCVD 또는 ALD 공법은, 스퍼터링 등의 다른 일반적인 증착법에 비해, 두께 균일도 및 조성 균일도가 더 우수하고, 더욱 고밀도의 박막을 형성할 수 있다.

- [0244] 이러한 MOCVD 또는 ALD 공법을 통해 형성되는 액티브층(ACT)과 제2 게이트 절연막(INS2)은 단차가 있는 영역에 서도 단선 없이 형성된 매우 얇은 박막일 수 있다.

- [0245] 또한, MOCVD 또는 ALD 공법을 통해 형성되는 액티브층(ACT)과 제2 게이트 절연막(INS2)은 위치 별 두께 편차가 매우 작을 수 있다. 즉, 액티브층(ACT)과 제2 게이트 절연막(INS2)은 좋은 두께 균일도를 가질 수 있다.

- [0246] 이에 반해, 제1 영역(IP1)과 제2 영역(IP2)을 포함하는 제1 게이트 절연막(INS1)은 MOCVD 또는 ALD 공법 이외의 다른 일반적인 증착법에 의해 형성될 수 있다. 예를 들면, 제1 게이트 절연막(INS1)은 PECVD 또는 스퍼터링 등의 증착법으로 형성될 수 있다.

- [0247] 제1 게이트 절연막(INS2)을 형성하는 공정에서, 제1 게이트 절연막(INS2)의 원료물질은 역테이퍼 형상의 절연 패턴(INP)의 상부 일 단에 가려져 절연 패턴(INP)의 측면과 대응되는 영역에 도달하지 못하게 된다. 이로 인해, 제1 게이트 절연막(INS2)은 절연 패턴(INP)의 측면에 대응되는 영역에서 형성되지 않고, 제1 전극(E1) 및 절연 패턴(INP)의 상면에 해당하는 영역에서만 형성될 수 있다.

- [0248] 그리고, 제2 게이트 절연막(INS2)은 제1 게이트 절연막(INS1)에 비해 작은 두께 편차와 높은 밀도를 가지면서 제1 게이트 절연막(INS1) 및 액티브층(ACT)을 덮으면서 배치될 수 있다.

- [0249] 또한, 제2 게이트 절연막(INS2)은 제1 게이트 절연막(INS1)보다 얇을 수 있다. 구체적으로, 제2 게이트 절연막 (INS2)이 최대 두께의 갖는 영역의 두께는 제1 게이트 절연막(INS1)이 최대 두께를 갖는 영역의 두께보다 얇을 수 있다.

- [0250] 예를 들면, 제2 게이트 절연막(INS2)의 두께는 50nm 이하일 수 있고, 제1 게이트 절연막(INS1)의 두께는 50nm 보다는 두꺼울 수 있으며, 200nm 이하의 두께를 가질 수 있다.

- [0251] 이에, 액티브층(ACT)의 채널 영역(CHA)과 게이트 전극(GATE) 사이에 배치된 게이트 절연막들의 두께는 위치 별로 상이할 수 있다.

- [0252] 구체적으로, 제2 전국(E2)의 일 단(A)과 절연 패턴(INP)의 일 단(B)이 이격되어 제2 전국(E2)이 절연 패턴(INP)의 상면을 노출하는 영역에서는 채널 영역(CHA)과 게이트 전국(GATE) 사이에 제1 게이트 절연막(INS1)과 제2 게이트 절연막(INS2)이 배치되고, 액티브층(ACT)이 절연 패턴(INP)의 일 측면과 중첩하는 영역에서는 채널 영역(CHA)과 게이트 전국(GATE) 사이에 제2 게이트 절연막(INS2)만 배치된다.

- [0253] 즉, 절연 패턴(INP)의 상면 상에 존재하는 채널 영역(CHA) 상의 게이트 절연막들(제1 및 제2 게이트 절연막)의 두께(t1)는 절연 패턴(INP)의 측면 상에 존재하는 채널 영역(CHA) 상의 게이트 절연막(제2 게이트 절연막)의 두 께(t2)보다 두껍다.

- [0254] 즉, 본 발명의 실시예에 따른 전자장치는, 마스크 공정 없이 채널 영역(CHA) 상의 게이트 절연막들(INS1, INS 2)의 두께를 조절할 수 있는 효과가 있다.

- [0255] 도 11은 본 발명의 또 다른 실시예에 따른 수직 구조의 트랜지스터를 나타낸 도면이다.

- [0256] 도 11을 참조하면, 수직 구조 트랜지스터(TR)는 제1 전극(E1), 제2 전극(E2) 및 절연 패턴(INP) 상에 배치되고, 액티브층(ACT)의 하부에 배치된 중간층(INT)을 더 포함할 수 있다.

- [0257] 구체적으로, 기판 상에 중간층(INT) 물질을 형성하고, 중간층(INT) 물질 상에 액티브층(ACT) 물질을 형성한 다음 동일 마스크를 통해 중간층(INT) 물질과 액티브층(ACT) 물질을 패터닝하여 중간층(INT)과 액티브층(ACT)을 형성할 수 있다.

- [0258] 여기서, 중간층(INT)은 무기 물질로 이루어질 수 있다. 예를 들면, Al203, TiO2, Ga203 및 ZnO 등 중 하나 이상을 포함하여 구성될 수 있다.

- [0259] 또한, 중간층(INT)의 두께는 10Å 내지 30Å의 범위에서 선택될 수 있다.

- [0260] 중간층(INT)의 두께는 제1 및 제2 게이트 절연막(INS1, INS2)의 두께보다 얇을 수 있다.

- [0261] 그리고, 액티브층(ACT)은 비정질 실리콘(a-Si: amorphous Silicon) 반도체로 구성될 수 있다. 이러한 액티브층 (ACT)을 포함하는 트랜지스터(TR)를 비정질 실리콘(a-Si) 트랜지스터라고 한다.

- [0262] 다른 예로, 액티브층(ACT)은 산화물(Oxide) 반도체로 구성될 수 있다. 이러한 액티브층(ACT)을 포함하는 트랜지스터(TR)를 옥사이드 트랜지스터라고 한다. 이 경우, 예를 들어, 산화물 반도체는 IGZO(Indium Gallium Zinc Oxide), IZO(Indium Zinc Oxide), ITZO(Indium Titanium Zinc Oxide) 등의 N형 산화물 반도체일 수도 있고, CuOx, SnOx, NiOx 등의 P형 산화물 반도체일 수도 있다.

- [0263] 중간층(INT)은 제1 전극(E1) 및 액티브층(ACT)과 컨택하는 영역과, 제2 전극(E2) 및 액티브층(ACT)과 컨택하는 영역을 포함한다.

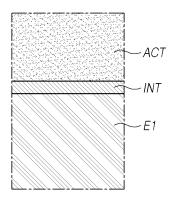

- [0264] 도 12를 참조하여 도 11의 컨택 영역(CTA: Contact Area)을 설명하면 다음과 같다.

- [0265] 도 12는 도 11의 컨택 영역(CTA: Contact Area)을 도시한 도면이다.

- [0266] 도 12를 참조하면, 컨택 영역(CTA: Contact Area)은 제1 전극(E1)과 액티브층(ACT)이 MIS (Metal Insulator Semiconductor) 컨택 원리에 의해 컨택하는 영역이고, 제2 전극(E2)과 액티브층(ACT)이 MIS(Metal Insulator Semiconductor) 컨택 원리에 의해 컨택하는 영역이다.

- [0267] 금속(Metal)과 반도체(Semiconductor)가 직접 컨택되는 경우, 높은 쇼트키 장벽(Schottky Barrier)를 갖기 때문에 컨택 저항이 높아진다. 그러나, 금속과 반도체 사이에 얇은 게이트 절연막이 삽입(MIS 컨택)되면, 금속과 반도체의 직접 컨택을 피하여 컨택 저항이 높아지는 것을 방지할 수 있다.

- [0268] 도 12를 참조하면, 제1 전극(E1)과 액티브층(ACT)의 사이에 중간층(INT)이 배치된다. 제2 전극(E2)과 액티브층 (ACT)의 사이에 중간층(INT)가 배치된다.

- [0269] 제1 전극(E1)과 액티브층(ACT)은 사이에 무기절연물질로 이루어진 중간층(INT)이 존재함에도 불구하고, 중간층 (INT)은 MOCVD 또는 ALD 등의 박막 증착 공법을 통해 매우 얇게 형성되어 있기 때문에, MIS (Metal Insulator Semiconductor) 컨택 원리에 의해, 제1 전극(S)과 액티브층(ACT) 간의 컨택 저항이 낮아질 수 있다.

- [0270] 마찬 가지로, 제2 전극(D)과 액티브층(ACT)은 사이에 무기절연물질로 이루어진 중간층(INT)이 존재함에도 불구하고, 중간층(INT)은 매우 얇게 형성되어 있기 때문에, MIS 컨택 원리에 의해, 제2 전극(E2)과 액티브층(ACT)간의 컨택 저항이 낮아질 수 있다.

- [0271] 한편, 도면에는 도시하지 않았으나, 전자장치가 패널(PNL) 등일 경우, 도 7, 도9 및 도 11에 도시된 수직 구조 트랜지스터(TR)는 액티브 영역의 서브픽셀(SP) 내에 배치될 수 있고, 이들은 픽셀 전극과 연결될 수 있다.

- [0272] 이를 도 13을 참조하여 검토하면 다음과 같다.

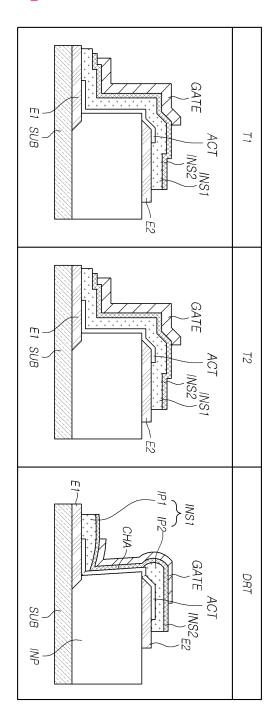

- [0273] 도 13은 본 발명의 실시예들에 따른 수직 구조 트랜지스터가 서브픽셀 내 배치된 경우, 픽셀 전극과 연결된 구조의 트랜지스터를 도시한 도면이다.

- [0274] 도 13을 참조하면, 액티브 영역(A/A)에서 서브픽셀(SP) 내에 배치되는 수직 구조 트랜지스터(TR) 중에는 제2 전 극(E2)이 픽셀 전극(PXL)과 전기적으로 연결되어야 하는 트랜지스터(DRT)가 존재할 수 있다.

- [0275] 이러한 트랜지스터(TR)의 게이트 전극(GATE)을 전극을 덮으면서 패시베이션층(PAS)이 배치될 수 있다. 도 13에 서는 설명의 편의를 위하여 게이트 전극(GATE) 상에 패시베이션층(PSA)이 배치된 구성을 도시하였으나, 본 발명이 이에 한정되는 것은 아니며, 게이트 전극(GATE)과 패시베이션층(PSA) 사이에 다른 절연막 등의 구성이 추가될 수 있다.

- [0276] 패시베이션층(PSA) 상에 픽셀 전극(PXL)이 위치할 수 있다. 픽셀 전극(PXL)은 패시베이션층(PSA)의 홀을 통해 제2 전극(E2)과 연결될 수 있다. 여기서, 제2 전극(E2)은 소스 전극이거나 드레인 전극일 수 있다.

- [0277] 도 13에서는 본 발명의 트랜지스터(TR)가 액티브 영역(A/A)에 배치된 구성을 설명하였으나, 본 발명의 실시예들에 따른 트랜지스터(TR)는 패널(PNL)의 외곽 영역인 넌-액티브 영역에도 배치될 수 있다.

- [0278] 이러한 수직 구조 트랜지스터(TR)가 차지하는 면적은 수평 구조 트랜지스터가 차지하는 면적에 비해 좁기 때문에, 본 발명의 실시예들에 따른 트랜지스터(TR)가 넌-액티브 영역에 배치될 경우, 넌-액티브 영역(베젤 영역이라고도함)의 사이즈를 줄일 수 있다.

- [0279] 본 발명의 실시예들에 따른 트랜지스터(TR)는 액티브층(ACT)이 짧은 채널을 구비함으로써 높은 온-커런트 특성을 가질 수 있고, 채널 영역(CHA) 영역 상에 배치된 게이트 절연막(INS)의 두께를 일부분에서만 두껍게 조절하여 S-계를 높임으로써, 가용 데이터 전압 범위를 넓힐 수 있는 효과가 있다.

- [0280] 본 발명의 실시예들에 따른 전자장치가 OLED 패널(PNL)일 경우, 액티브 영역의 서브픽셀(SP) 내에 다수의 트랜 지스터(TR)가 배치될 수 있고, 서브픽셀(SP) 내에 배치된 다수의 트랜지스터(TR) 중 적어도 하나는 본 발명의 실시예들에 따른 트랜지스터(TR) 구조를 가질 수 있다.

- [0281] 이를 도 14 내지 도 17을 통해 구체적으로 검토하면 다음과 같다.

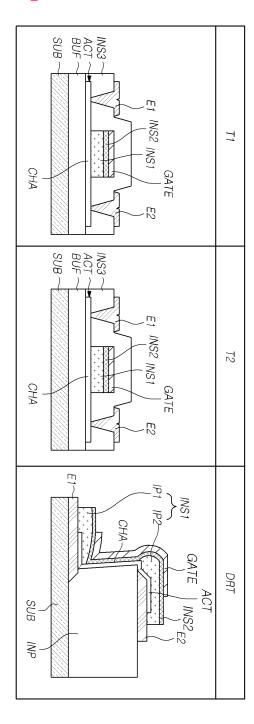

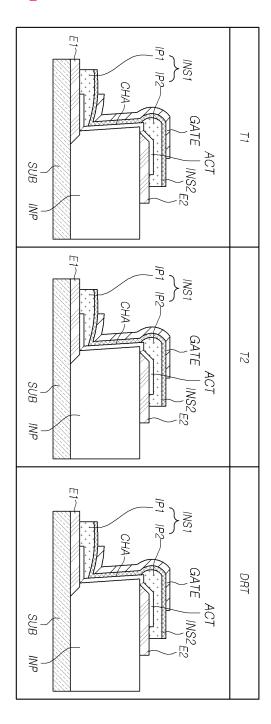

- [0282] 도 14 내지 도 17은 서브픽셀(SP) 내에 배치된 다수의 트랜지스터들의 구조를 도시한 도면이다.

- [0283] 설명의 편의를 위하여 도 14 내지 도 17에서는 하나의 서브픽셀(SP) 내에 3개의 트랜지스터(T1, T2, DR)가 배치된 구성을 중심으로 설명한다(도 4 참조).

- [0284] 도 14를 참조하면, 구동 트랜지스터(TR)는 본 발명의 실시예들에 따른 수직 구조 트랜지스터(TR)일 수 있다.

- [0285] 제1 트랜지스터(T1)와 제2 트랜지스터(T2)는 동일한 구조이며, 구동 트랜지스터(TR)와는 다른 수평 구조 트랜지스터의 수 있다.

- [0286] 구체적으로, 제1 및 제2 트랜지스터(T1, T2)는 기판(SUB) 상에 버퍼층(BUF)이 배치되고, 버퍼층(BUF) 상에 액티 브층(ACT)이 배치될 수 있다.

- [0287] 액티브충(ACT)의 채널 영역(CHA)과 대응되는 영역 상에 제1 게이트 절연막(INS1), 제2 게이트 절연막(INS2) 및 게이트 전극(GATE)이 순차적으로 적충될 수 있다.

- [0288] 게이트 전극(GATE)을 덮으면서 절연막(INS3)이 배치된다.

- [0289] 절연막(INS3) 상에는 제1 전극(E1) 및 제2 전극(E2)이 배치되고, 이들은 절연막(INS3)에 형성된 홀을 통해 액티 브층(ACT)과 컨택될 수 있다.

- [0290] 도 15에서는, 구동 트랜지스터(TR)가 본 발명의 실시예들에 따른 수직 구조 트랜지스터이고, 제1 및 제2 트랜지스터(T1, T2)는 도 14의 제1 및 제2 트랜지스터(T1, T2)와 다른 수평 구조 트랜지스터일 수 있다.

- [0291] 구체적으로, 도 15의 제1 및 제2 트랜지스터(T1, T2)의 구조를 검토하면 다음과 같다.

- [0292] 기판(SUB) 상에 게이트 전극(GATE)이 배치된다.

- [0293] 게이트 전극(GATE) 덮으면서 제1 게이트 절연막(INS1) 및 제2 게이트 절연막(INS2)이 순차적으로 배치된다.

- [0294] 제2 게이트 절연막(INS2) 상에는 액티브충(ACT), 제1 전극(E1) 및 제2 전극(E2)이 배치된다. 액티브충(ACT)의 일 단은 제1 전극(E1)과 중첩되고, 타 단은 제2 전극(E2)과 중첩될 수 있다.

- [0295] 한편, 도 15에는 도시하지 않았으나, 액티브층(ACT) 상에 배치되는 에치 스톱퍼를 더 포함할 수도 있다.

- [0296] 도 14 및 도 15를 참조하면, 본 발명의 실시예들에 따른 수직 구조 트랜지스터(TR)를 구동 트랜지스터(DRT)로 적용할 수 있다.

- [0297] 이와 같이, 액티브층(ACT)이 짧은 채널 영역의 길이를 갖고, S-계수가 높은 수직 구조의 트랜지스터(TR)가 구동 트랜지스터(TR)로 적용됨으로써, 가용 데이터 전압 범위가 넓어져 저 계조 표현에 용이(구동 마진 증가)한 효과 가 있다.

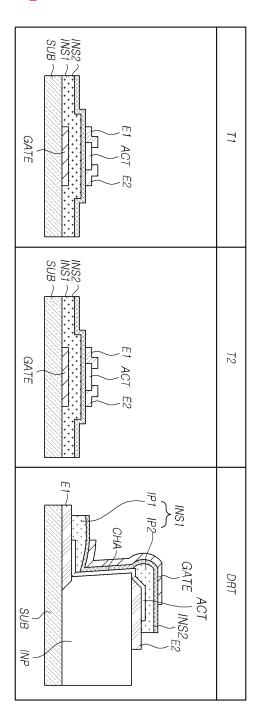

- [0298] 도 16을 참조하면, 구동 트랜지스터(TR)는 본 발명의 실시예들에 따른 수직 구조 트랜지스터(TR)가 적용될 수 있다.

- [0299] 제1 및 제2 트랜지스터(T1, T2)는 동일한 구조이며, 본 발명의 실시예들에 따른 수직 구조 트랜지스터(TR)와 다른 구조의 수직 구조 트랜지스터가 적용될 수 있다.

- [0300] 구체적으로, 제1 및 제2 트랜지스터(T1, T2)는 기판(SUB) 상에 제1 전극(E1)이 배치되고, 제1 전극(E1)의 일 단과 중첩하는 절연 패턴(INP)이 배치될 수 있다.

- [0301] 절연 패턴(INP) 상에는 제2 전극(E2)이 배치될 수 있다.

- [0302] 일 단이 제1 전극(E1)과 중첩되고 타 단이 제2 전극(E2)과 중첩하는 액티브층(ACT)이 배치될 수 있다. 이러한 액티브층(ACT)은 절연 패턴(INP)의 일 측면과 중첩할 수 있다.

- [0303] 액티브층(ACT)을 덮으면서 제1 게이트 절연막(INS1) 및 제2 게이트 절연막(INS2)이 순차적으로 배치될 수 있다.

- [0304] 제2 게이트 절연막(INS2) 상에는 게이트 전극(GATE)이 배치될 수 있다.

- [0305] 제1 및 제2 트랜지스터(T1, T2)에서 액티브층(ACT)과 게이트 전극(GATE) 사이에 배치된 제1 및 제2 게이트 절연 막(INS1, INS2)의 두께는 채널 영역(CHA)에 대응되는 영역에서 균일할 수 있다.

- [0306] 또한, 도 17을 참조하면, 구동 트랜지스터(DR)와 제1 및 제2 트랜지스터(T1, T2) 각각은 본 발명의 실시예들에 따른 수직 구조 트랜지스터(TR)로 적용될 수 있다.

- [0307] 도 16 및 도 17에서와 같이, 서브픽셀(SP)에 배치된 3개의 트랜지스터(TR)를 수직 구조로 형성할 경우, 소자들이 차지하는 면적을 크게 줄일 수 있으므로, 서브픽셀(SP) 사이즈를 대폭 줄일 수 있으므로, 초고해상도 패널 (PNL)을 구현할 수 있는 효과가 있다.

- [0308] 본 발명의 실시예들에 의하면, 액티브층(ACT)의 채널 영역(CHA)이 절연 패턴(INP)의 높이 통해 결정될 수 있으므로 용이하게 짧은 채널을 구현할 수 있고, 수직 구조의 트랜지스터를 제공함으로써, 소자의 크기를 작게 할 수 있으므로 소자의 집적화가 가능하다.

- [0309] 또한, 본 발명의 실시예들에 의하면, 채널 영역(CHA) 상에 배치된 게이트 절연막(INS2, INS2)의 두께를 부분적으로 상이하게 함으로써, 트랜지스터의 S-계수를 높여 구동 마진이 증가한 수직 구조의 트랜지스터 및 전자장치를 제공할 수 있다.

- [0310] 또한, 본 발명의 실시예들에 의하면, MOCVD 또는 ALD 공법을 통해, 액티브층(ACT)의 단선이 없는 구조를 갖는 수직 구조 트랜지스터 및 전자장치를 제공할 수 있다.

- [0311] 여기서, MOCVD 또는 ALD 공법은 우수한 스텝 커버리지(Step Coverage) 특성을 갖는 박막을 형성할 수 있고, 다른 일반적인 증착법에 비해 두께 균일도 및 조성 균일도가 더 우수하고, 더욱 고밀도의 박막을 형성할 수 있는 증착법이다.

- [0312] 또한, 액티브층(ACT)의 채널 영역(CHA) 전체와 중첩하는 제2 게이트 절연막(INS2) 역시 MOCVD 또는 ALD 공법을 통해 형성될 수 있으며, 이로 인해, 얇은 두께를 가지면서 단차가 있는 구조에서도 결함 없이 형성될 수 있다.

- [0313] 본 발명의 실시예들에 의하면, 수직 구조의 트랜지스터를 제공함으로써 소자 면적을 감소 시킬 수 있고, 이를 통해 초고해상도 패널(PNL)을 구현할 수 있다.

- [0314] 본 발명의 실시예들에 의하면, 채널 영역(CHA)의 길이를 짧게 형성함으로써, 트랜지스터의 구동 전류를 증가시키고, 소자 면적 감소로 인해 넌-액티브 영역의 크기를 줄일 수 있는 수직 구조 트랜지스터 및 전자장치를 제공할 수 있다.

[0315] 이상에서의 설명 및 첨부된 도면은 본 발명의 기술 사상을 예시적으로 나타낸 것에 불과한 것으로서, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자라면 본 발명의 본질적인 특성에서 벗어나지 않는 범위에서 구성의 결합, 분리, 치환 및 변경 등의 다양한 수정 및 변형이 가능할 것이다. 따라서, 본 발명에 개시된 실시예들은 본 발명의 기술 사상을 한정하기 위한 것이 아니라 설명하기 위한 것이고, 이러한 실시예에 의하여 본 발명의 기술 사상의 범위가 한정되는 것은 아니다. 본 발명의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사상은 본 발명의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

### 부호의 설명

[0316] SUB: 기판

INP: 절연 패턴

ACT: 액티브층

CHA: 채널 영역

INS1: 제1 게이트 절연막

INS2: 제2 게이트 절연막

S: 소스 전극

D: 드레인 전극

GATE: 게이트 전극

#### 도면

### 도면12

# CTA (Contact Area)

# TR+PXL