(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6218510号

(P6218510)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

G 06 F 11/07 (2006.01)

B 41 J 29/46 (2006.01)

H 04 N 1/00 (2006.01)G 06 F 11/07 1 5 7

B 41 J 29/46 Z

H 04 N 1/00 C

請求項の数 7 (全 8 頁)

(21) 出願番号

特願2013-181349 (P2013-181349)

(22) 出願日

平成25年9月2日(2013.9.2)

(65) 公開番号

特開2015-49731 (P2015-49731A)

(43) 公開日

平成27年3月16日(2015.3.16)

審査請求日

平成28年8月25日(2016.8.25)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100199820

弁理士 西脇 博志

(74) 代理人 100145827

弁理士 水垣 親房

(72) 発明者 高谷 保

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 大塚 俊範

最終頁に続く

(54) 【発明の名称】 画像処理装置、画像処理装置の制御方法、及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のCPUと第2のCPUが通信可能に接続され、

前記第1のCPUが再起動したことに従って、前記第2のCPUが再起動される画像処理装置において、

前記第2のCPUが正常に動作していないことを検知する検知手段と、

前記検知手段により前記第2のCPUが正常に動作していないことが検知されたことに従って、前記第2のCPUをリセットすることなく、前記第1のCPUに通知を行う通知手段と、を有し

前記通知手段からの通知に従って、前記第1のCPUが前記第2のCPUへの電力供給を停止することにより前記第2のCPUをリセットしてから、前記第1のCPUが再起動することを特徴とする画像処理装置。 10

## 【請求項 2】

前記検知手段は、ウォッチドッグタイマであることを特徴とする請求項1に記載の画像処理装置。

## 【請求項 3】

前記第1のCPUが前記通知手段による通知を受け付けたことに従って、前記画像処理装置を再起動することを通知する画面を表示する表示手段を備えることを特徴とする請求項1または2に記載の画像処理装置。

## 【請求項 4】

前記通知手段は、割り込み要求を前記第1のCPUに通知することを特徴とする請求項1乃至3のいずれか一項に記載の画像処理装置。

【請求項5】

前記第1のCPUは、前記通知手段による通知を受け付けたことに従って、エラー処理を抑制し、前記第2のCPUに前記第2のCPUをリセットしてから、前記第2のCPUが正常に動作しなかったことを記憶手段に記憶することを特徴とする請求項1乃至4のいずれか一項に記載の画像処理装置。

【請求項6】

通信可能に接続された第1のCPUと第2のCPUと、を有し、

前記第1のCPUが再起動したことに従って、前記第2のCPUが再起動される画像処理装置の制御方法において、

10

前記第2のCPUが正常に動作していないことを検知する検知工程と、

前記検知工程において、前記第2のCPUが正常に動作していないことが検知されたことに従って、前記第2のCPUをリセットすることなく、前記第1のCPUに通知を行う通知工程と、

前記通知工程において行われた通知に従って、前記第1のCPUが前記第2のCPUへの電力供給を停止することで前記第2のCPUをリセットしてから、前記第1のCPUが再起動する制御工程と、を有することを特徴とする画像処理装置の制御方法。

【請求項7】

請求項6に記載の画像処理装置の制御方法をコンピュータに実行させるためのコンピュータプログラム。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像処理装置、画像処理装置の制御方法、及びプログラムに関するものである。

【背景技術】

【0002】

メイン、サブのそれぞれのボードにCPUを搭載する画像形成装置において、サブ側はリアルタイム制を要求されるデバイス制御、画像処理などを行う。サブ側で制御を行うデバイスにはプリンタ、スキャナ、FAX等があげられる。デバイス制御中にサブ側のソフトに動作不具合が生じた場合、デバイスの制御が意図したタイミングで行えなくなる。

30

デバイスの動作中に制御不能な状態となった場合に、直ちにデバイスを止める必要がある。デバイスを停止するため、サブ側に搭載されるウォッチドッグタイマの機能を用いる。ウォッチドッグタイマはソフトから定められた時間内に定期的にクリアを行う。ソフトに不具合が生じた際にこのクリア動作ができなくなり、定められた時間を経過するとハードウェアにリセットが入る。リセットが入ることにより、デバイス制御用のモジュールがリセット状態となり、デバイス動作を停止させることができる。

このようにメイン、サブから成るマルチCPUシステムにおいて、サブ側のCPUの暴走を検知した際に自動リブートする技術が開示されている（特許文献1参照）。

40

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平4-33138号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、ウォッチドッグタイマを用いてサブ側をリセット状態とした際に、メイン側はサブ側が存在しなくなったように見え、エラー状態となってしまう。このような場合において、メイン側では予想できないサブ側のソフト不具合なので事前通知をサブ側か

50

ら受け取ることもできず、適切な処理を実行できない等の課題があった。

#### 【0005】

本発明は、上記の課題を解決するためになされたもので、本発明の目的は、メインボードがサブボードのデータ処理が正常でない状態に遷移したことを確実に認知して、サブボードを含むシステム全体の再起動処理を開始できる仕組みを提供することである。

#### 【課題を解決するための手段】

#### 【0006】

上記目的を達成する本発明の画像処理装置は以下に示す構成を備える。

第1のCPUと第2のCPUが通信可能に接続され、前記第1のCPUが再起動したことに従って、前記第2のCPUが再起動される画像処理装置において、前記第2のCPUが正常に動作していないことを検知する検知手段と、前記検知手段により前記第2のCPUが正常に動作していないことが検知されたことに従って、前記第2のCPUをリセットすることなく、前記第1のCPUに通知を行う通知手段と、を有し前記通知手段からの通知に従って、前記第1のCPUが前記第2のCPUへの電力供給を停止することにより前記第2のCPUをリセットしてから、前記第1のCPUが再起動することを特徴とする。

#### 【発明の効果】

#### 【0007】

本発明によれば、メインボードがサブボードのデータ処理が正常でない状態に遷移したことを確実に認知して、サブボードを含むシステム全体の再起動処理を開始できる。

#### 【図面の簡単な説明】

#### 【0008】

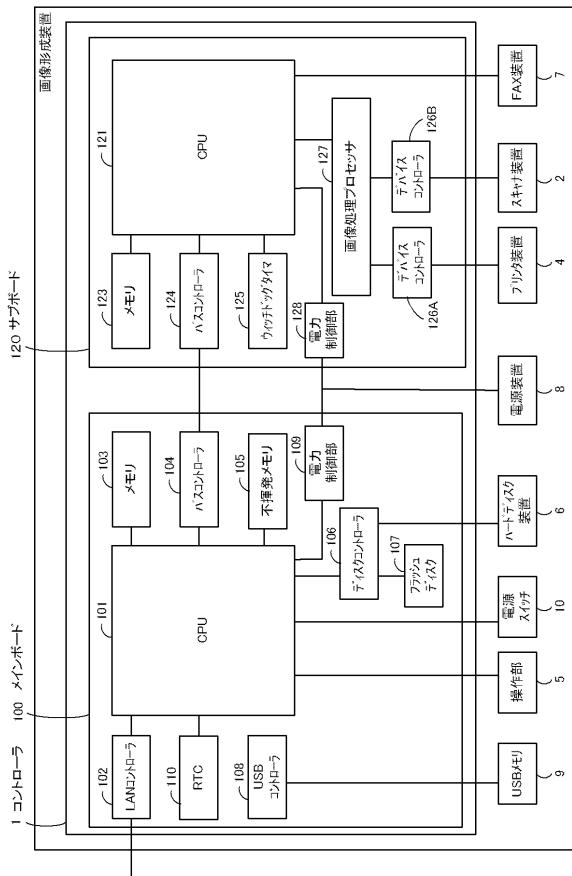

【図1】画像形成装置の構成を説明する図である。

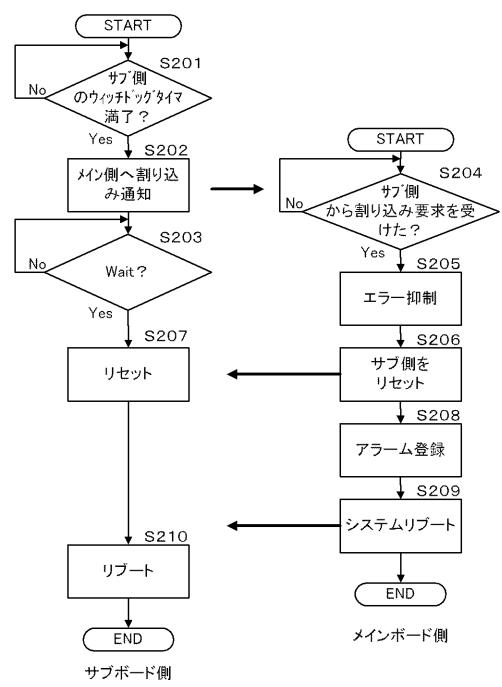

【図2】画像形成装置の制御方法を説明するフローチャートである。

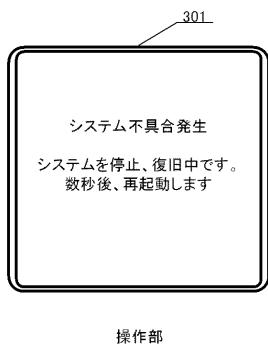

【図3】図1に示した操作部に表示されるUI画面の一例を示す図である。

#### 【発明を実施するための形態】

#### 【0009】

次に本発明を実施するための最良の形態について図面を参照して説明する。

＜システム構成の説明＞

〔第1実施形態〕

図1は、本実施形態を示す画像形成装置の構成を説明する図である。本例は、メインボード100とサブボード120とが通信して画像形成処理を行うデバイスを制御する画像形成装置の例である。なお、本画像形成装置は、プリント機能、スキャナ機能、コピー機能、センド機能等を行うMFP (Multi Function Printer) の例を示す。

図1において、100はメインボードで、いわゆる汎用的なCPUシステムで構成される。101はCPUで、メインボード100全体を制御する。102はLANコントローラで、外部機器とネットワークを通して通信を行う。103はメモリで、CPU101がワークメモリとして使用する。104はバスコントローラで、外部バスとのブリッジ機能を持つ。105は不揮発性メモリで、電源断された場合でも画像形成装置において設定された各種の情報を記憶している。110はリアルタイムクロック( RTC )で、電源が切られても電池で時間を保持し続ける。

#### 【0010】

106はディスクコントローラで、ストレージ装置への読み込み、書き込みを制御する。107はフラッシュディスク(SSD等)で、半導体デバイスで構成された比較的小容量なストレージ装置である。108はUSBコントローラで、USBとのデータアクセスを制御する。

#### 【0011】

メインボード100には外部に、USBメモリ9、操作部5、ハードディスク装置6、が接続される。ハードディスク装置6は記憶装置であればハードディスクである必要は必ずしも無く、不揮発デバイスであればその種を問わない。

10

20

30

40

50

## 【0012】

サブボード120は、比較的小さな汎用CPUシステムと、画像処理ハードウェアから構成される。

サブボード120において、121はCPUで、サブボード全体を制御する。123はメモリで、CPU121がワークメモリとして使用する。124はバスコントローラで、外部バスとのブリッジ機能をする。125はウォッチドッグタイマ(WDT)で、サブボード120のCPU121がプログラム実行中にタイマアップするかどうかを監視して、タイマアップした場合には、メインボード100へ割込要求を通知する。127は画像処理プロセッサで、メモリ123を利用してプリンタ装置4やスキャナ装置2、FAX装置7に適応した所定の画像処理を行う。126A、126Bはデバイスコントローラで、デバイスコントローラ126Aはプリンタ装置4と接続され、デバイスコントローラ126Bはスキャナ装置2と接続される。

10

スキャナ装置2とプリンタ装置4はデバイスコントローラ126を介してデジタル画像データの受け渡しを行う。FAX装置7はCPU121が直接制御を行う。

8は電源装置で、メインボード100とサブボード120の電源を給電する。109、128は電力制御部で、それぞれ対応するメインボード100、サブボード120上の電力が必要な各部への給電を管理する。

## 【0013】

10は電源スイッチで、ユーザの電源OFF、ON操作を受けるもので、電源スイッチが操作されるとCPU101へ割り込みが入る。CPU101は割り込みを検知すると状態に合わせて、電力制御部109を制御する。また、CPU121は、バスコントローラ104、124を介して電源スイッチ10の操作を検知し、電力制御部128を制御する。

20

## 【0014】

なお、図1に示すブロック図において、例えばCPU101、CPU121等にはチップセット、バスブリッジ、クロックジェネレータ等のCPU周辺ハードウェアが多数含まれているが、説明の粒度的に不必要であるため簡略化している。また、本発明の適用は、図1に示す構成を備える場合にのみ制限されるものではない。

## 【0015】

以下、本実施形態を示す画像形成装置におけるコントローラ1の動作について、プリンタ装置4が給紙するシートにスキャナ装置2から読み込む原稿の画像を複写する画像処理時の動作を説明する。

30

ユーザが操作部5から画像複写を指示すると、CPU101がCPU121を介してスキャナ装置2に画像読み取り命令を送る。スキャナ装置2は紙原稿を光学スキャンしデジタル画像データに変換してデバイスコントローラ126を介して画像処理プロセッサ127に入力する。画像処理プロセッサはCPU121を介してメモリ123にDMA転送を行いデジタル画像データの一時保存を行う。

## 【0016】

CPU101は、デジタル画像データがメモリ123に一定量もしくは全て入ったことが確認できると、CPU121を介してプリンタ装置4に画像出力指示を出す。CPU121は画像処理プロセッサ127にメモリ123の画像データの位置(アドレス)を通知する。プリンタ装置4からの同期信号に従ってメモリ123上の画像データは画像処理プロセッサとデバイスコントローラ126を介してプリンタ装置4に送信され、プリンタ装置4にてシートにデジタル画像データが印刷される。なお、プリンタ装置4は、各種のプリント方式があり、電子写真方式やインクジェット方式等のいずれであっても本発明を適用可能である。

40

## 【0017】

ここで、ユーザが操作部5を用いて複数部印刷を行うことを設定している場合、CPU101がメモリ123の画像データをハードディスク装置6に対して保存を行い、2部目以降はスキャナ装置2から画像をもらわざともプリンタ装置4に画像を送ることが可能で

50

ある。

【0018】

画像形成装置を構成するコントローラ3のブロックの待機中は、プリント動作、スキャナ動作を伴うジョブをユーザから受け付けるまでプリンタ装置4、スキャナ装置2への給電は停止している。ユーザ操作を受け付け、そのジョブがプリンタ機能を必要とするジョブと判断された際に、電力制御部128の制御の下で、プリンタ装置4への給電が開始され、プリンタ装置4の初期化動作が実行される。初期化が完了するとユーザ操作によって入力されたジョブが実行される。ジョブ終了後、一定時間が経過すると再びコントローラ1は待機状態となり、実行時に給電が開始されたプリンタ装置4、スキャナ装置2への給電が停止される。

10

【0019】

図2は、本実施形態を示す画像形成装置の制御方法を説明するフローチャートである。本例は、図1に示した画像形成装置のメインボード100とサブボード120とのデータ処理例である。本図を用いて本発明の具体的な処理の内容について述べる。なお、各Sは、メインボード100については、CPU101がメモリ103にロードされる制御プログラムを実行することで実現される。同様に、サブボード120については、CPU121がメモリ123にロードされる制御プログラムを実行することで実現される。

【0020】

S201では、CPU101がウォッチドッグタイマ125が、予め規定しているカウント時間を満了しているか判断する。ここで、カウント時間を満了しているとCPU101が判断した場合はS202へ、満了していないとCPU101が判断した場合はS201を繰り返す。なお、サブボード120のCPU121が正常に動作しているときは、ウォッチドッグタイマ125のタイマを定期的にクリアするためカウント時間を満了しない。

20

一方、サブボード120のCPU121が何らかの要因で正常動作していないときは、ウォッチドッグタイマ(WDT)125のタイマをクリアできないため規定している時間を満了する状態になる。

【0021】

ここで、通常のWDTであれば、WDT125のタイマが満了した時点で、サブボード120のCPU121のリセットを行う。これにより、メインボード100、サブボード120の構成になっている画像形成装置では、サブボード120からメインボード100側にその旨が事前に通知を行うことができずエラーとなってしまう。

30

【0022】

そこで、本実施形態では、S202において、ウォッチドッグタイマ125が、バスコントローラ124、104を介してメインボード100のCPU101へ通知を行う。なお、当該通知の方法はハードウェアによる割り込みが一般的だが形式は問わない。次に、S203では、CPU121がウェイト状態となる。そして、メインボード100側からリセットの通知が入ると(S203)、ウェイト状態から抜けてS207へ進む。

【0023】

次に、S204では、メインボード100のCPU101が、S202でサブボード120側から送られる割込み要求を受信したかを判断する。ここで、割込み要求を受信しているとCPU101が判断した場合、S205へ進み、受信していないとCPU101が判断した場合、S204を繰り返す。

40

【0024】

そして、S205では、メインボード100側のCPU101が、システム全体のエラー検知機能を抑制する。通常、CPU121で動作するソフトに不具合があった場合、その動作をCPU101が検知しエラーとするが、S204以降ではそのようなエラーによる処理を抑制する。エラーの抑制の一例としては、操作部5にエラー表示を行わないことと、内部的にエラー履歴を残さないことにより行う。

【0025】

50

次に、S206では、メインボード100側のCPU101が、電力制御部109、128を介して電源供給を停止することでサブボード120をハードリセット状態とするためのリセット指示を出力する。ここで、サブボード120側のCPU121が制御しているデバイスコントローラ126もリセット状態となり、デバイスコントローラ126先に接続するデバイスを停止することができる。そして、S207では、電力制御部128が、サブボード120をリセット状態とする。

これにより、メインボードがサブボードのデータ処理が正常でない状態に遷移したことを確実に認知して、サブボードを含むシステム全体の再起動処理を開始できる。

#### 【0026】

S208では、メインボード100側のCPU101が、CPU121で動作するソフトに何らかの不具合が生じ、ウォッチドッグタイマ125が満了したことの警告を、不揮発性メモリ105等に確保される領域に登録する。これにより、サービスマンが後ほど、この履歴を参照することによって不具合が発生したことを確認することができる。

そして、S209では、メインボード100側のCPU101がコントローラ1全体を再起動（システムリブート）する。これにより、S210で、サブボード120側のCPU101がS209で行った再起動によってサブボード120も正常に再起動することが可能となる。つまり、メインボード100は、サブボード120がプログラム実行中に暴走するような状態が発生した場合、サブボード120の状態を認識して、サブボード120を安全にリセットさせ、かつ、システム全体として適切な再起動処理を開始できる。

#### 【0027】

図3は、図1に示した操作部5に表示されるUI画面の一例を示す図である。本例は、図2のフローチャートを実行した際にCPU101が操作部5に表示する画面例である。

図3に示すように、サブボード120側のCPU121上で動作するソフト不具合のため、ユーザは何が起こったのか把握することが難しい。そのため、操作部5にその旨を通知する必要がある。

#### 〔第2実施形態〕

#### 【0028】

上記実施形態では、図2のS208において、メインボード100側のCPU101がシステム全体を再起動する場合について説明した。これはシステムを正常に戻すための動作で、メインボード100、サブボード120全体を再起動しないとシステムが復旧できないシステムの動作のためである。

しかしながら、サブボード120のみで再起動してシステム全体が復旧する場合は、S204でサブボード120のみを再起動するように制御してもよい。

これにより、サブボード120側において、CPU121が実行した、図2に示したS207の動作は不要とすることも可能となる。

#### 【0029】

本発明の各工程は、ネットワーク又は各種記憶媒体を介して取得したソフトウェア（プログラム）をパソコン（コンピュータ）等の処理装置（CPU、プロセッサ）にて実行することでも実現できる。

#### 【0030】

本発明は上記実施形態に限定されるものではなく、本発明の趣旨に基づき種々の変形（各実施形態の有機的な組合せを含む）が可能であり、それらを本発明の範囲から除外するものではない。

#### 【符号の説明】

#### 【0031】

100 メインボード

120 サブボード

10

20

30

40

【図1】

【図2】

【図3】

---

フロントページの続き

(56)参考文献 特開2007-058787(JP, A)

特開2012-155534(JP, A)

特開2005-219247(JP, A)

特開昭64-072242(JP, A)

特開2001-282302(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11 / 07

G 06 F 11 / 30 - 11 / 34

B 41 J 29 / 46

H 04 N 1 / 00