(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4608177号

(P4608177)

(45) 発行日 平成23年1月5日(2011.1.5)

(24) 登録日 平成22年10月15日(2010.10.15)

(51) Int.Cl.

F 1

G 11 C 11/15 (2006.01)

H 01 L 27/105 (2006.01)

H 01 L 21/8246 (2006.01)

H 01 L 43/08 (2006.01)

G 11 C 11/15 11 O

H 01 L 27/10 447

H 01 L 43/08 Z

請求項の数 18 (全 18 頁)

(21) 出願番号

特願2002-311295 (P2002-311295)

(22) 出願日

平成14年10月25日 (2002.10.25)

(65) 公開番号

特開2003-187570 (P2003-187570A)

(43) 公開日

平成15年7月4日 (2003.7.4)

審査請求日

平成16年6月11日 (2004.6.11)

審判番号

不服2008-1568 (P2008-1568/J1)

審判請求日

平成20年1月18日 (2008.1.18)

(31) 優先権主張番号

10/000652

(32) 優先日

平成13年10月31日 (2001.10.31)

(33) 優先権主張国

米国(US)

(73) 特許権者

390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人

100072349

弁理士 八田 幹雄

(74) 代理人

100110995

弁理士 奈良 泰男

(74) 代理人

100114649

弁理士 宇谷 勝幸

最終頁に続く

(54) 【発明の名称】 MRAMアレイ内のセルのための一様な磁気環境

## (57) 【特許請求の範囲】

## 【請求項 1】

一様な磁気環境を有する磁気メモリであって、

磁化容易軸を有し、アレイを画定するために複数の行および列に配列される複数の磁気メモリセルであって、前記磁気メモリセルが前記アレイ内の内側位置または周辺位置の選択された一方に配置され、前記内側位置を有する前記磁気メモリセルが、隣接する前記磁気メモリセルによって生成される第1の一様な磁気環境に晒され、前記第1の一様な磁気環境が、前記内側位置を有する磁気メモリセルと前記隣接する磁気メモリセルとによって生成される切替え磁界の大きさに影響を及ぼす、複数の磁気メモリセルと、

行方向および列方向においてそれぞれ前記磁気メモリセルを横切る行導体および列導体と、及び

磁化容易軸を有し、前記周辺位置を有する前記磁気メモリセルのうちの選択された1つまたは複数の磁気メモリセルに隣接して配置される複数のダミー磁気セルとを含み、前記周辺位置を有する磁気メモリセルが、隣接する前記磁気メモリセルと隣接する前記ダミー磁気セルとによって生成される第2の一様な磁気環境に晒され、前記第2の一様な磁気環境が、前記第1の磁気環境と概ね同じように、前記周辺位置を有する磁気メモリセルと、前記ダミー磁気セルと、前記隣接する磁気メモリセルとによって生成される切替え磁界の大きさに影響を及ぼす、磁気メモリ。

## 【請求項 2】

前記磁気メモリセルの磁化容易軸と、前記ダミー磁気セルの磁化容易軸とが、互いに概

10

20

ね同一直線をなす、請求項 1 に記載の磁気メモリ。

**【請求項 3】**

前記磁気メモリセルの磁化容易軸と、前記ダミー磁気セルの磁化容易軸とが、前記行方向と概ね同一直線をなす、請求項 2 に記載の磁気メモリ。

**【請求項 4】**

前記行上に配置され、前記周辺位置を有する前記磁気メモリセルに隣接して、前記ダミー磁気セルが配置される、請求項 3 に記載の磁気メモリ。

**【請求項 5】**

前記ダミー磁気セルが、少なくとも 1 つの行バンクに配列され、前記行バンク内の前記ダミー磁気セルが、前記周辺位置を有する磁気メモリセルとペアにされる、請求項 4 に記載の磁気メモリ。

10

**【請求項 6】**

前記磁気メモリセルの前記磁化容易軸と、前記ダミー磁気セルの前記磁化容易軸とが、前記列方向と概ね同一直線をなす、請求項 2 に記載の磁気メモリ。

**【請求項 7】**

前記列上に配置され、前記周辺位置を有する磁気メモリセルに隣接して、前記ダミー磁気セルが配置される、請求項 6 に記載の磁気メモリ。

**【請求項 8】**

前記ダミー磁気セルが、少なくとも 1 つの列バンクに配列され、前記列バンク内の前記ダミー磁気セルが、前記周辺位置を有する磁気メモリセルとペアにされる、請求項 7 に記載の磁気メモリ。

20

**【請求項 9】**

前記磁気メモリセルの前記磁化容易軸と、前記ダミー磁気セルの前記磁化容易軸とが、1 つのベクトルと概ね同一直線をなす、請求項 2 に記載の磁気メモリ。

**【請求項 10】**

前記ダミー磁気セルが、前記行導体および前記列導体のうちの選択された一方によって横切られる、請求項 1 に記載の磁気メモリ。

**【請求項 11】**

前記ダミー磁気セルが、前記行導体および前記列導体のうちの選択された一方によって横切られ、前記ダミー磁気セルが、前記行導体および前記列導体のうちの前記選択された一方から誘電体材料によって電気的に絶縁される、請求項 1 に記載の磁気メモリ。

30

**【請求項 12】**

前記ダミー磁気セルが前記行導体および前記列導体によって横切られない、請求項 1 に記載の磁気メモリ。

**【請求項 13】**

前記ダミー磁気セルは、前記周辺位置を有する磁気メモリセルが前記ダミー磁気セル、および隣接する磁気メモリセルによって対称的に包囲されるように配置される、請求項 1 に記載の磁気メモリ。

**【請求項 14】**

前記ダミー磁気セルが前記行導体および前記列導体によって交差されない、請求項 13 に記載の磁気メモリ。

40

**【請求項 15】**

前記ダミー磁気セルが、前記行導体および前記列導体のうちの選択された一方によって横切られ、前記ダミー磁気セルが、前記行導体および前記列導体のうちの前記選択された一方から誘電体材料によって電気的に絶縁される、請求項 13 に記載の磁気メモリ。

**【請求項 16】**

前記周辺位置を有するメモリセルのうちの選択された 1 つまたは複数のメモリセルが、前記ダミー磁気セルのうちの少なくとも 2 つとペアにされる、請求項 1 に記載の磁気メモリ。

**【請求項 17】**

50

前記周辺位置を有する磁気メモリセルが、行方向のペアリング、列方向のペアリングおよび対角線方向のペアリングのうちの選択された1つまたは複数のペアリングを有する、請求項1-6に記載の磁気メモリ。

【請求項1-8】

前記ペアリングの結果として、前記周辺位置を有するメモリセルの対称的な包囲のうちの選択された1つまたは複数と、前記周辺位置を有するメモリセルに隣接して配置される行バンクと、前記周辺位置を有するメモリセルに隣接して配置される列バンクとが形成される、請求項1-7に記載の磁気メモリ。

【発明の詳細な説明】

【0001】

10

【発明の属する技術分野】

本発明は全般に磁気ランダムアクセスメモリ内の磁気メモリセルのための一様な磁気環境に関する。より具体的には、本発明は、アレイの周辺部にあるセルが、アレイの内側部分の磁気メモリセルが受ける磁気環境に概ね同一である磁気環境を受ける、磁気メモリセルのアレイに関する。

【0002】

20

【従来の技術】

磁気ランダムアクセスメモリ(MRAM)は、高速アクセスの半導体メモリおよびハードディスクドライブのような従来のデータ記憶デバイスに対する代替形態を提供することができる新進の技術である。たとえば、MRAMを、コンピュータにおいてDRAMの代わりに用いることができる。典型的には、MRAMは磁気メモリセルのアレイを含み、アレイ内の各セルが1ビットのデータ(すなわち、情報)を格納する。アレイ内の各セルは、薄膜からなるいくつかの層を含み、その層のうちのいくつかが磁気特性を有する。これらの層のうちの1つが、変更可能な磁化の向きを有する薄い磁気データ層である。データ層は、安定し、かつ別個の2つの磁気状態を有するように設計される。それらの安定した磁気状態は、バイナリ1およびバイナリ0を定義する。そのデータは薄い磁気膜に格納されるが、アレイ内の各メモリセルは、非常に注意深く制御される磁気層、導電層および誘電体層を含む。

【0003】

30

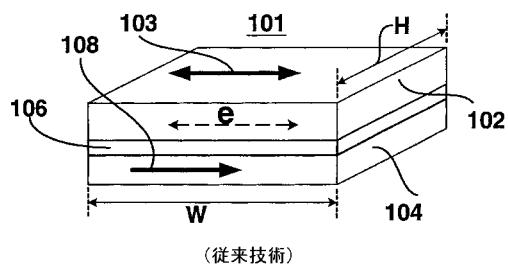

1つの有名なタイプのMRAMセルはスピントンネルデバイスである。スピントンネル効果の物理的現象は、MRAMの技術分野において良く理解されている。図1aでは、従来のスピントンネルメモリセル101が、変更可能な磁化の向き103として1ビットのデータを格納するデータ層102と、磁化の向きが固定された方向108にピン止めされる(pinned)基準層104と、データ層102と基準層104との間に配置される薄い層106とを含む。層106は、トンネル磁気抵抗メモリセル(TMR)内の誘電体層(トンネル障壁層とも呼ばれる)である。層106は同様に、巨大磁気抵抗メモリセル(GMR)では導電層とすることができる。トンネル障壁層106の厚みは通常、2.0nm未満である。形状異方性のため、従来のメモリセル101の幅Wおよび高さHは結果的に、1.0より大きな縦横比(W/H)を有し、変更可能な磁化の向き103がメモリセル101の磁化容易軸eに揃えられるようにすることができる。

40

【0004】

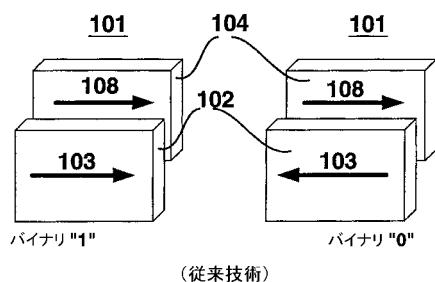

データ層102および基準層104の相対的な向き103および108がバイナリ状態を定義する。たとえば、図1bでは、ピン止めされた向き108および変更可能な向き103が互いに平行である(すなわち、それらが同じ方向を指す)ときに、従来のメモリセル101のデータ層102にバイナリ1が格納される。対照的に、ピン止めされた向き108および変更可能な向き103が互いに反平行である(すなわち、それらが反対の方向を指す)ときに、従来のメモリセル101のデータ層102にバイナリ0が格納される。これらの指示は逆にすることができる。すなわち、平行な向きがバイナリ0であり、反平行な向きがバイナリ1であることもできる。

【0005】

50

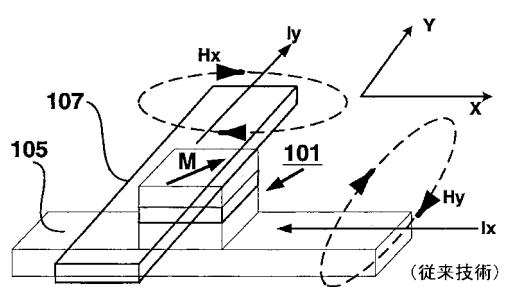

図 1 c では、従来のメモリセル 101 が、直交する方向に（すなわち、互いに 90° をなして）メモリセル 101 を横切る 2 つの導体（105 および 107）間に配置される。行導体 105 が、磁化容易軸（図 1 c では X 軸）に沿ってメモリセル 101 を横切り、列導体 107 が、Y 軸に沿ってメモリセル 101 を横切る。導体（105、107）に流れる電流  $I_y$  および  $I_x$  をそれぞれ用いて磁界  $H_x$  および  $H_y$  を生成することにより、1 ビットのデータが書き込まれる。磁界（ $H_x$ 、 $H_y$ ）はデータ層 102 と相互作用し、変更可能な磁化の向き（図 1 c には M として示される）を、X 軸に関して正の向き（バイナリ「1」）または負の向き（バイナリ「0」）に回転させる。

#### 【0006】

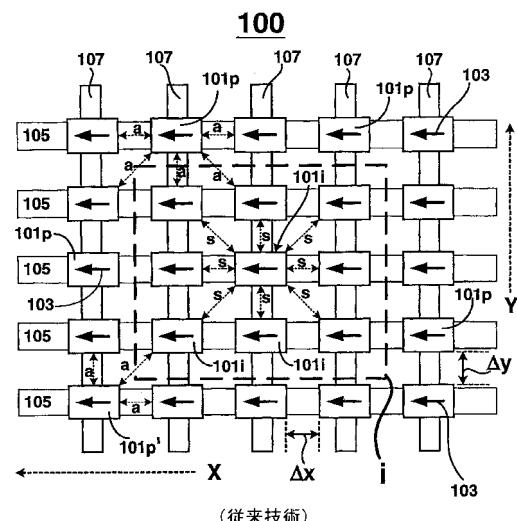

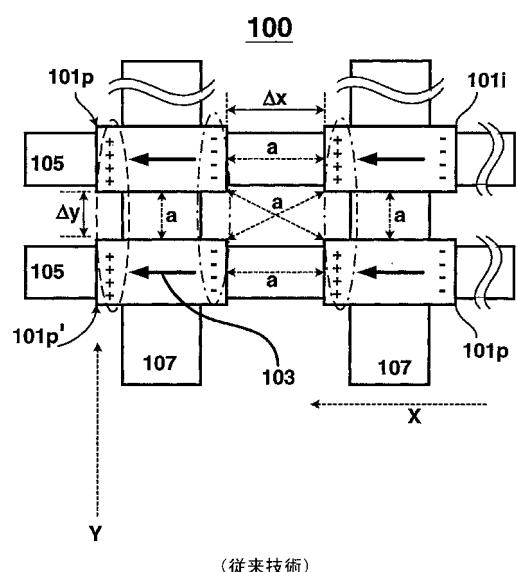

従来のメモリセル 101 は典型的には、同一のメモリセルからなる大規模アレイ内に配置される。図 2 では、従来の M R A M アレイ 100 が、複数の従来のメモリセル 101 を含む。メモリセル 101 はそれぞれ、上述の導体（105、107）間に配置される。たとえば、導体 105 をワード線とし、導体 107 をビット線とすることができる。メモリセル 101 は、X 方向および Y 方向に沿ってそれぞれ所定の距離 X および Y だけ間隔をおいて配置される。結合された磁界（ $H_x$  および  $H_y$ ）が、その現時点の向きから、メモリセル 101 に書き込まれることが望まれるデータを示す新たな向きに、変更可能な磁化の向きを切り替えるだけの十分な大きさを有するように、図 1 c に示されるような電流でメモリセル 101 を横切るワード線およびビット線に磁場を生じさせることにより、アレイ 100 内のメモリセル 101 が書き込み操作に関して選択される。

#### 【0007】

M R A M アレイ 100 の密度（すなわち、単位面積当たりのメモリセル 101 の数）を高めることが望ましい。密度を高めるために、メモリセル 101 のサイズを縮小し、かつメモリセル 101 間の距離（X および Y）を短縮して、セルサイズおよびセル間距離を低減した結果として面積を減少させることにより、M R A M アレイ 100 が、より小さなフットプリントしか占有しないようにする必要とされる。

#### 【0008】

図 2 は、メモリセル 101 から構成される M R A M 100 の図である。これは例示の目的であり、アレイ 100 の実際のサイズは、図示されるものと異なる可能性がある。図 2 では、メモリセル 101 は、行導体 105 の方向に沿って距離 X だけ、かつ列導体 107 の方向に沿って距離 Y だけ間隔をおいて配置される。各メモリセル 101 は、そのセル 101 のための切替え特性に寄与する切替え磁界  $H_c$  を有する。すなわち、切替え特性は結合された磁界（ $H_x$  および  $H_y$ ）の大きさであり、セル 101 を横切る行および列導体（105、107）に流れる書き込み電流に応答して、その磁界によりセル 101 がその変更可能な磁化の向き 103 を切り替えることになる。さらに、各メモリセル 101 は、磁界を生成する磁気ビットを含む。アレイ 100 内の全てのメモリセル 101 から結合された磁界が磁気環境を作り出す。個々のメモリセル 101 に作用する磁気環境は、アレイ 100 内のそのセル 101 の位置に依存するであろう。したがって、メモリセルのうちのいくつか（101i で示される）はアレイ 100 内の内側位置（破線 i を参照）を有し、一方、他のメモリセル（101p で示される）はアレイ 100 内の周辺位置（すなわち、破線 i 内ではない位置）を有する。

#### 【0009】

従来の M R A M アレイ 100 の 1 つの欠点は、ある特定の位置において、メモリセル 101 間の距離（X および Y）が、個々のメモリセル 101 が隣接するメモリセル 101 によって生成される磁気環境によって影響を受けるようになるほど小さくなることである。この磁気環境は、個々のメモリセル 101 の切替え特性に影響を及ぼす。理想的には、アレイ 100 内の全てのメモリセル 101 間で、ばらつきの少ない（tight）切替え特性分布（すなわち、低 の保磁力分布）を有することが望ましい。しかしながら、特定のメモリセル 101 が内側位置を有するか、周辺位置を有するかに応じて、切替え特性がアレイ 100 にわたって変動する。これにより、アレイ 100 の切替え特性分布が増加する。磁気環境がアレイ 100 にわたって変動するために、切替え特性は変動する。

10

20

30

40

50

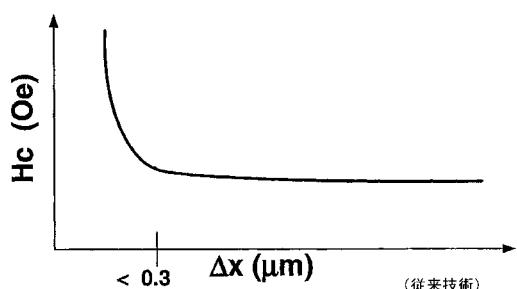

## 【0010】

図2では、内側位置を有する（たとえば、アレイ100の中央にある）メモリセル101iは、隣接するメモリセルによって対称的に包囲される（破線矢印Sを参照）。メモリセル101iに作用する磁気環境は、周辺位置に配置され、隣接するメモリセルによって非対称的に包囲される（破線矢印aを参照）メモリセル101pおよび101p'に作用する磁気環境とは異なる。したがって、メモリセル101pおよび101p'の切替え特性は、メモリセル101iの切替え特性とは異なる。

## 【0011】

図4では、メモリセル101p'が、行および列導体（105、107）の端部に周辺位置を有する。メモリセル101は、上述の磁気環境に寄与する磁極（+および-）を有し、メモリセル101の磁化容易軸103は、行導体105に揃えられる。破線矢印aは、メモリセル101間の磁界相互作用を示す。メモリセル101p'は、3つのメモリセルとのみ磁気的に相互作用し、メモリセル101p'の正極+は、対応する負極-を持たない。なぜなら、それが、行および列導体（105、107）の端部にあるためである。その不釣合いの結果として、メモリセル101p'の切替え特性は、101iまたは101pの場合とは異なることになる。磁化容易軸103に沿った（すなわち、行導体105に沿った）磁界が列導体107に沿った磁界よりも強くなるので、メモリセル101p'の切替え特性は、メモリセル101p'の右隣に配置されるメモリセル101pの切替え特性よりも大きく悪影響を及ぼされる。

## 【0012】

結果として、メモリセル101間の距離が減少すると、個々のセル101間の相互作用が増加する。図3では、Xが0.30μm未満であるとき、距離Xが減少すると、メモリセル101の切替え磁界が著しく増加する。それゆえ、アレイ100にわたって磁気環境が変動する結果として、切替え特性もアレイ100にわたって変動することになる。それらの切替え特性の変動は、周辺位置を有するメモリセル101の場合にさらに大きくなる。

## 【0013】

## 【発明が解決しようとする課題】

したがって、アレイ内の全てのメモリセルに対して一様な磁気環境を有するMRAMアレイが必要とされている。また、周辺位置を有するメモリセルに対して、内側位置を有するメモリセルのための磁気環境と概ね同じ磁気環境を提供することも必要とされている。最後に、アレイ内の全てのメモリセル間で、ばらつきの少ない切替え特性分布を有するMRAMアレイを提供することが必要とされている。

## 【0014】

## 【課題を解決するための手段】

本発明の一様な磁気環境を有するMRAMは上述の問題点を解決する。切替え特性の変動を伴う上述の問題は、周辺メモリセルに作用する磁気環境が、内側位置を有するメモリセルの磁気環境に概ね同一になるように、周辺メモリセルに隣接する位置に、電気的には不活性（inactive）なダミー磁気セルを配置することにより解決される。

## 【0015】

ダミー磁気セルは、MRAMアレイ内の電気的に活性（active）なメモリセルを形成するために用いられる同じ材料の層を用いて形成され得る。ダミー磁気セルは、ダミー磁気セルの磁化容易軸が活性なメモリセルの磁化容易軸に揃えられるように、かつ周辺メモリセルの磁極がダミー磁気セル上の極と相補的に釣り合うように配置され得る。さらに、ダミー磁気セルは、周辺メモリセルが、隣接する磁気セルとダミー磁気セルとの組み合わせによって対称的に包囲されるように配置され得る。

## 【0016】

概して、本発明は一様な磁気環境を有する磁気メモリにおいて具現化される。その磁気メモリは、内側位置および周辺位置を有するアレイを画定するために行および列に配列された複数の磁気メモリセルを含む。その磁気メモリセルは、内側または周辺位置のいずれか

10

20

30

40

50

一方に配置される。各磁気メモリセルは磁化容易軸を含み、1つの行導体および1つの列導体によって横切られる。

【0017】

内側位置に配置される磁気メモリセルは、隣接する磁気メモリセルによって形成される第1の一様な磁気環境に晒される。磁化容易軸を有する複数の電気的に不活性なダミー磁気セル（すなわち、それらはデータを格納せず、読み出しまだ書き込みが行われない）が、周辺位置にある1つまたは複数の磁気メモリセルに隣接して配置される。

【0018】

周辺位置にある磁気メモリセルは、隣接する磁気メモリセルと隣接するダミー磁気セルによって形成される第2の一様な磁気環境に晒される。第2の一様な磁気環境は、第1の一様な磁気環境に概ね等しい。結果として、磁気メモリは、アレイの全体にわたって一様な磁気環境を有し、その結果、アレイ内の磁気メモリセル間（すなわち、周辺位置および内側位置の磁気メモリセル間）の切替え特性も一様になる。

【0019】

本発明の一実施形態では、第1の一様な磁気環境が、内側位置と、隣接する磁気メモリセルとを有する磁気メモリセルによって生成される切替え磁界の大きさに影響を及ぼす。また、第2の一様な磁気環境は、第1の一様な磁気環境と概ね同じように、周辺位置と、ダミー磁気セルと、隣接する磁気メモリセルとを有する磁気メモリセルによって生成される切替え磁界の大きさに影響を及ぼす。

【0020】

本発明の他の態様および利点は、一例として本発明の原理を例示する、添付図面とともに取り上げられる、以下の詳細な説明から明らかになるであろう。

【0021】

【発明の実施の形態】

以下の詳細な説明および図面のうちのいくつかの図において、類似の要素は同じ参照番号で特定される。

【0022】

例示のための図面に示されるように、本発明は、一様な磁気環境を有する磁気メモリにおいて具現化される。磁気メモリは、磁化容易軸を有し、アレイを画定するために複数の行および列で配列される複数の磁気メモリセルを含む。磁気メモリセルは、アレイ内の内側位置または周辺位置のいずれかに配置される。行導体および列導体は、行方向および列方向においてそれぞれ、アレイの磁気メモリセルを横切る。内側位置に配置される磁気メモリセルは、隣接する磁気メモリセルによって生成される第1の一様な磁気環境に晒される。

【0023】

磁気メモリセルは、磁化容易軸を有し、周辺位置に配置される選択された1つまたは複数の磁気メモリセルに隣接して配置される複数のダミー磁気セルも含む。結果として、周辺位置に配置される磁気メモリセルは、隣接する磁気メモリセルおよび隣接するダミー磁気セルによって生成される第2の一様な磁気環境に晒される。第2の一様な磁気環境は第1の一様な磁気環境に概ね等しく、アレイ全体の磁気メモリセルが一様な磁気環境に晒されるようにする。一様な磁気環境は、アレイ内の磁気メモリセル間での切替え磁界の変動を伴う前述の問題に対処する。

【0024】

本発明の磁気メモリセルおよびダミー磁気セルは、以下に限定はしないが、トンネル磁気抵抗（TMR）磁気メモリセル、巨大磁気抵抗（GMR）磁気メモリセル、磁気的に軟らかい基準層を含むTMRまたはGMR磁気メモリセル、单一TMR磁気メモリセル、および二重TMR磁気メモリセルを含む任意の磁気メモリシステムを形成するために、MRA Mの技術分野において知られている薄い材料からなるいくつかの層から形成され得る。磁気メモリセルが行および列導体の両方によって横切られ、選択された磁気メモリセルにデータを書き込むために、行および列導体に流れる電流によって生成される磁界が、磁気メ

10

20

30

40

50

モリセルのデータ層と協働して相互作用することができる点で、ダミー磁気セルと磁気メモリセルとは異なる。また、行および列導体を用いて、選択された磁気メモリセルに格納された1ビットのデータを読み出すために、データ層の磁化の向きの状態をセンシング(検出)することもできる。著しく対照的に、本発明のダミー磁気セルは、行導体および列導体の双方によっては横切られず、行導体のみによって、列導体のみによって横切られることができるか、または行および列導体の双方によって横切られず、誘電体材料によってその導体から電気的に絶縁されることができる。

【0025】

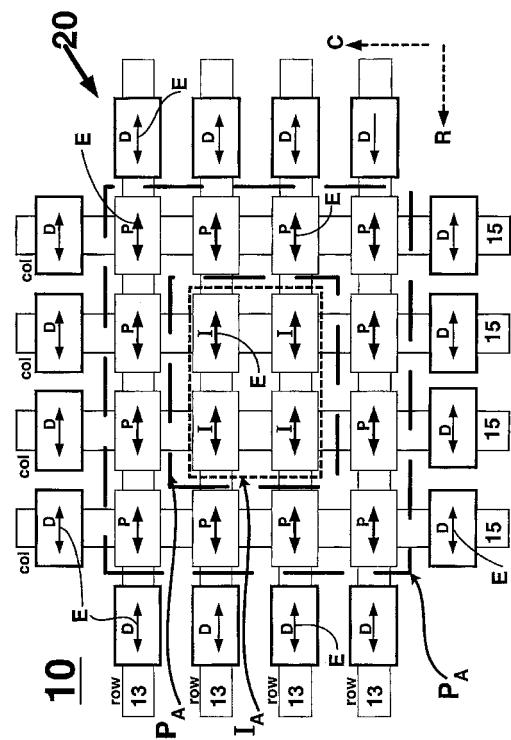

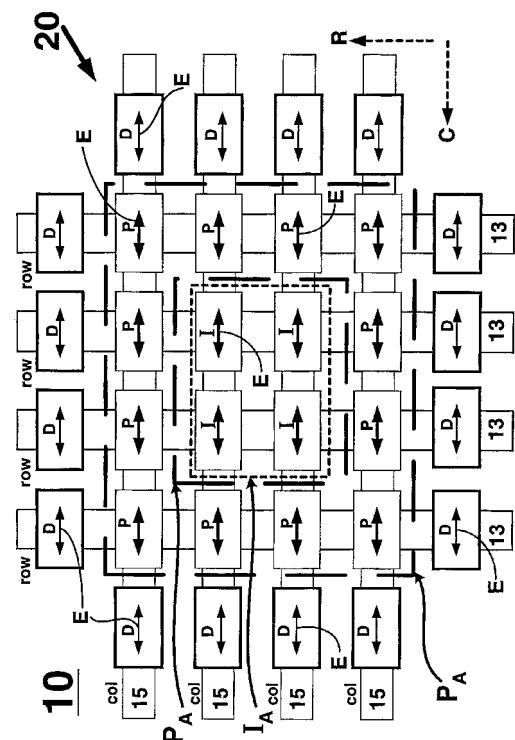

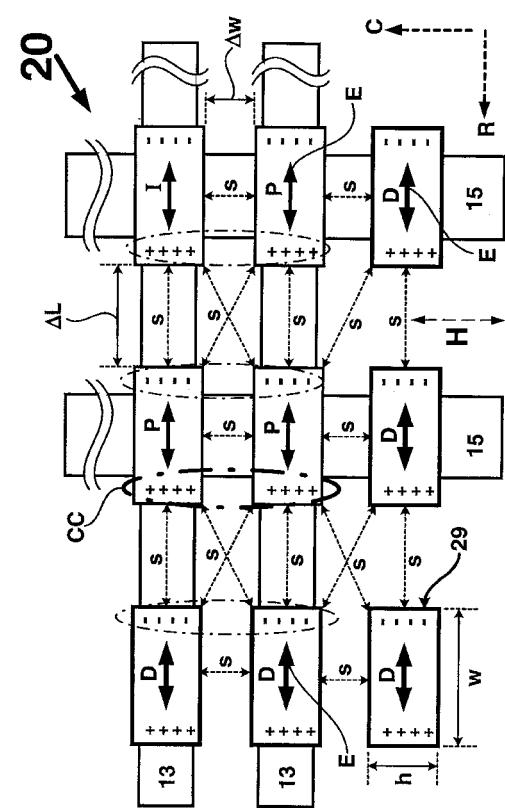

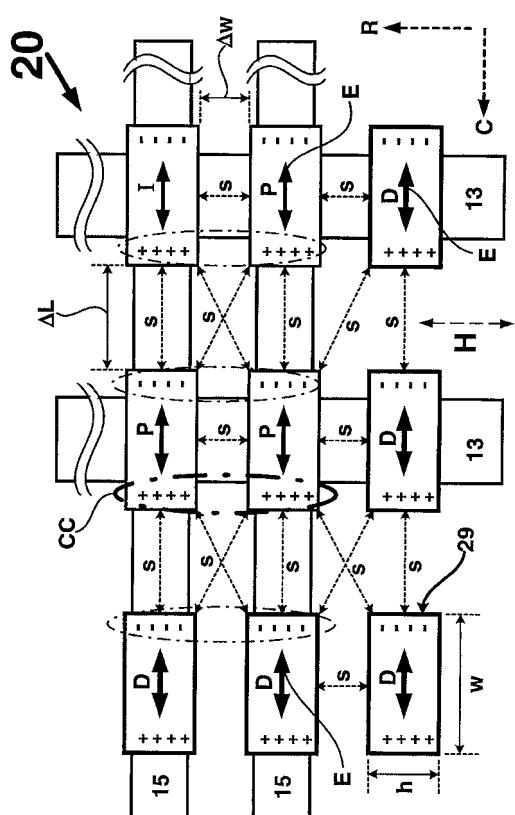

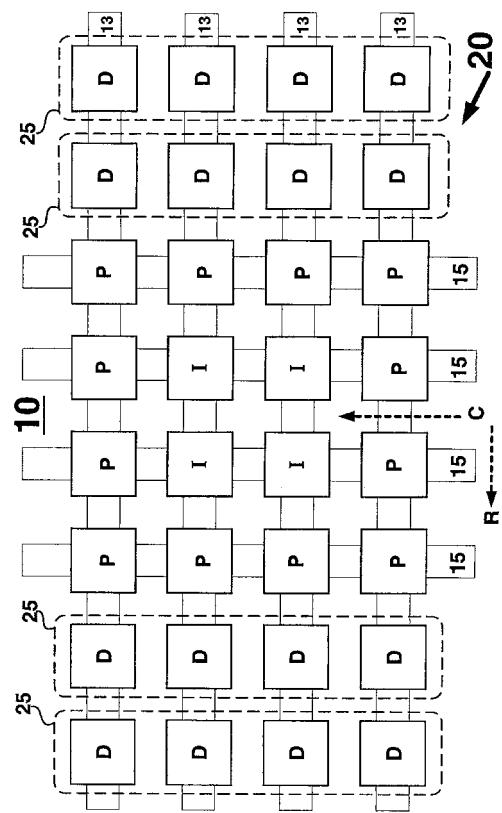

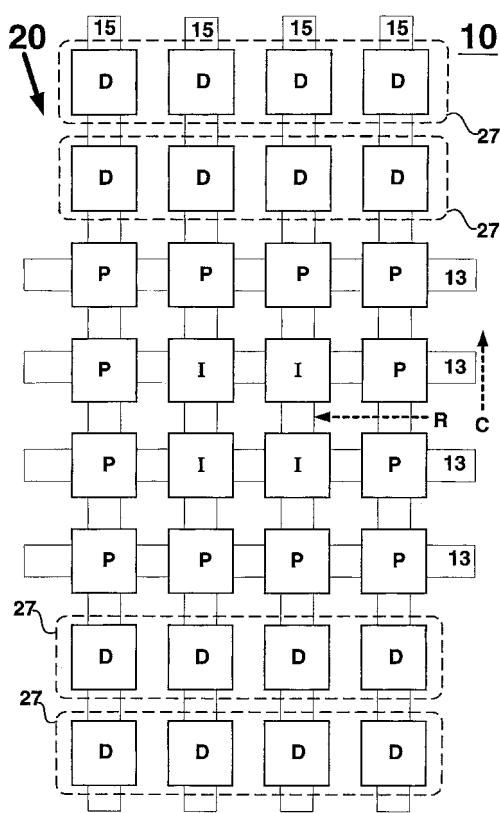

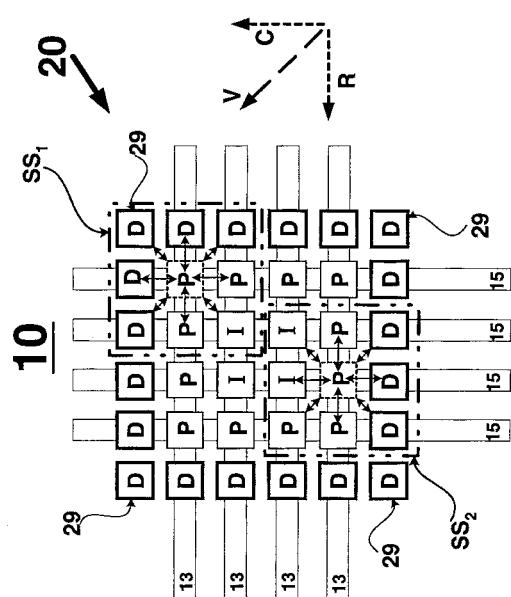

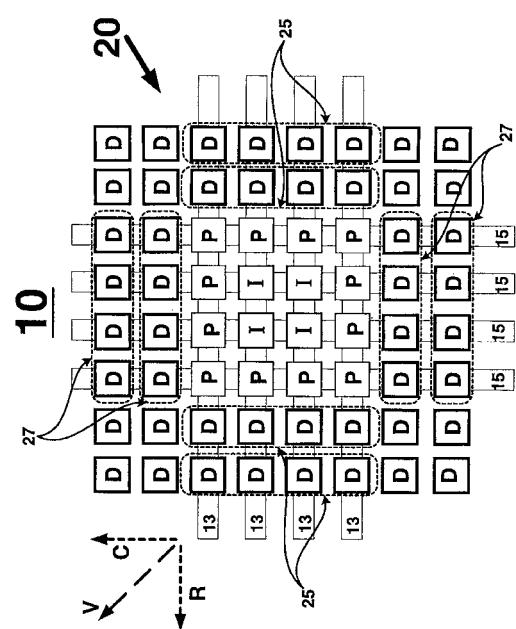

図5aおよび図5bでは、一様な磁気環境を有する磁気メモリ10が、アレイ20を画定するために行および列(図5aおよび図5bのrowおよびcolを参照)に配列される複数の磁気メモリセル(IおよびPとして示される)を含む。磁気メモリセルIは、アレイ20内の内側位置(メモリセルIを囲む破線IAによって示される)に配置され、磁気メモリセルPはアレイ20内の周辺位置(太い破線PAによって示される)に配置される。すなわち、磁気メモリセルPは、破線IAの外側、かつ破線PAの内側に配置される。磁気メモリセル(I、P)は、磁化容易軸Eを含む。ここに示されるようなアレイ20のサイズは、単なる例示であって、任意のサイズのアレイが使用され得る。

【0026】

行導体13および列導体15は、行方向Rおよび列方向Cにおいてそれぞれ磁気メモリセル(I、P)を横切る。典型的には、行および列導体(13、15)は、直交する方向に磁気メモリセル(I、P)を横切る(すなわち、導体が互いに90°の角度で配置される)。

【0027】

内側位置IAを有する磁気メモリセルIは、隣接する磁気メモリセル(I、P)によって生成される第1の一様な磁気環境に晒される。磁化容易軸Eを有する複数のダミー磁気セルDが、周辺位置PAを有する1つまたは複数の磁気メモリセルPに隣接して配置される。周辺位置PAを有する磁気メモリセルは、隣接する磁気メモリセル(I、P)と隣接するダミー磁気セルDとによって生成される第2の一様な磁気環境に晒される。第2の一様な磁気環境は、第1の一様な磁気環境に概ね等しく、磁気メモリ10を構成する活性なメモリセルは、アレイ20の全体にわたって一様な類似の磁気環境を有するようになる。

【0028】

本発明の一実施形態では、第1の一様な磁界は、内側位置IAを有する磁気メモリセルIと、内側位置IAを有するそれらの磁気メモリセルIに隣接する磁気メモリセル(I、P)とによって生成される切替え磁界の大きさに影響を及ぼす。同様に、第2の一様な磁気環境も、周辺位置PAを有する磁気メモリセルPと、ダミー磁気セルDと、周辺位置PAを有するそれらの磁気メモリセルPに隣接する磁気メモリセル(I、P)とによって生成される切替え磁界の大きさに影響を及ぼす。第2の一様な磁気環境は、第1の一様な磁気環境が内側位置IAを有する磁気メモリセルIによって生成される切替え磁界の大きさに影響を及ぼすのと概ね同じように、周辺位置PAを有する磁気メモリセルPによって生成される切替え磁界の大きさに影響を及ぼす。結果として、アレイ20の全体にわたる磁気メモリセル(I、P)の切替え特性は概ね同じになり、磁気メモリセル(I、P)間に、ばらつきの少ない切替え特性分布がもたされる。

【0029】

図5aおよび図5bでは、磁気メモリセル(I、P)およびダミー磁気セルDの磁化容易軸Eは、互いに概ね同一直線をなすことができる。すなわち、磁化容易軸Eは概ね同じ方向に揃えられることができる。

【0030】

図5aに示されるように、本発明の一実施形態では、磁気メモリセル(I、P)およびダミー磁気セルDの磁化容易軸Eは、概ね行方向Rと同一直線にある。

【0031】

また図5aに示される本発明の別の実施形態では、ダミー磁気セルDは、行上(すなわち

10

20

30

40

50

、行導体 13 の端部)に配置され、周辺位置  $P_A$  を有する磁気メモリセル P に隣接して配置されることができる。磁気メモリセル P およびダミー磁気セル D の磁化容易軸 E は行方向 R と概ね同一直線上にある。

【0032】

図 7 に示されるように、本発明のさらに別の実施形態では、ダミー磁気セル D が、少なくとも 1 つの行バンク 25 (2 つが示される) に配列され、行バンク 25 内のダミー磁気セル D は、周辺位置  $P_A$  を有する磁気メモリセル P とペアにされる。それゆえ、図 7 では、周辺位置  $P_A$  を有し、かつ行導体 13 の端部にも位置する磁気メモリセル P が、隣接する行バンク 25 内のダミー磁気セル D とペアにされる。たとえば、前述したように、第 2 の一様な磁気環境が第 1 の一様な磁気環境に概ね等しくなるように、2 つ以上の行バンク 25 が必要とされる場合がある。図 7 には示されないが、磁気メモリセル P およびダミー磁気セル D の磁化容易軸 E は、行方向 R と概ね同一直線をなす。行バンク 25 内のダミー磁気セル D は行導体 13 によって横切られるが、列導体 15 によっては横切られない。前述したように、ダミー磁気セル D は、行および列導体 (13、15) の双方によっては横切られず、行導体 13 のみか、列導体 15 のみによって横切られることができるか、あるいは行または列導体 (13、15) の一方または双方によって横切られず、以下に説明されるように、誘電体材料によってそれらの導体 (13、15) の一方または双方から電気的に絶縁される。

【0033】

図 5 b に示されるように、本発明の一実施形態では、磁気メモリセル (I、P) およびダミー磁気セル D の磁化容易軸 E は、列方向 C と概ね同一直線をなす。

【0034】

また、図 5 b に示されるように、本発明の別の実施形態では、ダミー磁気セル D は、列上 (すなわち、列導体 15 の端部) に配置され、周辺位置  $P_A$  を有する磁気メモリセル P に隣接して配置されることができる。磁気メモリセル P およびダミー磁気セル D の磁化容易軸 E は、列方向 C と概ね同一直線をなす。

【0035】

図 8 に示されるように、本発明のさらに別の実施形態では、ダミー磁気セル D は少なくとも 1 つの列バンク 27 に配列され (2 つが示される)、列バンク 27 内のダミー磁気セル D は、周辺位置  $P_A$  を有する磁気メモリセル P とペアにされる。それゆえ、図 8 では、周辺位置  $P_A$  を有し、列導体 15 の端部にも位置する磁気メモリセル P は、隣接する列バンク 27 内のダミー磁気セル D とペアにされる。前述したように、第 2 の一様な磁気環境が第 1 の一様な磁気環境と概ね等しくなるように、2 つ以上の列バンク 27 が必要とされる場合がある。図 8 には示されないが、磁気メモリセル P およびダミー磁気セル D の磁化容易軸 E は、列方向 C と概ね同一直線をなす。列バンク 27 内のダミー磁気セル D は、列導体 15 によって横切られるが、行導体 13 によっては横切られない。ダミー磁気セル D は、行および列導体 (13、15) のいずれか一方によっては横切られず、行導体 13 のみか、列導体 15 のみによって横切られることができるか、あるいは行または列導体 (13、15) の双方によって横切られず、以下に説明されるように、誘電体材料によってそれらの導体 (13、15) の一方または双方から電気的に絶縁される。

【0036】

磁気メモリ 10 は、図 13 に示されるように、アレイ 20 の周囲に配置される複数の上述した行および列バンク (25、27) を含むことができる。行および列バンク (25、27) 内に存在しないさらなるダミー磁気セル D がアレイ 20 の周囲に配置され、図 9 および図 10 を参照して以下に説明されるように、周辺位置  $P_A$  を有する磁気メモリセル P のうちのいくつかまたは全てを対称的に包囲することができる。

【0037】

図 9 では、周辺位置  $P_A$  を有する磁気メモリセル P がダミー磁気セル D と、隣接する磁気メモリセル (I、P) とによって対称的に包囲されるように、ダミー磁気セル D がアレイ 20 内に配置される。すなわち、周辺位置  $P_A$  を有する全ての磁気メモリセル P が、1 つ

10

20

30

40

50

または複数のダミー磁気セルDと、1つまたは複数の磁気メモリセル(I、P)とによって対称的に包囲される。

【0038】

たとえば、図9では、アレイ20の右上角部において、周辺位置P<sub>A</sub>を有する磁気メモリセルP(すなわち、それは行および列の端部にある)は、ダミー磁気セルDのうちの5つと、磁気メモリセルPのうちの2つ(同様に周辺位置P<sub>A</sub>を有する)と、1つの磁気メモリセルIとによって対称的に包囲される(破線外郭線SS<sub>1</sub>および隣接するセルD、I、P間の両方向矢印を参照)。矢印29は、行または列上に配置されず、かつ行および列導体(13、15)によって横切られないダミー磁気セルDを示す。それらのダミー磁気セルDは、アレイ20の周辺の角部に配置される磁気メモリセルPに対して対角線状に配置される。それらのダミー磁気セルD(すなわち29)は、アレイ20の角部に配置される全ての磁気メモリセルPの上述の対称的な包囲SS<sub>1</sub>を達成するために必要とされる対称性を提供する。

【0039】

対照的に、アレイ20の左下部分の周辺位置P<sub>A</sub>を有する磁気メモリセルPは、ダミー磁気セルDのうちの3つと、磁気メモリセルPのうちの3つ(同様に周辺位置P<sub>A</sub>を有する)と、磁気メモリセルIのうちの2つとによって対称的に包囲される(破線外郭線SS<sub>2</sub>および隣接するセルD、I、P間の両方向矢印を参照)。

【0040】

図9では、ダミー磁気セルDおよび磁気メモリセル(I、P)の磁化容易軸E(図示せず)は、行または列方向(R、C)のうちのいずれか一方と同一直線をなすことができる。代案として、ダミー磁気セルDおよび磁気メモリセル(I、P)の磁化容易軸E(図示せず)は、ベクトルV(図12を参照)と概ね同一直線をなすことができる。ベクトルVは、行または列方向(R、C)に対して測られる角度を有することができるか、あるいはアレイ20に対する任意の予め選択された原点に対して測られる角度を有することができる。

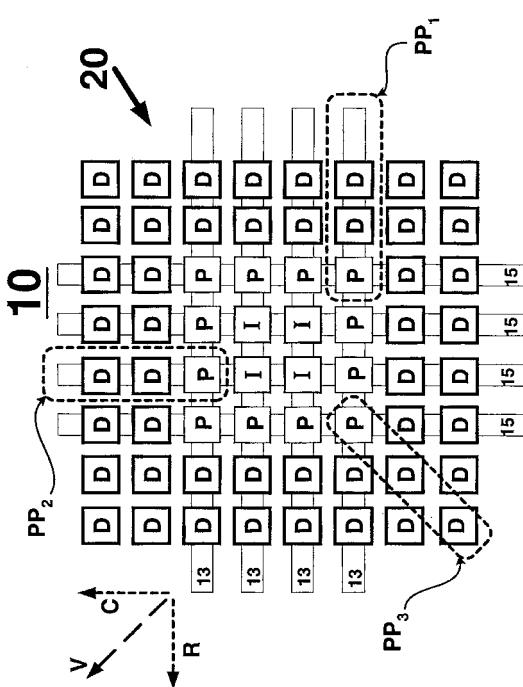

【0041】

図10では、周辺位置P<sub>A</sub>を有する、選択された1つまたは複数の磁気メモリセルPが、ダミー磁気セルDのうちの少なくとも2つとペアにされる。周辺位置P<sub>A</sub>を有する磁気メモリセルPとダミー磁気セルDのうちの少なくとも2つとのペアリングは、破線外郭線PP<sub>1</sub>によって示されるような行方向の(すなわち、行方向Rに沿った)ペアリング、破線外郭線PP<sub>2</sub>によって示されるような列方向の(すなわち、列方向Cに沿った)ペアリング、破線外郭線PP<sub>3</sub>によって示されるような対角線方向の(すなわち、メモリセルPに対して対角線状に配置されるダミー磁気セルとの)ペアリング、またはPP<sub>1</sub>、PP<sub>2</sub>およびPP<sub>3</sub>の任意の組み合わせとすることができます。

【0042】

対角線方向のペアリングPP<sub>3</sub>、列方向のペアリングPP<sub>2</sub>および行方向のペアリングPP<sub>1</sub>(またはそれらの組み合わせ)の結果として、図10に示されるように、かつ図9に関して前述したように(SS<sub>1</sub>およびSS<sub>2</sub>を参照)、周辺位置P<sub>A</sub>を有する磁気メモリセルPのうちのいくつかまたは全ての対称的な包囲を形成することができる。

【0043】

列方向のペアリングPP<sub>2</sub>および行方向のペアリングPP<sub>1</sub>の結果として、図7および図8に関して前述したように、1つまたは複数の行あるいは列バンク(25、27)を形成することもできる。

【0044】

図10では、ダミー磁気セルDおよび磁気メモリセル(I、P)の磁化容易軸E(図示せず)は行または列方向(R、C)のうちのいずれか一方と同一直線をなすことができる。一方、ダミー磁気セルDおよび磁気メモリセル(I、P)の磁化容易軸E(図示せず)は、ベクトルV(図12を参照)と概ね同一直線をなすこともできる。ベクトルVは、行または列方向(R、C)に対して測られる角度を有することができるか、あるいはアレイ2

10

20

30

40

50

0に対する任意の予め選択された原点に対して測られる角度を有することができる。

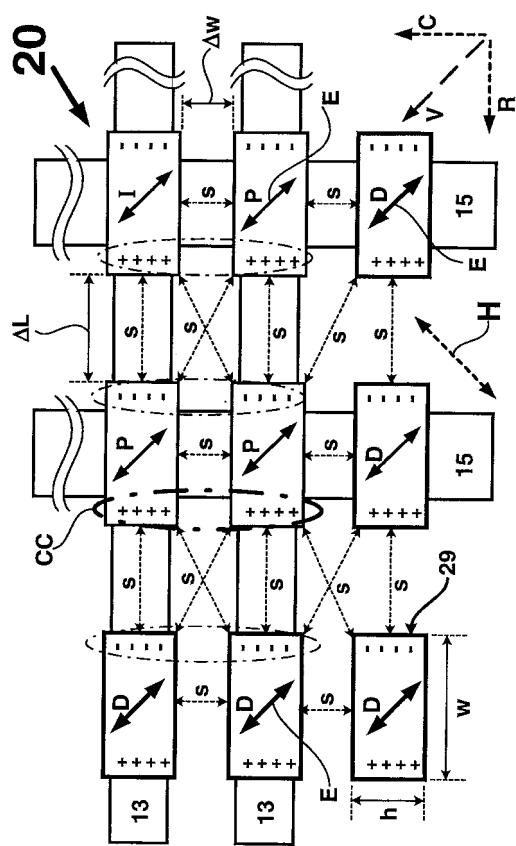

【0045】

図6aおよび図6bでは、第2の一様な磁界を達成するためのダミー磁気セルの配置が、アレイ20の一部を参照して示される。MRAMの技術分野では、形状異方性を解消するために、磁気メモリセルの幅と高さとの比が1.0より大きくされる（すなわち、セルは1より大きな縦横比を有する）ことが良く理解されている。そのため、ダミー磁気セルDおよび磁気メモリセル（I、P）の磁化容易軸Eは、そのセルの幅寸法に沿って揃うように設定されることがある。図6aおよび図6bでは、ダミー磁気セルDおよび磁気メモリセル（I、P）の幅wおよび高さh（ダミー磁気セル29を参照）が、1.0より大きい縦横比（w/h）を与えるように選択される。そのセルがh寸法の高さより、w寸法の長さが著しく長くなるように、縦横比は約3.0であることが好ましい。

10

【0046】

磁化容易軸Eが行方向Rに揃えられる場合（図6aを参照）、あるいは列方向Cに揃えられる場合（図6bを参照）、周辺位置P<sub>A</sub>を有する磁気メモリセルP上の磁極（+）は、行（図6a）または列（図6b）上に配置される隣接するダミー磁気セルD上の対応する磁極（-）によって補整され（破線外郭線CCを参照）、またはその逆の場合も成り立つ。セル（I、P）の変更可能な磁化の向き（図示せず）が磁化容易軸E（両方向矢印によって示されるようないずれかの方向）に沿っているので、任意の所与のメモリセル（I、P）の切替え磁界の影響は、磁化容易軸Eに沿って最も強くなり、磁化容易軸Eを横切る（すなわち、90°をなす）方向において最も弱くなる。その横切る方向は磁化困難軸Hとも呼ばれる。たとえば、磁化容易軸Eが行方向Rに揃えられるとき、磁化困難軸Hは列方向Cに沿って揃えられ、磁化容易軸Eが列方向Cに揃えられるとき、磁化困難軸Hは行方向Rに沿って揃えられる。

20

【0047】

切替え磁界の強さは、メモリセル（I、P）間の距離Lが磁化容易軸Eに沿って減少するのに応じて、著しく増加する。切替え磁界の強さは、メモリセル（I、P）間の距離Wが磁化困難軸Hに沿って減少する際に、それよりは少ない程度に増加する。それゆえ、最初の状況に従って、ダミー磁気セルDの最も有益な配置は、図6aおよび図6bに示されるように、磁化容易軸Eに揃えられる行または列の端部に存在することである。

30

【0048】

したがって、アレイ20にわたって切替え特性を釣り合わせるために、ダミー磁気セルDは、図6aに示されるように、周辺位置P<sub>A</sub>を有する磁気メモリセルPの磁化容易軸Eに揃えられる磁化容易軸Eを有する行13の端部に配置されることがある。結果として、磁化容易軸に沿った磁極は補整され、第2の一様な磁界が第1の一様な磁界と概ね同じになる。

【0049】

一方、アレイ20にわたって切替え特性を釣り合わせるために、ダミー磁気セルDは、図6bに示されるように、周辺位置P<sub>A</sub>を有する磁気メモリセルPの磁化容易軸Eに揃えられる磁化容易軸Eを有する列15の端部に配置されることがある。結果として、磁化容易軸に沿った磁極は補整され、第2の一様な磁界が第1の一様な磁界と概ね同じになる。

40

【0050】

図6aおよび図6bでは、メモリセルP（破線外郭線CCを参照）は、ダミー磁気セルDによる左側にある磁化容易軸Eに沿って、かつメモリセル（I、P）のいずれか一方による右側にある磁化容易軸Eに沿って釣り合った状態にされる。

【0051】

周辺位置P<sub>A</sub>を有する磁気メモリセルPを包囲する磁気環境においてさらなる対称性を与えるために、ダミー磁気セルDは、前述されたように、対角線の位置（参照番号29を参照）に配置されることがある。

【0052】

磁気メモリセル（I、P）およびダミー磁気セルDは、半導体処理技術においてよく知ら

50

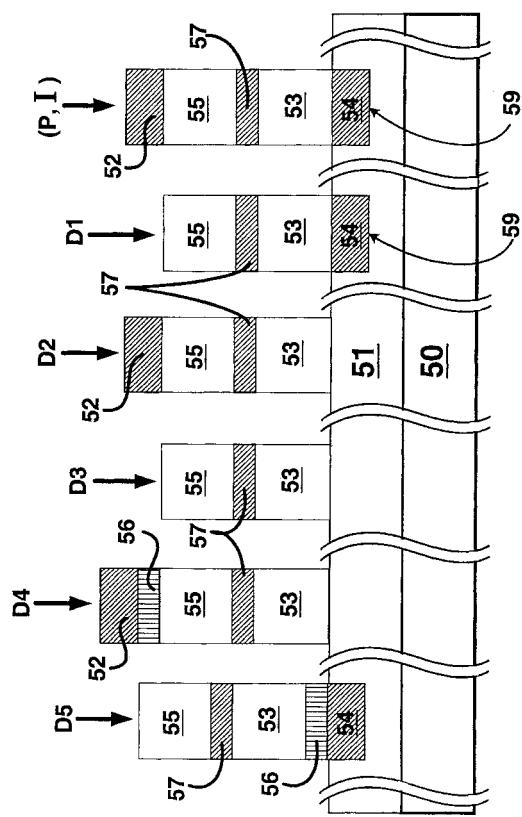

れている超小型電子プロセスを用いて形成され得る。図11では、シリコン(Si)基板のような基板50が、複数の磁気メモリセル(I、P)およびダミー磁気セルDを含むことができる。誘電体層51(たとえばSiO<sub>2</sub>)が基板50上に堆積され得る。ダマシンプロセスを用いてトレンチ59を形成することができ、トレンチ59には、行または列導体(13、15)のいずれか一方を形成するために、第1の導体54が堆積され、その後、平坦化される。次に、メモリセル(I、PまたはD1)の種々の層が導体54上に形成される。メモリセル(I、PまたはD1)は、ピン止めされた基準層53を形成する1つまたは複数の層と、薄いトンネル障壁層57を形成する1つまたは複数の層と、データ層55を形成する1つまたは複数の層とを含むことができる。メモリセル(I、P)の場合、行または列導体(13、15)のいずれか一方を形成するために第2の導体52が堆積される。第2の導体52はダミー磁気セルD1上には堆積されない。それゆえ、ダミー磁気セルDは第1の導体54によってのみ横切られる。

#### 【0053】

一方、ダミー磁気セルD2は、平坦化された誘電体層51上に形成され得る。層53、57および55を形成した後に、ダミー磁気セルD2が第2の導体52によってのみ横切られるように、第2の導体52が堆積される。

#### 【0054】

代案として、ダミー磁気セルD3が、平坦化された誘電体層51上に形成され得る。ダミー磁気セルD3は、第1および第2の導体(54、52)によって横切られない。この構成は、対角線状に配置されるダミー磁気セルD(図6a、図6bおよび図9の参照番号29を参照)に使用され得る。

#### 【0055】

さらに別の構成では、ダミー磁気セルD4が、平坦化された誘電体層51上に形成され得る。ダミー磁気セルD4は第1の導体52によって横切られ、誘電体材料56がダミー磁気セルD4を第1の導体52から電気的に絶縁する。同様に、ダミー磁気セルD5は第2の導体54によって横切られ、誘電体材料56がダミー磁気セルD5を第2の導体54から電気的に絶縁する。誘電体材料56は、たとえば、二酸化シリコン(SiO<sub>2</sub>)のような誘電体材料からなる層とすることができます。この構成は、対角線状に配置されるダミー磁気セルD(図6a、図6bおよび図9の参照番号29を参照)を含む、本明細書に説明される実施形態の任意のものに使用され得る。

#### 【0056】

本発明のいくつかの実施形態が開示および図示されてきたが、本発明は、そのように説明および図示される特定の形態または部品の構成に限定されない。本発明は、特許請求の範囲によってのみ制限される。

#### 【0057】

以下においては、本発明の種々の構成要件の組み合わせからなる例示的な実施形態を示す。

##### 1. 一様な磁気環境を有する磁気メモリであって、

磁化容易軸を有し、アレイを画定するために複数の行および列に配列される複数の磁気メモリセルであって、前記磁気メモリセルが前記アレイ内の内側位置または周辺位置の選択された一方に配置され、前記内側位置を有する前記磁気メモリセルが、隣接する前記磁気メモリセルによって生成される第1の一様な磁気環境に晒される、複数の磁気メモリセルと、

行方向および列方向においてそれぞれ前記磁気メモリセルを横切る行導体および列導体と、及び

磁化容易軸を有し、前記周辺位置を有する前記磁気メモリセルのうちの選択された1つまたは複数の磁気メモリセルに隣接して配置される複数のダミー磁気セルとを含み、前記周辺位置を有する磁気メモリセルが、隣接する前記磁気メモリセルと隣接する前記ダミー磁気セルとによって生成される第2の一様な磁気環境に晒され、前記第2の一様な磁気環境が前記第1の磁気環境に概ね等しい、磁気メモリ。

10

20

30

40

50

2. 前記第1の一様な磁気環境が、前記内側位置を有する磁気メモリセルと前記隣接する磁気メモリセルとによって生成される切替え磁界の大きさに影響を及ぼし、前記第2の一様な磁気環境が、前記第1の磁気環境と概ね同じように、前記周辺位置を有する磁気メモリセルと、前記ダミー磁気セルと、前記隣接する磁気メモリセルとによって生成される切替え磁界の大きさに影響を及ぼす、上記1に記載の磁気メモリ。

3. 前記磁気メモリセルの前記磁化容易軸と、前記ダミー磁気セルの前記磁化容易軸とが、互いに概ね同一直線をなす、上記1に記載の磁気メモリ。

4. 前記磁気メモリセルの前記磁化容易軸と、前記ダミー磁気セルの前記磁化容易軸とが、前記行方向と概ね同一直線をなす、上記3に記載の磁気メモリ。

5. 前記ダミー磁気セルが、前記行上に配置され、前記周辺位置を有する前記磁気メモリセルに隣接して配置される、上記4に記載の磁気メモリ。 10

6. 前記ダミー磁気セルが、少なくとも1つの行バンクに配列され、前記行バンク内の前記ダミー磁気セルが、前記周辺位置を有する磁気メモリセルとペアにされる、上記5に記載の磁気メモリ。

7. 前記磁気メモリセルの前記磁化容易軸と、前記ダミー磁気セルの前記磁化容易軸とが、前記列方向と概ね同一直線をなす、上記3に記載の磁気メモリ。

8. 前記ダミー磁気セルが、前記列上に配置され、前記周辺位置を有する磁気メモリセルに隣接して配置される、上記7に記載の磁気メモリ。

9. 前記ダミー磁気セルが、少なくとも1つの列バンクに配列され、前記列バンク内の前記ダミー磁気セルが、前記周辺位置を有する磁気メモリセルとペアにされる、上記8に記載の磁気メモリ。 20

10. 前記磁気メモリセルの前記磁化容易軸と、前記ダミー磁気セルの前記磁化容易軸とが、1つのベクトルと概ね同一直線をなす、上記3に記載の磁気メモリ。

11. 前記ダミー磁気セルが、前記行導体および前記列導体のうちの選択された一方によって横切られる、上記1に記載の磁気メモリ。

12. 前記ダミー磁気セルが、前記行導体および前記列導体のうちの選択された一方によって横切られ、前記ダミー磁気セルが、前記行導体および前記列導体のうちの前記選択された一方から誘電体材料によって電気的に絶縁される、上記1に記載の磁気メモリ。

13. 前記ダミー磁気セルが前記行導体および前記列導体によって横切られない、上記1に記載の磁気メモリ。 30

14. 前記ダミー磁気セルは、前記周辺位置を有する磁気メモリセルが前記ダミー磁気セル、および隣接する磁気メモリセルによって対称的に包囲されるように配置される、上記1に記載の磁気メモリ。

15. 前記ダミー磁気セルが前記行導体および前記列導体によって交差されない、上記1に記載の磁気メモリ。

16. 前記ダミー磁気セルが、前記行導体および前記列導体のうちの選択された一方によって横切られ、前記ダミー磁気セルが、前記行導体および前記列導体のうちの前記選択された一方から誘電体材料によって電気的に絶縁される、上記14に記載の磁気メモリ。

17. 前記周辺位置を有するメモリセルのうちの選択された1つまたは複数のメモリセルが、前記ダミー磁気セルのうちの少なくとも2つとペアにされる、上記1に記載の磁気メモリ。 40

18. 前記周辺位置を有する磁気メモリセルが、行方向のペアリング、列方向のペアリングおよび対角線方向のペアリングのうちの選択された1つまたは複数のペアリングを有する、上記17に記載の磁気メモリ。

19. 前記ペアリングの結果として、前記周辺位置を有するメモリセルの対称的な包囲のうちの選択された1つまたは複数と、前記周辺位置を有するメモリセルに隣接して配置される行バンクと、前記周辺位置を有するメモリセルに隣接して配置される列バンクとが形成される、上記18に記載の磁気メモリ。

【0058】

【発明の効果】

本発明によれば、周辺位置を有するメモリセルに対して、内側位置を有するメモリセルのための磁気環境と概ね同じ磁気環境を提供でき、アレイ内の全てのメモリセルに対して一様な磁気環境を有するM R A Mアレイを実現することができる。

【図面の簡単な説明】

- 【図1 a】従来のスピン依存トンネルメモリセルの斜視図である。

- 【図1 b】図1 aの従来のスピン依存トンネルメモリセルのデータ層の論理状態を示す図である。

- 【図1 c】従来のスピン依存トンネルメモリセルにデータを書き込むための行導体および列導体を示す概略図である。

- 【図2】従来のM R A Mアレイを画定するように構成される図1 cの構成の概略図である 10。

- 【図3】従来のM R A Mアレイ内の従来のスピン依存トンネルメモリセル間の距離を減少させると切替え磁界が増加することを示すグラフである。

- 【図4】従来のM R A Mアレイ内の周辺位置を有する従来のメモリセルのための一様でない磁界環境を示す概略図である。

- 【図5 a】本発明による一様な磁気環境を有するM R A Mアレイの概略図である。

- 【図5 b】本発明による一様な磁気環境を有するM R A Mアレイの概略図である。

- 【図6 a】本発明による、行端において周辺位置を有するメモリセルのための一様な磁気環境の概略図である。

- 【図6 b】本発明による、列端において周辺位置を有するメモリセルのための一様な磁気環境の概略図である 20。

- 【図7】本発明による行バンクで配列されるダミー磁気セルを示す概略図である。

- 【図8】本発明による列バンクで配列されるダミー磁気セルを示す概略図である。

- 【図9】本発明による、対称的に包囲された周辺メモリセルを示す概略図である。

- 【図1 0】本発明による、ダミー磁気セルとペアにされる周辺メモリセルを示す概略図である。

- 【図1 1】本発明による磁気メモリセルおよびダミー磁気セルの断面図である。

- 【図1 2】本発明による、1つのベクトルと同一直線上にある磁化容易軸を有するダミー磁気セルおよび活性な磁気メモリセルを示す概略図である。

- 【図1 3】本発明による、複数の行バンクおよび列バンクで配列されるダミー磁気セルを示す概略図である 30。

【符号の説明】

- 10 磁気メモリ

13 行導体

15 列導体

20 アレイ

50 基板

51 誘電体層

53 基準層

55 データ層

56 誘電体材料

57 トンネル障壁層

D ダミー磁気セル

E 磁化容易軸 40

【図 1 a】

【図 1 b】

【図 1 c】

【図 2】

【図 3】

【図 4】

【図 5 a】

【図 5 b】

【図 6 a】

### 【図 6 b】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

---

フロントページの続き

(72)発明者 ジャニス・エイチ・ニッケル

アメリカ合衆国カリフォルニア州 94087, サニーベイル, キンバリー・ドライブ・1772

合議体

審判長 北島 健次

審判官 加藤 俊哉

審判官 近藤 幸浩

(56)参考文献 特開昭61-214559 (JP, A)

特開2000-188382 (JP, A)

特開平04-061161 (JP, A)

特開平11-265891 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/14 - 11/15

H01L 27/10